# IMPLEMENTATION FEASIBILITY OF AN INTEGRATED LPDDR4 PHY BLOCK

A Master's Thesis Submitted to the Faculty of the Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona Universitat Politècnica de Catalunya by

**Pol Codina Vilanova**

In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONIC ENGINEERING

Advisor: Francesc de Borja Moll Echeto

Barcelona, June 2022

# **<u>Title of the thesis:</u>** Implementation feasibility of an integrated LPDDR4 PHY block

Author: Pol Codina Vilanova

Advisor: Francesc de Borja Moll Echeto

# Abstract

One of the bottlenecks in the performance of academic RISC-V ASIC processors is highspeed memory access. The use of high speed DDR RAM chips on the board requires the integration in the ASIC of a very complex physical interface block (PHY) that encompasses analog and digital parts. This PHY block is thus technology-specific and very expensive to acquire. Recently, Wavious Ltd. published an open-source description of an LPDDR4x and LPDDR5 with an Apache license containing the digital part and wrappers for the analog parts. This master's thesis will start from this implementation, and will study the feasibility and cost of implementation of this IP for the Barcelona Supercomputing Center RISC-V processor initiative.

Dedicated to all my family and specially to my parents and my grandparents who raised me and educated to be the man I am today. Also, to my friends from high school and college who helped me over the years.

# **Acknowledgements**

I wish to express my sincere thanks to all the team members of the BSC, in particular to the members of the computer sciences department for all their knowledge and previous work.

I also thank to my Project Supervisor, Francesc Moll, for guiding me through my thesis.

And finally, I place on record, my sense of gratitude to one and all who, directly or indirectly, have lent their helping hand in this venture.

# **Revision history and approval record**

| Revision | Date       | Purpose             |

|----------|------------|---------------------|

| 0        | 01/02/2022 | Document creation   |

| 1        | 01/07/2022 | Document completion |

|          |            |                     |

|          |            |                     |

| Written by: |                | Reviewed and approved by:   |  |  |

|-------------|----------------|-----------------------------|--|--|

| Date        | 01/07/2022     | Date 01/07/2022             |  |  |

| Name        | Pol Codina     | Name Francesc Moll          |  |  |

| Position    | Project Author | Position Project Supervisor |  |  |

# Table of contents

| Abstract   | t                                                              | 1  |

|------------|----------------------------------------------------------------|----|

| Acknowl    | ledgements                                                     | 3  |

| Revisior   | n history and approval record                                  | 4  |

| Table of   | f contents                                                     | 5  |

| List of Fi | igures                                                         | 7  |

| List of Ta | ables                                                          | 9  |

| 1. Intro   | oduction                                                       | 10 |

| 1.1.       | Context: DRAC project                                          | 10 |

| 1.2.       | BSC Lagarto ASIC                                               | 10 |

| 1.3.       | Wavious open source IP                                         | 11 |

| 1.4.       | Statement of purpose for this thesis                           | 11 |

| 1.5.       | Work plan                                                      | 11 |

| 1.6.       | Deviations from initial plan                                   | 12 |

| 2. Stat    | te of the art of the technology used or applied in this thesis | 13 |

| 2.1.       | LPDDR4                                                         | 13 |

| 2.1.       | .1. DRAM                                                       | 13 |

| 2.1.       | .2. LPDDR4                                                     | 14 |

| 2.1.       | .3. LPDDR4 operation                                           | 15 |

| 2.1.       | .4. Multiple channel connectivity                              | 17 |

| 2.2.       | Digital implementation                                         | 18 |

| 2.3.       | Analog design                                                  | 21 |

| 3. Met     | thodology / project development                                | 22 |

| 3.1.       | Wavious IP                                                     | 22 |

| 3.2.       | Clock structure                                                | 23 |

| 3.3.       | Synthesis process                                              | 27 |

| 3.3.       | .1. Physical libraries                                         | 27 |

| 3.3.       | .2. Synthesis issues                                           | 27 |

| 3.3.       | .3. Empty modules                                              | 28 |

| 3.4.       | Full Custom blocks: analog and mixed-signal                    | 29 |

| 3.4.       | .1. wphy_lp4x5_cmn_clks_svt.sv - Common clock driver           | 29 |

| 3.4.       | .2. wphy_rpll_mvp_4g.sv - Multi-VCO PLL                        |    |

#### UNIVERSITAT POLITÈCNICA DE CATALUNYA BARCELONATECH

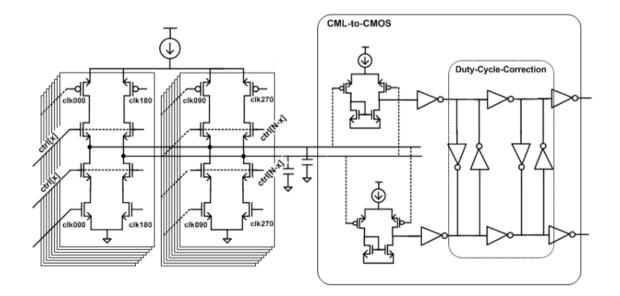

|     | 3.4.3.    | wphy_clk_div_4ph_10g_dlymatch_svt.sv - 4 phase clock divider of 31 | delay match |

|-----|-----------|--------------------------------------------------------------------|-------------|

|     | 3.4.4.    | wphy_clk_div_4ph_10g_svt.sv - 4 phase clock divider                | 31          |

|     | 3.4.5.    | wphy_pi_4g.sv - Phase interpolator                                 | 32          |

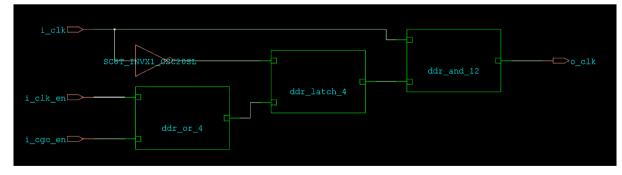

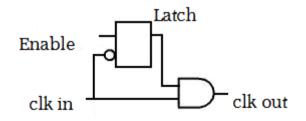

|     | 3.4.6.    | wphy_cgc_diff_lvt.sv - Differential clock gating cell (rest low)   | 33          |

|     | 3.4.7.    | wphy_pi_dly_match_4g.sv - Phase interpolator delay match           | 33          |

|     | 3.4.8.    | wphy_clk_div_2ph_4g_svt.sv - 2 phase clock divider                 | 33          |

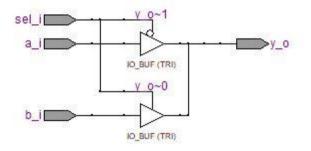

|     | 3.4.9.    | wphy_clkmux_3to1_diff.sv - Differential 3:1 clock mux              | 34          |

|     | 3.4.10.   | wphy_prog_dly_se_4g.sv - Programmable delay                        | 34          |

|     | 3.4.11.   | wphy_2to1_14g_rvt.sv - Differential 2:1 serializer                 |             |

|     | 3.4.12.   | LVSTL pin drivers                                                  |             |

|     | 3.4.13.   | wphy_lp4x5_cmn.sv - Common clock                                   |             |

| 3   | .5. Ger   | nerating placeholders                                              | 37          |

| 3   | .6. SR/   | ۹M                                                                 |             |

| 4.  | Results   |                                                                    | 40          |

| 5.  | Budget.   |                                                                    | 44          |

| 6.  | Conclus   | ions and future development                                        | 45          |

| 7.  | Bibliogra | aphy                                                               | 46          |

| 8.  | Appendi   | ces                                                                | 48          |

| Glo | ssary     |                                                                    | 49          |

# List of Figures

| Figure 1 Lagarto chip with the support FPGA                                                  | 10 |

|----------------------------------------------------------------------------------------------|----|

| Figure 2 DRAM bank composition [3]                                                           | 13 |

| Figure 3 SDRAM development tree [5]                                                          | 14 |

| Figure 4 Activate operation [7]                                                              | 16 |

| Figure 5 Burst read operation [7]                                                            | 16 |

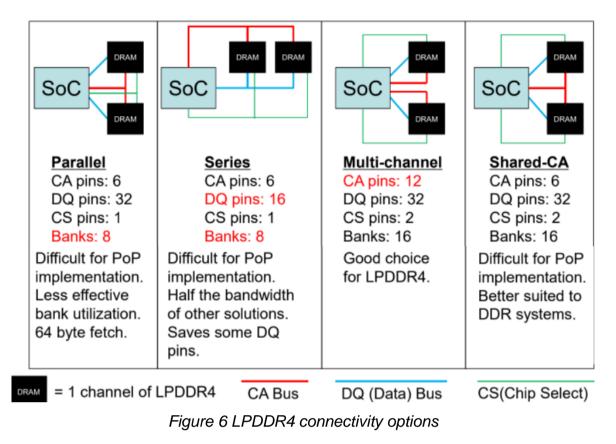

| Figure 6 LPDDR4 connectivity options                                                         | 18 |

| Figure 7 General IC design flow                                                              | 19 |

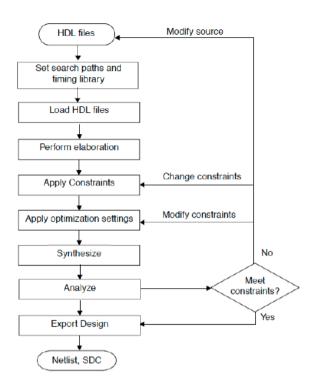

| Figure 8 Generic Genus Work Flow                                                             | 20 |

| Figure 9 System Block Diagram                                                                | 22 |

| Figure 10 DDR PHY Top Level Block Diagram                                                    | 22 |

| Figure 11 Clock distribution diagram                                                         | 23 |

| Figure 12 SimVision results                                                                  | 24 |

| Figure 13 From Cadence Genus Command Reference 21.1                                          | 25 |

| Figure 14 Clock gating cell visualized                                                       | 26 |

| Figure 15 Unresolved references found by Genus                                               | 29 |

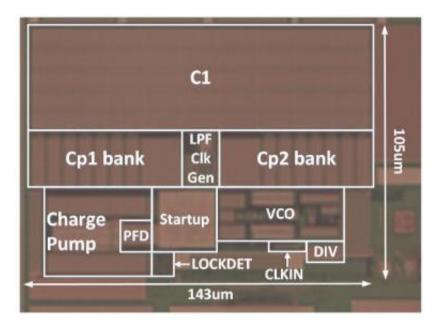

| Figure 16 22nm PLL [13]                                                                      | 31 |

| Figure 17 Diagram of proposed topology of two-phase mixing                                   | 32 |

| Figure 18 Typical clock gating cell                                                          | 33 |

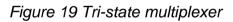

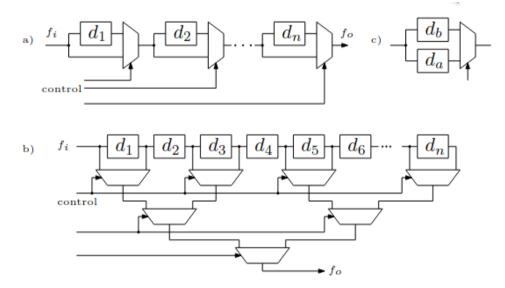

| Figure 19 Tri-state multiplexer                                                              | 34 |

| Figure 20 PDC delay line structure: (a) cascaded design (b) tree-like des differential delay |    |

| Figure 21 Load based delay line                                                              | 36 |

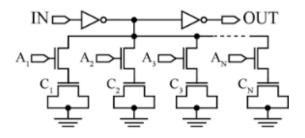

| Figure 22 Typical 2:1 serializer                                                             | 36 |

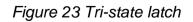

| Figure 23 Tri-state latch                                                                    | 36 |

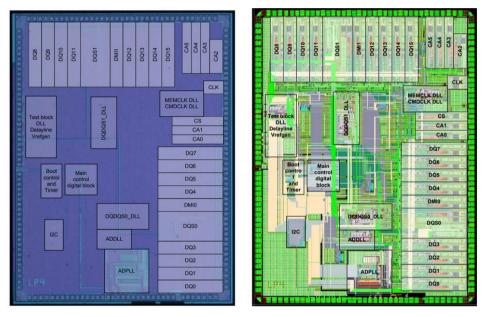

| Figure 24 LPDDR4 controller micrograph                                                       | 37 |

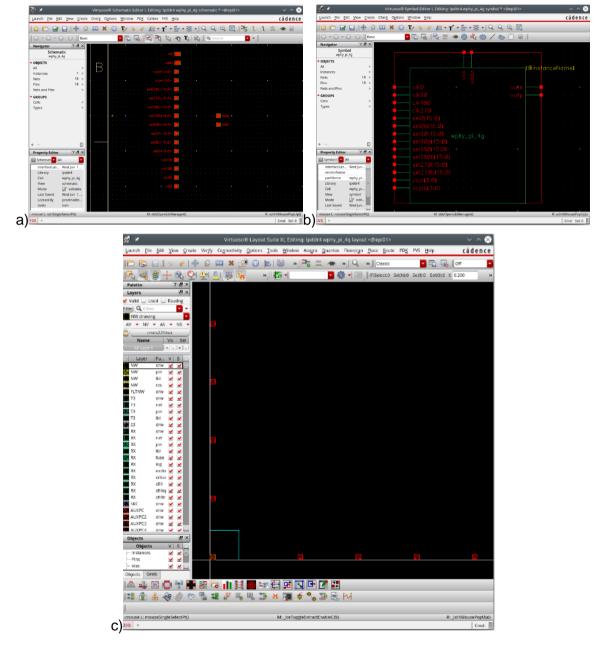

| Figure 25 a)Virtuoso schematics, b) symbol and c) layout                                     | 38 |

| Figure 26 Abstract generator                                                                 | 39 |

| Figure 27 SRAM area report                                                                   | 39 |

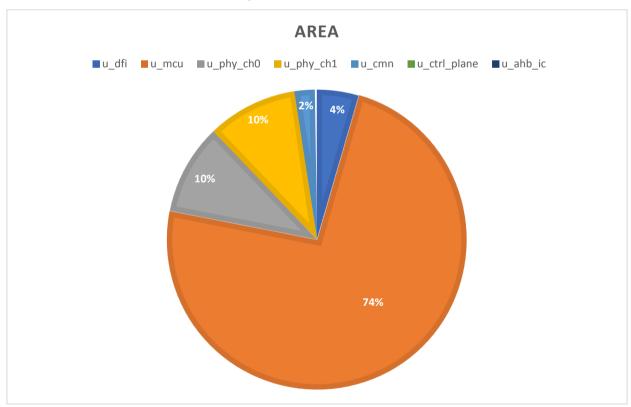

| Figure 28 final area report                                                                  | 40 |

| Figure 29 Area distribution                                                                  | 40 |

| Figure 30 Final gates report                                                                 | 41 |

| Figure 31 Final timing report                                                                | 42 |

| Figure 32 Slack distribution | 43 |

|------------------------------|----|

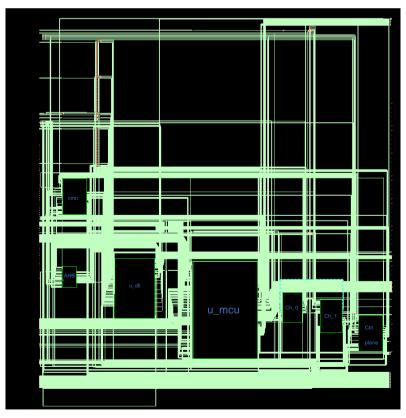

| Figure 33 GUI representation | 43 |

# List of Tables

| Table 1 Work plan               | 12 |

|---------------------------------|----|

| Table 2 LPDDR4 vs DDR4          | 15 |

| Table 3 Command truth table [7] | 17 |

# 1. Introduction

# 1.1. <u>Context: DRAC project</u>

DRAC is a project to develop a new processor and several open source accelerators [1]. DRAC (Designing RISC-V-based Accelerators for next generation Computers) is a new step in research led by the Barcelona Supercomputing Center (BSC) to manufacture open source chips from Europe. The project has the collaboration of the Universitat Politecnica de Catalunya (UPC), the Universitat de Barcelona (UB), the Universitat Autònoma de Barcelona (UAB) and the Universitat Rovira i Virgili (URV).

Both the processor and accelerators will be based on the RISC-V technology, which is the architecture with ISA (nomenclature that refers to the Instruction Set Architecture) open source chosen by the BSC for Lagarto and for the accelerator being developed in the EPI (European Processor Initiative) project.

# 1.2. BSC Lagarto ASIC

The first ASIC to be manufactured as part of the DRAC project was preDRAC Figure 1, containing a Lagarto processor.

Lagarto, built with TSMC's 65-nanometer transistors, is the first open-source instruction set architecture (ISA) processor developed in Spain, coordinated by the Barcelona Supercomputing Center (BSC). The preDRAC chip, was a key step in the center's strategy to become a benchmark in the open-source hardware technologies' field developed in Europe.

Figure 1 Lagarto chip with the support FPGA

The current implementation of the Lagarto processor needs to be supported by an FPGA that provides access to the DRAM memory as it is shown in Figure 1. The communication is carried out through AXI low speed (32b@50MHz through FMC connector: 200 Mbps), this poses a limitation on the access speed to the DDR3 memory, which has a theoretical performance of 64b@800MHz DDR: 12800 Mbps.

Other communication options are being explored currently that could improve the speed up to 1000 Mbps, but the best solution in terms of performance is an integrated DDR controller to access on-board DDR memory chips.

The physical interface (PHY) between the on-board DDR memory chips and the on-chip memory controller requires a high-speed interface with multiple analog and mixed-signal components. Multiple IP vendors have designs for sale. However it is a very expensive IP to buy (order of 250.000€).

# 1.3. <u>Wavious open source IP</u>

Wavious [2], a fabless semiconductor company which offers a platform based on mix-andmatch "chiplets," has released a RISC-V-powered open-source LPDDR4x/5 PHY – under the permissive Apache 2.0 licence.

The Wavious DDR PHY supports LPDDR4x and LPDDR5 standards and as further explained in section 3.1 is provided in a single 32-bit channel (1x32) configuration (Memory Controller side) consisting of two 16-bit channels (DRAM side). The single 32-bit channel configuration is chosen to mitigate MCU+SRAM area overhead to DRAM interface width.

The Wavious DDR PHY was initially developed in the GF12LPP process (12nm FinFET from Globalfoundries). Although the DDR PHY is highly digital in nature to improve portability to various foundries and process nodes, the DRAM protocol's high transfer rates and varying channel characteristics still require high performance mixed-signal and analog PHY circuits. The Wavious DDR PHY design includes various wrappers to ease standard cell migration and analog models for simulations. In order to port the DDR PHY to other process nodes, designers must perform two tasks. Firstly, designers must incorporate process-specific standard cells into the technology wrappers. Secondly, designers must create analog and mixed-signal schematics/layout which implement high performance circuits.

## 1.4. <u>Statement of purpose for this thesis</u>

The key points of this thesis are the following:

- Understand LPDDR & DDR PHY

- Understand the structure of the Wavious LPDDR4 PHY.

- Identify necessary analog components and their characteristics.

- Perform a size estimation of the analog components.

- Make a trial physical implementation using black boxes for analog blocks

| Task                           | Duration | Start    | End      |

|--------------------------------|----------|----------|----------|

| Research on DDR and LPDDR4     | 25 days  | 31/1/22  | 04/03/22 |

| Signals involved               | 25 days  | 31/1/22  | 04/03/22 |

| Timing and protocols           | 25 days  | 31/1/22  | 04/03/22 |

| MS1: presentation about LPDDR4 | 0 days   | 04/03/22 | 04/03/22 |

| Wavious LPDDR4 IP              | 30 days  | 07/03/22 | 15/4/22  |

| Structure of the digital part  | 12 days  | 07/03/22 | 22/3/22  |

## 1.5. Work plan

| Structure of the analog part                 | 25 days   | 12/03/22     | 15/4/22  |

|----------------------------------------------|-----------|--------------|----------|

| MS2: presentation of the digital part        | 0 days    | 22/3/22      | 22/3/22  |

| MS3: List and Specs for analog compoments    | 0 days    | 15/4/22      | 15/4/22  |

| Virtual prototyping with Innovus             | 40 days   | 18/4/22      | 10/06/22 |

| Review hierarchical top-down flow in Innovus | 4 days    | 18/4/22      | 21/4/22  |

| Study layout of Serdes components            | 30 days   | 19/4/22      | 31/5/22  |

| Synthesis of digital part                    | 10 days   | 09/05/22     | 20/5/22  |

| Iterative floorplan                          | 20 days   | 16/5/22      | 10/06/22 |

| Estimate timing                              | 15 days   | 20/5/22 8:00 | 09/06/22 |

| Top level prototype layout                   | 0 days    | 10/06/22     | 10/06/22 |

| Report writing                               | 15,5 days | 10/06/22     | 04/07/22 |

| writing                                      | 15 days   | 10/06/22     | 01/07/22 |

| MS6: Report                                  | 0 days    | 02/07/22     | 02/07/22 |

Table 1 Work plan.

## 1.6. <u>Deviations from initial plan</u>

The main issue with this project was the lack of documentation from Wavious, this made difficult the understanding of the IP, but also for the moment limits the work that can be done with the analog and mixed signal cells. Also, the implementation process finished with the synthesis of the IP instead of getting to the place and route of the design as initially envisioned.

# 2. <u>State of the art of the technology used or applied in this</u> thesis

# 2.1. <u>LPDDR4</u>

## 2.1.1. DRAM

Dynamic random-access memory (dynamic RAM or DRAM) [3] is a type of random-access semiconductor memory that stores each bit of data in a memory cell, usually consisting of a tiny capacitor and a transistor, both typically based on metal-oxide-semiconductor (MOS) technology. The capacitor can either be charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. The electric charge on the capacitors gradually leaks away; without intervention the data on the capacitor would soon be lost. To prevent this, DRAM requires an external memory refresh circuit which periodically rewrites the data in the capacitors, restoring them to their original charge. This refresh process is the defining characteristic of dynamic random-access memory, in contrast to static random-access memory (SRAM) which does not require data to be refreshed. Unlike flash memory, DRAM is volatile memory (vs. non-volatile memory), since it loses its data quickly when power is removed.

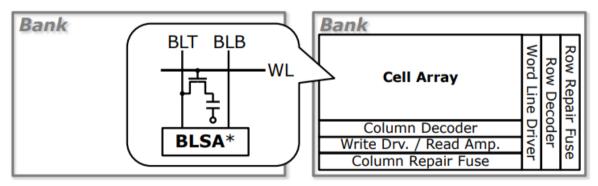

In order to access each storage cell there is a Bit Line Sense Amplifier (BLSA) that will read the small charge in the capacitor and amplify it to a digital signal, after this process the memory will recharge the capacitor. In order to activate a specific cell a decoder assembly will activate the transistor of that cell through each word line. This entire assembly is called a bank shown in Figure 2, RAM chips will feature multiple banks, so each one can be accessed independently of the others, that way it increases overall speed, as one can be read while another one is refreshing.

Figure 2 DRAM bank composition [3]

The advantage of DRAM is the density of storage, as a single capacitor and transistor can be integrated in less area than other technologies like SRAM that take 6 transistors [4]. The disadvantage is the refreshing time, although with the use of banks it can be reduced.

Synchronous dynamic RAM (SDRAM) significantly revises the asynchronous memory interface, adding a clock (and a clock enable) line. All other signals are received on the rising edge of the clock. This memory can achieve transfer rates up to 1.3GB/s with a clock speed of 133MHz, this number is dependent on manufacturer optimizations.

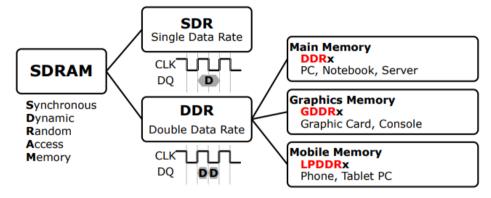

Double data rate SDRAM (DDR SDRAM or DDR) [5] was a later development of SDRAM as seen in Figure 3, used in PC memory beginning in 2000. Subsequent versions are numbered sequentially (DDR2, DDR3, etc.). DDR SDRAM uses both the rising and falling edge of the clock and thus internally performs double-width accesses at the clock rate, and uses a double data rate interface to transfer one half on each clock edge, achieving transfer rates up to 3.2GB/s with a clock speed of 200MHz. DDR2 and DDR3 increase transfer speeds up to 6.4GB/s at 400MHz and 14.9GB/s at 933MHz respectively.

Figure 3 SDRAM development tree [5]

# 2.1.2. LPDDR4

LPDDR4-SDRAM [6] is a high-speed synchronous DRAM device intended for low power and portable devices, it is designed to reduce power consumption and simplify on-board connectivity. Internally each memory chip is configured as 2 channels, each channel provides an interface that can be accessed independently in order to increase the access speed. Each chip is specified for a capacity up to 16Gb.

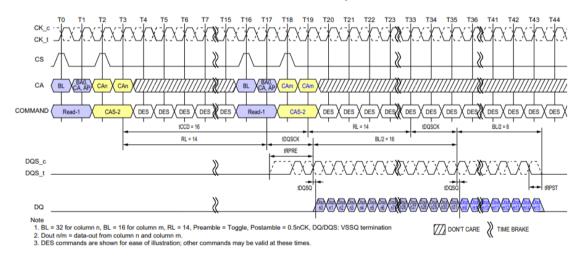

While a DDR4 device has an 18-bit address interface and a dedicated 4-bit command interface, the LPDDR4 devices combine on a single 6-bit interface the commands for the memory shown in Table 3 and the address for the data (row and column) as compared in Table 2, this is achieved because the LPDDR4 uses a 2 or 4 clock architecture on the Command/Address (CA) bus, this means that each command or address is divided in 2 or 4 chunks that are transmitted on 2 or 4 clock periods. These devices use a double data rate architecture on the data (DQ) pins to achieve high speed operation.

| Attribute               | LPDDR4                    | DDR4                     |

|-------------------------|---------------------------|--------------------------|

| Target Market           | Mobile Devices            | Laptop,PC,Server         |

| Die Architecture        | 2chX16                    | 1chX16                   |

| IO Spec.                | ~350mV LVSTL              | POD_12                   |

| DLL in Dram             | No                        | Yes                      |

| Termination             | VSSQ                      | VDDQ                     |

| CI/O                    | <1.0pF                    | >1.0pF                   |

| C/A                     | 6pin SDR CA bus           | 22pins                   |

| Topology                | Point-to-point<br>PoP&MCP | DIMM                     |

| Bandwith                | 3.2Gbps/4.2Gbps           | 3.2Gbps                  |

| Low Frequency operation | Yes                       | Yes (DLL off<br><125MHz) |

| Target Supply           | 1.1V(1.0V)                | 1.2V                     |

Table 2 LPDDR4 vs DDR4

# 2.1.3. LPDDR4 operation

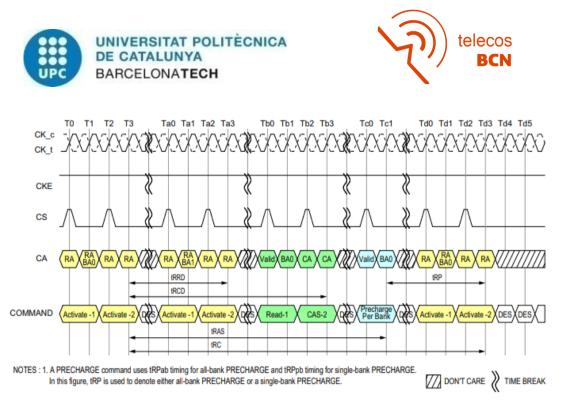

Prior to normal operation, the LPDDR4 SDRAM must be initialized [7]. The following provides detailed information covering device initialization, register definition, command description and device operation as shown in Figure 4.

# Activate Command

The ACTIVATE command is composed of two consecutive commands, Activate-1 command and Activate-2. The bank addresses BA0, BA1 and BA2 (3-bit address gives access to 8 banks) are used to select the desired bank. Row addresses are used to determine which row to activate in the selected bank. The ACTIVATE command must be applied before any READ or WRITE operation can be executed. After a bank has been activated, it must be precharged before another ACTIVATE command can be applied to the same bank.

Figure 4 Activate operation [7]

#### **Burst Read Operation**

After a bank has been activated, a read or write command can be executed. This is accomplished by asserting CKE asynchronously, with CS and CA[5:0] set to the proper state as shown in Figure 5. The LPDDR4-SDRAM provides a fast column access operation. A single Read or Write command will initiate a burst read or write operation, where data is transferred to/from the DRAM on successive clock cycles.

Figure 5 Burst read operation [7]

Finally, a sample of the CA table, that shows a few commands used to operate the memory. Each command is composed of two sections, each one is read during a clock edge, so each operation takes two clock edges to be transmitted as seen previously. They are composed of a combination of a 5-bit encoding to show which command is being sent and the information itself, for example the address itself.

#### UNIVERSITAT POLITÈCNICA DE CATALUNYA BARCELONATECH

|                                                | SDR<br>Command<br>Pins | SDR CA Pins (6) |     |           |     |     |     |              |             |

|------------------------------------------------|------------------------|-----------------|-----|-----------|-----|-----|-----|--------------|-------------|

| SDRAM Command                                  | CS                     | CA0             | CA1 | CA2       | CA3 | CA4 | CA5 | CK_t<br>edge | Notes       |

| Deselect (DES)                                 | L                      |                 |     | )         | ×   |     |     | R1           | 1,2         |

| Multi Purpose Command                          | Н                      | L               | L   | L         | L   | L   | OP6 | R1           | 1,2,9       |

| (MPC)                                          | L                      | OP0             | OP1 | OP2       | OP3 | OP4 | OP5 | R2           | 1,2,0       |

| Precharge (PRE)                                | Н                      | L               | L   | L         | L   | н   | AB  | R1           | 1,2,3,4     |

| (Per Bank, All Bank)                           | L                      | BA0             | BA1 | BA2       | V   | V   | V   | R2           | 1,2,0,4     |

| Refresh (REF)                                  | н                      | L               | L   | L         | н   | L   | AB  | R1           | 1,2,3,4     |

| (Per Bank, All Bank)                           | L                      | BA0             | BA1 | BA2       | V   | V   | V   | R2           | 1,2,3,4     |

| Self Refresh Entry                             | Н                      | L               | L   | L         | н   | н   | V   | R1           | 1.2         |

| (SRE)                                          | L                      |                 |     | · · · · · | V   |     |     | R2           | 1,2         |

| Write -1 (WR-1)                                | Н                      | L               | L   | н         | L   | L   | BL  | R1           | 1,2,3,6,7,9 |

| White -1 (WK-1)                                | L                      | BA0             | BA1 | BA2       | V   | C9  | AP  | R2           |             |

| Self Refresh Exit (SRX)                        | н                      | L               | L   | н         | L   | Н   | V   | R1           | 1.2         |

| Sell Kellesh LXI (SIXX)                        | L                      |                 |     | ````      | V   |     |     | R2           | 1,2         |

| Mask Write -1                                  | Н                      | L               | L   | н         | н   | L   | L   | R1           | 1,2,3,5,6,9 |

| (MWR-1)                                        | L                      | BA0             | BA1 | BA2       | V   | C9  | AP  | R2           | 1,2,3,5,0,9 |

| RFU                                            | н                      | L               | L   | н         | н   | н   | V   | R1           | 1.2         |

| Kru                                            | L                      |                 | •   | ١         | V   | •   |     | R2           | 1,2         |

| Deed 4 (DD 4)                                  | н                      | L               | н   | L         | L   | L   | BL  | R1           | 100070      |

| Read -1 (RD-1)                                 | L                      | BA0             | BA1 | BA2       | V   | C9  | AP  | R2           | 1,2,3,6,7,9 |

| CAS-2 (Write-2, Mask<br>Write -2, Read-2, MRR- | н                      | L               | н   | L         | L   | н   | C8  | R1           | 1.8.9       |

| 2, MPC)                                        | L                      | C2              | C3  | C4        | C5  | C6  | C7  | R2           | 1,0,0       |

Table 3 Command truth table [7]

# 2.1.4. Multiple channel connectivity

LPDDR4 is the first JEDEC specification [8] that specifies two DDR DRAM channels per die, and packages with four LPDDR4 DDR DRAM channels, giving chip architects new options when designing chips that connect to LPDDR4 displayed in Figure 6.

#### Parallel connection:

Both DRAM devices receive the same command & address but transmit data over different byte lanes. Both devices are accessed simultaneously.

Difficult for Package on Package (PoP) implementation, it also has less effective bank utilization, has a 64 byte fetch.

#### Series (Multi-rank) Connection:

Both DRAM devices receive the same command & address and use the same byte lanes. Chip select signals determine which device is being accessed.

Half the bandwidth of other solutions, but saves some DQ pins.

#### Multi-Channel Connection:

Each DRAM device operates independently of the other, receives a different command & address, transmits over different byte lanes. It is considered the best option for LPDDR4

#### Multi-channel with Shared-CA (aka Shared-AC):

Both DRAM devices receive the same command & address but only one device is accessed with an active chip select at a time, so each DRAM device operates independently. DRAM devices use different byte lanes, it is fine for DDR4/3, not recommended for LPDDR4.

## 2.2. Digital implementation

In order to implement high-level designs it is necessary to describe it at a high level of abstraction. For this reason hardware description languages (HDL) like Verilog provide the

platform to design complex behaviours. RTL is an acronym for register transfer level, this implies that your HDL code describes how data is transformed as it is passed from register to register. The transforming of the data is performed by the combinational logic that exists between the registers.

Synthesis transforms an RTL code, that is, one using high-level structures like finite state machines, conditional assignments and so on, into a netlist [9]. A netlist is a list of logic gates belonging to a physical library, such that their connection is specified to correctly implement the original RTL description. This netlist is in Verilog language. Therefore, the library information must be provided to the Synthesis tool so that the original description is mapped to the gates corresponding to actual technology. This is referred to as synthesis, the first step of an IC design flow as shown in Figure 7.

Figure 7 General IC design flow

As mentioned, the synthesis process expects a logical description of a design, but some designs are more analog oriented, this means it is not feasible to use an HDL to design them. Therefore, a synthesis tool is not capable of working with them, these blocks are macros that will be designed using different tools and later included in the design as blackboxes, where the synthesis will connect them to the rest of RTL components. Cadence tool for digital synthesis is called Genus.

In order to avoid typing the same commands time and again, the tool makes extensive use of scripts, written in a standard scripting language, Tool Control Language (TCL). This allows to simplify the procedure by writing several scripts that are modified at convenience without having to type individual commands.

The goal of Genus is to provide the best Quality of Results (QoR) or close to the best with the template flows provided. Still, additional commands and configuration options can be added to improve results. Here, the quality is measured in terms of three aspects: Timing (or performance) given a set of timing constraints written in a special language as described in sections below; Power consumption of the design; and Area of the design.

Digital circuits are typically very large in terms of number of transistors and thus a detailed description of their behaviour at electrical level is not feasible. Instead, they are described at logic level, generally describing transactions at the register level, abbreviated as RTL. This description benefits from well-established algorithms that starting from a description in a Hardware Description Language (either VHDL or Verilog) make possible to obtain the optimum number of logic gates implementing the original RTL description. The logic gates used in the synthesis process are predesigned and characterised for a given technology in a so-called Standard Cell library, on which the RTL description is mapped. This process seen in Figure 8 of translating an RTL description into a netlist of logic gates from a library is called synthesis. The gates in the netlist are after that optimally placed on the chip, and the wires routed to connect the gates. This is done automatically with another CAD tool for Place and Route (PnR), Innovus in the case of Cadence.

Design constraints are an essential part of the synthesis process. You apply a set of timing and, optionally, power constraints such that the final design must comply with them. Verifying timing constraints (clock frequency, maximum I/O delays, and so on) are considered the primary goal. No synthesis result is correct until the timing constraints are met. This is measured with a concept called slack. A positive slack means that the timing constraints are met with a given margin (the slack). A negative slack means that the timing constraint is not met, so that netlist must be transformed until the obtained slack is positive. Timing constraints are described in SDC format (a text file).

The final product of the synthesis process is the LEF file. A Library Exchange Format (LEF) file contains library information for a class of designs. Library data includes layer, via, placement site type, and macro cell definitions. This LEF file contains all the data that will later be used to follow with the place and route stage.

# 2.3. Analog design

However, selected parts of the digital circuit may be designed specifically by hand or with a different design methodology. Typically, analog components and memories belong to this class. They are different from Standard Cells (SC) in which SC represent logic functions that are part of algebraic expressions and so, simplifications and algebraic manipulation with these functions take place when translating from RTL to gates. In addition, all SC in a given library have the same vertical size (thus the name Standard ). By contrast, these selected parts, called Macros, have a non-standard size and generally do not represent a simple algebraic expression, but a more complex behaviour. In the RTL they are simply instantiated instead of being described with high level constructs.

The main software used to design analog and mixed-signal systems is Cadence Virtuoso, and Spectre is used to simulate the design. At this stage of the design the aim is to validate the functionality of the design. At this point the design is using an abstract model of the electrical components (Transistors, capacitors...). But, after this stage is completed, the designer needs to implement the design, the layout phase is where the designer will draw the shapes of metal, and different doping areas on the silicon in order to define transistors and the connections between them, also the pins that will connect this design. Finally using abstraction tools, the layout needs to be converted to another LEF file so the Synthesis tools can use it to include it with the rest of the RTL design.

# 3. <u>Methodology / project development</u>

The Methodology is included in this chapter and should include all relevant methods that have been used as well as research methods and measurements, software and hardware development, etc.

# 3.1. Wavious IP

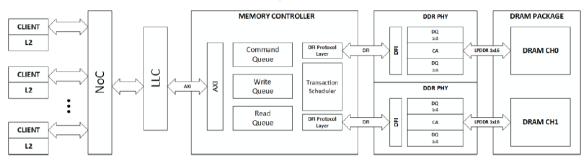

The Wavious IP [10] provides the DDR PHY block, the DDR Physical Interface (PHY) IP provides an interface to external DRAM and is an important component to meet system performance requirements as shown in Figure 9.

Figure 9 System Block Diagram

The block that we are going to focus on is the DDR PHY interface, inside this PHY we find the following blocks shown in Figure 10.

Figure 10 DDR PHY Top Level Block Diagram

The proposed design has an integrated RISC-V MCU and dedicated SRAM for instructions and data storage. Also, it has a common block that contains the PLLs and LDO to provide the clock sources that are needed in this design.

The DDR PHY Interface (DFI) is used in several consumer electronics devices including smart phones. DFI is an interface protocol that defines signals, timing, and programmable parameters required to transfer control information and data to and from the DRAM devices, and between MC (Memory Controller) and PHY.

The DFI interface is not necessary when the MC and PHY are being developed specifically to work together. However, in many situations, the MC and PHY are designed separately – often by different companies. DFI permits companies to develop both MC and PHY IP designs knowing that they will be able to interoperate with the devices developed by other companies.

Additionally, MC devices are primarily digital designs, whereas PHY generally consists of a significant amount of analog logic, therefore the two devices are often developed by different engineers even within the same company. DFI creates a well-defined interface for the two separate design teams.

Finally, it includes the two channels, each one with the TX/RX transceivers.

## 3.2. Clock structure

Synchronous digital designs are constrained by a clock signal, the period of which establishes the maximum time a signal path can take between two registers. The time that is left between the arrival of the signal to the register and the next edge of the clock signal is the slack, and a positive slack indicates a digital path that is within the time constraints of the system. During the synthesis process Genus will evaluate the timing of every signal path and check the slack, in case it is negative, the designer needs to make changes to the design. For complex designs the clock structure can be composed of multiple clock signals for different domains.

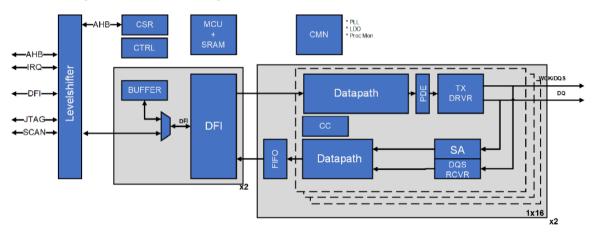

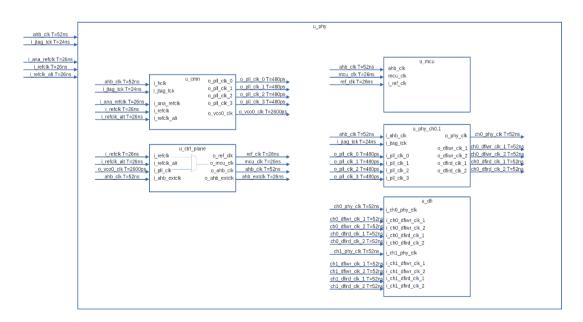

In order to synthesise the Wavious IP we need to define the timing constraints of the different clocks of the design. These constraints are specified in an SDC file. In this file we have to specify all the external clock sources, the generated clocks from PLL, clock gating cells and all the load and IO delays. Since Wavious hasn't provided a clock distribution guide to this day, we will need to use multiple tools to understand the clock structure of the system so it can be specified for the SDC file, in Figure 11 is represented the main clock structure.

Figure 11 Clock distribution diagram

First of all the input clock sources, to find the clock period of these sources we take a look at the simulation testbench that is provided by Wavious with the design, this simulation testbench is intended to validate the design.

| <pre>// Clock Frequencies</pre> |     |       |

|---------------------------------|-----|-------|

| localparam AHBCLK_PERIOD        | =   | 10;   |

| localparam REFCLK_FREQ          | =   | 38.4; |

| localparam REFCLK_PERIOD        | =   | 26;   |

| localparam REFCLK_ALT_PERIO     | ) = | 26;   |

| localparam TCK_PERIOD           | =   | 25;   |

From there we can define the clocks in the SDC file.

create\_clock -name "Ref\_clk" -period 26000.0 -waveform {0.0 13000.0} [get\_ports i\_refclk] create\_clock -name "Ana\_refclk" -period 24000.0 -waveform {0.0 12000.0} [get\_ports i\_ana\_refclk] create\_clock -name "Refclk\_alt" -period 26000.0 -waveform {0.0 13000.0} [get\_ports i\_refclk\_alt] create\_clock -name "i\_jtag\_tck" -period 26000.0 -waveform {0.0 13000.0} [get\_ports i\_jtag\_tck] create\_clock -name "AHB\_clk" -period 26000.0 -waveform {0.0 13000.0} [get\_ports i\_ahb\_clk]

Some other clock signals are generated by the PLLs, these also have to be specified in the SDC. In order to get the values of these clock periods we can take a look at the simulation results, and measure all the internal clock signals, an example is represented in Figure 12.

| Image       Image <td< th=""><th><b>*</b> *</th><th>Waveform 1 - SimVision</th><th>~ ^ 🛇</th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>*</b> *                                                                         | Waveform 1 - SimVision                                         | ~ ^ 🛇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: The second se        | <u>F</u> ile <u>E</u> dit <u>V</u> iew Explore For <u>m</u> at Sim <u>u</u> lation | VM <u>W</u> indows <u>H</u> elp                                | cādence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Image: State Stat        | 🔁 隆 🕜 🐟   😹 🗅 🛍 🕽 👼 📖                                                              | 🛐 💼 🖻 Search Names: Signal 🗸 💌 🖍 👫                             | Send To: 🔖 🚝 🚉 🗱 📰 📰 🗐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Cursor-Baseline - S24/244,838p=                  Ware             o_tag_tido               Ogg             [602,580,000ps             [602,581,000ps             [602,583,000ps             [602,580,000ps             [602,580,000ps             [602,580,000ps            [602,580,000ps             [602,580,000ps            [60                                                                                                          | 📔 🕶 🎹 🔣 🔤 🔤 614,508,801,076fs + 21                                                 | imeA▼ = 524,244,693 ▼ ps▼ 👯 ▼ 🔩 💁 Search Times: Digital Value▼ | I I II. II. II. II. II. II. II. II. II.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Image: notion of the state        | Cursor-Baseline - 524,244,693ps                                                    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Image: solution of the solution        | A18                                                                                | ps 602,580,000ps 602,581,000ps 602,582,000ps 6                 | 602,583,000ps 602,584,000ps 602,585,000ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Image: Second |                                                                                    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Image: page page page         z           Image page page         0           Image: page page         0           Image: page page         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ···· <b>··⊡</b> o_vco0_olk 0<br>····· <b>i€&gt;</b> pad_atb z                      |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | K pad_rext z                                                                       |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| الم                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | pll0_div_clk_rst_int 1                                                             | )0731 <u>8</u> 41F07c1_42BA78F1                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |