FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

## **Fast Loop for a Capless LDO**

Filipe de Oliveira Barros

Mestrado em Engenharia Eletrotécnica e de Computadores

Company supervisor: Rui Teixeira Supervisor: Cândido Duarte Second Supervisor: Vítor Grade Tavares

October, 2022

© F. Oliveira, 2022

### Resumo

A evolução de Circuitos Integrados e gestão de potência na indústria de semicondutores tem vindo a forçar circuitos eletrónicos a permitirem uma maior integração em soluções de sistemas em *chip*.

Reguladores de tensão convencionais de baixa queda possuem um condensador externo de dimensões elevadas para compensar a resposta em frequência e em variações transientes. De forma a ser integrado em aplicações de sistemas em *chip*, o condensador externo tem de ser removido.

A solução apresentada dispõe de um caminho rápido de regulação para compensação de respostas transientes do regulador de tensão de baixa queda sem condensador externo, para uma tecnologia de processo CMOS de 28nm. O regulador de tensão de baixa queda sem condensador externo com caminho rápido de regulação é alimentado com uma tensão nominal de 1.8V, sendo capaz de regular tensões de saída de 1.2V, 1.1V, 1V, 0.9V, 0.8V e 0.7V. A partir de uma arquitetura genérica, sem compensação, de um regulador de tensão de baixa queda sem condensador externo, um condensador interno de Miller com valor de 5pF é implementado no amplificador de erro com o objetivo de gerar compensação em frequência no sistema e garantir a estabilidade em corrente alternada do mesmo. Um esquema de compensação de um caminho rapido de regulação é estudado e implementado para a compensação de uma resposta transiente a uma variação máxima da corrente de carga de 1mA com uma capacidade de carga equivalente a 1pF.

Os resultados das simulações mostram que o regulador de tensão de baixa queda é competitivo entre as arquiteturas do estado da arte, passando algumas, registando um valor de variação transiente positiva e negativa na tensão de saída de 48mV e 49.8mV, respetivamente, com  $0.5\mu$ s de tempo de recuperação.

simulações de casos extremos de *PVT (Process, Voltage, Temperature)* e análises de Monte Carlo feitas posteriormente, mostram que o sistema desenhado cumpre com a norma ISO 26262.

O desenho do *layout* do sistema proposto é apresentado para uma futura integração do mesmo.

**Palavras-chave:** CMOS, LDO, regulador de tensão, tensão de queda, caminho rápido de regulação, sem condensador externo, compensação transiente, compensação em frequência, regulação de carga. ii

### Abstract

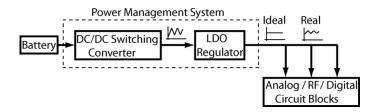

The evolution of Integrated Circuits (IC) and power management in the semiconductor's industry has pushing circuit designs to allow for more integration in system-on-chip (SoC) solutions.

Conventional LDO voltage regulator topologies have a large external capacitor to compensate frequency and transient response. In order to be integrated in SoC applications, the external capacitor has to be removed.

The presented solution provides a fast loop for transient compensation for a capacitor-less LDO voltage regulator, in a 28nm CMOS process technology. The proposed fast loop capacitor-less LDO voltage regulator is supplied with a nominal voltage of 1.8V with the ability to regulate an output voltage of 1.2V, 1.1V, 1V, 0.9V, 0.8V and 0.7V. From a generic, uncompensated, architecture of a LDO voltage regulator without a bulky external capacitor, a 5pF internal Miller capacitor is implemented in the Error Amplifier in order to provide frequency compensation to the system and guarantee the systems AC stability. A Fast loop compensation scheme is studied and implemented for transient compensation of 1mA maximum load current step and a load capacitance of 1pF.

Simulation results show that the proposed LDO voltage regulator is competitive among the state-of-the-art architectures, exceeding some in transient response, reporting an output voltage overshoot and undershoot of 48mV and 49.8mV, respectively, with  $0.5\mu$ s of settling time.

PVT (Process, Voltage, Temperature) corner simulations and further Monte Carlo analysis show that the designed system complies with the ISO 26262 standard.

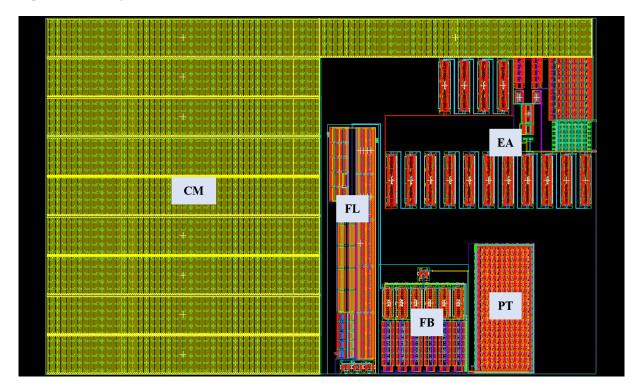

A layout design of the proposed fast loop capacitor-less LDO voltage regulator is presented, for future integration.

**Keywords:** CMOS, LDO, voltage regulator, dropout voltage, fast loop, dual loop, capless, capacitor-less, transient compensation, frequency compensation, load regulation

iv

### Acknowledgements

I would like to thank my supervisors, Professor Cândido Duarte and Professor Vítor Tavares, for all the guidance and the support in this work.

This work was carried out with the support of the host institution: Synopsys and supervised at the institution by: Rui Teixeira. I thank Synopsys for providing the right tools and environment in the duration of this dissertation and thank specially Rui Teixeira for all the technical support and advising throughout this journey, without him, this work would not be possible.

I thank Professor João Canas Ferreira for giving me the opportunities to trace my path throughout the course.

I thank my mother and my grandmother for being always available to help me with everything.

I specially want to thank Catarina for the encouragement, emotional support and for being always on my side no matter what.

Filipe Oliveira

vi

"Knowledge is a skyscraper. You can take a shortcut with a fragile foundation of memorization, or build slowly upon a steel frame of understanding."

Naval Ravikant

viii

## Contents

| Al | Abbreviations xvi                               |                            |                                                                              |                            |

|----|-------------------------------------------------|----------------------------|------------------------------------------------------------------------------|----------------------------|

| 1  | <b>Intro</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Motiva<br>Object<br>System | n<br>e Regulators                                                            | 1<br>1<br>2<br>2<br>3<br>3 |

| 2  | State                                           | e of the                   | Art                                                                          | 5                          |

|    | 2.1                                             | Literat                    | ure Review                                                                   | 5                          |

|    |                                                 | 2.1.1                      | Overshoot Detection Circuit, implemented by Liu and Chen (2020)              | 5                          |

|    |                                                 | 2.1.2                      | Fast differential stage architecture, implemented by Yosef-Hay et al. (2017) | ) 7                        |

|    |                                                 | 2.1.3                      | Transient Enhancement Circuit based on a Differentiator, designed by Yu      |                            |

|    |                                                 |                            | Peng <i>et al.</i> (2021)                                                    | 8                          |

|    |                                                 | 2.1.4                      | Common Source Stage, design by N. Deleuran et al. (2015)                     | 10                         |

|    |                                                 | 2.1.5                      | Summary                                                                      | 11                         |

| 3  | LDC                                             | ) Voltag                   | ge Regulator                                                                 | 13                         |

|    | 3.1                                             | Compo                      | onents                                                                       | 14                         |

|    |                                                 | 3.1.1                      | Pass Transistor                                                              | 14                         |

|    |                                                 | 3.1.2                      | Error amplifier                                                              | 15                         |

|    |                                                 | 3.1.3                      | Feedback Network                                                             | 19                         |

|    |                                                 | 3.1.4                      | Stability                                                                    | 19                         |

|    | 3.2                                             | Charac                     | terisation                                                                   | 21                         |

|    |                                                 | 3.2.1                      | Static-State Specifications                                                  | 21                         |

|    |                                                 | 3.2.2                      | Dynamic-State Specifications                                                 | 23                         |

|    |                                                 | 3.2.3                      | High-Frequency State Specifications                                          | 24                         |

|    |                                                 | 3.2.4                      | Figure of Merit (FoM)                                                        | 24                         |

|    | 3.3                                             | PVT V                      | Variability                                                                  | 24                         |

|    |                                                 | 3.3.1                      | Process Variation                                                            | 24                         |

|    |                                                 | 3.3.2                      | Supply Voltage                                                               | 25                         |

|    |                                                 | 3.3.3                      | Operating Temperature                                                        | 25                         |

|    |                                                 | 3.3.4                      | Monte Carlo Analysis                                                         | 26                         |

|    | 3.4                                             | Summa                      | arv                                                                          | 26                         |

| 4  | Fast   | Loop Design                                                    | 31 |

|----|--------|----------------------------------------------------------------|----|

|    | 4.1    | Sizing Flow                                                    | 31 |

|    | 4.2    | Literature Assessment                                          | 32 |

|    |        | 4.2.1 Overshoot/Undershoot Detection Circuit                   | 32 |

|    |        | 4.2.2 Fast and Slow Loop Architecture                          | 35 |

|    |        | 4.2.3 Transient Enhancement Circuit based on a Differentiator  | 38 |

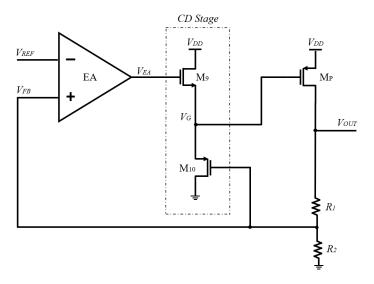

|    |        | 4.2.4 Common Drain Fast Loop                                   | 41 |

|    |        |                                                                | 42 |

|    | 4.3    |                                                                | 43 |

|    |        |                                                                | 48 |

|    | 4.4    | -                                                              | 50 |

|    | 4.5    | -                                                              | 52 |

|    | 4.6    | 1                                                              | 55 |

|    |        |                                                                |    |

| 5  | Fina   | al System's Results                                            | 57 |

|    | 5.1    | Testbench setup                                                | 57 |

|    | 5.2    | Results                                                        | 58 |

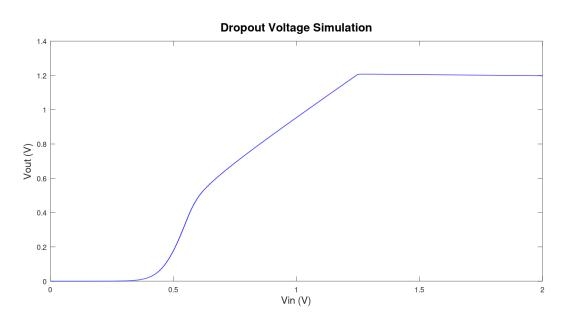

|    |        | 5.2.1 Dropout Voltage                                          | 58 |

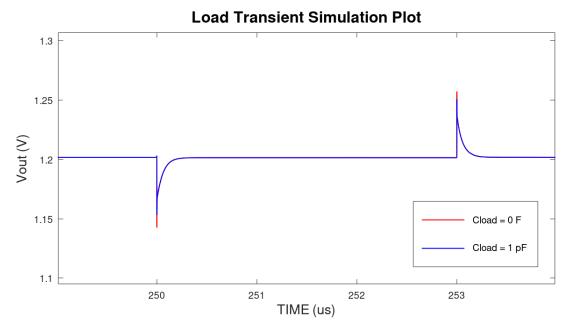

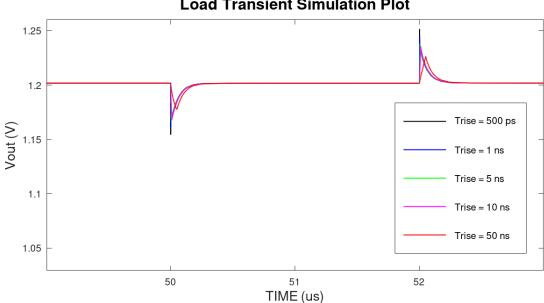

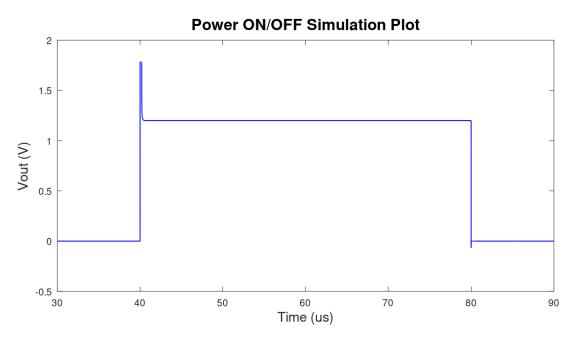

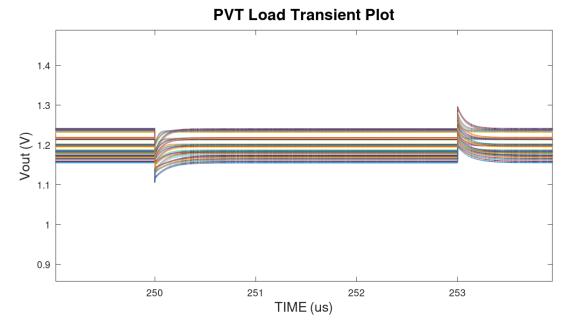

|    |        | 5.2.2 Transient Behaviour                                      | 59 |

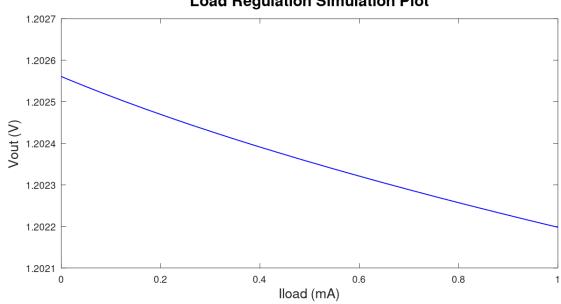

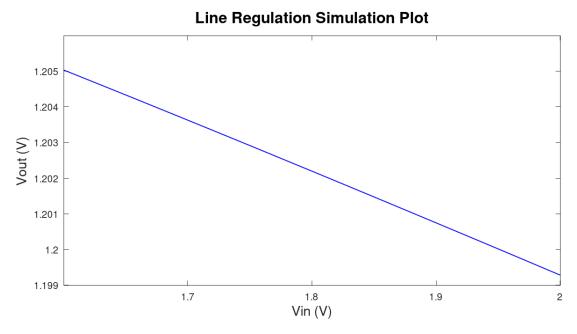

|    |        | 5.2.3 Output Regulation                                        | 61 |

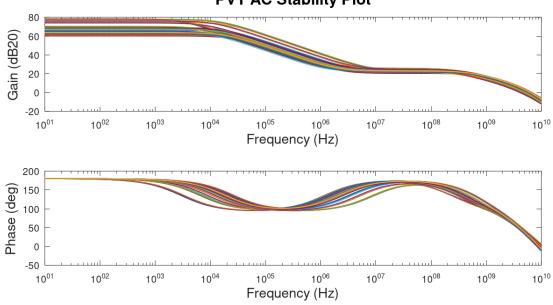

|    |        | 5.2.4 Stability of the Fast Loop capless LDO voltage regulator | 61 |

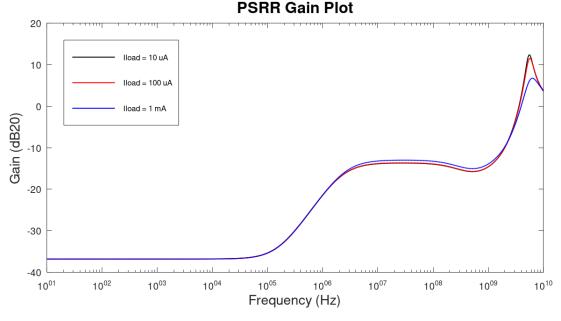

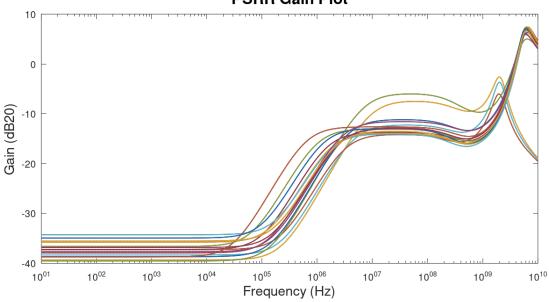

|    |        | 5.2.5 Ripple Rejection Behaviour                               | 63 |

|    |        |                                                                | 64 |

|    |        | 5.2.7 Efficiency                                               | 65 |

|    |        | 5.2.8 PVT corner variations                                    | 65 |

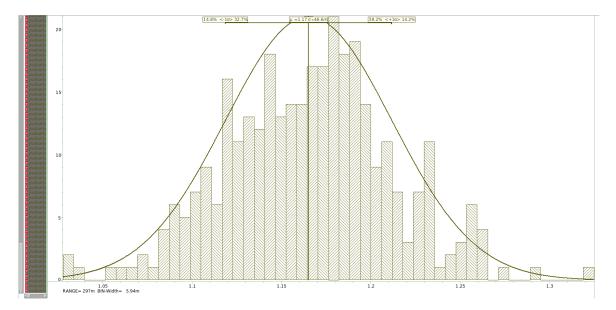

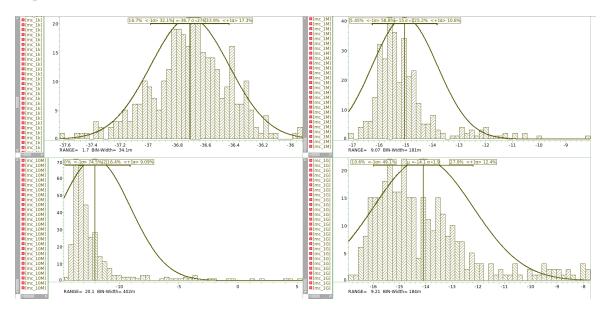

|    |        | 5.2.9 Monte Carlo Analysis                                     | 67 |

|    | 5.3    | System Validation and Datasheet                                | 70 |

| 6  | Con    | clusion                                                        | 71 |

| U  | 6.1    |                                                                | 72 |

|    | 0.1    |                                                                | 12 |

| Re | eferen | ices                                                           | 73 |

| 7  | Refe   | erences                                                        | 75 |

# List of Figures

| 1.1  | Block diagram of a typical power management system, taken from [1]                  | 1  |

|------|-------------------------------------------------------------------------------------|----|

| 2.1  | Fast local loop including load, [27]                                                | 6  |

| 2.2  | Robust Overshoot Detection Circuit, [27]                                            | 6  |

| 2.3  | Simulation results obtain in [27]                                                   | 7  |

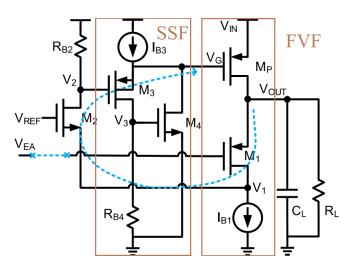

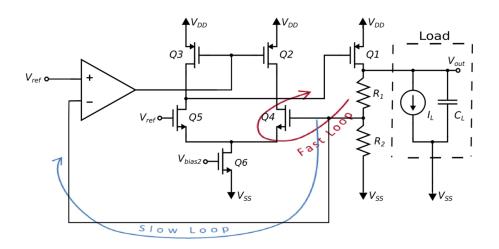

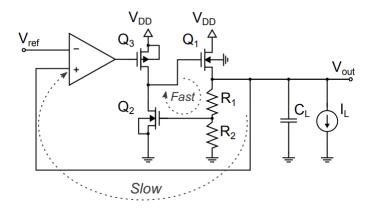

| 2.4  | Fast loop and slow loop of the LDO proposed in [10]                                 | 8  |

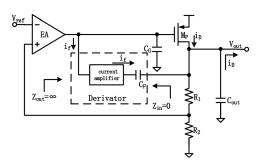

| 2.5  | Derivator separation poles frequency compensation schematic, [26]                   | 9  |

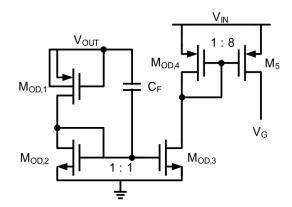

| 2.6  | Class AB transient enhancement circuit based on a differentiator, [26]              | 9  |

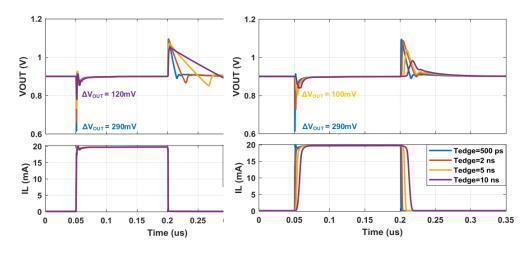

| 2.7  | Simulation results of load transient characteristics, [26]                          | 10 |

| 2.8  | Functional diagram of the LDO, [28]                                                 | 10 |

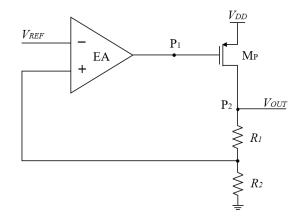

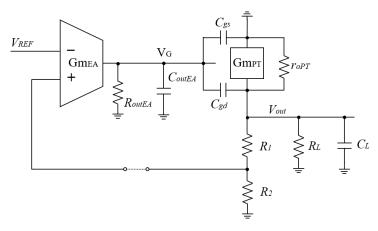

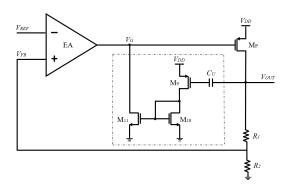

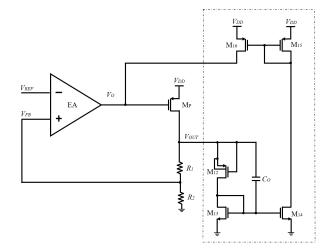

| 3.1  | Proposed uncompensated LDO voltage regulator                                        | 13 |

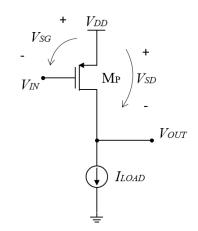

| 3.2  | Pass Transistor design                                                              | 14 |

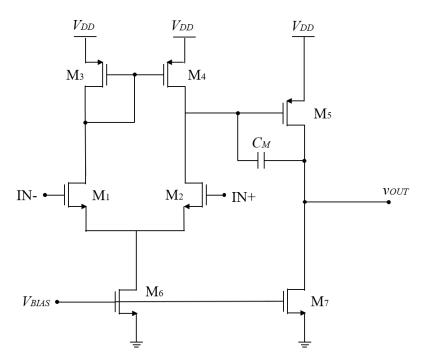

| 3.3  | Error Amplifier - Two stage Operational Amplifier                                   | 16 |

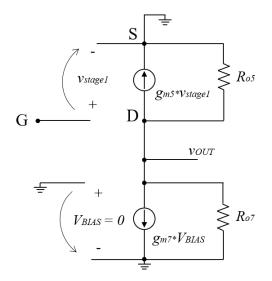

| 3.4  | Small Signal Model of the 2nd stage of the EA                                       | 17 |

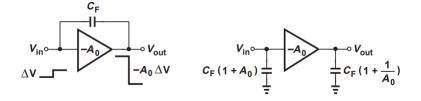

| 3.5  | Miller's effect, [17]                                                               | 18 |

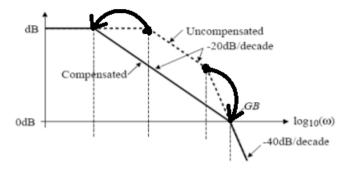

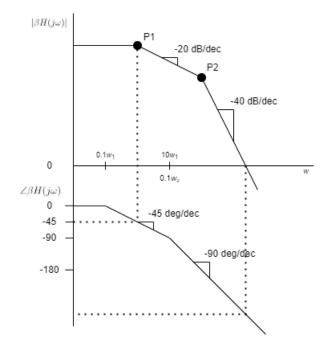

| 3.6  | Bode Plot of Miller Compensation, adapted from [16]                                 | 18 |

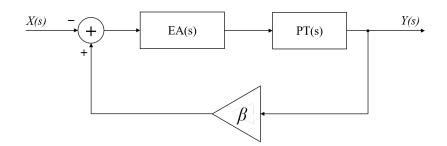

| 3.7  | System Block Diagram of the proposed LDO voltage regulator                          | 20 |

| 3.8  | Gain and Phase Bode Plot of an uncompensated LDO voltage regulator, [16]            | 21 |

| 3.9  | Small Signal Model of the proposed LDO voltage regulator                            | 23 |

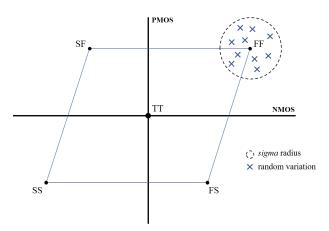

| 3.10 | Monte Carlo Analysis' set up illustration                                           | 26 |

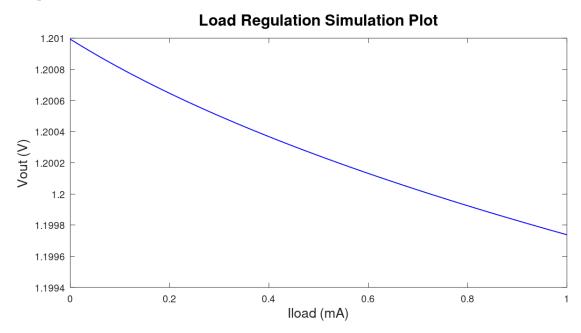

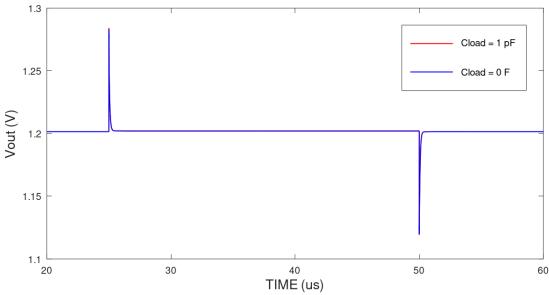

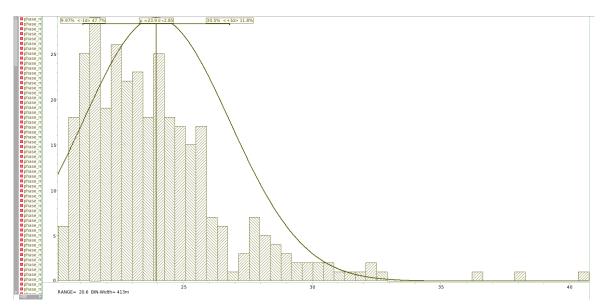

|      | Load Regulation simulation results for $V_{in}$ =1.8V and $C_L$ =0 F                | 27 |

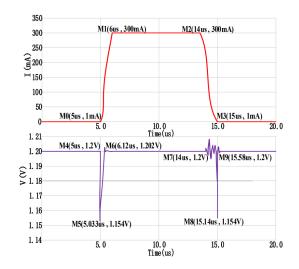

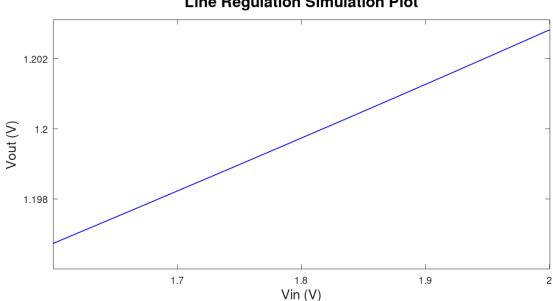

|      | Line Regulation simulation results for $I_L$ =1mA and $C_L$ =0 F                    | 27 |

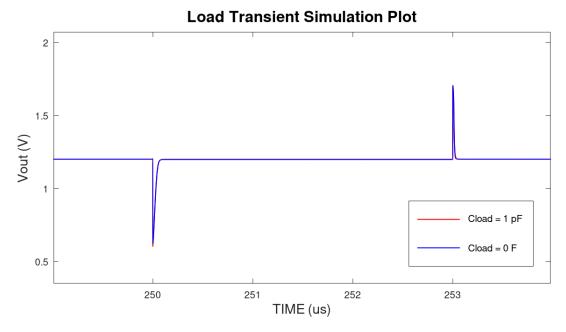

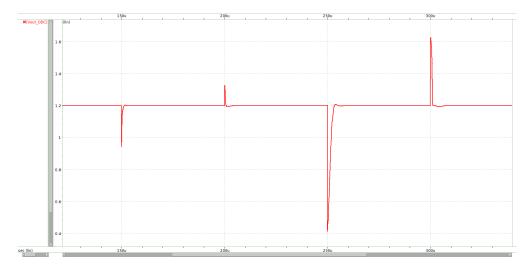

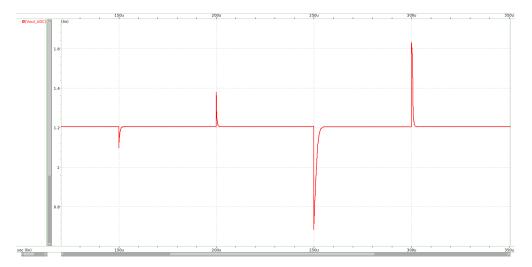

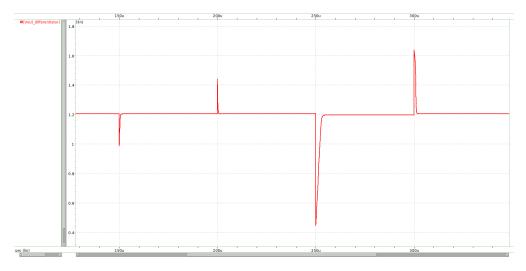

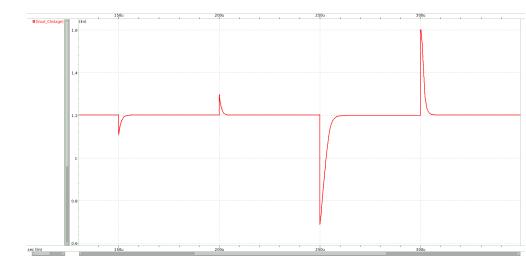

|      | Load transient simulation results for $I_L$ =1mA with $C_L$ =0, 1 pF                | 28 |

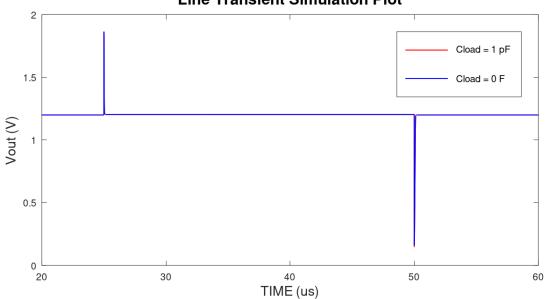

|      | Line transient simulation results for $I_L$ =1mA with $C_L$ =0, 1 pF                | 28 |

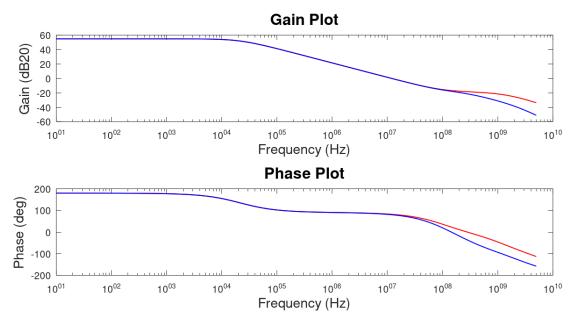

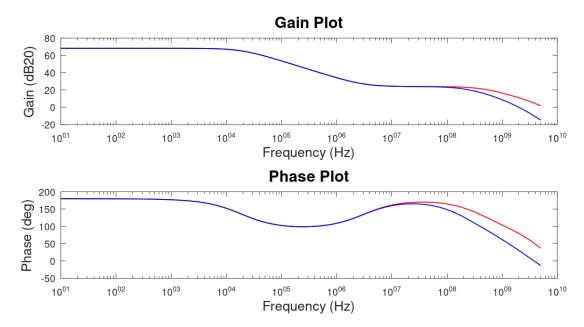

|      | AC simulation results for $I_L$ =0mA with $C_L$ =0, 1pF                             | 29 |

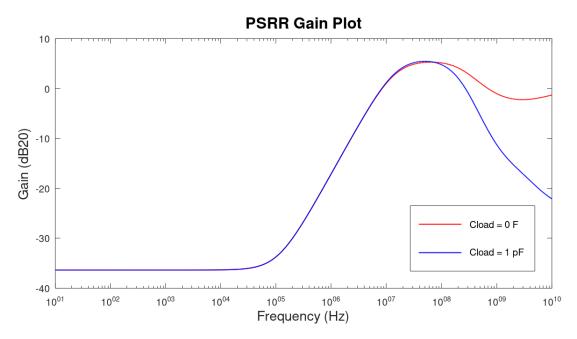

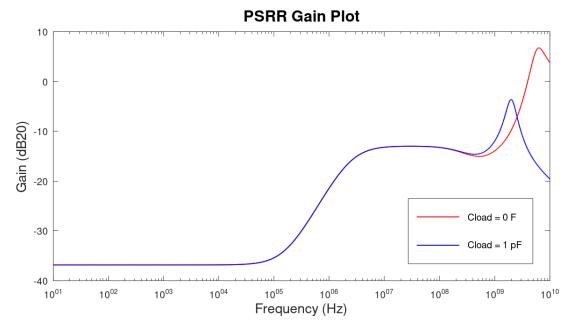

| 3.16 | PSRR simulation results for $I_L$ =0mA with $C_L$ =0, 1pF                           | 29 |

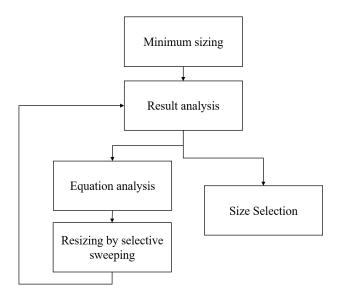

| 4.1  | Sizing flow used to select components' dimensions of the circuit at hand            | 31 |

| 4.2  | Robust Overshoot Detection Circuit, adapted from [27]                               | 33 |

| 4.3  | Undershoot Detection Circuit                                                        | 33 |

| 4.4  | Overshoot Detection Circuit                                                         | 33 |

| 4.5  | Load transient simulation of the ODC                                                | 34 |

| 4.6  | Load transient simulation of the UDC                                                | 35 |

| 4.7  | Load transient simulation of the Full Spike Detection Circuit                       | 35 |

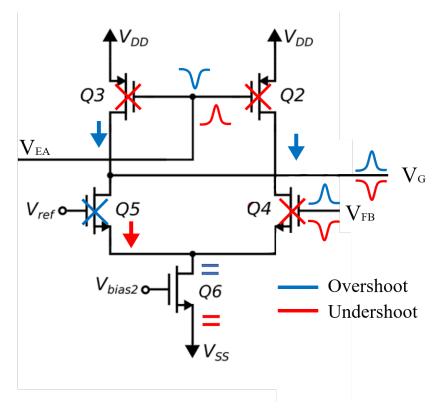

| 4.8  | Fast loop configuration and analysis of the LDO proposed in [10]                    | 36 |

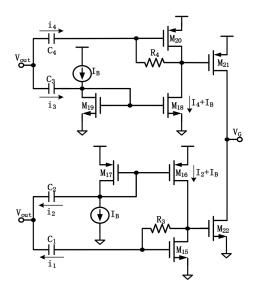

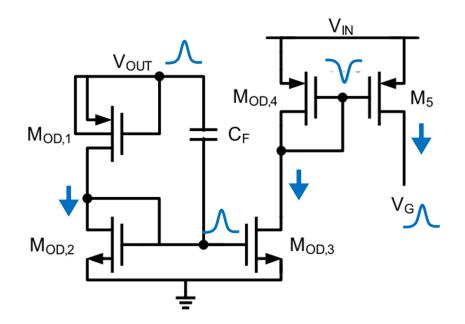

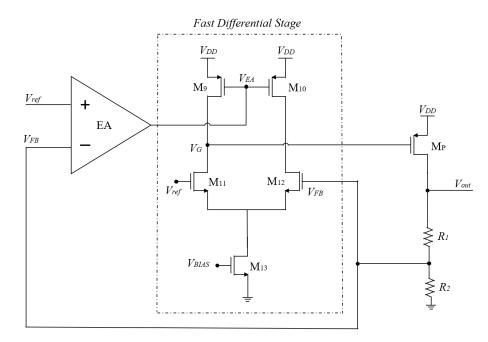

| 4.9  | Fast Differential Stage implemented in the proposed LDO                             | 37 |

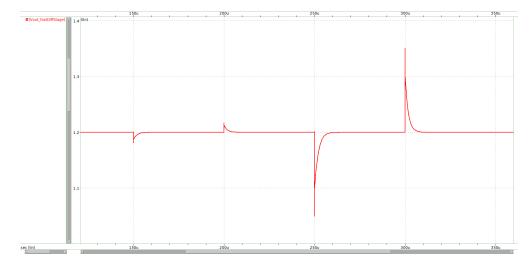

|      | Load transient simulation of the Fast Differential Stage                            | 38 |

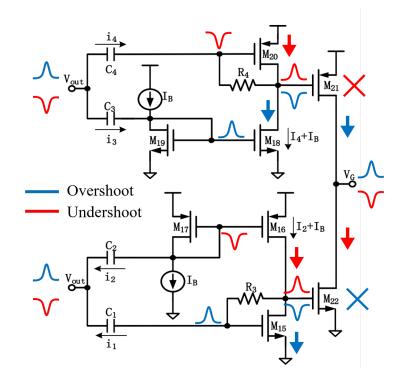

| 4.11 | Class AB transient enhancement circuit based on a differentiator, adapted from [26] | 39 |

|      |                                                                                     |    |

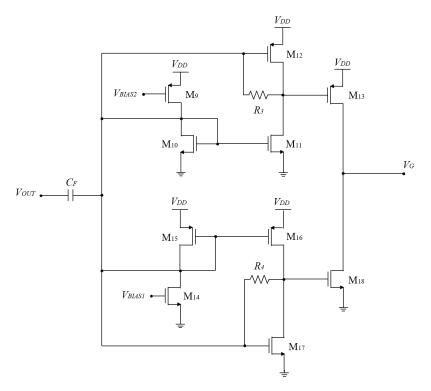

| 4.12  | Fast Loop based on a Differentiator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.13  | Load transient simulation of the differentiator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40       |

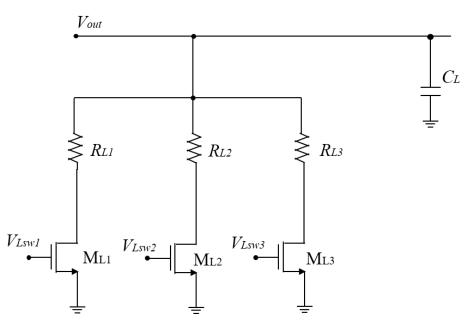

|       | Common Source Fast Loop Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41       |

|       | Load transient simulation of the Common source fast loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42       |

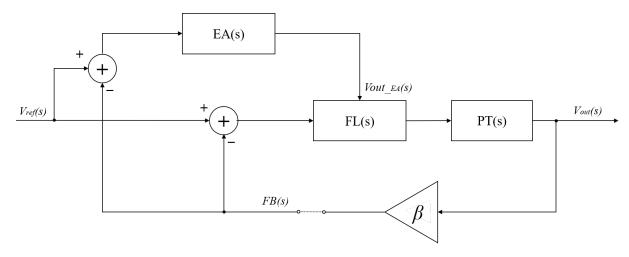

|       | Block Diagram of the system proposed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44       |

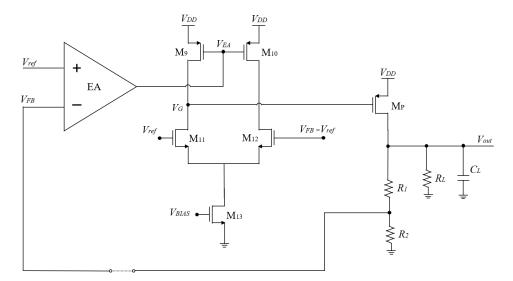

|       | Simulation setup for the open loop frequency response analysis of the slow loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45       |

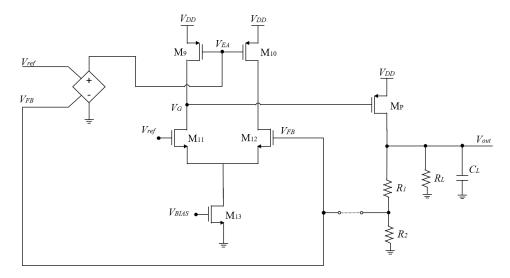

|       | Simulation setup for the open loop frequency response analysis of the fast loop .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45       |

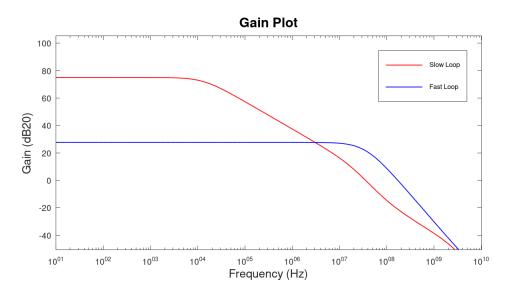

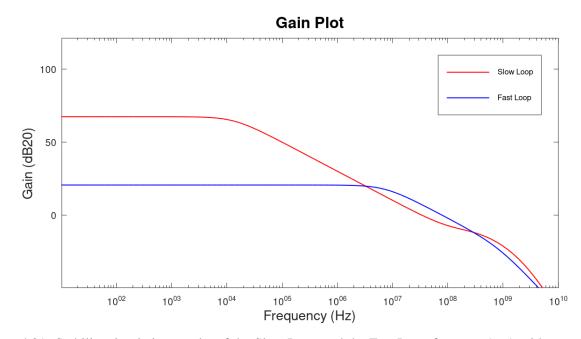

|       | Stability simulation results of the Slow Loop and the Fast Loop for $I_{load}=1$ mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _        |

| ,     | with $C_L=0$ F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46       |

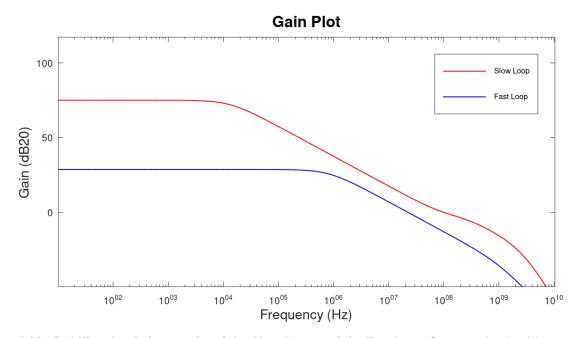

| 4.20  | Stability simulation results of the Slow Loop and the Fast Loop for $I_{load}=1$ mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|       | with $C_L=0$ F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47       |

| 4 2 1 | Stability simulation results of the Slow Loop and the Fast Loop for $I_{load}=1$ mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .,       |

| 1.21  | with $C_L=0$ F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48       |

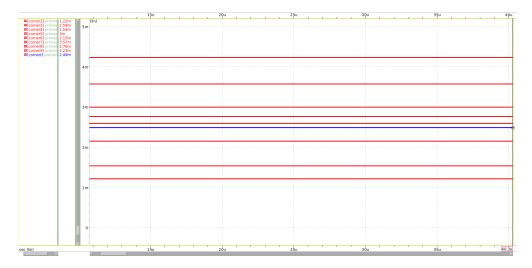

| 4 22  | Current simulations under PVT corner variations when applying a bias voltage in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10       |

| 1.22  | $M_{13}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48       |

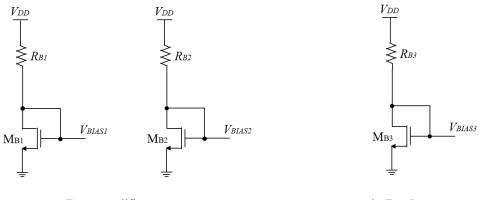

| 1 23  | Implemented Bias Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49       |

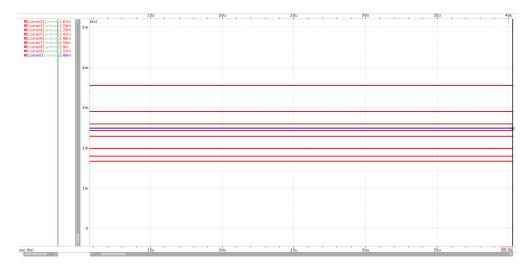

|       | Current simulations under PVT corner variations when biasing transistor $M_{13}$ through                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 7.27  | a current mirror                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50       |

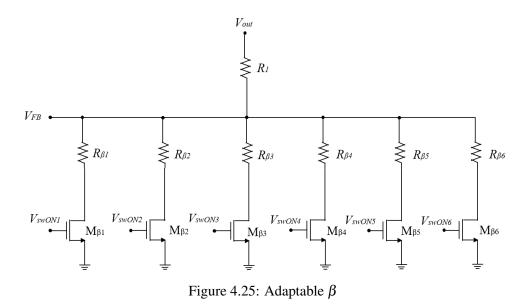

| 1 25  | Adaptable $\beta$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50<br>50 |

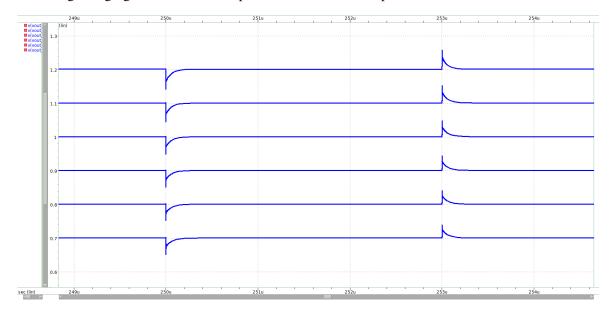

|       | Transient response of the proposed LDO voltage regulator for the available output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50       |

| 4.20  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52       |

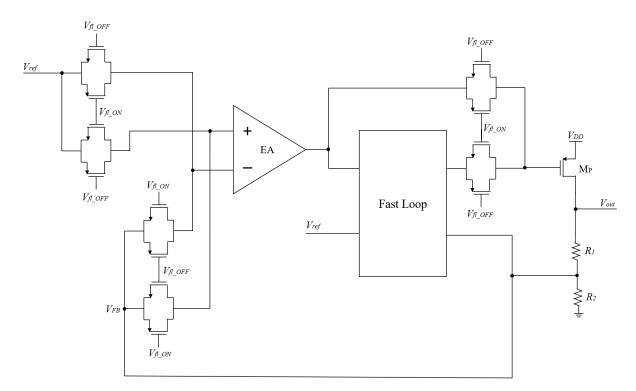

| 4 27  | values, with a load current step of 1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52<br>53 |

|       | Proposed Start-up Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|       | Control Signals of the Start-up circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53       |

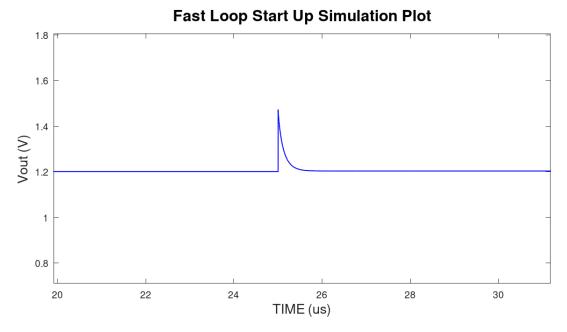

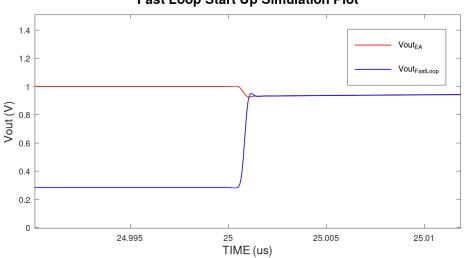

|       | Transient response for the start up circuit under no load conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54       |

|       | Transient response for the start up circuit under no load conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54       |

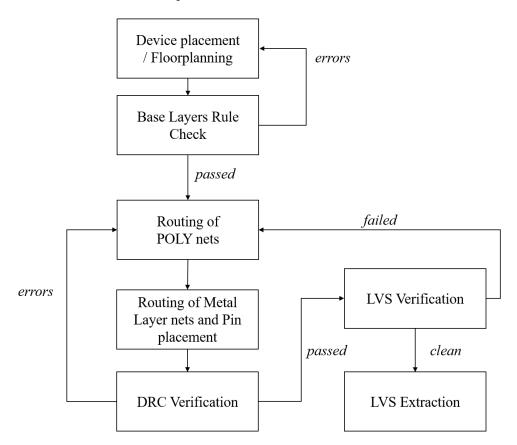

|       | Layout Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55       |

| 4.32  | Layout Design of the proposed fast loop capless LDO voltage regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56       |