# A Wideband Doherty Combiner with Phase Variation Compensation Using LTCC Applicable for High Power Transmission

Youna Jang · Kwanhun Jeong · Jiwon Kim · Daeung Lee · Dal Ahn\*

## Abstract

In this paper, we propose a small-sized Doherty combiner with phase variation compensation using low temperature co-fired ceramic (LTCC) substrate. The proposed design theory for the Doherty combiner is derived using the phase calculation of the S-parameter based on the relation between the input and output ports. The proposed circuit is designed after determining the band edge frequency and the targeted degree of the phase balance. The proposed circuit is verified using the microstrip line and the LTCC substrate. The implemented structure, using LTCC as the substrate, is operated under a high-power test of continuous wave 50 W, the results of which also show that the amplitude and phase balance have variations within 0.2 dB and  $\pm 1^{\circ}$ , respectively. The high-power test shows that the implemented structure is applicable for high power Doherty amplifiers or combiners.

Key Words: Doherty Combiner, High Power Test, LTCC Substrate, Transmission Line, Wide Bandwidth.

## I. Introduction

A power amplifier (PA) is an important component that satisfies the requirements of high linearity and high-power efficiency in a radio frequency (RF) communication system. The PA generally operates near the saturation region to achieve maximum power efficiency. However, the power efficiency of a PA undergoes degradation due to distortions in output signals. Furthermore, its efficiency degrades if the PA operates at power levels below the saturation region. As efficiency decreases, most of the power diverges to produce heat, which deteriorates the characteristics of the amplifier and causes various issues, including heat generation and heat dissipation problems [1–2]. The Doherty power amplifier (DPA) possesses the advantages

of easy implementation and high-power efficiency, although it is widely known to suffer from the disadvantage of a narrow bandwidth.

Therefore, many studies [3–9] have attempted to improve the narrow bandwidth of the DPA. For this purpose, previous studies have used a two-stepped transmission line impedance transformer [3], a branch line structure with a splitter and a combiner [4–5], and the addition of resonance circuits [6–8] or an additional line [9]. However, these previous designs occupy large combiner areas on their substrates due to the  $\lambda/4$  or  $\lambda/2$  electrical lengths of their microstrip lines.

In this paper, a Doherty combiner is implemented to improve the phase bandwidth and reduce the size of the proposed combiner using low temperature co-fired ceramic (LTCC) as the

Manuscript received December 1, 2021; Revised January 11, 2022; Accepted May 4, 2022. (ID No. 20211201-141J) Department of ICT Convergence, Soonchunhyang University, Asan, Korea.

\*Corresponding Author: Dal Ahn (e-mail: dahnkr@sch.ac.kr)

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/4.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

© Copyright The Korean Institute of Electromagnetic Engineering and Science.

substrate. In addition, the desired target specification is satisfied as a result of the continuous wave (CW) 50 W high power test, suggesting the possibility of not only miniaturization but also high-power RF systems.

#### II. DESIGN THEORY

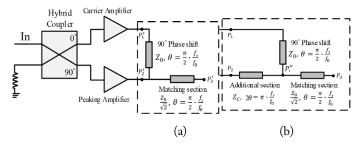

The basic structure of the Doherty power amplifier is composed of a carrier amplifier, a peaking amplifier, and a combiner region, as depicted in Fig. 1(a). The carrier amplifier stage is combined at  $P'_1$ , the peaking amplifier stage at  $P'_2$ , and the output power at  $P'_3$ . The proposed combiner adds a 20 transmission line between  $P_2$  and  $P''_1$ , as shown in Fig. 1(b), while the added characteristic impedance is  $Z_C$ . The added transmission line establishes the desired phase deviation of the target band edge frequency. Phases  $\angle S_{31}$  and  $\angle S_{32}$  of the proposed structure can be obtained by Eqs. (1) and (2) through the ABCD $|_{31}$  and ABCD $|_{32}$  of [9] and by applying the electrical length  $\theta$  of the phase shift line from point  $P_1$  to  $P''_1$  and the  $\angle S_{31}$ ".

where,

A =  $Z_0 Z_C \tan 2\theta (50^2 - Z_C^2)$ , B =  $50\sqrt{2}Z_0 Z_C^2 (1 + \tan 2\theta^2)$ , C =  $50Z_0 Z_C^2 (1 + \tan 2\theta^2)$ , D =  $\sqrt{2}Z_0 Z_C \tan 2\theta (50^2 - Z_C^2)$ ,  $\delta = 50^2 Z_C^2 + Z_C^4 \tan 2\theta^2$ .

$$\angle S_{32} = -\angle \tan^{-1} \left\{ \frac{\sin 2\theta \cos \theta \left(\frac{2Z_C}{Z_0} + \frac{Z_0}{Z_C}\right) + 2\sqrt{2}\cos 2\theta \sin \theta}{3\cos 2\theta \cos \theta - \sin 2\theta \sin \theta \left(\frac{3\sqrt{2}Z_C}{2Z_0} + \frac{\sqrt{2}Z_0}{2Z_C}\right)} \right\}$$

$$(2)$$

Assuming that the phase differences of  $\angle S_{31}$  and  $\angle S_{32}$  at center frequency  $f_0$  is  $\emptyset$ , the phase difference  $\emptyset_0$  between the two inputs of the proposed structure at  $f_0$  is  $\emptyset_0 = \theta_0 + \angle S_{31}'|_{\theta_0} - \angle S_{32}|_{\theta_0}$ . Meanwhile, the phase difference  $\emptyset_1$  be-

Fig. 1. Block diagram of the Doherty power amplifier with (a) a conventional combiner, and (b) the proposed output combiner.

tween the two inputs at the selected frequency  $f_1$  is obtained as  $\emptyset_1 = \theta_1 + 4S_{31}''|_{\theta_1} - 4S_{32}|_{\theta_1}$ . Thus, when  $\theta_0 = \frac{\pi}{2}$ , a phase difference of 90° can be obtained at the center frequency through Eq. (3) [9].

$$(\emptyset_0 - \emptyset_1) - \frac{\pi}{2} \left( 1 - \frac{\omega_1}{\omega_0} \right) = - \measuredangle S_{31}^{"}|_{\theta = \theta_1} + \measuredangle S_{32}|_{\theta = \theta_1}$$

(3)

The proposed circuit has a center frequency of 3.5 GHz, while the phase deviation is set to 2° at an edge frequency of 3.6 GHz. Finally, the  $Z_C$  of the additional transmission line is obtained by solving  $4S_{31}''$ ,  $4S_{32}$ ,  $\theta_1 = \frac{\omega_1}{\omega_0} \frac{\pi}{2}$ , and Eq. (3). The obtained value of the transmission line  $Z_C$  is 38.81 ohm.

#### III. 3D STRUCTURE AND FABRICATION RESULTS

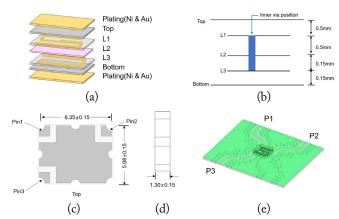

The proposed circuit is implemented using an LTCC substrate with a dielectric constant of 6 for a small-sized Doherty combiner, as shown in Fig. 2. The ground L2 is added in order to integrate three transmission lines into one chip. The thickness of the chip from L1 to L3, as depicted in Fig. 2(a) and 2(b), is controlled through the characteristic impedance equations of the strip line. One of the three lines is for the 180° electrical length of the additional section, while the other two lines are for the 90° phase and the matching section.

Since the characteristic impedance  $Z_{C}$  of the additional section has 38.81  $\Omega$  with a 180° electrical length, the additional line is located at the L3 layer, which is 0.15 mm away from the bottom ground (GND).

To apply a 180° line within a 6.35 mm  $\times$  5.08 mm size, as shown in Fig. 2(c)–2(e), the height of the layer from the GND is reduced to realize a wider line width for  $Z_C$ . The two lines for the 90° phase shift and the matching section are implemented in one layer. The L1 and L3 layers are connected at the  $P_1''$  node. The realized LTCC structure is then mounted on the PCB substrate—a Rogers 5880 with a dielectric constant of 2.2. Fig. 3(a)–

Fig. 2. (a) LTCC diagrams with several layers, (b) side diagrams of the LTCC, (c) top dimension, (d) side dimension, and (e) 3D structure with PCB substrate.

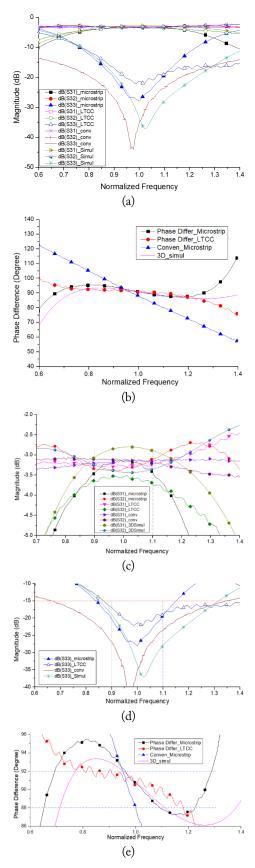

Fig. 3. Comparison results of the conventional, proposed 3D structure, and measured results: (a) magnitude, (b) output phase difference, (c) insertion loss, (d) return loss, and (e) phase balance.

3(e) show the magnitude characteristics, phase differences, insertion loss, return loss, and phase balance of the fabrication results. The Doherty combiner is implemented using a Rogers 5880 microstrip line. The magnitude results are  $S_{31} = -3.16$  dB,  $S_{32} = -3.35$  dB, and  $S_{33} = -28.06$  dB, while the phase difference is 90.72° at the normalized center frequency. Meanwhile, the Doherty combiner with the LTCC substrate exhibits magnitude performances of  $S_{31} = -3.26$  dB,  $S_{32} = -3.54$  dB, and  $S_{33} =$ -21.42 dB, with a 90.39° phase difference between  $S_{32}$  and  $S_{31}$ at normalized center frequency. The analysis confirmed that it has uniform phase differences within the targeted bandwidth close to 90° at the center frequency and close to 89.71° at the normalized selected frequency ( $f_1 = 1.06$ ). The proposed structure has a 34.3% normalized fractional bandwidth (FBW) ranging from 0.837 to 1.18 for  $90^{\circ} \pm 2^{\circ}$ . The magnitude and phase characteristics of the LTCC Doherty combiner also show similar results as the proposed circuit using the microstrip line. Therefore, the measurement results confirm the validity of the proposed theory.

## IV. HIGH POWER TEST OF DUT

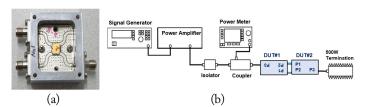

Fig. 4(a) shows the PCB jig with the LTCC substrate implemented as the Device Under Test (DUT). The high-power test (HPT) is used for checking RF performances when high power is conducted by the test jigs. Fig. 4(b) depicts the setup for the HPT. The equipment required for the HPT process consists of a signal generator, a power amplifier, a power meter, an isolator, a coupler, a termination component, and two test jigs. The signal generator produces a signal, which the power amplifier amplifies, while the power meter checks whether 50 W power is appropriately supplied. The HPT procedures are as follows:

- 1. The experimental setup for the high-power test is organized, as shown in Fig. 4(b).

- 2. Two DUTs are linked with each other in a back-to-back connection—the P3 of the first DUT signifies the input port, while the P3 of the second DUT signifies the output port.

- 3. A 50-W CW at 3.6 GHz is applied to the P3 of the first DUT for 5 minutes.

- 4. The other DUTs are also tested in the same manner.

Fig. 4. (a) PCB jig with DUT, (b) setup diagram for the high-power test.

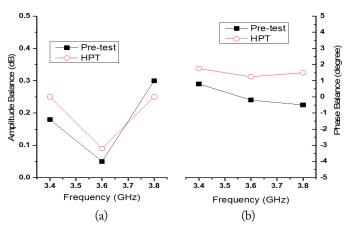

Fig. 5. Pre- and post-high-power test: (a) amplitude balance and (b) phase balance.

The HPT results highlight that the amplitude and phase balance have variations within 0.2 dB and  $\pm 1^{\circ}$ , respectively, as shown in Fig. 5. Therefore, the proposed Doherty combiner using LTCC operates well, with fewer variations in phase balance, even under 50 W CW conditions.

#### V. CONCLUSION

In this paper, a small-sized Doherty combiner using LTCC substrate is proposed. The structure sets the selected frequency of f1 and the targeted degree of phase balance. Thus, the characteristic impedance with a 180° line can be obtained in the additional section of the combiner from the proposed design theory. Furthermore, to minimize the circuit size, the proposed circuit was implemented using three layers in the LTCC substrate. For the wideband application of the Doherty power amplifier, the proposed circuit was operated under CW 50 W at 3.6 GHz. The amplitude and phase balance were found to be less than 0.06 dB and  $\pm 1^\circ$ , respectively. Therefore, the proposed circuit is applicable for use in miniaturized high power Doherty Power amplifiers and small-sized high-power combiners in future communication systems.

These results are supported by the Regional Innovation Strategy (RIS) through the National Research Foundation of Korea (NRF), funded by the Ministry of Education (MOE) (No. 2021RIS-004) and the Soonchunhyang University Research Fund.

#### REFERENCES

- [1] S. C. Cripps, *RF Power Amplifiers for Wireless Communications*, Norwood, MA: Artech House, 1999.

- [2] B. Kim, J. Kim, I. Kim, and J. Cha, "The Doherty power amplifier," *IEEE Microwave Magazine*, vol. 7, no. 5, pp. 42-50, 2006.

- [3] A. Grebennikov and J. Wong, "A dual-band parallel Doherty power amplifier for wireless applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 10, pp. 3214-3222, 2012.

- [4] L. Piazzon, R. Giofre, P. Colantonio, and F. Giannini, "A wideband Doherty architecture with 36% of fractional bandwidth," *IEEE Microwave and Wireless Components Letters*, vol. 23, no. 11, pp. 626-628, 2013.

- [5] R. Giofre, P. Colantonio, F. Giannini, and L. Piazzon, "New output combiner for Doherty amplifiers," *IEEE Microwave and Wireless Components Letters*, vol. 23, no. 1, pp. 31-33, 2013.

- [6] M. N. A. Abadi, H. Golestaneh, H. Sarbishaei, and S. Boumaiza, "An extended bandwidth Doherty power amplifier using a novel output combiner," in *Proceedings of 2014 IEEE MTT-S International Microwave Symposium (IMS)*, Tampa, FL, 2014, pp. 1-4.

- [7] S. Chen, "New output combiner design for broadband Doherty power amplifier," in *Proceedings of 2016 IEEE International Conference on Computational Electromagnetics (ICCEM)*, Guangzhou, China, 2016, pp. 391-393.

- [8] S. Chen, G. Wang, Z. Cheng, and Q. Xue, "A bandwidth enhanced Doherty power amplifier with a compact output combiner," *IEEE Microwave and Wireless Components Letters*, vol. 26, no. 6, pp. 434-436, 2016.

- [9] D. Lee, S. Kim, Y. Jang, S. Koo, I. S. Kim, J. Lim, J. Cho, and D. Ahn, "Modified Doherty combiner with adjustable phase deviation," *Microwave and Optical Technology Letters*, vol. 60, no. 11, pp. 2834–2839, 2018.

## Youna Jang

received her master's degree in Display Engineering from Hanyang University, Seoul, Korea, in 2014. She also received her Ph.D. in Electrical Communication System Engineering from Soonchunhyang University, Choongnam, Korea, in 2019. She participated as a designer of the Duplexer filter in an internship program in 2015 at Qorvo, Bundang, South Korea. She was a lecturer at Soonchunhyang

University from 2016 to 2020. She is currently a research professor at the Radio and Mechatronics Research Center. Her research areas include the design of passive components in microwave bands.

## Daeung Lee

was born in Korea in 1989. He received his Ph.D. degree in Electrical and Communication System Engineering from Soonchunhyang University, Asan, Korea, in 2019. Currently, he works for Huba. His current research interests include RF passive elements theory, design, and multi-layer passive device design.

## Kwanhun Jeong

was born in Mokpo, Korea, in 1994. He received his B.E. degree in Electrical Engineering from Soon-chunhyang University, Asan, Korea, in 2020. Currently, he is an M.E. student at Soonchunhyang University. His current research interests include RF passive device theory, design, and testing.

## Dal Ahn

received his B.S., M.S., and Ph.D. degrees in Electronics from Sogang University, Seoul, Korea, in 1984, 1986, and 1990, respectively. From 1990 to 1992, he worked with the Mobile Communications Division, Electronics, and Telecommunications Research Institute (ETRI), Daejeon, Korea. Since 1992, he has been affiliated with the School of Electrical and Electronic Engineering, Soonchunhyang University,

Asan, Chungnam, Korea, where he is currently a professor. Currently, he is also the chief of the RF and Microwave Component Research Center (RAMREC), Soonchunhyang University. He is also a technical consultant for Tel Wave Inc., Suwon, Korea. His current research interests include the design and application of passive and active components at radio and microwave frequencies, the design of RF front-end modules for various handset systems using low-temperature co-fired ceramic (LTCC) technology, DGS circuit applications, and circuit modeling using a commercial EM analysis program. Prof. Ahn is also an editor of the *Journal of Korea Electromagnetic Engineering Society* and a senior member of the Korea Electromagnetic Engineering Society (KEES).

## Jiwon Kim

was born in Seoul, Korea, in 1994. She received her M.E. degree in Electrical Communication System Engineering from Soonchunhyang University, Asan, Korea, in 2019. Currently, she is a Ph.D. student at Soonchunhyang University. Her current research interests include RF passive device and filter design, and process design kit (PDK).