Wayne State University Dissertations

January 2021

# High Mobility N-Type Field Effect Transistors Enabled By Wse2/ pdse2 Heterojunctions

Arthur Bowman Iii Wayne State University

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations

Part of the Electrical and Computer Engineering Commons, and the Quantum Physics Commons

#### **Recommended Citation**

Bowman Iii, Arthur, "High Mobility N-Type Field Effect Transistors Enabled By Wse2/pdse2 Heterojunctions" (2021). Wayne State University Dissertations. 3509. https://digitalcommons.wayne.edu/oa\_dissertations/3509

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

# HIGH MOBILITY N-TYPE FIELD EFFECT TRANSISTORS ENABLED BY WSE<sub>2</sub>/PDSE<sub>2</sub> HETEROJUNCTIONS

by

# ARTHUR BOWMAN III DISSERTATION

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

#### **DOCTOR OF PHILOSOPHY**

| Advisor        | Da |

|----------------|----|

| Approved By:   |    |

|                |    |

| MAJOR: PHYSICS |    |

| 2021           |    |

#### **DEDICATION**

This work is dedicated to my father, Attorney Arthur Bowman, Jr., who passed away from complications due to covid-19 in May 2020. It is one of the great disappointments of my life that he did not survive to witness this. He played an integral role in my decision to study the nanoscale world. I will continue that study in his honor.

#### ACKNOWLEDGEMENTS

I would like to acknowledge my advisor, Dr. Zhixian Zhou, whose attentiveness to my work and great enthusiasm for research made this all possible. Much appreciation also goes to the members of my dissertation committee: Dr.'s Jian Huang, Zhi Feng Huang, and Ming-Cheng Cheng, and Dr.'s Sean Gavin and Ratna Naik of the Wayne State University Department of Physics and Astronomy for their mentorship and encouragement.

I commend the previous generation of students in the Zhou Group; Dr.'s Hsun Jen Chuang, Bhim Chamlagain, and Meeghage Madusanka Perera, who taught me to perform many of the techniques I will discuss in this work. I owe a great debt to the other group members of my generation, Dr.'s Kraig Andrews and Upendra Rijal, whose collaboration and advice made me the researcher I am today. Our research would not have been possible without the Lurie Nanofabrication Facility, and LNF staff members Sandrine Martin, Vishva Ray, and Matt Oonk.

I also wish to acknowledge our collaborators, Dr. David Mandrus at The University of Tennessee, Knoxville and his students, Dr. Michael Koehler, and Amanda Haglund, for providing materials used in this work. I would like to thank the Initiative for Maximizing Student Development Program, National Science Foundation Alliances for Graduate Education and the Professoriate Program, and Dr. Jim Kaskas for providing financial support. Thank you.

### TABLE OF CONTENTS

| DEDICATION                                                                     | ii  |

|--------------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                               | iii |

| LIST OF FIGURES                                                                | vi  |

| CHAPTER 1: MOTIVATION                                                          |     |

| 1.1: PdSe <sub>2</sub> : A Promising New Material for Post-Silicon Electronics | 1   |

| 1.2: The PdSe <sub>2</sub> Lattice and Energy Band Structure                   | 5   |

| 1.3: Performance Limitations of PdSe <sub>2</sub> FETS                         | 10  |

| 1.3.1: Transfer Characteristics                                                | 12  |

| 1.3.2: Output Characteristics                                                  | 16  |

| 1.4: Strategy for High Performance PdSe <sub>2</sub> FETS                      | 17  |

| Chapter 2: DEVICE FABRICATION AND CHARACTERIZATION                             |     |

| 2.1 Mechanical Exfoliation                                                     | 25  |

| 2.2 Van der Waals Assembly                                                     |     |

| 2.2.1: PDMS Transfer                                                           | 28  |

| 2.2.2: PC Pick Up Method                                                       | 30  |

| 2.2.3: PPC Pick Up Method                                                      | 32  |

| 2.3 Characterization_Surface Morphology and Film Thickness                     |     |

| 2.3.1: Optical Microscopy                                                      | 35  |

| 2.3.2: Atomic Force Microscopy                                                 | 35  |

| 2.4 Metallization Process                                                      |     |

| 2.4.1: Electron Beam Lithography                                               | 37  |

| 2.4.2: Metal Deposition                                                        | 37  |

| 2.5 Electrical Characterization                                                | 40  |

## **Chapter 3: RESULTS AND DISCUSSION**

| 3.1 Comparison of WSe <sub>2</sub> /PdSe <sub>2</sub> FETs and PdSe <sub>2</sub> FETs |    |

|---------------------------------------------------------------------------------------|----|

| 3.1.1 Room Temperature Performance                                                    | 43 |

| 3.1.2 Temperature Dependence                                                          | 50 |

| 3.1.3 Schottky Barrier Height                                                         | 55 |

| 3.1.4 Contact Resistance                                                              | 58 |

| Chapter 4: CONCLUSION AND FUTURE WORK                                                 | 63 |

| REFERENCES                                                                            | 65 |

| ABSTRACT                                                                              | 74 |

| AUTORIOCDAPHICAL STATEMENT                                                            | 74 |

#### LIST OF FIGURES

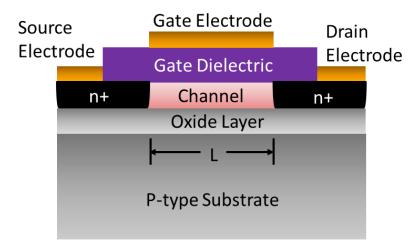

| <b>Figure 1.1</b>   Schematic of a basic 3-terminal MOSFT. This device is ' <i>n</i> -type', meaning most charge carriers are electrons, rather than holes. <i>n</i> -type MOSFETs will be the focus of this work, although the logic is ever the same for <i>p</i> -type                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

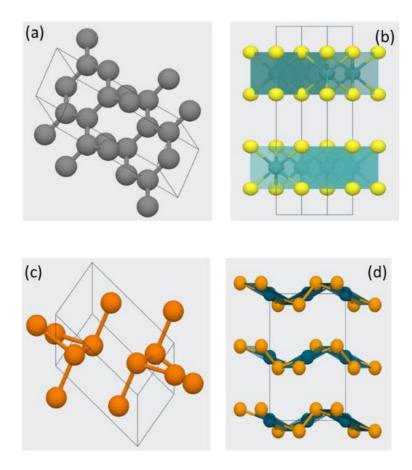

| <b>Figure 1.2</b>   Lattice Structure of <b>a:</b> graphene, <b>b:</b> MoS <sub>2</sub> (to represent traditional 1T and 2H TMDCs), <b>c:</b> BP, and <b>d:</b> PdSe <sub>2</sub> . The graphene and BP crystals are side viewed to show the shapes of their respective unit cells. Note that atoms in graphene and MoS <sub>2</sub> lattices are confined to a single plane, while those of BP and PdSe <sub>2</sub> are in and out-ofplane but are still within the limit of a 2D system. This is an illustration of 'puckering'. Originally appeared in the Materials Project. <sup>106</sup> |

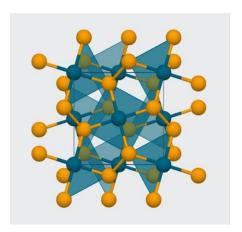

| <b>Figure 1.3</b>   Overhead view of the PdSe <sub>2</sub> lattice. Originally appeared in the Materials Project. <sup>106</sup> <b>6</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

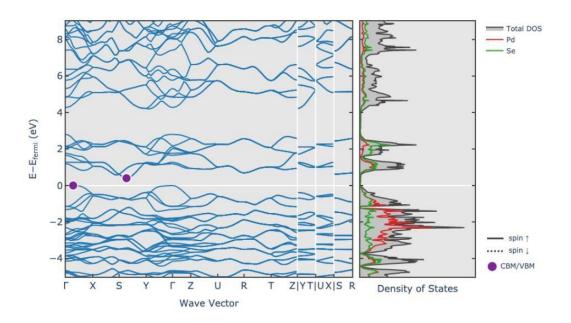

| <b>Figure 1.4</b>   Calculated DOS and energy band structure for bulk PdSe <sub>2</sub> . Originally appeared in the Materials Project. 107                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

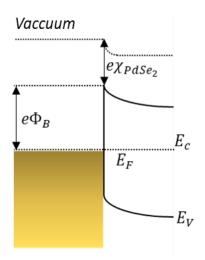

| Figure 1.5   Metal source contact of a PdSe <sub>2</sub> FET at the Schottky-Mott limit14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

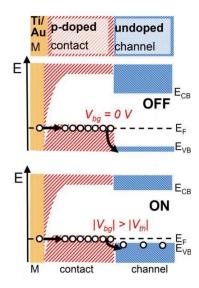

| <b>Figure 1.6</b>   Band diagram explaining the operation of a WSe <sub>2</sub> FET with degenerately <i>p</i> -doped 2D/2D contacts. Originally appeared in ref. 59                                                                                                                                                                                                                                                                                                                                                                                                                             |

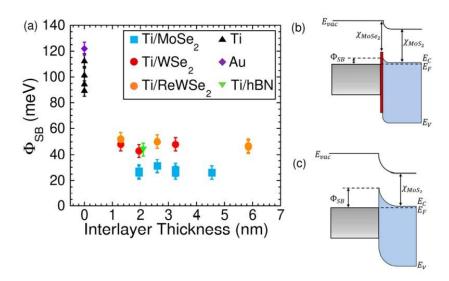

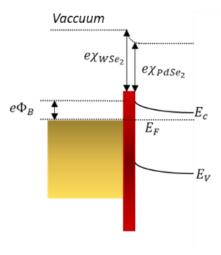

| <b>Figure 1.7</b>   <b>a.</b> SBH of MoS <sub>2</sub> FETs with 2D material interlayers as a function of interlayer thickness. <b>b-c.</b> Energy band diagrams of an MoS <sub>2</sub> FETs with and without MoSe <sub>2</sub> as a semiconductor interlayer, showing the mechanism by which the SBH is reduced when MoSe <sub>2</sub> is reduced at the metal/semiconductor interface. ( <b>a-c</b> originally appeared in ref 64) <b>d.</b> Proposed energy band diagram of PdSe <sub>2</sub> FETs with semiconductor interlayer. The interlayer can be any (stable) group 6 or group 10 TMDC  |

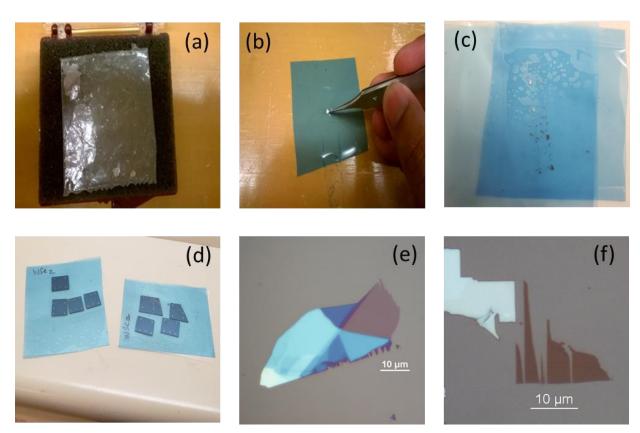

| <b>Figure 2.1</b>   <b>a-c:</b> Mechanical exfoliation of MoS <sub>2</sub> . <b>d:</b> Clean SiO <sub>2</sub> on Si substrates after being placed on exfoliated WSe <sub>2</sub> (before heating step) <b>e-f:</b> Optical micrographs of large area monolayer WSe <sub>2</sub> (left) and few-layer PdSe <sub>2</sub> (right). Both samples were exfoliated to SiO <sub>2</sub> using our modified version of the method developed by Huang32                                                                                                                                                   |

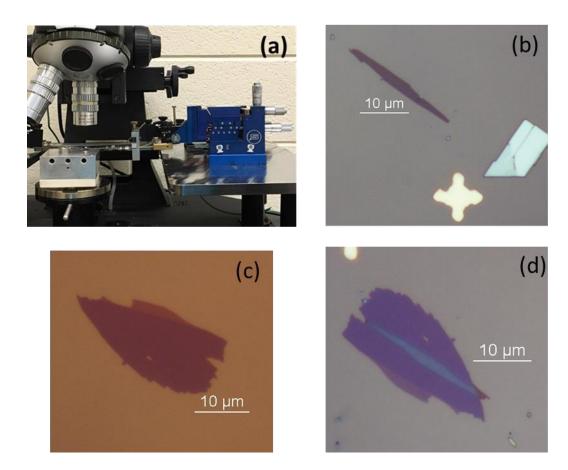

| <b>Figure 2.2</b>   <b>a:</b> Set-up for VDW assembly: optical microscope, (for viewing the transfer) sample stage, and micromanipulator (with mounted glass side). <b>B:</b> Few-layer PdSe <sub>2</sub> on SiO <sub>2</sub> , <b>c:</b> Few-layer WSe <sub>2</sub> on SiO <sub>2</sub> , <b>d:</b> VDW consisting of few-layer WSe <sub>2</sub> stacked atop few-layer PdSe <sub>2</sub> . <b>35</b>                                                                                                                                                                                           |

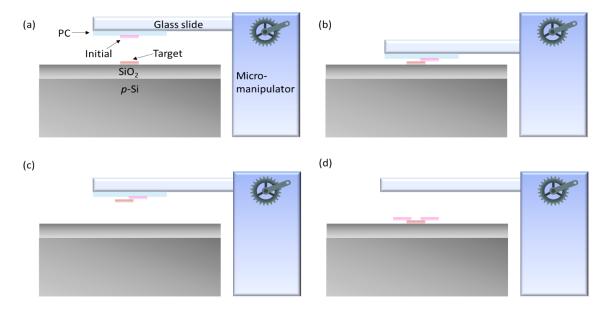

Figure 2.3| a: sample on PDMS aligned with another on  $SiO_2$  via the micromanipulator. b: Touchdown of the PC film to bring the initial and target materials into intimate contact. c: Pick

| up of the target material by the initial material <b>d:</b> Completed VDW heterostructure on SiO <sub>2</sub> (after dissolving PC)38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

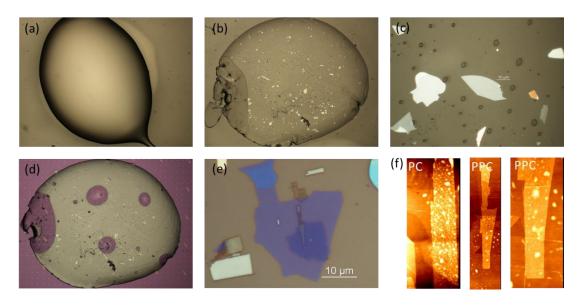

| <b>Figure 2.4</b>   <b>a:</b> drop-casted PPC film on PDMS <b>b-c</b> : PPC film after picking up h-BN at 40° C. <b>d</b> : PPC film after being flipped onto SiO <sub>2</sub> . <b>e:</b> Completed VDW heterostructure on SiO <sub>2</sub> after annealing away PPC. <b>f:</b> comparison of atomic force micrographs of the structure fabricated in part <b>e</b> to a similar structure fabricated using PC. Notice the near-absence of bubbles in the overlap region between materials when PPC is used instead of PC41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

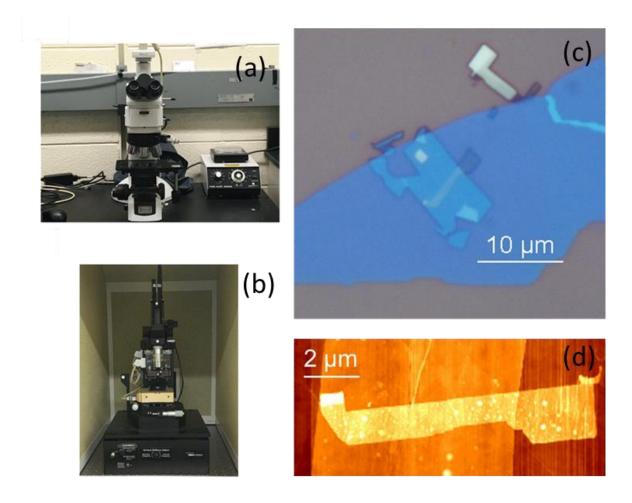

| <b>Figure 2.5</b> a: Nikon Eclipse LV150 Optical Microscope and optical micrograph of VdWH b: Park XE15 AFM and AFM scan of the same sample, confirming the sample has a smooth and atomically clean surface44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| atomically clean surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

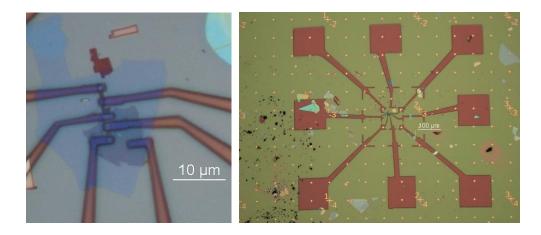

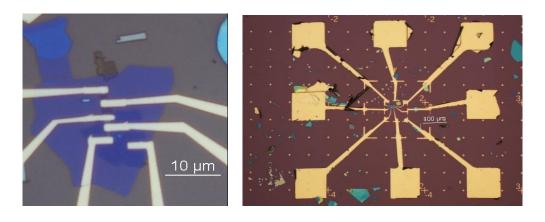

| <b>Figure 2.7</b>   Optical micrographs of a few-layer PdSe <sub>2</sub> FET after liftoff, the final step of the metallization process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

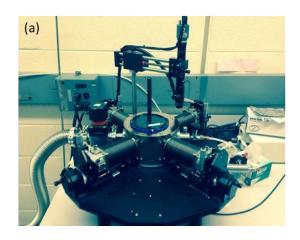

| Figure 2.8 a: Lakeshore TTPX Vacuum Probe Station b: Keithley 4200 Semiconductor Characterization System50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

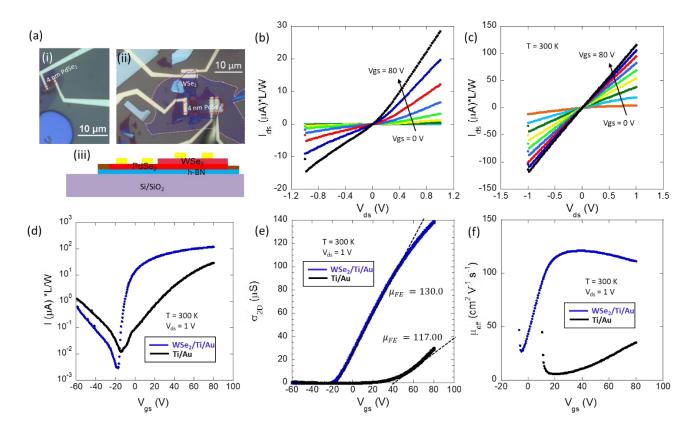

| <b>Figure 3.1</b>   <b>a:</b> ( <b>a</b> ) Device structure of WSe <sub>2</sub> and WSe <sub>2</sub> /PdSe <sub>2</sub> FETs. Optical micrograph of FETs consisting of ( <b>i</b> ) a ~ 4nm thick PdSe <sub>2</sub> channel, ( <b>ii</b> ) a heterostructure channel of ~4 nm thick PdSe <sub>2</sub> and a ~ 2 nm thick WSe <sub>2</sub> , and ( <b>iii</b> ) the side-view schematics of the PdSe <sub>2</sub> and WSe <sub>2</sub> /PdSe <sub>2</sub> devices. ( <b>b-c</b> ) Output characteristics of ( <b>b</b> ) the PdSe <sub>2</sub> and ( <b>c</b> ) the WSe <sub>2</sub> /PdSe <sub>2</sub> FETs. ( <b>d</b> ) Transfer characteristics of the PdSe <sub>2</sub> and WSe <sub>2</sub> /PdSe <sub>2</sub> FETs plotted on semilog scale. ( <b>e</b> ) Two-terminal 2D conductivity of the PdSe <sub>2</sub> and WSe <sub>2</sub> /PdSe <sub>2</sub> FET as a function of gate voltage plotted on linear scale. ( <b>f</b> ) Effective-mobility of the PdSe <sub>2</sub> and WSe <sub>2</sub> /PdSe <sub>2</sub> FETs as a function of gate voltage. All the date are taken at room temperature |

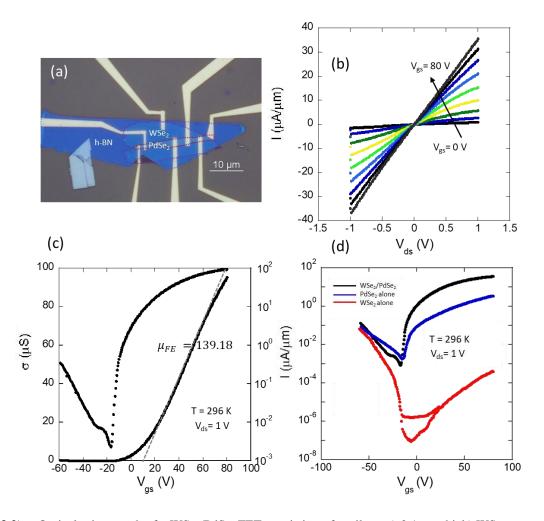

| <b>Figure 3.2</b>   <b>a:</b> Optical micrograph of a WSe <sub>2</sub> /PdSe <sub>2</sub> FET consisting of a trilayer (~2.1 nm thick) WSe <sub>2</sub> over a ~ 4 nm thick PdSe <sub>2</sub> in the channel. ( <b>b</b> ) Output and ( <b>c</b> ) transfer characteristics of the WSe <sub>2</sub> /PdSe <sub>2</sub> FET at room temperature. ( <b>d</b> ) Comparison of the drain current <i>versus</i> gate voltage of FETs consisting of WSe <sub>2</sub> /PdSe <sub>2</sub> , PdSe <sub>2</sub> , and WSe <sub>2</sub> channels. The over 4 orders of magnitude lower on-current through the WSe <sub>2</sub> channel than through the WSe <sub>2</sub> /PdSe <sub>2</sub> channel indicates that the current in the WSe <sub>2</sub> /PdSe <sub>2</sub> device primarily passes through the PdSe <sub>2</sub> layer in the channel region                                                                                                                                                                                                                                                         |

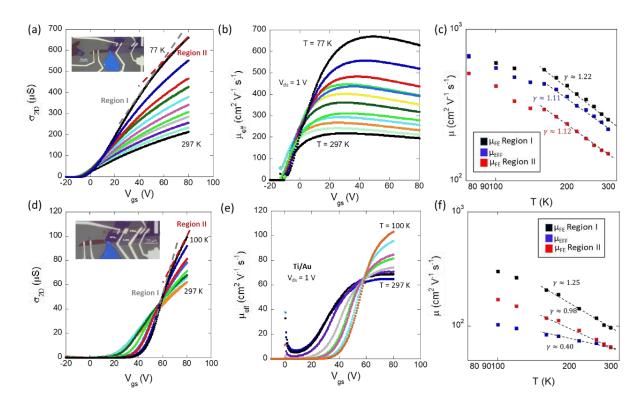

| <b>Figure 3.3</b>   <b>a:</b> Temperature-dependent transfer characteristics and mobility comparison for two FETs with Ti/WSe <sub>2</sub> /PdSe <sub>2</sub> ( <b>a,b, c</b> ) and Ti/PdSe <sub>2</sub> contacts ( <b>d,e,f</b> ). Both devices consist of a 6.7 nm thick PdSe <sub>2</sub> in the channel; and the WSe <sub>2</sub> at the contacts is $\sim 2.1$ nm. ( <b>a,d</b> ) The 2D conductivity measured down to 77 K at $V_{ds} = 1$ V. Red dashed lines indicate different slopes in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

the low and high gate-voltage regions labeled as region I and region II, respectably). (**b,e**) Effective mobility defined as  $\mu_{eff} = \sigma_{2D}/C_{gs}$  ( $V_{gs}-V_{th}$ ). (**c,f**) Comparison of temperature-

| dependent peak (maximum) effective mobility ( $\mu_{eff}$ ) and field-effect mobility ( $\mu_{FE}$ ) extracted from regions I and II in (a, d)65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

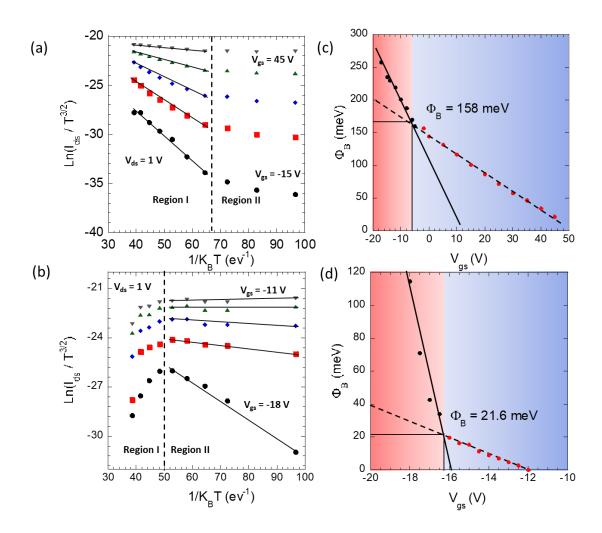

| <b>Figure 3.4</b>   <b>a:</b> Flat-band Schottky barrier height extraction. ( <b>a,b</b> ) Arrhenius plots of ( <b>a</b> ) PdSe <sub>2</sub> and ( <b>b</b> ) WSe <sub>2</sub> /PdSe <sub>2</sub> FETs contacted by Ti metal for various gate voltages. ( <b>c,d</b> ) The extracted <i>n</i> -type effective barrier height at various gate voltage, where the flat-band SBH is measured to be ( <b>c</b> ) 158 meV and ( <b>d</b> ) 21.6 meV in PdSe <sub>2</sub> and WSe <sub>2</sub> /PdSe <sub>2</sub> FETs, respectively. The PdSe <sub>2</sub> FET consists of a ~ 9 nm PdSe <sub>2</sub> channel. The WSe <sub>2</sub> /PdSe <sub>2</sub> FET consists of a ~ 4 nm PdSe <sub>2</sub> and ~ 2 nm WSe <sub>2</sub> in the heterostructure channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

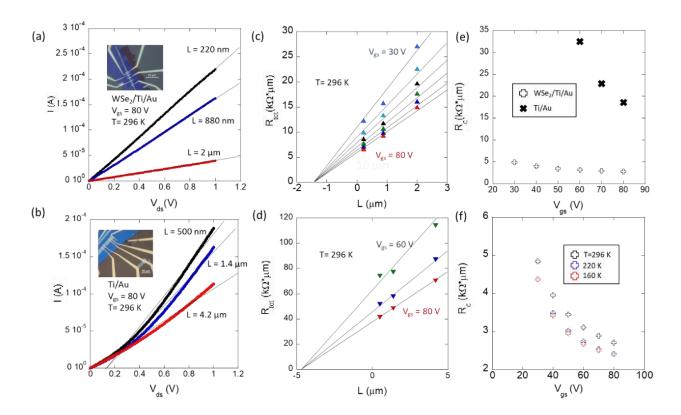

| <b>Figure 3.5</b>   <b>a:</b> Contact resistance of WSe <sub>2</sub> /PdSe <sub>2</sub> and PdSe <sub>2</sub> FETs with Ti metal contacts. ( <b>a</b> - <b>b</b> ) Room-temperature $I_{ds}$ - $V_{gs}$ output curves for different channel length at $V_{gs} = 80$ V for ( <b>a</b> ) WSe <sub>2</sub> /PdSe <sub>2</sub> and ( <b>b</b> ) PdSe <sub>2</sub> FETs. Both the WSe <sub>2</sub> /PdSe <sub>2</sub> and PdSe <sub>2</sub> devices contain a ~ 9 nm thick PdSe <sub>2</sub> in the channel. ( <b>c-d</b> ) The total resistance normalized by width ( $R_{Total}$ ) as a function of channel length for each type determined by the slopes from ( <b>a-b</b> ) at different gate voltages for the ( <b>c</b> ) WSe <sub>2</sub> /PdSe <sub>2</sub> and ( <b>d</b> ) PdSe <sub>2</sub> FETs. The y-intercept yields twice the contact resistance ( $2R_{\rm C}$ ). ( <b>e</b> ) Comparison of extracted contact resistance for the WSe <sub>2</sub> /PdSe <sub>2</sub> and PdSe <sub>2</sub> devices as a function of carrier density (gate voltage bias). ( <b>f</b> ) Contact resistance of the WSe <sub>2</sub> /PdSe <sub>2</sub> devices as a function of carrier density measured at different temperatures |

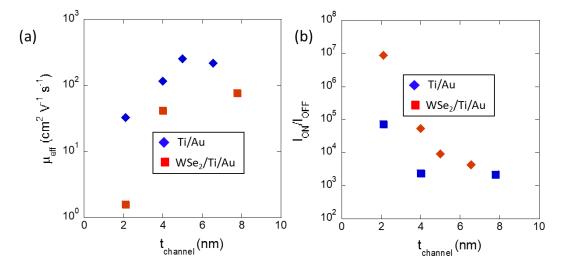

| <b>Figure 3.6</b>   <b>a:</b> Effective mobility of several PdSe <sub>2</sub> /WSe <sub>2</sub> FETs and PdSe <sub>2</sub> FETs with varying PdSe <sub>2</sub> thicknesses. ( <b>b</b> ) ON/OFF ratios of the PdSe <sub>2</sub> /WSe <sub>2</sub> and PdSe <sub>2</sub> FETs fabricated as a function of PdSe <sub>2</sub> thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

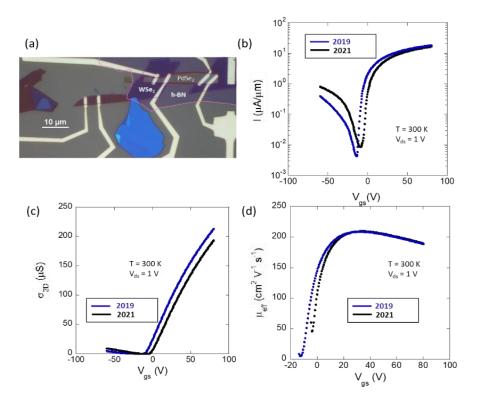

| <b>Figure 3.7</b> a: 6.7 nm WSe <sub>2</sub> /PdSe <sub>2</sub> FET when it was first fabricated in 2019. b: Semilog plot of transfer characteristics of 6.7 nm WSe <sub>2</sub> /PdSe <sub>2</sub> FET in 2019 and 2021, showing the increase in the OFF current. c: 2-terminal conductivity of 6.7 nm WSe <sub>2</sub> /PdSe <sub>2</sub> FET in 2019 and 2021, showing a slight decrease and positive shift of the threshold voltage. d: Effective mobility of 6.7 nm WSe <sub>2</sub> /PdSe <sub>2</sub> FET in 2019 and 2021, showing little change over time76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **CHAPTER 1. MOTIVATION**

#### 1.1 PdSe<sub>2</sub>: A Promising Candidate for Post-Silicon Electronics

The continued downscaling of metal-oxide-semiconductor field effect transistor (MOSFET) technology has been the driving force of the digital age. The progress is basically measured by Moore's Law, which predicts that the number of transistors that are densely packed into an integrated circuit doubles every 2 years<sup>1</sup>. The highest count to date was achieved in 2020 by the Chinese technology company Huawei who reported 1.53 x 10<sup>10</sup> MOSFETs on their HiSilicon Kirin 9000 processor. A schematic of a standard three-terminal MOSFET is shown in figure 1.1. Silicon is the most widely used channel material in MOSFETs. However, silicon MOSFETs are approaching a fundamental limit. In standard silicon-on-insulator (SOI) devices this is captured by the transistor characteristic length, λ,

$$\lambda_{SOI} = \sqrt{\frac{\varepsilon_s}{c_g} t_s} \tag{1.1}$$

Where  $\varepsilon_s$  is the channel dielectric constant,  $C_g$  is the gate capacitance per unit area and  $t_s$  is the channel thickness. If the channel length is 5 to 10 times larger than  $\lambda$ , the drain electrode will be electrostatically shielded from the source by the combination of the gate and substrate. Around the 7 nm mark, the drain electrode is close enough to the source to participate in the injection of charge carriers into the channel region, which causes the device to turn on prematurely in a phenomenon known as Drain Induced Barrier Lowering (DIBL)<sup>2</sup>.

IBM departed from the conventionally used MOSFET and FinFET designs to demonstrate silicon-based FETs with 5 nm channel lengths using nanosheets in a "gate all around" configuration<sup>3</sup>. Yet we could also continue downscaling by simply replacing silicon with a different semiconductor that possesses similar properties, but not does not exhibit DIBL at sub-10

nm channel lengths. Thus, around the dawn of the new millennium, the search began for an alternative.

**Figure 1.1**: Schematic of a basic 3-terminal MOSFT. This device is '*n*-type', meaning most charge carriers are electrons, rather than holes. *n*-type MOSFETs will be the focus of this work, although the logic is ever the same for *p*-type.

The 2004 discovery of graphene was a seminal moment in this search. Graphene is a monolayer of graphite; an atomically thin sheet of carbon bonded in a hexagonal lattice. Graphene has an extremely high theoretical mobility of ~ 10<sup>4</sup> cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, is chemically and thermally stable, and is mechanically strong enough for applications in flexible electronics<sup>4</sup>. The intraplanar bonds in graphene are covalent, while the interplanar bonds are supplied by a much weaker Van Der Waals (VDW) interaction. This allows for the peeling of graphene layers from graphite using a scotch-tape-based exfoliation technique, and the fabrication of graphene-based heterostructures and devices via a simple dry pick-up and transfer<sup>5</sup>. However, graphene is a semi-metal; its valence and conduction bands meet at the so-called Dirac point (where the carrier mobility can approach that of a Dirac fermion<sup>6</sup>). The absence of an intrinsic bandgap leads to

high leakage currents in graphene-based FETs and attempts to engineer a bandgap in graphene were only marginally successful.<sup>7-9</sup>

Fortunately, graphene is only one member of the large family of layered two-dimensional (2D) materials. The hundreds of such materials that have been found have a wide range of electrical properties from metals and semi-metals to insulators, topological insulators, semiconductors, and superconductors <sup>10-12</sup>. In the last five years, transition metal dichalcogenides (TMDCs) have arisen as a subset of 2D materials with a graphitic structure and widely tunable band gaps. <sup>13-15</sup> TMDCs are so-named because their elemental structures follow the general formula of MX<sub>2</sub>, where M is a *d*-block transition metal, (e.g., Mo, W, and Ti) and X is a chalcogen (e.g., S, Se, and Te). The graphitic lattice of TMDCs render the preparation of monolayers and heterostructure devices a relatively simple task <sup>16</sup>. TMDCs such as MoS<sub>2</sub> have shown moderate carrier mobilities of ~ 50 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and high transistor ON/OFF ratios near ~ 10<sup>6</sup> at room temperatures <sup>17</sup>. Monolayer MoS<sub>2</sub> FETs have also been shown to perform well at single nanometer gate lengths <sup>18</sup>.

With the discovery of group 6 TMDC monolayers, the search for a viable alternative to silicon has already come close to achieving its purpose. But there is still significant room to improve the performance of FETs based on 2D material devices. Alongside the TMDCs, phosphorene has also been shown to be a promising body for high performance devices. Phosphorene FETs show more moderate ON/OFF ratios of ~ 10<sup>4</sup>, but a mobility nearly 5 times that of MoS<sub>2</sub>, owing to a smaller and narrower bandgap and thus a small effective hole mass. The phosphorene bandgap is also more widely tunable than those of the group 6 TMDCs, varying from ~ 300 meV for bulk phosphorene and 2 eV for monolayer crystals. <sup>19</sup> Unlike graphene and TMDCs, the phosphorene lattice is orthorhombic, and the atoms are strongly puckered; that is, they are not ideally planar, but oscillate in-and-out of plane in a regular, corrugated manner. This leads to lower

symmetry in phosphorene than in TMDC layers, giving rise to exotic in-plane anisotropic electronic,<sup>20</sup> optoelectronic,<sup>21</sup> and thermal<sup>22</sup> properties. However, apropos practical device applications, TMDCs are generally preferred to phosphorene, as phosphorene is highly unstable in air.

**Figure 1.2**| Lattice Structure of **a:** graphene, **b:**  $MoS_2$  (to represent traditional 1T and 2H TMDCs), **c:** BP, and **d:**  $PdSe_2$ . The graphene and BP crystals are side viewed to show the shapes of their respective unit cells. Note that atoms in graphene and  $MoS_2$  lattices are confined to a single plane, while those of BP and  $PdSe_2$  are in and out-ofplane but are still within the limit of a 2D system. This is an illustration of 'puckering'. Originally appeared in the Materials Project. 106

Thus, we desire a 2D material which possesses the high mobility and highly tunable bandgap of phosphorene, high ON/OFF ratio of TMDCs, but is also highly stable. In the last four years, 'noble' TMDCs such as palladium di-selenide (PdSe<sub>2</sub>) and platinum di-selenide emerged as a class of candidates<sup>23-25</sup>. The noble TMDCs also follow the MX<sub>2</sub> formula, only now M is a noble

metal (e.g., Pd or Pt) bonded to the usual chalcogens. The lattice structures of MoS<sub>2</sub>, phosphorene, and PdSe<sub>2</sub> are shown in **figure 1.2**.

Both PtSe<sub>2</sub> and PdSe<sub>2</sub> are stable in air and have high carrier mobilities, but the PdSe<sub>2</sub> band structure affords a slightly larger ON/OFF ratio<sup>26</sup>, so we shall henceforth focus on the latter. The PdSe<sub>2</sub> lattice consists of strongly puckered pentagons, quite unique among 2D materials. Its bandgap has a similar degree of tunability as that of phosphorene, varying from 300 meV for bulk to 1.3 eV for monolayer crystals. Bulk PdSe<sub>2</sub> FETs have shown a carrier mobility of ~158 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, and few-layer FETs have shown ON/OFF ratios as high as 10<sup>6[27]</sup>. Yet, a PdSe<sub>2</sub>-based FET which simultaneously shows high mobility and ON/OFF ratio has yet to be demonstrated. In this work, we will elucidate a mechanism to overcome current performance limitations on few-layer PdSe<sub>2</sub> FETs and study the intrinsic transport properties of this novel 2D material.

#### 1.2 The PdSe<sub>2</sub> Lattice and Energy Band Structure

Layered PdSe<sub>2</sub> crystallizes in the space group pbca with an orthorhombic unit cell of

$$\vec{a} = 5.75 \text{ Å (4)}, \vec{b} = 5.87 \text{ Å (4)}, \vec{c} = 7.70 \text{ Å (3)}$$

and  $V = 259.43 \text{ (5)}^{28}$  (1.2)

As can be seen from figure 1.2, the chalcogen atoms in  $MoS_2$  (and the other group 6 TMDCs) layers lie along a straight line. But because of strong puckering, the chalcogen atoms in  $PdSe_2$  layers lie periodically above and below the ab plane. The vertical puckering distance is  $\sim 1.6 \text{ Å}$ . An overhead view of the  $PdSe_2$  lattice is shown in **figure 1.3**. It can be seen from this that a single Pd atom is coordinated with four Se atoms in the same layer, compared with six chalcogens coordinated with the transition metal in  $MoS_2$ . In other words,  $PdSe_2$  has a much larger crystal field than the group 6 TMDCs. This could mean a more disordered electronic field as well.<sup>29</sup>

Figure 1.3 Overhead view of the PdSe<sub>2</sub> lattice. Originally appeared in the Materials Project. 106

Due to the atomic scale thickness of 2D materials, intrinsic properties such as band structure and lattice vibrations are highly sensitive to the preparation method of growing the bulk crystal. The same material grown by slightly different methods can produce different layer sizes, thicknesses, doping, defects, vacancies, etc<sup>30</sup>.

The intensity, line shapes, peak positions, and full widths at half maxima of the Raman peaks of 2D materials all contain useful information to characterize physical and chemical properties such as electronic states and electron-phonon coupling<sup>31</sup>. This combined with the fact that device fabrication can be carried out using the same flakes as those sampled for Raman peaks makes Raman spectroscopy a powerful characterization method. 2D materials exhibit Raman peaks due to both intralayer and interlayer modes. The composition and structural phase can be deduced from the intralayer modes. Much can be learned about the interlayer coupling by treating the layers as wholes and considering the layer-layer vibration between them in the socalled linear-chain model.

Chi et. al reported peaks at 143, 205, 221, and 255  $cm^{-1}$  in the first-order Raman spectrum of few-layer PdSe<sub>2</sub><sup>32</sup>, originating from intralayer vibrations of the crystal lattice, namely  $A_g^1$ ,  $A_g^2$ ,  $B_{1g}$ , and  $A_g^3$ . They then used the same flakes to fabricate PdSe<sub>2</sub>-based phototransistors. Defining

the photoresponsivity as the photoresponse current generated per unit power of incident light on a specified area,

$$R = \frac{I_{ph}}{PA_s} \tag{1.3}$$

Bulk ( $\sim$  8 nm thick) PdSe<sub>2</sub> phototransistors showed R = 500  $\mu$ A/W, which increased to a 5.35 A/W in devices based on few-layer ( $\sim$  3.8 nm thick) crystals. The 6 order of magnitude increase in the photoresponse current was attributed to the large degree of tunability of the PdSe<sub>2</sub> bandgap, specifically tuning to a stronger valley convergence in the conduction band in fewlayer PdSe<sub>2</sub>. However, Javey<sup>33</sup> (who also reported PdSe<sub>2</sub> phototransistors) found that the intensity of first-order Raman peaks also increases with decreasing thickness. The locations of their Raman peaks were consistent with those found by Chi, although there is some disparity in the physical explanations for the peaks.

Liu identified the location of the first mode as  $A_g^1 - B_g^1$ . The smaller two peaks that constitute the second mode are defined as those at  $A_g^2$ , and  $B_g^2$ , respectively. These first three modes are believed to be due to vibration of the Se atoms. The fourth and strongest mode is taken to be a convolution of two modes at  $A_g^3$ , and  $B_g^3$ , and believed to be due to the relative motion between the Pd and Se atoms.

Liu further found some peaks in the spectrum of few-layer  $PdSe_2$  that were absent in bulk which were predicted by ab initio calculations. As the thickness tunes from bulk to few-layer, the space group changes from Pbca to  $Pca2_1$ , resulting in additional peaks.

Unlike the Raman spectra, there is not much experimental data available to elucidate the energy band structure of PdSe<sub>2</sub> layers. Photoluminescence (PL) measurements would normally be performed to accomplish this. The PL spectrum of PdSe<sub>2</sub> (and PdS<sub>2</sub>) quantum dots was investigated<sup>33</sup>, but this is a 1D phase of the material. There would likely be more emissions in the

spectrum of 2D PdSe<sub>2</sub> due to the additional degrees of freedom. However, Singh did perform calculations of the density of states (DOS) and energy band structure of layered PdSe<sub>2</sub> using the linearized augmented plane wave (LAPW) method in the WEIN2K code<sup>34</sup>.

The LAPW is one of the most accurate methods for calculating the electronic structures of crystalline solids. Like most methods in the Density Functional Theory, it is a procedure for solving the Kohn-Sham equations for the ground state density, total energy, and Kohn-Sham eigenvalues which yield the energy band structure of electrons in a crystalline system for a specified basis set. The unit cells are divided into non-overlapping atomic spheres and centered at their lattice sites and interstitial regions. Inside the atomic spheres, the linearized radial eigenfunctions and eigenvalues can be obtained from

$$\varphi_{k_n} = \sum_{lm} [A_{lm} u_l(r, E_l) + B_{lm} \dot{u}_l(r, E_l)] Y_{lm}(\hat{r})$$

(1.4)

Where  $(r, E_l)$  is the solution of the radial Schrödinger equation corresponding to an energy,  $E_l$ ,  $l(r, E_l)$  is its derivative for the same energy value, and  $Y_{lm}(\hat{r})$  are spherical harmonics.  $(r, E_l)$  and  $u(r, E_l)$  are generally obtained via numerical integration of a radial mesh. The coefficients  $A_{lm}$  and  $B_{lm}$  are functions of  $k_n$  and are determined by requiring that the basis function inside the sphere matches that at the interstitial regions.

In the interstices, the eigenfunctions are given by a plane wave expansion,

$$\varphi_{k_n} = \frac{1}{\sqrt{\omega}} e^{ik_n r} \tag{1.5}$$

Where k is the wavevector in the first Brillouin zone and  $k_n = k + k_n$  are the reciprocal lattice vectors. The solutions to the Khon-Sham equations in each region are then expanded in a combined basis set according to the linear variation method,

$$\psi_{k_n} = \sum_n c_n \varphi_{k_n} \tag{1.6}$$

And the coefficients  $c_n$  are determined using the Rayleigh-Ritz variational principle. Cutoff parameters  $R_{min}K_{max}$  corresponding to the smallest atomic radius and the magnitude of the largest wave vector are typically introduced to ensure convergence. Singh first performed the LAPW calculations for the experimental bulk structure, using the unit cell in Equation 1.2, atomic radii of R = 2.5 Bohr for Pd and 2.1 Bohr for Se and cutoff parameters  $R_{min}K_{max} = 7$ .

After bulk structure calculations, the modified Beck-Johnson potential (mBJ) was used to relax the internal coordinates for both bulk and monolayer. Spin-orbit coupling was considered in all calculations.

**Figure 1.4** shows the calculated DOS of bulk PdSe<sub>2</sub>. The Fermi energy is set to zero. As was previously noted, both the bulk and the monolayer phases exhibit well defined band gaps of 300 meV for bulk and 1.43 eV for monolayer. Interestingly, the binding energy of 190 meV/atom is well above that of graphite<sup>35</sup> (~ 35 meV/atom), BP<sup>36</sup> (~ 40 meV/atom), and MoS<sub>2</sub><sup>37</sup> (130 meV/atom) which is a testament to the strong interaction between layers that arises due to puckering. This also suggests it may be difficult to prepare monolayer PdSe<sub>2</sub> via mechanical exfoliation, a challenge we will revisit in the "Fabrication Methods".

It is clear from the DOS that in both monolayer and bulk crystals most states at the band edges are contributions from the d-orbitals of the Pd atoms and the p-orbitals of Se. There is also some visible hybridization of the 4d states of Pd and the 4p states of Se that arises due to the intraplanar (covalent) bonds.

**Figure 1.4** also shows the calculated band structure of the bulk  $PdSe_2$  phase along high symmetry k points. The band gap is indirect. Incidentally, the transition to a direct band gap in the monolayer phase that occurs in many group 6 TMDs does not occur in  $PdSe_2$ . Special attention should be paid to the concavity of the valence and conduction bands near the Γ point.

The valence band is extremely flat, while the conduction band is quite narrow. Although PdSe<sub>2</sub> FETs are ambipolar (as we shall see in the coming sections) the band structure behooves us to focus on demonstrating high performance *n*-type devices. The large effective mass would be a limiting factor on the hole mobility.

**Figure 1.4** | Calculated DOS and energy band structure for bulk  $PdSe_2$ . Originally appeared in the Materials Project.  $^{107}$

#### 1.3 Performance Limitations on PdSe<sub>2</sub> FETs

As is the case with all 2D semiconductors, the main performance limitation in PdSe<sub>2</sub>based MOSFETs is a substantial Schottky barrier which tends to form at the drain source contacts<sup>38</sup>. The barrier is a result of an energy mismatch between the electron affinity of the PdSe<sub>2</sub> channel,  $\chi_s$ , and the work-functions of conventionally used metal electrodes,  $\Phi_M$ . In most cases,  $\Phi_M > \chi_s$ .

At equilibrium, electrons flow from the semiconductor to the metal and leave a positive space charge region in the semiconductor. Under forward bias, electrons easily flow from semiconductor to metal. But under reverse bias, the flow of electrons from the metal is limited to only those with enough energy to pass over the built-in potential barrier. For this reason, Schottky-

type contacts are sometimes also referred to as rectifying contacts because the current can be large or small depending on the direction of an applied bias. Ideally, the Schottky Barrier Height (SBH),  $\Phi_B$ , can be predicted by the Schottky-Mott rule,

$$\Phi_B = \Phi_M - \chi_S \tag{1.7}$$

However, experimental reports of Schottky Barrier heights are usually far greater than those predicted by the rule, even in the case of the Si and GaAs FETs that are used in digital electronics today<sup>39</sup>. Instead, the Fermi level tends to pin to a fixed point in the semiconductor bandgap and this Fermi Level Pinning (FLP) effect tends to be dominant regardless of the choice of metal workfunction<sup>40-42</sup>.

The sources of the Fermi Level Pinning (FLP) effect in 2D semiconductor devices are many. Firstly, the Schottky-Mott model presumes an atomically sharp discontinuity between electrode and channel, which is rarely the case due to chemical bonds that take place spontaneously and modify the original energy levels. Secondly the decaying metallic wavefunction can penetrate the channel region by several nanometers, leading to metal-induced gap states. Third and most determinately, the VDW assembly and metallization processes introduce chemical disorder and defect states. This is especially true when the metal contacts are formed via aggressive processes like thermal evaporation, which deposits metal into lithographs via cluster bombardment and heating of the contact region. Such a process can easily damage the semiconductor lattice near the interface<sup>44</sup>.

There hasn't been much investigation into the sensitivity of  $PdSe_2$  FETs to metal work function, so it is difficult to postulate exactly where the Fermi level pins. However, the slight oscillation of  $PdSe_2$  atoms in and out of the crystal plane implies the d-orbitals of the Pd atoms and the p-orbitals of Se which lie along the band edges could have an even stronger interaction

with metal electrodes than orbitals lying along the band edges of the group 6 TMDCs. This may be reflected in the reported SBH of  $\sim 250$  meV for PdSe<sub>2</sub> FETs formed using Ti electrodes<sup>45</sup>. The contact resistance of 2 M $\Omega$ µm is also much larger than that reported for any group 6 TMDC.

**Figure 1.5** shows an energy band diagram of a metal source contact in a PdSe<sub>2</sub> MOSFET at the Schottky-Mott limit.

Figure 1.5 | Metal source contact of a PdSe<sub>2</sub> FET at the Schottky-Mott limit

#### 1.3.1: Transfer Characteristics:

Generally, a MOSFET is said to be 'high performing' based on two plots: the transfer characteristics (current as a function of gate voltage,  $V_g$ , at a specified drain-source bias,  $V_{ds}$ ) and the output characteristics (current as a function of the drain-source bias,  $V_{ds}$ , at a specified  $V_g$ ). Usually, the transfer characteristics are plotted for a series of drain-source biases and the output characteristics are plotted for a series of gate voltages. Every other figure of merit that we will discuss (carrier mobility, SBH, etc.) is extracted from these two curves, either at room temperature or from their temperature dependence. We will flesh this out more fully in the "Results" section.

In the presence of a large Schottky barrier, the transfer characteristics will generally show a 'bowing' region at low gate voltages (specifically where  $V_g \cong V_{th}$ ). In this region, the current is

small and primarily due to thermally assisted tunneling. There isn't enough energy for thermionic emission, and the tunneling resistance is high due to large depletion layer widths, which can be on the order of nanometers<sup>46</sup>. At higher gate voltages, most carriers can emit over the barrier, and the 'bowing' region gives way to a linear current-voltage relationship.

The 2D conductivity and carrier mobility are both extracted from the transfer characteristics. In an ideal MOSFET, the carrier mobility is limited only by the quantum mechanical scattering of charge carries by acoustic phonons, which emanate from the crystal lattice of the channel. This is conventionally referred to as the 'phonon-limited mobility' or 'channel limited mobility'. As the device is cooled to cryogenic temperatures, thermal excitations of these acoustic phonons are suppressed- hence the mobility increases, usually by a factor of two or three. Due to lattice defects and other unavoidable traps, it is nearly impossible for any material to reach its theoretical mobility. PdSe<sub>2</sub> FETs have shown a cryogenic mobility as high as 520 cm<sup>2</sup>/Vs<sup>47</sup>, although its theoretical value is believed to be 9,800 cm<sup>2</sup>/Vs.

As we will see, there are different ways of discussing mobility, but they are all extracted from the transfer characteristics. A Schottky barrier can have two possible effects on the temperature dependence. It *may* cause the mobility to appear to decrease, an artifact which results from barrier heights that are so large they cannot be overcome even at high gate voltages. But even if the mobility appears to increase upon cooling, there will be a substantial positive shift in the threshold voltage (causing the 'bowing' region to grow larger). This latter effect is often neglected in reports of high performance 2D MOSFETs, even though its presence is a clear indication that the device is barrier limited.

To see how, let us briefly dig into the thermionic emission and diffusion theory of Bethe and the diffusion theory of Schottky $^{98}$ . The current voltage characteristics of an n or p-type (in the

latter case, the barrier is modeled as a series of *forward* biased Schottky diodes) FET are described by the Shockley Diode Equation:

$$I = A^{**}T^{2}e^{\frac{-q\phi_{B}}{K_{B}T}} \left[ e^{\frac{-qV}{K_{B}T}} - 1 \right]$$

(1.8)

Where T is the temperature and  $A^{**}$  is the effective Richardson constant. To first approximation, the probability of electrons emitting over the potential maximum is Maxwell distributed over the mean free path,  $\lambda$ ,

$$f_p = e^{-x_m/\lambda} \tag{1.9}$$

But the electronic energy distribution tends to be distorted from this Maxwellian form by quantum mechanical tunneling of some electrons through the barrier as well as reflection of other electrons off it. The impacts of these quantum effects are accounted for in the reduced effective Richardson constant,  $A^{**}$ , which reduces up to 50% from  $A^*$  according to the relation

$$A^{**} = \frac{f_p f_Q A^*}{1 + \left(\frac{f_p f_Q v_R}{v_D}\right)} \tag{1.10}$$

The ratio of the total current flow,  $f_Q$ , in which these effects are considered to current flow  $f_p$  in which they are neglected is strongly dependent on the applied gate voltage and the position of the quasi-Fermi level relative to the SBH.

As was previously noted, at room temperature, there is enough thermal energy for a substantial amount of charge carriers to thermionically emit over the barrier, while a smaller portion can tunnel through, and the current will be predominately given by **Equation 1.8**. But as cryogenic temperatures are approached that thermal energy can no longer be supplied, hence the current will be due entirely to tunneling. The tunneling current is given by

$$J = ev_R n\Theta \tag{1.11}$$

Where e is the electron charge,  $v_R$  is the Richardson velocity, n is the carrier density, and  $\Theta$  is the tunneling probability.  $v_R$  has the form,

$$v_R = \sqrt{\frac{K_B T}{2\pi m^*}} \tag{1.12}$$

The average velocity with which electrons approach the interfaces of the barrier. The tunneling probability is derived from the Time Independent Schrodinger Equation, treating the Schottky barrier as a triangular potential in the WKB approximation to obtain

$$\Theta = exp\left(-\frac{4}{3}\left(\frac{\sqrt{2qm^*}}{\hbar}\right)\frac{\phi_B^{3/2}}{\varepsilon}\right)$$

(1.13)

Where  $\mathcal{E}$  is the applied electric field. The fact that  $\Theta \propto e^{-(\phi_B)^{\frac{3}{2}}/\mathcal{E}}$  indicates that the tunneling current can be severely limited by a large contact barrier, and successively greater voltages must be applied to turn on a FET at cryogenic temperatures. Thus, we have explained why the positive shift in the threshold voltage is evidence that a FETs is contact limited.

Now that we understand the reason for this phenomenon, how do we quantify it? One way is to calculate the subthreshold swing, SS. The SS is the inverse of the subthreshold slope; the amount of gate voltage needed to produce one decade of drain current.

$$SS = \frac{dV_{GS}}{dlog(I_D)} \tag{1.14}$$

The drain current behaves similarly to a forward biased diode in the subthreshold region, so the SS can also be written as

$$SS = \frac{dV_{GS}}{dlog(I_D)} = mu_T \ln(10)$$

(1.15)

Where  $u_T$  is the thermal voltage and m is the diode ideality factor<sup>48</sup>. In most FET designs at room temperature, the diffusion of charge carriers sets the minimum possible SS- known as the thermionic limit- to 60 mV/dec. At this limit, the ideality factor is close to unity, and the thermal

voltage is  $\approx$  30 mV. Yet, sub-thermionic field effect transistors have been demonstrated via band-to-band tunneling<sup>49</sup>.

Obviously, a large 'bowing' region implies a large SS. The transfer characteristics will not rise 'sharply' upon reaching the threshold voltage. Instead, the slope of the current vs gate voltage (not to be confused with the subthreshold slope, since contact effects can be seen well after turn-on) will be smaller than ideal, and vary by region, according to whether the current is due to thermally assisted tunneling or thermionic emission. Cooling to cryogenic temperatures will only exacerbate the problem.

If the drain/source contacts are Ohmic, the transfer characteristics will rise with near infinite slope and the SS will be close to the thermionic limit. The fact that we cannot reduce the SS all the way to zero does mean that there is always going to be some 'bowing' in the transfer characteristics and therefore the Schottky barrier will always have some non-zero height. But so long as the SBH is smaller than the thermal energy of charge carriers, (25 meV at room temperature) its effects can be said to negligible.

#### 1.3.2: Output Characteristics:

The effects of the barrier on the output characteristics are often much less noticeable.

Ohmic contacts will simply show output characteristics that obey Ohm's law; so long as the gate voltage is above threshold, the current will rise linearly with the applied bias, until the bias is large enough to cause the channel resistance to decrease, at which point the current saturates. The total resistance can be readily obtained from the inverse slope of the I-V curves in the linear region.

A substantial barrier will lead to non-linear output characteristics, especially at lower applied biases and gate voltages. Sometimes, the non-linearity is symmetric, suggesting that the SBH is roughly the same at both the drain/source contacts. Yet, most of the time there is some asymmetry. As we elucidated earlier, there are many factors that can contribute to Fermi level

pinning and each contact can suffer from a different combination of these factors. To reiterate further, a large enough gate voltage will enable thermionic emission over the barrier. I-V curves can become linear in this gate voltage range.

Sometimes, at higher temperatures the output characteristics can show a deceiving linearity that belies the presence of a contact barrier. This is generally not an intrinsic effect. It has been shown that annealing can create hybridized contacts to the channel and modify the band alignment<sup>50</sup>, and this is just one possible reason for such deceiving linearity. Therefore the output and transfer characteristics have to be considered together in order to make any reliable proclamations on the nature of the contacts.

Javey fabricated a 6.8 nm thick PdSe<sub>2</sub> FET fabricated on a commercial SiO<sub>2</sub>/Si substrate<sup>51</sup>. The room temperature electron mobility was decently high at  $\sim 130~\text{cm}^2/\text{Vs}$ , with a moderate ON current of  $\sim 10~\mu\text{A}/\mu\text{m}$ . The transfer and output characteristics were nearly linear at room temperature- even at lower gate voltages. Yet upon examining the temperature dependence of the transfer characteristics, we see a  $\sim 15~\text{V}$  shift in the threshold voltage as the device is cooled to 77 K. The SBH was not calculated in this work, but it is likely several times the thermal energy of charge carriers.

#### 1.4 Strategies for High Performance FETs

The tendency of large Schottky barriers to form at the interface between the semiconducting channel and metal drain/source contacts is not only a performance limitation for TMDC-based MOSFETs. Even the Si-based FETs used in commercial technologies have substantial contact barriers. The difference is that barriers in Si devices can be virtually eliminated at the contact regions using a process known as selective ion implantation<sup>52</sup>.

In this method, a high-powered plasma is generated via RF or microwave radiation to ionize donor (or acceptor) atoms under ultra-high vacuum. The vacuum suppresses collisions with

ambient gas molecules, causing the ions to form a linearized beam. The ion beam is then accelerated via electromagnetic fields and directed at a target substrate. The substrate surface is bombarded with ion energies ranging from a few hundred to a few million meV; enough to penetrate the substrate lattice and knock out atoms from their sites. Annealing is then implored to "activate" the dopant by substituting dopant ions into the vacancies.

This can have one of two cumulative effects; either a lowly doped layer will form near the silicon surface, or an interfacial dipole will form. In both cases, the silicon conduction (or valence, in the case of *p* contacts) band bends downwards relative to the Fermi level of the metal, reducing the SBH. The reduction can be controlled simply by modulating the ion dose.

Unfortunately, local doping of the contact regions via selective ion implantation is not possible for 2D materials. The technique is too destructive; the penetration depth of implanted ions is usually anywhere from 10 nm-1  $\mu$ m, which is thicker than a monolayer of any 2D material.

Thus, the search began for a different method of locally doping the contact regions in 2d TMDCs, or otherwise reducing the Schottky barrier height. One method that has drawn a lot of attention is phase engineering. Chhowalla showed that the metallic 1T phase of MoS<sub>2</sub> can be locally induced on the (typical) semiconducting 2H phase, dropping the contact resistance by an order of magnitude<sup>52</sup>. Yang performed a similar study in which the contact resistance to MoTe<sub>2</sub> was reduced via a locally induced transition of MoTe<sub>2</sub> from its hexagonal layer structure into an octahedral metallic phase. However, such transitions are usually unstable above critical temperatures, (100° C in the latter case) limiting their practical device applications.

There has also been great success in engineering low resistance Ohmic contacts via surface and substitutional doping. Javey demonstrated a high performance FET based on monolayer WSe<sub>2</sub> by chemically doping the surface of the contact regions with NO<sub>2</sub>. The channel region was

encapsulated with Pd, both to ensure local doping of the contact regions as well as to exploit the fact that Pd is a high-κ dielectric and therefore a good candidate for a top-gate with excellent electrostatics<sup>54</sup>. The same group also saw success with surface charge transfer doping of MoS<sub>2</sub> using potassium<sup>55</sup> and benzyl viologen<sup>56</sup>.

Ye had some success with surface doping of few-layer MoS<sub>2</sub> and WS<sub>2</sub> using a chlorination technique<sup>57</sup>. However, the doping was not localized in this case, but instead diffused throughout the channel region. Although Ye's devices happened to not suffer from this effect, non-localized dopants can lead to a significant amount of charge-impurity scattering, somewhat degrading the mobility compared to typically reported values.

MOSFETs based on  $MoS_2$  tend to show naturally n-type behavior, whereas  $WSe_2$  FETs tend to be more naturally p-type. As such, it is generally easier to n-dope the contacts in  $MoS_2$  FETs and p-dope  $WSe_2$  contacts to improve the device performance. However, Suh managed to show degenerate hole doping of  $MoS_2$  by substitution of Mo cations with Nb atoms<sup>57</sup>.

Effective though they may be at significantly reducing the Schottky barrier height and contact resistance, most surface doping techniques suffer from poor air or thermal stability.<sup>58</sup> It would also be challenging to scale them up for commercial applications. Substitutional doping presented a great alternative in this sense. The Nb atoms are secured via covalent bonding during the growth process, and do not degrade the chemical or thermal stability of MoS<sub>2</sub> in any way.

In 2016, our group (lead by Chuang) devised a completely dry method of degenerately doping the contact region of WSe<sub>2</sub> FETs that exploits the pristine nature of the VDW bonds between 2D materials<sup>59</sup>. They transferred two distinct pieces of Nb-doped WSe<sub>2</sub> onto a WSe<sub>2</sub> channel via VDW assembly. This was advantageous over attempting to form locally doped contact regions in the same crystal due to the difficulty associated with creating a doping profile that is sharply demarcated from the channel region. Each contact was ~20 nm thick to ensure degenerate

doping, and the channel region was passivated with ~10 nm h-BN to ensure a welldefined channel and locally doped contacts.

The result was WSe<sub>2</sub> FETs which showed excellent behavior at room temperature and a temperature dependence (the mobility reached ~10<sup>3</sup> at 5 K) which facilitated the study of several intrinsic properties of WSe<sub>2</sub> due to the absence of any noticeable contact effects. The mechanism of this '2D/2D contact' strategy is remarkably like selective ion implantation in Si devices. A larger carrier density in the degenerately doped contact as compared to the intrinsically doped channel leads to a work function difference between the two, and therefore a band offset. The offset is generally small owing to the weak interaction between VDW materials and can thus be readily tuned by a back-gate voltage. An energy band diagram explaining this phenomenon is shown in **Figure 1.6**.

**Figure 1.6** | Band diagram explaining the operation of a  $WSe_2$  FET with degenerately *p*-doped 2D/2D contacts. Originally appeared in ref. 59.

Clearly, 2D/2D contacts are the superior strategy to try out on demonstrating low resistance Ohmic contacts to PdSe<sub>2</sub>. However, if we take another look at the (calculated) PdSe<sub>2</sub> band structure in **figure 1.4** as we said before, along the  $\Gamma$  point, the valence band is quite wide, leading to a low

hole mobility- a problem that cannot be solved by doping. In principle, this would cause us to look for a substitutional n dopant like Re, which has also been shown to enhance the carrier concentration in WSe<sub>2</sub><sup>60</sup>. However, our group also demonstrated that while 0.5% Nb doped WSe<sub>2</sub> showed degenerate doping and a nearly temperature-independent carrier density, 0.5% Re doped WSe<sub>2</sub> showed- in contrast- a thermally activated behavior, owing to the trapping of electrons in localized states below the mobility edge<sup>61</sup>. It would seem PdSe<sub>2</sub> differs too much from the group VI TMDs for 2D/2D contacts to result in high performance FETs.

So, if we've ruled out the most effective strategies in both industry and research for engineering low resistance contacts in FET, how will we achieve the high performance PdSe<sub>2</sub> FETs we desire? In this work, we will discuss the results from another strategy developed by our group that is every bit as stable and scalable as 2D/2D contacts, but suitable for improving the the performance of ultrathin PdSe<sub>2</sub> FETs: using TMDCs as semiconducting *interlayers*.

As is the case with all things in the field, the use of 2D materials as a contact interlayer began with graphene. When Park inserted it at the interface of Ti and bulk  $Si^{62}$ , the contact resistivity, , was reduced to  $1.4~n\Omega~cm^2$ , which is very close to the theoretical value of  $1.3~n\Omega~cm^2$ . Interestingly, that study showed the exact same reduction occurs when monolayer h-BN is inserted as the interlayer, despite the fact that h-BN is an insulator. Clearly, something happens to modify the band alignment when a monolayer of a 2D material is inserted at the metal/semiconductor interface.

Our first guess may be that the interlayers de-couple the metal/semiconductor interface to de-pin the Fermi level and eliminate the effects of MIGS. Insulating thin films such as SiN, TiO<sub>2</sub>, and ZnO have been inserted at the Si/metal interface before, and all served to reduce the  $\rho_c$ . They had to be thin enough (< 1 nm) to avoid incurring a large tunneling resistance, which explains

why monolayers of graphene and h-BN were used. But Park's calculation of the pinning factor complicated the picture. The pinning factor is one if the FL is de-pinned (Schottky limit) and zero if it is fully pinned (Bardeen limit). Park showed that the pinning factor between conventionally used metal contacts, graphene interlayers, and monolayer h-BN interlayers are all near the Bardeen limit.

The Fermi level is still quite pinned, but as Park elucidated, the metal/2D interlayer contact acts as a fully metalized contact with a reduced metal work function and pinning point near the conduction band edge of the channel. Furthermore, a dipole forms at the interface of the metal and 2D interlayer, buttressing the barrier height reduction. Park stipulates that the surface roughness of Si and the presence of dangling bonds may be the reason we still observe strong FLP. It stands to reason that the pinning factor would approach the Schottky limit if a 2D semiconductor was used as an interlayer to contact a 2D TMDC channel.

Pop et al employed this method to improve the performance of MoTe<sub>2</sub>-based FETs<sup>77</sup>. They chose to use Sc contacts to MoTe<sub>2</sub> due to the low Sc work function but had to insert an hBN monolayer to mitigate performance losses since Sc is also highly reactive. The result was a nearly threefold reduction in the barrier height compared to that of conventionally used metals. But the reduction was not a complete one; the measured barriers were consistently in the 80-100 meV range, which is comparable to the barrier height of few-layer MoS<sub>2</sub> FETs with Ti/Au contacts. This can be explained by the *partial* de-pinning of the Fermi level. With the insertion of an h-BN interlayer, their MoTe<sub>2</sub> devices went from showing a significant amount of reverse biased leakage (hole) current to completely *n*-type behavior. However, the substantial electron barrier suggests the de-pinning effect is not complete. They stipulate this is due to local metaltelluride compounds still playing some role in the transport. MoTe<sub>2</sub> is not very chemically stable itself. Perhaps with

more stable metals and channel materials we can use an h-BN monolayer to realize a high performance device TMDC-based FET with a pinning factor that is close to the Schottky limit.

Our group (lead by Andrews and myself) accomplished this <sup>79</sup>. We used monolayer h-BN as an interlayer in air-stable MoS<sub>2</sub>-based FETs with Ti/Au contacts. The result was again a significant reduction in the barrier height to around ~ 50 meV. However, we found that large bandgap of h-BN leads to a series tunneling resistance, even if the Fermi level is de-pinned. Hence, we decided to move in a different direction altogether. We used WSe<sub>2</sub> and MoSe<sub>2</sub> as interlayers to an MoS<sub>2</sub> channel. We found that the barrier height of devices with WSe<sub>2</sub> interlayer was comparable to that when h-BN is used, but the lowest height was observed using MoSe<sub>2</sub>. Our results showed that we can not only use 2D semimetals and insulators as interlayers, but 2D semiconductors as well, with the best device performance yielded by the latter.

The mechanism of 2D semiconductor interlayers differs completely from that of 2D semimetals or insulators. Our goal is no longer to de-pin the Fermi level; the pinning factor of our MoS<sub>2</sub> FETs is nearly zero. Rather, we seek to take advantage of favorable energy band alignment across the metal/TMDC interlayer/TMDC channel interface to engineer a small effective contact barrier. On the one hand, the Fermi level of the metal will pin close to the conduction band edge of the interlayer. One the other hand, there will be an offset between the band edges of the channel and interlayer, which will be small since both materials are group 6

TMDCs. Thus, the effective barrier height will follow the relation,

$$\Phi_{B_r} = (E_F - \chi_{IL}) - (\chi_{channel} - \chi_{IL}) = E_F - \chi_{channel}$$

(1.16)

Where E<sub>F</sub> is the energy at which FLP occurs at the metal/TMDC interlayer interface.

In the case of MoSe<sub>2</sub> interlayers in MoS<sub>2</sub> FETs, the band offset between the two materials is relatively small- hence the barrier height follows suit. This was further confirmed by the fact

that the height was slightly larger in WSe<sub>2</sub> interlayer FETs than in MoSe<sub>2</sub> interlayer FETs, since the band offset between WSe<sub>2</sub> and MoS<sub>2</sub> is slightly larger than that between MoS<sub>2</sub> and MoSe<sub>2</sub>. The barrier height was also similar using lightly *n*-doped Re<sub>0.005</sub>W<sub>0.995</sub>Se<sub>2</sub> as an interlayer, suggesting the reduction is principally due to the small band offset; interfacial dipoles do not play a major role. A summary of the calculated SBH of MoS<sub>2</sub> FETs with 2D material interlayers is shown in **Figure 1.7a**.

Figure 1.7d shows a proposed energy band diagram for high performance PdSe<sub>2</sub> devices using this contact strategy. We do not know as much about the experimental band structure of PdSe<sub>2</sub>, (particularly the position of the conduction band edge) hence it is harder to predict exactly which of the group 6 TMDCs will work best as a contact interlayer to a PdSe<sub>2</sub> channel. The small band gap of PdSe<sub>2</sub> could lead to a large band offset regardless of which material we select. But it's also possible we will find that the small bandgap facilitates a large ON current due to an ultralow tunneling resistance.

**Figure 1.7**| **a.** SBH of MoS<sub>2</sub> FETs with 2D material interlayers as a function of interlayer thickness. **b-c.** Energy band diagrams of an MoS<sub>2</sub> FETs with and without MoSe<sub>2</sub> as a semiconductor interlayer, showing the mechanism by which the SBH is reduced when MoSe<sub>2</sub> is reduced at the metal/semiconductor interface. (**a-c** originally appeared in ref 64) **d.** Proposed energy band diagram of PdSe<sub>2</sub> FETs with semiconductor interlayer. The interlayer can be any (stable) group 6 or group 10 TMDC.

#### **CHAPTER 2: DEVICE FABRICATION AND CHARACTERIZATION**

#### 2.1 Mechanical Exfoliation

Most groups that study devices based on 2D materials find it easier to use chemical vapor deposition (CVD) to grow ultrathin samples. But CVD is an expensive and time consuming process, and the defects<sup>65,66</sup> and grain boundaries<sup>67</sup> that tend to form during growth can introduce challenges in subsequent steps of device fabrication. Hence, as we mentioned in the introduction, mechanical exfoliation from a bulk CVD grown crystal is the ideal method to prepare few-layer, bilayer, and monolayer TMDCs as well as graphene and h-BN.

Our bulk PdSe<sub>2</sub> crystals were grown by Mandrus' group at the University of Tennessee. The synthesis was performed via chemical vapor transport with iodine as the agent.

Polycrystalline  $PdSe_2$  was made from a mixture of Pd, (Alfa-Aesar, 99.999%) and Se (AlfaAesar, 99.999%) powders, and then used as a starting material to grow single crystals, resulting in a ~ 2.5 mm<sup>3</sup> flake. The flake was confirmed to be phase pure via X ray diffraction. Bulk crystals of group

6 TMDCs, graphite, and h-BN were all purchased from various nanotechnology companies (HQ Graphene, SPI Supplies, and 2D Semiconductor Supplies, respectively).

To exfoliate, a smaller flake of the bulk material is placed on a piece of scotch tape. A top scotch tape is then pressed onto the flake and bottom scotch tape, and then peeled back. The (weak) interlayer interaction implies the top scotch tape can easily peel off a much thinner layer from the bulk crystal. The process is then repeated until both tapes hold a checkerboard of exfoliated crystals with randomly distributed thicknesses, as shown in **figure 2.1c**.

In practice, obtaining ultrathin layers by mechanical exfoliation requires 3-5 pieces of top scotch tape, wasting both tape and crystals. Huang developed a repeatable method for exfoliating high-quality, large area samples of graphene and the bismuth, strontium, calcium, copper oxide superconductor  $Bi_2Sr_2CaCu_2O_2^{68}$ . In the conventional exfoliation method, substrates comprised of  $SiO_2$  on heavily doped Si are sonicated in acetone and isopropyl alcohol (DI water and piranha solution are also used), and then exposed to oxygen plasma to destroy any ambient adsorbates. Immediately after the plasma clean, the substrate is placed face down on the top scotch tape. The tape is then slowly removed and some percentage of the samples on tape are transferred to the substrate. The thicknesses of transferred crystals can be readily determined by their optical contrast; a bright white color indicates a thickness > 20 nm. Monolayers and bilayers are a translucent pink.