# High Temperature Electronics Design for Aero Engine Controls and Health Monitoring

Lucian Stoica, Steve Riches and Colin Johnston

# High Temperature Electronics Design for Aero Engine Controls and Health Monitoring

#### RIVER PUBLISHERS SERIES IN CIRCUITS AND SYSTEMS

Series Editors

#### MASSIMO ALIOTO

#### KOFI MAKINWA

National University of Singapore Singapore Delft University of Technology The Netherlands

#### DENNIS SYLVESTER

University of Michigan USA

The "River Publishers Series in Circuits & Systems" is a series of comprehensive academic and professional books which focus on theory and applications of Circuit and Systems. This includes analog and digital integrated circuits, memory technologies, system-on-chip and processor design. The series also includes books on electronic design automation and design methodology, as well as computer aided design tools.

Books published in the series include research monographs, edited volumes, handbooks and textbooks. The books provide professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics covered in the series include, but are by no means restricted to the following:

- Analog Integrated Circuits

- Digital Integrated Circuits

- Data Converters

- Processor Architecures

- System-on-Chip

- Memory Design

- Electronic Design Automation

For a list of other books in this series, visit www.riverpublishers.com

# High Temperature Electronics Design for Aero Engine Controls and Health Monitoring

#### Lucian Stoica

GE Global Research Germany

#### **Steve Riches**

Tribus-D Ltd UK

#### **Colin Johnston**

University of Oxford UK

#### **Published 2016 by River Publishers**

River Publishers

Alsbjergvej 10, 9260 Gistrup, Denmark

www.riverpublishers.com

#### **Distributed exclusively by Routledge**

4 Park Square, Milton Park, Abingdon, Oxon OX14 4RN 605 Third Avenue, New York, NY 10017, USA

#### **Open Access**

This book is distributed under the terms of the Creative Commons Attribution-Non-Commercial 4.0 International License, CC-BY-NC 4.0) (http://creativecommons.org/ licenses/by/4.0/), which permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, a link is provided to the Creative Commons license and any changes made are indicated. The images or other third party material in this book are included in the work's Creative Commons license, unless indicated otherwise in the credit line; if such material is not included in the work's Creative Commons license and the respective action is not permitted by statutory regulation, users will need to obtain permission from the license holder to duplicate, adapt, or reproduce the material.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

High Temperature Electronics Design for Aero Engine Controls and Health Monitoring / by Lucian Stoica, Steve Riches, Colin Johnston.

© The Editor(s) (if applicable) and The Author(s) 2016. This book is published open access.

Routledge is an imprint of the Taylor & Francis Group, an informa business

ISBN 978-87-93379-25-1 (print)

While every effort is made to provide dependable information, the publisher, authors, and editors cannot be held responsible for any errors or omissions.

## **Contents**

| Pr | reface                                                                                                                                                                                                                         | xi                    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Ac | cknowledgments                                                                                                                                                                                                                 | xiii                  |

| Li | st of Figures                                                                                                                                                                                                                  | xv                    |

| Li | st of Tables                                                                                                                                                                                                                   | xxi                   |

| Li | st of Abbreviations                                                                                                                                                                                                            | xxiii                 |

|    | PART I: High Temperature Electronics Background Lucian Stoica, Steve Riches, Colin Johnston                                                                                                                                    |                       |

| 1  | High Temperature Electronics for Aviation Applications  1.1 Value Story                                                                                                                                                        | 3<br>3<br>4<br>4<br>6 |

| 2  | High Temperature Integrated Technologies 2.1 Introduction                                                                                                                                                                      | <b>11</b><br>11       |

|    | PART II: Development of Multi-Sensor Data Acquisition System Lucian Stoica, Valentyn Solomko, Ozan Iskilibli, Renato Del Regno, Reece Beigh, Thorsten Baumheinrich, Steve Riches, Colin Johnston, Geoff Rickard, Paul Williams |                       |

| 3  | Outline of System  3.1 High Level Input Specification                                                                                                                                                                          | <b>19</b><br>19       |

#### vi Contents

|   | 3.3 | Defini      | tion of Prototype System                           | (   |

|---|-----|-------------|----------------------------------------------------|-----|

|   |     | 3.3.1       | HIGHTECS SOI ASIC                                  | 1   |

|   |     | 3.3.2       | HIGHTECS Hybrid Circuit                            | 13  |

|   |     | 3.3.3       | HIGHTECS Module                                    | !4  |

|   | 3.4 | Manuf       | Facture of Prototypes                              | !4  |

|   |     | 3.4.1       | HIGHTECS ASIC in PGA Package 2                     | !4  |

|   |     |             | 3.4.1.1 HIGHTECS hybrid circuit 2                  | !4  |

|   |     |             | 3.4.1.2 Assembly of Ceramic Substrate              |     |

|   |     |             | to Metal Package 2                                 | 7   |

|   |     |             | 3.4.1.3 High Temperature PCB for Resistors 2       | 9   |

|   |     |             | 3.4.1.4 HIGHTECS Module                            | 9   |

|   |     |             | GI A A A A A A A A A A A A A A A A A A A           |     |

| 4 |     |             | Characterization of HIGHTECS Signal                | . 1 |

|   |     |             | nd Building Blocks                                 |     |

|   | 4.1 | Opera 4.1.1 | tional Amplifiers                                  |     |

|   |     | 4.1.1       | 1 1                                                |     |

|   |     |             | 4.1.1.1 Schematic diagram                          |     |

|   |     |             | <b>,</b>                                           |     |

|   |     | 4.1.2       |                                                    |     |

|   |     | 4.1.2       | 1 1 1                                              |     |

|   | 4.2 |             | 1 1 1                                              |     |

|   | 4.2 |             | ap Reference Generator                             |     |

|   | 4.4 |             | letwork                                            |     |

|   | 4.4 | 4.4.1       | Top Level Schematic Diagram 4                      |     |

|   |     | 4.4.1       | Bias Network Layout                                |     |

|   |     | 4.4.3       | Reference Voltages Generator                       |     |

|   |     | 4.4.4       | Voltage to Current Converter                       |     |

|   |     | 4.4.5       | Current Mirrors                                    |     |

|   | 4.5 |             | g Multiplexer                                      |     |

|   | 1.5 | 4.5.1       | Layout of Analog Multiplexer                       |     |

|   | 4.6 |             | -Ended to Differential Converter                   |     |

|   |     | 4.6.1       | Simulation Results                                 |     |

|   |     | 4.6.2       | Layout of Single-Ended to Differential Converter 5 |     |

|   |     | 4.6.3       | Single-Ended to Differential Converter 5           |     |

|   |     | 4.6.4       | Measurement Results                                | ;4  |

|   | 4.7 |             | o — Temperature Channels                           |     |

|   |     | 4.7.1       | Temperature Channels                               | 7   |

|   |     | 4.7.2       | T1/TFo Operating Principle                         | 9   |

|   |     |                | Contents                                                                | vii |

|---|-----|----------------|-------------------------------------------------------------------------|-----|

|   |     | 4.7.3          | T1/TFo Functionality                                                    | 59  |

|   |     |                | 4.7.3.1 Voltage-gain profile                                            | 59  |

|   |     |                | 4.7.3.2 Static accuracy                                                 | 60  |

|   |     |                | 4.7.3.2.1 Static accuracy simulation for                                |     |

|   |     |                | variable chip temperature and                                           |     |

|   |     |                | constant sensor temperature                                             | 61  |

|   |     |                | 4.7.3.2.2 Static accuracy simulation for                                |     |

|   |     |                | variable chip temperature and                                           |     |

|   |     |                | variable sensor temperature                                             | 62  |

|   |     |                | 4.7.3.3 Temperature error due to quantization                           |     |

|   |     |                | error                                                                   | 62  |

|   |     |                | 4.7.3.4 Input ESD protection                                            | 62  |

|   |     |                | 4.7.3.5 Short and open circuit detection                                | 63  |

|   |     | 4.7.4          | Mirrored Bias Current for Temperature Probe                             |     |

|   |     |                | Excitation                                                              | 63  |

|   |     | 4.7.5          | T1/TFo Channels Schematic Diagrams                                      | 64  |

|   |     |                | 4.7.5.1 T1 top level connection                                         | 64  |

|   |     | 4.7.6          | T1/TFo Channels Layout                                                  | 67  |

|   | 4.8 | SG2 –          | — Strain Gauge Channel                                                  | 68  |

|   |     | 4.8.1          | Testing of HIGHTECS Module                                              | 68  |

|   | 4.9 | QFRE           | Q — Frequency Channel                                                   | 69  |

|   |     | 4.9.1          | Introduction                                                            | 69  |

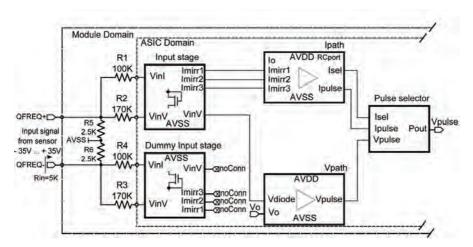

|   |     | 4.9.2          | System Architecture                                                     | 71  |

|   |     |                | 4.9.2.1 Input signal definition                                         | 73  |

|   |     |                | 4.9.2.2 Theoretical performance                                         | 74  |

|   |     | 4.9.3          | Circuit Design and Implementation                                       | 75  |

|   |     |                | 4.9.3.1 Input circuit                                                   | 75  |

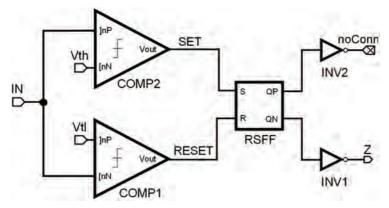

|   |     |                | 4.9.3.2 Current detect path                                             | 80  |

|   |     |                | 4.9.3.3 Voltage path                                                    | 82  |

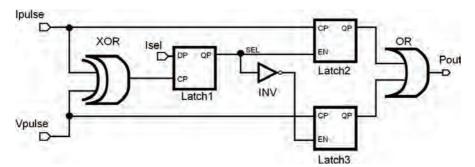

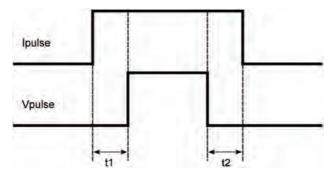

|   |     |                | 4.9.3.4 Pulse selector                                                  | 84  |

|   |     | 4.9.4          | Experimental Results                                                    | 85  |

|   |     |                | 4.9.4.1 High voltage amplifier                                          | 90  |

|   |     |                | 4.9.4.2 Measurement results                                             | 90  |

| _ | CI. | , .            | 4. 6D 4.4                                                               | 0.5 |

| 5 |     |                | zation of Prototypes                                                    | 95  |

|   | 5.1 |                | sment of Prototype Performance                                          | 95  |

|   |     | 5.1.1          | ASIC in PGA Package                                                     | 95  |

|   |     | 5.1.2<br>5.1.3 | Functional Tests                                                        | 95  |

|   |     | 5.1.5          | Design Changes Implemented for 2 <sup>nd</sup> Version of HIGHTECS ASIC | 06  |

|   |     |                | OI DIOTIECS ASIC                                                        | 96  |

|   |      | 5.1.4    | Modifica             | ation to Top Layer Metallisations                |     |

|---|------|----------|----------------------|--------------------------------------------------|-----|

|   |      |          | on 1st Ve            | ersion of HIGHTECS ASIC                          | 97  |

|   |      | 5.1.5    | 2 <sup>nd</sup> Vers | ion of HIGHTECS ASIC                             | 97  |

|   |      | 5.1.6    | Environ              | mental Tests                                     | 98  |

|   |      | 5.1.7    | Characte             | erisation Tests                                  | 98  |

|   |      | 5.1.8    | Prototyp             | be SiC Transient Voltage Suppressors             | 98  |

|   | 5.2  | Testing  | g of SOI T           | Test Chip                                        | 100 |

|   |      | 5.2.1    | High Te              | mperature Storage (250°C)                        | 102 |

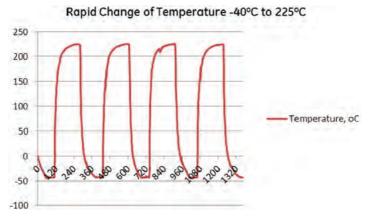

|   |      | 5.2.2    | Rapid To             | emperature Cycling (-40°C to +225°C)             | 103 |

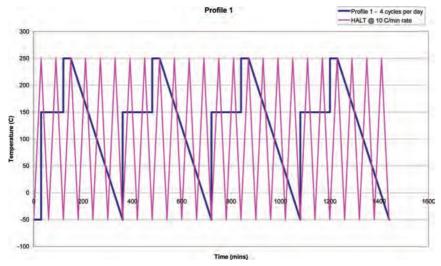

|   |      |          | 5.2.2.1              | Profile No. 1: $4 \times$ following cycle        | 104 |

|   |      |          | 5.2.2.2              | Profile No. 2: $2 \times \text{following cycle}$ | 104 |

|   |      | 5.2.3    | Vibratio             | n (Room Temperature and 200°C)                   | 107 |

|   |      | 5.2.4    | Silicon (            | Capacitors                                       | 107 |

|   | 5.3  | Functi   | onal Tests           | on Eagle Test Systems                            | 108 |

|   |      | 5.3.1    | Room To              | emperature Testing                               | 108 |

|   |      | 5.3.2    |                      | d Low Temperature Testing                        | 110 |

|   |      | 5.3.3    | Environ              | mental Tests                                     | 110 |

|   |      |          | 5.3.3.1              | High temperature storage                         | 110 |

|   |      |          | 5222                 | (200°C and 250°C)                                | 110 |

|   |      |          | 5.3.3.2              | Temperature cycling                              | 111 |

|   |      |          | 5222                 | (-40°C to +250°C)                                | 111 |

|   |      |          | 5.3.3.3<br>5.3.3.4   | Vibration/Shock                                  | 112 |

|   |      |          | 3.3.3.4              | Testing of HIGHTECS hybrid circuit               |     |

|   |      |          |                      | and high temperature PCB containing              | 110 |

|   |      |          |                      | resistors                                        | 113 |

| 6 |      | • /      |                      | lates and Lifetime Prediction                    | 119 |

|   | 6.1  |          |                      | e Tests and Lifetime Prediction                  | 119 |

|   |      | 6.1.1    |                      | Ageing at 200°C and 250°C                        | 119 |

|   | 6.2  |          |                      | ability Prediction                               | 119 |

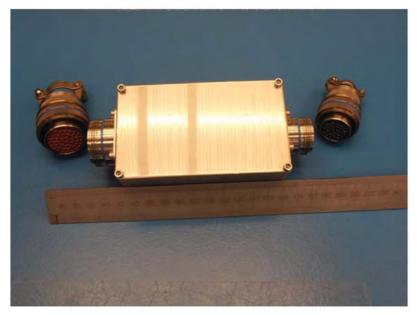

|   |      | 6.2.1    |                      | Weight and Dimensions                            | 119 |

|   |      | 6.2.2    |                      | Power Consumption                                | 121 |

|   | 6.3  | Summ     | ary                  |                                                  | 121 |

| 7 | Futi | ıre Dire | ections for          | r High Temperature Electronics                   | 123 |

|   | 7.1  |          |                      | Devices                                          | 123 |

|   | 7.2  | Passiv   | e Compon             | nents                                            | 123 |

|   | 7.3  | 1st and  | d 2nd Leve           | el Assembly                                      | 124 |

|   | 7.4  | Custor   | n Metallis           | sations                                          | 124 |

|         |                        |                              | Contents | ix  |

|---------|------------------------|------------------------------|----------|-----|

| 7.5     | EMI/L                  | ightning Protection          |          | 125 |

| 7.6     | Applic                 | ations                       |          | 125 |

| 7.7     | Comm                   | ercial/Environmental Factors |          | 126 |

|         | 7.7.1                  | Market Size                  |          | 126 |

|         | 7.7.2                  | Custom vs Discrete Solutions |          | 126 |

|         | 7.7.3                  | Integration into Systems     |          | 126 |

|         | 7.7.4                  | Lifetime Support             |          | 127 |

|         | 7.7.5                  | Economics                    |          | 127 |

| Index   |                        |                              |          | 129 |

| About t | he Auth                | nors                         |          | 131 |

| About t | About the Contributors |                              |          | 133 |

#### **Preface**

Incorporating electronics into hotter parts of equipment for monitoring and measuring outputs from sensors in aircraft engines or for down-well drilling and logging has been the goal of several organisations worldwide, with the objectives of reducing the amount of cables and eliminating the need for cooling systems, leading to increased fuel efficiency and reduced gaseous emissions. The challenges include finding semiconductors that can work at temperatures of 200°C and above, the availability of passive components and having reliable packaging and interconnections that can withstand the high temperature environment for the lifetime of the product (up to 25 years for aircraft).

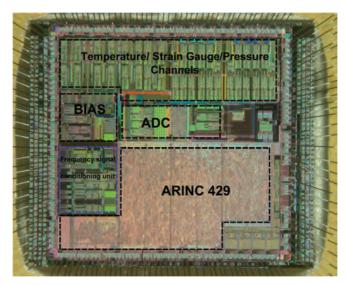

This book is the culmination of work carried out within an EU Clean Sky project called HIGHTECS, which realised an Application Specific Integrated Circuit (ASIC) to carry out the signal conditioning and processing from a range of sensors representative of an aero-engine application and fabricated using a Silicon-on-Insulator (SOI) semiconductor process. The ASIC functionality was characterised over a range of temperatures from –40°C to +250°C and demonstrators were built using high temperature electronics assembly techniques.

Finally, some thoughts on the future applications of high temperature electronics and the issues influencing more widespread commercial exploitation are presented.

#### **Acknowledgments**

The results presented in this book were generated during High Temperature Survival Electronic Devices for Engine Control Systems (HIGHTECS) project.

HIGHTECS was partially funded by EU Clean Sky Grant 255749 and support from GE. The specification was defined by Turbomeca and the project was carried out by a consortium of GE-Research Munich (Germany), GE Aviation Systems (Newmarket, U.K.) and Oxford University (U.K.).

#### **Disclaimer**

The results presented in this book reflect only the author's view. The Joint Undertaking (JU) is not responsible for any use that may be made of the information it contains.

#### **Book Abstract**

This book will cover the development of a demonstrator distributed high temperature electronics platform for integration with sensor elements to provide digital outputs that can be used by the FADEC (Full Authority Digital Electronic Control) system or the EHMS (Engine Health Monitoring System) on an aircraft engine.

# **List of Figures**

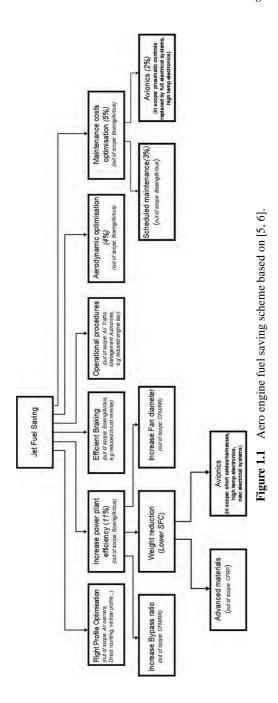

| Figure 1.1         | Aero engine fuel saving scheme based on [5, 6]                          | 5  |

|--------------------|-------------------------------------------------------------------------|----|

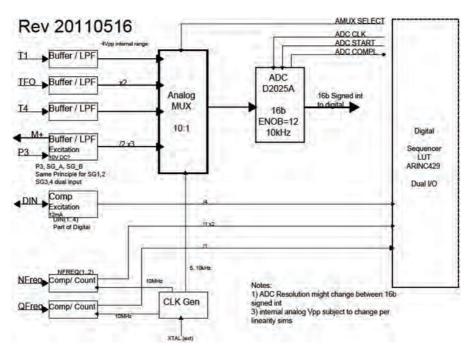

| Figure 3.1         | Block diagram for SOI ASIC in HIGHTECS                                  |    |

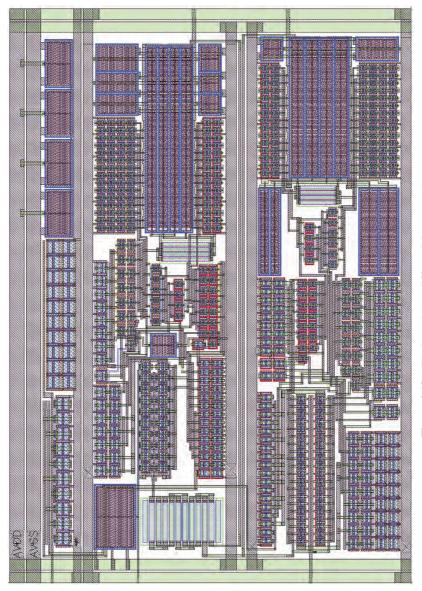

| J                  | module                                                                  | 21 |

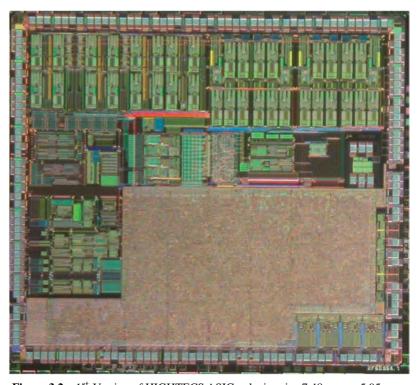

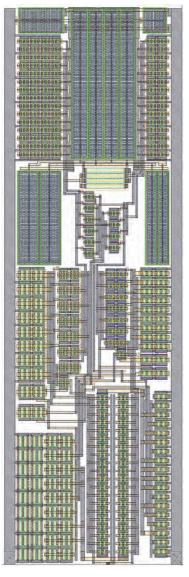

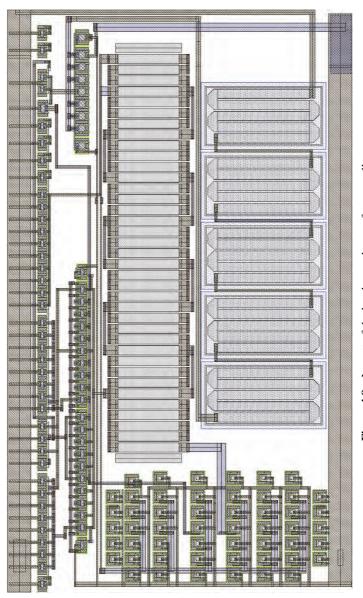

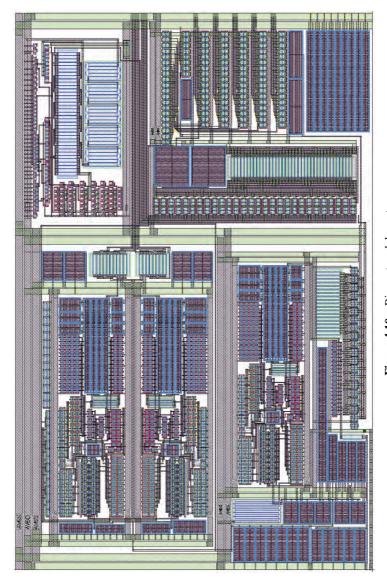

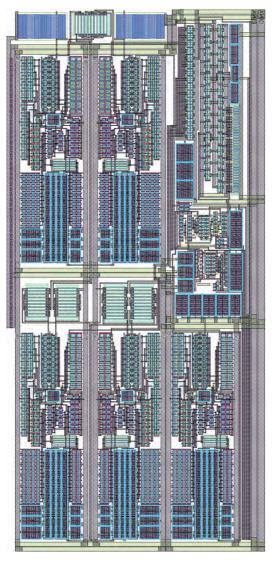

| Figure 3.2         | 1 <sup>st</sup> Version of HIGHTECS ASIC – device size                  |    |

|                    | $7.48 \text{ mm} \times 5.95 \text{ mm}. \dots \dots \dots \dots \dots$ | 22 |

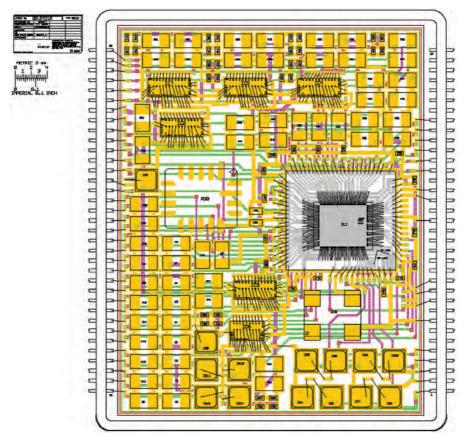

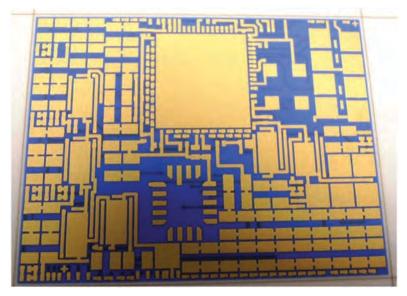

| Figure 3.3         | Layout of HIGHTECS hybrid circuit                                       | 23 |

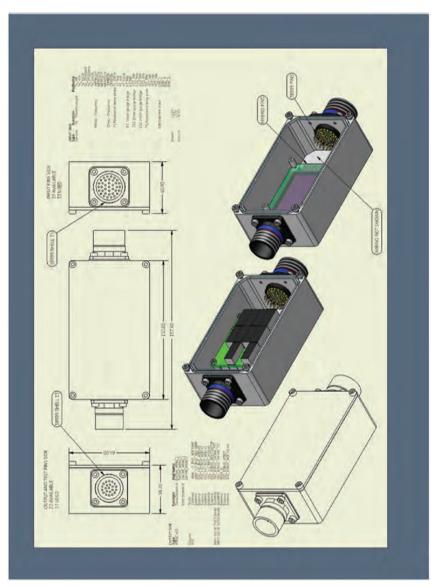

| Figure 3.4         | Mechanical assembly drawing for HIGHTECS                                |    |

| J                  | module                                                                  | 25 |

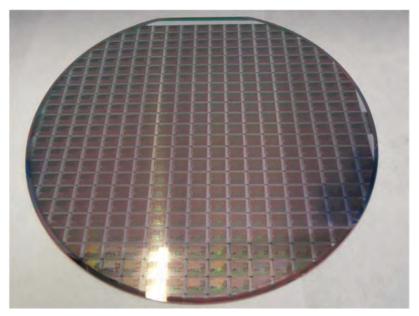

| Figure 3.5         | Silicon wafer containing HIGHTECS ASICs                                 | 26 |

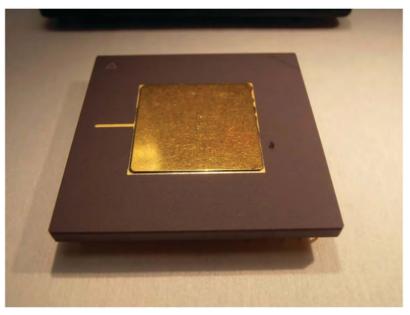

| Figure 3.6         | HIGHTECS ASIC assembled in HTCC PGA                                     |    |

| _                  | package                                                                 | 26 |

| Figure 3.7         | HIGHTECS hybrid circuit substrate                                       | 27 |

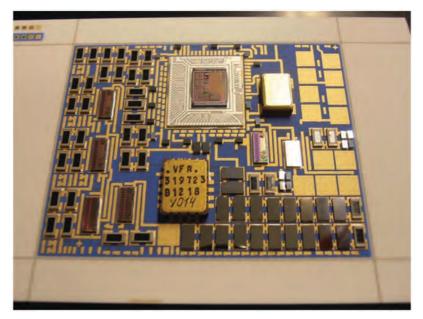

| Figure 3.8         | HIGHTECS populated hybrid circuit substrate                             | 28 |

| Figure 3.9         | HIGHTECS hybrid circuit mounted in metal                                |    |

|                    | package                                                                 | 28 |

| Figure 3.10        | Resistors surface mounted onto high temperature                         |    |

|                    | printed circuit board                                                   | 29 |

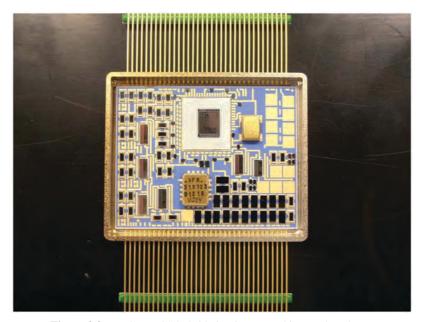

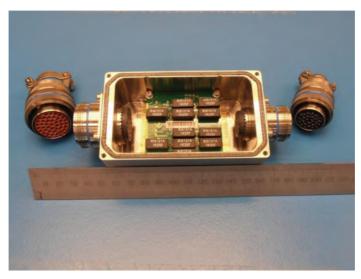

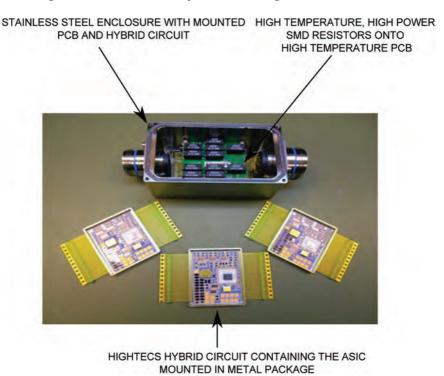

| <b>Figure 3.11</b> | Stainless Steel enclosure with mounted PCB                              |    |

|                    | and hybrid circuit                                                      | 30 |

| <b>Figure 3.12</b> | Stainless steel enclosure with lid incorporating                        |    |

|                    | EMI gasket                                                              | 30 |

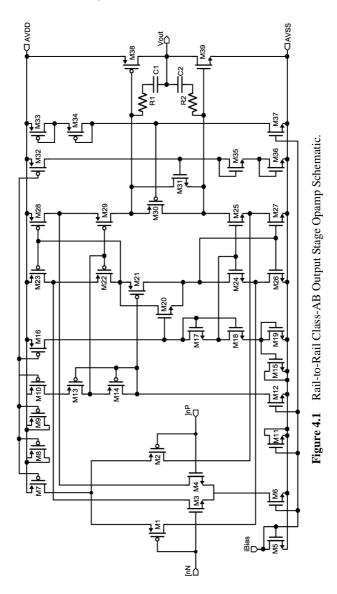

| Figure 4.1         | Rail-to-Rail Class-AB Output Stage Opamp                                |    |

|                    | Schematic                                                               | 32 |

| Figure 4.2         | Rail-to-Rail Class-AB Output Stage                                      |    |

|                    | Opamp Layout                                                            | 33 |

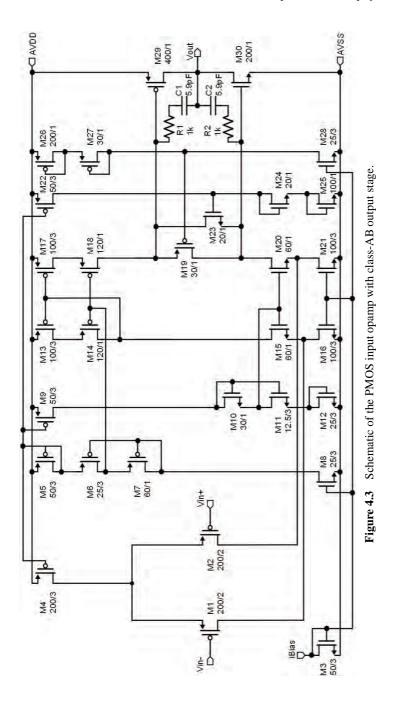

| Figure 4.3         | Schematic of the PMOS input opamp with class-AB                         |    |

|                    | output stage                                                            | 35 |

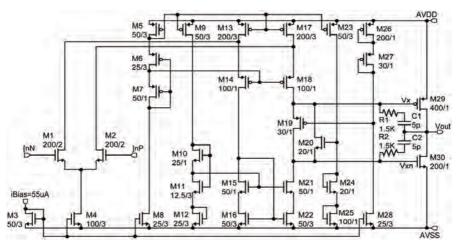

| Figure 4.4         | Circuit schematic, device sizes and bias current                        |    |

|                    | of the NMOS input class AB output stage                                 |    |

|                    | opamp                                                                   | 37 |

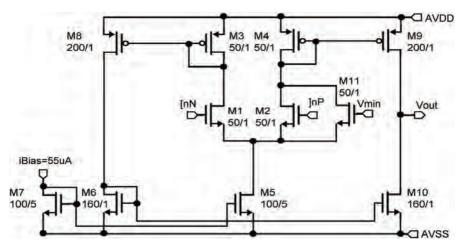

| Figure 4.5         | Circuit schematic, device sizes and bias current                        |    |

|                    | of the 3 input opamp                                                    | 39 |

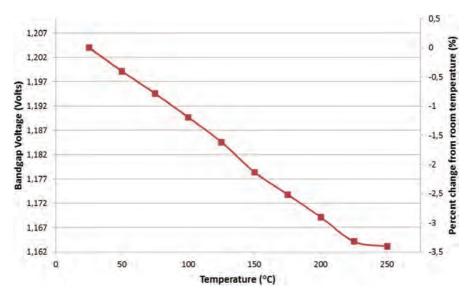

| Figure 4.6  | Symmetrically matched current-voltage mirror         |    |

|-------------|------------------------------------------------------|----|

|             | to generate V-reference                              | 39 |

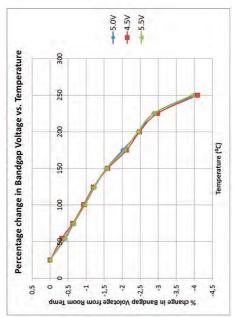

| Figure 4.7  | Bandgap voltage (actual and percent change)          |    |

|             | vs. temperature                                      | 40 |

| Figure 4.8  | Layout of the bandgap voltage reference cell         | 42 |

| Figure 4.9  | Post-layout extraction simulation results            |    |

|             | of the bandgap voltage cell over PVT                 |    |

|             | corners                                              | 43 |

| Figure 4.10 | Bias network layout                                  | 44 |

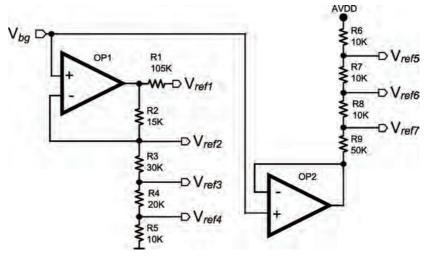

| Figure 4.11 | Reference voltages generator schematic diagram       | 45 |

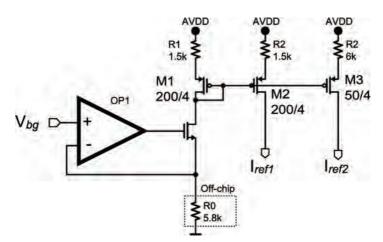

| Figure 4.12 | Schematic diagram of voltage to current              |    |

|             | converter                                            | 45 |

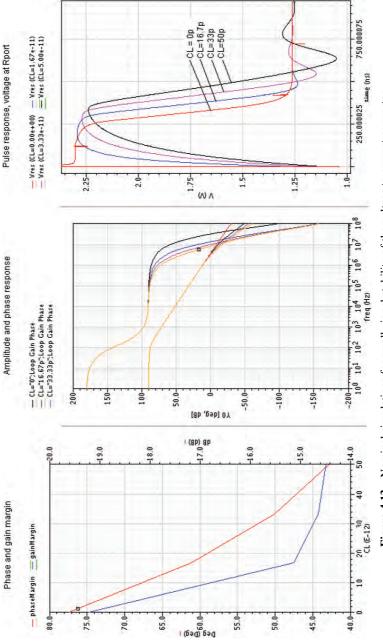

| Figure 4.13 | Nominal simulations for small-signal stability       |    |

|             | of the voltage to current converter                  | 47 |

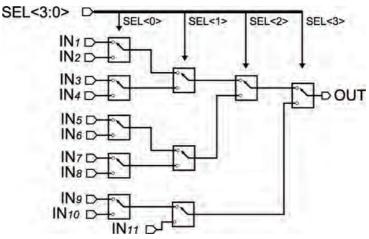

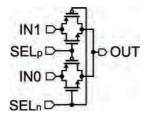

| Figure 4.14 | Analog multiplexer schematic diagram                 | 48 |

| Figure 4.15 | 2:1 Multiplexer and transmission gate                |    |

|             | implementation                                       | 48 |

| Figure 4.16 | Multiplexer simulation results                       | 49 |

| Figure 4.17 | Layout of analog 11:1 multiplexer                    | 51 |

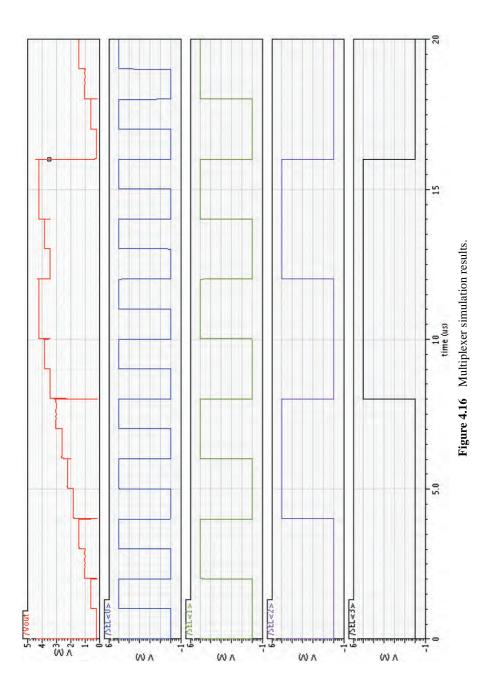

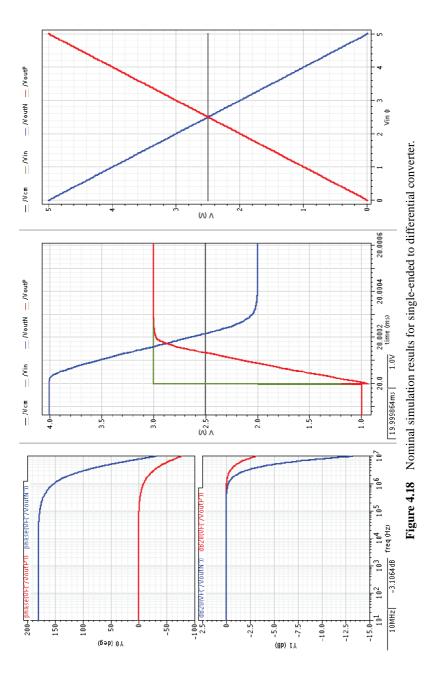

| Figure 4.18 | Nominal simulation results for single-ended          |    |

|             | to differential converter                            | 52 |

| Figure 4.19 | Single-ended to differential converter layout        | 53 |

| Figure 4.20 | Schematic of the single-ended to differential        |    |

|             | converter                                            | 54 |

| Figure 4.21 | Micrograph of the designed instrumentation           |    |

|             | amplifier and single-ended to differential converter |    |

|             | in X-FAB XI10 SOI process                            | 55 |

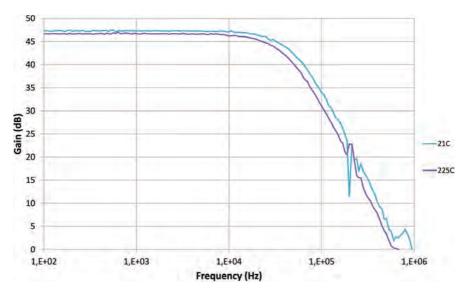

| Figure 4.22 | Measured DC gain of the instrumentation amplifier    |    |

|             | used in the strain gauge channel                     | 55 |

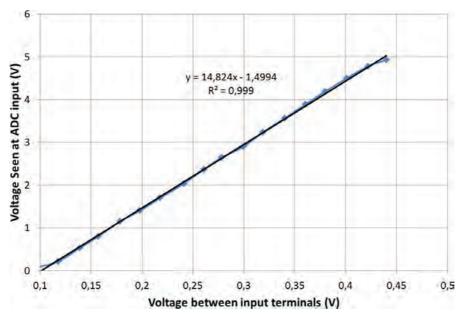

| Figure 4.23 | Measured linearity of the temperature channel        |    |

|             | at 225°C                                             | 56 |

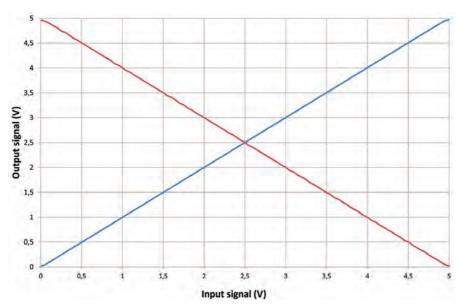

| Figure 4.24 | Measured transfer function of the single-ended       |    |

|             | to differential converter at 225°C                   | 56 |

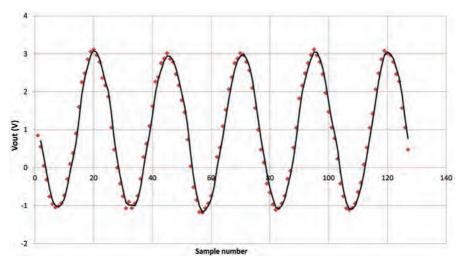

| Figure 4.25 | Measured output waveform of the strain gauge         |    |

|             | channel with a 16 mV sinusoidal input indicates a    |    |

|             | gain of 240                                          | 57 |

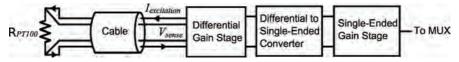

| Figure 4.26 | Temperature channel T1 signal conditioning           |    |

|             | diagram                                              | 58 |

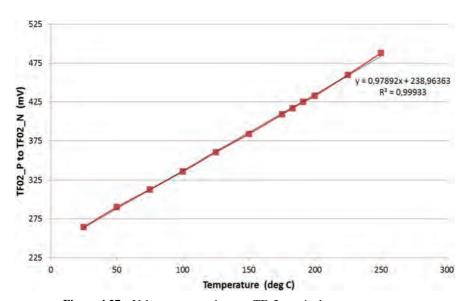

| Figure 4.27        | Voltage measured across TFo2 terminals                                             |    |

|--------------------|------------------------------------------------------------------------------------|----|

|                    | vs. temperature                                                                    | 58 |

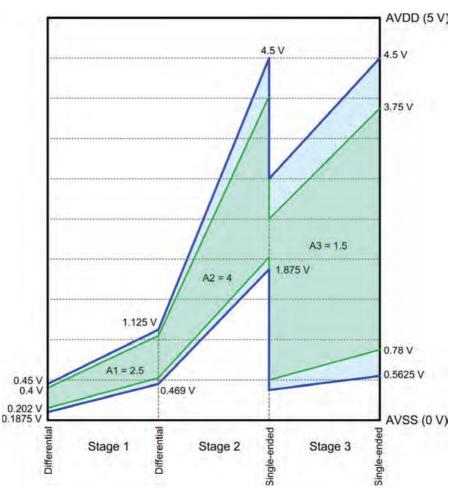

| Figure 4.28        | Voltage gain profile of the analog front-end. Blue                                 |    |

|                    | area – extreme voltages, corresponding to 2.5 mA/                                  |    |

|                    | 3 mA excitation current. Green area – nominal                                      |    |

|                    | profile, corresponding to 2.7 mA excitation                                        |    |

|                    | current                                                                            | 60 |

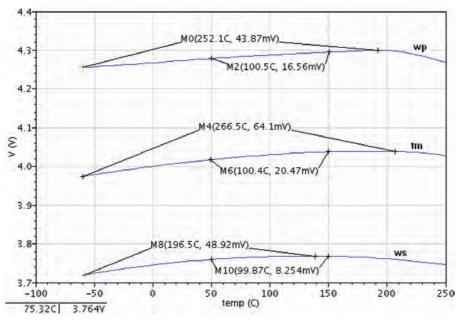

| Figure 4.29        | Output voltage of T1 channel. Transistor-level                                     |    |

|                    | bandgap and excitation current source. The largest                                 |    |

|                    | static error over three simulated cases is 4.5°C                                   |    |

|                    | $(\pm 2.26^{\circ}\text{C})$ at $-60 \dots +250^{\circ}\text{C}$ temperature span, |    |

|                    | and $1.41^{\circ}$ C ( $\pm 0.7^{\circ}$ C) at +50 +150°C                          | 62 |

| Figure 4.30        | Output voltage of T1 channel. Ideal excitation                                     |    |

|                    | current source and reference voltage source.                                       |    |

|                    | The largest static error over three simulated                                      |    |

|                    | cases is $1.76^{\circ}$ C ( $\pm 0.88^{\circ}$ C) at $-60 \dots +250^{\circ}$ C    | 63 |

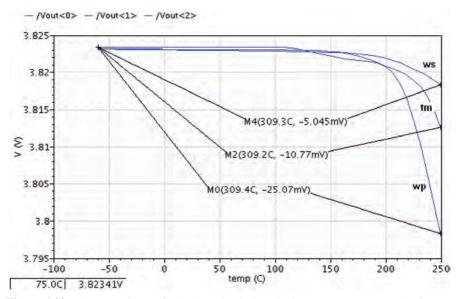

| Figure 4.31        | Simulated resistance error. Transistor-level bandgap                               |    |

|                    | and excitation current source. The largest static                                  |    |

|                    | error over three simulated cases is 0.67 Ohm,                                      |    |

|                    | which corresponds to $1.77^{\circ}\text{C}~(\pm 0.89^{\circ}\text{C})$             |    |

|                    | at -60 +130°C                                                                      | 65 |

| Figure 4.32        | Input pad for channel T1/TFo ("APRBDF")                                            | 65 |

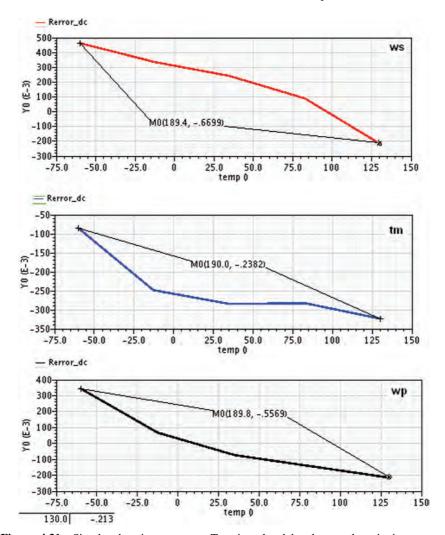

| Figure 4.33        | T1 top level schematic                                                             | 66 |

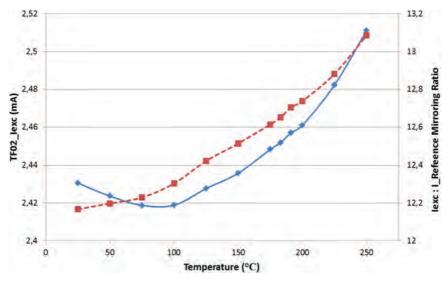

| Figure 4.34        | TFo2 $I_{excitation}$ (solid) and mirroring ratio (dotted)                         |    |

|                    | vs. temperature                                                                    | 66 |

| Figure 4.35        | T1/TFo layout – size: 730 um $\times$ 1530 um                                      | 67 |

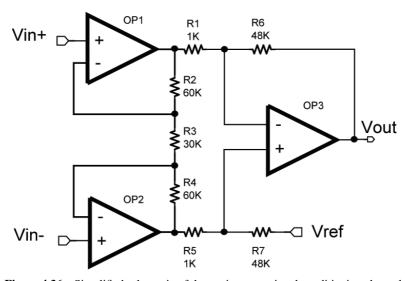

| <b>Figure 4.36</b> | Simplified schematic of the strain gauge signal                                    |    |

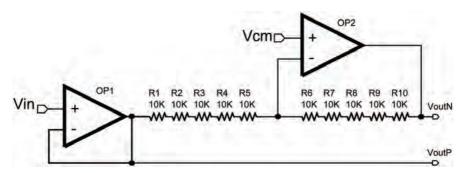

|                    | conditioning channel                                                               | 68 |

| Figure 4.37        | HIGHTECS module                                                                    | 69 |

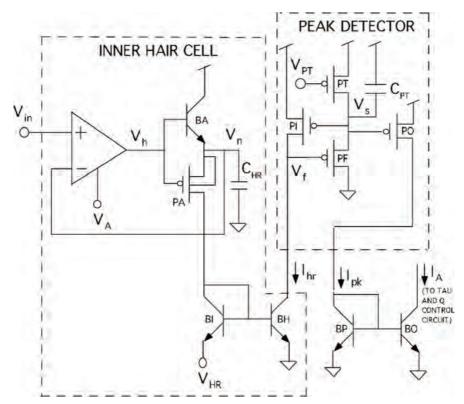

| Figure 4.38        | Peak detector presented in Figure 9 of [9].                                        |    |

|                    | (c) Springer. Reprinted with permission                                            | 70 |

| Figure 4.39        | Peak detector presented in Figure 2 of [11]                                        |    |

|                    | (c) IEEE. Reprinted with permission                                                | 71 |

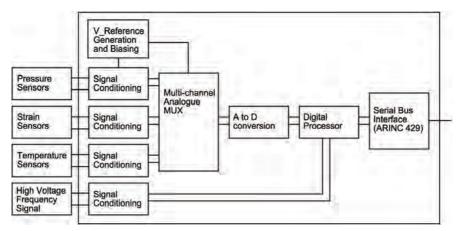

| Figure 4.40        | HIGHTECS ASIC function level block diagram                                         |    |

|                    | including the signal conditioning processing                                       | _  |

|                    | the high voltage frequency signal                                                  | 72 |

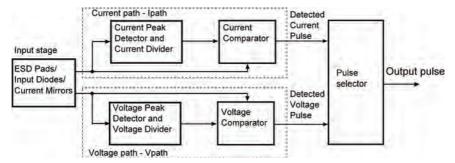

| Figure 4.41        | Block diagram of the frequency signal conditioning                                 |    |

|                    | unit for rotating equipment                                                        | 73 |

| Figure 4.42        | Input signal model.                                                                | 73 |

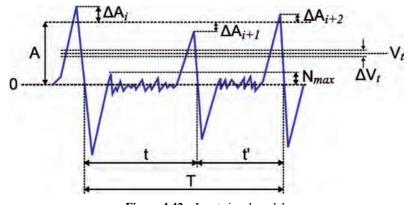

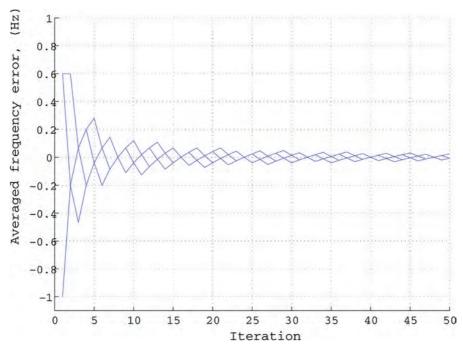

| Figure 4.43 | System averaged frequency error simulation results              |    |

|-------------|-----------------------------------------------------------------|----|

|             | for a maximum input frequency $F_{sig} = 3999$ Hz and           |    |

|             | a reference clock frequency $F_{ref} = 10 \text{ MHz.} \dots 7$ | 76 |

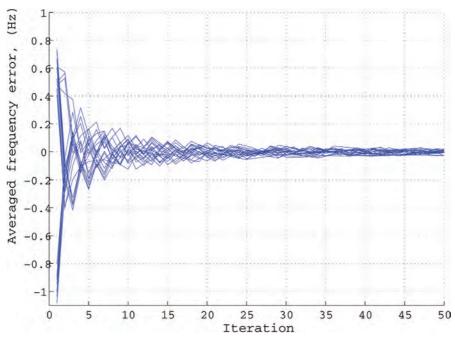

| Figure 4.44 | System averaged frequency error simulation results              |    |

|             | with added uniformly distributed jitter between                 |    |

|             | $\pm 25$ ns for a maximum input frequency $F_{siq} =$           |    |

|             | 3999 Hz and a reference clock frequency                         |    |

|             |                                                                 | 77 |

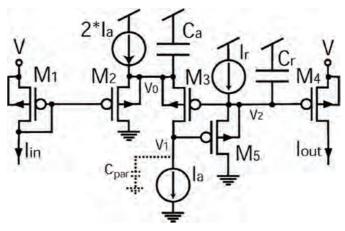

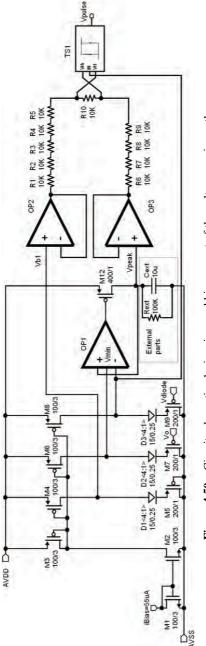

| Figure 4.45 | Top level circuit schematic of the signal                       |    |

| S           | conditioning unit processing the high voltage                   |    |

|             |                                                                 | 77 |

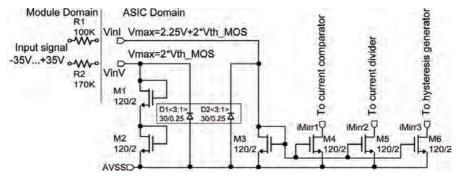

| Figure 4.46 | Input stage circuit schematic. Diodes D1, D2                    |    |

| 8           | are providing the current path for negative input               |    |

|             |                                                                 | 78 |

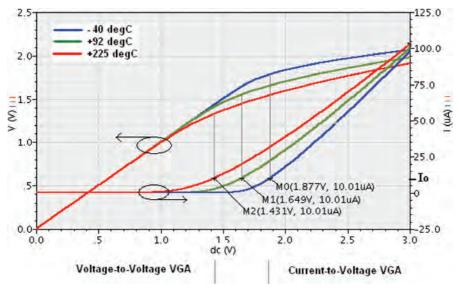

| Figure 4.47 | Simulated MOS diode current and voltage outputs                 |    |

|             |                                                                 | 78 |

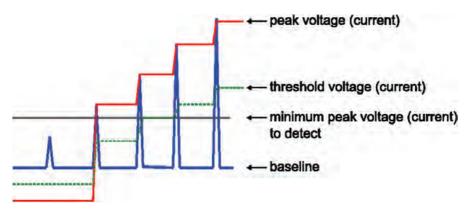

| Figure 4.48 | Pulse detection principle based on peak current                 |    |

|             |                                                                 | 79 |

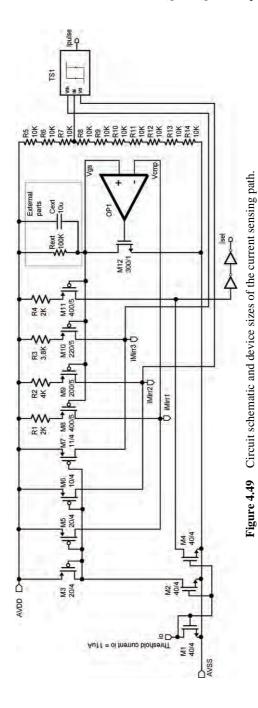

| Figure 4.49 | Circuit schematic and device sizes of the current               |    |

|             | sensing path                                                    | 31 |

| Figure 4.50 | Circuit schematic, device sizes and bias current                |    |

|             | of the voltage sensing path                                     | 33 |

| Figure 4.51 | Circuit schematic of Schmitt Trigger                            | 34 |

| Figure 4.52 | Pulse selector schematic                                        | 34 |

| Figure 4.53 | Pulse timing diagram                                            | 35 |

| Figure 4.54 | Stainless steel enclosure with mounted PCB and                  |    |

|             | hybrid circuit including the HIGHTECS ASIC 8                    | 36 |

| Figure 4.55 | Photograph of the customized high temperature                   |    |

|             | evaluation board used during HIGHTECS ASIC                      |    |

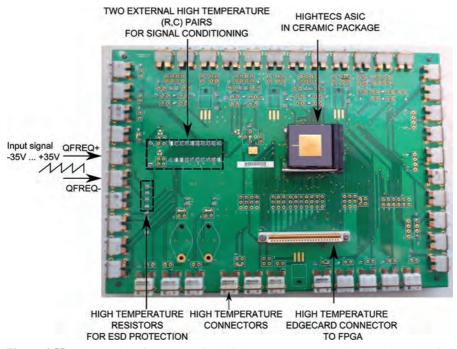

|             |                                                                 | 37 |

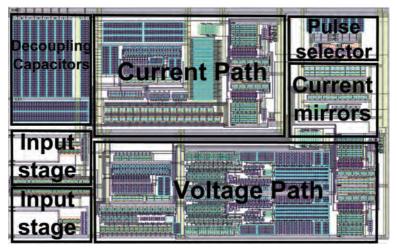

| Figure 4.56 | Layout of the frequency signal conditioning unit                |    |

|             | $[1  mm \times 1.5  mm]$ integrated onto the fabricated         |    |

|             |                                                                 | 37 |

| Figure 4.57 | Micrograph of the bonded HIGHTECS ASIC                          |    |

|             | fabricated in the X-FAB XI10 SOI process.                       |    |

|             | The frequency signal conditioning unit is positioned            |    |

|             | ` ,                                                             | 38 |

| Figure 4.58 | Block diagram of the HIGHTECS ASIC hardware                     |    |

|             | & software test platform                                        | 39 |

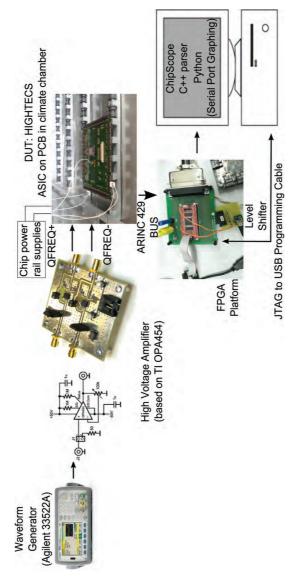

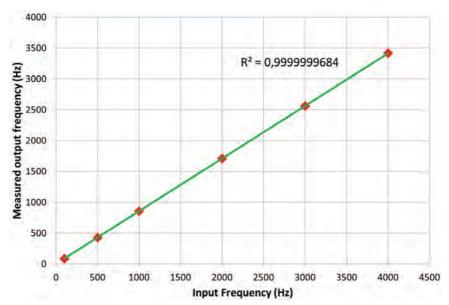

| Figure 4.59  |                                                              |     |

|--------------|--------------------------------------------------------------|-----|

|              | and FPGA at 25°C shows a linearity value of $R^2$ =          |     |

|              | 0.999999684 with a reference clock frequency                 | 0.1 |

| T: 4.60      | of $F_{ref}$ = 12.288 MHz                                    | 91  |

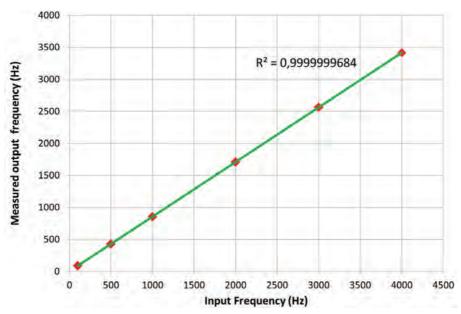

| Figure 4.60  |                                                              |     |

|              | and FPGA at 235°C shows a linearity value of $R^2$ =         |     |

|              | 0.999999684 with a reference clock frequency                 | 0.2 |

| F: 4.61      | of $F_{ref} = 12.288 \text{ MHz.}$                           | 92  |

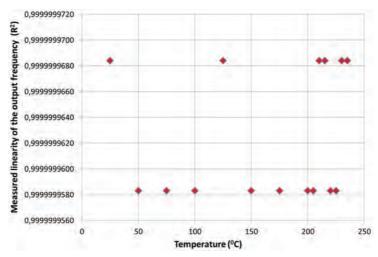

| Figure 4.61  | Measured linearity values $(R^2)$ of the output              |     |

|              | frequency over the 25°C to 235°C temperature range           |     |

|              | are within specification limits. The reference clock         | 0.2 |

| T: #4        | frequency value is $F_{ref} = 12.288 \text{ MHz.}$           | 93  |

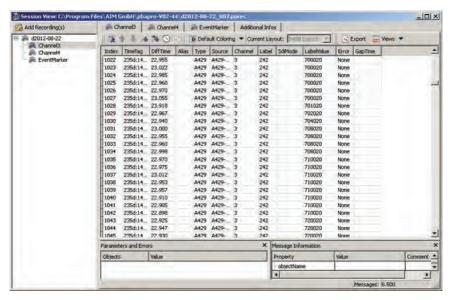

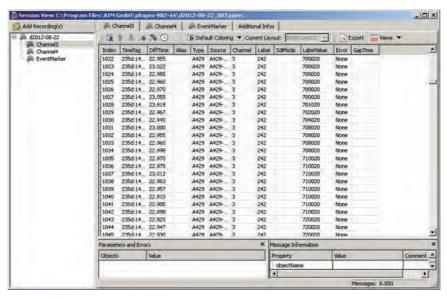

| Figure 5.1   | HIGHTECS ASIC in PGA package connected to                    | 0.0 |

| F: 5.0       | ARINC 429 data reader                                        | 96  |

| Figure 5.2   | ARINC 429 output from HIGHTECS ASIC                          | 97  |

| Figure 5.3   | ADC linearity plot of 2 <sup>nd</sup> version of HIGHTECS    | 00  |

| Te: 5.4      | ASIC assembled in PGA packages                               | 99  |

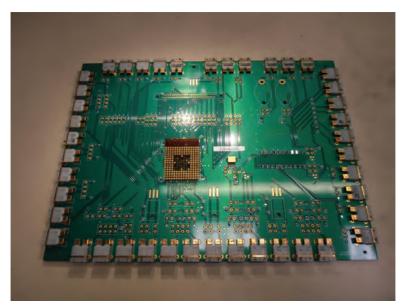

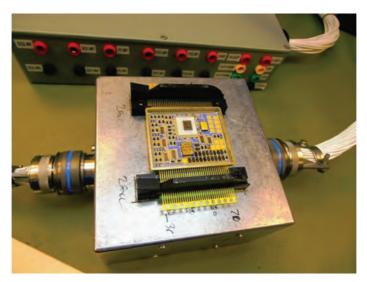

| Figure 5.4   | Characterisation board for testing of HIGHTECS               | 100 |

| Te: 5.5      | ASIC in PGA package.                                         | 100 |

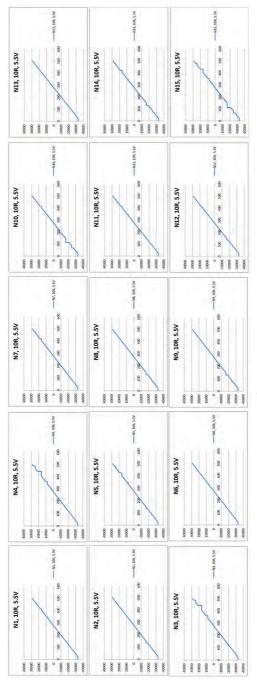

| Figure 5.5   | Voltage bandgap change with temperature and                  |     |

|              | effective temperature coefficient of 2 <sup>nd</sup> version | 101 |

| E: 5.6       | of HIGHTECS ASIC                                             | 101 |

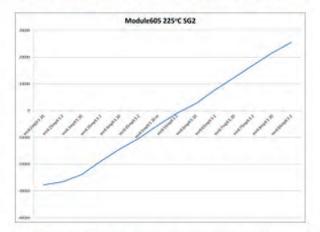

| Figure 5.6   | Output from SG2 sensor on HIGHTECS module                    | 100 |

| E: 5.7       | at +225°C                                                    | 102 |

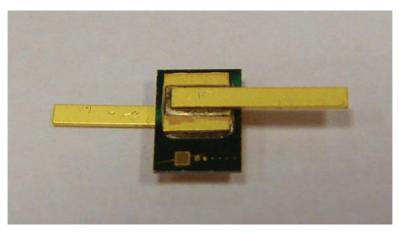

| Figure 5.7   | Prototype SiC TVS devices with copper tags                   | 102 |

| Eigene 50    | attached                                                     | 102 |

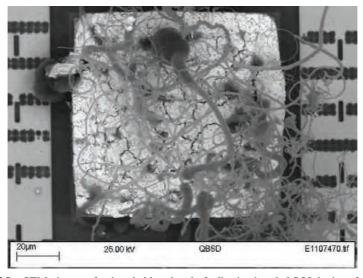

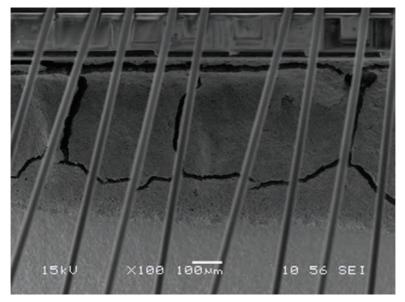

| Figure 5.8   | SEM picture of unbonded bond pad of adhesive                 |     |

|              | bonded SOI device after 11,088 hours exposure                | 104 |

| Figure 5.9   | to 250°C showing growth of whiskers                          | 104 |

| Figure 3.9   | for Profile 1                                                | 105 |

| Figure 5.10  | Example of full day equivalent running                       | 103 |

| riguite 5.10 | for Profile 2                                                | 105 |

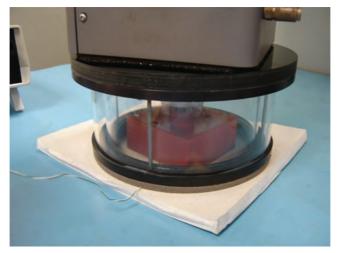

| Figure 5.11  | Equipment for rapid change of temperature from               | 103 |

| riguite 3.11 | -40°C to +225°C with 320 second cycle time                   | 106 |

| Figure 5.12  | •                                                            | 100 |

| riguit 3.12  | of temperature with 320 second cycle time                    | 106 |

| Figure 5.13  | •                                                            | 100 |

| riguit 3.13  | to ARING 429 data reader                                     | 109 |

|              |                                                              |     |

#### xx List of Figures

| Figure 5.14 | ARINC 429 output from HIGHTECS ASIC                   | 110 |

|-------------|-------------------------------------------------------|-----|

| Figure 5.15 | Cracking of die attach material after 375 cycles from |     |

|             | -40°C to +250°C                                       | 112 |

| Figure 5.16 | Test Box for HIGHTECS hybrid circuit                  |     |

|             | and module                                            | 113 |

| Figure 5.17 | Test of HIGHTECS hybrid circuit                       | 114 |

| Figure 5.18 | Test of HIGHTECS module                               | 114 |

| Figure 5.19 | Output from ARINC 429 monitor from HIGHTECS           |     |

|             | hybrid                                                | 115 |

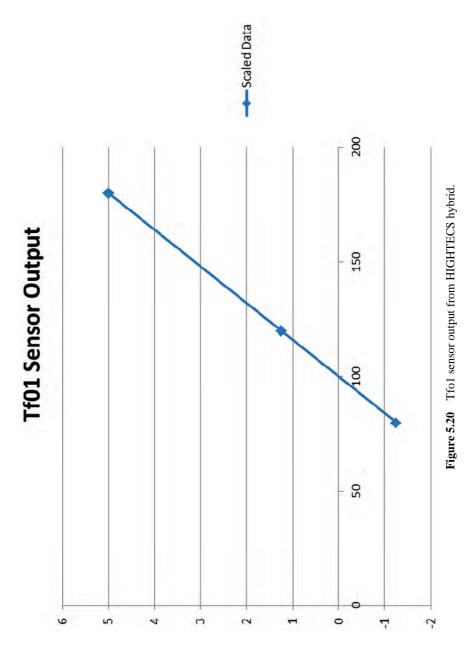

| Figure 5.20 | Tfo1 sensor output from HIGHTECS hybrid               | 116 |

| Figure 5.21 | Pulse generators used for testing of Qfreq            |     |

|             | sensor                                                | 117 |

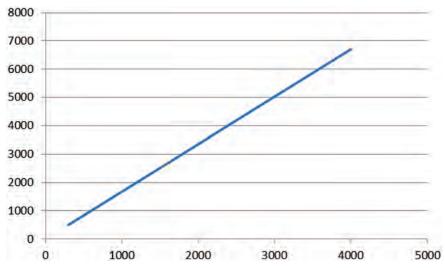

| Figure 5.22 | Qfreq sensor output against input frequency at room   |     |

|             | temperature                                           | 118 |

|             |                                                       |     |

## **List of Tables**

| Table 1.1   | Clean Sky1 and Clean Sky2 targets                 | 7   |

|-------------|---------------------------------------------------|-----|

| Table 3.1   | Functional blocks for HIGHTECS ASIC               | 22  |

| Table 4.1   | Rail-to-Rail opamp corner simulation results      | 31  |

| Table 4.2   | Corner simulation results of the PMOS input opamp |     |

| 14510 112   | with class AB output stage                        | 36  |

| Table 4.3   | Process variation                                 | 38  |

| Table 4.4   | PVT corner simulation results of the NMOS input   | 50  |

| 14510 111   | class AB output stage opamp. Process variation    |     |

|             | corners are presented in Table 4.3                | 38  |

| Table 4.5   | Bandgap voltage generator simulation results      | 40  |

| Table 4.6   | Simulation results                                | 43  |

| Table 4.7   | Simulation results of the voltage reference       | 73  |

| 1abic 4.7   | generator                                         | 46  |

| Table 4.8   | Specification versus achieved performance         | 57  |

| Table 4.9   | Functional blocks included in the ASIC            | 71  |

| Table 4.10  | Specification versus measurement results          | 92  |

| Table 5.1   | -                                                 | 92  |

| Table 5.1   | Summary of environmental tests on HIGHTECS        | 100 |

| T-11- 52    | ASIC in PGA package                               | 100 |

| Table 5.2   | Lightning induced transient susceptibility – pin  | 102 |

| T. 1.1. 5.0 | injection tests                                   | 103 |

| Table 5.3   | Summary of environmental tests carried out on SOI | 100 |

|             | test chip                                         | 103 |

| Table 5.4   | Temperature storage tests at 200°C on HIGHTECS    |     |

|             | ASIC in PGA package                               | 111 |

| Table 5.5   | Temperature storage tests at 250°C on HIGHTECS    |     |

|             | ASIC in PGA package                               | 111 |

| Table 5.6   | Temperature cycling tests from –40°C to 250°C     |     |

|             | on HIGHTECS ASIC in PGA package                   | 112 |

| Table 5.7   | Vibration and shock tests on HIGHTECS ASIC        |     |

|             | in PGA package                                    | 113 |

#### xxii List of Tables

| Table 6.1        | Estimate of operating lifetime after extrapolation |     |

|------------------|----------------------------------------------------|-----|

|                  | of temperature storage results for 1000 hours      |     |

|                  | at 200°C and 250°C                                 | 120 |

| <b>Table 6.2</b> | Summary of values derived from FMEA                |     |

|                  | on HIGHTECS module                                 | 120 |

| <b>Table 6.3</b> | Breakdown of weight by component for prototype     |     |

|                  | HIGHTECS module                                    | 120 |

| <b>Table 6.4</b> | Target and actual dimensions for prototype         |     |

|                  | HIGHTECS module                                    | 121 |

| <b>Table 6.5</b> | Target and actual current power consumption        |     |

|                  | for prototype HIGHTECS module                      | 121 |

|                  |                                                    |     |

#### List of Abbreviations

A/D Analogue to Digital

ARINC Aeronautical Radio Incorporated

ASIC Application Specific Integrated Circuit

BJT Bipolar Junction Transistor

CMOS Complementary Metal Oxide Semiconductor

DC Direct Current

DO-160 Environmental Conditions and Test Procedures

for Airborne Equipment

ECU Engine Control Unit

EHMS Engine Health Management System EMI Electro-magnetic Interference

ESD Electrostatic Discharge

FADEC Full Authority Digital Engine (or Electronic) Control

GDP Gross Domestic Product

HTCC High Temperature Co-Fired Ceramic

JFET Junction Gate Field Effect Transistor

MEMS Microelectromechanical system

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PCB Printed Circuit Board

PGA Pin Grid Array

SiC Silicon Carbide

SOI Silicon on Insulator

VHDL VHSIC Hardware Description Language

## **PART I**

# High Temperature Electronics Background

Lucian Stoica, Steve Riches, Colin Johnston

1

# High Temperature Electronics for Aviation Applications

Aviation is a dynamic industry that continuously adapts to various market forces. The aviation market doubles in size, every 10 to 15 years, so there will be a greater need in the future for large aircrafts.

Key market forces that impact the airline industry are fuel prices, economic growth and development, environmental regulations, infrastructure, market liberalization, airplane capabilities, other modes of transport, business models, and emerging markets [1]. Each of these forces can have both positive and negative impacts on the industry.

While the world economy GDP is expected to grow by 3.2% between 2012 to 2032, the number of airline passengers and airline traffic is expected to grow by 4.1% and 5%, respectively in the same interval.

The fleet size is expected to roughly double from 2013 to 2032 [1]. A long-term demand of 35280 new airplanes, valued at \$4.8 trillion is forecasted [1]. 14350 of them will replace older, less efficient airplanes, reducing the cost of air travel and decreasing carbon emissions.

Europe is forecasted to be second largest market in the world by 2032 [1]. As shown in one of following section, from 2008 EU has already started to address and shape future aviation needs in Clean Sky and Clean Sky2 programs.

#### 1.1 Value Story

Air traffic contributes today about 3% to global greenhouse gas emissions, and it is expected to triple by 2050 [2]. Although, other sectors are more polluting (electricity and heating produces 32% of greenhouse gases), pollution from air traffic is released high in the atmosphere where the impact is much greater. Meeting the climate and energy objectives will require reducing drastically the sector's environmental impact by reducing its emissions. Maximizing fuel

efficiency to use less to go farther is also a key cost-cutting factor in a very competitive industry – and as air traffic increases, better noise reduction technologies are needed. Game-changing innovation in Aviation is risky, complex and expensive, and requires long-term commitment. This is why all relevant aviation stakeholders must work together to develop proof-of-concept demonstrators.

#### 1.2 Fuel Prices Are Challenging the Airliners Profitability

Volatile oil prices have been the greatest challenge to airline profitability apart from the weak economy. Fuel costs have surpassed labor as the largest segment of airline operating cost [1]. Fuel costs, approximately 13 percent of total costs in 2002, are closer to 34 percent today. After spiking in early 2012, oil prices have decreased in 2015. On the demand side, the weak economic outlook has moderated near-term growth projections. On the supply side, rising shale oil production in the United States is moderating near-term price projections. Lower jet fuel prices, are bolstering near-term airline profitability as shown in Figure 4 of [3]. However, long term projections for jet fuel are indicating a significant price increase [4], from approximately \$60/barrel in 2015 to \$90/barrel in 2020, \$142/barrel in 2030 and \$229/barrel in 2040. Jet fuel price is growing faster than other goods and services.

Therefore, there is a strong need for long term investment in the development of low consumption technologies for jet engines.

#### 1.3 Growing Fuel Efficiency

Fuel costs have nearly doubled over the past 10 years. Fuel represents up to 30 percent of total operating cost for single-aisle airplanes and up to 50 percent for widebody airplanes [1]. Fuel saving is a constant research topic of airplane manufacturers [5, 6], as this has a direct impact on costs. The main ways to save fuel for aero engines are presented in Figure 1.1 [5–7]. They must be balanced against all the costs and can only be realized when the initiative is fully deployed and sustained.

Airlines can improve their fuel efficiency in different ways [5–7]:

1. Deploying more fuel-efficient engines: replace older, less efficient airplanes with new-technology airplanes, such as the Boeing 787 or Airbus 350 XWB. Weight reduction can be achieved by using composites and advanced avionics. Airbus has reported an 11% fuel burn improvement of A330neo versus current A330 at powerplant level [6].

- 2. Improving operational procedures. Airlines can optimize fuel efficiency by making changes in operations, such as reducing the engine taxi time and the use of Auxiliary Power Unit (APU). Air carriers are also keen on raising the load factors on flights, which means making sure flights are close to or at aircraft capacity (all the seats are filled) [5].

- 3. Increasing braking efficiency by reducing the flap approach and a reduced thrust reverse [5].

- 4. Optimization of flight profile includes the optimum cruise altitude, the optimum climb/descent and the optimization of the cruising speed [5].

- 5. Optimization of aerodynamics & weight body shape by using of sharklets at the tips of the wings and the use of light composite materials. Airbus has reported an 4% fuel burn improvement of A330neo versus current A330 [6].

- 6. Maintenance costs optimization: Airbus has reported a 5% fuel burn improvement of A330neo versus current A330 due to lower direct maintenance costs [6]. This was achieved with longer maintenance intervals and by replacing the pneumatic controls with an electrical bleed air system.

The scope of current project is to focus on improving jet fuel saving by increasing the engine efficiency through a reduction of its weight which can be achieved with high temperature electronics placed closer to the engine such shortening the length of cables and harnesses. Further possible applications of high temp electronics, includes the replacement of pneumatic/mechanical controls with full electrical systems.

Benefits for high temperature electronics for aero-engines: By placing the electronics near to the sensor, the weight will also be reduced since the physical length between terminals will be minimized while the cost will be reduced since fewer cables will be needed, and the associated time to mount them on the engine will be also reduced. The fault rate will decrease as the signal is digitized before transmission and cables length is reduced. Sensor accuracy is improved as signal is digitized on the spot, also as cables length is minimized there is less noise coupling area to the signals. As the components are operational at higher temperatures there will be a reduced need for cooling. The flexibility of the system is increased as the components may be now placed in hot areas, which were previously inaccessible.

#### 1.4 Clean Sky Initiative

The EU has taken a lead in green aviation technologies through Clean Sky1 and Clean Sky2 [8].

The Clean Sky Joint Technology Initiave started in 2008, and constitutes an industry wide, coherent program totaling €1.6 bn, equally shared by the EU and the European Aeronautical Industry.

Clean Sky2 is a natural continuation to progress achieved in Clean Sky1 (which has ended).

Clean Sky1 and Clean Sky2 are targeting very significant environmental gains, as shown in Table 1.1 [8].

By 2050, 75% of the world's fleet now in service (or on order) will be replaced by aircraft that can deploy Clean Sky2 technologies. Based on the same methodology applied in the Clean Sky1 economic case in 2007, the market opportunity related to these programes is estimated at ~€2000 bn. The direct economic benefit is estimated at ~€350–€400 bn and the associated spill-over is of the order of €400 bn.

The environmental case for continuing Clean Sky1 is even more compelling with an estimate of the CO<sub>2</sub> saving potential of 4 billion tones through Clean Sky2. These 4 billion tones of CO<sub>2</sub> to be saved from 2020 to 2050 will be additive to the approximately 3 billion tones achievable as a consequence of the Clean Sky Program.

GE was represented in Clean Sky1 by GE Aviation Systems (UK) & GE Global Research Munich as participants in High Temperature Survival Electronic Devices for Engine Control Systems (HIGHTECS) project no. 255749 working with Oxford University Materials.

#### 1.4.1 Benefits of High Temperature Electronics for Jet Engine **Controls and Health Monitoring**

#### Environmental benefits: lower emissions – CO<sub>2</sub> reduction by 15–20%

For the aero-engine market, the extended high temperature electronics capability will facilitate the implementation of distributed architectures, where smart actuators and sensors can replace (or off-load) the centralised control

| Table 1.1 Clean Sky1 and Clean Sky2 targets |                     |                          |  |

|---------------------------------------------|---------------------|--------------------------|--|

|                                             | Clean Sky1*         | Clean Sky2*              |  |

| CO <sub>2</sub> and Fuel Burn               | -20% to -40% (2020) | -20% to -30% (2025/2035) |  |

| $NO_x$                                      | 60% (2050)          | -20% to -40% (2025/2035) |  |

| Population exposed to                       |                     |                          |  |

| noise/Noise footprint                       | 10dB to 20dB less   |                          |  |

| impact                                      | noise (2020)        | Up to -75% (2035)        |  |

Table 1.1 Clean Sky1 and Clean Sky2 targets

<sup>\* =</sup> Baseline for Clean Sky1 and Clean Sky2 figures are best available performance in 2000 and 2014, respectively.

electronics. Up to 500 conductors are currently used for interfacing between jet engine sensors, actuators, flight control computers and the centralised FADEC. The application of distributed architectures could reduce the conductor count from 500 to 8 for duplex control, offering cable and harness weight saving, connector pin reduction, fault reduction and a simpler FADEC [9]. This type of electronic unit would be installed inside the actuator or sensor housing and would consist of the sensor signal conditioning electronics, A/D converters, multiplexers and a serial interface bus [9].

At present, long, high-temperature mineral insulated (MI) or fibre-optic cable is required to connect the sensor to the electronics located in a more benign region of the gas turbine. Electronics co-located with the sensor will lead to a reduction in associated cabling, connectors, and terminals leading to reductions in weight and parts count (hence cost). The development of MEMS sensors with electronics integrated onto a multi-chip module could also lead to significant enhancement of performance at reduced costs. Moreover, the ability to perform signal handling/conditioning prior to engine control unit (ECU) will have benefits in terms of enhancing the data available for engine health monitoring. For example, temperature signals from thermocouple arrays must be averaged prior to sending the signal to the ECU as weight restrictions do not allow for individual cables from each thermocouple to be relayed to the ECU. The use of a multiplexing systems that can withstand engine casing temperatures (~250°C) would allow individual thermocouple signals to be analyzed by the ECU off a single cable harness. This could permit the detection of engine hotspots, radial distortions in temperature and condition monitoring of individual thermocouples.

Managing engine performance is receiving a greater amount of attention for safety, reliability and fuel burning savings [10]. Advances in heat resisting sensors and the desire to use full authority digital control electronics (FADEC) and engine health monitoring systems (EHMS) near to the sensing element is accelerating the interest in the use of high temperature electronics. This is leading to the development of "intelligent sensors", which incorporate high temperature electronics in the sensor itself and have the capability to perform self-diagnosis of their health. The output of the "intelligent sensor" will be a digital signal which is then fed into the FADEC. The reduced need for processing of analogue signals within the FADEC unit can increase the capacity for incorporating the EHMS within the same unit, saving weight, space and costs.

For the aerospace market, improved sensor technology will have significant benefits in a number of areas. Firstly, although sensor weight may be small relative to the total weight of the aircraft, any improvements that could be achieved through reductions in lead-outs, terminals, connectors, etc. can still have a tangible impact on fuel consumption and running costs. For example, weight savings of even a few kilos can result in hundreds of thousands of pounds in annual fuel saving. Secondly, improved engine monitoring capability should result in engines being run at conditions for more optimal thermodynamic efficiency, resulting in reduced fuel consumptions (and engine emissions) and potentially increased component life. Moreover, improved sensor performance could lead to a reduction in maintenance costs through "smart scheduling" of servicing and overhaul based on reliable and indicative sensor data and not on fixed flight hour intervals.

#### References

- [1] Current Market Outlook 2013–2032, Boeing, www.boeing.com.

- [2] Overview of Clean Sky 2 Initiative, October 2013.

- [3] Economic Performance of the Airline Industry, IATA, Brian Pearce, Chief Economist.

- [4] Annual Energy Outlook 2015, with projections to 2040, DOE/EIA 0383 (2015), April 2015.

- [5] Airbus Customer Service, Fuel and Emissions Performance Manager, Simon Weselby, Saving Fuel: It's A Team Sport, IATA Maintenance Cost Conference, October 2012.

- [6] Airbus, The A330neo Powering into the future, John Leahy, Chief Commercial Officer - Customers.

- [7] US Energy Information Administration, www.eia.gov/todayinenergy/ detail.cfm?id=6670

- [8] Overview of the Proposed Programme, Clean Sky 2, October 2013.

- [9] HIGHTECS Project Final Report, Steve Riches, 26 October 2012.

- [10] HIGHTECS Cahier Des Charges Techniques Technical Specification v3.0, Turbomeca, Groupe Safran, 2011.

# 2

#### **High Temperature Integrated Technologies**

#### 2.1 Introduction

There is a growing desire to install electronic power and control systems in high temperature environments to improve the accuracy of critical measurements, reduce the amount of cabling and elimination of cooling systems. Typical applications include down-hole petroleum/gas/geothermal exploration and production, turbine engines for aircraft propulsion and power generation and power modules for electric/hybrid vehicles [1–4].

Fuel costs for aeroengines have approximately doubled over the past 10 years and now represent up to 50% of the operating costs of many modern widebody aircraft [5]. Reducing specific fuel consumption by reducing aircraft weight has become a major focus for research and development. The use of sensors developed to operate for long periods in high temperature environments allows sensors to be replaced close to the engine sensing and control units eliminating the need for complex heat sinks, special fuel pumping and interfacing, which in turn assists with the goal of aircraft weight reduction [6]. Mounting the engine sensing and control unit close to the sensors means ambient temperatures may easily reach 200°C. This requirement has posed a challenge to the bulk CMOS technologies which are typically qualified for operation between -55°C and 125°C. The leap in operating temperature to above 200°C in combination with high pressures, vibrations and potentially corrosive environments means that different semiconductors, passives, circuit boards and assembly processes will be needed to fulfill the target performance specifications. Although extensive research to investigate temperature related reliability effects in semiconductors such as leakage current, electromigration and time dependent dielectric breakdown (TDDB) has been carried out [7], understanding the design constraints, development of robust packaging systems and reliable interconnections are the key to the success of high temperature electronics systems. The main advantage of SOI technology in high temperature applications are the reduced leakage

current due to the reduced junction area and reduced latchup due to isolated PMOS (P-type Metal Oxide Semiconductor Logic) and NMOS (N-type Metal Oxide Semiconductor Logic) transistors [8]. CMOS SOI technology has been shown to be better suited for high temperature operation over bulk CMOS [9–11]. The reliability of CMOS SOI for use at 250°C was presented in [12]. CMOS SOI integrated circuits have been designed and tested for high-temperature applications up to 300°C in [13–19] and up to 400°C in [20]. Silicon carbide (SiC) BJT, JFET and MOSFET based integrated circuits have been demonstrated up to 600°C [21–23]. High temperature electronics technologies and applications have been recently reviewed in [24]. The major effects of elevated temperature on semiconductor material and devices are:

- An exponential increase in leakage current of reverse-biased pn junctions. This might significantly limit the performance of bulk-CMOS ICs, where the transistors are isolated from the common bulk by means of a pn junction. In SOI technologies, however, buried oxide prevents any leakage current into the bulk, thus making this technology well suited for high temperature applications. Still, structures necessarily incorporating pn diodes, like ESD protection circuits, may adversely influence the performance of a system at high temperatures.

- Carrier mobility degradation, occurring with the rate of T<sup>-n</sup> for MOS devices, where n ranges from 1.5 to 1.8 between 25°C and 200°C [17]. This directly impacts the transfer characteristics of MOS transistors since drain current of the saturated devices is proportional to the carrier mobility in the channel.

- Finally, the threshold voltage shifts by  $1-3 \text{ mV/}^{\circ}C$  as the Fermi potential, the depletion width and charge under channel reduce with temperature [17].

The above mentioned temperature effects were accounted for during the design of the circuits presented in this book by using the Zero-Temperature Coefficient (ZTC) and " $g_m/I_d$ " methodologies [25].

The European Union (EU) has taken a lead in green aviation technologies by funding projects such as Clean Sky1 and Clean Sky2 [26]. The Clean Sky Joint Technology Initiave started in 2008, and constitutes an industry wide program targeting very significant environmental gains: a reduction of  $CO_2$  and  $NO_x$  emissions of 40% and 60%, respectively. General Electric was represented in Clean Sky by GE Aviation Systems (UK) and GE Global Research Munich as participants in the High Temperature Survival Electronic

Devices for Engine Control Systems (HIGHTECS) project working with Oxford University Materials.

The HIGHTECS design concept was to take the output from several onengine sensors (temperature probe, thermocouple, strain gauges, frequency) and carry out the signal conditioning on the sensor signals, multiplexing, analogue to digital conversion, and transmission of the data through a serial data bus on a single ASIC (Application Specific Integrated Circuit) [6]. The unit was designed to meet the environmental requirements of DO-160 for a helicopter engine, with the specific needs of operation at 200°C with a lifetime of 50,000 engine operating hours. Due to the temperature and lifetime requirements, and the current feasibility of SOI technology over SiC, the HIGHTECS ASIC was fabricated as a custom CMOS SOI device to be assembled on a ceramic hybrid carrier [6, 27]. The hybrid was assembled in a stainless steel enclosure, mounted on an aeroengine during tests on the ground, and due to the shorter cables needed in between the sensors and the electronics, it helps reducing the weight of the aeroengine by several kilograms [28].

#### References

- [1] B. Parmentier, O. Vermesan, and L. Beneteau, "Design of high temperature electronics for well logging applications," in Proc. International Conference on High Temperature Electronics (HiTEN), Oxford, United Kingdom, Jul. 2003, pp. 77–84.

- [2] B. Ohme and M. Larson, "Analog component development for 300°C sensor interface applications," in Proc. International Conference on High Temperature Electronics (HiTEC), Albuquerque, United States, May. 2012, pp. 1–17.

- [3] D. MacGugan, "DM300 a 300°C geothermal directional module development," in Proc. International Conference on High Temperature Electronics (HiTEC), Albuquerque, United States, May. 2012, pp. 293-300.

- [4] R. W. Johnson, J. L. Evans, P. Jacobsen, J. R. Thompson, and M. Christopher, "The changing automotive environment: High-temperature electronics," IEEE Trans. Electron. Packag. Manuf., vol. 27, pp. 164-176, Jul. 2004.

- [5] Boeing. (2014, Sep.) Current market outlook 2013–2032. [Online]. Available: www.boeing.com/boeing/commercial/cmo/

- [6] L. Stoica, V. Solomko, T. Baumheinrich, R. D. Regno, R. Beigh, S. Riches, I. White, G. Rickard, and P. Williams, "Design of a high temperature signal conditioning ASIC for engine control systems HIGHTECS," in *Proc. IEEE International Symposium on Circuits and Systems*, Melbourne, Australia, May. 2014, pp. 2117–2120.

- [7] J. D. Cressler and H. A. Mantooth, *Extreme Environment Electronics*. CRC Press, 2012.

- [8] D. Vanhoenacker-Janvier, M. E. Kaamouchi, and M. S. Moussa, "Silicon-on-insulator for high-temperature applications," *IET Circuits Devices Syst.*, vol. 2, pp. 151–157, Feb. 2008.

- [9] G. Shahidi, "Mainstreaming of the SOI technology," *Proceedings SPIE Microelectronic Device Technology III*, vol. 3881, Oct. 1999.

- [10] P. Francis, A. Terao, B. Gentinne, D. Flandre, and J.-P. Colinge, "SOI technology for high-temperature applications," in *Proc. IEDM Tech. Dig.*, San Francisco, United States, Dec. 1992, pp. 13.5.1–13.5.4.

- [11] D. Flandre, A. Nazarov, and P. Hemment, Eds., *Science and Technology of Semiconductor-On-Insulator Structures and Devices Operating in a Harsh Environment*. Dordrecht, The Netherlands: Kluwer Academic Publishers, 2005.

- [12] K. Grella, S. Dreiner, H. Vogt, and U. Paschen, "Reliability of CMOS Silicon-in-Insulator for use at 250°C," *IEEE Trans. Device Mater. Rel.*, vol. 14, pp. 21–29, Mar. 2014.

- [13] J. Eggermont, D. D. Ceuster, D. Flandre, B. Gentinne, P. Jespers, and J. Colinge, "Design of SOI CMOS operational amplifiers for applications up to 300°C," *IEEE J. Solid-State Circuits*, vol. 31, pp. 179–186, Feb. 1996.

- [14] D. Flandre, S. Adriaensen, A. Afzalian, J. Laconte, D. Levacq, C. Renaux, L. Vancaillie, J. Raskin, L. Demeus, P. Delatte, V. Dessard, and G. Picun, "Intelligent SOI CMOS integrated circuits and sensors for heterogeneous environments and applications," in *Proc. IEEE Sensors*, Orlando, United States, Jun. 2002, pp. 1407–1412.

- [15] J. O'Connor, J. Tsang, and J. McKitterick, "225°C high temperature silicon-on-insulator (SOI) ASICs for harsh environments," in *Proc. IEEE International Workshop for Integrated Power Packaging (IWIPP)*, Chicago, United States, Sep. 1998, pp. 2–5.

- [16] H. Kappert, N. Kordas, S. Dreiner, U. Paschen, and R. Kokozinski, "High temperature SOI CMOS technology and circuit realization for

- applications up to 300°C," in *Proc. IEEE International Symposium on* Circuits and Systems, Lisbon, Portugal, May. 2015, pp. 1162–1165.

- [17] L. Demeus, V. Dessard, A. Viviani, S. Adriaensen, and D. Flandre, "Integrated sensor and electronic circuits in fully depleted SOI technology for high-temperature applications," IEEE Trans. Ind. Electron., vol. 48, pp. 272–280, Apr. 2001.

- [18] F. Silveira, D. Flandre, and P. G. A. Jespers, "A gm/Id based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA," IEEE J. Solid-State Circuits, vol. 31, pp. 1314–1319, Sep. 1996.

- [19] J. Watson, "An ultra-low noise instrumentation amplifier designed for high temperature applications," in Proc. International Conference on High Temperature Electronics (HiTEC), Albuquerque, United States, May. 2012, pp. 82–86.

- [20] A. Schmidt, H. Kappert, and R. Kokozinski, "High temperature analog circuit design in PD-SOI CMOS technology using reverse body biasing," in Proc. IEEE 39th European Solid-State Circuit Conference, Bucharest, Romania, Sep. 2013, pp. 359–362.

- [21] P. Neudeck, D. Spry, L. Chen, G. Beheim, R. Okojie, C. Chang, R. Meredith, T. Ferrier, L. Evans, M. Krasowski, and N. Prokop, "Stable electrical operation of 6HSiC JFETs and ICs for thousands of hours at 500°C," *IEEE Electron Device Lett.*, vol. 29, pp. 456–459, May. 2008.

- [22] R. Ghandi, C.-P. Chen, L. Yin, X. Zhu, L. Yu, S. Arthur, F. Ahmad, and P. Sandvik, "Silicon carbide integrated circuits with stable operation over a wide temperature range," IEEE Electron Device Lett., vol. 35, pp. 1206-1208, Dec. 2014.

- [23] S. Garverick, C.-W. Soong, and M. Mehregany, "SiC JFET integrated circuits for sensing and control at temperatures up to 600°C," in *Proc*. *IEEE Energytech*, Cleveland, United States, May. 2012, pp. 1–6.

- [24] J. Watson and G. Castro, "A review of high-temperature electronics technology and applications," Journal of Material Science: Materials in Electronics, vol. 26, pp. 9226-9235, Jul. 2015.

- [25] D. Flandre, L. Demeus, V. Dessard, A. Viviani, B. Gentinne, and J. P. Eggermont, "Design and application of SOI CMOS OTAs for hightemperature environments," in Proc. IEEE 24th European Solid-State Circuit Conference, The Hague, The Netherlands, Sep. 1998, pp. 404-407.

- [26] CleanSky. (2013, Oct.) Clean Sky2 overview of the proposed programme. [Online]. Available: http://www.cleansky.eu/content/document/cleansky-2-overviewproposed-programme

- [27] S. Riches, C. Warn, K. Cannon, G. Rickard, and L. Stoica, "Design and assembly of high temperature distributed aero-engine control system demonstrator," in *Proc. International Conference on High Temperature Electronics (HiTEC)*, Albuquerque, United States, May. 2014.

- [28] J. Rigaud and L. Stoica, "Turbomeca TCON," Oct. 2015, Meeting Notes.

# **PART II**

# **Development of Multi-Sensor Data Acquisition System**

Lucian Stoica, Valentyn Solomko, Ozan Iskilibli, Renato Del Regno, Reece Beigh, Thorsten Baumheinrich, Steve Riches, Colin Johnston, Geoff Rickard, Paul Williams

# **Outline of System**

#### 3.1 High Level Input Specification

A high level draft technical specification was provided by Turbomeca as the basis for the design of the high temperature electronics platform. The design concept was to take the output from several on-engine sensors (temperature probe, thermocouple, strain gauges, frequency), carry out the signal conditioning on the sensor signals, multiplexing, analogue to digital conversion and transmission of the data through a serial data bus. The DC power supply for the unit is provided by the FADEC. The unit has to meet the environmental requirements of DO-160 for a helicopter engine, with the specific need to operate at 200°C, with short term operation at temperatures up to 250°C. The system service lifetime target is 50,000 engine flight hours.

## 3.2 Technology Assessment and Selection

A review of the options for the high temperature electronics to be considered for the HIGHTECS module was carried out. This review included the availability of devices and components, the status of high temperature electronics packaging technology, an assessment of the technology maturity, potential failure modes and a review of accelerated life tests to predict service life.

For the electronic devices and components, an ASIC based on a Silicon-on-Insulator (SOI) semiconductor manufactured using the X-FAB 1 µm SOI foundry in Germany was selected to perform the analogue signal conditioning, multiplexing, ADC (Analogue to Digital Conversion), logic control and serial data transmission. The circuit also required additional high temperature voltage regulators, a clock oscillator, capacitors, precision resistors and lightning protection devices, all of which should be capable of meeting the high temperature operating conditions. The review highlighted the limitations of ceramic based capacitors and Si based lightning protection

devices. High temperature silicon capacitors produced by Ipdia - France became available during the course of the project and development SiC transient voltage suppressors, which have potential for operation above 150°C were evaluated.

The status of high temperature electronics packaging for the HIGHTECS module was also reviewed, covering materials and processes for die attach and wire bonding, attachment of passive devices and packaged components to ceramic substrates and connections for external inputs/outputs to/from the HIGHTECS module. An assessment of potential failure modes relating to the packaging technology options was undertaken, which highlighted areas to focus on within the testing programme.

The review covered the use of accelerated reliability tests to predict service life. In conclusion, the following tests were defined to address the concerns for the reliability of the electronics components and packaging technology operating at high temperature:

- Long term temperature storage at +250°C to assess the long term degradation at temperature

- Rapid thermal cycling from -40°C to +225°C to represent the stresses endured during the typical flight profile

- Vibration at room temperature and at 200°C to investigate whether the combined effect of vibration and temperature accelerates any failure mechanism

Tests have been carried out to investigate these factors on a SOI test chip.

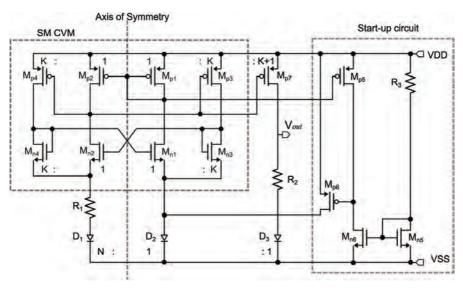

#### 3.3 Definition of Prototype System

The design principle of the HIGHTECS module was based on a custom silicon on insulator (SOI) ASIC being used for the majority of the signal processing and conditioning from the range of sensors (i.e. temperature probe, strain gauges, thermocouple, frequency), multiplexing, analogue to digital conversion and transmission of data through an ARINC 429 databus. The ASIC was then integrated with a high temperature external clock and packaged onto a ceramic hybrid circuit. This hybrid circuit was assembled in a Kovar package together with development high temperature SiC based transient voltage suppressors, which was hermetically sealed in an inert gas atmosphere. The Kovar package was then mounted into a stainless steel enclosure containing high temperature connectors and EMI shielding.

#### 3.3.1 HIGHTECS SOI ASIC