# Defects in Hardened Latches: Analysis, Detection and Evaluation

| 著者       | Ma Ruijun                        |  |  |

|----------|----------------------------------|--|--|

| その他のタイトル | 耐ソフトエラーラッチにおける欠陥の分析、検出及          |  |  |

|          | び評価に関する研究                        |  |  |

| 学位授与年度   | 令和4年度                            |  |  |

| 学位授与番号   | 17104甲情工第371号                    |  |  |

| URL      | http://doi.org/10.18997/00009010 |  |  |

# Defects in Hardened Latches: Analysis, Detection and Evaluation

(耐ソフトエラーラッチにおける欠陥の分析、 検出及び評価に関する研究)

MA RUIJUN

#### **Abstract**

The development of modern integrated circuits (ICs) has greatly changed the life of humankind. Nowadays, ICs are also indispensable to mission-critical applications, such as medical devices, autonomous cars, aircraft navigating systems, and satellites. The reliability of these mission-critical applications is a major concern.

A soft-error occurring in an IC is a severe threat to its reliability, especially for mission-critical applications. The continuous trend of shrinking technology feature sizes makes modern ICs more and more vulnerable to soft-errors. Soft-errors are caused by radiation particles striking an IC and generating current pulses to disturb its functionality. A soft-error can cause data corruption and may eventually lead to system failures. If a soft-error occurs in an operational medical device during surgery, it may cause a malfunction of this device and interrupt the surgery process. A soft-error may change the control data of an autonomous car, which may lead to an accident. A soft-error may corrupt the aircraft navigating systems. No one would take the chance to let it happen even though malfunctions caused by soft-errors can be solved by resetting these devices. Because reset takes time and severe results may happen during the resetting. If a soft-error causes a malfunction in the control system of a satellite, it may not be able to maintain its height and eventually burn up as it falls into the Earth's atmosphere. Hence, it is important to protect ICs from soft-errors.

Many soft-error tolerance methods have been proposed to protect ICs against soft-errors. In an IC, memory elements and storage elements (e.g., latches and flip-flops) are the most vulnerable to soft-errors, and data stored in them are crucial to the operation of a circuit. Error correction codes (ECCs) can be used to protect memories. Register-level soft-error tolerance methods can be used to detect soft-errors in latches by using parity-checking and correct them by resetting. Hardened designs protect latches against soft-errors by using redundant feedback loops to store the same input data and using a voter to select the correct output. The advantage of using hardened designs is that they can prevent soft-errors from reaching outputs while ECCs and register-level soft-error tolerance methods must detect soft-errors and then correct them by restoring the data. For protecting storage elements in mission-critical applications, hardened latch design is the best option because it has high reliability and can save the resetting time. Many state-of-the-art hardened latch designs have been proposed to tolerate soft-errors and they are believed to have good soft-error tolerability.

Defects (physical flaws due to imperfect production (production defects) and physical changes caused by aging effects after a long operation time (aging-related defects)) can also cause a malfunction of a circuit and cause a system failure eventually. Different from the temporal state change of a circuit caused by soft-errors, defects are permanent damages to a circuit and can disturb the behavior of a circuit from its desired manner. Defects in storage elements should be detected to make sure a system/device

operating correctly and stably. Scan test is a commonly used defect detection method, which connects reconfigured storage elements to form a shift register with external access and the internal states of these storage elements can be easily controlled and checked.

However, the impact of defects on existing state-of-the-art hardened latch design has not been considered. This impact requires consideration because added redundancy in hardened latch designs can not only mask soft-errors but also mask the effects of defects and it can lead to two serious problems:

**Problem-1** (**Low Testability**): Production defects in hardened latch designs are difficult to detect with conventional scan tests, in which the observability (an important metric to evaluate a circuit's testability) of defects in hardened latch designs can be greatly reduced. Therefore, existing state-of-the-art hardened latches have low observability and thus low testability. Furthermore, defects that escaped the production test (undetected defects) may become more and more serious and cause a system failure eventually.

**Problem-2** (Low Soft-Error Tolerability): Undetected defects and aging-related defects can make hardened latch designs vulnerable to soft-errors while defect-free ones do not. The soft-error tolerability of hardened latch designs may be compromised by undetected defects or aging-related defects.

This research is the first to consider **Problem-1** of low testability of hardened latches and **Problem-2** of defects reducing the reliability of hardened latches. Furthermore, this research is the first to propose a comprehensive solution to solve these two problems with the following five major contributions:

**Contribution-1:** A first-of-its-kind metric for quantifying the impact of defects on hardened latches, called Post-Test Vulnerability Factor (*PTVF*). It is used to analyze the residual soft-error tolerability of hardened latches after testing. **Problem-2** is solved by this first major contribution.

**Contribution-2:** A novel design called Scan-Test-Aware Hardened Latch (STAHL) that provides the highest defect coverage in comparison with all existing hardened latches. **Problem-1** is solved by using STAHL to build a scan cell to perform a scan test.

**Contribution-3:** A novel scan test procedure is proposed to solve **Problem-1** by fully testing the STAHL-based scan cell.

**Contribution-4:** A novel High-Performance Scan-Test-Aware Hardened Latch (HP-STAHL) design can also solve **Problem-1** and has similar defect coverage as STAHL but has lower power consumption and higher propagation speed.

**Contribution-5:** A novel scan test procedure is proposed to fully test the HP-STAHL-based scan cell to solve **Problem-1**.

Comprehensive simulation results demonstrate the accuracy of the PTVF metric

and the effectiveness of the STAHL-based scan test and HP-STAHL-based scan test. As the first comprehensive study bridging the gap between hardened latch designs and IC testing, the findings of this research are expected to significantly improve the soft-error-related reliability of IC designs for mission-critical applications. Furthermore, the two proposed hardened latches and the scan test procedures can not only be used to detect defects after production but also can be applied to detect aging-related defects in the field through performing built-in self-test (BIST).

In Chapter 1, an example is introduced to indicate **Problem-1** and **Problem-2**. Chapter 2 shows the background information of soft-errors and defects. Chapter 3 shows some typical soft-error mitigation methods and details of a scan test. Chapter 4 describes the detailed information of *PTVF* (**Contribution-1**). Chapter 5 shows the structure of STAHL (**Contribution-2**) and Chapter 6 shows the scan test procedure of testing the STAHL-based scan cell (**Contribution-3**). Chapter 7 shows the structure of HP-STAHL (**Contribution-4**) and Chapter 8 shows the scan test procedure of testing the HP-STAHL-based scan cell (**Contribution-5**). Chapter 9 shows the experimental results of comparing STAHL and HP-STAHL with state-of-the-art hardened latch designs. Chapter 10 concludes this thesis.

## Contents

| 1. | Introduction | 1                                                | 11 |

|----|--------------|--------------------------------------------------|----|

|    | 1.1. Prob    | olem Statement                                   | 11 |

|    | 1.2. Rese    | earch Objectives                                 | 14 |

|    | 1.3. Thes    | sis Organization                                 | 15 |

|    | 1.4. Sum     | ımary                                            | 16 |

| 2. | Background   | 1                                                | 17 |

|    | 2.1. Soft-   | -Error                                           | 17 |

|    | 2.1.1.       | Soft-Error Mechanism                             | 17 |

|    | 2.1.2.       | Sources of Radiation Particles                   | 18 |

|    | 2.1.3.       | Soft-Errors Induced Incidents                    | 19 |

|    | 2.1.4.       | Soft-Error Classification                        | 20 |

|    | 2.1.5.       | Soft-Error Rate (SER) Definition and Calculation | 20 |

|    | 2.2. Defe    | ect                                              | 22 |

|    | 2.2.1.       | Production Defect                                | 22 |

|    | 2.2.2.       | Aging-Related Defect                             | 23 |

|    | 2.2.3.       | Radiation-Induced Defect                         | 23 |

|    | 2.3. Faul    | t Model                                          | 24 |

|    | 2.4. Defe    | ect Coverage                                     | 26 |

|    | 2.5. Sum     | mary                                             | 27 |

| 3. | Related Wor  | rks                                              | 28 |

|    | 3.1. Soft-   | -Error Mitigation                                | 28 |

|    | 3.1.1.       | Error Correction Code                            | 28 |

|    | 3.1.2.       | System-Level Mitigation                          | 28 |

|    | 3.1.3.       | Register-Level Mitigation                        | 29 |

|    | 3.1.4.       | Hardened Latch Design                            | 29 |

|    | 3.2. Defe    | ect Detection                                    | 31 |

|    | 3.2.1.       | Functional Test                                  | 31 |

|    | 3.2.2.       | Scan Design                                      | 32 |

|    | 3.2.3.       | Scan Test                                        | 32 |

|    | 3.3. The     | Importance of This Research                      | 34 |

|    | 3.4. Sum     | nmary                                            | 34 |

| 4. | Post-Test Vu | ulnerability Factor (PTVF)                       | 36 |

|    | 4.1. Defi    | inition of PTVF                                  | 36 |

|    | 4.2. Calc    | culation of PTVF                                 | 37 |

|    | 4.3. Sum     | ımary                                            | 38 |

| 5. | Scan-Test-A  | Aware Hardened Latch (STAHL)                     | 39 |

|    |              | cture of STAHL                                   |    |

|    | 5.2. Fund    | ctional (Hardened) Mode of STAHL                 | 40 |

|    | 5.3. Shift   | t Mode of STAHL                                  | 41 |

|    | 5.4 Sum      | nmary                                            | 42 |

| 6.   | Scan Test Based on STAHL |                                                        | 43 |

|------|--------------------------|--------------------------------------------------------|----|

|      | 6.1.                     | Scan Chain Structure Based on STAHL                    | 43 |

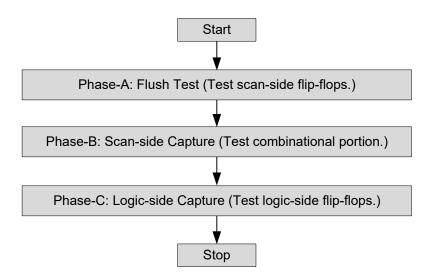

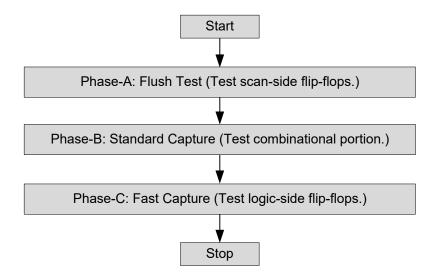

|      | 6.2.                     | Test Procedure Flow                                    | 45 |

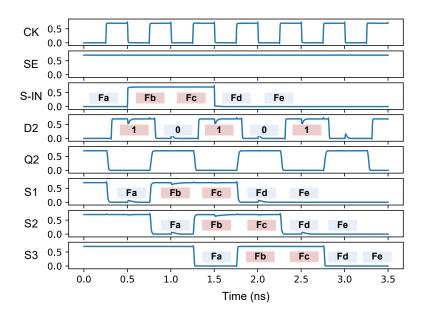

|      | 6.3.                     | Phase-A: Flush Test                                    | 46 |

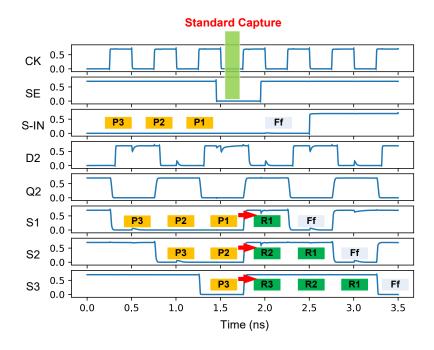

|      | 6.4.                     | Phase-B: Scan-side Capture                             | 47 |

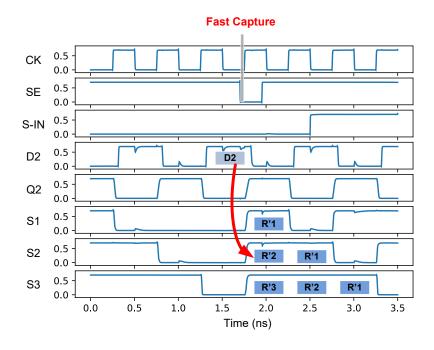

|      | 6.5.                     | Phase-C: Logic-side Capture                            | 48 |

|      | 6.6.                     | Full Test Procedure                                    | 49 |

|      | 6.7.                     | Summary                                                | 50 |

| 7.   | High                     | Performance Scan-Test-Aware Hardened Latch (HP-STAHL)  | 51 |

|      | 7.1.                     | Structure of HP-STAHL                                  | 51 |

|      | 7.2.                     | Functional (Hardened) Mode of HP-STAHL                 | 52 |

|      | 7.3.                     | Shift Mode of HP-STAHL                                 | 53 |

|      | 7.4.                     | Summary                                                | 54 |

| 8.   | Scan                     | Test Based on HP-STAHL                                 | 55 |

|      | 8.1.                     | Scan Chain Structure Based on HP-STAHL                 | 55 |

|      | 8.2.                     | Test Procedure Flow                                    | 56 |

|      | 8.3.                     | Phase-A: Flush Test                                    | 57 |

|      | 8.4.                     | Phase-B: Standard Capture                              | 58 |

|      | 8.5.                     | Phase-C: Fast Capture                                  | 59 |

|      | 8.6.                     | Full Test Procedure                                    | 60 |

|      | 8.7.                     | Summary                                                | 61 |

| 9.   | Expe                     | rimental Evaluation                                    | 62 |

|      | 9.1.                     | Basic Statistics of Latch Cells                        | 62 |

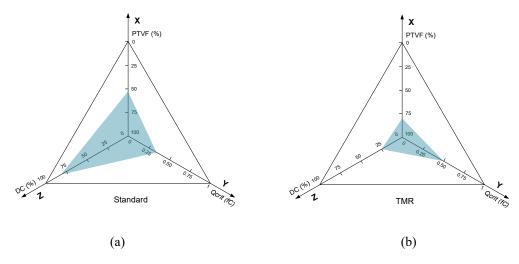

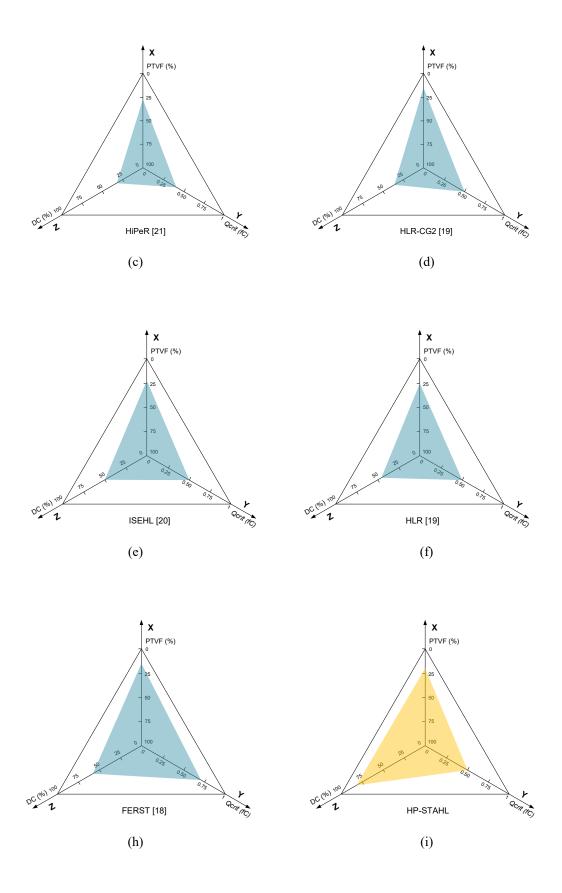

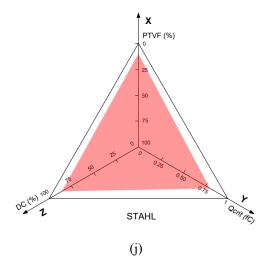

|      | 9.2.                     | Soft-Error Tolerability Evaluation                     | 64 |

|      | 9.3.                     | Defect Coverage and PTVF of Single Latches             | 67 |

|      | 9.4.                     | Defect Coverage of Latch Based Scan Cells in Scan Test | 69 |

|      | 9.5.                     | Overall Comparison                                     | 70 |

|      | 9.6.                     | Applicability Comparison                               | 73 |

|      | 9.7.                     | Summary                                                | 73 |

| 10.  | Conc                     | lusions and Future Works                               | 75 |

|      | 10.1.                    | Conclusions                                            | 75 |

|      | 10.2.                    | Future Works                                           | 76 |

|      | 10.3.                    | Summary                                                | 76 |

| Bib  | liograp                  | ohy                                                    | 78 |

| Ack  | nowle                    | dgements                                               | 84 |

| List | of Pul                   | dications                                              | 85 |

## **List of Tables**

| Table 3-1 | C-element truth table                        | 29 |

|-----------|----------------------------------------------|----|

| Table 9-1 | Basic statistics of latch cells              | 63 |

| Table 9-2 | Soft-error hardness of latch cells           | 67 |

| Table 9-3 | Defect coverage (DC) and PTVF of latch cells | 68 |

| Table 9-4 | Defect coverage (DC) of scan cells           | 70 |

| Table 9-5 | Overall comparison results                   | 72 |

| Table 9-6 | Applicability comparison results             | 73 |

# **List of Figures**

| Figure 1.1 | The impact of defects1                                                                     | 3  |

|------------|--------------------------------------------------------------------------------------------|----|

| Figure 1.2 | Thesis organization1                                                                       | 5  |

| Figure 2.1 | Soft-error mechanism                                                                       | 8  |

| Figure 2.2 | Soft-error vulnerability (SEV) calculation flow                                            | 1  |

| Figure 2.3 | Stuck-at fault models. 2                                                                   | 4  |

| Figure 2.4 | Transistor fault models                                                                    | 5  |

| Figure 2.5 | Wire short and open fault models                                                           | 5  |

| Figure 2.6 | Defect coverage (DC) calculation flow                                                      | 7  |

| Figure 3.1 | Structure of C-element                                                                     | 9  |

| Figure 3.2 | Triple modular redundancy (TMR) latch                                                      | 0  |

| Figure 3.3 | FERST [18] latch                                                                           | 0  |

| Figure 3.4 | HLR [19] latch                                                                             | 1  |

| Figure 3.5 | Functional test                                                                            | 2  |

| Figure 3.6 | Scan chain example                                                                         | 3  |

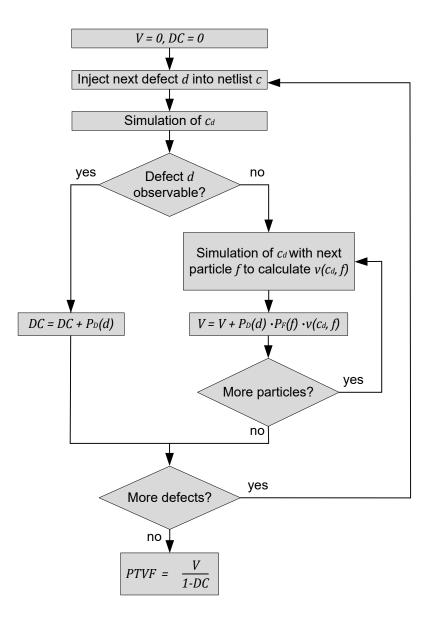

| Figure 4.1 | PTVF calculation flow                                                                      | 8  |

| Figure 5.1 | Structure of the proposed STAHL                                                            | 9  |

| Figure 5.2 | SE = 0: functional (hardened) mode                                                         | 0  |

| Figure 5.3 | SE = 1: shift mode4                                                                        | 1  |

| Figure 6.1 | STAHL-based scan cell                                                                      | 3  |

| Figure 6.2 | STAHL-based scan chain                                                                     | 4  |

| Figure 6.3 | Test procedure flow4                                                                       | 5  |

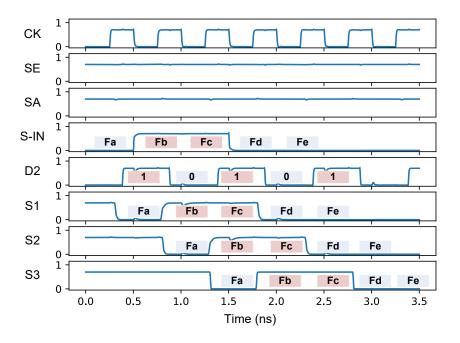

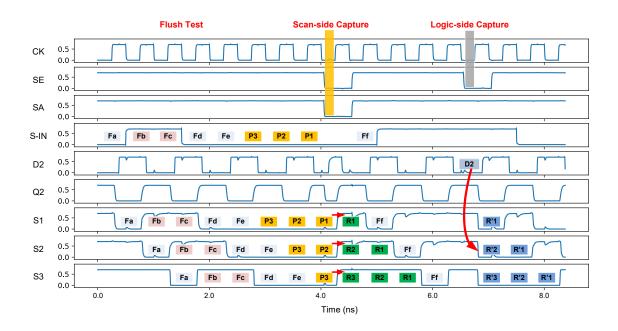

| Figure 6.4 | SE=1 and $SA=1$ : a test pattern of $FaFbFcFdFe=01100$ flushes through the scan            | l- |

| side fl    | lip-flops4                                                                                 | 6  |

| Figure 6.5 | SE = 0 and $SA = 0$ : the next rising clock captures R1R2R3 = 111 (test response of        | f  |

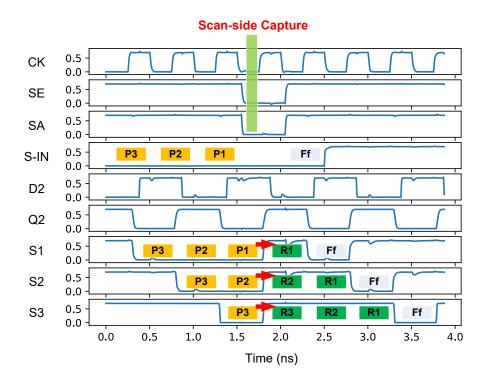

| the pa     | ttern P1P2P3 = 000)4                                                                       | 7  |

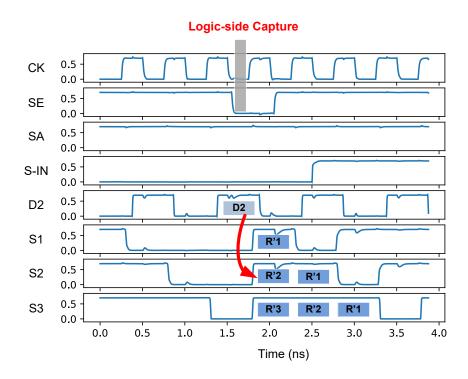

| Figure 6.6 | SE = 0 and $SA = 1$ : the next rising clock captures $D2 = 1$ (test response to the value) | e  |

| stored     | in the logic-side flip-flop of Scan Cell 2)4                                               | 8  |

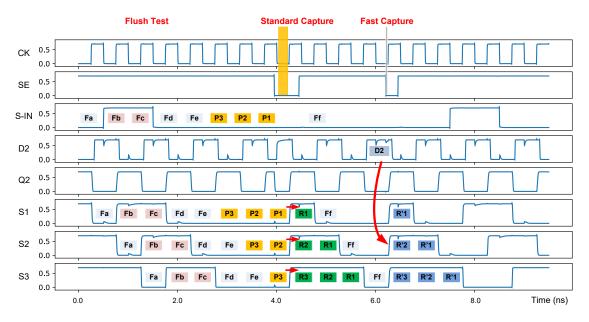

| •          | Test procedure of the STAHL-based scan chain                                               |    |

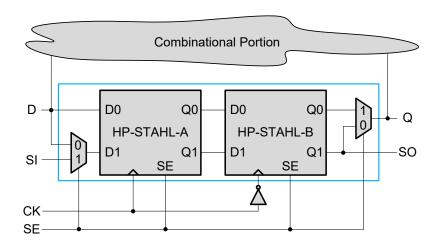

| Figure 7.1 | Structure of HP-STAHL                                                                      | 1  |

| Figure 7.2 | SE = 0: functional (hardened) mode.                                                        | 2  |

| Figure 7.3 | SE = 1: shift mode5                                                                        | 3  |

| Figure 8.1 | HP-STAHL-based scan-cell                                                                   | 5  |

| Figure 8.2 | HP-STAHL-based scan chain. 5                                                               | 6  |

| •          | Test procedure flow5                                                                       |    |

|            | SE = 1: a test pattern of FaFbFcFdFe = 01100 flushes through the scan-side flip            |    |

| flops      | 5                                                                                          | 7  |

| •          | SE = 0: the next rising clock captures $R1R2R3 = 111$ (test response of the patter         |    |

| P1P2I      | 23 = 000)                                                                                  | 8  |

| Figure 8.6 | SE = 0: the next rising clock captures $D2 = 1$ (test response to the value stored in the  | e  |

| logic-     | side flin-flon of Scan Cell 2)                                                             | a  |

| Figure 8.7 | Test procedure of the HP-STAHL-based scan chain | 60 |

|------------|-------------------------------------------------|----|

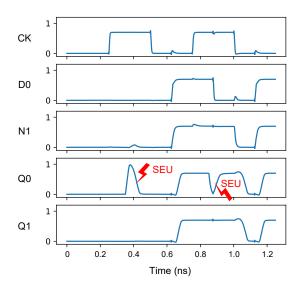

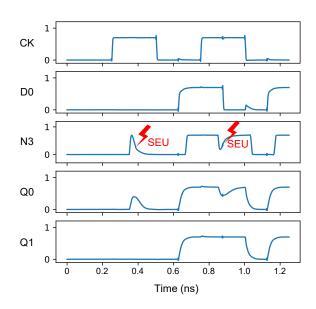

| Figure 9.1 | Impact of SEUs on Q0 of STAHL.                  | 65 |

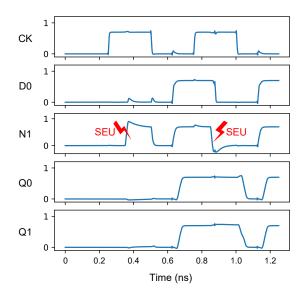

| Figure 9.2 | Impact of SEUs on N1 of STAHL                   | 65 |

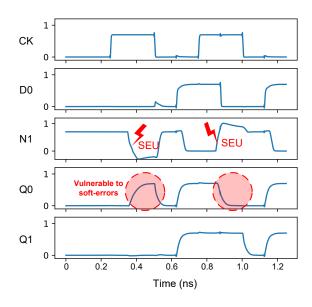

| Figure 9.3 | Impact of SEUs on N1 of HP-STAHL                | 66 |

| Figure 9.4 | Impact of SEUs on N3 of HP-STAHL                | 66 |

| Figure 9.5 | Overall comparison of latch cells.              | 72 |

#### **Abbreviations**

IC Integrated Circuit

CUT Circuit Under Test

DUT Device Under Test

VLSI Very-Large-Scale-Integration

LSI Large-Scale-Integration

FinFET Fin Field-Effect Transistor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

GND Ground

VDD Supply Voltage

DICE Dual Interlocked Storage Cell

TMR Triple Modular Redundancy

SPICE Simulation Program with Integrated Circuit Emphasis

FL Feedback Loop

DFT Design-for-Test

PTVF Post-Test Vulnerability Factor

STAHL Scan-Test-Aware Hardened Latch

HP-STAHL High Performance Scan-Test-Aware Hardened Latch

SER Soft-Error Rate

SEB Single-Event Burnout

SEL Single-Event Latchup

SET Single-Event Transient

SEU Single-Event Upset

DDD Displacement Damage Dose effect

TID Total Ionizing Dose effect

SNU Single-Node Upset

MNU Multiple-Node Upset

TVF Timing Vulnerability Factor

AVF Architectural Vulnerability Factor

SEV Soft-Error Vulnerability

LELE Litho-Etch-Litho-Etch

*I<sub>DDQ</sub>* Quiescent Power Supply Current

DC Defect Coverage

ECC Error Correction Code

NAND Not-AND gate

XOR Exclusive-OR gate

CE C-Element

SE Scan-Enable

SA Scan-Apply

CK Clock

SI Scan-In

SO Scan-Out

SRAM Static Random-Access Memory

TG Transmission Gate

MUX Multiplexer

PDP Power-Delay Product

$\label{eq:decomposition} \mathsf{DPQP} \qquad \qquad \mathsf{DC\text{-}PTVF\text{-}} Q_{crit} \ \mathsf{Product}$

BIST Built-In Self-Test

#### 1. Introduction

#### 1.1. Problem Statement

The shrinking of transistor feature sizes continues for decades since the famous Moore's Law was released [1]. A smaller feature size allows for manufacturing a smaller transistor as well as the integration of more transistors on a chip to achieve more functionalities. For a given wafer size, a smaller technology feature size means more chips can be manufactured on a wafer and IC foundries can earn more profits since the whole wafer is processed in the same steps.

A smaller technology feature size usually comes with a smaller supply voltage. Because of the reduction of geometry sizes, a smaller supply voltage is enough to drive the gate of a transistor to form a propagation channel between source and drain. Due to this supply voltage reduction, the amount of charge (critical charge) that defines the state of a storage element becomes smaller, making a storage element more and more vulnerable to soft-errors, which raises a great threat to the reliability of modern circuits.

Soft-errors are caused by particles (such as heavy ions, alpha particles, muons, protons, neutrons, and electrons) striking the IC. The strikes can generate current pulses and possibly disrupt the states of storage elements [2-7]. Soft-errors can change data or disrupt a computer system, thus causing an erroneous operation. The impact of soft-errors depends on many factors, such as the angle of the strike, supply voltages, technology nodes, the energy of the particle, and process variations [8, 9]. A fin field-effect transistor (FinFET) shows lower sensitivity to radiation-induced soft-errors than a planer metal-oxide-semiconductor field-effect transistor (MOSFET) because of its smaller radiation-sensitive volumes at drain junctions [10]. However, a FinFET is still vulnerable to radiation-induced soft-errors [10, 11].

Soft-errors impact not only systems in high-radiation environments, such as aerospace [5, 6, 12], but also systems or devices at the sea-level [13, 14]. Normally, the magnetosphere of earth can prevent most outer space radiation particles since 92% of them are protons and 6% of them are alpha particles [26]. The magnetosphere can make almost all of them fall into the poles of the earth. However, the activity of the sun (such as sunspots and solar flares) can bring a large amount of high energetic and accelerated plasmas to change the magnetosphere. As a result, a large number of radiation particles can enter the atmosphere of the earth and have interactions with the atoms in the atmosphere to generate cascade particles. These entering particles and the following generated cascade particles may hit operating devices or systems on earth or satellites in low earth orbit (LEO) [5, 6]. With the reduction of technology feature sizes and supply voltages, these radiation particles can easily change the state of a circuit and interrupt its

functional working. If a soft-error causes a malfunction of an electronic device like a personal computer, this malfunction can be solved by resetting this device since a soft-error will not cause permanent damage. However, if a soft-error causes a malfunction of mission-critical applications (such as medical devices, autonomous cars, the navigating systems of aircraft, and satellites), it may lead to a catastrophic result. Hence, it is important to protect chips in mission-critical applications against the impact of soft-errors to maintain high reliability.

Many soft-error tolerance approaches have been proposed to protect circuits from the impact of soft-errors. Error correction codes (ECCs) can be used to protect memory cells (such as SRAM and DRAM) [50-51]. A register-level soft-error tolerance approach can be used to detect soft-errors in latches [60]. Hardened designs [15-25] can be used to protect storage elements (such as latches or flip-flops) by adding redundancy. This research focuses on using hardened latch designs to tolerate soft-errors for the following three reasons:

- (1) Sequential elements, such as latches and flip-flops, are the most susceptible to soft-errors in logic circuits [7].

- (2) A flip-flop is commonly constructed of two latches. Tolerating soft-errors in latches can reduce the soft-error vulnerability of flip-flops as well.

- (3) Hardened latch design is an effective approach that can prevent soft-errors from reaching outputs by using redundant feedback loops to store the same input data and using a voter to select the correct output. Other existing soft-error tolerance methods must detect and then correct soft-errors while protecting sequential elements. For mission-critical applications, a hardened latch design is a good option to protect sequential elements while compared with other soft-error tolerance methods.

If a soft-error occurred in a latch and changes the internal state of this latch, this soft-error is called a single-event upset (SEU). To tolerate SEUs, many hardened latches [15-25] have been proposed by adding redundancy to their structures. The latch in [15] adds transistors at feedback loops to prevent SEUs from propagating. This latch has fewer transistors than most other hardened latches. The dual interlocked storage cell (DICE) [16] can tolerate soft-errors by its interlocked structure. Triple modular redundancy (TMR) uses three standard latches to store the same data and uses a voter circuit to select the majority as its output. The hardened latches in [17-21] store logic values in multiple feedback loops and use a voter circuit (such as C-element) to select the correct output. The design in [22] can tolerate SEUs by its dual-modular structure. The design in [4] can be used to tolerate multiple-node upsets (MNUs). However, there are two major problems with these state-of-the-art hardened latches as follows:

**Problem-1** (Low Testability): Observability, the ability to obtain a circuit's internal state by checking its outputs, is an important metric to evaluate a circuit's testability. Some production defects within hardened latches cannot be observed at their

outputs. This is because the impacts of these production defects are masked by the same circuitry designed to mask SEUs. Therefore, hardened latches have low observability and thus low testability. Furthermore, undetected defects may become more and more serious and cause a system failure eventually.

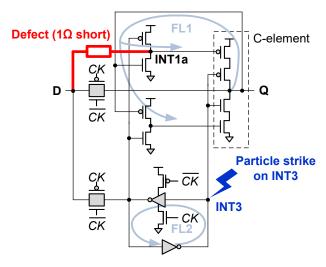

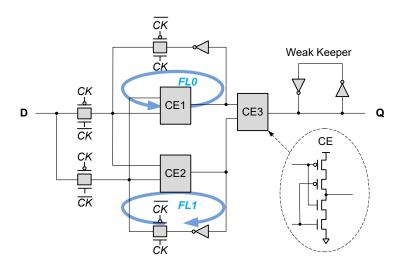

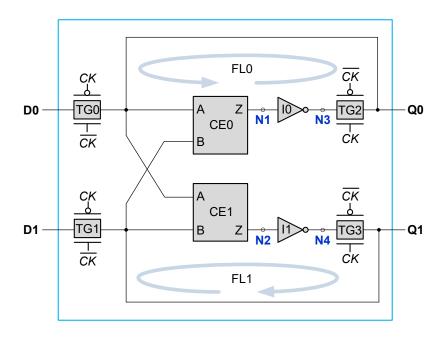

(a) HiPeR [21] with a short defect

(b) SPICE simulation

Figure 1.1 The impact of defects.

Figure 1.1 illustrates this problem. Figure 1.1 (a) shows a typical hardened latch (HiPeR) [21], which has two feedback loops FL1 and FL2. Suppose that a short defect exists between D and INT1a due to imperfect production. The SPICE simulation result in Figure 1.1 (b) shows that this defective latch still works functionally, and this defect cannot be observed. Undetected defects may lead to early-life failures. Furthermore, a

lower defect coverage of a hardened latch may lead to an overestimation of production quality.

**Problem-2** (Low Soft-Error Tolerability): Undetected defects and aging-related defects can make hardened latch designs vulnerable to soft-errors while defect-free ones do not. If a defect exists in a hardened latch, the hardened latch's soft-error tolerability may be reduced, making it more vulnerable to SEUs.

Consider the hardened latch shown in Figure 1.1 (a), which has an undetected short defect. Usually, when the node INT3 is hit by a particle, the change of state will be tolerated by the C-element and the output Q remains correct. However, the SPICE simulation in Figure 1.1 (b) shows that a particle strike on INT3 cannot be tolerated by this defective latch. This is because an input (INT1a) of the C-element is compromised by the short defect. Consequently, this defective hardened latch suffers from SEUs while a defect-free one does not.

#### 1.2. Research Objectives

This thesis focuses on improving the testability of hardened latch designs by addressing the above two problems (**Problem-1: Low Testability** and **Problem-2: Low Soft-Error Tolerability**) through the following five major contributions:

**Contribution-1** (*PTVF*): This research is the first to analyze the relationship between the soft-error tolerability of hardened latch designs and defects (**Problem-2**). A novel metric, called Post-Test Vulnerability Factor (*PTVF*), is proposed for quantifying the impact of defects on hardened latches. **Problem-2** is solved by using this *PTVF* metric to evaluate the impact of defects on hardened latches.

Contribution-2 (STAHL): To solve Problem-1, we introduce a novel Scan-Test-Aware Hardened Latch (STAHL) which is hardened against SEUs and at the same time has the highest defect coverage among all state-of-the-art hardened latch designs. Problem-1 is solved by using STAHL to build a scan cell to perform a scan test.

**Contribution-3 (An STAHL-based Scan Test):** Taking full advantage of STAHL's high testability requires some changes to the Design-for-Test (DFT) infrastructure. We propose a novel minimal-overhead scan design and a novel test procedure based on the STAHL-based scan chains to solve **Problem-1**.

**Contribution-4 (HP-STAHL):** To solve **Problem-1**, we also propose a novel High Performance Scan-Test-Aware Hardened Latch (HP-STAHL) design, which has similar defect coverage as the STAHL but costs lower power consumption and has a faster propagation speed by compromising part of its soft-error tolerability.

**Contribution-5 (An HP-STAHL-based Scan Test):** A novel scan test procedure is proposed to test HP-STAHLs to solve **Problem-1**.

#### 1.3. Thesis Organization

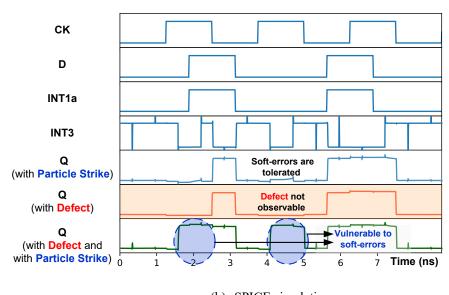

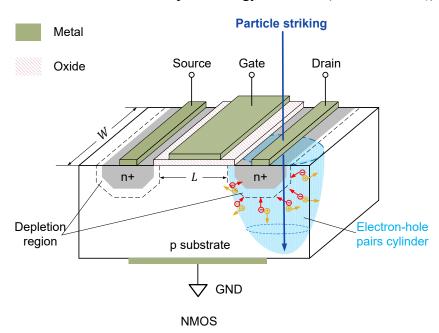

The organization of this thesis is shown in Figure 1.2, which includes 10 chapters. The first chapter introduces the target problem and contributions of this research.

Figure 1.2 Thesis organization.

Chapter 2 describes the background of this research, such as soft-error, soft-error rate (SER), defects, fault models, and defect coverage. Chapter 3 describes the related works of soft-error mitigation and defect detection. The *PTVF* metric is introduced in Chapter 4 for evaluating the residual soft-error tolerability of hardened latch designs after manufacturing. The Scan-Test-Aware Hardened Latch (STAHL) design is described in Chapter 5, including its structure as well as its operation details in both shift and functional modes. Chapter 6 shows the scan chain structure based on STAHLs and a novel test procedure for fully testing the STAHLs. Chapter 7 shows the High Performance Scan-Test-Aware Hardened Latch (HP-STAHL) design along with its structure and operation details. The scan chain based on HP-STAHL and its test procedure is shown in Chapter 8. Chapter 9 shows evaluation results and Chapter 10 concludes this thesis.

#### 1.4. Summary

This chapter introduces two problems that are caused by defects in hardened latches: Problem-1: Low Testability and Problem-2: Low Soft-Error Tolerability.

For solving these two problems, 5 major contributions are introduced in section 1.2. In **Contribution-1** (*PTVF*), This research is the first to find that defects can reduce the soft-error tolerability of hardened latch designs. A novel metric, called Post-Test Vulnerability Factor (*PTVF*), is proposed for quantifying the impact of defects on hardened latches. In **Contribution-2**, the first hardened latch design, Scan-Test-Aware Hardened Latch (STAHL), has high defect coverage and high soft-error tolerability. In **Contribution-3**, we propose a novel minimal-overhead scan design and a novel test procedure based on the STAHL-based scan chains to test STAHLs. In **Contribution-4**, a novel High Performance Scan-Test-Aware Hardened Latch (HP-STAHL) design is proposed. HP-STAHL has the same merits as STAHL but has lower power and delay. In **Contribution-5**, A novel scan test procedure is proposed to test HP-STAHLs.

Section 1.3 introduces the organization of this thesis.

### 2. Background

#### 2.1. Soft-Error

Soft-errors are caused by radiation particles striking ICs, which can temporally change the states of circuits but cause no physical damage. The following subsections show the basic knowledge of soft-errors.

#### 2.1.1. Soft-Error Mechanism

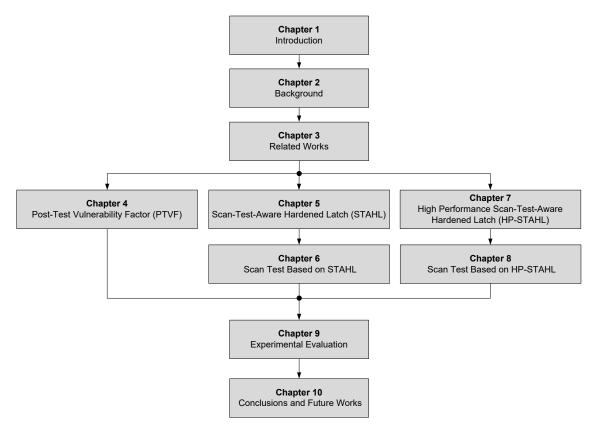

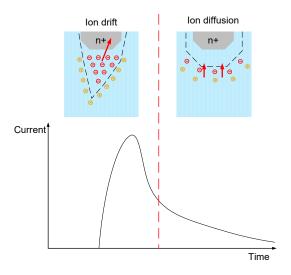

A soft-error is caused by a particle striking an OFF transistor and generating a current pulse to disturb the output results. Figure 2.1 (a) shows an NMOS transistor with a particle striking on its drain side p-n junction. The p substrate of this NMOS connects with the ground (GND). When this NMOS is in an OFF state, there is no current from drain to source because there is no channel beneath the oxide. The electrical field in the two depletion regions can prevent electrons from free propagating. When a particle strikes on this NMOS, it generates a cylinder of electron-hole pairs in this drain side p-n junction along the striking track. These generated electrons can be accumulated by the electrical field to generate a current pulse at the drain. Generating a pair of electron-hole in bulk silicon requires energy of 3.6 eV ( $1 \text{ eV} = 10^{-19} \text{ J}$ ) [47].

(a) Particle striking on an NMOS transistor.

(b) Particle striking generates a current pulse.

Figure 2.1 Soft-error mechanism.

Figure 2.1 (b) shows two phases of a particle striking: ion drift and ion diffusion. These generated electrons will be collected by the electrical field in the depletion region and then emerge from the drain to generate a current pulse. This is called ion drift and may last in the scale of picoseconds. Then, the electrical field in the drain side depletion region disappears when several electrons are collected. These residual ionized electrons and holes may temporally conduct the drain and GND, which features a temporary short between them. A diffusion process will follow the drift until all carriers diffuse away and the inner electrical field reestablish. This is called ion diffusion and it may last from a few picoseconds to hundreds of picoseconds [32].

This generated current pulse may disturb the state of a circuit to generate a softerror [2]. If this soft-error changes the state of a latch during its latching phase, this latch will continue to output the corrupted data until a new datum arrives. Hence, it is very important to protect latches from the impact of soft-errors.

#### 2.1.2. Sources of Radiation Particles

Radiation particles on the planet earth can be generally classified into two types: primary particles and secondary particles [26, 34]. Secondary particles are the major cause of soft-errors on earth or satellites in low earth orbit (LEO) [5-6] and are usually generated by the interaction between primary particles and the atoms (such as oxygen or nitrogen atoms) in the atmosphere.

One source of primary particles is galactic particles, which are generated by

supernova explosions, stellar flares, or pulsars in the galaxy. These generated highenergy particles can last about 200 million years and may enter the solar system and hit the earth during their life circle [26]. Another source of primary particles is the sun, which may enter an active period almost every 11 years. During an active period of the sun, solar flare creates high energetic and density solar particles, whose number is about two times its quiet period [26, 27]. Also, the high-energy solar wind may disturb the magnetosphere of the earth (which can deflect the outer-space particles) and increase the possibility of high energetic particles reaching the terrestrial.

The secondary particles are generated by the interaction of these primary particles and atoms in the atmosphere. When these primary particles escape from the magnetosphere of the earth and enter the atmosphere, they may hit the atmospheric atoms (such as oxygen or nitrogen atoms) to generate secondary particles, such as protons, alpha particles, neutrons, heavy ions, pions, muons, and so on [26]. These secondary particles are responsible for soft-errors in terrestrial devices and systems. Also, the radioactive isotope in the package and silicon wafer process materials may emit alpha particles and can cause soft-errors [28, 29]. However, these materials caused soft-errors can be solved by replacing them with low alpha materials [29].

#### 2.1.3. Soft-Errors Induced Incidents

Soft-errors can cause serious consequences. In 2008, a soft-error occurred at the computer system of an Australian flight (Qantas flight 72). The soft-error corrupts the control data (angle of attack, AOA [66]) of the flight, which changes its gesture and made this flight abnormally pitched down two times during cruising over the Indian Ocean [35]. This incident caused more than 100 people (including passengers and crew members) injured because many of them had released their safety belts when this incident occurred. Due to this incident, European Aviation Safety Agency requires that aircraft computers should have the capability to tolerate soft-errors [36].

Another incident is the stuck accelerator pedals of Toyota cars in 2009 [37], which caused 89 people killed and 57 injured. According to the report [37], the suspect cause is that soft-errors occurred in the memories and caused a system malfunction.

In the study [79] reported in 1975, soft-errors changed the states of flip-flops of a satellite system and led to several anomalies.

In 2003, a soft-error in a voting machine adding 4096 extra votes to a candidate [38]. It is because all the votes are recorded by a binary number and a soft-error changes the  $13^{th}$  bit from 0 to 1, thus added  $4096 = 2^{12}$  extra votes. Another interesting thing is that a soft-error in a video game helps the player directly skip to the next level [39]. As can be noticed that soft-errors can impact electronic devices on earth anywhere, anytime, these mission-critical applications should be protected against the impact of soft-errors.

#### 2.1.4. Soft-Error Classification

Depending on the occurrence location of a soft-error in a circuit, it can be classified into single-event upset (SEU), which is occurred in a sequential circuit, and single-event transient (SET), which is occurred in a combinational circuit. An SEU can be divided into single-node upset (SNU) and multiple-node upset (MNU). If a particle striking only affects a p-n junction, it changes the logic value of a node. However, if a particle strikes multiple p-n junctions and may cause charge sharing, this particle striking changes the logic values of multiple nodes, thus flipping multiple bits. Due to the shrinking of technology sizes, MNUs are possible to occur in the storage elements. So far, there is no valid evidence to prove that MNUs may frequently occur in storage elements. On the contrary, the occurrence of SNUs can be proved by many valid data [61]. Therefore, tolerating SNUs in storage elements is more important than MNUs.

#### 2.1.5. Soft-Error Rate (SER) Definition and Calculation

The soft-error rate (SER) is defined as the occurrence frequency of soft-errors. To reduce SER, various soft-error tolerance methods have been proposed. A lower SER means that these methods have better soft-error tolerability. Therefore, these methods can be evaluated by calculating their SER [63-65]. There are some SER calculation metrics for combinational logic and memories [40], as well as for latches [7, 30].

The SER calculation metrics of latches usually consider two factors: timing vulnerability factor (TVF) and architectural vulnerability factor (AVF) [7]. The TVF is defined as the fraction of time that a node is susceptible to a soft-error. The AVF is defined as the probability that a soft-error at a node of a latch results in erroneous output. In our previous research [41], we proposed an SER calculation metric for latches, called soft-error vulnerability (SEV). In the calculation of SEV, the TVFs are set to 1 for the following reasons.

- (1) This research focuses on the AVF of latches.

- (2) AVFs and TVFs are independent of each other.

- (3) TVFs should be the same for a fair comparison.

Let c be a standard cell of a latch. Let F(c) be a set of particles that may hit the cell c during operation. We assume that a cell is hit by a single particle  $f \in F(c)$  at a time, but depending on the underlying soft-error model, particles may hit multiple nodes in the cell [4]. Let  $P_F: f \in F(c) \to (0 \cdots 1]$  be the probability density function that gives the relative occurrence probability of a particular particle strike f. By definition, we have:  $\sum_{f \in F(c)} P_F(f)$ . The particle set F(c) and probabilities  $P_F$  are determined by the chosen soft-error model, e.g. [21]. This modeling does not put any restrictions on the

number of nodes being hit by a particle. As multiple-node upsets are becoming more common in modern technology nodes [4], they can be easily added as elements to F(c) with their corresponding probabilities in  $P_F$ .

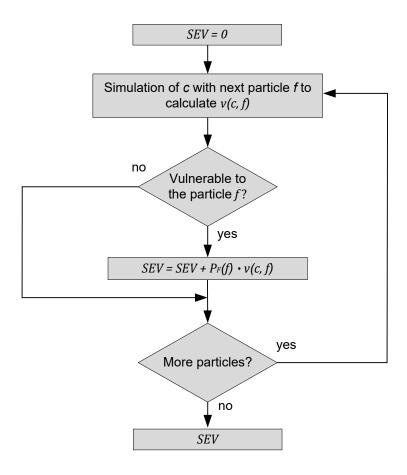

Figure 2.2 Soft-error vulnerability (SEV) calculation flow.

The soft-error vulnerability (SEV) is the probability that a latch cell shows erroneous outputs when the latch cell is hit by particles. The vulnerability of a latch cell c for a soft-error f can be defined as a characteristic function  $v(c, f): L \times F(c) \rightarrow [0 \cdots 1]$ . This function gives a cell  $c \in L$  (with L being the set of latch designs) and a soft-error  $f \in F(c)$  the probability that the output of the latch cell shows an error. The overall soft-error vulnerability of a latch cell c is calculated by:

$$SEV(c) = \sum_{f \in F(c)} P_F(f) \cdot v(c, f)$$

(2.1)

The calculation flow of SEV is shown in Figure 2.2. After initialization of the variable SEV = 0 for accumulating the result, all particles  $f \in F(c)$  are injected into the SPICE netlist of the cell c. For each particle f, v(c, f) is calculated. If the cell c is vulnerable to a particle strike, v(c, f) will be positive. SEV is increased by the combined probability of the particles occurring and the particle strike leading to an

erroneous output of the latch cell:  $P_F(f) \cdot v(c, f)$ .

These SER metrics are for the defect-free hardened latches. However, defects may occur during hardened latches' manufacturing and may make these defective latches vulnerable to soft-errors. Thus, there is a significant need to propose a new metric to evaluate the impact of defects on the soft-error vulnerability of these hardened latches.

#### 2.2. Defect

Defects are physical flaws caused by imperfect production (production defects) and physical changes caused by aging effects (aging-related defects). High energy radiation particle striking can also cause physical damages of a circuit, which are radiation-induced defects. Defects may change the behavior of a circuit and make it deviate from its proper manner.

#### 2.2.1. Production Defect

The manufacturing of chips contains a lot of repetitive physical and chemical process steps, including photoresist coating, lithography, etching, deposition, and ionization. An example of forming an n-well on p-type silicon (as shown in Figure 2.1 (a)) is introduced to show these processes. Some Group V dopants need to be doped into the exact location on the p-substrate to change it from p-type to n-type. Before defining the n-well location, a protective layer on the wafer is formed by a reaction with oxygen to form an oxide on its surface. Then, a photoresist coating will be spread on the oxide surface and the photoresist on the determined n-well location is then exposed to the ultraviolet light through a mask pattern. The area of photoresist exposed to the light becomes more soluble and can be easily removed to reveal the oxide. Hydrofluoric acid can be used to etch the oxide area and cause no damage to the photoresist protected area. Another acid called piranha acid is used to clean the residual photoresist and dopant ions are prepared to dope into the n-well location as well as the surface of the remaining oxide layer. The remaining oxide layer protects the p-substrate from the dopant ions. Finally, the hydrofluoric acid can be used to remove the oxide layer and the n-well is formed.

Manufacturing chips need repetitions of the above process to form transistors and metal layers. Any randomly occurred manufacturing imperfection (such as a weakly connected line bonding, impurities, improperly etched metal traces, shorts between lines or opens) or process variation (the channel length of a transistor, transistor threshold voltage, or metal line thickness and width) can cause a flaw on the chip, which may affect the behavior of a transistor, the conductivity of a metal line, or even worse a malfunction.

Along with the shrinking of the technology feature sizes, a lithography technology called multiple pattern technology helps to support 20nm and below. Multiple pattern technology is developed to enhance the resolution of lithography exposure [42]. The commonly used multiple pattern methods are litho-etch-litho-etch (LELE) process [43] and self-aligned double patterning (SADP) [44]. However, this technology increases the process steps as well as the risk of generating production defects.

#### 2.2.2. Aging-Related Defect

Aging effects refer to the degradation of the parameters of ICs after a long time of stressful field operation. These parameter changes can affect the performance of ICs and cause permanent physical damage, called aging-related defects. Three typical aging effects may cause aging defects and they are electromigration (EM), negative bias temperature instability (NBTI), and hot carrier injection (HCI).

**Electromigration (EM):** It is a gradual movement of metal atoms pushed by the momentum of a high density of electrons. With the continuously shrinking of technology sizes, the risk of EM-caused ICs malfunction will increase because the density of both current and power increases [45]. EM can cause the movement of atoms in metal wire and cause two possible results. (1) It may make the wires thinner and eventually lead to open defects. (2) It may push atoms together to form a bumped knot, which may conduct with adjacent wires (short defects).

**Negative Bias Temperature Instability (NBTI):** It affects PMOS transistors by changing the threshold voltage. It is because the positive charges are trapped at the oxide, which increases the threshold voltage.

Hot Carrier Injection (HCI): Different from NBTI, HCI affects NMOS transistors. Due to high switching activity, hot electrons (energetic electrons) may enter the depletion region to permanently damage the activity of NMOS transistors or become trapped in the gate dielectric to change the threshold voltage.

#### 2.2.3. Radiation-Induced Defect

A radiation-induced defect is also called a hard-error, which is permanently physical damage caused by the striking of radiation particles and will not disappear after resetting. Radiation-induced defects include single-event latch-up (SEL), single-event burnout (SEB), displacement damage effect (DDD), and total ionizing dose effect (TID). These hard-errors are not a big concern to the terrestrial electronic devices because most of arriving particles on the terrestrial are secondary particles that are not as energetic as the outer space particles. They are a big concern for outer space devices, such as satellites. There are two typical radiation-induced defects:

**Single-Event Latchup (SEL):** It is a type of short effect caused by particle striking. A particle strikes a transistor and causes permanent damage to it, which makes it continually conducting.

**Single-Event Burnout (SEB):** It is a type of single event caused by a high-energy particle striking and it induces localized high current damage that leads to a failure.

#### 2.3. Fault Model

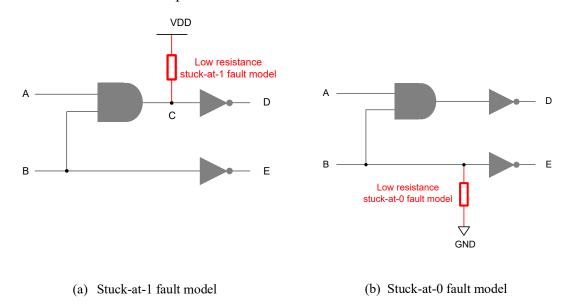

A fault is the logical level abstraction of the physical behavior of a defect. Fault models are a series of faults, which can precisely reflect the physical condition of defects. The probably occurred defects can be assumed according to the layout information. These assumed defects are represented by fault models, which can show their physical conditions and make the test pattern generation more easily. Using fault models can greatly reduce test time and increase test efficiency. A good fault model can accurately show the behavior of a defect and can be efficient for simulation and test pattern generation [67-69]. The commonly used fault models are stuck-at fault models, transistor fault models, wire open fault models, and wire short fault models.

Stuck-at faults refer to a signal line stuck at a constant logic value ("1" or "0"), which can represent a short defect that this signal line shorted with VDD or GND, respectively. The stuck-at fault models are widely used in combinational circuits. Figure 2.3 shows an example of stuck-at fault models. Figure 2.3 (a) shows a stuck-at-1 fault model to represent a short defect between VDD and node C. Figure 2.3 (b) shows a stuck-at-0 fault model to represent a short defect between GND and node B.

Figure 2.3 Stuck-at fault models.

These stuck-at faults can be tested by using quiescent power supply current  $(I_{DDQ})$

#### measurement [49].

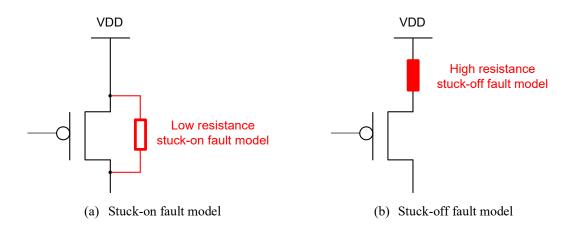

Transistor faults refer to the stuck-on or stuck-off of a transistor. The stuck-on fault of a transistor represents a transistor short defect (such as gate oxide shorts, defective p-n junctions, and parasitic transistor leakage) that will turn ON this transistor. The stuck-off fault of a transistor represents a transistor open defect (such as gate oxide opens and defective p-n junctions) that will turn OFF this transistor. Figure 2.4 shows an example of transistor fault models. Figure 2.4 (a) shows a stuck-on fault model to represent a short defect between source and drain. Figure 2.4 (b) shows a stuck-off fault model to represent an open defect at the source of this transistor.

Figure 2.4 Transistor fault models.

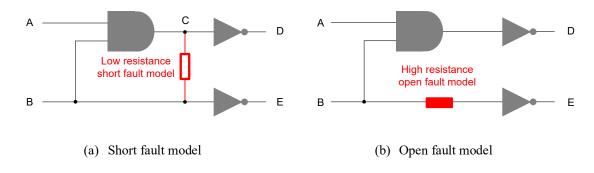

Figure 2.5 Wire short and open fault models.

Short faults and open faults refer to short defects and open short defects in metal wires. Short faults represent shorts between two adjacent metals. Open faults represent opens in diffusion, poly, or metal due to process variation or production imperfection. Figure 2.5 (a) shows a wire short fault model to represent a short defect between wires C and B. Figure 2.5 (b) shows a wire open fault model to represent an open defect at the wire connecting node B and the input of an inverter.

#### 2.4. Defect Coverage

For a given circuit under test (CUT), a series of fault models can be generated according to its layout information. After applying test patterns (according to the fault models) to the inputs of this CUT and observing the test responses from its outputs, this CUT can be tested. If all considered faults are observed, we can say that the defect coverage (fault coverage) of this CUT is 100%. If not, its defect coverage is defined as:

$$Defect Coverage = \frac{Number of Detected Faults}{Total Number of Faults}$$

(2.2)

For evaluating the testability of a circuit, defect coverage (*DC*) is used to measure the portion of all possible cell-internal production defects that are detected in a complete production test setting [75, 76, 78].

The defect coverage of a hardened latch cell is calculated by simulating a simple flush test with all possible defects. We use the fault model of every possible defect based on the latch structure because most published hardened latch designs do not provide actual cell layouts. Also, this fault model can identify these undetected defects and can provide a guide when making a layout of a standard hardened latch cell. Let d be a defect. Let D(c) be a set of defects that may occur in the cell c during manufacturing. A cell c may be affected by at most one defect d, and we denote the defective cell as  $c_d$ . Let  $P_D: d \in D(c) \to (0 \cdots 1]$  be a probability density function that gives the relative occurrence probability of a defect d. By definition, we have:  $\sum_{d \in D(c)} P_D(d)$ . The set D(c) and the probabilities  $P_D$  are determined by the used fault model.

After the production of the cell c, we assume a simple pass-fail test modeled by a characteristic function  $t: C \to \{1,0\}$  with C being the set of all instances of the defective cell  $c_d$ . For any production defect  $d \in D(c)$ , the characteristic function evaluates to  $t(c_d) = 1$ , if the cell c with defect d passes the production test, and to  $t(c_d) = 0$ , otherwise. Clearly, the test passes always for the defect-free cell: t(c) = 1.

The defect coverage of the test t is:

$$DC(c,t) = \sum_{d \in D(c)} P_D(d) \cdot (1 - t(c_d))$$

(2.3)

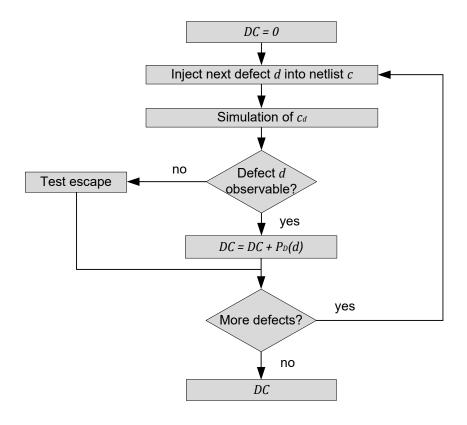

The calculation flow of defect coverage (DC) of a latch cell is shown in Figure 2.6. After initialization of the variable DC = 0 for accumulating the result, a defect  $d \in D(c)$  is injected into the original SPICE netlist to generate a model of  $c_d$ . The new netlist is simulated, and the output of the defective latch is checked for erroneous values. If the defect d is observable ( $t(c_d) = 0$ ), DC is updated to reflect the defect coverage. If the defect d is not observable, this defect escapes the test. After all considered defects are simulated and the DC can be calculated.

Figure 2.6 Defect coverage (DC) calculation flow.

If the test t fails  $(t(c_d) = 0)$  for all possible defects in the defect set, then the defect coverage DC(c,t) is 100%. If the test does not detect all possible defects, DC(c,t) will be reduced by the probability that the cell contains these undetected defects. For evaluating the impact of defects on the hardened latches, the cases that pass the test t  $(t(c_d) = 1)$  need to be analyzed.

#### 2.5. Summary

This chapter briefly introduces the basics of soft-errors, including the mechanism of soft-errors, sources of radiation particles, the impact of soft-errors, and soft-error classification. The introduced soft-error rate (SER) calculation metric (soft-error vulnerability, SEV) can be used to evaluate the soft-error tolerability of hardened latches. However, this SEV metric is only for defect-free hardened latches. This chapter also introduces the basics of defects (production defects, aging-related defects, and radiation-induced defects). For simplifying test generation for LSI circuits, fault models are provided to behave the physical condition of defects, which are located according to the layout information. At last, defect coverage is introduced.

#### 3. Related Works

This chapter introduces some typical soft-error tolerance methods, including Error Correction Codes (ECCs) for protecting the memories, system-level soft-error mitigation, register-level soft-error mitigation, and hardened latch designs. Also, this chapter introduces some defect detection methods.

#### 3.1. Soft-Error Mitigation

Due to the stochastic nature of radiation-induced soft-errors, various elements (such as memories and sequential elements) in modern chips may suffer from the impact of soft-errors. For mission-critical applications, protecting these soft-error vulnerable elements becomes especially important.

#### 3.1.1. Error Correction Code

Error Correction Codes (ECCs) are widely applied to protect memories from the impact of soft-errors [50, 51]. The ECCs are performed by adding parity checking bits to check and correct soft-errors caused bit flips. These parity bits are computed into the code along with their write operations and can be decoded by the read operations. The encoding and decoding of these parity bits are performed by a specific circuitry. With the help of these added parity bits, corrupted data in memories can be checked and corrected. However, bigger memory requires more overhead for the parity bits. Also, the decoding process needs a lot of time when the parity bits scale is very large [52].

#### 3.1.2. System-Level Mitigation

A system-level soft-error tolerance scheme [53] is applied in small satellites by combining hardware and software. It uses multiple cores to operate the same process and uses a software program to compare the results of these cores. If a core shows wrong results, the rest cores will continue with the majority of results and this corrupted core will roll back to a few clock cycles before continuing this process.

Another system-level soft-error tolerance scheme [54] is using a combination of soft-error tolerance techniques together to protect process cores, including hardened designs [55, 56], parity checking [57], and micro-architectural recovery [58, 59].

#### 3.1.3. Register-Level Mitigation

A register-level soft-error detection and correction method was proposed in [60]. It uses latches, NAND, and XOR cells to form a parity tree and two of these parity trees can form an error detecting register. This method can locate the soft-error occurred register and be reapplied for both offline and online testing.

#### 3.1.4. Hardened Latch Design

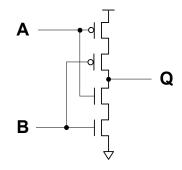

Hardened latch designs achieve soft-error tolerability by adding redundant feedback loops and using a voter to select the correct output. Some typical hardened latches will be introduced in this section. C-element is a commonly used voter, which is shown in Figure 3.1. Its truth table is shown in Table 3-1. If two inputs (input A and input B) of a C-element are the same logic value, the C-element works as an inverter, which inverts the input logic value. If two inputs of a C-element hold different logic values, the output of this C-element is at a high-impedance state.

Figure 3.1 Structure of C-element.

Table 3-1 C-element truth table

| A | В | Q              |

|---|---|----------------|

| 0 | 0 | 1              |

| 1 | 1 | 0              |

| 0 | 1 | High-Impedance |

| 1 | 0 | High-Impedance |

Figure 3.2 shows a triple modular redundancy (TMR) latch design, which uses three standard latches to store the same input data and uses a voter circuit to select the majority as its output. This latch can prevent the soft-errors from appearing at the output. However, it cannot correct the corrupted logic value until the arrival of a new datum.

Figure 3.2 Triple modular redundancy (TMR) latch.

Figure 3.3 shows a feedback redundant hardened latch design (FERST) [18], which stores the same logic value in two feedback loops (FL0 and FL1) and uses a C-element (CE3) to prevent the soft-errors from outputting. Within each feedback loop, a C-element is applied to tolerate soft-errors. A weak keeper is at the output of CE3 to avoid the impact of the high-impedance state of CE3.

Figure 3.3 FERST [18] latch.

Figure 3.4 shows a hardened latch design (HLR) [19], which uses three transmission gates, two feedback loops (FL0 and FL1), and a clock-controlled C-element to form a hardened latch design.

Figure 3.4 HLR [19] latch.

In transparent mode, the input signal propagates through three transmission gates and divides into three parts. Two feedback loops store the input signal, and the third part propagates directly to the output. During this transparent mode, the clock-controlled transistors in the C-element are in the OFF state and it can prevent the probable conflict at the output of this latch. In hold mode, the clock-controlled transistors in the C-element are in the ON state and two feedback loops will continually drive the clock-controlled C-element. Similar to the TMR latch, the HLR latch can prevent the soft-errors from appearing at the output, however, it cannot correct the corrupted logic value.

#### 3.2. Defect Detection

Testing is used to find defective manufactured devices. It applies test vectors to a circuit under test (CUT) and analyzes its test responses. A circuit that outputs correct test responses passes the test; otherwise, it fails the test [46].

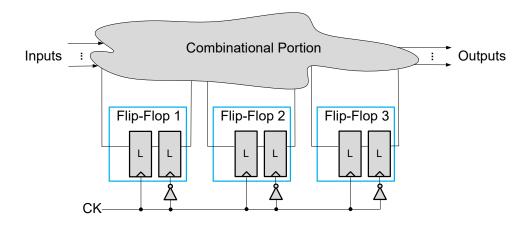

#### 3.2.1. Functional Test

Figure 3.5 shows an example of a sequential circuit with a combinational portion and three flip-flops. Using functional tests can detect defects in flip-flops. The test vectors are applied to the inputs of the combinational portion and the test results can be checked at the output of this circuit.

Figure 3.5 Functional test.

When the scale of the CUT is very small, it is an acceptable way to apply all possible test patterns to the inputs of the CUT to fully test it. However, this way meets problems when testing large-scale-integration (LSI) or very-large-scale-integration (VLSI) circuits and it is very difficult to check and control the internal states of numerous flip-flops. In the following section, a design-for-test (DFT) technique called scan design can be used to overcome this difficulty [70, 71].

#### 3.2.2. Scan Design

Due to the complexity of modern circuits, it is difficult to set and check numerous internal states of sequential circuits from limited external pins. DFT techniques can overcome this difficulty by modifying storage elements and providing direct access to these storage elements.

Scan design is a commonly used DFT technique [46]. In a full-scan design, all functional flip-flops in a circuit are replaced with scan cells, which are then connected into scan chains. The internal states of all scan cells can be set by shifting test vectors through these scan chains and be checked by shifting out the corresponding test responses, which can greatly improve the testability.

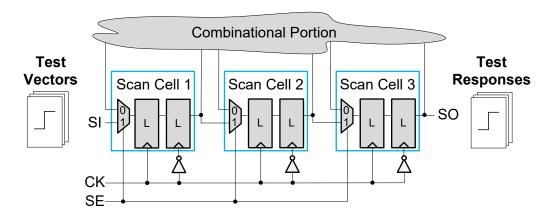

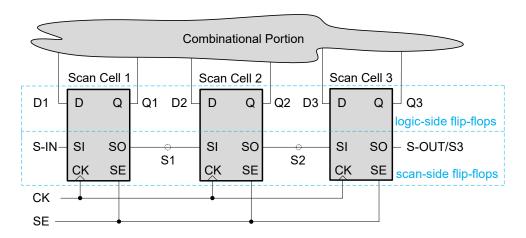

#### 3.2.3. Scan Test

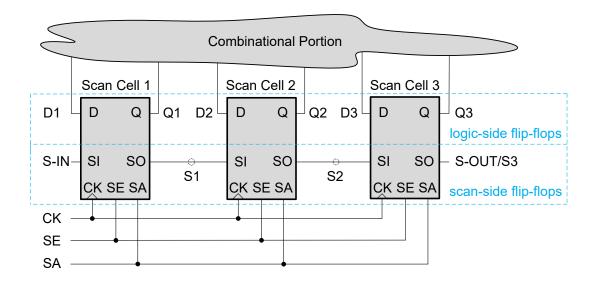

Figure 3.6 shows a scan chain example with a combinational portion and three scan cells. Each scan cell has a multiplexer and a flip-flop constructed by two latches. The scan-enable (SE) signal switches each scan cell between shift mode and functional mode by controlling its multiplexer. The clock (CK) signal controls the operation of latches.

This scan chain can perform a scan test to fully test a sequential circuit and the operation is as follows. First, SE is set to 1 and this scan chain operates in shift mode. Scan cells work collectively as a shift register for shifting in test vectors from scan-in (SI). By this operation, each scan cell stores a logic value. A sequence of these stored logic values is called a test vector. The logic values stored in these scan cells then propagate to the combinational portion and generate corresponding test responses. Second, SE is set to 0, all scan cells operate individually as flip-flops (functional mode), and test responses are captured by each scan cell with the next clock. Finally, SE is set to 1 for shifting out these test responses through scan-out (SO) for analysis.

Figure 3.6 Scan chain example.

Before a scan test, flush tests are performed to make sure all scan cells work correctly. A flush test is a shift test where a chosen flush pattern (such as "01100" [46]) is shifted through a scan chain to verify that the same flush pattern reaches the end of the scan chain at the correct clock cycle. For example, Figure 3.6 shows a scan chain with 3 scan cells. During a flush test, SE remains at 1. A flush pattern is shifted in from SI. The same flush pattern is expected to reach the SO after 3 clock cycles. If the shift-out pattern is changed or at a different clock cycle, then this scan chain contains production defects. Flush tests can be applied to detect the transition delay faults in scan cells. A good flush test pattern should provide four causes of transitions, including 0 - to - 0, 0 - to - 1, 1 - to - 0, and 1 - to - 1. Also, flush tests can be applied for diagnosis.

However, if these scan cells in a scan chain are based on hardened latches, many defects in the scan cells may not be detected by using flush tests due to the cell-internal redundancy. The defective hardened latches may become vulnerable to soft-errors. Furthermore, undetected defects in hardened latches may become more and more serious and cause chips to fail eventually. Hence, it is important to propose a new DFT for testing hardened latch designs that contain defects.

#### 3.3. The Importance of This Research

With the continuously reduction of technology feature sizes and supply voltages, modern ICs become more and more vulnerable to soft-errors. Sequential elements (like latches and flip-flops) are the most vulnerable to soft-errors in a circuit. Hence, it is very important to protect them from the impact of soft-errors. A register-level soft-error mitigation method is available to detect soft-errors in latches [60]. However, it is not suitable to protecting mission-critical applications because it requires some time to process the roll-back operation to tolerate soft-errors. During this time interval, bad results may have already happened. Hardened latch designs can be used to protect sequential elements as well. The advantage of using hardened latch designs is that hardened latch designs can prevent soft-errors from reaching their outputs and do not need to sacrifice valuable time.

So far, many state-of-the-art hardened latch designs have been proposed to tolerate soft-errors and they are believed to have high reliability. However, the problem with the application of these hardened latch designs is that the impact of defects on the tolerability of hardened latches has not been considered. The soft-error tolerability of manufactured chips based on these hardened latch designs cannot be evaluated because defects can reduce the soft-error tolerability of hardened latch designs. Furthermore, redundancy in hardened latch designs may mask not only soft-errors but also the defect effects, which makes defects in hardened latches difficult to detect. This research is the first to find the impact of defects on the soft-error tolerability of hardened latches and the first to propose a novel metric to evaluate residual soft-error tolerability of hardened latches after production. Furthermore, this research proposes novel hardened latch designs with good defect detectability. It is the first research that bridges the hardened latch design field and defect detection field as well.

In this research, the impact of defects on the tolerability of hardened latches has been analyzed. This research proposed the first soft-error vulnerability metric, called post-test vulnerability factor (*PTVF*), that takes defects into account to evaluate the impact of defects (in Chapter 4). Furthermore, two new hardened latches (scan-test-aware hardened latch, STAHL, as shown in Chapter 5 and a novel high performance scan-test-aware hardened latch design, HP-STAHL, as shown in Chapter 7) with good defect detectability are proposed. A new test procedure for testing STAHLs is proposed in Chapter 8.

#### 3.4. Summary

In this chapter, some typical soft-error tolerance methods are introduced. Error correction codes can be used to protect memories. A register-level soft-error tolerance method can be used to detect soft-errors in latches [60]. Hardened latches can be used to

protect latches from the impact of soft-errors. This research focuses on using hardened latches because hardened latches can prevent soft-errors from reaching their outputs.

Some defect detection methods are also introduced in this chapter. This research focuses on using scan chains and performing flush tests to detect defects in latches. Because scan design is a commonly used industry practice, it is easy to control and check the internal logic values stored in latches.

# 4. Post-Test Vulnerability Factor (*PTVF*)

There is no previous work considering the interplay among physical defects, the redundancy in hardened latches, and the residual soft-error tolerability of latches with undetected defects. In this section, I will address this problem by proposing the first-of-its-kind metric, called Post-Test Vulnerability Factor (*PTVF*), to evaluate the impact of defects on hardened latches.

### 4.1. Definition of *PTVF*

In previous works, defect coverage DC(c,t) and soft-error vulnerability SEV(c) have only been considered independently. However, whenever the defect coverage DC(c,t) is less than 100%, some defective cells  $c_d$  pass the test  $(t(c_d) = 1)$ . While the original defect-free cell  $c_d$  can tolerate soft-errors, the defective cell  $c_d$  that escaped the test t may not. In other words, the soft-error vulnerability to some particles f can change if some defect d is present:  $v(c,f) \neq v(c_d,f)$ . I define a novel metric called Post-Test Vulnerability Factor (PTVF) [48] that takes the probabilities of the test-escaping defects into account as follows:

$$PTVF(c,t) = \frac{\sum_{d \in D(c)} P_D(d) \cdot t(c_d) \cdot SEV(c_d)}{1 - DC(c,t)}$$

(4.1)

The *PTVF* indicates the vulnerability of a cell when the cell has production defects and is hit by particles. It depends both on the defect coverage and the soft-error vulnerability of cells with undetected defects. If all defects are detected, DC(c,t) = 1, we define PTVF(c,t) = 0. If all defects  $d \in D(c)$  that escape the test  $(t(c_d) = 1)$  do not impact the soft-error vulnerability of the latch cell  $(SEV(c_d) = 0)$ , then the PTVF(c,t) is 0 as well. In the remaining cases, the value of PTVF is less than or equal to 1 since the denominator of Eq. (4.1) is always greater than or equal to the numerator.

For example, let's assume that there are 100 possible defects in a hardened latch cell and each defect has an equal occurrence probability of 1%. Assume that the defect coverage (*DC*) of this hardened latch is 95%. Thus, 5 undetected defects make  $t(c_d) = 1$ . Let  $UD = \{ud1, \dots, ud5\}$  be a set of these undetected defects. The numerator of Eq. (4.1)  $\sum_{d \in D(c)} P_D(d) \cdot t(c_d) \cdot SEV(c_d)$  equals to  $\sum_{ud \in UD} P_D(ud) \cdot SEV(c_{ud})$  because  $t(c_d) = 0$  for all detected defects. The  $P_D(ud)$  is 1% in this example and  $SEV(c_{ud})$  can be calculated by Eq. (2.1). Assume that each calculated  $SEV(c_{ud})$  is 30%. The numerator of Eq. (4.1) is then:  $5 \times 1\% \times 30\% = 1.5\%$ . The denominator of Eq. (4.1)

is (1 - DC), which is 5% in this example. So, the *PTVF* is 1.5% / 5% = 30%. The *PTVF* is independent from the overall defect coverage and the overall soft-error vulnerability. It is useful for characterizing and comparing latch designs.

### 4.2. Calculation of *PTVF*

A series of SPICE simulations are performed to calculate the PTVF. The necessary inputs are the SPICE netlist of the latch cell c, the set of production defects D(c) and their probabilities  $P_D$ , the set of particles F(c) and their probabilities  $P_F$ , the test conditions, test procedure, and pass/fail criterions. Each defect  $d \in D(c)$  must be injected into the SPICE netlist (e.g. by inserting additional components like resistances between nets). Each particle  $f \in F(c)$  must be injectable during transient analysis, e.g., by using additional current sources. The test t is given in form of a set of measurement times, expected values, and tolerances at the output of the latch. Without loss of generality, we assume a latch cell to be exhaustively tested with all possible combinations of inputs and states. A defect in the latch is considered to be detected if the latch outputs a wrong logic value for longer than a quarter of a clock cycle. Each SPICE simulation is a transient analysis of a few clock cycles and varying inputs similar to the inputs shown in Figure 1.1 (b). A particle strike is considered to lead to an erroneous output, whenever the output of the latch has settled on a wrong logic value until the end of the latching phase.

The calculation flow is shown in Figure 4.1. After initialization of two variables V = 0 and DC = 0 for accumulating the results, a production defect  $d \in D(c)$  is injected into the original SPICE netlist to generate a model of  $c_d$ . The new netlist is simulated, and the output of the defective latch is checked for erroneous values. If the defect d is observable ( $t(c_d) = 0$ ), DC is updated to reflect the defect coverage. The V will not be changed, and the loop continues with the next production defect. If the defect d is not observable, all particles  $f \in F(c)$  are injected into the model  $c_d$ . For each particle f,  $v(c_d, f)$  is calculated. If the model  $c_d$  is vulnerable to a particle strike,  $v(c_d, f)$  will be positive. V is increased by the combined probability of the defect, the particles occurring, and the particle strike leading to an erroneous output of the latch cell:  $P_D(d) \cdot P_F(f) \cdot v(c_d, f)$ .

Calculating the PTVF needs a large number of SPICE simulations since each latch is simulated with all possible production defects and the combinations of particles and undetected defects. However, each simulation is rather quick since it lasts a few clock cycles on a single cell. Furthermore, most SPICE simulations are independent and can be executed in parallel. The worst-case computation complexity is  $O(|D(c)| \cdot |F(c)|)$  with |D(c)| being the number of defects and |F(c)| being the number of particles.

Figure 4.1 PTVF calculation flow.

# 4.3. Summary

Post-Test Vulnerability Factor (*PTVF*) is the first metric to evaluate the impact of defects on the soft-error tolerability of hardened latches. *PTVF* considers both the impact of defects and the impact of soft-errors on the defective hardened latches. It is an important metric to evaluate the reliability of hardened latch designs.

# 5. Scan-Test-Aware Hardened Latch (STAHL)

To overcome **Problem-1** (Low Testability), a novel scan-test-aware hardened latch (STAHL) design is proposed [77]. In this chapter, the structure of STAHL is introduced in Section 5.1. Both functional mode and shift mode of the STAHL are introduced in the following sections. The summary section concludes this chapter.

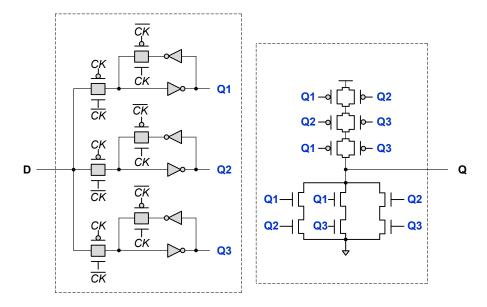

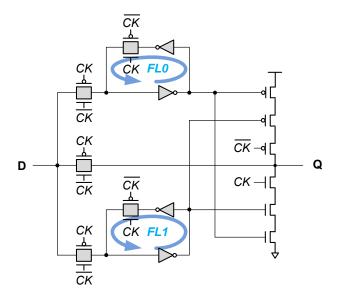

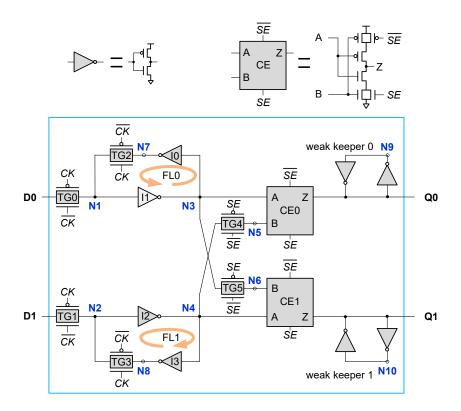

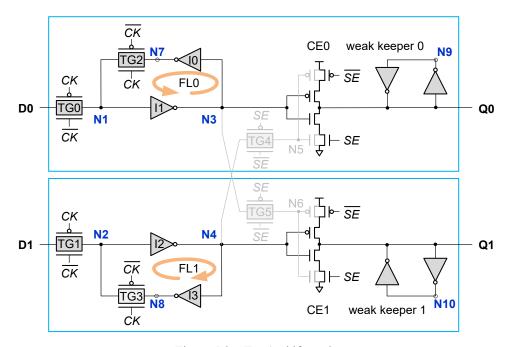

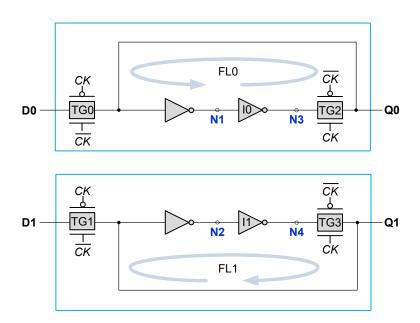

## 5.1. Structure of STAHL

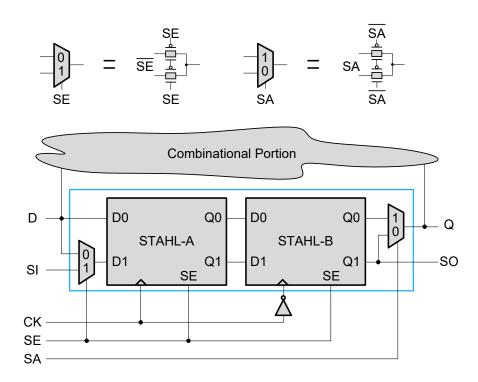

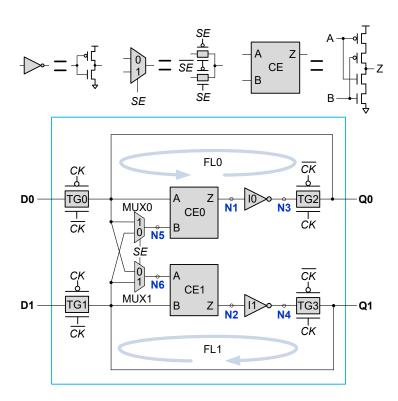

The STAHL's structure is shown in Figure 5.1. Instead of using just one input D and one output Q as in a common latch, the STAHL has 2 inputs (D0 and D1) as well as 2 corresponding outputs (Q0 and Q1). In addition to the normal clock signals CK and  $\overline{CK}$  (inverse signal of CK), the STAHL has an additional scan-enable (SE) signal that switches between shift mode (SE = 1) and functional mode (SE = 0).  $\overline{SE}$  is the inverse signal of the SE. The STAHL contains 2 independent feedback loops (FL0 and FL1) formed by 2 clock-controlled transmission gates (TG2 and TG3), and 4 inverters (I0 to I3). The clock-controlled transmission gate TG0 (TG1) connects the input D0 (D1) to the feedback loop FL0 (FL1).

Figure 5.1 Structure of the proposed STAHL.

2 SE-signal-controlled transmission gates (TG4 and TG5) drive the inputs of 2 C-elements (CE0 and CE1). For each C-element, we add 2 SE-signal-controlled transistors (an SE-controlled PMOS and an SE-controlled NMOS), which will be ON in shift mode and OFF in functional mode. 2 C-elements work as 2 equivalent inverters in shift mode and can prevent SEUs from appearing at their outputs in functional mode. Note that weak keeper 0 (weak keeper 1) is at the output Q0 (Q1) to maintain the output value while the outputs of C-elements are in high-impedance.

Now, we describe the operation of the STAHL in both functional (hardened) mode and shift mode.

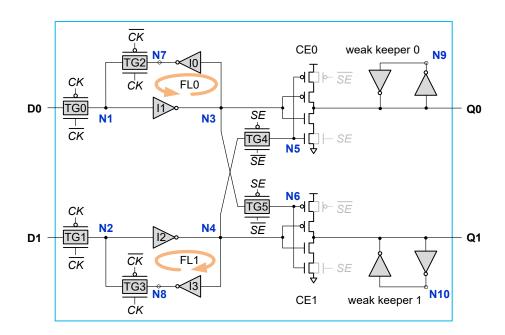

# 5.2. Functional (Hardened) Mode of STAHL

The STAHL is in functional mode when SE = 0. Figure 5.2 shows the circuit for this mode. In functional mode, the value to be stored in the latch needs to be applied to both inputs D0 and D1. The transistors shown in gray in CE0 and CE1 are OFF. 2 SE-signal-controlled transmission gates (TG4 and TG5) are ON.

Figure 5.2 SE = 0: functional (hardened) mode.

In transparent phase (CK = 0), the transmission gates TG0 and TG1 are ON. The input value at D0 (D1) propagates through node N1 (N2), inverter I1 (I2), node N3 (N4), C-elements (CE0 and CE1) to outputs Q0 and Q1. Q0 or Q1 can be chosen as the main output.