Shen, C., Jahdi, S., Mellor, P. H., Yang, J., Bashar, E., Ortiz-Gonzalez, J., & Alatise, O. (2022). Investigation of the Static Performance and Avalanche Reliability of High Voltage 4H-SiC Merged-PiN-Schottky Diodes. In *24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe)* Institute of Electrical and Electronics Engineers (IEEE). https://ieeexplore.ieee.org/document/9907751

Peer reviewed version

Link to publication record in Explore Bristol Research PDF-document

This is the accepted author manuscript (AAM). The final published version (version of record) is available online via IEEE at https://ieeexplore.ieee.org/document/9907751. Please refer to any applicable terms of use of the publisher.

## University of Bristol - Explore Bristol Research General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/red/research-policy/pure/user-guides/ebr-terms/

# Investigation of the Static Performance and Avalanche Reliability of High Voltage 4H-SiC Merged-PiN-Schottky Diodes

Chengjun Shen, Saeed Jahdi, Phil Mellor, Juefei Yang Erfan Bashar, Jose Ortiz-Gonzalez , Olayiwola Alatise

Department of Electrical Engineering University of Bristol Bristol, United Kingdom Phone: +44 (0) 117 455 9492 Email: chengjun.shen@bristol.ac.uk URL: http://www.bristol.ac.uk/engineering/research/em/

#### Acknowledgments

CT data were obtained at the XTM Facility, Palaeobiology Research Group, University of Bristol.

### Keywords

«Silicon Carbide», «Junction Barrier Schottky», «Merged-PiN-Schottky», «Schottky Diode»

## Abstract

A comprehensive range of static measurements and UIS tests have been conducted for Silicon PiN diodes, SiC JBS diodes and SiC MPS diodes with temperatures ranging to up to 175°C. The results shows that the forward voltage of Silicon PiN diode is lower at the on-state, even at high temperatures and at high currents. Higher forward voltage and positive temperature coefficient are observed for SiC devices during the static measurements, while they outperform the Silicon devices in terms of the electrothermal ruggedness, as validated by the UIS measurements and its subsequent calculated avalanche energy and die area as measured by means of CT-Scan imaging of the devices.

### Introduction

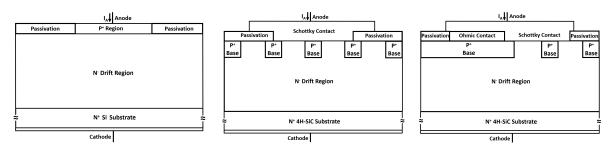

Merged-PiN-Schottky (MPS) diode structure can be the compromise to exhibit the best attributes of both PiN and Schottky diode for power electronics applications [1]. This is because the significant reduction of electric field at Schottky contact suppress the leakage current [2] and carriers from the P<sup>+</sup> regions, as shown in Fig. 1, will be injected into the drift region [2, 3], allowing the occurrence of conductivity modulation to reduce the on-state voltage drop. A further reduction of leakage current is expected in SiC MPS diode as the peak electric field occurring at the SiC surface defects on Schottky contact [4] is reduced. In addition to performance metrics, reliability of power semiconductor devices and lifetime prediction has been a major topic of research in the last few decades [5, 6]. In some applications such as grid-level converters, power diodes can experience such high voltage transients that they may be led into the avalanche rating conduction, and potentially failure [7]. These diodes can also be used for high frequency and medium voltage applications as output diodes in Power Factor Correction (PFC) circuit and as clamping diode in high voltage DC transmission. Clamping diodes can experience such high voltage transients that they may be led into the avalanche rating conduction and potentially failure, while undetected grid failures in PFC circuit [8] may lead to overcurrent in output diodes. Previously, electrothermal ruggedness and avalanche robustness of SiC MPS diode have been assessed [9, 10, 11, 12] under Unclamped Inductive Switching (UIS) tests, though in absence of like-for-like comparison with similarly rated power rectifiers. Previous studies of static performance have also not dealt with the selfheating effects of the SiC MPS diode at different current levels while the high-level injection effect of MPS diode has not been discussed by means of experimental measurements.

This paper explores the static characteristic of commercially available 4H-SiC MPS diodes in contrast to Silicon PiN and 4H-SiC Junction Barrier Schottky (JBS) diodes in order to characterize the on-state limits. In addition, single event avalanche performance of these three devices is evaluated by means of experimental measurements. Section II of this paper provides the static performance analysis of the three devices while Section III explains the mechanism of UIS stressing and provides insights based on the experimental results. Conclusions are provided in Section IV.

Fig. 1: From left: cross-section of Silicon PiN diode, SiC JBS diode and SiC MPS diode.

### **Static Performance**

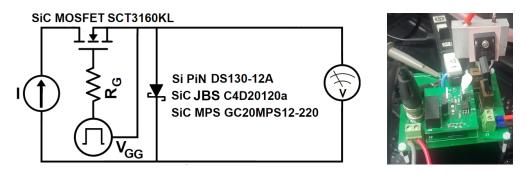

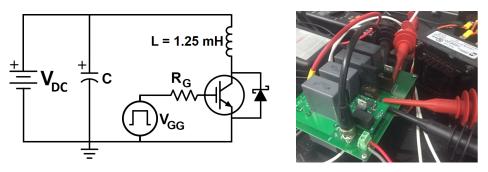

Table. I includes the key parameters of the three diodes to be used for further analysis. All the devices are in TO-220 packages. The static performance of these diodes have been characterized by using the static measurement test circuit shown in Fig. 2. The SiC power MOSFET SCT3160KL connected in series to diodes is used to accurately control the current conduction period through the diode. An ELC ALR3220 power supply provides the on-state current ranged from 5 to 20 A while the conducting period is set by an Agilent 33220A 20MHz arbitrary waveform generator to 3 seconds for all three diodes. The initial case temperature before the circuit is turned-on is controlled from 25°C to 175°C in 25-degree increments via ITC-100RL PID temperature controller. A Tektronix current probe model TCP312 in conjunction with a probe amplifier model TCPA300 was used for measuring the diode currents while a JAMECO P6100 100MHz voltage probe was used to measure the diode voltage. Both the captured current and voltage waveform are shown in a Keysight MSO7104 A 1-GHz 4 GSa/s oscilloscope. The I-V characteristic of all three diodes has also been measured by using B2901A Source/Measure Unit.

|                  | Silicon PiN   | 4H-SiC JBS    | 4H-SiC MPS    |

|------------------|---------------|---------------|---------------|

| Model            | DSI30-12A     | C4D20120A     | GC20MPS12-220 |

| Manufacture      | IXYS          | CREE          | GeneSiC       |

| Package          | TO-220-2      | TO-220-2      | TO-220-2      |

| Blocking Voltage | 1200 V        | 1200 V        | 1200 V        |

| Forward Current  | 30 A at 130°C | 26 A at 135°C | 30 A at 135°C |

| Leakage Current  | 40 µA         | 200 µA        | 10 µA         |

Table I: The key electrical parameters of the three Silicon and SiC rectifiers.

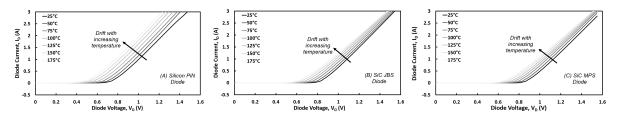

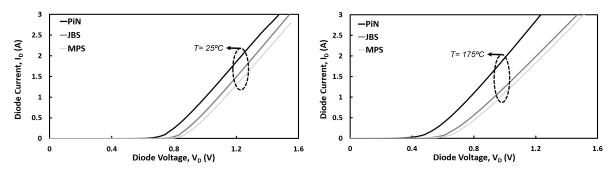

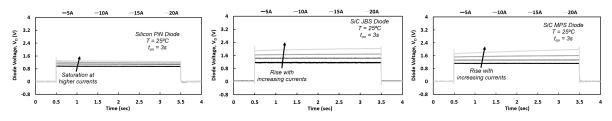

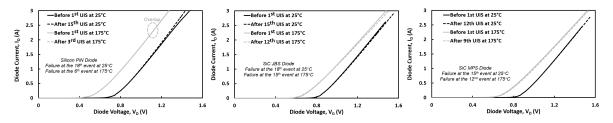

Fig. 3 and Fig. 4 show the IV characteristic of the three diodes. It is observed that the on-state voltage of SiC MPS diode is the highest followed by that of the SiC JBS diode and Silicon PiN diode. The higher on-state voltage of SiC devices is due to the larger junction voltage because of the much lower intrinsic carrier concentration. At high temperatures, the junction voltage is found to decrease by the increase of intrinsic carrier concentration, while the temperature stability of SiC device leads to the convergence of I-V curves as in Fig. 3. Fig. 5 highlights the conductivity modulation effect observed during the self-heating of Silicon PiN diode since a less voltage increment is observed at high currents. However, the conductivity modulation is not observed in SiC JBS and MPS diode as they are primarily functioning

Fig. 2: (A) The equivalent circuit and (B) devices connection for On-State measurements.

as Unipolar devices with a large built-in voltage of the SiC P-N junction of about 3 V confirmed by the experiments.

Fig. 3: The I-V characteristics of Silicon PiN, SiC JBS and SiC MPS diode.

Fig. 4: The I-V characteristics of the 3 diode compared with each other at 25°C & 175°C.

Fig. 5: On-state voltage during self-heating for Silicon PiN, SiC JBS and SiC MPS diode at 25°C.

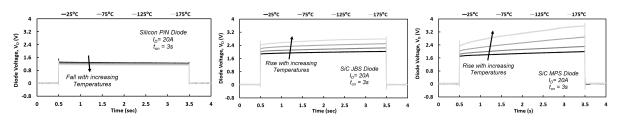

Fig. 6 also shows the negative temperature dependence of the on-state voltage of Silicon PiN diode at the on-state. In contrary to the Silicon PiN diode, the positive temperature dependence for SiC devices, especially for SiC MPS diode, is also observed. This is because the increased current levels across the series resistance causes the forward voltage to have a positive temperature coefficient. The absence of conductivity modulation is beneficial for the JBS diode because it favours the unipolar conduction through the JBS structure which is designed to block high voltage while maintaining its unipolar conduction mode. However, this is a crucial disadvantage of MPS diodes which is expected to have high level injection. This property is suitable for high frequency application as the low stored charge and thus

the fast-switching transient is maintained. Nevertheless, it is not beneficial for parallel connection of the Silicon PiN diodes with negative temperature dependence of on-state voltage [13, 14, 15]. A positive feedback loop between current and temperature is generated since the hotter diode with lower voltage can conduct more current which will continue to increase until failure. Fig. 5 and Fig. 6 also show larger on-state voltage at high currents and at high temperatures in SiC devices, further increases during the on-state. The on resistance is further increased due to the negative temperature coefficient of the carrier mobility.

Fig. 6: On-state voltage during self-heating for Silicon PiN, SiC JBS and SiC MPS diode at 175°C.

#### **Unclamped Inductive Switchings**

The single event avalanche ruggedness of Silicon PiN, SiC JBS and SiC MPS diodes have been investigated through a wide scale of UIS measurements. All the devices are fabricated in a standard TO-220 package as shown in Table. I. The UIS testing board is shown in Fig. 7 with a high voltage IGBT (IXBX55N300) acting as the power switch [16]. The initial temperature of diodes before each UIS event is controlled in the same way as that of on-state measurement. A load inductor of 1.25 mH is charged to the peak avalanche current that is proportional to the length of the gate pulse  $L_P$ , ranging at 80  $\mu$ s & 160  $\mu$ s, and also proportional to the initial DC link voltage  $V_{DC}$  increased from 90 V to 360 V. Two GW-Instek GDP-100 100 MHz voltages probes and a CWT Ultra-mini 50 MHz Rogowski current coil (CWT1) are used to capture voltage and current waveforms while both are shown in the same oscilloscope as that for the on-state measurement.

Fig. 7: The UIS test circuit schematic and the test board.

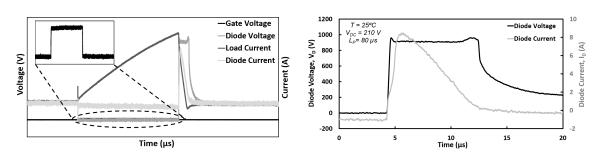

Typical current and voltage waveforms in a single UIS event is shown in Fig. 8. When the IGBT switches off, the current flowing through the inductor starts to decrease. Since a counter Electromagnetic Force (EMF) will be induced to resist the abruptly change of inductor current, the peak over-voltage transient voltage  $V_{PK}$  can be derived [17, 18] as:

$$V_{PK} = L \times \frac{dI_{off}}{dt} \tag{1}$$

Where *L* is the load inductance,  $\frac{dI_{off}}{dt}$  is the rate of change of current at turn-off. Such surge voltage usually reaches the breakdown voltage [19] of the diode (*V*<sub>BR</sub>), conducting the avalanche current and remain steady under higher DC link voltage. The resulting power dissipation cause the surge of junction temperature, degrades the diode breakdown ruggedness or destroys the device as the hotspot at junction

termination with potential for melting of the anode metallization [9]. Unlike the power diodes which will suffer high electrothermal stress, the IGBT will stay safe due to the much higher voltage/current ratings (voltage of 3 kV & steady-state current of 55 A at 110°C). The increase of DC link voltage is used to increase the rate of current turn-on  $(\frac{diI_{on}}{dt})$ , because:

$$V_{DC} = L \times \frac{dI_{on}}{dt} \tag{2}$$

Fig. 8: Typical waveforms under UIS test and its zoomed-in version.

Therefore, the load current is proportional to the DC link voltage. To monitor the device degradation before & after the single UIS test, the I-V characteristic of all three diodes has also been measured. Fig. 9 shows the degradation of the IV characteristics of those diodes under test. Unlike the repetitive UIS test which imposes the same thermal stress for all UIS pulses, the single UIS tests aim to fail the device with just a few progressively prolonged pulses. Meanwhile, all three devices under test show stable behaviour with minor degradation at 25°C and at 175°C during the single UIS tests, when compared with the forward degradation in [11]. Therefore, this single UIS test methodology are shown to be reliable while the devices' degradation is also found to have a limited impact on their failure.

Fig. 9: Forward voltage degradation of the IV characteristics at 25°C and at 175°C for Silicon PiN, SiC JBS and SiC MPS diode.

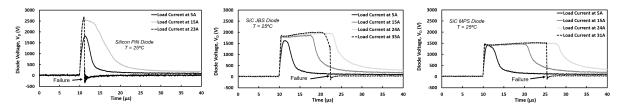

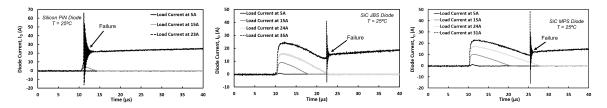

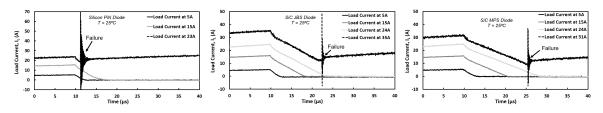

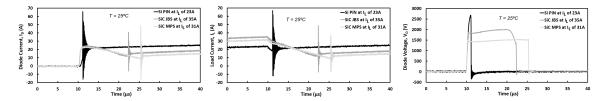

Fig. 10 and Fig. 11 show the zoomed-in view of UIS waveforms for diodes with different technologies with load current increased until failure of devices. Although all three diodes are rated at 1.2 kV, a much higher breakdown voltage, especially for the Silicon PiN diode can be observed. This is mainly because the Schottky contact which causes higher leakage current when reverse biased is not present in the Silicon PiN diode structure. At load current of 5A, the diode voltage cannot reach the breakdown voltage in SiC devices. This is because the stored energy inside the load inductor is not sufficient to keep charging the parasitic capacitor inside the diode to the breakdown voltage, as expected by Equation 1. It can also be seen in Fig. 11 and in Fig. 12 that the higher effective breakdown voltage of Silicon PiN leads to much lower diode current compared to that of SiC devices. This is the leakage current instead of the avalanche current. The avalanche duration increases with increase of load current while the tail current indicates the process to discharging parasitic capacitor. Fig. 11 and Fig. 12 shows that the current decrease rate of SiC MPS diode is smaller than that of SiC JBS diode. This is because of the larger drift velocity in JBS diode due to the higher electric field applied. When the device failure occurs, the diode conducts in the reverse conduction with increasing current exceeding the preset load current levels because of the

avalanche multiplication effect together with the thermal runaway effect, while the diode voltage drops to zero as the blocking capability is lost. Silicon PiN diode failed at lower load current compared with the SiC JBS & SiC MPS while its recovery process, as in Fig. 11, has been skipped as the device cannot handle such high induced avalanche current.

Fig. 10: Avalanche diode voltage as a function of time for different load currents until device failure for Silicon PiN diode, SiC JBS diode and SiC MPS diode.

Fig. 11: Avalanche diode Current as a function of time for different load currents until device failure for Silicon PiN diode, SiC JBS diode and SiC MPS diode.

Fig. 12: Avalanche load current as a function of time for different load currents until device failure for Silicon PiN diode, SiC JBS diode and SiC MPS diode.

Fig. 13 and Fig. 14 emphasize the difference in avalanche ruggedness among three different diodes at failure mode. It is seen that the SiC devices can sustain the avalanche conduction for a longer time than that of Silicon device before the avalanche multiplication is triggered. In contrast with the diode current of Silicon devices which is increased to the preset load level immediately after the failure, the rate of current increase is found to be much smaller. This is because of the much smaller impact ionization coefficients in SiC devices which enables a slower generation process of electron-hole pairs [20]. It can also be seen that the highest breakdown voltage in Silicon PiN diode, followed by that of SiC JBS and that of MPS. At high temperatures, all devices is found to fail at lower currents with shorter recovery period. This can be explained by the fact that there is less headroom to dissipate power during the recovery process when the temperature of controller is increased even though the less avalanche energy is generated due to the smaller load current.

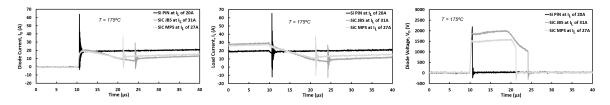

The avalanche energy is an important parameter since the avalanche breakdown mechanism of power rectifiers is avalanche energy breakdown as a high induced power increase the junction temperature to destroy the devices. The critical avalanche energy is determined as the maximum value before failure of the device during the progressive single UIS tests as highlighted in Fig. 15, can be derived as:

$$E_{ava} = \int_0^{t_{ava}} V_{diode}(t) \cdot I_{diode}(t) \cdot dt$$

(3)

where  $t_{ava}$  is the time duration of device avalanche.

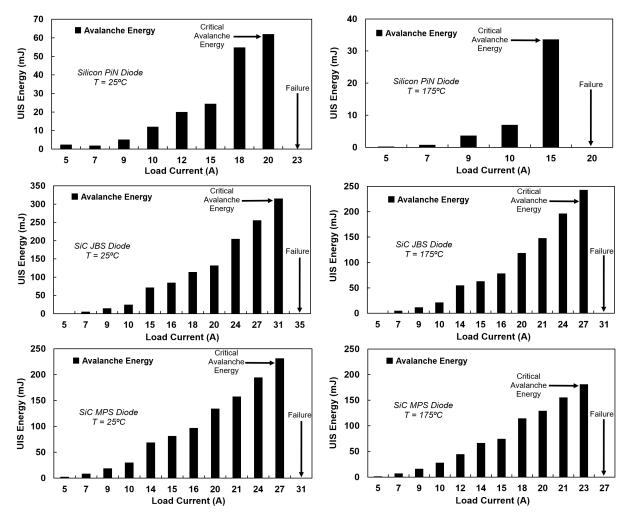

Fig. 13: The (left) diode current, (center) load current, and (right) diode voltage when failure occurs at 25°C.

Fig. 14: The (left) diode current, (center) load current, and (right) diode voltage when failure occurs at 175°C.

Fig. 15: Determination of critical avalanche energy from the UIS test at 25°C and at 175°C.

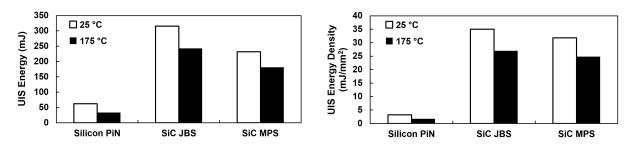

The critical avalanche energy of SiC JBS is the highest, followed by that of SiC MPS, and then that of Silicon PiN diode. This is expected from Fig. 11 and Fig. 10 as the recovery time after the event dominates the avalanche energy. The critical energy is found to be lower at higher temperatures. This is because of the shorter recovery period observed at high temperatures, primarily due to the smaller

difference between the junction temperature and the preset temperature making the energy dissipation more difficult. Despite the Silicon PiN diode able to sustain a higher reverse voltage compared to SiC devices before the actual failure takes place, this device always failed at lower load currents during the progressive UIS tests. Fig. 16 shows the CT scan image of the three devices after failure. The three devices have similar packaging, though with different dies areas, and thus it is conceived that the packaging has limited impact on difference between the results of devices. The failure pattern of three test devices indicate that the molten anode metallization is likely to have happened, especially at elevated temperatures similar to that in [11], leading to failures of the die and subsequently wire-bonds.

Fig. 16: Corresponding front side CT scan image of the devices from Fig. 13 for Silicon PiN diode, SiC JBS and SiC MPS diode.

Fig. 17: Comparison of critical avalanche energy for Silicon PiN, SiC JBS & SiC MPS diode at different temperatures.

The factors that would influence the higher avalanche ruggedness of the SiC devices compared with the Silicon PiN, excluding the packaging, can be listed with the following factor. The thermal conductivity of SiC is two times higher than that of Silicon for a more effective heat dissipation. In addition, the widebandgap of SiC limits the generation of additional carriers due to the higher thermal energy [21, 22, 23]. The lower carrier lifetime of SiC also enables a faster recombination of the thermally generated carriers. Additionally, the impact ionization coefficient of SiC devices is smaller than Silicon, so less electronhole pairs are generated at reverse bias. All of these would lead to a better performance of the SiC diodes than the Silicon counterparts as demonstrated in the measurements of this paper.

#### Conclusion

In this paper, the on-state performance and avalanche ruggedness of Silicon PiN diode, SiC JBS diode, and SiC MPS diode have been investigated by means of wide-scale experimental measurements in a range of temperatures to up to 175°C. It is shown that the Silicon PiN diodes have a lower on-state voltage compared with SiC JBS diode and SiC MPS diode, enabling a lower steady-state power dissipation while the negative temperature dependence of diode voltage further decreases the losses at the conduction mode and at high temperatures. On the other hand, SiC MPS diode and SiC JBS diode have shown positive temperature coefficient and a positive feedback loop is observed. The conductivity modulation effect is only observed for Silicon PiN diode at high currents, while the built-in voltage of P-N junction in SiC devices is larger which favors high-speed operation. In terms of the UIS measurements, the difference in device packaging have negligible influence to the single UIS tests. Although the Silicon PiN diode exhibits the highest breakdown voltage among these three similarly-rated power devices, the SiC JBS diode is the most electrothermally rugged devices, followed by that of the SiC MPS diode, and then the Silicon PiN diode, as is reflected by the measurement results and the calculated avalanche energy.

#### References

- [1] S. Jahdi, et al., 'Renewable hybrids Grid-Connection using converter interferences' International Journal of Sustainable Energy Development (IJSED), vol. 2, no. 1, 2013.

- [2] J. Baliga, 'Advanced Power Rectifier Concepts', Springer US, 2009.

[3] C. Shen, et al., 'Prospects and Challenges of 4H-SiC Thyristors in Protection of HB-MMC-VSC-HVDC Converters,' in IEEE Open Journal of Power Electronics, vol. 2, pp. 145-154, 2021. [4] B. Thomas, 'SiC Schottky Diode Device Design: Characterizing, Performance & Reliability', Wolfspeed, A

- Cree Company, 2015.

- [5] J. Liu, et al., 'Reliability consideration of low-power grid-tied inverter for photovoltaic application,' 24th European Photovoltaic Solar Energy Conference and Exhibition, Germany, Sep. 2009.

- [6] S. Yang, et al., 'An industry based survey of reliability of power electronic converters,' IEEE Trans. Ind. Appl., vol. 47, no. 3, pp. 14411451, May 2011.

- [7] S. Jahdi, et al., 'Electrothermal modeling and characterization of SiC Schottky and silicon PiN diodes switching transients', IEEE Energy Conversion Congress and Exposition (ECCE), 2014, pp. 2817-2823.

- [8] J.W. Hancock, 'SiC Device Applications: Identifying and Developing Commercial Applications', 2006.

[9] T. Basler, et al., 'Avalanche Robustness of SiC MPS Diodes', PCIM Europe 2016; Int. Exhibition and Conf.

- for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2016, pp. 1-8. [10] R. Rupp et al., 'Avalanche behaviour and its temperature dependence of commercial SiC MPS diodes: Influ-

- ence of design and voltage class,' IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2014, pp. 67-70. [11] S. Palanisamy, et al., 'Repetitive surge current test of SiC MPS diode with load in bipolar regime,' IEEE 30th

- International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2018, pp. 367-370.

- [12] J. Ortiz Gonzalez, et al., 'Dynamic characterization of SiC and GaN devices with BTI stresses', Microelectronics Reliability, vol. 100101, pp. 113389, 2019.

- [13] R. Wu, et al., 'Performance of Parallel Connected SiC MOSFETs under Short Circuits Conditions', Energies, 2021, 14, 6834.

- [14] R. Wu, et al., 'Measurement and simulation of short circuit current sharing under parallel connection: SiC MOSFETs and SiC Cascode JFETs', Microelectronics Reliability, vol. 126, 2021, 114271.

- [15] R. Wu, et al., 'Current Sharing of Parallel SiC MOSFETs under Short Circuit Conditions', 23rd European Conference on Power Electronics and Applications (EPE'21 ECCE Europe), 2021, pp. 1-9.

- [16] R. Bonyadi, et al., 'Physics-based modelling and experimental characterisation of parasitic turn-on in IG-BTs,' 17th European Conf. on Power Electronics and Applications (EPE'15 ECCE-Europe), 2015, pp. 1-9.

- [17] Renesas, Unclamped Inductive Switching (UIS) Test and Rating Methodology Application note.

- [18] Toshiba, MOSFET Avalanche Ruggedness Application note.

- [19] P. Alexakis, et al., 'Improved Electrothermal Ruggedness in SiC MOSFETs Compared With Silicon IGBTs,' in IEEE Transactions on Electron Devices, vol. 61, no. 7, pp. 2278-2286, July 2014.

- [20] J. Baliga, 'Fundamentals of Power Semiconductor Devices', Springer US, 2019.

[21] S. Jahdi, et al., 'The Impact of Temperature and Switching Rate on Dynamic Transients of High-Voltage Silicon and 4H-SiC NPN BJTs: A Technology Evaluation,' in IEEE Transactions on Industrial Electronics, vol. 67, no. 6, pp. 4556-4566, June 2020. [22] S.N. Agbo, et al., 'UIS performance and ruggedness of stand-alone and cascode SiC JFETs', Microelectron-

- ics Reliability, Volume 114, pp. 113803, 2020.

- [23] E. Bashar, et al., 'Comparison of Short Circuit Failure Modes in SiC Planar MOSFETs, SiC Trench MOS-FETs and SiC Cascode JFETs', IEEE 8th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2021, pp. 384-388.