# UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                       | An Improved linearity ring oscillator-based current-to-digital converter                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Author(s)                   | Wall, Anthony; Walsh, Paul; Sadeghipour, Khosrov; O'Connell, Ivan; O'Hare Daniel                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Publication date            | 2022-08-11                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Original citation           | Wall, A., Walsh, P., Sadeghipour, K., O'Connell, I. and Hare D. (2022) 'An Improved Linearity Ring Oscillator-Based Current-to-Digital Converter', IEEE Solid-State Circuits Letters, 5, pp. 202-205. doi: 10.1109/LSSC.2022.3198367                                                                                                                                                            |  |  |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Link to publisher's version | https://doi.org/10.1109/LSSC.2022.3198367 http://dx.doi.org/10.1109/LSSC.2022.3198367 Access to the full text of the published version may require a subscription.                                                                                                                                                                                                                              |  |  |  |  |

| Rights                      | © 2022 IEEE. Personal use of this material is permitted.  Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works |  |  |  |  |

| Item downloaded from        | http://hdl.handle.net/10468/13637                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

Downloaded on 2022-12-08T08:40:51Z

# An Improved Linearity Ring Oscillator Based Current to Digital Converter

Anthony Wall, Student Member, IEEE, Paul Walsh, Member, IEEE, Khosrov Sadeghipour, Member, IEEE, Ivan O'Connell, Senior Member, IEEE, Daniel O'Hare, Member, IEEE,

Abstract—Many biosensors produce single-ended current outputs. Lab-on-chip applications demand parallel readout channels requiring low area current-to-digital converters. High HD2 has limited the Current Controlled Ring Oscillator's adoption as a low area, single-ended converter. This work improves CCRO open loop linearity by 10 dB. A wide-bandwidth current buffer is also designed. A low area (0.0025 mm²), low power (357  $\mu\mathrm{W}$ ), single-ended, 1 MHz bandwidth converter suitable for array readout is presented with measured performance.

Index Terms—Data Converters, ADC, Current, Ring Oscillator, Phase to Digital, Current to Digital, VCO Based ADC, Direct Digitization, Flipped Voltage Follower, Linearization Techniques

#### I. Introduction

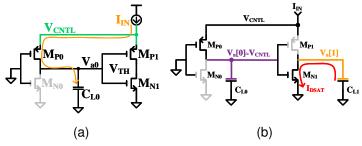

THE COVID-19 pandemic has created a surge in demand for new biosensors to detect viruses and other microorganisms. Many yield an output current proportional to their stimulus e.g. electrochemical sensors, photodiodes, nanopore sensors, ISFETs etc. Lab-on-chip applications also require multiple sensors and multiple readout channels in parallel [1]. We propose a low area, low power, single-ended currentto-digital converter (CDC) which can be used in an array to readout multiple biosensors in parallel. Presently, the use of Transimpedance Amplifiers and subsequent voltage-mode ADCs limits the area and power efficiency of existing readout circuits. In this work, a Current Controlled Ring Oscillator (CCRO) is implemented as a low area CDC solution. HD2 is the performance limitation in CCROs. While pseudodifferential architectures are a common workaround, most biosensors yield a single-ended current so can't exploit differential HD2 cancellation. An improved single-ended open loop CCRO with 10 dB improved linearity, compared to a traditional CCRO, provides the highest open-loop linearity seen to date in a CCRO. The proposed architecture is shown in Fig. 1. It consists of a Flipped Voltage Follower (FVF) current buffer and an open loop CCRO-based ADC.

### II. THE PROPOSED CIRCUIT

#### A. Flipped Voltage Follower

The FVF [2], shown in Fig. 1, is a current buffer achieving superior bandwidth compared to a traditional Common Gate (CG) stage. It achieves this with the same power consumption, noise and current dynamic range as the CG by using negative

Manuscript received Xxxxxx xx, 202x; revised Xxxxxx xx, 202x; accepted Xxxxxx xx 202x. Date of publication Xxxxxx xx 202x; date of current version Xxxxxx xx 202x. This article was approved by xxxxxx xxxxxx xxxxxx (Corresponding Author: Anthony Wall)

Anthony Wall, Ivan O'Connell & Daniel O'Hare are with MCCI, Tyndall National Institute, Cork, T12 R5CP, Ireland. (e-mail: anthony.wall@mcci.ie) Paul Walsh & Khosrov Sadeghipour are with Infineon Technologies AG, 3 Lee House, Riverview Park, Blackrock, Cork, T12 F76C, Ireland

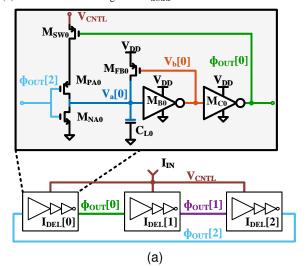

Fig. 1. Proposed readout with FVF current buffer and CCRO CDC.

feedback. The FVF's operation is examined by considering a small voltage increase  $\partial v_{in}$  at the IN pin. The drain of  $M_2$  is HiZ; no current can flow downwards, but the source of  $M_1$  has an impedance  $1/g_m^{M1}$ , so current  $\partial i_{M_1}$  flows through  $M_1$  to the  $V_{G2}$  node. This node is high impedance (dominated by  $r_o^{M_1}$  and  $r_o^{M_3}$ ), so  $\partial i_{M_1}$  causes voltage increase at  $V_{G2}$ ,  $\partial v_{G2}$ . This actuates the gate of  $M_2$  and thus additional current  $\partial i_{M_2}$  flows through  $M_2$ . This  $\partial i_{M_2}/\partial v_{in}$  is akin to the input impedance of a CG multiplied by  $g_m r_o$ .  $Z_{IN}$  of the FVF is thus:

$$Z_{IN} \simeq \frac{1}{g_m^{M_1} \left(1 + \frac{1}{2} g_m^{M_2} Z_{g2}\right)} \simeq \frac{2}{g_m^2 r_0} = \frac{2Z_{IN}^{CG}}{A_0}$$

(1)

assuming  $Z_{IN}^{CCRO}=1/g_m^{M2}$ . Since  $Z_{g2}\simeq r_o^{M_1}$  is the impedance at the  $V_{G2}$  node,  $Z_{IN}$  is decreased by  $A_0$ , the intrinsic gain of a device, compared to a CG. Thus the FVF has a wider 3 dB point than the CG by the same margin:

$$f_{3dB}^{FVF} \simeq A_0^{M_1} \frac{I_{BIAS} (g_m/I_D)_{M_2}}{4\pi C_{IN}}$$

(2)

assuming the pole due to the parasitic capacitance,  $C_p$ , at  $V_{G2}$  is much greater than that due to  $C_{IN}$ .

Comparing the FVF and CG in simulation, given the same bias current (3  $\mu$ A) and load ( $C_{in}=1~\mathrm{pF}$ ), the bandwidth of the FVF ( $f_{3dB}=101~\mathrm{MHz}$ ) is  $8.4\times$  that of the traditional CG ( $f_{3dB}=12~\mathrm{MHz}$ ). Usually [2], the output current is taken by mirroring M2 but in this work, the CCRO is under the FVF; reusing the FVF  $I_{BIAS}$  to bias the CCRO, saving power.

# B. Improved Linearity CCRO

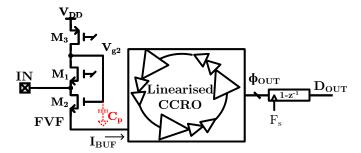

Previous single ended, open loop, uncorrected, MHz bandwidth CCROs have been limited by linearity to  $< 6\,$  b ENOB [3]. This work extends linearity to  $> 8.6\,$  b without feedback or calibration. Fig. 2a shows a traditional, inverter-based 3-element CCRO, its waveforms shown in Fig 2b. Ideally, the cell charges from GND to the  $V_{TH}$  of the next inverter, ending the charging phase and beginning another. The equation for such an oscillator would be:

$$f_{CCRO}(t) = I_{IN}(t)/\left(3C_L V_{TH}\right) \tag{3}$$

(a)

Fig. 2. Inverter-based 3-element CCRO (a) schematic and (b) waveforms. however the circuit possesses significant non-linearities. These non-linearities are derived from two main sources, namely that  $V_{CNTL}$  is not constant but varies with  $I_{IN}(t)$  and that the finite time required to discharge each cell in the ring adds an additional delay into the ring named the dead time,  $t_{dead}$ .

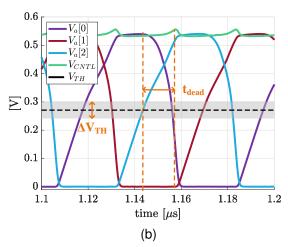

Fig 3a shows that as the input current,  $I_{IN}$  charges the delay cell load capacitor,  $C_L$ , the  $V_{CNTL}$  node voltage is set by  $V_{GS}$  of the PMOS device, in this case  $M_{P0}$ .  $V_{CNTL}$  is the supply node for all the inverters in the CCRO, and so as  $V_{CNTL}$  changes due to  $I_{IN}$ , the threshold,  $V_{TH}$ , of the other delay cell inverters in the ring also changes. This causes the  $V_{TH}$  term in Eqn. 3 to have a log-like relationship with  $I_{IN}$  and results in a very non-linear transfer charateristic. Once a delay cell has completed charging, a cell discharge must occur in order for the phase to propagate around the ring (as seen in Fig. 2b). This takes a finite time, known as the dead time,  $t_{dead}$ , and since the oscillator phase is not advanced during  $t_{dead}$ , the transfer characteristic is modified:

$$f_{CCRO}(t) = \frac{1}{(3C_L V_{TH}/I_{IN}(t)) + 3t_{dead}}$$

(4)

The cell discharge mechanism is shown in Fig. 3b. When  $V_a[0]$  reaches  $V_{TH}$  of the inverter formed by  $\{M_{P1}, M_{N1}\}$  (and continues toward  $V_{CNTL}$ ),  $C_{L1}$ , initially charged to  $V_{CNTL}$  begins to discharge through  $M_{N1}$ . The time taken for this node,  $V_a[1]$  to fall below  $V_{TH}$  and thus for the phase to propagate is  $t_{dead}$ , shown in Fig. 2b.  $t_{dead}$  depends on  $I_{DSAT}^{M_{N1}}$ , which, since  $V_{GS}^{M_{N1}} \simeq V_{CNTL}$ , has an approximately linear inverse relationship with  $I_{IN}$ . The CCRO linearity is greatly improved by keeping  $V_{TH}$  constant across  $I_{IN}$  and reducing

Fig. 3. Schematics illustrating (a) the effect of  $I_{IN}$  on  $V_{CNTL}$  and  $V_{TH}$  and (b) the finite cell discharge time  $t_{dead}$ .

Fig. 4. (a) Schematic and (b) associated waveforms of the improved CCRO.  $t_{dead}$  as much as possible. Recent work [4] placed squaring inverters at the output of each delay cell, making inverter  $V_{TH}$  constant and reducing  $t_{dead}$  by driving the NMOS with a rail-rail signal. Silicon results were not provided, however, and several shortcomings were noted upon simulation, namely residual nonlinearities due to parasitic charging of multiple cells in parallel and metastability at low input currents.

An improved CCRO implementation is shown in Fig. 4a, comprising of 3 delay cells which reduces  $t_{dead}$  and the dependence of  $V_{TH}$  on  $I_{IN}$  .  $M_{B0}$  is a supply-connected inverter, so its  $V_{TH}$  is constant and thus the  $V_{TH}$  required for the phase to propagate to the next cell is always constant and independent of  $I_{IN}$ . The second squaring inverter,  $M_{C0}$ provides the necessary inversion and ensures that the output of the cell is rail-to-rail (See  $\Phi_{OUT}[2]$  in Fig. 4b). Thus, the first inverter NMOS of the subsequent cell (e.g.  $M_{NA0}$  shown in Fig. 4a) has  $V_{GS} = V_{DD}$  and the highest possible  $I_{DSAT}$ , greatly reducing the discharge time,  $t_{dead}$ .  $t_{dead}$  now consists of the reduced discharge time, and also the propagation delay of the  $M_B$  and  $M_C$  inverters. The total delay is < 200 ps inthe implemented circuit (see zoomed-in waveform of Fig. 4b) as compared with the 10 ns seen at the same bias point in the traditional CCRO (Fig. 2b).

At very low input currents, the cell's  $V_a$  node charges slowly, causing the  $M_B$  inverter to transition slowly; resulting in large short-circuit current consumption and large  $t_{dead}$ . A positive feedback device,  $M_{FB}$ , was placed around the  $M_B$ inverter such that when  $V_a$  approaches  $V_{TH}^{M_B}$ ,  $M_{FB}$  begins to turn on and latches  $V_a$  to  $V_{DD}$ , causing  $M_B$  to transition quickly at all input current levels. This is seen in the zoomedin section of Fig. 4b; as  $V_a[0]$  slowly approaches  $V_{TH}$ , it is suddenly latched to  $V_{DD}$  as soon as  $V_{TH}$  is reached. In a 3element CCRO, two cells' PMOS  $M_{PA}$  are on at any given time (as seen by two  $\Phi_{OUT}$  signals being LOW at any given time in Fig. 4b). This is true of the traditional CCRO also and provides two paths for  $I_{IN}$ ; the primary charging cell path and another secondary path into a cell which has already completed charging. Some unknown portion of  $I_{IN}$  will leak into the secondary path and not contribute to the main cell charging, another source of non-linearity. A device,  $M_{SW}$  is added to ensure that only one primary cell charging path is available in the CCRO so all of  $I_{IN}$  contributes to the charging of the delay cell. The gate of  $M_{SW}$  is low until the cell has received its charge, then  $\Phi_{OUT}$  transitions high, turning off  $M_{SW}$  and preventing any further charging until the next cycle.

The  $t_{dead}$  is now the only significant contributor to CCRO nonlinearity. The level of harmonic distortion is a function of the cell charge time to  $t_{dead}$  ratio, so  $HD2 \propto I_{IN}t_{dead}/3C_LV_{TH}$ . This presents a tradeoff with the input-referred quantisation noise of the CCRO, which is proportional to  $1/K_{CCRO}$ , where  $K_{CCRO} = 1/(3C_LV_{TH})$ .  $V_{TH}$  was fixed by the headroom requirements of the FVF atop the CCRO, so  $C_L$  was adjusted so that the input-referred quantisation noise of the converter falls just below the input-referred thermal noise but is still large enough to provide sufficient linearity. A value of  $\sim 120~{\rm fF}$  was chosen for  $C_L$ , implemented as a combination of MOM capacitor and the MOS capacitance of the  $M_B$  inverter. Simulation results show that the input-referred phase noise of the improved oscillator is the same as the traditional oscillator.

#### III. MEASUREMENT RESULTS

The FVF and CCRO are coupled to form the CDC, implemented in a 65 nm CMOS process, at a supply voltage of 1.2 V. The transfer characteristics of both the traditional (simulated) CCRO and the improved (measured) CCRO are

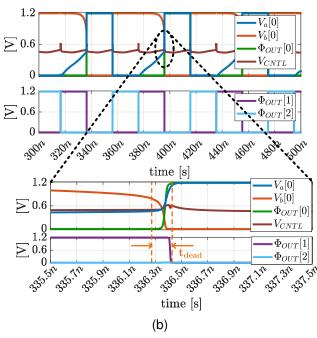

Fig. 5. CCRO transfer characteristic comparison between traditional and measured CCRO

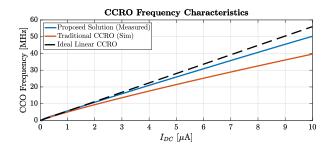

Fig. 6. Plot of HD2 vs.  $I_{IN}$  comparing the traditional and measured results from the improved CCRO.

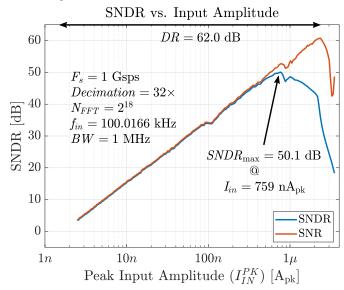

Fig. 7. Measured dynamic range plot of the CDC.

shown in Fig. 5. At the 3  $\mu$ A bias point, the centre frequency is  $f_0 \simeq 16~\mathrm{MHz}$  and the CCRO gain is  $K_{CCRO} \simeq 5~\mathrm{MHz}/\mu$ A. The improved CCRO closely approximates the linear characteristic of an ideal CCRO. The traditional CCRO shows 16 % gain deviation at 3  $\mu$ A  $\pm$  2  $\mu$ A compared to 9 % for the improved oscillator. This improved static linearity results in lower harmonic distortion, which is illustrated in Fig. 6. The improved CCRO presents consistently lower HD2, being 9.75 dB lower at the peak SNDR point.

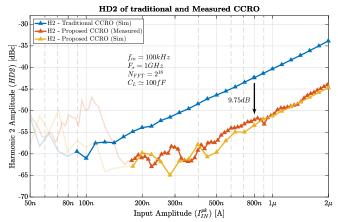

The CDC is sampled at 1 GS/s using a 1st order difference

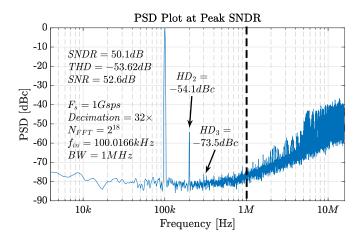

Fig. 8. FFT plot at peak SNDR.

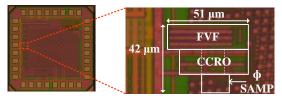

Fig. 9. Die micrograph showing zoomed-in view of the CDC.

DFF+XOR arrangement and then decimated by 32 to bring the data off-chip. The dynamic range of the CDC is shown in Fig. 7. The plot shows a noisefloor at  $\sim 1.85 \text{ nArms}$ limited by FVF thermal noise and CCRO quantisation noise. Beyond the peak SNDR point, the SNDR is instead limited by distortion - specifically the CCRO HD2. Once the input amplitude approaches the 3  $\mu$ A FVF bias current, the oscillator and FVF become increasingly non-linear. Taking the input range as  $\sim 1.85~{\rm nA_{pk}} \rightarrow 2.35~\mu{\rm A_{pk}}$ , the dynamic range is 62.0 dB. The notches seen in the SNDR plot at 100 nApk and 1  $\mu$ Apk are due to the CCRO pulse-frequency modulated tone (PFM) harmonics aliasing in-band due to the decimation filter. An FFT is shown for the peak SNDR case in Fig. 8. The flicker noise corner is seen at  $\sim 30~\mathrm{kHz}$  and the 1st order noise shaping corner at  $\sim 700$  kHz. It is clear that the harmonic distortion is limited by HD2 of the CCRO, with HD3 being close to the noisefloor. Aliased PFM tones can be seen just out of band, and these tones aliasing in-band at certain amplitudes limits performance also.

Fig. 9 shows the CDC's area to be  $0.0025~\mathrm{mm^2}$ , with the FVF current source consuming the majority of the area (for low flicker noise). The CDC consumes a total power of  $357.6~\mu\mathrm{W}$  with the CCRO consuming 81 %, the FVF consuming 14 % and the 1st difference phase sampler consuming 5 %. Table I shows a comparison with the state of the art. [5] is pseudo-differential and uses an analog control loop to stabilise  $V_{CNTL}$ , limiting scalability and power efficiency. [6] uses an input resistor network to compensate for CCRO nonlinearity, but requires a voltage input and is not robust to PVT variation. It was sampled off-chip at  $10~\mathrm{Gs/s}$ ; the power consumption of which is not included in the analysis, inflating the reported SNDR and FoM. [7] appears to use a large delay cell capacitance to linearise the transfer function at the cost of higher quantisation noise, which is counteracted

TABLE I COMPARISON WITH THE STATE OF THE ART.

| Specification                        | This Work            | [5]                                  | [6]                                         | [7]                       | [8]                                     |

|--------------------------------------|----------------------|--------------------------------------|---------------------------------------------|---------------------------|-----------------------------------------|

| Architecture                         | OL CCRO              | OL CCRO                              | OL CCRO                                     | OL CCRO                   | OL CCRO                                 |

| Non-Linearity<br>Correction          | Improved<br>Squaring | V <sub>CNTL</sub> Regulation         | Input Resistor<br>Network<br>& Cancellation | Large Load<br>Capacitance | Non-Linear<br>Feedback<br>& Calibration |

| Single-Ended/<br>Pseudo-Differential | SE                   | PD                                   | SE                                          | SE                        | SE                                      |

| Technology [nm]                      | 65                   | 180                                  | 65                                          | 130                       | 130                                     |

| Supply Voltage [V]                   | 1.2                  | 1.8                                  | 1.0                                         | 1.8                       | -                                       |

| Max Input                            | $6 \mu A_{pp}$       | $\sim 37~\mu  m A_{ m diff}^{ m pp}$ | $1 V^{pp}$                                  | $640~\mathrm{mV^{pp}}$    | $400~\mathrm{mV^{pp}}$                  |

| DR [dB]                              | 62.0                 | -                                    | $\sim 70$                                   | 93.5                      | 66                                      |

| HD2 [dBc]                            | 54.1                 | 83.8 ***                             | 51                                          | $\sim 76$                 | $\sim 61$                               |

| HD3 [dBc]                            | 74                   | 84 ***                               | 74                                          | $\sim 88$                 | $\sim 75$                               |

| SNDR [dB]                            | 50.1                 | 68.2 ***                             | 56                                          | 69.6                      | 60.2                                    |

| BW [MHz]                             | 1                    | 1                                    | 2                                           | 0.02                      | 2                                       |

| Power [µW]                           | 357.6                | 2,900                                | 650 *                                       | 280                       | 25,000 **                               |

| Area [mm <sup>2</sup> ]              | 0.0021               | 0.03                                 | 0.0015 *                                    | 0.02                      | 0.048                                   |

| Schreier FoM<br>(SNDR) [dB]          | 143.9                | 153.6 ***                            | 150.9 *                                     | 148.1                     | 139.23 **                               |

| Walden FoM [fJ/conv - step]          | 684                  | 1910 ***                             | 315 *                                       | 2835                      | 3000 **                                 |

\*Offchip Input Buffer & Sampling at 10GS/s, Power & Area not Included \*\* Pad Driver Power Included

#### IV. CONCLUSION

Table I shows a lack of single-ended, open-loop, current-mode CDCs. All existing solutions are either pseudo-differential or voltage mode, limiting their power and area efficiency and their suitability for use with single-ended sensors. The improved squaring delay cell with positive feedback and cell selection results in the lowest area, lowest power open-loop, single-ended, MHz-bandwidth CCRO-based CDC.

## REFERENCES

- [1] C. L. Hsu, A. Sun, Y. Zhao, E. Aronoff-Spencer, and D. A. Hall, "A 16×20 electrochemical CMOS biosensor array with in-pixel averaging using polar modulation," in 2018 IEEE Custom Integrated Circuits Conference, CICC 2018. IEEE, Apr. 2018, pp. 1–4.

- [2] J. Ramirez-Angulo, R. G. Carvajal, A. Torralba, J. Galan, A. P. Vega-Leal, and J. Tombs, "The flipped voltage follower: A useful cell for lowvoltage low-power circuit design," in *Proceedings - IEEE International Symposium on Circuits and Systems*, vol. 3. Phoenix, AZ: IEEE, 2002, pp. III–615–III–618.

- [3] J. Kim, T. K. Jang, Y. G. Yoon, and S. H. Cho, "Analysis and design of voltage-controlled oscillator based analog-to-digital converter," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 1, pp. 18–30, 2010.

- [4] L. M. Alvero-Gonzalez, E. Gutierrez, and L. Hernandez, "A Highly Linear Ring Oscillator for VCO-based ADCs in 65-nm CMOS," in 2018 25th IEEE International Conference on Electronics Circuits and Systems, ICECS 2018. Institute of Electrical and Electronics Engineers Inc., Jan. 2019, pp. 465–468.

- [5] M. Voelker, S. Pashmineh, J. Hauer, and M. Ortmanns, "Current feedback linearization applied to oscillator based ADCs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 11, pp. 3066–3074, Nov. 2014.

- [6] A. Babaie-Fishani and P. Rombouts, "Highly linear VCO for use in VCO-ADCs," *Electronics Letters*, vol. 52, no. 4, pp. 268–270, Feb. 2016.

- [7] F. Cardes, E. Gutierrez, A. Quintero, C. Buffa, A. Wiesbauer, and L. Hernandez, "0.04-mm2 103-dB-A Dynamic Range Second-Order VCO-Based Audio \$\Sigma\Delta\$ ADC in 0.13- μ m CMOS," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 6, pp. 1731–1742, Jun. 2018.

- [8] M. Amin and B. Leung, "Design Techniques for Linearity in Time-Based ΣΔ Analog-To-Digital Converter," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 63, no. 5, pp. 433–437, 2016.

<sup>\*\*\*</sup> Pseudo-Differential Result not conducive to Single-Ended sensor readout by a narrower bandwidth and second order noise shaping. [8] uses non-linear feedback to compensate for the CCRO nonlinearity, but suffers from high power consumption and area.