# Bitslicing Arithmetic/Boolean Masking Conversions for Fun and Profit

with Application to Lattice-Based KEMs

Olivier Bronchain and Gaëtan Cassiers

Crypto Group, ICTEAM Institute, UCLouvain, Louvain-la-Neuve, Belgium. {olivier.bronchain,gaetan.cassiers}@uclouvain.be

**Abstract.** The performance of higher-order masked implementations of lattice-based based key encapsulation mechanisms (KEM) is currently limited by the costly conversions between arithmetic and Boolean masking. While bitslicing has been shown to strongly speed up masked implementations of symmetric primitives, its use in arithmetic-to-Boolean and Boolean-to-arithmetic masking conversion gadgets has never been thoroughly investigated. In this paper, we first show that bitslicing can indeed accelerate existing conversion gadgets. We then optimize these gadgets, exploiting the degrees of freedom offered by bitsliced implementations. As a result, we introduce new arbitrary-order Boolean masked addition, arithmetic-to-Boolean and Boolean-to-arithmetic masking conversion gadgets, each in two variants: modulo  $2^k$  and modulo p (for any integers k and p). Practically, our new gadgets achieve a speedup of up to 25x over the state of the art. Turning to the KEM application, we develop the first open-source embedded (Cortex-M4) implementations of Kyber768 and Saber masked at arbitrary order. The implementations based on the new bitsliced gadgets achieve a speedup of 1.8x for Kyber and 3x for Saber, compared to the implementation based on state-of-the-art gadgets. The bottleneck of the bitslice implementations is the masked Keccak-f[1600] permutation.

Keywords: Masking · Lattice-based KEM · Kyber · Saber · Bitslice · PINI

### 1 Introduction

Quantum attacks against traditional asymmetric cryptography schemes (based on RSA, discrete logarithm or elliptic curves) have been a growing concern. This led to the introduction of post-quantum (PQ) schemes for signatures and key encapsulation mechanisms (KEM), many of which are based on lattices. Their implementation raises new challenges, in particular for embedded systems that require protection against side-channel attacks (SCA) such as power or electro-magnetic analysis [KJJ99, QS01]. Such attacks are particularly powerful against many state-of-the-art PQ KEMs due to their usage of the Fujisaki-Okamoto (FO) transform [FO99]: an adversary can carefully forge ciphertexts to trigger the re-encryption of a single bit whose value depends on a secret (sub-)key. The leakage from this re-encryption depends only on this single secret bit, which is thus easily recovered and from which information on the secret key can be retrieved [RRCB20, UXT+22]. Strong protection against side-channel attacks is therefore a must for lattice-based cryptography in embedded systems deployed on-the-field [ABH+22].

The most studied countermeasure against SCA is masking, whose core idea is to randomize the intermediate computations while maintaining their correctness [CJRR99, ISW03]. When using arithmetic masking, each intermediate variable x of the original computation is replaced by a sharing  $(x_0, \ldots, x_{d-1})$  such that  $x = x_0 + \cdots + x_{d-1} \mod p$

Licensed under Creative Commons License CC-BY 4.0.

Received: 2022-04-15 Accepted: 2022-06-15 Published: 2022-08-31

for some integer p, where the addition degenerates to the Boolean XOR in the particular case p=2, which is therefore named Boolean masking. Masked implementations are usually analyzed in the t-probing model [ISW03], which formalizes the notion of t-order security by requiring all tuples of t intermediate values in the computation to be independent of any secret value. However, security in the t-probing model is not composable: the sequential use of two t-probing secure gadgets (gadgets are algorithms computing on masked values) is not necessarily probing secure [CPRR13]. To circumvent the t-probing security analysis of a full masked cryptographic algorithm (which is impractical), composable security properties have been introduced, such as (strong-)non-interference (NI/SNI) [BBD+16], or probe-isolating non-interference (PINI) [CS20]. These properties are stronger than probing security and gadgets that satisfy them can be securely composed.

The protection of masking does not come for free and sometimes leads to orders of magnitudes larger costs than non-masked implementation [BGR $^+$ 21]. A key question in the design of masked implementation is therefore the minimization of computational cost, which is particularly critical when considering embedded software PQ KEMs implementations. Indeed, unprotected implementations of PQ KEMs are already computationally expensive [KRSS], and on top of this a high masking order is needed, due to the low intrinsic noise level on commercial micro-controllers [BS20, BS21]. Masking overheads (in randomness usage and runtime) generally grow quadratically with the number of shares, except for masked linear operations modulo p, which incur only linear computational overhead (and no randomness usage).

Lattice-based KEMs use many arithmetic operations in the field of integers modulo p (e.g.,  $p=3329,\ 2^{10}$  or  $2^{13}$ ). These operations are often linear with respect to the secret values [ABD+19, BBMD+19], which leads to a very efficient implementation when using arithmetic masking modulo p [RRVV15, OSPG18]. These KEMs also use symmetric cryptography primitives to generate pseudo-randomness, which are often best implemented using Boolean masking since they contain many bit-level operations [BDPA13, GR16, BDM+20]. As a result, conversions between arithmetic and Boolean masking are key components of masked implementations of lattice-based KEMs.

These conversions are a bottleneck of the current state-of-the-art implementations [BGR<sup>+</sup>21, FBR<sup>+</sup>22] and they are an active field of research. Arbitrary-order arithmeticto-Boolean masking conversions (A2B) were first introduced in [CGV14] for fields of characteristic two and a masking order equal to half of the number of shares. In a series of works [CGTV15, BBE+18, SPOG19], the construction was generalized to arbitrary p and optimal masking order (d-1), along with optimizations to reach  $\mathcal{O}(d^2 \log(\log p))$  CPU instructions. Alternative table-based constructions have also been introduced, achieving similar properties [CGMZ21a]. Boolean-to-arithmetic conversion (B2A) has also been studied thoroughly. The original arbitrary-order B2A [CGV14] is based on A2B and benefited from its improvements, as well as being proven secure at optimal security order in [BBE<sup>+</sup>18]. Recently, efficient B2A algorithms for conversion of a single bit have been introduced [SPOG19, CGMZ21a], from which a B2A algorithm for an arbitrary number of bits can be derived. Finally, the *compression* modulo p is an operation which consists in a linear scaling then a rounding, and is commonly found in Lattice-based KEMs. Its masking can be performed thanks to A2B conversions and has been recently optimized in  $[BPO^{+}20, BDH^{+}21, CGMZ21b]$ .

In parallel over the last years, the *bitslicing* technique has brought significant speed improvements to software implementations of symmetric cryptography, be it masked [GR16, BDM<sup>+</sup>20] or not [Bih97, AP21]. In short, bitslicing leverages the intrinsic parallelism of bitwise operations within processors. E.g., a processor that manipulates 32-bit integers can perform 32 bitwise operations with a single instruction. Therefore, bitslicing only applies to algorithms whose operations are bitwise, such as [GLSV14], but sometimes an algorithm can be re-written to use bit-level operations (while preserving efficiency) [BMP13]. In

particular, Boolean masking is very well suited to bitslicing since most Boolean masking gadgets only use bit-level operations, whereas arithmetic masking gadgets use additions and multiplications (whose equivalent bitwise circuits are large) and therefore do not benefit from bitslicing. To the best of our knowledge, despite many works on A2B and B2A, no efficient bitslice implementation of such conversion algorithm has ever been introduced.

**Contributions** We introduce the usage of bitslicing for the masked implementation of lattice-based cryptography, and for this purpose, we design new masked gadgets for all masking orders. Our new gadgets are A2B and B2A conversions. Additionally, we also design a new addition gadget for Boolean masking which is used in the conversion gadgets. These gadgets come in two variants: one for arithmetic modulo any integer p, and one for the particular case of arithmetic modulo  $2^k$ , which is more efficient. All our gadgets are PINI, and are therefore easily composed.

As a testbed for our new gadgets, we develop arbitrary-order masked Kyber and Saber implementations on the Cortex-M4 platform. First, for each of them, we build a non-bitsliced masked implementation (hereafter named respectively K1 and S1) based on state-of-the-art components: the gadgets of Coron et al. [CGMZ21a], some gadgets from [SPOG19] and some (non-masked) functions from the NIST PQ benchmarking project (PQM4) [KRSS]. To the best of our knowledge, implementations K1 and S1 are the first open-source <sup>1</sup> embedded masked at arbitrary order Kyber and Saber software implementations. Next, we build new bitslice implementations (named K2 and S2) that use our new gadgets and satisfy the PINI secure composition strategy. Implementation K2 achieves a speedup of up to 1.84x over K1, and up to 8.7x over the best reported performance in the state-of-the-art on an embedded platform [BGR<sup>+</sup>21]. Similarly, S2 achieves a speedup of 3x over S1. In both K2 and S2, the execution time is dominated by hashing respectively by 50% for Kyber and 72% for Saber. Eventually, we also propose implementations K3 and S3 which include assembly implementation of masked Boolean gates to avoid lower-order leakages due to transitions.<sup>2</sup>

**Related work** We note that the noise sampling proposed in [SPOG19, BDK<sup>+</sup>21] leverages bitslicing in order to perform the CBD with Boolean masking, but the conversion to arithmetic masking is not bitsliced. Moreover, [DHP<sup>+</sup>22] mentions a bitsliced implementation of the A2B conversion of [CGV14] but does not optimize the algorithm.<sup>3</sup>

**Organization** In Section 2, we introduce some preliminaries on masking and describe the state-of-the-art gadgets for Boolean masked addition, A2B masking conversion, as well as B2A. Next, we present our new gadgets and prove that they are PINI in Section 3, before comparing their performance to the state-of-the-art in Section 4. We then perform leakage assessment of the proposed gadgets in Section 5. Finally, we describe our Kyber768 and Saber implementations and measure their performance in Section 6.

# 2 Background

In this Section, we first introduce our notations and the masking schemes we use, then we describe state-of-the-art gadgets that operate on masked values to perform simple operations, namely addition and conversion between masking schemes.

$<sup>^1{</sup>m The~implementations~K1/S1~are~available~at~https://github.com/uclcrypto/pqm4_masked/files/8048895/implems.zip.}$

The implementations K2/K3/S2/S3 are available at https://github.com/uclcrypto/pqm4\_masked.

$<sup>^3</sup>$ Another recent work [DBV22] (which appeared online after the original submission of this paper to TCHES) implements with bitslicing the B2A algorithm of [CGV14].

**Notations** We denote by  $[\![x,y]\!]$  the set  $[\![x,y]\!] \cap \mathbb{N}$  and by  $[\![x,y]\!]$  the set  $[\![x,y]\!] \cap \mathbb{N}$ . For non-negative integers x and y,  $x \oplus y$  is the (unsigned) integer whose binary representation is the bitwise XOR of the binary representations of x and y.

### 2.1 Masking and elementary gadgets

In this paper, we consider two masking schemes: arithmetic and Boolean masking. A secret variable  $x \in [0, p]$  for some integer p is represented by the d-shares arithmetic sharing

$$\boldsymbol{x}^{A_p} = \left(\boldsymbol{x}_i^{A_p}\right)_{i=0,\dots,d-1} \in \llbracket 0,p \rrbracket^d \text{ such that } \boldsymbol{x} = \boldsymbol{x}_0^{A_p} + \boldsymbol{x}_1^{A_p} + \dots + \boldsymbol{x}_{d-1}^{A_p} \mod p.$$

In order to achieve d-1-order security for x, any set of d-1 shares must be uniformly distributed. Similarly, the k-bit Boolean sharing of a secret  $x \in [0, 2^k]$  is

$$\boldsymbol{x}^{B,k} = \left(\boldsymbol{x}_i^{B,k}\right)_{i=0,\dots,d-1} \in \left[\!\left[0,2^k\right]\!\right]^d \text{ such that } x = \boldsymbol{x}_0^{B,k} \oplus \boldsymbol{x}_1^{B,k} \oplus \dots \oplus \boldsymbol{x}_{d-1}^{B,k}.$$

Computation on sharings is performed by algorithms named gadgets. The inputs and outputs of a d-share gadget are d-shares sharings, which allows such gadgets to be composed: the composition of multiple gadgets (which must all have the same number of shares) results in a composite gadget. The input sharings of the composing gadgets (named hereafter sub-gadgets) may be the input sharing of the composite gadget, or an output sharing of another sub-gadget.

For both arithmetic and Boolean masking, the operations that are linear with respect to the sharing operation are implemented by simple gadgets: the operation can be applied share-wise, hence the computational cost is  $\mathcal{O}(d)$ . In particular, for arithmetic (respectively Boolean) masking, one such operation is the addition modulo p (resp. bitwise XOR) of two shared variables. We denote these algorithms as  $+^{\mathtt{A}}$  (resp.  $\oplus^{\mathtt{B}}$ ).

The ISW multiplication gadget [ISW03], which we denote SecAnd allows computing bitwise AND of Boolean-shared values at a randomness and computational cost  $\mathcal{O}\left(d^2\right)$ . This gadget may also be used to compute the product modulo p of two arithmetically shared secrets.

A last commonly used gadget is the refresh gadget, which implements the identity function, but re-randomizes the sharing. This gadget is sometimes used to ensure the security of a computation that composes multiple simpler gadgets.

### 2.2 Composable probing security

In this paper, we target (d-1)-probing security for our d-shares implementations. That is, the statistical distribution of any d-1 intermediate values (named probes) in our computation should be independent of any secret. We build our masked gadgets by composing multiple smaller gadgets. However, probing security is not composable [CPRR13]: composing (d-1)-probing secure gadgets is not enough to ensure (d-1)-probing security.

As a result, we consider stronger security definitions that are composable. These definitions rely on the notion of simulatability.

**Definition 1** (Simulatability [BBP<sup>+</sup>16]). A set of t probes in a masked gadget G can be simulated with a subset I of the input shares of G if there exists a randomized algorithm S (named the simulator) such that for any value taken by the input shares of G, the joint distribution of the probes is equal to the distribution of the output of S when the values of the shares in I are given to it as inputs.

The two following composable security definitions were introduced in [BBD<sup>+</sup>16].

**Definition 2** (t-NI). A gadget is t-Non-Interfering (t-NI) if every set of t probes can be simulated by using at most t shares of each input sharing.

**Definition 3** (t-SNI). A gadget with one output sharing is t-Strong-Non-Interfering (t-SNI) if every set of  $t_1$  probes on the internal values and  $t_2$  probes on the output shares, with  $t_1 + t_2 \le t$ , can be simulated by using at most  $t_1$  shares of each input sharing.

The  $+^{\mathbb{A}}$  and  $\oplus^{\mathbb{B}}$  gadgets are (d-1)-NI while the ISW multiplication is (d-1)-SNI. Furthermore, the refresh gadget obtained by setting one input sharing of the ISW multiplication to  $(1,0,\ldots,0)$  is also SNI, and this set of gadgets enables to securely mask any computation [BBD<sup>+</sup>16].

Composition based on the NI and SNI definitions requires the usage of refresh gadgets, which may significantly increase the computational and randomness cost. More recently, Cassiers and Standaert [CS20] introduced a new definition that allows to remove those refresh gadgets.

**Definition 4** (t-PINI). A gadget is t-Probe-Isolating-Non-Interfering (t-PINI) if, for every set P of  $t_1$  probes on the internal values and set  $A \subset [0, d[$  with  $t_1 + |A| \le t$ , there exists a set  $B \subset [0, d[$  with  $|B| \le t_1$  such that the probes in P and the output shares whose index (i.e., the position of the share in the sharing) belongs to A can be simulated by using the input shares whose share index belongs to  $A \cup B$ .

Following [CGZ20], we say in the following that a gadget with d shares is PINI if it is (d-1)-PINI, since this implies that it is t-PINI for any t. The  $+^{A}$  and  $\oplus^{B}$  are share-isolating: all the computation on the input and output shares with a given share index is isolated from computations for any other share index. All share-isolating gadgets are PINI [CS20], but the ISW multiplication is not PINI. There however exists a PINI SecAnd gadget [CS20, Algorithm 2] with a cost similar to the ISW multiplication: same amount of randomness and roughly double the number of arithmetic operations. Finally, PINI gadgets are trivially composable: the composition of t-PINI gadgets is t-PINI [CS20], which enables composition without the use of refresh gadgets.

#### 2.3 Modular addition in Boolean masking

We first consider the addition modulo  $2^k$  of two k-bit Boolean shared operands, and denote this gadget as SecAdd. It can be implemented by taking the Boolean circuit of a k-bit binary adder, rewriting it to only use AND and XOR gates, and finally implementing this circuit with 1-bit SecAnd and  $\oplus^B$  gadgets. The 1-bit inputs of this circuit are obtained by selecting single bit sharings in the k-bit input sharings. Using a chain of full-adders, this technique yields a complexity of  $\mathcal{O}(kd^2)$  operations (each on single-bit words).

This technique has been refined in [CGTV15] by using the Kogge-Stone (KS) adder for the 2-shares case. This circuit allows to perform some Boolean operations in parallel, that is, with multiple-bit SecAnd and  $\oplus^{B}$  gadgets. This gives a complexity of  $\mathcal{O}\left(\log(k)d^{2}\right)$  operations (on up-to k-bit words). Barthe et al. then generalized the gadget to arbitrary masking order and, by inserting refresh gadgets, proved it (d-1)-NI (Algorithm 9 of [BBE+18]).

Next, we consider the SecAddModp gadget which performs the addition modulo p. The construction of Algorithm 2 (from [BBE+18]) is based on the SecAdd gadget. Namely, it first computes the sum s of the inputs x and y on k+1 (to avoid overflow and thus modulo  $2^k$  reduction), then adds  $2^k-p$  to obtain s'. The most significant bit of s' indicates whether  $x+y\geq p$ . Based on this bit, either s or s' is selected as the output, using a MUX implemented with SecAnd and  $\oplus^{\rm B}$  gadgets. Finally, the most significant bit is dropped to get the result on k bits. The complexity is still  $\mathcal{O}\left(\log(k)d^2\right)$  operations on up-to k-bit words.

# $\overline{\mathbf{Algorithm}}$ 1 BitCopyMask $_k^d$ (share-isolating)

Input: Boolean sharing  $\boldsymbol{x}^{B,1}$  and integer  $p < 2^k$ . Output: Boolean sharing  $\boldsymbol{y}^{B,k}$ .

```

1: for i = 0, ..., k-1 do

2: if \lfloor (p \mod 2^i)/2^i \rfloor = 1 then

3: y^{B,k}[i] \leftarrow x^{B,1}

4: else

5: y^{B,k}[i] \leftarrow (0,...,0)

```

# **Algorithm 2** SecAddModp $_k^d$ from [BBE+18] (NI)

**Input:** Boolean sharings  $\boldsymbol{x}^{B,k}$  and  $\boldsymbol{y}^{B,k}$ , integer p such that  $p < 2^k$  and  $x, y \in [0, p[$ . **Output:** Boolean sharing  $\boldsymbol{z}^{B,k}$  such that  $z = x + y \mod p$ .

```

1: \boldsymbol{p}^{B,k+1} \leftarrow (2^k - p, 0, \dots, 0)

2: \boldsymbol{s}^{B,k+1} \leftarrow \operatorname{SecAdd}_{k+1}^d (\boldsymbol{x}^{B,k}, \boldsymbol{y}^{B,k}) \rightarrow Algorithm 9 of [BBE+18].

3: \boldsymbol{s'}^{B,k+1} \leftarrow \operatorname{SecAdd}_{k+1}^d (\boldsymbol{s}^{B,k+1}, \boldsymbol{p}^{B,k+1})

4: \boldsymbol{b}^{B,1} \leftarrow \boldsymbol{s'}^{B,k+1}[k]

5: \boldsymbol{c}^{B,1} \leftarrow \operatorname{RefreshSNI}_1^d (\boldsymbol{b}^{B,1})

6: \boldsymbol{c'}^{B,1} \leftarrow \operatorname{RefreshSNI}_1^d (\boldsymbol{b}^{B,1})

7: \boldsymbol{c}^{B,k} \leftarrow \operatorname{BitCopyMask}_k^d (\boldsymbol{c}^{B,1}, 2^k - 1) \rightarrow Copy input sharing where bitmask (2^k - 1) is set.

8: \boldsymbol{c'}^{B,k} \leftarrow \operatorname{BitCopyMask}_k^d (\boldsymbol{s'}^{B,1}, 2^k - 1)

9: \boldsymbol{z}^{B,k} \leftarrow \operatorname{SecAnd}_k^d (\boldsymbol{s}^{B,k+1}[[0,k[],\boldsymbol{c}^{B,k}) \oplus^{\mathsf{B}} \operatorname{SecAnd}_k^d (\boldsymbol{s'}^{B,k+1}[[0,k[],\boldsymbol{c'}^{B,1})) \rightarrow MUX

```

### 2.4 Arithmetic-to-Boolean masking conversion

Coron et al. [CGV14] introduced a simple way to convert from arithmetic to Boolean masking (SecA2BModp). This technique first masks each arithmetic share into a d-shares Boolean sharing and then computes the addition modulo p of these Boolean shared values. This removes the arithmetic masking, its result is therefore a Boolean masking of the original value.

This can be optimized by remarking that the addition of d' arithmetic shares can be securely masked using d'-shares Boolean masking instead of d. Therefore, the optimized technique (Algorithm 3 from [SPOG19]) proceeds recursively: it splits the arithmetic sharing into two groups of d/2 arithmetic shares, converts each group separately into a d/2-shares Boolean sharing, re-masks each Boolean sharing to d shares, computes their sum. This algorithm has a complexity of  $\mathcal{O}\left(\log(k)d^2\right)$  on up-to k-bit words. As an alternative, a table-based SecA2BModp implementation with the same complexity was recently introduced in [CGMZ21a].

### **Algorithm 3** SecA2BModp $_{k}^{d}$ from [SPOG19] (SNI)

**Input:** d shares arithmetic sharing  $\mathbf{x}^{A_p}$ , integer p such that  $p < 2^k$  and  $x \in [0, p[$ . **Output:** d shares Boolean sharing  $\mathbf{z}^{B,k}$  such that z = x.

```

1: if d=1 then

2: \boldsymbol{z}^{B,k} \leftarrow \boldsymbol{x}^{A_p}

3: else

4: \boldsymbol{y}^{B,k} \leftarrow \operatorname{SecA2BModp}_k^{\lfloor d/2 \rfloor} \left( \boldsymbol{x}_{\llbracket 0, \lfloor d/2 \rfloor, d \rrbracket}^{A_k} \right)

5: \boldsymbol{y'}^{B,k} \leftarrow \operatorname{SecA2BModp}_k^{d-\lfloor d/2 \rfloor} \left( \boldsymbol{x}_{\llbracket \lfloor d/2 \rfloor, d \rrbracket}^{A_k} \right)

6: \boldsymbol{y}^{B,k} \leftarrow \operatorname{RefreshSNI}_k^d \left( \left( \boldsymbol{y}_0^{B,k}, \boldsymbol{y}_1^{B,k}, \dots, \boldsymbol{y}_{\lfloor d/2 \rfloor-1}^{B,k}, 0, \dots, 0 \right) \right) \triangleright \operatorname{Expand} \operatorname{to} d \operatorname{shares}.

7: \boldsymbol{y'}^{B,k} \leftarrow \operatorname{RefreshSNI}_k^d \left( \left( 0, \dots, 0, \boldsymbol{y}_{\lfloor d/2 \rfloor}^{B,k}, \dots, \boldsymbol{y}_{d-1}^{B,k} \right) \right) \triangleright \operatorname{Expand} \operatorname{to} d \operatorname{shares}.

8: \boldsymbol{z}^{B,k} \leftarrow \operatorname{SecAddModp}_k^d \left( \boldsymbol{y}^{B,k}, \boldsymbol{y'}^{B,k} \right)

```

### 2.5 Boolean-to-arithmetic masking conversion

Similarly to arithmetic-to-Boolean conversions, there are multiple efficient techniques for Boolean-to-arithmetic conversion. First, one may generate d-1 random arithmetic shares, generate a d-share Boolean masking of the opposite of their sum (using SecA2BModp), add this to the input sharing (with SecAddModp), and finally unmask (that is, XOR the shares together) the result to get the last arithmetic share. This idea, originally introduced in [CGTV15], has been adapted to the modulo p setting in [BBE+18] (see Algorithm 4). This gadget is (d-1)-SNI.<sup>4</sup>

Second, Schneider et al. [SPOG19] introduced a conversion based on the observation that if  $x,y \in [0,1]$ ,  $x \oplus y = x + y - 2xy$ . The gist of the conversion algorithm is to start from a 1-bit Boolean sharing  $\boldsymbol{x}^{B,1}$ , then arithmetically mask each share, and finally use the previous equation to compute the XOR of these arithmetic sharings. This single-bit conversion algorithm may then be applied to each of a multi-bit input, and the results can be recombined sharewise (with sums and multiplications by 2). Thanks to various optimizations of the algorithm [SPOG19], the complexity of this technique is  $\mathcal{O}\left(kd^2\right)$  operations on k-bit words.

$<sup>^4</sup>$ The proof that SecB2AModp is SNI is not given explicitly, in [BBE<sup>+</sup>18], but it can be deduced from the proof of Lemma 5, if SecA2BModp is SNI.

### **Algorithm 4** SecB2AModp $_k^d$ from [BBE+18] (SNI)

**Input:** d shares Boolean sharing  $\mathbf{x}^{B,k}$ , integer p such that  $p < 2^k$  and  $x \in [0, p[$ . **Output:** d shares arithmetic sharing  $\mathbf{z}^{A_p}$  such that z = x.

```

1: \mathbf{for}\ i = 0 \text{ to } d - 2 \text{ do}

2: \mathbf{z}_i^{A_k} \overset{\$}{\leftarrow} \mathbb{Z}_p

3: \mathbf{z'}_i^{A_k} \leftarrow p - \mathbf{z}_i^{A_k}

4: \mathbf{z'}_{d-1}^{A_k} \leftarrow 0

5: \mathbf{a}^{B,k} \leftarrow \text{SecA2BModp}_k^d \left( \mathbf{z'}^{A_p} \right)

6: \mathbf{b}^{B,k} \leftarrow \text{SecAddModp}_k^d \left( \mathbf{a}^{B,k}, \mathbf{x}^{B,k} \right)

7: \mathbf{z}_{d-1}^{A_k} \leftarrow \text{UnMask}_k^{d-1} \left( \text{FullRefresh}_k^{d-1} \left( \mathbf{b}^{B,k} \right) \right)

```

Finally, Coron et al. [CGMZ21a] introduced recently another conversion algorithm. This algorithm also performs k single-bit conversions, but the single-bit conversion is a table-based gadget.

## 2.6 Bitslicing

When an algorithm computes a Boolean circuit (i.e., it operates on single-bit variables), it can be bitsliced. That is, it can be implemented to perform w evaluations parallel on a processor with w-bit words (e.g., w=32) by using bitwise operations. While the bitslicing technique can bring a large performance increase, it has some drawbacks. Since it does work only on Boolean circuits, bitslicing a computation requires writing it as a Boolean circuit. Moreover, it requires the availability of a significant amount of parallelism in the operations to perform, otherwise it loses it performance benefits. Finally, bitslicing requires representation changes: the data processed is often used in a canonical form in which all the bits for one circuit evaluations are stored contiguously in memory words (we model the memory as a sequence of w-bit words). However, bitslicing works with a bitslice representation: each parallel evaluation contributes a single-bit to each word.

Let us take the example of computations on a k-bit variable  $a_i$ : the Boolean circuit takes k input bits (the bits of  $a_i$ ), and outputs the k bits of  $b_i = f(a_i)$ . Moreover, let us assume that there are N computations to perform: i = 0, ..., N-1 (and, for simplicity, we assume that N is a multiple of w). Let  $a_i[k-1]\cdots a_i[0]$  be the bit representation of  $a_i$ , the canonical<sup>5</sup> representation would be (assuming that  $w \ge k$ )

$$\begin{pmatrix} a_0[0] & \cdots & a_0[k-1] & 0 & \cdots & 0 \\ \vdots & & \vdots & \vdots & & \vdots \\ a_{N-1}[0] & \cdots & a_{N-1}[k-1] & 0 & \cdots & 0 \end{pmatrix}$$

where each row contains w bits and represents a word of the memory. In the same case, and using the same notation, a bitslice representation would be

$$\begin{pmatrix} a_0[0] & \cdots & a_{w-1}[0] \\ \vdots & & \vdots \\ a_{N/w-k}[0] & \cdots & a_{N/w-1}[0] \\ a_0[1] & \cdots & a_{w-1}[1] \\ \vdots & & \vdots \\ a_{N/w-k}[k-1] & \cdots & a_{N/w-1}[k-1]) \end{pmatrix}.$$

$<sup>^{5}</sup>$ The order of the words in memory usually does not matter much, compared to the way the bits are grouped into words.

Therefore, the inputs bits have to be mapped from canonical to bitslice with CToBs before the bitslice computation, and the result bits have to be mapped again to canonical with BsToC after it. Since the changes of representation can be expensive it is important to implement these efficiently (and to minimize their number, by avoiding unnecessary CToBs / BsToC ). A naive implementation of representation changes requires a number of CPU instructions proportional to the number of bits manipulated.

However, in some cases, this can be made more efficiently, such as when k=w. Then, the change of representation can be grouped in N/w parts, each handling the words  $a_{wj},\ldots,a_{w(j+1)-1}$  for  $0\leq j< N/w$ , and both CToBs and BsToC can be represented as the transposition of the following square matrix

$$\begin{pmatrix} a_{wj}[0] & \cdots & a_{wj}[w-1] \\ \vdots & & \vdots \\ a_{w(j+1)-1}[0] & \cdots & a_{w(j+1)-1}[w-1] \end{pmatrix}$$

where each row represents a memory word. This transposition can be computed more efficiently than the naive algorithm:  $\mathcal{O}(w \log w)$  instead of  $\mathcal{O}(w^2)$  [Jr.13].<sup>6</sup>

Furthermore, the technique can be adapted to k < w. For example, let us assume that  $w/4 < k \le w/2$  (this matches our implementation for Kyber768: k = 12 and we work on a w = 32-bit processor). In that case,  $a_{2i}$  and  $a_{2i+1}$  are typically stored in a single processor word (to save memory), hence the canonical form can be represented as

$$\begin{pmatrix} a_{2wj}[0] & \cdots & a_{2wj}[k-1] & 0 \cdots 0 & a_{2wj+1}[0] & \cdots & a_{2wj+1}[k-1] & 0 \cdots 0 \\ a_{2wj+2}[0] & \cdots & a_{2wj+2}[k-1] & 0 \cdots 0 & a_{2wj+3}[0] & \cdots & a_{2wj+3}[k-1] & 0 \cdots 0 \\ \vdots & & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ a_{2wj+2(w-1)}[0] & \cdots & a_{2wj+2(w-1)}[k-1] & 0 \cdots 0 & a_{2wj+2(w-1)+1}[0] & \cdots & a_{2wj+2(w-1)+1}[k-1] & 0 \cdots 0 \end{pmatrix}$$

where both chunks of "0" columns are equally large. This matrix can then be transposed, and the resulting "0" lines can be removed (by copying only the useful rows), giving the bitslice representation:

$$\begin{pmatrix} a_{2wj}[0] & a_{2wj+2}[0] & \cdots & a_{2wj+2(w-1)}[0] \\ \vdots & \vdots & \vdots & \vdots \\ a_{2wj}[k-1] & a_{2wj+2}[k-1] & \cdots & a_{2wj+2(w-1)}[k-1] \\ a_{2wj+1}[0] & a_{2wj+3}[0] & \cdots & a_{2wj+2(w-1)+1}[0] \\ \vdots & \vdots & \vdots \\ a_{2wj+1}[k-1] & a_{2wj+3}[k-1] & \cdots & a_{2wj+2(w-1)+1}[k-1] \end{pmatrix}$$

Regarding security, the use of the CToBs and BsToC algorithms has no impact on the t-probing security since they only copy bits and therefore to not give new choices of probes to the adversary. Practically for masking, the changes of representation can be implemented as a masked CToBs or BsToC share-isolating gadget.

We next introduce our new gadgets, which are all (except SecB2AModp) Boolean circuits, hence are trivially implemented using the bitslice technique (fully working in bitslice representation, with no CToBs or BsToC needed). We describe them as Boolean circuits and give their complexity in Boolean operations. This complexity should be divided by w to obtain the complexity in CPU instructions for bitslice implementations.

# 3 New gadgets

As we already mentioned in the introduction, our starting point is the observation that high-level cryptographic algorithms such as Kyber have large data parallelism, hence

<sup>&</sup>lt;sup>6</sup>While this algorithm is well-known, and used in at least one bitsliced cryptographic implementation (https://github.com/Ko-/aes-armcortexm/blob/public/aes128ctrbs/aes\_128\_ctr\_bs.s, from [SS16]), we have not found any discussion of its use in the bitslicing literature.

they may benefit from bitsliced implementations for the Boolean sharings (while staying non-bitsliced for the arithmetic sharings). We therefore introduce algorithms that represent Boolean circuits, and which are therefore well-suited to bitslicing. As main elementary gadgets, we use  $\oplus^B$  and PINI SecAnd from [CS20], where the SecAnd is more expensive than  $\oplus^B$  ( $\mathcal{O}(d^2)$  vs.  $\mathcal{O}(d)$ ).

# 3.1 SecAdd: Bitslice Boolean masked addition modulo $2^k$

Our first algorithm is a new SecAdd implementation (Algorithm 6). Thanks to bitslicing, we do not have any structure constraint and simply aim to minimize the number of SecAnd. Therefore, we use a simple chain of full-adders, where the addition of x, y and z computes  $a:=x\oplus y$ , then outputs  $(a\oplus z,x\oplus a\cdot (x\oplus z))$ . This requires only one SecAnd per full-adder, hence k-1 in total (since the carry-out does not have to be computed for the addition of the most significant bits), which is the minimum achievable (we prove this in Appendix A). The total complexity of Algorithm 6 is  $\mathcal{O}\left(kd^2\right)$  bit operations. We finally prove the security of this gadget.

**Proposition 1.** Algorithm 6 and Algorithm 5 are PINI.

*Proof.* These two gadgets are the composition of PINI gadgets, therefore they are PINI.  $\Box$

### Algorithm 5 SecFullAdder<sup>d</sup> New (PINI)

```

Input: Boolean sharings x^{B,1}, y^{B,1} and z^{B,1}.

```

**Output:** Boolean sharing  $w^{B,2}$  such that w = x + y + z.

```

1: \boldsymbol{a}^{B,1} \leftarrow \boldsymbol{x}^{B,1} \oplus^{\mathtt{B}} \boldsymbol{y}^{B,1}

2: \boldsymbol{w}^{B,2}[0] \leftarrow \boldsymbol{z}^{B,1} \oplus^{\mathtt{B}} \boldsymbol{a}^{B,1}

3: \boldsymbol{w}^{B,2}[1] \leftarrow \boldsymbol{x}^{B,1} \oplus^{\mathtt{B}} \operatorname{SecAnd}_{1}^{d} \left(\boldsymbol{a}^{B,1}, \boldsymbol{x}^{B,1} \oplus^{\mathtt{B}} \boldsymbol{z}^{B,1}\right) \triangleright PINI SecAnd

```

# **Algorithm 6** SecAdd $_k^d$ New (PINI)

**Input:** Boolean sharings  $\boldsymbol{x}^{B,k}$  and  $\boldsymbol{y}^{B,k}$ , such that  $x,y \in [0,2^k]$ . **Output:** Boolean sharing  $\boldsymbol{z}^{B,k}$  such that  $z=x+y \mod 2^k$ .

```

1: c^{B,1} \leftarrow (0,0,\ldots,0)

2: for i=0 to k-2 do

3: c^{B,2} \leftarrow \texttt{SecFullAdder}^d \left( c^{B,k}[i], c^{B,k}[i], c^{B,1} \right)

4: c^{B,k}[i], c^{B,1} \leftarrow (c^{B,2}[0], c^{B,2}[1])

5: c^{B,k}[k-1] \leftarrow c^{B,k}[k-1] \oplus^{\mathsf{B}} c^{B,k}[k-1] \oplus^{\mathsf{B}} c^{B,1}

```

### 3.2 SecAddModp: Bitslice Boolean masked addition modulo p

Next, we consider addition modulo p. A simple approach is to adapt Algorithm 2 to use Algorithm 6 as SecAdd. On top of this adaptation, we remark that the MUX in Algorithm 2 costs 2k 1-bit SecAnd gadgets, and that we can replace it with the computation of  $s'+p\cdot b \mod 2^k$ , which costs one SecAdd $_k^d$  (i.e., k-1 single-bit SecAnd). This replacement is correct: if b=0, the result is s', and if b=1 the result is  $s'+p \mod 2^k=s$ . Overall, our new addition modulo p requires two k+1-bit adders and one k-bit adder, totaling to 3k-1 1-bit PINI SecAnd, hence  $\mathcal{O}\left(kd^2\right)$  bit operations and randomness.

Proposition 2. Algorithm 7 is PINI.

*Proof.* All the sub-gadgets are PINI (BitCopyMask only replicates a sharing, hence it is share-isolating, which implies that it is PINI).

### **Algorithm 7** SecAddModp $_k^d$ New (PINI)

**Input:** Boolean sharings  $\boldsymbol{x}^{B,k}$  and  $\boldsymbol{y}^{B,k}$ , integer p such that  $p < 2^k$  and  $x, y \in [0, p[$ . **Output:** Boolean sharing  $\boldsymbol{z}^{B,k}$  such that  $z = x + y \mod p$ .

```

1: \boldsymbol{p}^{B,k+1} \leftarrow (2^{k+1}-p,0,\ldots,0)

2: \boldsymbol{s}^{B,k+1} \leftarrow \operatorname{SecAdd}_{k+1}^d(\boldsymbol{x}^{B,k},\boldsymbol{y}^{B,k}) \triangleright Use Algorithm 6.

3: \boldsymbol{s'}^{B,k+1} \leftarrow \operatorname{SecAdd}_{k+1}^d(\boldsymbol{s}^{B,k+1},\boldsymbol{p}^{B,k+1}) \triangleright Use Algorithm 6.

4: \boldsymbol{b}^{B,1} \leftarrow \boldsymbol{s'}^{B,k+1}[k]

5: \boldsymbol{a}^{B,k} \leftarrow \operatorname{BitCopyMask}_k^d(\boldsymbol{b}^{B,1},p) \triangleright \operatorname{Copy sharing } \boldsymbol{b} where bitmask \boldsymbol{p} is set (computes \boldsymbol{a} = \boldsymbol{p} \cdot \boldsymbol{b}).

6: \boldsymbol{z}^{B,k} \leftarrow \operatorname{SecAdd}_k^d(\boldsymbol{a}^{B,k},\boldsymbol{s'}^{B,k+1}) \triangleright Use Algorithm 6.

```

### 3.3 SecA2B: Bitslice arithmetic-to-Boolean conversion modulo $2^k$

For arithmetic modulo  $2^k$  to Boolean conversion (SecA2B), we take inspiration from the conversion algorithm of [SPOG19] (Algorithm 3). Namely, we also use a recursive structure where two halves of the arithmetic sharing are first converted to Boolean, then the two resulting sharing are added together. We use our new SecAdd (Algorithm 6) for this purpose, which, thanks to PINI composition, allows us to remove the refresh gadget, giving Algorithm 8 whose complexity is  $\mathcal{O}(kd^2)$  random bits and single-bit operations.

#### **Algorithm 8** SecA2B<sub>k</sub> New (PINI)

**Input:** d shares arithmetic sharing  $\mathbf{x}^{A_{2^k}}$ , such that  $x \in [0, 2^k]$ . **Output:** d shares Boolean sharing  $\mathbf{z}^{B,k}$  such that z = x.

```

1: if d=1 then

2: \boldsymbol{z}^{B,k} \leftarrow \boldsymbol{x}^{A_{2^k}}

3: else

4: \boldsymbol{y}^{B,k} \leftarrow \operatorname{SecA2B}_k^{\lfloor d/2 \rfloor} \left( \boldsymbol{x}^{A_{2^k}} [\llbracket 0, \lfloor d/2 \rfloor \rrbracket] \right) \triangleright \lfloor d/2 \rfloor sharing.

5: \boldsymbol{y'}^{B,k} \leftarrow \operatorname{SecA2B}_k^{d-\lfloor d/2 \rfloor} \left( \boldsymbol{x}^{A_{2^k}} [\llbracket \lfloor d/2 \rfloor, d \rrbracket] \right) \triangleright d - \lfloor d/2 \rfloor sharing.

6: \boldsymbol{s}^{B,k} \leftarrow \left( \boldsymbol{y}_0^{B,k}, \boldsymbol{y}_1^{B,k}, \dots, \boldsymbol{y}_{\lfloor d/2 \rfloor-1}^{B,k}, 0, \dots, 0 \right) \triangleright \operatorname{Expand} \operatorname{to} d \operatorname{shares}.

7: \boldsymbol{s'}^{B,k} \leftarrow \left( 0, \dots, 0, \boldsymbol{y'}_{\lfloor d/2 \rfloor}^{B,k}, \dots, \boldsymbol{y'}_{d-1}^{B,k}, \right) \triangleright \operatorname{Expand} \operatorname{to} d \operatorname{shares}.

8: \boldsymbol{z}^{B,k} \leftarrow \operatorname{SecAdd}_k^d \left( \boldsymbol{s}^{B,k}, \boldsymbol{s'}^{B,k} \right) \triangleright \operatorname{Use Algorithm} 6.

```

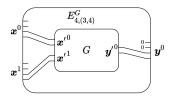

To prove that Algorithm 8 is PINI, we will use the PINI composition theorem from [CS20], and introduce a new technique to deal with the composition of PINI gadget with various numbers of shares. The core idea is to embed gadgets that use a lower number of shares into "virtual gadgets" that use more shares, with a mapping from the share indexes of the embedded gadgets to the indexes of the embedding gadgets. The embedding gadget discards the input shares that are not used, and sets to 0 the output shares that are not generated by the embedded gadgets, as illustrated in Figure 1.

**Definition 5** (Gadget embedding). Let G be a d'-share gadget with n (resp. n') input (resp. output) sharings, and let  $m \in [0, d[^{d'}]]$  (with  $d \geq d'$ ) have unique components

**Figure 1:** Example of 2-share to 4-share gadget embedding.

**Algorithm 9**  $E_{d,m}^G$ : embedding of the d'-shares gadget G to d shares with mapping m with  $d' \leq d$ .

Input: n d-shares input sharings  $x^0, \dots x^{n-1}$ ; Output: n' d-shares output sharings  $y^0, \dots, y^{n'-1}$

```

1: for j=0,\ldots,n-1 do

2: for i=0,\ldots,d'-1 do

3: \mathbf{x'}_i^j \leftarrow \mathbf{x}_{m_i}^j

4: \left(\mathbf{y'}^0,\ldots,\mathbf{y'}^{n'}\right) \leftarrow G\left(\mathbf{x'}^0,\ldots,\mathbf{x'}^n\right)

5: for j=0,\ldots,n'-1 do

6: for i=0,\ldots,d-1 do

7: \mathbf{y}_i^j \leftarrow 0 \triangleright Initialize all shares to 0.

8: for i=0,\ldots,d'-1 do

9: \mathbf{y}_{m_i}^j \leftarrow \mathbf{y'}_i^j \triangleright Override some output shares with outputs of G.

```

$(m_i \neq m_j \text{ for all } i, j)$ . The d-share embedding of G with mapping m is the d-share gadget denoted  $E_{d,m}^G$  described in Algorithm 9.

**Lemma 1** (PINI embedding). If G is a PINI gadget, its embedding  $E_{d,m}^G$  is PINI for any d and m.

*Proof.* We describe the (d-1)-PINI simulator for  $E_{d,m}^G$  that has to simulate a set of internal probes P and the output shares with index in B. First, P can be partitioned in a set  $P_G$  of probes in G and a set  $P_i$  of probes on the input shares. Next, B is partitioned as  $B_0$  (the elements of B that appear in M), and  $B_1$  (the remaining elements).

Let  $B_0' = \{i \in [0, d'[$  s.t.  $m_i \in B_0\}$ , we have  $|B_0'| = |B_0|$ . We use the PINI simulator of G to simulate the probes  $P_G$  and its output shares with index in  $B_0'$  (which are the outputs of  $E_{d,m}^G$  with index in  $B_0$ ). This simulator requires knowledge of its input shares with index in  $A' \cup B'$ , for some  $A_0'$  such that  $|A_0'| \leq |P_G|$ . Let us define  $A_0 = \{m_i \text{ for all } i \in A_0'\}$ , such that knowing the input shares of  $E_{d,m}^G$  with index in  $A_0 \cup B_0$  allows sending the inputs required to the simulator of G, that simulates the probes  $P_G$  and the output shares with index in  $B_0$ .

Finally, the probes in  $P_i$  can be simulated with the input shares with index in  $A_1$ , for some  $A_1$  such that  $|A_1| \leq |P_i|$ , and all the output shares with index in  $B_1$  can be trivially simulated (their value is always 0). As a result, all the required values can be simulated with the input shares of  $E_{d,m}^G$  with index in  $(A_0 \cup A_1) \cup B$ , and  $|A_0 \cup A_1| \leq |P|$ .

# Proposition 3. Algorithm 8 is PINI.

*Proof.* In the case d=1, this is trivial. In the other cases, we decompose the gadget in three parts, which are then embedded: wires carrying the constant "0" value are added such that all sharings have d shares (this has no impact on the security). This gives a decomposition of the gadget into three sub-gadgets:  $E_{d,(0,\dots,\lfloor d/2\rfloor-1)}^{\mathsf{SecA2B}_k^{\lfloor d/2\rfloor}}$  (which computes

$s^{B,k}$  from  $x^{A_{2k}}$ ),  $E^{\mathtt{SecA2B}_k^{d-\lfloor d/2 \rfloor}}_{d,(\lfloor d/2 \rfloor,\dots,d-1)}$  (which computes  $s'^{B,k}$  from  $x^{A_{2k}}$ ) and  $\mathtt{SecAdd}_k^d$  (which computes  $z^{B,k}$  from  $s^{B,k}$  and  $s'^{B,k}$ ). Since  $\mathtt{SecA2B}_k^{\lfloor d/2 \rfloor}$  and  $\mathtt{SecA2B}_k^{d-\lfloor d/2 \rfloor}$  are PINI (by induction on d), their embeddings are PINI (by Lemma 1). Furthermore,  $\mathtt{SecAdd}_k^d$  is PINI (Proposition 1). Therefore, Algorithm 8 is a composition of PINI gadgets.

# 3.4 SecA2BModp: Bitslice arithmetic-to-Boolean conversion modulo p

A simple way to implement arithmetic modulo p to Boolean masking conversion is to adapt Algorithm 8 (SecA2B) to use addition modulo p (SecAddModp, Algorithm 7) instead of addition modulo  $2^k$  (SecAdd, Algorithm 6).<sup>7</sup> On top of this adaptation, we can perform a small optimization inspired by the first-order A2B conversion from [FBR<sup>+</sup>22]: the first operation of our addition modulo p (Algorithm 7) is to subtract p from one of the two operands which can be done before double the number of shares in the A2B algorithm. This has no impact on the final result, but the cost of this subtraction is divided by about 4 (since this operation is in  $\mathcal{O}(kd^2)$ ).

These changes do not impact the asymptotic complexity of the algorithm, which is still  $\mathcal{O}(kd^2)$  random bits and single-bit operations.

# **Algorithm 10** SecA2BModp $_k^d$ New (PINI)

**Input:** d shares arithmetic sharing  $\boldsymbol{x}^{A_p}$ , integer p such that  $p < 2^k$  and  $x \in [0, p[$ . **Output:** d shares Boolean sharing  $\boldsymbol{z}^{B,k}$  such that z = x.

```

1: if d = 1 then

\boldsymbol{z}^{B,k} \leftarrow \boldsymbol{x}^{A_p}

3: else

\begin{aligned} & \boldsymbol{y}^{B,k} \leftarrow \texttt{SecA2BModp}_k^{\lfloor d/2 \rfloor} \left( \boldsymbol{x}^{A_p} [\llbracket 0, \lfloor d/2 \rfloor \rrbracket ] \right) \\ & \boldsymbol{y'}^{B,k} \leftarrow \texttt{SecA2BModp}_k^{d-\lfloor d/2 \rfloor} \left( \boldsymbol{x}^{A_p} [\llbracket \lfloor d/2 \rfloor, d \rrbracket ] \right) \\ & \boldsymbol{p}^{B,k+1} \leftarrow \left( 2^k - p, 0, \dots, 0 \right) \end{aligned}

\triangleright |d/2| sharing.

\triangleright d - |d/2| sharing.

6:

\triangleright \lfloor d/2 \rfloor sharing.

\begin{aligned} & \boldsymbol{p} & \leftarrow (2-p, 0, \dots, 0) \\ & \boldsymbol{s}^{B,k+1} \leftarrow \mathtt{SecAdd}_{k+1}^{\lfloor d/2 \rfloor} \left( \boldsymbol{p}^{B,k+1}, \boldsymbol{y}^{B,k} \right) \\ & \boldsymbol{s}^{B,k+1} \leftarrow \left( \boldsymbol{y}_0^{B,k+1}, \boldsymbol{y}_1^{B,k+1}, \dots, \boldsymbol{y}_{\lfloor d/2 \rfloor-1}^{B,k+1}, 0, \dots, 0 \right) \\ & \boldsymbol{s'}^{B,k} \leftarrow \left( 0, \dots, 0, \boldsymbol{y'}_{\lfloor d/2 \rfloor}^{B,k}, \dots, \boldsymbol{y'}_{d-1}^{B,k}, \right) \end{aligned}

7:

\triangleright Use Algorithm 6.

8:

\triangleright Expand to d shares.

9:

\triangleright Expand to d shares.

oldsymbol{u}^{B,k+1} \leftarrow \mathtt{SecAdd}_{k+1}^d \left( oldsymbol{s}^{B,k+1}, oldsymbol{s'}^{B,k}

ight)

10:

▶ Use Algorithm 6.

\boldsymbol{b}^{B,1} \leftarrow \boldsymbol{u}^{B,k+1}[k]

11:

oldsymbol{a}^{B,k} \leftarrow 	exttt{BitCopyMask}_k^d \left(oldsymbol{b}^{B,1}, p

ight)

12:

\triangleright Copy sharing b where bitmask p is set (a := p \cdot b).

oldsymbol{z}^{B,k} \leftarrow \mathtt{SecAdd}_h^d\left(oldsymbol{a}^{B,k},oldsymbol{u}^{B,k+1}

ight)

13:

▶ Use Algorithm 6.

```

#### Proposition 4. Algorithm 10 is PINI.

*Proof.* The proof is almost identical to the proof of Algorithm 10. The case d=1 is trivial, and in the other cases, we exhibit a decomposition into PINI sub-gadgets. We first consider the d-share embedding of the  $\lfloor d/2 \rfloor$ -share composite gadget whose input is  $\boldsymbol{x}^{A_p}[\llbracket 0, \lfloor d/2 \rfloor \llbracket ]$  and whose output is  $\boldsymbol{s}^{B,k+1}$ . This gadget is the composition of two PINI gadgets (SecA2BModp $_k^{\lfloor d/2 \rfloor}$  and SecAdd $_{k+1}^{\lfloor d/2 \rfloor}$ ), hence it is PINI, and the embedding is PINI. Next, the d-share embedding of SecA2BModp $_k^{d-\lfloor d/2 \rfloor}$  is PINI, as well as the other d-share sub-gadgets (SecAdd, BitCopyMask).

<sup>&</sup>lt;sup>7</sup>Another solution would be to use the compression algorithm (HOCompress) from [CGMZ21b] which it has a worse asymptotic complexity of  $\mathcal{O}\left(kd^2\log(d)\right)$ , but which might be an interesting alternative if we care only about small enough d.

### 3.5 SecB2AModp: Bitslice Boolean-to-arithmetic conversion modulo p

We now adapt in Algorithm 11 the SecB2AModp from [BBE<sup>+</sup>18] (Algorithm 4) to use our new SecA2BModp and SecAddModp algorithms. Furthermore, we replace the refresh gadget to reduce its cost (from  $\mathcal{O}(d^2)$  to  $\mathcal{O}(d\log d)$ ). The new refresh gadget is the input-output separative (IOS) refresh gadget from [GPRV21]. We generalize this gadget to any value of d in Algorithm 18 (Appendix B), since only the power of 2 cases were handled in [GPRV21].

Algorithm 11 combines arithmetic operations (lines 1 to 4) which are best implemented using a canonical representation (see Subsection 2.6) and bit-level operations (starting at line 5), which are best implemented bitsliced, hence with a bitslice representation. As a result, Algorithm 11 takes as input a Boolean sharing in canonical representation, applies CToBs to the sharing  ${z'}^{A_p}$  before its conversion to Boolean masking, and finally applies BsToC the share  ${z_{d-1}^{A_p}}$  to output a canonical representation of the sharing.

### **Algorithm 11** SecB2AModp $_k^d$ New (PINI)

**Input:** d shares Boolean sharing  $\mathbf{x}^{B,k}$ , integer p such that  $p < 2^k$  and  $x \in [0, p[$ . **Output:** d shares arithmetic sharing  $\mathbf{z}^{A_p}$  such that z = x.

```

1: for i = 0 to d - 2 do

2: z_i^{A_p} \leftarrow \mathbb{Z}_p

3: z'_i^{A_p} \leftarrow p - z_i^{A_p}

4: z'_{d-1}^{A_p} \leftarrow 0

5: a^{B,k} \leftarrow \text{SecA2BModp}_k^d \left( z'^{A_p} \right) \Rightarrow \text{Applies CToBs to } z'^{A_p} \text{ and use Algorithm 10.}

6: b^{B,k} \leftarrow \text{SecAddModp}_k^d \left( a^{B,k}, x^{B,k} \right) \Rightarrow \text{Use Algorithm 17.}

7: c^{B,k} \leftarrow \text{RefreshIOS}_k^d \left( b^{B,k} \right) \Rightarrow \text{Use algorithm 1 of [GPRV21], generalized in Algorithm 18.}

8: z_{d-1}^{A_p} \leftarrow \text{UnMask}_k^d \left( c^{B,k} \right) \Rightarrow \text{XOR all shares together, and applies BsToC } z_{d-1}^{A_p}.

```

Let us introduce two definitions relating to the properties of the IOS refresh gadget before proving the security of Algorithm 11.

**Definition 6** (Uniformity ([GPRV21], adapted)). A refresh gadget G is uniform if its output is a uniformly distributed sharing of x for any fixed input sharing x.<sup>8</sup>

**Definition 7** (IOS ([GPRV21], adapted)). A refresh gadget G is t-IOS if it is uniform and if for every pair of sharings (x,y) that represent the same value (i.e., such that x=y) and for every set of probes P with  $|P| \leq t$ , there exists a simulator that can perfectly simulate the probes (i.e., output values with the same distribution) by knowing only |P| input shares and |P| output shares. A refresh gadget with d shares is said to be IOS if it is (d-1)-IOS.

#### Proposition 5. Algorithm 11 is PINI.

*Proof.* We build a PINI simulator: given a set of probes P and share indexes B. We distinguish two cases: either (i)  $d-1 \in B$  or there is a probe of P in the UnMask gadget, or (ii) there is no such probe.

In case (ii), we remark that the gadgets SecA2BModp and SecAddModp are PINI, as well as RefreshIOS (it is sharewise after application of the random-zero transform of [Cor18]). The probes in these gadgets can thus be simulated by knowing at most |P| shares of  $\boldsymbol{x}^{B,k}$

<sup>&</sup>lt;sup>8</sup>This is not the same notion as the uniformity used in threshold implementations [NRR06], where the sharing x is assumed to be uniform. Here, the distribution of the output sharing y must be independent of x, conditioned on x.

and some  $z_i^{A_p}$  for  $i \in [0, d-2]$ . Such  $z_i^{A_p}$ , which also are the possible output shares to simulate, can be perfectly simulated since they are randomly generated by the gadget.

In case (i), we consider the (d-1)-PINI simulator that has to simulate the output shares with index in B and the internal probes P. Let  $(P_0, P_r, P_u)$  be a partition of P such that the probes of  $P_0$  are in SecA2BModp and SecAddModp, the ones of  $P_r$  are in RefreshIOS, and the ones of  $P_u$  are in UnMask. We first describe the simulator, then prove that it is correct.

The PINI simulator for SecB2AModp first selects randomly  $\boldsymbol{z}_{d-1}^{A_p}$ , then it generates a uniformly random sharing  $\boldsymbol{c}^{B,k}$  of  $\boldsymbol{z}_{d-1}^{A_p}$ , from which it can simulate any probe in  $P_u$ . Next, using the IOS simulator, it determines the set of share indexes  $B_r$  of  $\boldsymbol{b}^{B,k}$  required to simulate  $P_r$ , with  $|B_r| \leq |P_r|$  (some shares from  $\boldsymbol{c}^{B,k}$  are also needed for this simulation, but they are already simulated). We then consider the PINI simulation of the composition of SecA2BModp and SecAddModp (since these two gadgets are PINI): the shares of  $\boldsymbol{b}^{B,k}$  with index in  $B_r$  and the probes  $P_0$  can be simulated with the shares of  $\boldsymbol{x}^{B,k}$  and  $\boldsymbol{z'}^{A_p}$  whose index belongs to  $B_r \cup B_0$ , for some  $B_0$  such that  $|B_0| \leq |P_0|$ . Finally, the simulator completes the simulation by requesting the shares of  $\boldsymbol{x}^{B,k}$  with index in  $B_r \cup B_0$  and draws randomly all shares  $\boldsymbol{z}_i^{A_p}$  with  $i \in (B_r \cup B_0 \cup B) \setminus \{d-1\}$ , which enables the simulation of the required  $\boldsymbol{z'}_i^{A_p}$ .

Let us first observe that the number of inputs required for the simulation is admissible:  $|B_r \cup B_0| \leq |P|.$  Further, let us denote by  $B^* \subset \llbracket 0,d-2 \rrbracket$  the set of i such that  $\boldsymbol{z}_i^{A_p}$  is used in the simulation (we exclude  $\boldsymbol{z}_{d-1}^{A_p}$  for now). We remark  $B^* = B_r \cup B_0 \cup (B \setminus \{d-1\})$ , and therefore that  $|B^*| \leq |P_r \cup P_0| + |B \setminus \{d-1\}| \leq d-2$  where the latter inequality comes from the hypothesis that either  $|P_u| \geq 1$  (hence  $|P_0 \cup P_r| + |B| \leq d-2$ ), or  $d-1 \in B$  (hence  $|P| + |B \setminus \{d-1\}| \leq d-2$ ). As a result  $|\llbracket 0,d-2 \rrbracket \setminus B^*| \geq 1$ , and, taking  $i^* \in \llbracket 0,d-2 \rrbracket \setminus B^*$ , we observe that  $\boldsymbol{z}_{i^*}^{A_p}$  is never used in the simulation.

We now show that the simulation is correct: for each value that is simulated, we show that its distribution matches the true distribution, and furthermore we prove that the simulation is consistent with (i.e., the simulated joint distribution is equal to the true distribution) the simulation of the values for which we already proved the correctness. First, the simulated shares  $\mathbf{z}_i^{A_p}$  (except  $\mathbf{z}_{d-1}^{A_p}$ ) and  $\mathbf{z'}_i^{A_p}$  follow the same distribution as in Algorithm 11. Next, since  $\mathbf{z}_{d-1}^{A_p} = \mathbf{z} - \sum_{i=0}^{d-2} \mathbf{z}_i^{A_p} \mod p$  and since one of the terms of the sum  $(\mathbf{z}_{i^*}^{A_p})$  is not used in the simulation and is uniformly distributed,  $\mathbf{z}_{d-1}^{A_p}$  appears to the adversary as a fresh uniform value, and its simulation is correct. We continue with the correct simulation of the probes in  $P_0$  and the shares  $\mathbf{b}_i^{B,k}$ : it follows from the PINI simulators of SecA2BModp and SecAddModp. Since RefreshIOS is uniform, its output sharing  $\mathbf{c}^{B,k}$  is a uniform sharing of  $\mathbf{z}_{d-1}^{A_p}$  which is independent of  $\mathbf{b}^{B,k}$ . The simulation of the probes in  $P_r$  by the RefreshIOS simulator ensures that the simulation of these probes and of  $\mathbf{c}^{B,k}$  are correct. Finally, the simulation of the probes  $P_u$  is trivially correct.

We finally remark that the conversion modulo  $2^k$  SecB2A $_k^d$  can be implemented by following Algorithm 11, using the new SecA2B and SecAdd instead of SecA2BModp and SecAddModp. The security proof is not changed.

# 4 Gadgets performance

In this section, we compare the performance of each of our new gadgets to the state-of-theart gadgets implementing the same feature (ignoring the differences in security property). We first describe the benchmark setup and the general implementation strategy, then we report the performance of state-of-the-art gadgets compared to the new gadgets.

### 4.1 Benchmarking setup

We implemented all the gadgets of Section 3 in the C programming language<sup>9</sup> and measured their performance on a ARM Cortex-M4 32-bit micro-controller. The recursive gadgets were naively implemented, only forcing inlining at a few places where the control flow overhead was identified as a bottleneck. The benchmarks were run on the NUCLEO-L4R5ZI development board, which is used by the PQM4 benchmarking project [KRSS].<sup>10</sup> We used the default clock configuration of PQM4: the system clock and the AHB bus are clocked to 16 MHz and the TRNG peripheral is clocked at 48 MHz as recommended by the manufacturer. The performance measurements are based on the DWT\_CCYCNT cycle accurate counter (hence also clocked at 16 MHz).

The randomness used in the gadget is taken on-the-fly from the on-chip TRNG, with no buffering, hence the time needed to generate randomness is included in the gadget's execution time. Concretely, the TRNG outputs 32-bit words, which are used as-is when randomness is needed in a bitsliced gadget. When uniform randomness in  $\mathbb{Z}_p$  is needed, we extract two k-bit blocks in a 32-bit word from the TRNG ( $k = \lceil \log_2 p \rceil \le 16$ ) and apply rejection sampling: each block whose value is lower than p is accepted as a fresh  $\mathbb{Z}_p$  random element while the other blocks are discarded. When uniform randomness in  $\mathbb{F}_2^k$  with k < 32 is needed (e.g., in the Kyber implementation, k = 13 for the KS adder), we generate  $\lfloor 32/k \rfloor$  k-bit words from 32 bits of randomness, dropping the remaining bits. The bottleneck in the randomness generation is the TRNG, which outputs four fresh random 32-bit words every 213 cycles with the previously described clock configuration 11, resulting in a throughput of 32 random bits every 53.25 cycles.

In the rest of this Section, we report the performance of concrete implementations, for which we have to fix the value of p. We take the prime of Kyber: p=3329, which implies that most of the gadgets will be benchmarked for  $k=\lceil\log_2(p)\rceil=12$ . All the cycle counts reported in this Section are for 256 independent calls to a given gadget since it is the polynomial size of Kyber. Since 256 is a multiple of the register width (32 bits), we fully exploit the bitslicing potential of the processor.

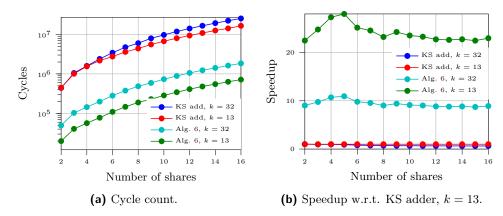

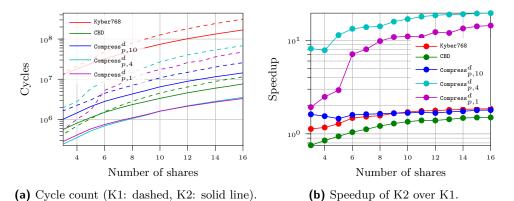

# 4.2 Performance of SecAdd $_k^d$

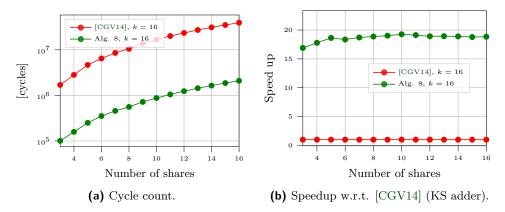

We first analyze masked adders on k bits. We compare in Figure 2 the Kogge-Stone adder from [BBE<sup>+</sup>18], which has a complexity of  $\mathcal{O}(\log(k)d^2)$  CPU instructions, and the Algorithm 6 which has a complexity of  $\mathcal{O}(kd^2)$  bit operations. First, we observe that Algorithm 6 requires fewer cycles than the KS adder. For k=13, Algorithm 6 is about 23 times faster and for k=32, the speedup is about 9x. As expected form the complexities, the gain of Algorithm 6 decreases as k increases. Yet for relevant parameters for lattice-based cryptography, it provides a significant improvement.

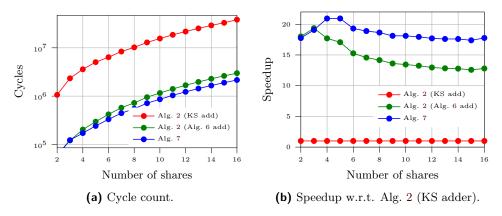

# 4.3 Performance of SecAddModp $_k^d$

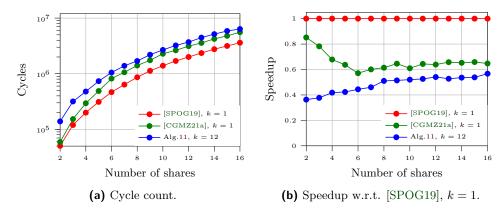

Next, we compare in Figure 3 the execution time for various  $\mathtt{SecAddModp}_d^k$  gadgets. Concretely, we compare (i) Algorithm 2 when using the KS adder (not bitsliced), (ii) Algorithm 2 with the Algorithm 6 as underlying  $\mathtt{SecAdd}$  (hence leveraging bitslicing), and (iii) Algorithm 7 (also using Algorithm 6). We observe that (ii) has a speedup of about 12x over

<sup>&</sup>lt;sup>9</sup>The need for assembly implementations is discussed in Section 5 (as well as their performance characteristics). We focus on C implementations in this section to ease the comparison with state-of-the-art gadgets, which were implemented in C.

<sup>&</sup>lt;sup>10</sup>Our benchmarks are compiled with options -02 -flto, and we note that speedup figures for the -03 and -0s optimization levels are very similar. The GCC version is 9.4.0.

<sup>&</sup>lt;sup>11</sup>As written in Section 3.2 of the datasheet (https://www.st.com/resource/en/reference\_manual/rm0432-stm3214-series-advanced-armbased-32bit-mcus-stmicroelectronics.pdf), and confirmed by our experiments.

Figure 2: Performance comparison of SecAdd implementations.

**Figure 3:** Performance comparison of  $SecAddModp_{12}^d$  implementations.

(i), which is smaller than the improvement of 21x on the adder (SecAdd) itself. Indeed, the execution time of (ii) is dominated by the SecAdd calls and the MUX (Line 9) since both require in total 2(13-1) SecAnd executions, and while the speedup for the SecAdd part is 21x, the one for the MUX part is only the bitslicing gain of 32/12 = 2.7x. Finally, in case (iii), the dedicated gadget allows to roughly half the cost of the MUX by replacing it with a SecAdd, which gives a speedup of about 1.3x over (ii).

### 4.4 Performance of arithmetic-to-Boolean conversions

SecA2BModp $_k^d$ . Similarly, we compare the performance of SecA2BModp $_k^d$  implementations in Figure 4. The reference implementation (i) is Algorithm 3 (with KS adder). We compare it to (ii) a modified Algorithm 3 using the bitsliced adder (Algorithm 7), and to (iii) the new Algorithm 10. We note that the speedup of (ii) over (i) is similar to the one we got for the corresponding SecAddModp gadgets (albeit a bit lower due to the presence of RefreshSNI whose bitslicing speedup is only 32/12). The new gadget (iii) has a speedup of 2x over (ii), thanks to the removal of refresh gadgets and the execution of one SecAdd with the number of shares halved.

SecA2B $_k^d$ . We compare the performances of SecA2B $_k^d$  gadgets in Figure 5 for k=16. The reference implementation (i) corresponds to the conversion from [CGV14, Alg. 4] with a KS adder. It is equivalent to Algorithm 3 by replacing the SecAddModp with SecAdd. It is compared to (ii) the new Algorithm 8 for SecA2B $_k^d$  leveraging the bitsliced adder

Figure 4: Performance comparison of SecA2BModp $_{12}^d$  implementations.

**Figure 5:** Performance comparison of  $SecA2B_{16}^d$  implementations.

(Algorithm 7). The performance gain is around 18.8x by moving from (i) to (ii). This is expected from the improvements on the underlying  $\mathtt{SecAdd}_k^d$  (see Figure 2).

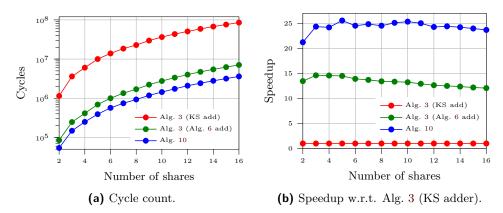

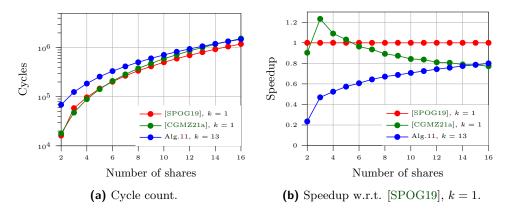

#### 4.5 Performance of Boolean-to-arithmetic conversions

SecB2AModp $_k^d$ . We next compare in Figure 6 the performance of various implementations of SecB2AModp. We consider as state-of-the-art the algorithms from [SPOG19] and [CGMZ21a] which both implement SecB2AModp $_k^d$  from single-bit conversions. As a result, their computational cost is proportional to k, and we observe that they have comparable cost, with a small advantage for [SPOG19] (which agree with the results on Intel x86 processors of [CGMZ21a], Table 4).

Our bitsliced conversion gadget (Algorithm 11) always operates on  $\lceil \log_2(p) \rceil$  bits (here, 12). Concretely, for 16 shares, the bitsliced conversion of any  $x \in \mathbb{Z}_p$  is only twice as slow as the state-of-the-art single-bit conversions, and is therefore on par with state-of-the-art 2-bit conversions. For larger k-bit conversions, the advantage of Algorithm 11 grows linearly with k.

SecB2A. Finally, we compare in Figure 7 the performance of various implementations of SecB2A. To do so, instantiate the  $2^k$  variant of the gadgets in the previous experiment. The conclusions are similar: for a single bit (k=1) to convert from Boolean to arithmetic masking, both [SPOG19] and [CGMZ21a] are more efficient than the new gadget. For k>1, our gadget is more efficient.

Figure 6: Performance comparison of SecB2AModp implementations.

Figure 7: Performance comparison of SecB2A implementations.

# 5 Side-channel leakage assessment of implementations

The previous section demonstrates that using a Boolean representation (hence using bitslicing for micro-controllers) for masking conversion leads to performance gains. In order to ensure that the proposed gadgets meet their goal of providing concrete d-1-order security, we perform leakage assessment. As hinted by the literature [BGG<sup>+</sup>14, BWG<sup>+</sup>22], the gadgets from the previous section, which are written in C to ease comparisons, lead to unintended leakage recombination.

In the following section, we first recall the Test Vector Leakage Assessment (TVLA) [GJJ<sup>+</sup>11, CMG<sup>+</sup>, SM16] and introduce our side-channel measurement setup. We then show that TVLA confirms the presence of unintended leakage in the gadgets written in C. Next, we present hardened implementations of the new conversion gadgets which, using a mix C and assembly, remove these problematic leakages. Finally, we discuss the overhead of this hardening, answering an open question from [BWG<sup>+</sup>22].

### 5.1 Test vector leakage assessment

**TVLA.** Student's t-test performs hypothesis testing to highlight difference in the i-th order moment of two distributions. In the context of side-channel leakage assessment, these two sets are traces corresponding to two distinct values for the secret input of a cryptographic implementation. This methodology is known as the (fixed-versus-fixed) TVLA, and the commonly adopted threshold for declaring the presence of leakage at a given order is a p-value smaller than  $10^{-5}$ . This p-value is translated to a threshold on the t statistic, taking into account the number of independent tests performed [DZD<sup>+</sup>17, WO19] (otherwise there is a high risk of false positive).

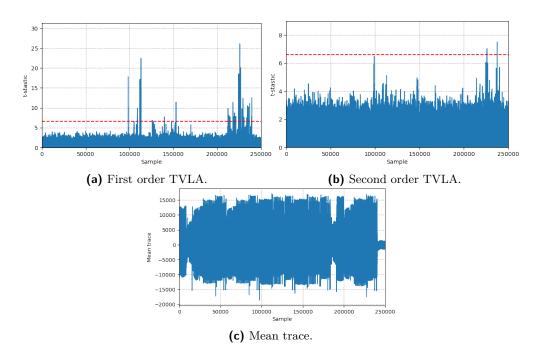

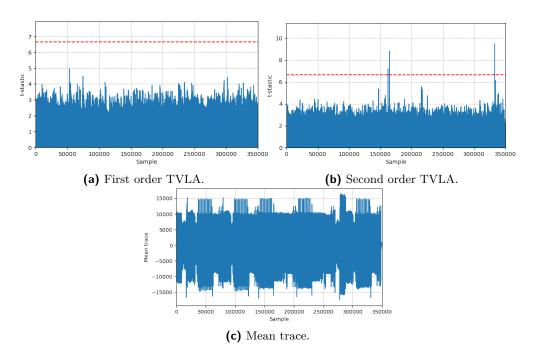

Concretely, we instantiate the SecA2BModp^p\_k and SecB2AModp^p\_k gadgets with d=2, p=3329 and k=12 (to match Kyber parameters in the next section). We analyze the difference in the means (first-order moment), and in the variance (second-order centered moment) following the algorithm from [SM16].<sup>12</sup> In both cases, we collect 100,000 traces to compute the t statistic. In the following plots, the threshold is denoted with a red horizontal line.

SCA measurement setup. The side-channel evaluation is performed on the STM32F415 target board of the CW308 Chipswhisperer. The target is running at a clock frequency of 80 MHz which is derived from an 8 MHz external crystal. The side-channel traces are captured thanks to a Picoscope5244D with a 250 MSamples/sec attached to a CT1 current probe from Tektronix. As a result, the signal-to-noise ratio on a canonical representation of a word over  $\mathbb{Z}_p$  within the implementation is around 0.4, showing that the setup provides clean measurements.

**Disclaimer.** TVLA is a good tool to detect the presence of unintended lower-order leakage and to perform root cause analysis of weaknesses [GOP21]. It does however not guarantee the security of the implementation [Sta18], especially in the case of low-noise targets [BS20, BS21].

#### 5.2 Leakage assessment of C implementations

Figure 8 shows the TVLA analysis of the (pure) C implementation of the SecB2AModp and SecA2BModp gadgets with two shares. Namely, Figure 8b highlights evidence of second-order leakage, as expected. However, Figure 8a highlights evidence of first-order leakage,

<sup>12</sup>Using the implementation of the SCALib library (https://scalib.readthedocs.io/en/latest/source/scalib.metrics.html).

$<sup>^{13} \</sup>mathtt{https://rtfm.newae.com/Targets/UF0\%20Targets/CW308T-STM32F/}$

**Figure 8:** TVLA results with 100,000 traces for SecB2AModp followed by a SecA2BModp on both distinct sets of inputs (fixed vs. fixed). Implementation is in plain C.

which should not happen in a proper first-order secure implementation. This is due to so-called "transition leakage" phenomenon, where the leakage depends (for example) on the Hamming distance between the two consecutive values stored in a register [BGG<sup>+</sup>14]. When these two values are the two shares of a Boolean sharing, this produces first-order leakage, since the Hamming distance of the two shares is equal to the Hamming weight of the shared value.

### 5.3 Implementing masking conversions with C & assembly

Avoiding Hamming distance leakage between the shares of a sharing requires an accurate control of the (micro-)architectural state of a processor. Since the C programming language does not give this level of control, we implement the manipulations of the shares in assembly. However, we keep C implementations for gadgets that compose other gadgets and do not touch the shares directly. <sup>14</sup> This eases the writing and improves the readability of the implementations without degrading its security.

Heuristics for secure assembly gadgets. Based on an abstract understanding of the architecture of a small micro-controller<sup>15</sup>, we anticipate transition leakage to appear in the registers, on the ALU inputs and outputs, and in the memory read and write paths. Each assembly gadget (SecAnd<sup>d</sup>,  $\oplus^d$  and BitCopyMask<sup>d</sup><sub>k</sub>) therefore takes as input a pointer to the shares (avoiding the presence of the shares in the registers when C code is executed) and uses dummy operations to avoid damaging transition leakage. We use a defensive approach: a dummy load (resp. store) of a non-sensitive variable (e.g., a constant) is

<sup>&</sup>lt;sup>14</sup>We also kept the C implementations for gadgets that manipulate shares but do not exhibit lower-order leakage. This is admittedly not robust to compilation toolchain changes, but we do not see it as an issue since the compiler-generated code can be used as new assembly source. Moreover, our evaluations are specific to a single MCU, hence our code offers anyway to portable security guarantees.

$<sup>^{15}\</sup>mathrm{We}$  do not have access to the detailed architecture of the Cortex-M4 MCU.

**Figure 9:** TVLA results with 100,000 traces for SecB2AModp followed by a SecA2BModp on both distinct sets of inputs (fixed vs. fixed). Implementation is a mix of C and assembly.

**Table 1:** Gadget hardening overhead: number of execution cycles of the hardened C & assembly implementation divided by the number of execution cycles for the pure C implementation.

| d                          | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   |

|----------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| $\mathtt{SecAdd}_{12}$     | 1.45 | 1.57 | 1.61 | 1.67 | 1.69 | 1.73 | 1.71 | 1.71 | 1.69 | 1.69 | 1.68 | 1.68 | 1.67 | 1.66 | 1.65 |

| $SecAddModp_{12}$          | 1.36 | 1.49 | 1.56 | 1.63 | 1.66 | 1.70 | 1.69 | 1.69 | 1.68 | 1.67 | 1.67 | 1.67 | 1.66 | 1.65 | 1.65 |

| $SecB2AModp_{12}$          | 1.29 | 1.36 | 1.39 | 1.43 | 1.46 | 1.48 | 1.48 | 1.50 | 1.51 | 1.52 | 1.52 | 1.53 | 1.53 | 1.53 | 1.53 |

| $\mathtt{SecA2BModp}_{12}$ | 1.35 | 1.42 | 1.42 | 1.47 | 1.50 | 1.51 | 1.51 | 1.53 | 1.54 | 1.55 | 1.56 | 1.57 | 1.57 | 1.57 | 1.57 |

executed between the loads (resp. stores) of shares. Moreover, we keep a minimum number of shares in the register file at any moment (there are at most three shares in the register file at the same time), erasing any register containing a share as soon as possible.

**Leakage assessment.** We first applied TVLA to SecAnd<sup>d</sup> and  $\oplus$ <sup>d</sup> in order to ensure that our defensive approach is effectively preventing lower-order leakage. Then, the masked conversions SecA2BModp and SecB2AModp are evaluated, and the results are reported in Figure 9, showing no first-order leakage with up to 100,000 traces on the evaluated micro-controller (showing that the remaining C code does not cause lower-order leakage).

**Performance.** The defensive implementation approach has a significant performance overhead (between 1.29x and 1.71x) over the pure C implementation (see Table 1).<sup>16</sup> Formal verification tools that leverage detailed knowledge of the processor's microarchitecture [GHP<sup>+</sup>21, BGG<sup>+</sup>21] could be used to improve the performance of these implementations by allowing a less defensive implementation strategy. It would also increase the confidence in the security of these implementations (as well as formally validating the security of the code generated by the C compiler), providing a complementary evaluation to the TVLA.

$<sup>^{16}</sup>$ The benchmarking setup is the same as the one used in Section 4.

```

{f Algorithm~13} Kyber.CPAPKE.Dec (\hat{m s},c)

Algorithm 12 Kyber.CCAKEM.Dec (c, sk)

Input: Ciphertext c = (c_u, c_v), secret key

Input: Secret key \hat{s} \in \mathbb{R}_p^l, ciphertext c =

sk := (\hat{s}, pk, H(pk), z).

(c_u, c_v).

Output: Decapsulated secret K.

Output: Plaintext m.

1: m' := \text{Kyber.CPAPKE.Dec}(\hat{s}, c)

1: u := \mathtt{Decompress}_{p,d_u}^d(c_u) \quad \triangleright u \in \mathbb{R}_p^l, d_u = 10

2: v := \mathtt{Decompress}_{p,d_v}^d(c_v) \quad \triangleright v \in \mathbb{R}_p, d_v = 4

2: (\bar{K}', \sigma') := G^d(m'||H(pk))

3: (c'_u, c'_v) := \text{Kyber.CPAPKE.Enc}(pk, m', \sigma')

3: \hat{z} = \hat{s}^T \circ \text{NTT}(u)

\triangleright \hat{z} \in \mathbb{R}_p

4: if (c_u = c'_u) \& (c_v = c'_v) then

4: w := v - NTT^{-1}(\hat{z})

K := \mathtt{KDF}(\bar{K}'||\mathtt{H}(c))

5: m := \mathsf{Compress}_{p,1}^d(w) \triangleright m is a 256-bit string

6: else

7:

K := KDF(z||H(c))

```

# 6 Application to lattice-based KEMs

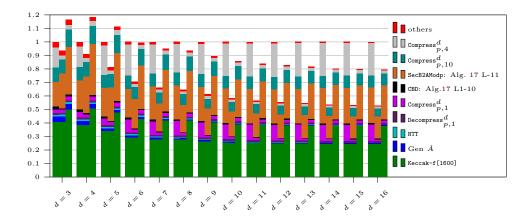

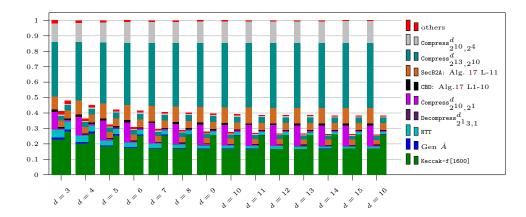

In this section, we put our new gadgets together into an implementation of Kyber. We focus on Kyber768 to maximize to comparability with the recent works of Coron et al. [CGMZ21a, CGMZ21b]. Eventually, we apply the same methodology to Saber and report the results. <sup>17</sup>

# 6.1 Overview of masked Kyber

Kyber leverages the Fujisaki-Okamoto (FO) transform to transform a chosen-plaintext attack (CPA) secure public encryption scheme (PKE) intro a chosen-ciphertext attack (CCA) secure KEM [FO99, ABD+19]. Kyber decapsulation is described Algorithm 12 where the ciphertext c is decrypted with CPAPKE.Dec(·) to obtain the message m'. This message is then re-encrypted with CPAPKE.Enc(·) to derive the ciphertext c' using some pseudo-randomness  $\sigma'$  derived from m' and the public key. The encapsulated secret K is then returned only if c and c' are identical, which ensures that the c has been derived from the public key. We focus on the masked implementation of Kyber.CCAKEM.Dec since it is the most sensitive to SCA [RRCB20, UXT+22]. In the following algorithms, green means that no masking is required  $^{18}$ , blue that masking is required and has linear complexity with d (when implemented with arithmetic masking), and red that masking with quadratic complexity is required, which means that bitsliced Boolean masking may be beneficial.

Kyber.CPAPKE manipulates polynomial ring  $\mathbb{Z}_p[X]/(X^n+1)$  that we denote as  $\mathbb{R}_p$ . Vectors of size l of polynomials are next denoted with bold such that  $\boldsymbol{x} \in \mathbb{R}_p^l$ . Kyber makes also use of NTT representation that we denote  $\hat{x} := \text{NTT}(x)$ . The first step (Line 1-2) in decryption is to map the ciphertext c into the corresponding (vector of) polynomial(s). Then, the secret key  $\hat{\boldsymbol{s}}$  is multiplied with  $\boldsymbol{u}$  and subtracted to v (Line 3-4). Concretely, these operations (addition, multiplications and NTT) are performed with arithmetic masking and can be applied share-by-share, hence with linear complexity. Finally, each coefficient (in  $\mathbb{Z}_p$ ) of the resulting polynomial is compressed to a single bit, which represents the rounding to  $\lceil p/2 \rceil$  or 0. We detail the masked implementation of Compress $_{p,c}^d$  in Algorithm 15.

Finally, Kyber.CPAPKE.Enc is described in Algorithm 14. This algorithm starts by generating 2l+1 noise polynomials (Line 2-4) whose coefficients follow a central binomial distribution (CBD, see Algorithm 17) with parameter  $\eta$ , such that they belong to  $[-\eta, \eta]$ . The CBD takes as input a pseudo-random string of bits which is computed as the hash PRF of the random seed  $\sigma$  and a nonce. Next, the noise  $(e_1$  and  $e_2)$  is added to the product

$<sup>^{17}</sup>$ We implemented the NIST level 2 version of the Saber family, which is called Saber.

$<sup>^{18}</sup>$ We focus on long-term security of the Kyber private key, and assume that the exchanged key K can be leaked to a side-channel adversary. Otherwise, the derivation of K should also be protected.

of the public key and the vector of noise polynomials r (Line 5-7). The message m is decompressed to a polynomial with  $\mathtt{Decompress}_{q,1}^d$  (see Algorithm 16) and added to the sum. The last step is to compress (i.e., rounding then divide) both u to  $d_u$  bits and v to  $d_v$  bits, which gives the ciphertext (Lines 8-9).

#### Algorithm 14 Kyber.CPAPKE.Enc $(pk, m, \sigma)$

**Input:**  $pk = (\hat{t}, \hat{A})$  with  $\hat{t} \in \mathbb{R}_p^l$ ,  $\hat{A} \in \mathbb{R}_p^{l \times l}$ ; message  $m \in \{0, 1\}^n$ , randomness  $\sigma \in \{0, 1\}^{256}$ . **Output:** Ciphertext  $c = (c_u, c_v)$ .

```

1: for i = 0 to l - 1 do

▶ Noise sampling

m{r}[i] := \mathtt{CBD}^d_{\eta_1}(\mathtt{PRF}^d(\sigma,i))

\triangleright r \in \mathbb{R}_p^l, \, \eta_1 = 2

e_1[i] := \mathtt{CBD}_{\eta_2}^d(\mathtt{PRF}^d(\sigma, i+l))

\triangleright e_1 \in \mathbb{R}_p^l, \, \eta_2 = 2

4: e_2 := CBD_{n_2}^d(PRF^d(\sigma, 2 \cdot l))

\triangleright e_2 \in \mathbb{R}_p, \, \eta_2 = 2

5: \hat{\boldsymbol{r}} := \text{NTT}(\boldsymbol{r})

6: \boldsymbol{u} := \mathtt{NTT}^{-1}(\hat{\boldsymbol{A}}^T \circ \hat{\boldsymbol{r}}) + \boldsymbol{e}_1

riangleright oldsymbol{u} \in \mathbb{R}_p^l

7: v := \mathtt{NTT}^{-1}(\hat{\boldsymbol{t}}^T \circ \hat{\boldsymbol{r}}) + e_2 + \mathtt{Decompress}_{v,1}^d(m)

\triangleright v \in \mathbb{R}_p

8: c_u := \mathtt{Compress}_{p,d_u}^d(\boldsymbol{u})

\triangleright d_u = 10

9: c_v := \mathtt{Compress}_{p,d_v}^d(v)

\triangleright d_v = 4

```

### 6.2 Kyber768 implementations

Next, we detail our implementation of Kyber768, whose parameters are  $d_u=10$ ,  $d_v=4$ ,  $\eta_1=\eta_2=2$ , l=3 and  $p=3329.^{19}$  For each of the algorithms  $\mathtt{Compress}_{p,c}^d$ ,  $\mathtt{Decompress}_{p,c}^d$  and  $\mathtt{CBD}_{\eta}^d$ , we will describe our new construction together with the previous state-of-the-art solution.

The implementations K1, K2 and K3 are derived from the PQM4 [KRSS] optimized Kyber implementation for the Cortex-M4: the linear operations (such as the NTT) are kept (and applied to all the shares), while the non-linear operations are replaced by masked gadgets. We keep a single noise polynomial in memory at any time in Algorithm 14 to reduce the stack usage. Implementation K1 relies on the C implementation provided by Coron et al. of their gadgets [CGMZ21b] and on new C implementations of the single-bit B2A conversion of [SPOG19]. Implementation K2 is based on a C-only implementation of the new bitsliced gadgets while K3 uses a mix of C and assembly to avoid lower-order leakage (see details in Subsection 5.3).