**River Publishers Series in Circuits and Systems**

# RF CMOS OSCILLATORS FOR MODERN WIRELESS APPLICATIONS

Masoud Babaie, Mina Shahmohammadi and Robert Bogdan Staszewski

## **RF CMOS Oscillators for Modern** Wireless Applications

Series Editors:

### MASSIMO ALIOTO

National University of Singapore Singapore

#### **KOFI MAKINWA**

Delft University of Technology The Netherlands

#### **DENNIS SYLVESTER**

University of Michigan USA

Indexing: All books published in this series are submitted to the Web of Science Book Citation Index (BkCI), to SCOPUS, to CrossRef and to Google Scholar for evaluation and indexing.

The "River Publishers Series in Circuits & Systems" is a series of comprehensive academic and professional books which focus on theory and applications of Circuit and Systems. This includes analog and digital integrated circuits, memory technologies, system-on-chip and processor design. The series also includes books on electronic design automation and design methodology, as well as computer aided design tools.

Books published in the series include research monographs, edited volumes, handbooks and textbooks. The books provide professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics covered in the series include, but are by no means restricted to the following:

- Analog Integrated Circuits

- Digital Integrated Circuits

- Data Converters

- Processor Architecures

- System-on-Chip

- Memory Design

- Electronic Design Automation

For a list of other books in this series, visit www.riverpublishers.com

## RF CMOS Oscillators for Modern Wireless Applications

### **Masoud Babaie**

Delft University of Technology The Netherlands

### Mina Shahmohammadi

Catena The Netherlands

### Robert Bogdan Staszewski

University College Dublin Ireland

#### Published 2019 by River Publishers River Publishers Alsbjergvej 10, 9260 Gistrup, Denmark www.riverpublishers.com

#### **Distributed exclusively by Routledge** 4 Park Square, Milton Park, Abingdon, Oxon OX14 4RN 605 Third Avenue, New York, NY 10017, USA

*RF CMOS Oscillators for Modern Wireless Applications /* by Masoud Babaie, Mina Shahmohammadi, Robert Bogdan Staszewski.

© The Editor(s) (if applicable) and The Author(s) 2019. This book is published open access.

#### **Open Access**

This book is distributed under the terms of the Creative Commons Attribution-Non-Commercial 4.0 International License, CC-BY-NC 4.0) (http://creativecommons.org/licenses/by/4.0/), which permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, a link is provided to the Creative Commons license and any changes made are indicated. The images or other third party material in this book are included in the work's Creative Commons license, unless indicated otherwise in the credit line; if such material is not included in the work's Creative Commons license and the respective action is not permitted by statutory regulation, users will need to obtain permission from the license holder to duplicate, adapt, or reproduce the material.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper.

Routledge is an imprint of the Taylor & Francis Group, an informa business

#### ISBN 978-87-93609-49-5 (print)

While every effort is made to provide dependable information, the publisher, authors, and editors cannot be held responsible for any errors or omissions.

### Contents

| Pr  | eface                      |                                                                                                                                                 | ix                    |

|-----|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Lis | st of F                    | igures                                                                                                                                          | xi                    |

| Lis | st of T                    | ables                                                                                                                                           | xxi                   |

| Lis | st of A                    | bbreviations                                                                                                                                    | xxiii                 |

| 1   | <b>Intro</b><br>1.1<br>1.2 | Deduction         Introduction         Technology Scaling         1.2.1         Supply Voltage         1.2.2         Quality Factor of Passives | 1<br>1<br>5<br>6<br>7 |

|     |                            | 1.2.3       Noise of Active Devices          References                                                                                         | 9<br>10               |

| 2   | LC (                       | Oscillator Structures                                                                                                                           | 13                    |

|     | 2.1                        | Introduction                                                                                                                                    | 13                    |

|     | 2.2                        | Class-B Oscillator Topology                                                                                                                     | 16                    |

|     | 2.3                        | Class-C Oscillator Topology                                                                                                                     | 19                    |

|     | 2.4                        | Class-D Oscillator Topology                                                                                                                     | 21                    |

|     | 2.5                        | Class-F Oscillator Topologies                                                                                                                   | 22                    |

|     | 2.6                        | Conclusion                                                                                                                                      | 22                    |

|     |                            | References                                                                                                                                      | 23                    |

| 3   | <b>A Cl</b><br>3.1<br>3.2  | ass-F <sub>3</sub> CMOS Oscillator         Introduction         Evolution Towards Class-F <sub>3</sub> Oscillator                               | <b>27</b><br>27<br>29 |

|     |                            | 3.2.1 Realizing a Square Wave Across the LC Tank                                                                                                | 30                    |

|     |                            | 3.2.2 $F_3$ Tank                                                                                                                                | 31                    |

#### vi Contents

|   |      | 3.2.3 Voltage Gain of the Tank                                 | 36  |

|---|------|----------------------------------------------------------------|-----|

|   |      | 3.2.4 Class- $F_3$ Oscillator                                  | 38  |

|   | 3.3  | Class-F <sub>3</sub> Phase Noise Performance                   | 41  |

|   |      | 3.3.1 Quality Factor of Transformer-Based Resonator            | 41  |

|   |      | 3.3.2 Phase Noise Mechanism in Class-F <sub>3</sub> Oscillator | 43  |

|   |      | 3.3.3 Class-F <sub>3</sub> Operation Robustness                | 48  |

|   | 3.4  | Experimental Results                                           | 49  |

|   |      | 3.4.1 Implementation Details                                   | 49  |

|   |      | 3.4.2 Measurement Results                                      | 50  |

|   | 3.5  | Conclusion                                                     | 54  |

|   |      | References                                                     | 55  |

| 4 | An U | Ultra-Low Phase Noise Class-F <sub>2</sub> CMOS Oscillator     | 59  |

|   | 4.1  | Introduction                                                   | 59  |

|   | 4.2  | Challenges in Ultra-Low Phase Noise Oscillators                | 60  |

|   | 4.3  | Evolution Towards Class-F <sub>2</sub> Operation               | 64  |

|   | 4.4  | Phase Noise Mechanism in Class- $F_2$ Oscillator               | 71  |

|   | 4.5  | Experimental Results                                           | 77  |

|   | 4.6  | Conclusion                                                     | 82  |

|   |      | References                                                     | 83  |

| 5 | A 1/ | f Noise Upconversion Reduction Technique                       | 87  |

|   | 5.1  | Introduction                                                   | 87  |

|   | 5.2  | Method to Reduce 1/f Noise Upconversion                        | 91  |

|   |      | 5.2.1 Auxiliary Resonant Frequencies                           | 91  |

|   |      | 5.2.2 Harmonic Effects on the Effective ISF                    | 92  |

|   |      | 5.2.3 Resonant Frequency at $2\omega_0$                        | 99  |

|   |      | 5.2.4 $\omega_{CM}$ Deviation from $2\omega_0$                 | 100 |

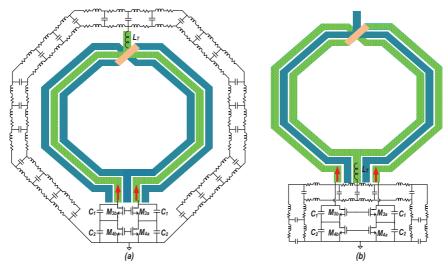

|   | 5.3  | Circuit Implementation                                         | 102 |

|   |      | 5.3.1 Inductor-Based $F_2$ Tank                                | 106 |

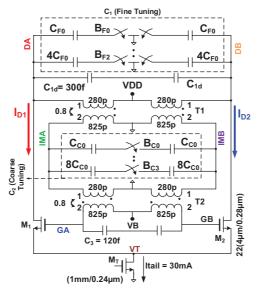

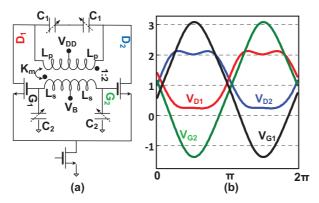

|   |      | 5.3.2 Class- $D/F_2$ Oscillator                                | 108 |

|   |      | 5.3.3 Transformer-Based F <sub>2</sub> Tank                    | 110 |

|   |      | 5.3.4 Class- $F_{2,3}$ Oscillator                              | 111 |

|   | 5.4  | Experimental Results                                           | 114 |

|   |      | 5.4.1 Class- $D/F_2$ Oscillator                                | 114 |

|   |      | 5.4.2 Class- $F_{2,3}$ Oscillator                              | 115 |

|   | 5.5  | Conclusion                                                     | 118 |

|   |      | References                                                     | 118 |

|   |      |                                                                |     |

| 6 | A Sv       | vitching Current-Source Oscillator                 | 123  |

|---|------------|----------------------------------------------------|------|

|   | 6.1        | Introduction                                       | 123  |

|   | 6.2        | Oscillator Power Consumption Trade-offs            | 125  |

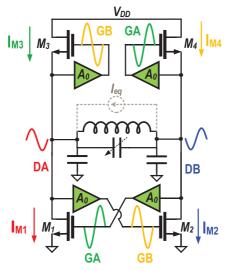

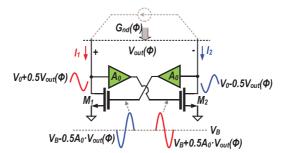

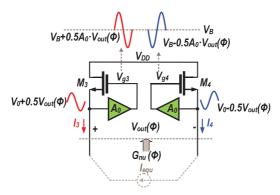

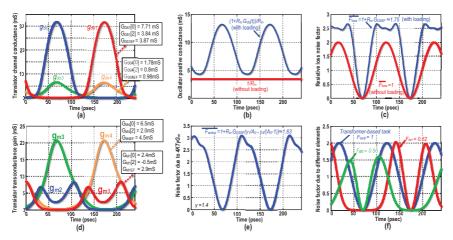

|   | 6.3        | Switching Current-Source Oscillator                | 129  |

|   | 6.4        | Thermal Noise Upconversion                         | 134  |

|   |            | 6.4.1 Calculating the Effective Noise Due to       |      |

|   |            | Transconductance Gain of $M_{1-4}$ Transistors     |      |

|   |            | $(\overline{i_{n,Gm}^2(\phi)})$                    | 134  |

|   |            | 6.4.2 Calculating the Negative Conductance of the  | 10 1 |

|   |            | Oscillator $(G_n(\phi))$                           | 136  |

|   |            | 6.4.3 Calculating the Positive Conductance of the  | 150  |

|   |            | Oscillator $(G_{DS}(\phi))$                        | 139  |

|   |            | 6.4.4 Satisfying Barkhausen Criterion              | 142  |

|   |            | 6.4.5 Phase Noise Equation                         | 142  |

|   | 6.5        | 1/f Noise Upconversion                             | 140  |

|   | 6.5<br>6.6 | •                                                  | 150  |

|   |            | Optimizing Transformer-Based Tank                  |      |

|   | 6.7        | Experimental Results                               | 152  |

|   | 6.8        | Conclusion                                         | 155  |

|   |            | References                                         | 155  |

| 7 |            | ing Range Extension of an Oscillator Through       |      |

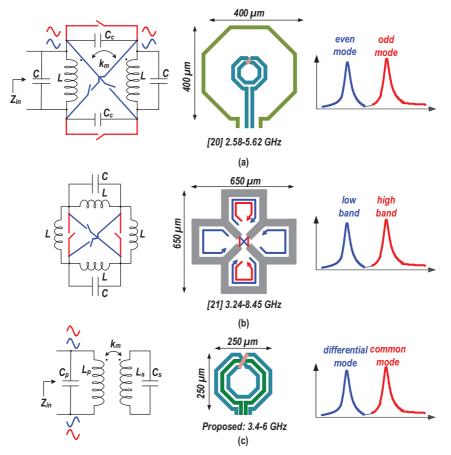

|   | СМ         | Resonance                                          | 161  |

|   | 7.1        | Introduction                                       | 161  |

|   | 7.2        | Mode-Switching Oscillator                          | 164  |

|   | 7.3        | Common-Mode Resonances                             | 170  |

|   | 7.4        | Novel Wide Tuning Range Oscillator                 | 173  |

|   |            | 7.4.1 Dual-Core Oscillator                         | 173  |

|   |            | 7.4.2 Phase Noise Analysis                         | 176  |

|   |            | 7.4.3 Center Tap Inductance                        | 184  |

|   | 7.5        | Experimental Results                               | 184  |

|   |            | 7.5.1 Supply and Ground Routing Inductances        |      |

|   |            | and Losses                                         | 186  |

|   | 7.6        | Conclusion                                         | 188  |

|   |            | References                                         | 189  |

| 0 | A 64       | ndr of DE Oppillaton Deliability in Nanopools CMOS | 193  |

| 8 |            | udy of RF Oscillator Reliability in Nanoscale CMOS |      |

|   | 8.1        | Introduction                                       | 193  |

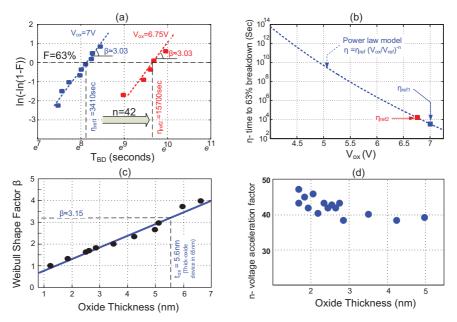

|   | 8.2        | Gate-Oxide Breakdown                               | 194  |

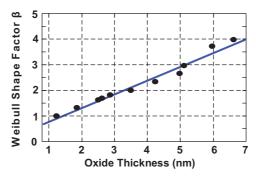

|   |            | 8.2.1 Weibull Slope                                | 195  |

| About tl | he Authors                                              | 211 |

|----------|---------------------------------------------------------|-----|

| Index    |                                                         | 207 |

|          | References                                              | 205 |

| 8.6      | Conclusion                                              | 204 |

|          | 8.5.2 Class- $F_2$ Oscillators                          | 201 |

|          | 8.5.1 Class-F <sub>3</sub> Oscillators                  | 199 |

| 8.5      | Reliability of Class-F <sub>3</sub> Oscillators         | 199 |

| 8.4      | Negative Bias Temperature Instability                   | 199 |

| 8.3      | Hot Carrier Degradation                                 | 198 |

|          | Condition                                               | 197 |

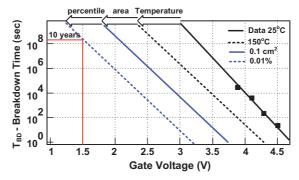

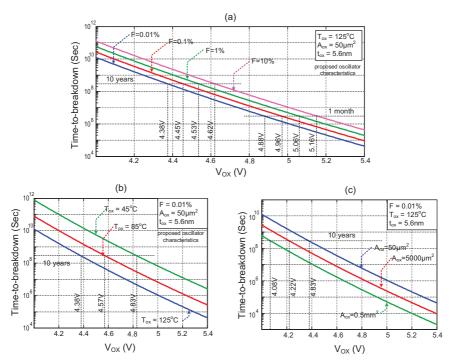

|          | 8.2.4 Principle of Extrapolation to a Specified         |     |

|          | 8.2.3 Area and Temperature Dependence of $T_{BD}$       | 197 |

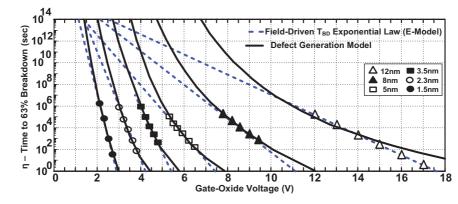

|          | 8.2.2 $\eta$ Estimation for Different Oxide Thicknesses | 195 |

The steady growth of cellular and wireless communications motivates researchers to improve the performance of the systems, overcome the limitations and face new the challenges. One of the key blocks in a wireless radio is the RF oscillator which its purity limits the radio performance. The oscillator's phase noise in a transmit chain results in power leakage into adjacent channels. In the receive chain, the downconversion of a large interferer with noisy local oscillator (LO) cause reciprocal mixing. Furthermore, in orthogonal frequency-division multiplexing (OFDM) systems, the phase noise leads to inter carrier interference and a degradation in the digital communication bit error rate. The trade-off between oscillator's phase noise and its power consumption introduce a challenge for oscillator designers.

The main focus of this book is on the design and implementation of RF oscillators for wireless (mostly cellular) applications. Each oscillator that is introduced in these chapters tackles an obstacle in RF designs, such as low  $1/f^2$  or low  $1/f^3$  phase noise requirements, low voltage, low power requirements, and wide tuning range requirements.

Chapter 1 discusses how a transceiver performance can be limited by an oscillator characteristics. It also reviews how technology scaling affects an oscillator's performance.

Chapter 2 is a reminder how circuit noise up-converts to phase noise in an oscillator, and then briefly introduces and compares different LC oscillator structures.

In Chapter 3 we introduce a class- $F_3$  oscillator topology which demonstrates an improved phase noise performance by enforcing a pseudo-square voltage waveform around the LC tank by increasing the third harmonic of the fundamental oscillation voltage through an additional impedance peak. Furthermore, a comprehensive study of circuit-to-phase-noise conversion mechanisms of different classes of RF oscillator is presented.

#### x Preface

In Chapter 4, we elaborate on a design and implementation of class- $F_2$  oscillators. The main idea is to enforce a clipped voltage waveform around the LC tank by increasing the second-harmonic of fundamental oscillation voltage through an additional impedance peak, thus giving rise to a class- $F_2$  operation. This oscillator specifically addresses the ultra-low phase noise design space while maintaining high power efficiency. Extensive experimental results are also presented at the end of this chapter.

Excited by a harmonically rich tank current, a typical oscillation voltage waveform is observed to have asymmetric rise and fall times. This results in an effective impulse sensitivity function (ISF) of a non-zero dc value, which facilitates the flicker (1/f) noise up-conversion into the oscillator's  $1/f^3$  phase noise. Chapter 5 elaborates a method to reduce a 1/f noise up-conversion in voltage-biased RF oscillators.

Chapter 6 introduces and analyzes in detail an oscillator with switching current sources to reduce supply voltage and power without sacrificing its phase noise and startup margins. This oscillator is specifically addressed IoT application constraints.

In Chapter 7 a method to broaden a tuning range of an LC-tank oscillator without sacrificing its area is presented. The extra tuning range is achieved by forcing a strongly coupled transformer-based tank into a common-mode resonance at a much higher frequency than in its main differential-mode oscillation. The oscillator employs separate active circuits to excite each mode but it shares the same tank, which largely dominates the core area but is on par with similar single-core designs.

Chapter 8 presents a design guide to estimate the time dependent dielectric beak down of any analog circuit with evaluating life time of class-F oscillators as an example.

## **List of Figures**

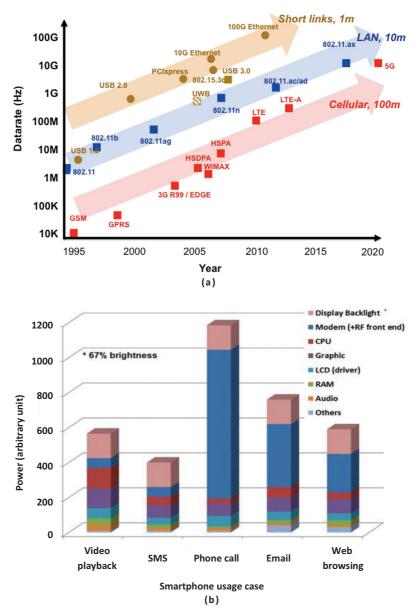

| Figure 1.1 | (a) Evolution of data rates for wireless LAN, cellular, and wireline short links over time; |    |

|------------|---------------------------------------------------------------------------------------------|----|

|            | (b) power usage in a smartphone                                                             | 2  |

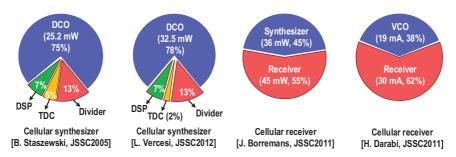

| Figure 1.2 | Contribution of RF oscillator to the power                                                  | 2  |

|            | consumption of cellular frequency synthesizers and                                          |    |

|            | receivers.                                                                                  | 3  |

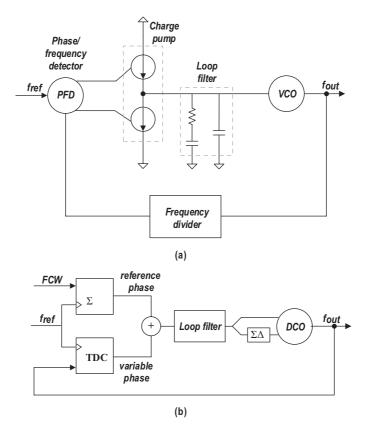

| Figure 1.3 | (a) Analog and; (b) digital phase locked loops                                              | 5  |

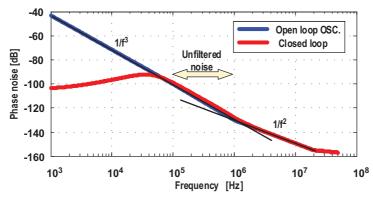

| Figure 1.4 | Oscillator's open loop and output frequency phase                                           |    |

|            | noise.                                                                                      | 6  |

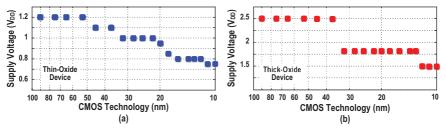

| Figure 1.5 | Nominal supply voltage versus CMOS technology                                               |    |

|            | node for (a) thin-oxide and (b) thick-oxide                                                 |    |

|            | devices                                                                                     | 7  |

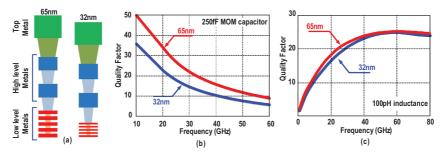

| Figure 1.6 | (a) Back-end-of-line (BEOL) metallization; quality                                          |    |

|            | factor of (b) a 250 fF capacitor, and (c) a 100 pH                                          |    |

|            | inductor in 65 nm and 32 nm CMOS                                                            |    |

|            | technologies.                                                                               | 8  |

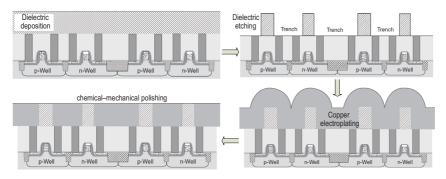

| Figure 1.7 | Damascene process steps                                                                     | 8  |

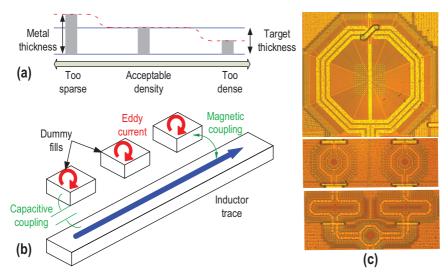

| Figure 1.8 | (a) Thickness variation by erosion in the CMP stage;                                        |    |

|            | (b) electromagnetic coupling between the wire and                                           |    |

|            | dummy fills; (c) inductor/transformer with lots of                                          |    |

|            | dummy metal fills.                                                                          | 9  |

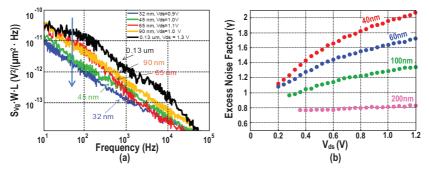

| Figure 1.9 | (a) Flicker noise scaling trend; (b) measured excess                                        |    |

|            | noise $(\gamma)$ factor versus drain-source voltage at                                      |    |

|            | 10 GHz and $V_{gs}$ = 1.0 V for different gate lengths                                      |    |

|            | of NMOS transistors in 40 nm LP technology                                                  | 10 |

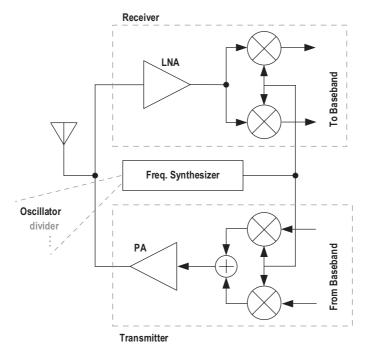

| Figure 2.1 | A generic RF transceiver                                                                    | 14 |

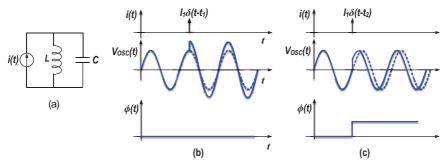

| Figure 2.2 | Phase response to an impulse current                                                        | 14 |

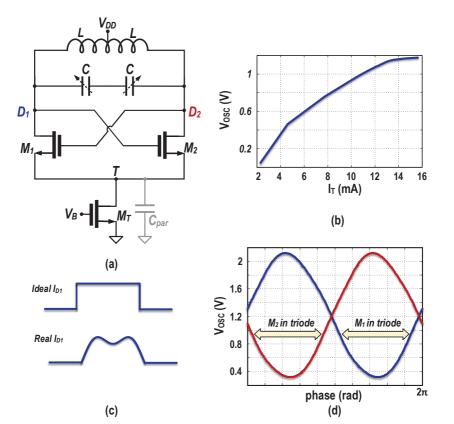

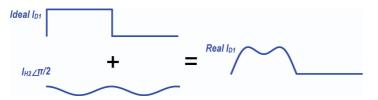

| Figure 2.3 | A class-B oscillator (a) schematic; (b) oscillation                                         |    |

|            | amplitude versus tail current; (c) ideal and real drain                                     |    |

|            | current waveforms; (d) oscillation voltage                                                  |    |

|            | waveforms.                                                                                  | 17 |

#### xii List of Figures

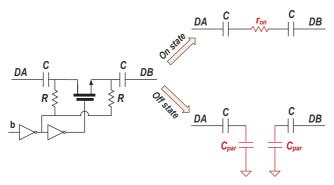

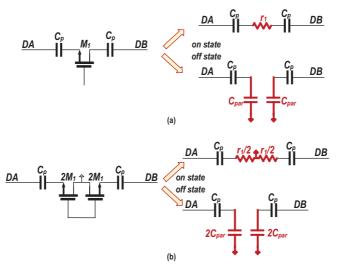

| Figure 2.4  | The switch capacitor tuning circuit in on and off states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

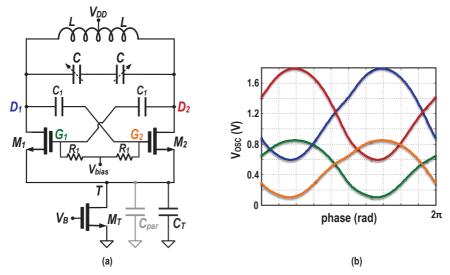

| Figure 2.5  | (a) A class-C oscillator schematic and (b) its voltage waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

| Figure 2.6  | (a) A class-C with dynamic generation of $V_{bias}$ ;<br>(b) a hybrid class-B/class-C oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

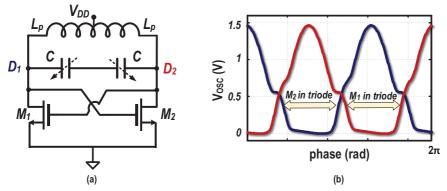

| Figure 2.7  | (a) A class-D oscillator schematic and (b) its voltage waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 |

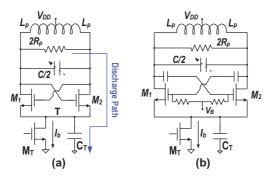

| Figure 3.1  | Oscillator schematic: (a) traditional class-B;<br>(b) class-C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28 |

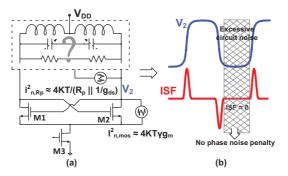

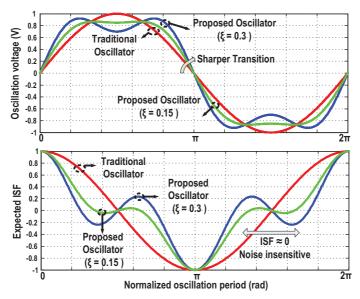

| Figure 3.2  | LC-tank oscillator: (a) noise sources; (b) targeted<br>oscillation voltage (top) and its expected<br>ISF (bottom).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

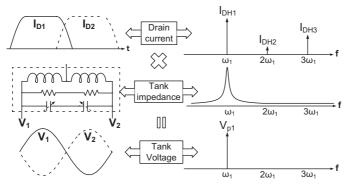

| Figure 3.3  | Traditional oscillator waveforms in time and frequency domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

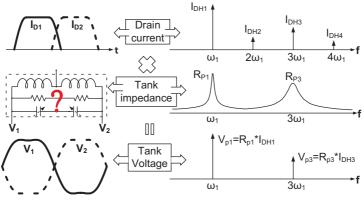

| Figure 3.4  | New oscillator's waveforms in time and frequency domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

| Figure 3.5  | The effect of adding third harmonic in the oscillation waveform (top) and its expected ISF (bottom).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32 |

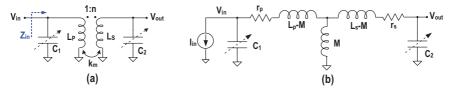

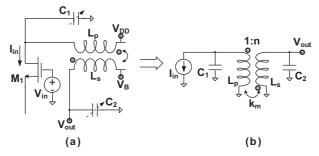

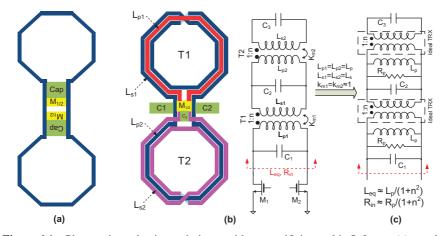

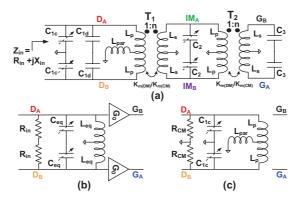

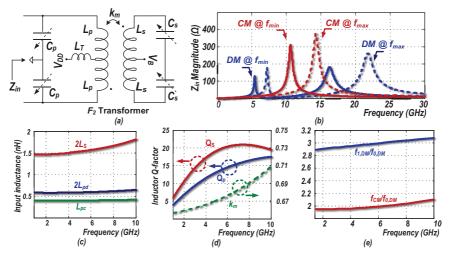

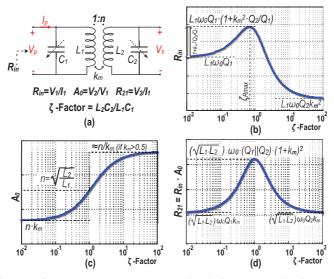

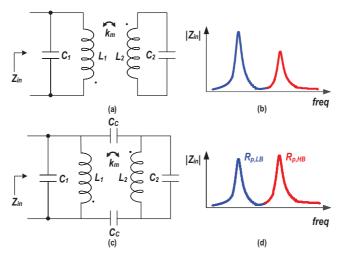

| Figure 3.6  | Transformer-based resonator (a) and its equivalent circuit (b).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32 |

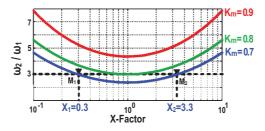

| Figure 3.7  | Ratio of the tank resonant frequencies versus $X$ -factor for different $k_m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34 |

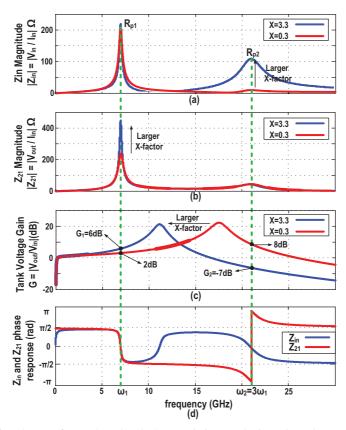

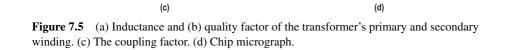

| Figure 3.8  | The transformer-based tank characteristics: (a) the input impedance, $Z_{in}$ magnitude; (b) the trans-impedance, $Z_{21}$ magnitude; (C) transformer's secondary to primary voltage gain; (d) the phase of $Z_{21}$ magnitude; (C) transformer's secondary to primary voltage gain; (d) the phase of $Z_{22}$ magnitude; (e) the phase of $Z_{22}$ magnitude; (f) the phase of $Z_{22}$ magnitude; (h) the phase of $Z_{22}$ mag | 25 |

| Figure 3.9  | $Z_{in}$ and $Z_{21}$ (momentum simulation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

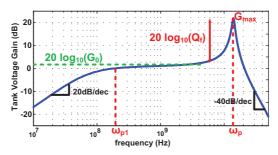

| Figure 3.10 | frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36 |

|             | more advantageous in this work.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |

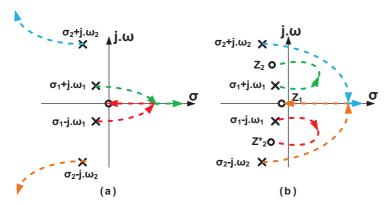

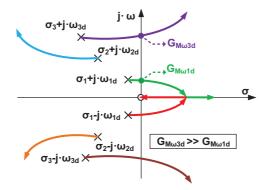

| Figure 3.11 | Root-locus plot of the transformer-based class- $F_3$                                                                              |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|----|

|             | oscillator: (a) transformer-coupled structure of                                                                                   |    |

|             | Figure 3.10(a); and (b) cross-coupled structure of                                                                                 |    |

|             | Figure 3.10(b)                                                                                                                     | 39 |

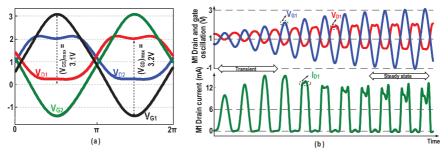

| Figure 3.12 | (a) Oscillation voltage waveforms and (b) transient                                                                                |    |

|             | response of the class- $F_3$ oscillator                                                                                            | 40 |

| Figure 3.13 | Open-loop circuit for unloaded Q-factor calculation                                                                                |    |

|             | (a); its equivalent circuit (b)                                                                                                    | 41 |

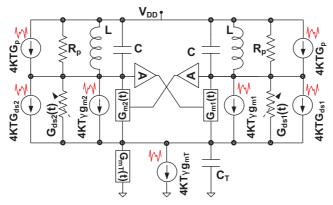

| Figure 3.14 | RF CMOS oscillator noise sources                                                                                                   | 44 |

| Figure 3.15 | Mechanisms of circuit noise to phase noise                                                                                         |    |

|             | conversion in different classes of RF CMOS                                                                                         |    |

|             | oscillator.                                                                                                                        | 46 |

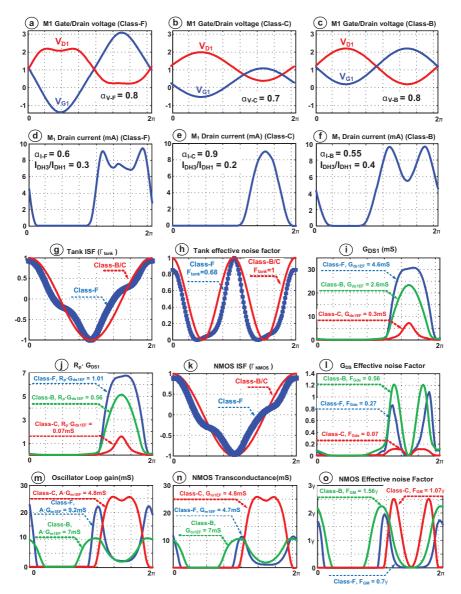

| Figure 3.16 | Sensitivity of class-F <sub>3</sub> oscillator to the position                                                                     |    |

|             | of the second resonant frequency: tank's input                                                                                     |    |

|             | impedance magnitude and phase (top); oscillation                                                                                   |    |

|             | waveform (bottom).                                                                                                                 | 49 |

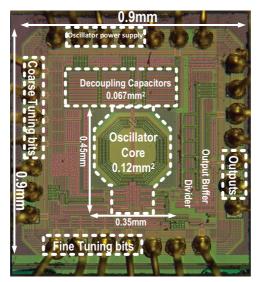

| Figure 3.17 | Die photograph of class- $F_3$ oscillator.                                                                                         | 51 |

| Figure 3.18 | Measured phase noise at 3.7 GHz and power                                                                                          |    |

|             | dissipation of 15 mW. Specifications (MS: mobile                                                                                   |    |

|             | station; BTS: basestation) are normalized to the                                                                                   |    |

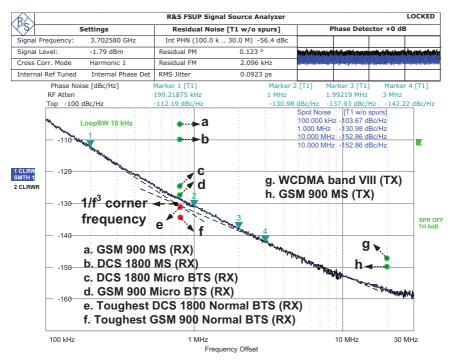

|             | carrier frequency.                                                                                                                 | 51 |

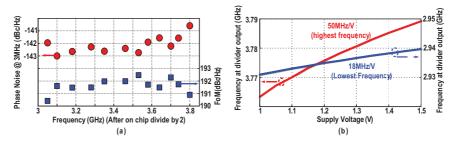

| Figure 3.19 | (a) Phase noise and figure of merit (FoM) at 3 MHz                                                                                 |    |

|             | offset versus carrier frequency and (b) frequency                                                                                  |    |

|             | pushing due to supply voltage variation                                                                                            | 52 |

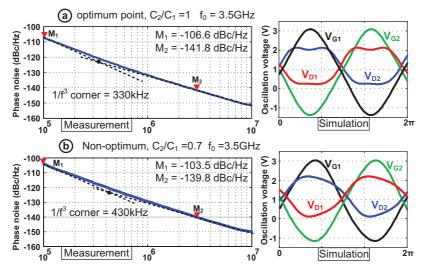

| Figure 3.20 | Measured phase noise at 3.5 GHz and simulated                                                                                      |    |

|             | oscillation waveforms: (a) optimum case;                                                                                           |    |

|             | (b) exaggerated non-optimum case                                                                                                   | 53 |

| Figure 4.1  | Phase noise reduction techniques without sacrificing                                                                               |    |

|             | tank's Q-factor: (a) coupled oscillators,                                                                                          |    |

|             | (b) connecting two step-up transformers back-to-                                                                                   |    |

|             | back, and (c) its equivalent circuit model                                                                                         | 62 |

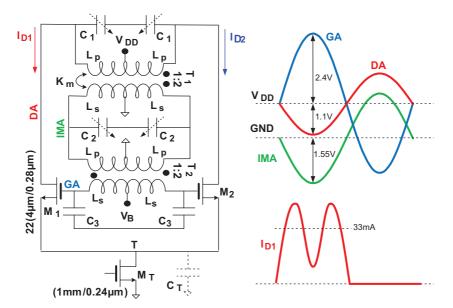

| Figure 4.2  | Preliminary oscillator schematic and its simulated                                                                                 |    |

|             | voltage and estimated current waveforms at $f_0 =$                                                                                 |    |

|             | $8 \text{ GHz}, \text{V}_{\text{DD}} = 1.2 \text{ V}, \text{I}_{\text{DC}} = 33 \text{ mA}, \text{L}_{\text{eq}} = 80 \text{ pH},$ |    |

|             | and $C_{eq} = 4.95 \text{ pF.} \dots \dots \dots \dots \dots$                                                                      | 63 |

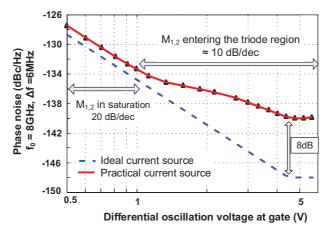

| Figure 4.3  | Simulated phase noise performance of the                                                                                           |    |

|             | preliminary oscillator of Figure 4.2 versus gate                                                                                   |    |

|             | differential oscillation voltage for the ideal and real                                                                            |    |

|             | current sources.                                                                                                                   | 63 |

#### xiv List of Figures

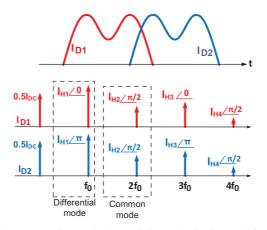

| Figure 4.4  | Drain current of $M_{1,2}$ devices of Figure 4.2 in time                             |    |

|-------------|--------------------------------------------------------------------------------------|----|

|             | and frequency domains                                                                | 64 |

| Figure 4.5  | New oscillator's waveforms in time and frequency                                     |    |

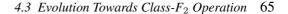

| -           | domains                                                                              | 65 |

| Figure 4.6  | Effect of adding second harmonic in the oscillation                                  |    |

| 0           | voltage waveform (top) and its expected ISF based                                    |    |

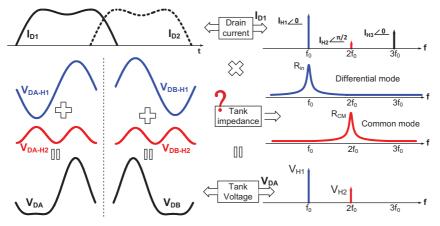

|             | on Equation (38) (bottom).                                                           | 66 |

| Figure 4.7  | Transformer behavior in (a) differential-mode and                                    |    |

| 0           | (b) common-mode excitations                                                          | 67 |

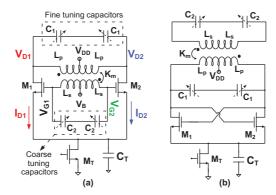

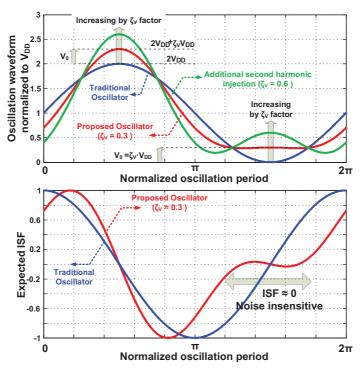

| Figure 4.8  | New transformer-based resonator: (a) schematic, (b)                                  |    |

| 0           | its simplified equivalent differential-mode circuit                                  |    |

|             | $(k_{m(DM)} \approx 1)$ , and (c) simplified tank schematic                          |    |

|             | for common-mode input signals ( $k_{m(CM)} \approx 0$ )                              | 67 |

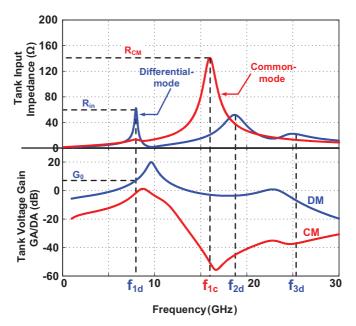

| Figure 4.9  | Simulated characteristics of the transformer-based                                   |    |

| 0           | tank of Figure 4.8: (top) magnitude of input                                         |    |

|             | impedance Z <sub>in</sub> ; (bottom) tank voltage gain between                       |    |

|             | gate and drain of core devices.                                                      | 69 |

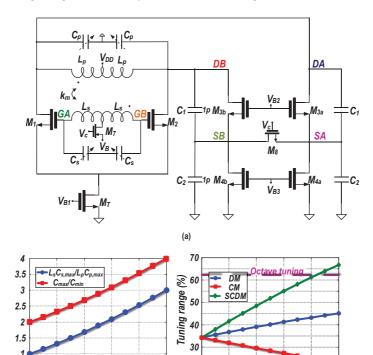

| Figure 4.10 | Transformer-based class- $F_2$ oscillator schematic.                                 | 69 |

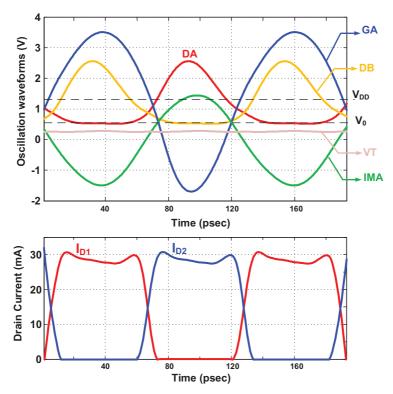

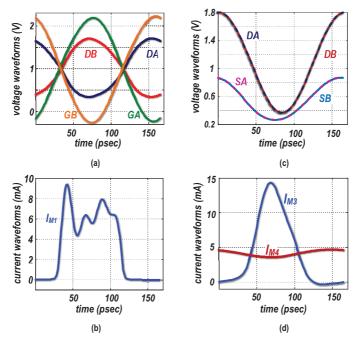

| Figure 4.11 | Simulated oscillation waveforms of the class- $F_2$                                  |    |

| 0           | oscillator at $V_{DD} = 1.2$ V and $I_{DC} = 29$ mA:                                 |    |

|             | (top) oscillation voltage of different circuit nodes                                 |    |

|             | and (bottom) core transistors drain current                                          | 70 |

| Figure 4.12 | Root-locus plot of the class- $F_2$ oscillator                                       | 71 |

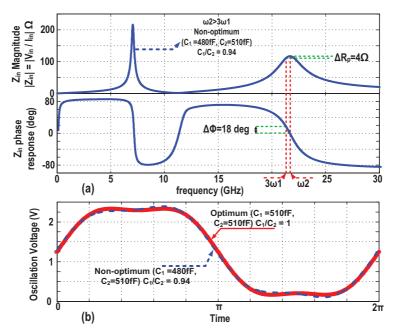

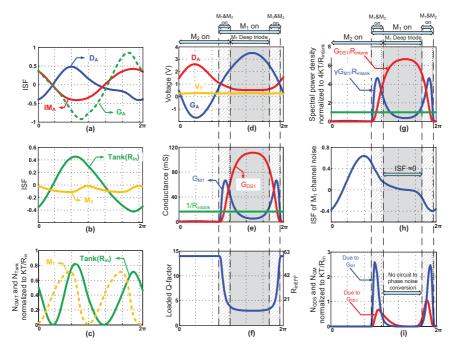

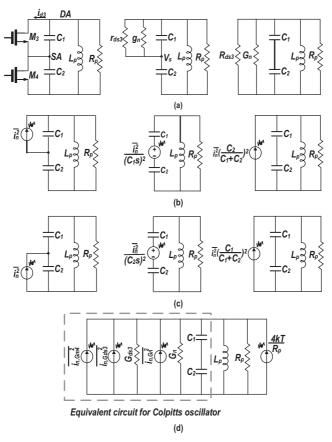

| Figure 4.13 | Mechanisms of circuit-to-phase-noise conversion                                      |    |

|             | across the oscillation period in the class- $F_2$                                    |    |

|             | oscillator: (a) simulated ISF of different tank nodes,                               |    |

|             | (b) equivalent ISF in the simplified oscillator                                      |    |

|             | schematic of Figure 4.14, (c) simulated effective                                    |    |

|             | power spectral density of the oscillator's noise                                     |    |

|             | sources normalized to $\mathrm{KT/R}_{\mathrm{in}}$ , (d) oscillation                |    |

|             | waveforms and operation region of $M_{1,2}$ ,                                        |    |

|             | (e) transconductance and channel conductance of                                      |    |

|             | M <sub>1</sub> , (f) loaded Q-factor and effective parallel input                    |    |

|             | resistance of the tank, (g) power spectral density                                   |    |

|             | of $M_1$ noise sources normalized to $4\mathrm{KT}/\mathrm{R}_{\mathrm{in}}\text{,}$ |    |

|             | (h) simulated ISF function of $M_1$ channel noise,                                   |    |

|             | and (i) simulated effective power spectral density of                                |    |

|             | different noise sources of M1 normalized to                                          |    |

|             | $\mathrm{KT/R_{in}}$                                                                 | 73 |

|             |                                                                                      |    |

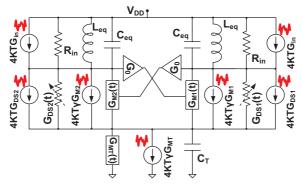

| Figure 4.14   | Simplified noise source model of the class- $F_2$ oscillator.           | 73 |

|---------------|-------------------------------------------------------------------------|----|

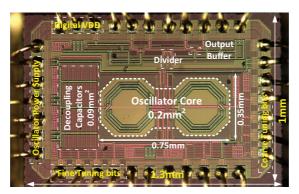

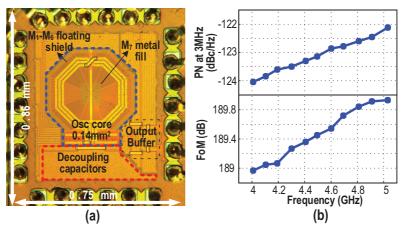

| Figure 4.15   | Die photograph of the class- $F_2$ oscillator                           | 78 |

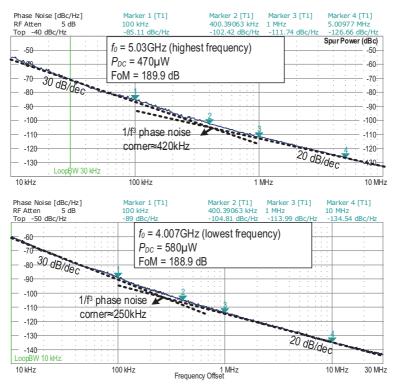

| Figure 4.16   | Measured (blue) and simulated (red) phase noise                         |    |

|               | plots at 4.35 GHz, $V_{\rm DD} = 1.3$ V and $P_{\rm DC} =$              |    |

|               | 41 mW. Specifications (MS: mobile station, BTS:                         |    |

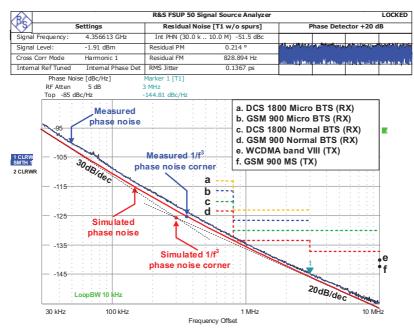

|               | basestation) are normalized to the carrier frequency.                   | 79 |

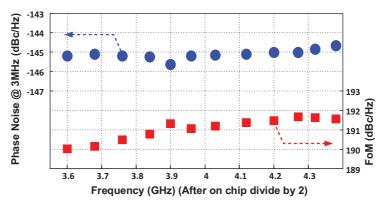

| Figure 4.17   | Measured phase noise and figure of merit (FoM) at                       | ., |

| inguite mit   | 3 MHz offset versus carrier frequency.                                  | 81 |

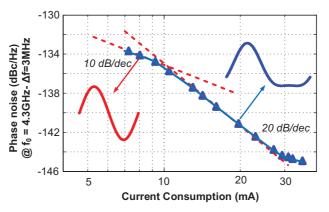

| Figure 4.18   | Measured phase noise at 3 MHz offset frequency                          | 01 |

| inguite mito  | from 4.3 GHz carrier versus the oscillator current                      |    |

|               | consumption.                                                            | 81 |

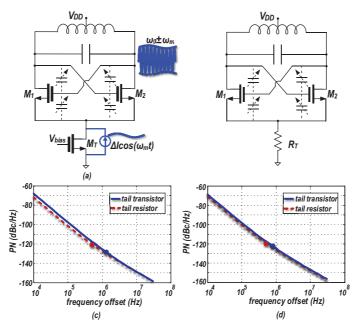

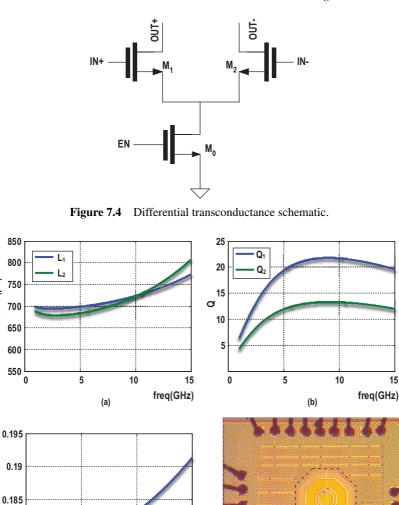

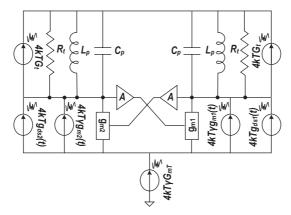

| Figure 5.1    | Class-B oscillator: (a) with tail transistor $M_T$ ; (b)                | 01 |

| i igui e e i  | with tail resistor $R_T$ ; and their PN when (c) $M_T$                  |    |

|               | is always in saturation; (d) $M_T$ enters partially into                |    |

|               | triode.                                                                 | 88 |

| Figure 5.2    | (a) Current harmonic paths; (b) drain current in time                   | 00 |

| i igui e e iz | and frequency domains; (c) frequency drift due to                       |    |

|               | Groszkowski effect.                                                     | 89 |

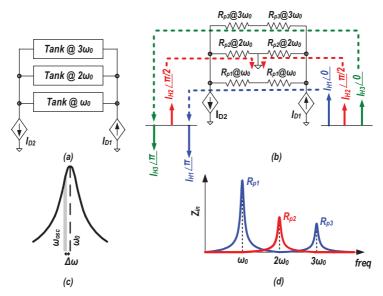

| Figure 5.3    | (a) Auxiliary resonances at higher harmonics; (b)                       | 07 |

|               | current harmonic paths; (c) frequency drift; (d)                        |    |

|               | input impedance of the tank.                                            | 92 |

| Figure 5.4    | Oscillator example: (a) schematic; (b) $V_{DS}$ , $V_{GS}$ ,            |    |

| 8             | and $g_m$ of $M_1$ transistor when oscillation voltage                  |    |

|               | contains only fundamental component; (c) its ISF,                       |    |

|               | NMF, and effective ISF.                                                 | 93 |

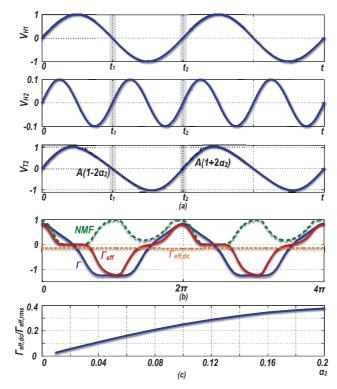

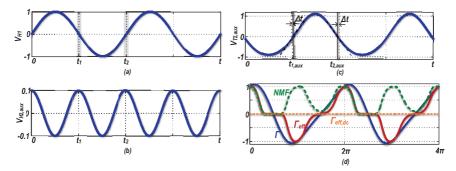

| Figure 5.5    | Conventional tank waveforms: (a) fundamental,                           |    |

| C             | $V_{H1}$ , second harmonic, $V_{H2}$ , voltage components,              |    |

|               | and oscillation waveform, $V_{T2}$ ; (b) its ISF, NMF,                  |    |

|               | and effective ISF; (c) $\Gamma_{eff,dc}/\Gamma_{eff,rms}$ for different |    |

|               | $\alpha_2$ values.                                                      | 95 |

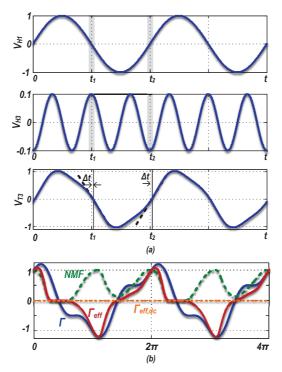

| Figure 5.6    | Conventional tank waveforms: (a) fundamental,                           |    |

|               | $V_{H1}$ , third harmonic, $V_{H3}$ , voltage component, and            |    |

|               | oscillation waveform, $V_{T3}$ ; (b) its ISF, NMF, and                  |    |

|               | effective ISF.                                                          | 96 |

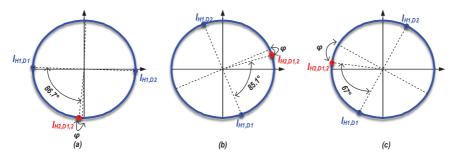

| Figure 5.7    | Ideal and real current waveforms                                        | 97 |

| Figure 5.8    | Tank's current fundamental and second-harmonic                          |    |

|               | phases in (a) class-D; (b) class- $F_3$ ; and (c) class-C               |    |

|               | topologies                                                              | 98 |

#### xvi List of Figures

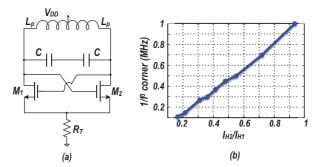

| Figure 5.9  | (a) Voltage-biased class-B oscillator schematics;                                       |     |

|-------------|-----------------------------------------------------------------------------------------|-----|

|             | (b) $1/f^3$ corner versus $I_{H2}/I_{Hn}$                                               | 99  |

| Figure 5.10 | Proposed tank waveforms: (a) fundamental voltage                                        |     |

|             | component, $V_{H1}$ ; (b) voltage second harmonic                                       |     |

|             | in the presence of auxiliary resonance, $V_{H2,aux}$ ;                                  |     |

|             | (c) oscillation waveform, $V_{T2,aux}$ ; (d) its ISF, NMF,                              |     |

|             | and effective ISF                                                                       | 100 |

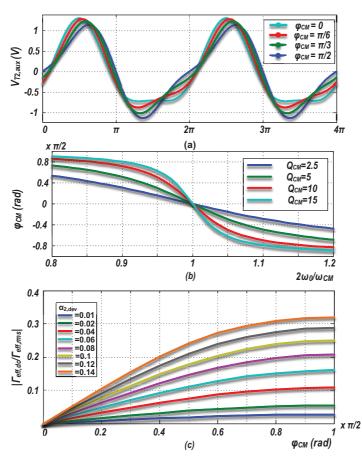

| Figure 5.11 | (a) $V_{T2,aux}$ for different $\phi_{CM}$ ; (b) $\phi_{CM}$ for                        |     |

|             | different $Q_{CM}$ when $\omega_{CM}$ deviates from $2\omega_0$ ;                       |     |

|             | (c) $\Gamma_{eff,dc}/\Gamma_{eff,rms}$ for different $\alpha_{2,aux}$ and $\phi_{CM}$ . | 102 |

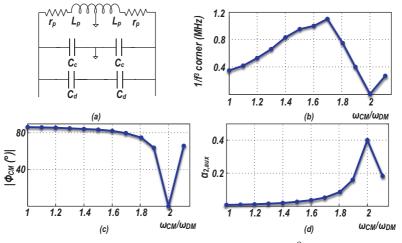

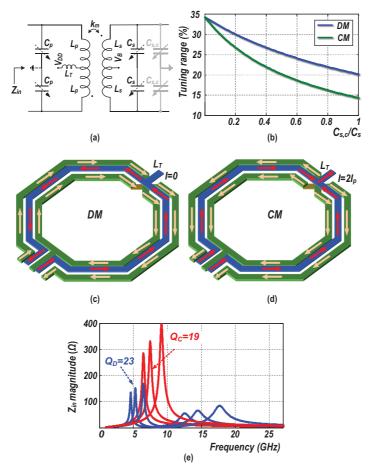

| Figure 5.12 | (a) A tank with DM and CM resonances; (b) $1/f^3$                                       |     |

|             | corner of the oscillator employing this tank;                                           |     |

|             | (c) $\phi_{CM}$ ; and (d) $\alpha_{2,aux}$ of the tank versus                           |     |

|             | $\omega_{CM}/\omega_{DM}$                                                               | 103 |

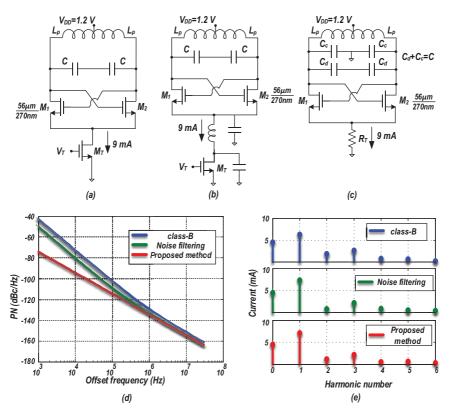

| Figure 5.13 | (d) PN and (e) current harmonic components of                                           |     |

|             | a class-B oscillator (a), and similar counterparts                                      |     |

|             | with noise filtering technique (b) and the proposed                                     |     |

|             | method applied (c)                                                                      | 105 |

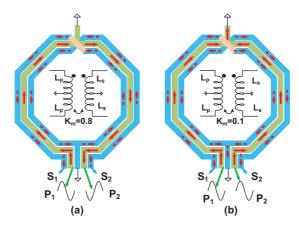

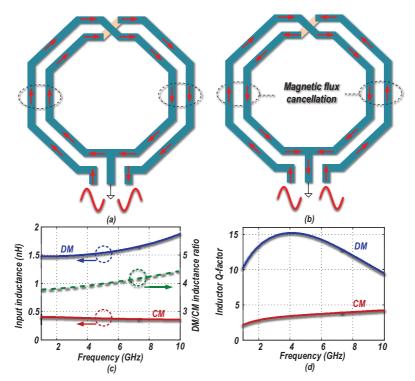

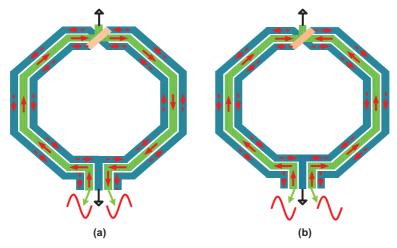

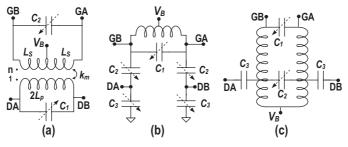

| Figure 5.14 | A 2-turn "F <sub>2</sub> " inductor in (a) DM excitation; (b) CM                        |     |

|             | excitation; (c) $F_2$ DM and CM inductances and their                                   |     |

|             | ratio; (d) $Q_{DM}$ and $Q_{CM}$                                                        | 106 |

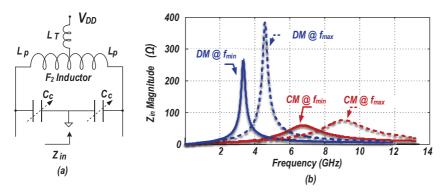

| Figure 5.15 | (a) Inductor-based $F_2$ tank and (b) its input                                         |     |

|             | impedance                                                                               | 107 |

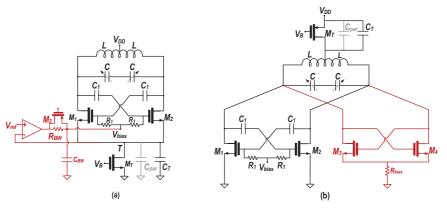

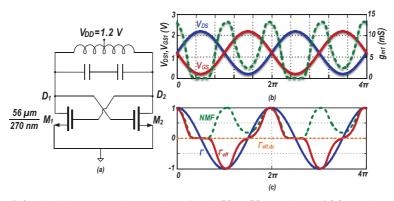

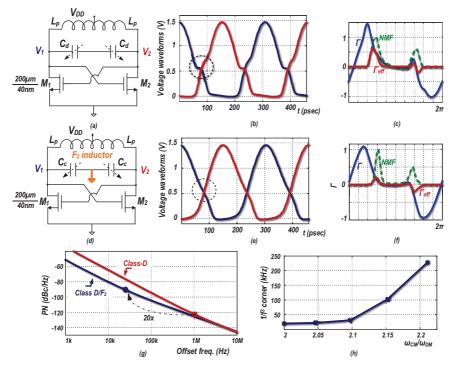

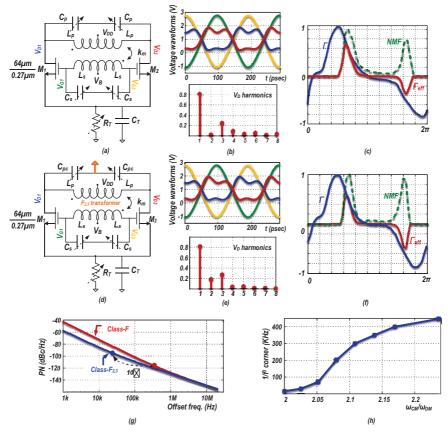

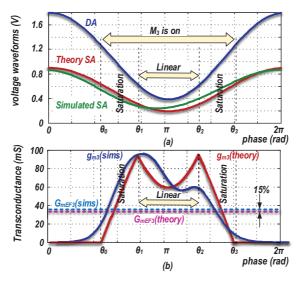

| Figure 5.16 | Class-D oscillator: (a) schematic; its (b) waveforms;                                   |     |

|             | and (c) gm-transistor ISF, NMF, and effective                                           |     |

|             | ISF. Class-D/ $F_2$ oscillator: (d) schematic; its (e)                                  |     |

|             | waveforms; and (f) gm-transistor ISF, NMF, and                                          |     |

|             | effective ISF; (g) their PN performance; and (h) $1/f^3$                                |     |

|             | corner sensitivity to $\omega_{CM}/\omega_{DM}$                                         | 108 |

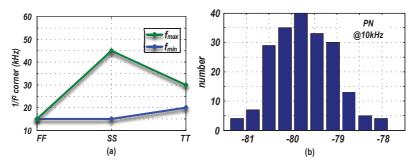

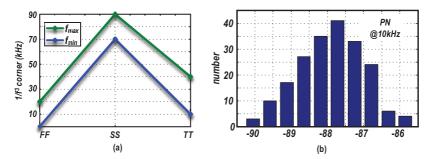

| Figure 5.17 | Class-D/F <sub>2</sub> oscillator: $1/f^3$ corner over process                          |     |

|             | variation and (b) histogram of PN at 10-kHz offset                                      |     |

|             | frequency                                                                               | 110 |

| Figure 5.18 | 1:2 transformer when the primary is excited with                                        |     |

|             | (a) DM and (b) CM currents                                                              | 110 |

| Figure 5.19 | (a) Transformer-based $F_2$ tank; (b) its input                                         |     |

|             | impedance; (c) DM and CM primary and secondary                                          |     |

|             | inductance; (d) primary and secondary inductance                                        |     |

|             | quality factor and coupling factor; (e) DM and CM                                       |     |

|             | resonant frequencies over TR                                                            | 111 |

| Figure 5.20               | Class- $F_3$ oscillator: (a) schematic; (b) its waveforms;<br>and (c) gm-transistor ISF, NMF, and effective |     |

|---------------------------|-------------------------------------------------------------------------------------------------------------|-----|

|                           | ISF. Class- $F_{2,3}$ oscillator: (d) schematic; (e) its                                                    |     |

|                           | waveforms; and (f) gm-transistor ISF, NMF, and                                                              |     |

|                           | effective ISF; (g) their PN performance; and (h) $1/f^3$                                                    |     |

|                           | corner sensitivity to $\omega_{CM}/\omega_{DM}$                                                             | 112 |

| Figure 5.21               | Class- $F_{2,3}$ oscillator: $1/f^3$ corner over process variation and (b) histogram of PN at 10-kHz offset |     |

|                           | frequency                                                                                                   | 113 |

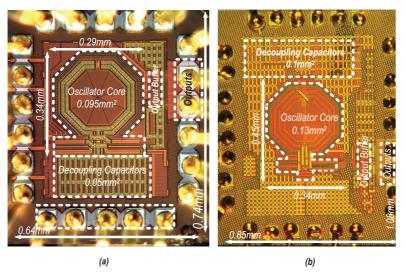

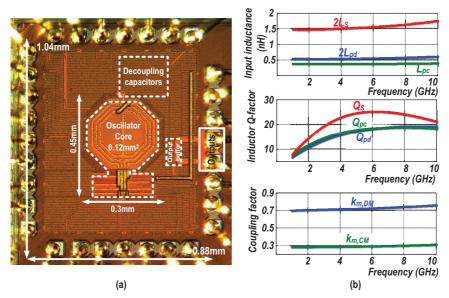

| Figure 5.22               | Chip micrographs: (a) class-D/F <sub>2</sub> oscillator;                                                    |     |

|                           | (b) class- $F_{2,3}$ oscillator                                                                             | 115 |

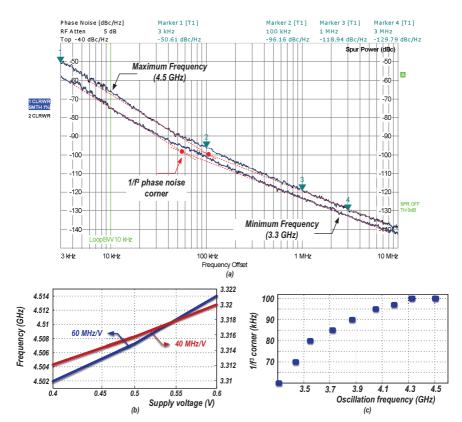

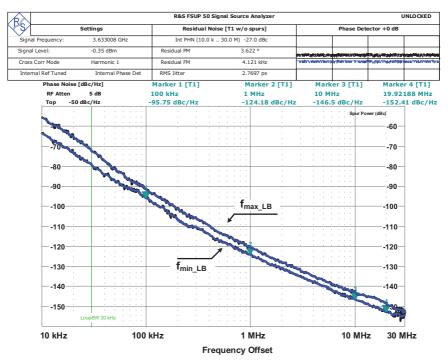

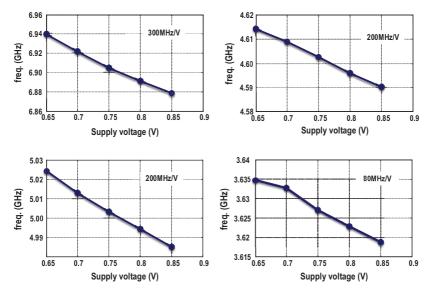

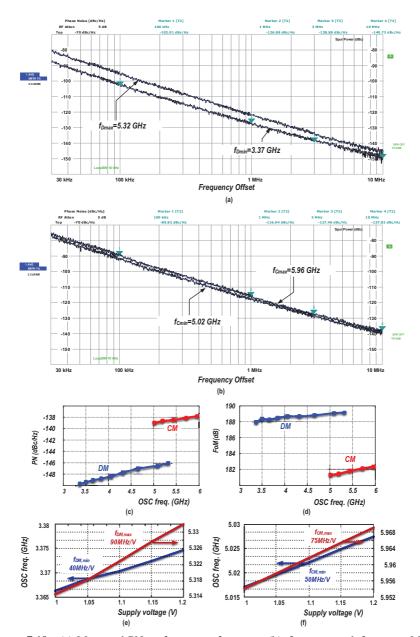

| Figure 5.23               | Class-D/F <sub>2</sub> oscillator: measured (a) PN at $f_{\rm max}$ and                                     |     |

|                           | $f_{\min}$ ; (b) frequency pushing due to supply voltage                                                    |     |

|                           | variation; and (c) $1/f^3$ corner over tuning range                                                         | 116 |

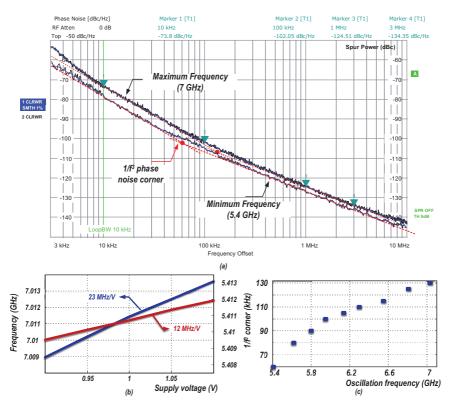

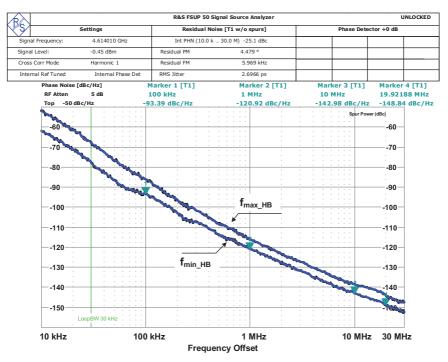

| Figure 5.24               | Class- $F_{2,3}$ oscillator: measured (a) PN at $f_{\text{max}}$ and                                        |     |

|                           | $f_{\min}$ ; (b) frequency pushing due to supply voltage                                                    |     |

| <b>D•</b> (1)             | variation; and (c) $1/f^3$ corner over tuning range                                                         | 117 |

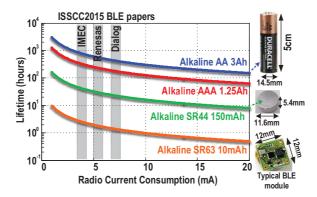

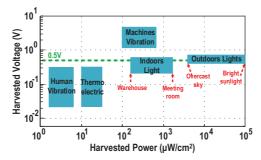

| Figure 6.1                | BLE system lifetime versus radio current                                                                    | 104 |

| <b>E</b> <sup>1</sup> ( ) | consumption for various battery types                                                                       | 124 |

| Figure 6.2                | Delivered voltage and power density for various                                                             | 104 |

| Figure 63                 | harvester types                                                                                             | 124 |

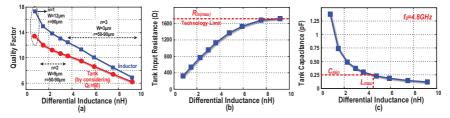

| Figure 6.3                | 28-nm LP CMOS across inductor value:                                                                        |     |

|                           | (a) inductor and tank Q-factor; (b) equivalent                                                              |     |

|                           | differential input resistance of the tank; and                                                              |     |

|                           | (c) required tank capacitance at 4.8-GHz resonance.                                                         |     |

|                           | Note that at this point the inductors are without                                                           |     |

|                           | dummy metal fills.                                                                                          | 127 |

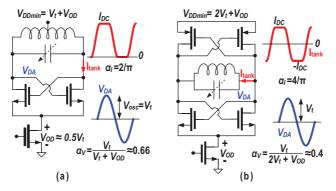

| Figure 6.4                | $V_{DD,min}$ , $\alpha_I$ and $\alpha_V$ parameters for: (a) cross-                                         |     |

| 8                         | coupled NMOS and (b) complementary push–pull                                                                |     |

|                           | oscillators.                                                                                                | 128 |

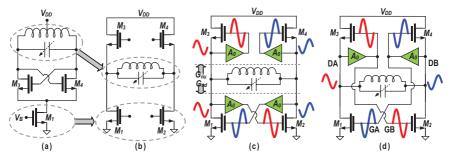

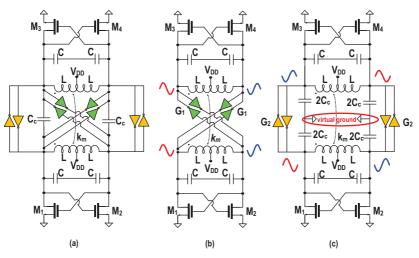

| Figure 6.5                | Evolution towards the switching current-source                                                              |     |

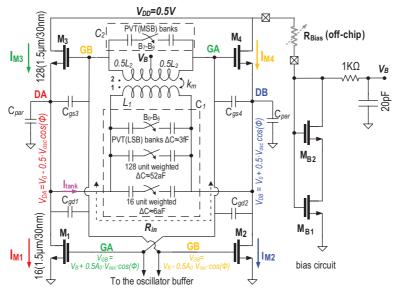

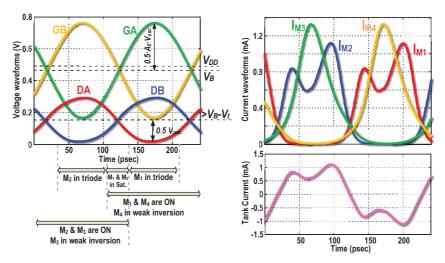

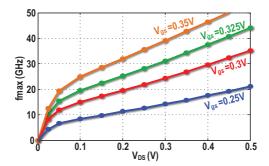

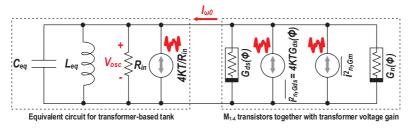

| C                         | oscillator.                                                                                                 | 130 |