## Advanced Techniques for Diagnostics and Control Applied to Particle Accelerators

Doctoral thesis submitted for the degree of Doctor from the UPV/EHU by

#### Inari Badillo Fernández

Directed by

Dr. Josu Jugo García

Leioa, 2015

Departamento de Electricidad y Electrónica Facultad de Ciencia y Tecnología Elektrika eta Elektronika Saila Zientzia eta Teknologia Fakultatea

© 2015, Inari Badillo Fernández.

## Agradecimientos

Ahora que la escritura de esta tesis llega a su fin, me gustaría agradecer a un montón de personas todo su apoyo.

Unos más en el aspecto "profesional", otros quizá más por otras cuestiones menos técnicas. Tengo muy claro que sin ellos esto no habría salido adelante. Se que en cuanto recoja las tesis de la imprenta me acordare de gente a la que se me ha olvidado mencionar aquí, así que les pido disculpas de antemano.

Para empezar, me gustaría agradecer a Josu Jugo el haber dirigido esta tesis. Por haberme dado la oportunidad de empezar en la aventura de la investigación, por su ayuda constante y por ser el principal culpable de que realmente me haya gustado hacer este trabajo. Estoy convencido que allá por el 2009, al terminar la carrera, fui a hablar con el profesor correcto.

Tampoco me quiero olvidar del resto de miembros de los grupos de investigación involucrados en esta tesis, como Victor Etxebarria, sin cuyo trabajo nada de esto habría existido. Por supuesto Joaquin Portilla y Juan Mari Collantes, que además de ayudar con esa materia arcana que son las RF, siempre me han dado soporte con la financiación de los contratos (múltiples y alguno más) que he tenido. Mención especial a Jorge Feuchtwanger por su ayuda en tantas cosas... creo que no he encontrado (ni existe) ningún problema ante el que Jorge no haya aparecido con la solución.

A los que fueron mis compañeros de laboratorio (y jefe en la descalabrada etapa ESS) Mikel Egiraun e Iñigo Arredondo, por enseñarme y ayudarme tanto especialmente con LabVIEW y EPICS. A Carlos SanVicente, por lo compartido en este laboratorio de automática Harry Nyquist.

Agradecimiento especial a toda la becariada del departamento de Electricidad y Electrónica, por los buenos momentos vividos en los pasillos y en el campus. Muy especialmente a Mireia, por todos estos años de cafeterías.

A la familia; aita, ama, Peio y amamas, por su apoyo de diario y ánimos continuos, a pesar de la mirada perdida que se les queda cuando les cuento de que trata el trabajo. ¡Un beso muy grande!

Para finalizar, a la persona que más le debo en lo personal, a Helia por estar ahí cada día, cada momento. Por haber hecho este tiempo más llevadero a base

de risa y compañía, bu. ¡Muchas gracias a todos!

Leioa, Octubre 2015

## Laburpena

Tesi honek jorratzen du partikula-azeleragailuen diagnostiko eta kontrol tresnei zuzenduriko teknika eta teknologia aurreratuen gaia. Aipaturiko tresnentzako bi aplikazioen inguruan zentraturik dago nagusiki: sorta-posizioaren monitore (BPM, Beam Postion Monitor ingelesez) bat alde batetik, eta maila baxuko RF (LLRF, Low Level-RF ingelesez) izeneko kontrol sistema bat bestetik.

Partikula-azeleragailuak ezinbesteko tresnak dira zientzia ulertzeko eta anbizio handiko erronka zientifikoei aurre egiteko. Hala ere, mota honetako makinen erabilera ez da bakarrik proiektu zientifiko handien esparrura mugatzen. Izan ere, azeleragailu gehienak aplikazio mediko eta industrialetara zuzendurik daude.

Makina hauen konplexutasun handia dela eta, erronka teknologiko oso handia dira, eta beraz, oso bizia da haien inguruko tresneria eta teknologia berrien ikerketa eta garapena.

Diagnostikoak eta RF kontrola, edozein partikula-azeleragailuren funtsezko atalak dira. Diagnostikoak ezinbestekoak dira makinaren doiketan eta funtzionamendu normalean. Makinaren osagai eta prozesu askoren inguruko informazio inportantea eskaintzen dute. Neurtu nahi den aldagaiaren edo azeleragailu motaren arabera, hainbat fenomeno fisikotan oinarriturik egon daitezke. Diagnostiko tresna askok, prezisio altuko neurketak burutu behar dituzte informazio erabilgarria eskaini ahal izateko.

Beste alde batetik, RF kontrol sistemak nahitaezkoak dira partikulen azelerazio prozesuan. Sistema hauen diseinu eta garapenean, ezinbestekoa suertatzen da kontrol automatikoaren eta RF-aren jakintza arloen elkarlana, kontrolatu beharreko aldagaiak abiadura altuko seinaleak baitira, ehunka MHz-ren ordenakoak. Azelerazio egokia emateko, partikulak garraio-uhinarekin sinkronizatu behar dira. Horrek eskatzen du seinalearen anplitude eta fasearen kontrol azkar eta zehatza.

Honela, tesi honen motibazioa izan da partikula-azeleragailuentzako diagnostiko eta kontroleko tresna flexible, modular eta berkonfiguragarri berrien garapena. Horretarako, soluzio digitaletan oinarritzea erabaki da. Horrek, diseinuan aldaketa handiak burutzea ahalbidetzen du, esaterako, funtzionalita-

teak gehitu edo aldatu, programaren kodea baino ez aldatuz. Ezaugarri hau oso abantaila handia da prototipazioari begira, garapen denbora murriztu eta errekerimendu berriei aurre egitea ahalbidetzen baitu.

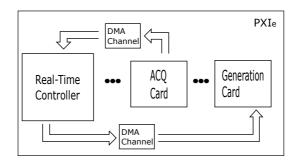

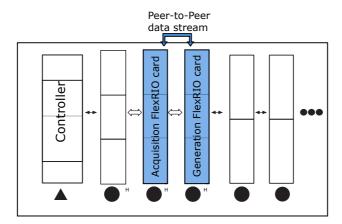

Hau guztia kontuan hartuta, National Instruments-eko PXIe plataforma aukeratu da proposaturiko aplikazio berrien garapenaren arkitektura nagusi bezala. PXIe-k, mota askotako moduluak eskaintzen ditu. Esaterako, data eskuraketa, data sorrera, FPGA teknologia, timing-a, etab. Arkitektura honen beste abantaila handi bat da sistema osoa ingurugiro berdinpean integratzeko aukera, LabVIEW bitartez operatua. Ezaugarri honek errazten du hardware gailu anitzen integrazioa, driver-en garapena, puntuz-puntuko komunikazioa edota DMA bitartezko transferentziak bezalako prozesuen konplexutasuna gutxituz. Aipatzekoa da ere, LabVIEW-ren erabilpenak ahalbidetu duela FPGA-n oinarrituriko txartelak programatzea ahalbidetu duela maila-baxuko VHD kodea erabili barik, modu honetan garapena erraztuz denbora eta esfortzuaren ikuspegitik.

Proposaturiko ideiarekin jarraituz, gailu analogikoak ekiditea izan da lan honen helburuetako bat, ahal den heinean. Hau erronka bat da, RF-ko seinaleak erabiltzen baitira, haien frekuentzia harmarka edo ehunka MHz-takoa izanik. Garaturiko aplikazioetan, RF seinaleak zuzenean lagintzen dira, seinalea eta ADC-en artean inolako tarteko etaparik gabe.

Ohiko laginketa teknikak erabiltzea oso laginketa abiadura azkarren beharra suposatzen du lan arlo honetan, ekipamendu garestiaren erabilpena dakarrena. Hain abiadura azkarrak ekiditeko asmoz, eta ondorioz, soluzio merkeagoak eraiki ahal izateko, azpilaginketa (subsampling ingelesez) izeneko laginketa teknika aurreratu bat aztertu eta inplementatu da. Teknika hau aliasing deituriko fenomenoaz baliatzen da frekuentzia baxuetan kokaturiko informaziotik seinaleak berreraikitzeko, modu honetan abiadura gutxiagoko ADC-ak erabiltzea ahalbidetuz. Teknika honen erabilpena, garaturiko diagnostiko eta kontrol tresnetako oso parte garrantzitsua da.

Modu honetan, tesi honen kontribuzio aipagarrienak dira BPM baten eta LLRF kontrol sistema baten garapena, biak era flexible eta berkonfiguragarrian eratuta eta hardware digitalean oinarrituta. Aurkeztutako soluzioak, diseinatuak izan dira laborategi-prototipaziorako lagungarriak diren tresnak eratzeko helburuarekin, aldi berean instalazio erreal batean modu errazean integragarriak izanik. Lortutako aplikazioek bete egiten dute helburu hau, modularitate handia eta prototipazio azkarra bezalako ezaugarri baliotsuak edukirik. Diseinaturiko sistemen balidazio esperimentala burutzeko, laborategi-muntaiak eraiki dira, modu honetan aipaturiko tresnak laborategian frogatu ahal izateko. Haien

bitartez, hainbat esperimentu burutu dira, emaitza egokiak lortu direlarik.

Horrez gain, tesi honetan aurkezturiko beste ikerketa lerro batek jorratzen ditu aipaturiko tresnek eskaintzen dituzten datuak EPICS-en integratzeko soluzioak, hau izanik partikula-azeleragailu askotan erabilitako kontrol teknologia garrantzitsuenetarikoa.

### Resumen

Esta tesis versa en torno a tecnologías y técnicas novedosas orientadas al diagnóstico y control para aceleradores de partículas. Se centra principalmente en el desarrollo de dos aplicaciones para dicho propósito: un monitor de posición de haz (beam position monitor o BPM en inglés) por un lado, y un control de RF denominado sistema de RF de bajo nivel (low-level RF o LLRF en inglés) por el otro.

Los aceleradores constituyen herramientas fundamentales para el estudio de la ciencia y para ayudar a afrontar algunos de los retos científicos más ambiciosos. Aún así, el uso de este tipo de máquinas no se limita a grandes proyectos científicos. De hecho, la gran mayoría de los aceleradores están orientados a aplicaciones médicas e industriales.

Debido a la gran complejidad de estas máquinas, representan un gran reto tecnológico, y por lo tanto, la investigación y el desarrollo de nuevas tecnologías en este área es muy dinámico.

Los diagnósticos y el control RF son aspectos esenciales en cualquier acelerador de partículas. Los diagnósticos son clave en el ajuste y la operación normal de la máquina. Proporcionan información relevante relacionada con numerosos procesos y componentes de la máquina, y pueden estar basados en diferentes fenómenos físicos dependiendo en la variable que se desea medir o el tipo de acelerador. Muchas de estas herramientas de diagnóstico necesitan efectuar medidas de gran precisión para poder generar información útil.

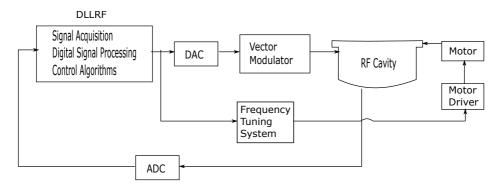

Por otro lado, los sistemas de control RF son vitales para el proceso de aceleración de las partículas. En el diseño y desarrollo de estos sistemas, la colaboración entre las áreas de conocimiento del control automático y las RF es necesaria, ya que las variables que se requiere controlar son señales de alta velocidad, habitualmente del orden de centenas de MHz. Para una aceleración correcta, las partículas deben sincronizarse con la onda viajera, lo que requiere un control rápido y preciso de la amplitud y la fase de la señal.

Así, la motivación de esta tesis ha sido el desarrollo de nuevas herramientas flexibles, modulares y reconfigurables para el diagnostico y control para aceleradores de partículas. Para este propósito, se ha tomado la decisión de basarlas

en soluciones digitales. Esto permite introducir cambios sustanciales en el diseño, así como añadir o cambiar funcionalidades simplemente modificando el código del programa. Esta característica es una gran ventaja a la hora de prototipar, ya que reduce el tiempo de desarrollo y permite una rápida adaptación a nuevos requerimientos.

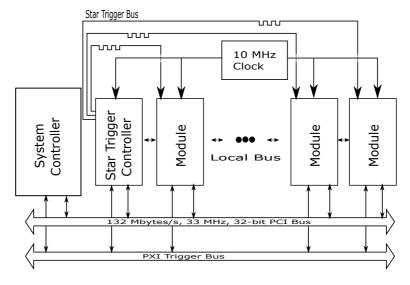

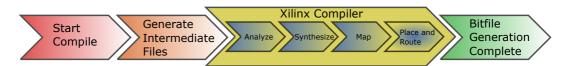

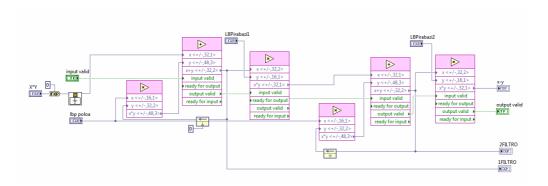

Considerando esto, se ha escogido la plataforma PXIe de National Instruments como la arquitectura principal para el desarrollo de las aplicaciones descritas. PXIe proporciona una gran variedad de módulos de muy diversa índole, como adquisición de señal, generación de señal, tecnología FPGA, temporización, etc. Otra gran ventaja de trabajar con esta arquitectura es que todo el sistema puede ser integrado bajo un entorno común operado en LabVIEW. Esto facilita la tarea de integrar una gran cantidad de dispositivos hardware, reduciendo el esfuerzo empleado para tareas complejas como el desarrollo de drivers, el uso de comunicaciones punto-a-puto o transferencias por DMA entre otras. También cabe destacar que el uso de LabVIEW ha permitido programar tarjetas basadas en FPGA en lenguaje estándar de LabVIEW, evitando el uso de VHD a bajo nivel, lo que ha facilitado el desarrollo en términos de esfuerzo y tiempo.

Siguiendo con la idea propuesta, uno de los objetivos de este trabajo ha sido evitar en lo posible el uso de componentes analógicos en el diseño de la herramientas propuestas. Esto supone un reto debido a que se emplean señales de RF, cuya frecuencia se encuentra en el rango de las decenas o centenas de MHz. En las aplicaciones desarrolladas, las señales RF son muestreadas directamente, evitando cualquier etapa intermedia entre la señal y los ADCs.

El uso de técnicas convencionales de muestreo conlleva la necesidad de velocidades de muestreo muy altas en el presente área, lo que se traduce en el empleo de equipamiento costoso. Con el objetivo de evitar tan altas velocidades de muestreo y por lo tanto construir soluciones más económicas, se ha estudiado e implementado una técnica de muestreo avanzada conocida como submuestreo (subsampling en inglés). Esta técnica hace uso del fenómeno denominado aliasing para reconstruir señales desde la información alojada en frecuencias bajas, abriendo la puerta al uso de ADCs de menor velocidad. La aplicación de esta técnica juega un papel central en las soluciones de diagnostico y control desarrolladas.

De esta manera, las principales contribuciones de esta tesis son el desarrollo de un BPM y un sistema de control LLRF altamente flexibles y reconfigurables, estando ambos basados en hardware digital. Las soluciones presentadas han sido diseñadas para crear herramientas que faciliten las labores de prototipado en laboratorio, aún siendo fácilmente integrables en una instalación real. Las

aplicaciones obtenidas cumplen este objetivo, mostrando características especialmente valiosas como una rápida etapa de prototipado y alta modularidad. Para la validación experimental de los sistemas diseñados, se han desarrollado completos bancos de pruebas, permitiendo de esta manera el testeo de las mencionadas soluciones en el laboratorio. Haciendo uso de ellos, las soluciones desarrolladas han sido testeadas en diversos experimentos, obteniendo resultados satisfactorios.

Adicionalmente, otra linea de investigación presentada en esta tesis se centra en la integración de los datos proporcionados por las mencionadas herramientas en redes EPICS, una de las principales tecnologías de control empleadas en muchos aceleradores de partículas.

Hor doa...

# Contents

| Intro                                                                    | oduction                                                                       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.1.                                                                     | Context of the Thesis                                                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 1.2.                                                                     | Objectives of the Thesis                                                       | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 1.3.                                                                     | Structure of the Thesis                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Diag                                                                     | gnostics and RF Control in Particle Accelerators                               | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2.1.                                                                     | Introduction                                                                   | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2.2.                                                                     | Diagnostics and RF control                                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2.3.                                                                     | Particle accelerator beam diagnostics                                          | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          | 2.3.1. Beam Position Monitoring                                                | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2.4.                                                                     | Low-Level RF control systems                                                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          |                                                                                | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2.5.                                                                     |                                                                                | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 2.6.                                                                     | Bibliography                                                                   | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Digi                                                                     | tal Solution Selected and Involved Technologies & Sampling                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Digital Solution Selected and Involved Technologies & Sampling Technique |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 3.1.                                                                     | Introduction                                                                   | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3.2.                                                                     | Digital Technology Selected                                                    | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3.3.                                                                     | Subsampling                                                                    | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          |                                                                                | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          | 3.3.2. Sampling process                                                        | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          | 3.3.3. Sampling Bandpass Signals                                               | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          |                                                                                | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          | _                                                                              | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3.4.                                                                     |                                                                                | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3.5.                                                                     |                                                                                | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                          | 1.1. 1.2. 1.3.  Diag 2.1. 2.2. 2.3.  2.4.  2.5. 2.6.  Digi Tecl 3.1. 3.2. 3.3. | 1.2. Objectives of the Thesis 1.3. Structure of the Thesis 1.3. Structure of the Thesis  Diagnostics and RF Control in Particle Accelerators 2.1. Introduction 2.2. Diagnostics and RF control 2.3. Particle accelerator beam diagnostics 2.3.1. Beam Position Monitoring 2.4. Low-Level RF control systems 2.4.1. Digital Low-Level RFs (DLLRFs) 2.5. Summary and conclusions 2.6. Bibliography  Digital Solution Selected and Involved Technologies & Sampling Technique 3.1. Introduction 3.2. Digital Technology Selected 3.3. Subsampling 3.3.1. Aliasing 3.3.2. Sampling process 3.3.3. Sampling Bandpass Signals 3.3.4. Spectral inversion 3.3.5. Advantages of Subsampling 3.4. Conclusions |  |

Contents

| 4. | Design and testing of a compact BPM diagnostic for particle accelerators based on PXIe |                                                                     |  |

|----|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

|    | 4.1.                                                                                   | Elerators based on PXIe 95 Introduction                             |  |

|    |                                                                                        | 4.1.1. Area of the project work                                     |  |

|    | 4.2.                                                                                   | Proposed solution                                                   |  |

|    | 4.3.                                                                                   | Developed BPM                                                       |  |

|    | 1.0.                                                                                   | 4.3.1. Description of the technology used 100                       |  |

|    |                                                                                        | 4.3.2. Subsampling technique: implementation details 102            |  |

|    |                                                                                        | 4.3.3. BPM diagnostic tool designed 102                             |  |

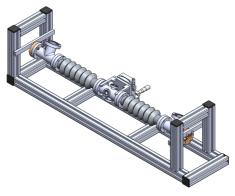

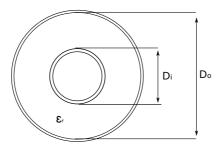

|    | 4.4.                                                                                   | Test bench description                                              |  |

|    | 4.5.                                                                                   | Experimental results                                                |  |

|    | 1.0.                                                                                   | 4.5.1. Input power range testing                                    |  |

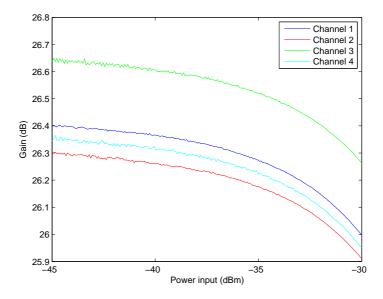

|    |                                                                                        | 4.5.2. Gain calibration and correction                              |  |

|    |                                                                                        | 4.5.3. Sensitivity coefficient and offset calculation               |  |

|    |                                                                                        | 4.5.4. Accuracy in the position measurement                         |  |

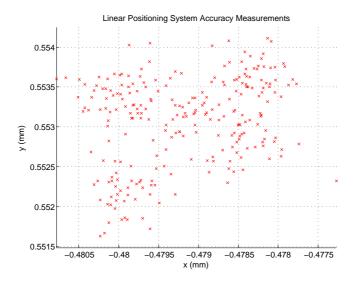

|    |                                                                                        | 4.5.5. Linear positioning system accuracy                           |  |

|    |                                                                                        | 4.5.6. Long term position stability (LTPS)                          |  |

|    |                                                                                        | 4.5.7. Position map                                                 |  |

|    | 4.6.                                                                                   | Summary and conclusions                                             |  |

|    | 4.7.                                                                                   | Bibliography                                                        |  |

|    | 1.1.                                                                                   | Dibnography                                                         |  |

| 5. |                                                                                        | e-based LLRF architecture and versatile test bench for heavy        |  |

|    |                                                                                        | linear acceleration 121                                             |  |

|    | 5.1.                                                                                   | Introduction                                                        |  |

|    | 5.2.                                                                                   | LLRF Control system: Proposed Solution                              |  |

|    | 5.3.                                                                                   | LLRF control system developed                                       |  |

|    |                                                                                        | 5.3.1. Description of the technology used 126                       |  |

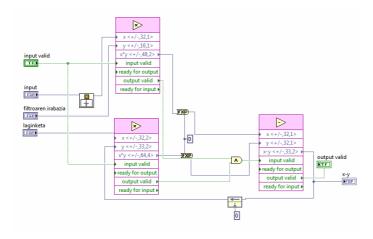

|    |                                                                                        | 5.3.2. Sampling technique performed: subsampling 129                |  |

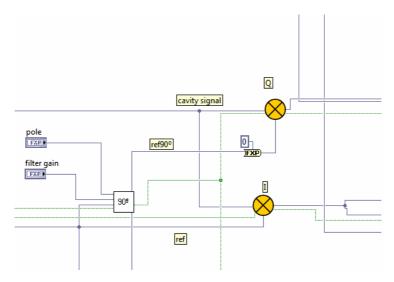

|    |                                                                                        | 5.3.3. Digital processing techniques performed: IQ demodulation 130 |  |

|    |                                                                                        | 5.3.4. LLRF control system design                                   |  |

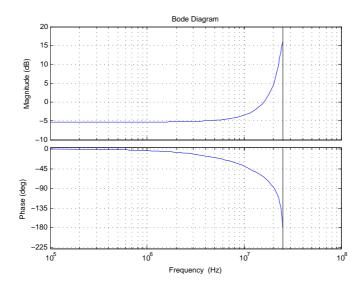

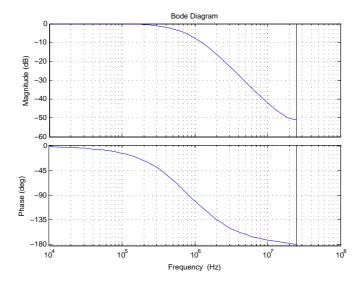

|    |                                                                                        | 5.3.5. Phase and Amplitude feedback control loop implementation 135 |  |

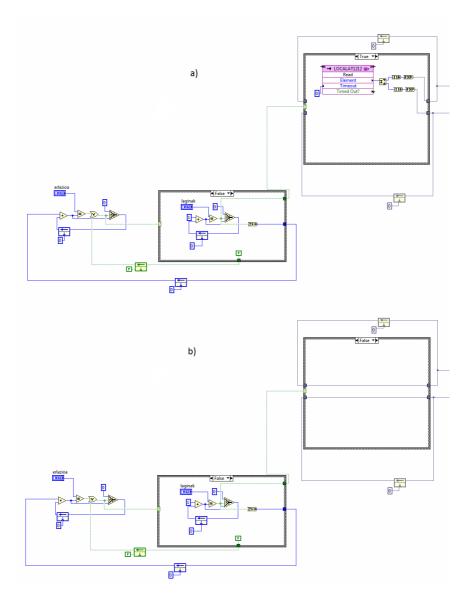

|    |                                                                                        | 5.3.5.1. Real-time controller based approach 136                    |  |

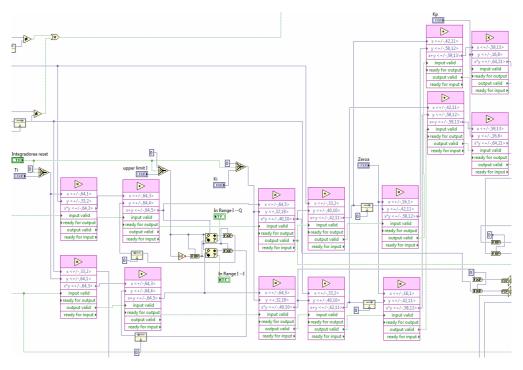

|    |                                                                                        | 5.3.5.2. FPGA approach                                              |  |

|    |                                                                                        | 5.3.6. Frequency tuning loop                                        |  |

|    |                                                                                        | 5.3.6.1. Phase detection based tuning loop 146                      |  |

|    |                                                                                        | 5.3.6.2. Reflected power minimization based tuning loop 147         |  |

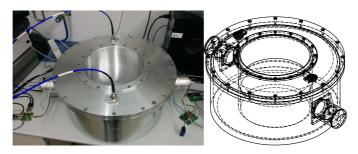

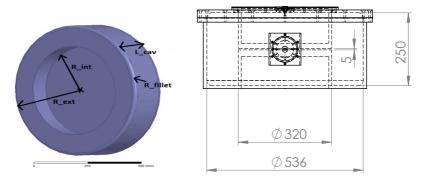

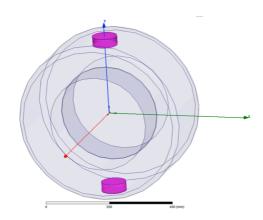

|    | 5.4.                                                                                   | Test bench description: $79.59 \ MHz$ resonant cavity 148           |  |

Contents Contents

|    | 5.5.  | Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 152 |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 0.0.  | 5.5.1. Phase and Amplitude feedback control loop experimental                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 102 |

|    |       | results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 152 |

|    |       | 5.5.1.1. Real-time controller based approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 152 |

|    |       | 5.5.1.2. FPGA approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 153 |

|    |       | 5.5.2. Frequency tuning loop experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 159 |

|    | 5.6.  | Summary and conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 160 |

|    | 5.7.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 161 |

| 6  | 1 - 6 | VIEW are core variable intermetion in EDICS activables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| U. |       | VIEW process variable integration in EPICS networks: formance test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 165 |

|    | •     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 167 |

|    | 6.2.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 168 |

|    | 6.3.  | Testbench description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 171 |

|    | 6.4.  | Performance Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 174 |

|    | 6.5.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 177 |

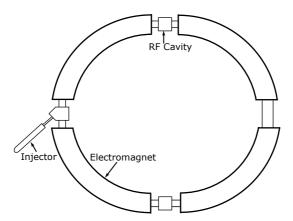

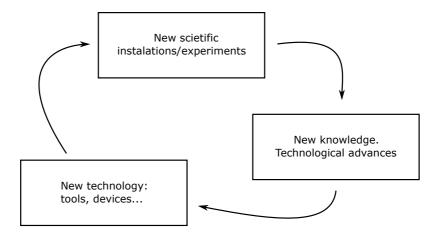

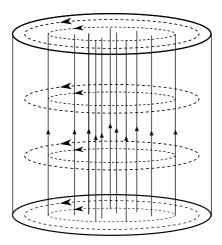

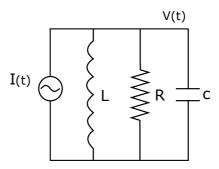

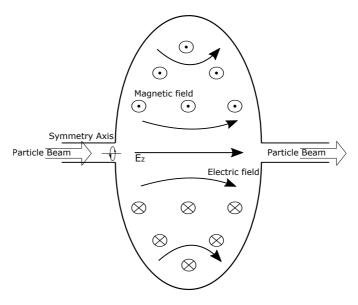

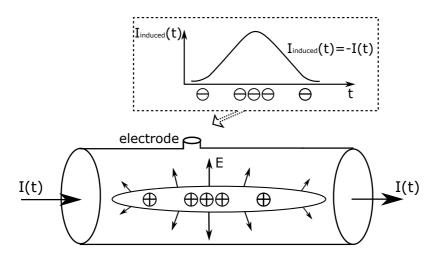

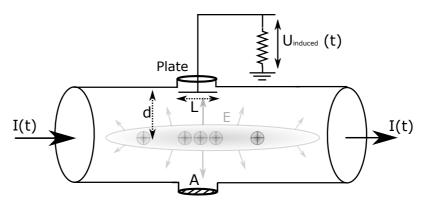

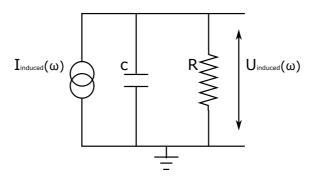

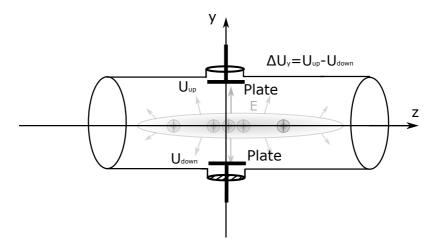

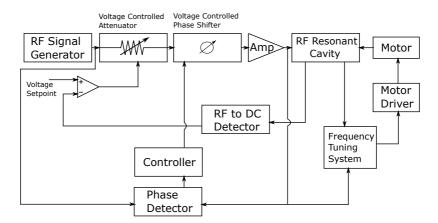

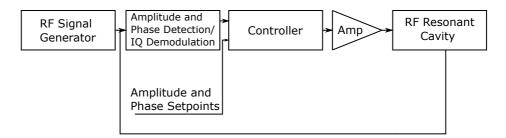

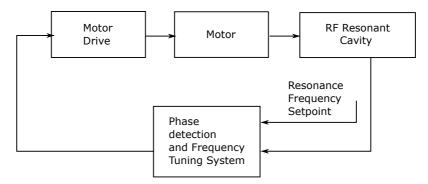

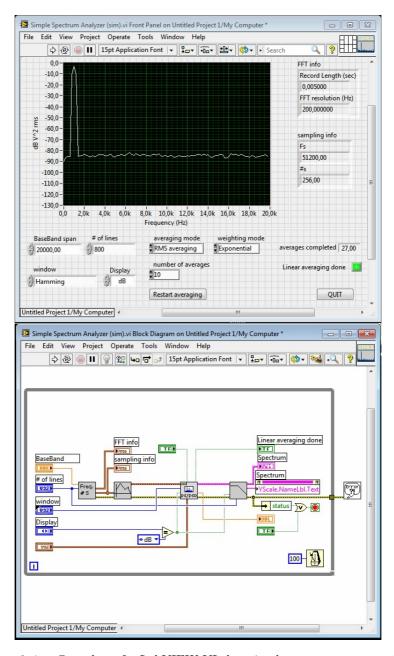

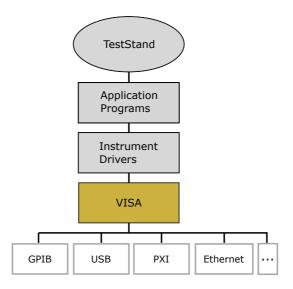

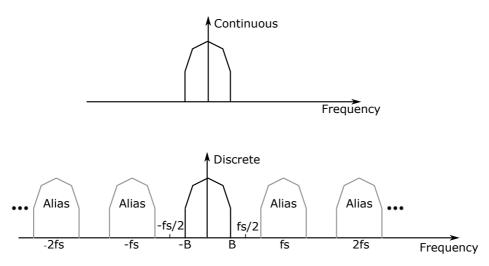

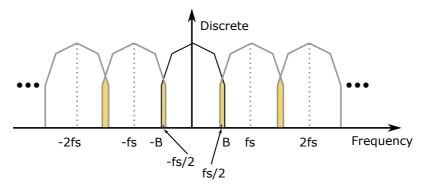

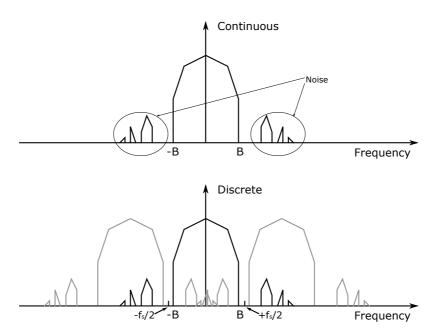

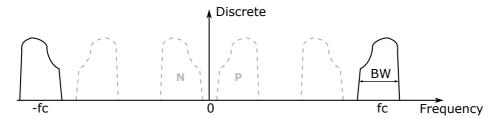

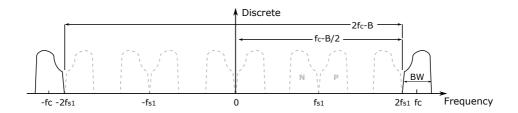

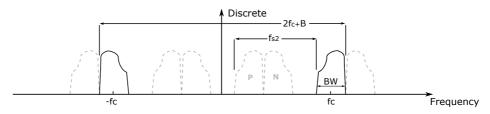

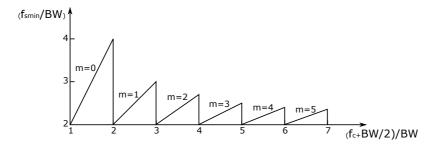

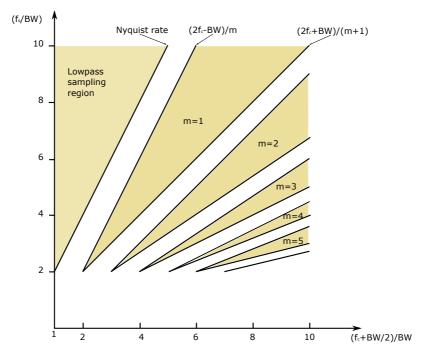

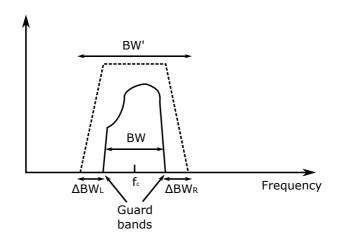

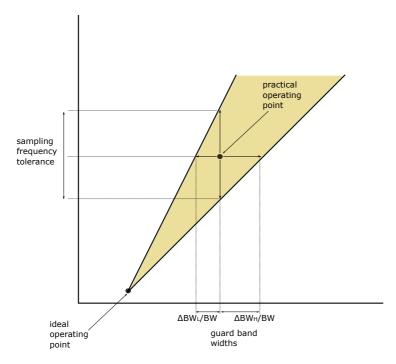

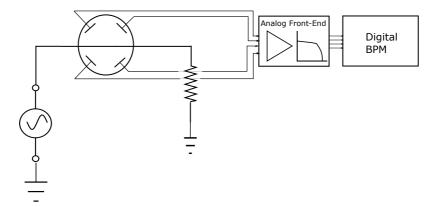

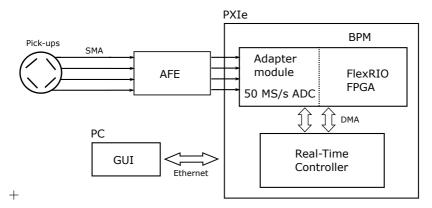

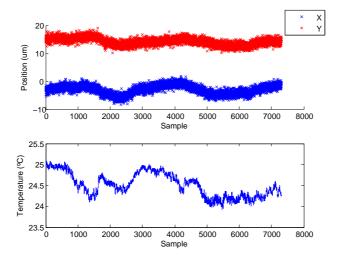

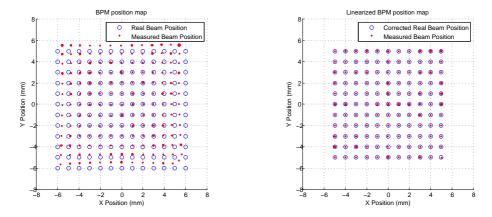

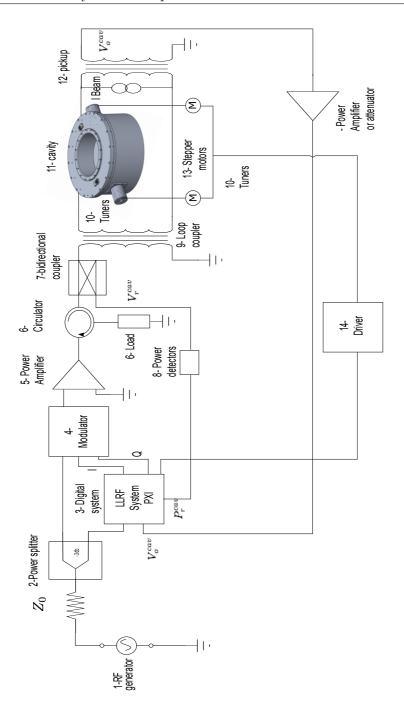

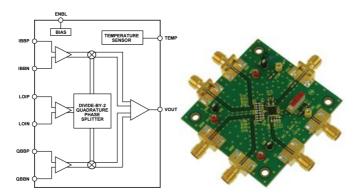

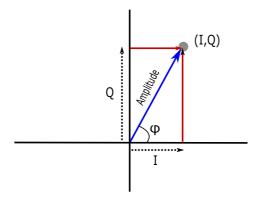

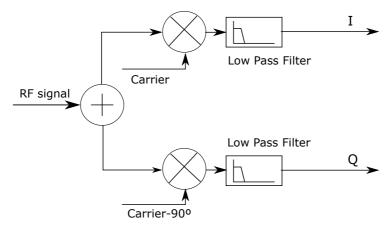

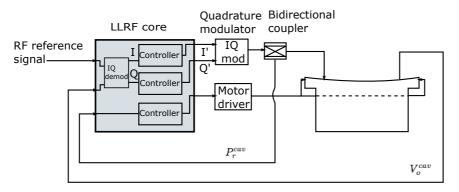

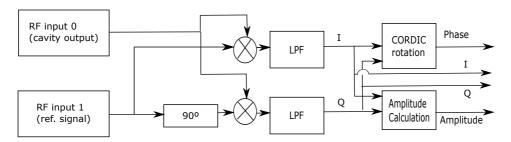

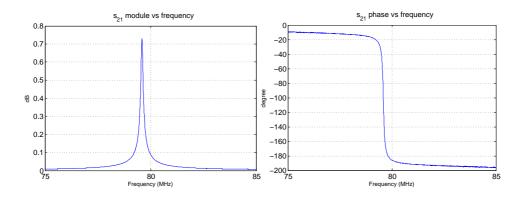

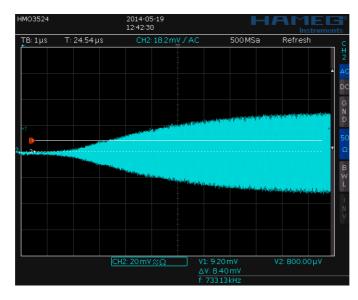

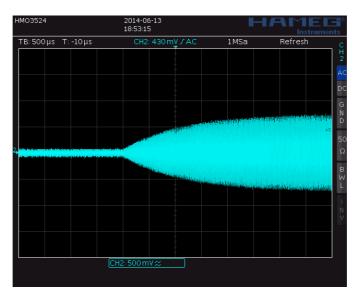

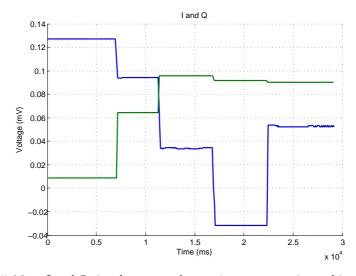

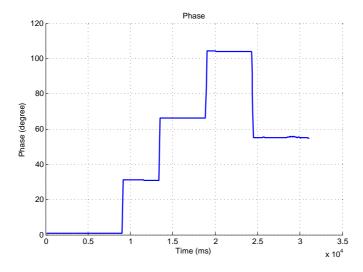

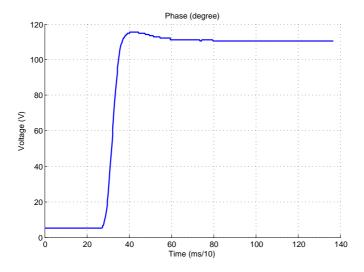

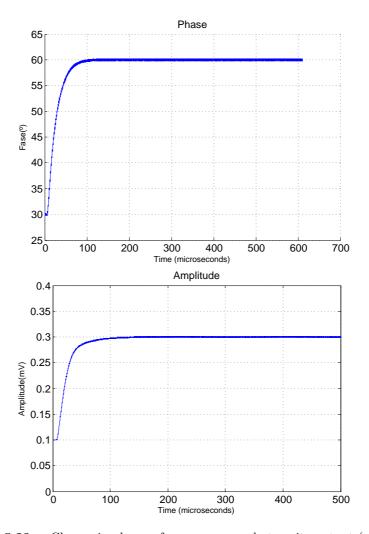

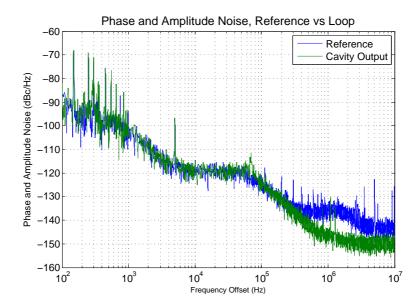

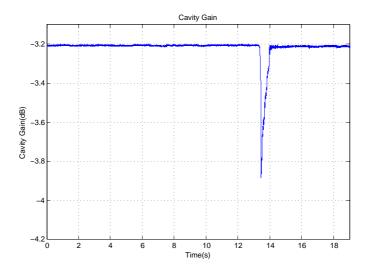

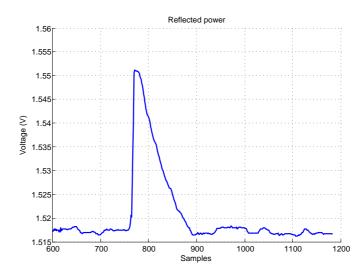

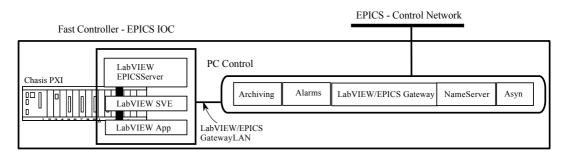

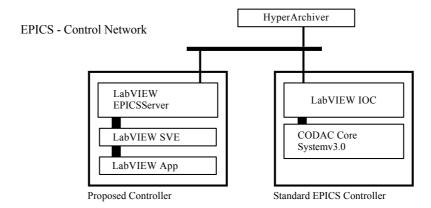

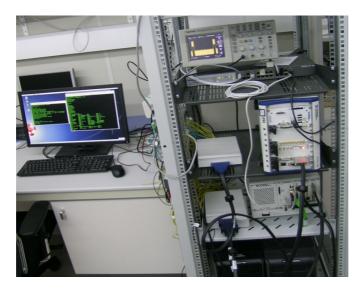

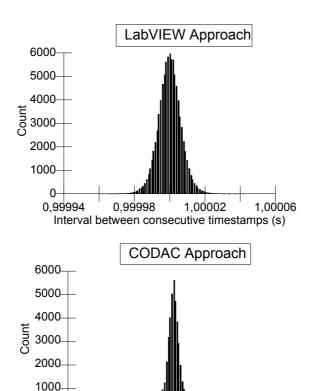

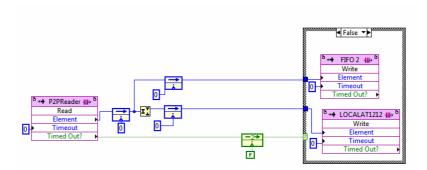

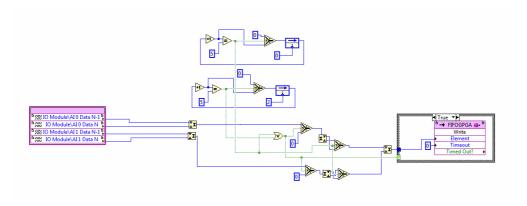

|    | 6.6.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 178 |