Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores

#### eman ta zabal zazu

INFORMATIKA FAKULTATEA FACULTAD DE INFORMÁTICA

# The Computer Input/Output Subsystem Education in an undergraduate introductory course: a Multiperspective Study

Dissertation Presented to the department of Computer Architecture and Technology in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Computer Science by Edurne Larraza-Mendiluze

> PhD Advisor Nestor Garay-Vitoria

Donostia, December 20, 2013

Servicio Editorial de la Universidad del País Vasco (UPV/EHU) Euskal Herriko Unibertsitateko Argitalpen Zerbitzua (UPV/EHU) University of the Basque Country - Editorial Service (UPV/EHU) ISBN: 978-84-9082-010-0

### Laburpena

Tesi hau informatikaren irakaskuntzaren ikerkuntza lerroaren barruan kokatzen da. Oinarri gisa, teknologia, pedagogia eta edukien ezagutza eredua (TPACK model, bere ingeleseko sigletatik) hartzen du. Ikerketa honetan, aipatutako ereduaren osagai bakoitza ikuspuntu desberdin gisa erabilia izan da konputagailuaren S/I azpisistemaren irakaskuntza aztertzeko.

**Edukien ezagutza** osagaiaren ikuspuntutik, testuliburuak, unibertsitateetako programak eta ikerkuntza bibliografia aztertu dira eta gaia irudikatzeko hurbilpen bat baino gehiago badaudela aurkitu da.

**Teknologiaren ezagutza** osagaiaren ikuspuntutik, Nintendo DS makinaren S/I azpisistemaren funtzionamendua aztertu da.

**Pedagogiaren ezagutza** osagaiaren ikuspuntutik, proiektuetan oinarritutako ikaskuntza eta beste hainbat metodologia aktibo ikasi egin dira ondoren aplikatu ahal izateko.

Txosten honek azaltzen du nola konbinatu diren osagai horietako ezagutzak bestelako ezagutzak sortzeko: **teknologia eta edukien** ezagutza, **teknologia eta pedagogia** ezagutza, **pedagogia eta edukien** ezagutza, eta azkenik, **teknologia, pedagogia eta edukien** ezagutza. Ezagutza berri hauekin konputagailuaren S/I azpisistemarentzako hezkuntza ingurune eraginkor bat sortzeko asmoz. Horretarako pauso hauek jarraitu dira:

- Edukiak irudikatzeko hurbilpen bat aukeratzea,

- Nintendo DS makina eduki zehatza lantzeko prestatzea eta

- Proposatutako teknika pedagogikoen baliozkotzea.

TPACK ereduan nolabait ezkutatuta baldin badago ere, hezkuntzarako eredu bat den neurrian, ikasleak ere hartzen ditu ikuspuntu gisa. Eta lan hau TPACK ereduan oinarritzen den neurrian, ikasleak ere hartzen ditu ikuspuntu gisa, eta haien ezagutza aztertu egiten du horretarako.

Lan honek informatikaren irakaskuntzaren ikerkuntza lerroan ate asko irekitzen ditu. Izan ere, informatikaren irakaskuntzaren ikerkuntzak konputagailuen S/I aspisistemari ez baitio arreta handirik ipini.

## Abstract

This dissertation is framed in the Computing Education Research area. As background, the Technological, Pedagogical and Content Knowledge framework (TPACK model) has been used. Each construct of the mentioned framework serves as a different study perspective, where the topic analysed is the computer I/O subsystem.

From the **content knowledge** perspective, textbooks, university syllabi and research bibliography have been analysed and different approaches found.

From the **technological knowledge** perspective, the I/O subsystem of the Nintendo DS machine has been studied.

From the **pedagogical knowledge** perspective, project-based learning (PBL), and other active learning methodologies have been learned for its latter application.

The dissertation explains how these constructs have been combined into **technological content** knowledge, **technological pedagogical** knowledge, **pedagogical content** knowledge, and finally **technological, pedagogical and content** knowledge in order to define an effective educational environment for the computer I/O subsystem topic. The following steps are followed:

- The selection of a content representation approach,

- The preparation of the Nintendo DS machine for its use this the specific content, and

- The validation of the proposed pedagogical techniques.

Although somehow hidden, the TPACK model, as an educational framework, includes the student as a perspective, and also does this work, with the analysis of students' knowledge.

This work opens many doors in the field of Computing Education Research towards the computer I/O subsystem, which has been barely payed attention.

# Eskaintza

### Familiari

Zentzurik zabalenean, zaretenoi eta izan gabe zaudetenoi, izandakoei eta izango direnei, tarte batzuetan egon ez banaiz ere, egongo naizelako.

Muxu.

A la familia

En el sentido más amplio, A quienes sois y a quienes sin serlo estáis, A quienes fueron y a quienes serán, Porque, aunque a veces no he estado, Estaré.

Muxu.

## Eskerrak

Azkenean ez da ba hau izango tesiko atalik zailena? Nik den denak eskertu nahi zaituztet. Inguruan zaudeten guztiek izan duzue nolabaiteko eragina tesi honen garapenean, animoak emanez besterik ez bada ere, eta hori eskertzekoa da. Hala ere, izenak jarri behar dira, eta zerrenda ez da motza inondik inora.

Lehenik, esker mila Nestor. Zuk onartu zenuen nere tesia zuzentzea nik planteatzen nuena bertako normatik ateratzen bazen ere. Beste askok arazoak ikusten zituzten lekuan, zuk aurrera egiteko erabakia hartu zenuen. Harez gero, urteak pasa dira, era guztietako gora beherak izan dira, tesiaren proiektua erabat aldatu egin da, eta zuri esker amaitzea lortu dut.

Eskerrik asko ere finantzio propiorik izan ez duen proiektu hau ekonomikoki bideratzen lagundu duzuenoi, Konputagailuen Arkitektura eta Teknologia Saila eta Egokituz taldeari.

Eskerrik asko PIE/HBPetan parte hartu duzuen guztioi, Txelo, Natxo, Javi, Iratxe, Nestor, Lukas, Santiago, Teresa eta Ibai. Hor egindako lanak ere berebiziko garrantzia izan du tesi honengan.

Bazkalorduko taldetxoa ezin ahaztu. Horko tertuliak eta fotosintesi gabe seguruenik indar falta izango nintzateke.

Ezin ahaztu tesian zehar egindako esperimentuetan parte hartu duten guztiak. Batetik ikasleak, metodologia eta teknologia berriak probatu behar izan dituzue eta jarraitu beharrekoa ez da beti arrosa bidea izan. Bereziki nirekin 2010/2011, 2011/2012 eta 2012/2013 ikasturteetan egon zaretenek sufritu behar izan duzue tesi hau, baina aurreko urteetan, oraindik ere plan zaharrean nirekin izan zineten ikasleak ere ez zaituztet ahazten. Bestetik irakasleak, zuen ezagutza kontzeptu mapen bidez adierazteko eskatu nizuen batzuei eta jakin badakit ez zela lan makala izan, eskerrak beraz Gonzalo, Teresa, Javi, Natxo, Iratxe, Txelo, Clemente eta Nestor.

Roberto, eskerrik asko Latex-ekin laguntzeagatik, auskalo nolako txostena edukiko nukeen zure txantiloi eta aholkurik gabe.

Ana, zuri ere eskerrik asko bulegokide aparta izanagatik, eman didazun laguntza eta animoengatik.

GALAN taldekoei, bereziki Iñakiri ere eskerrik asko kontzeptu mapekin emandako laguntzagatik eta aplikazioan gauzak nire beharretara egokitzeagatik.

Oro har, Informatika Fakultateari ere eskertu nahi dizkiot bertan jaso ditudan ezagutzak. Lehenik nire irakasle izan zineten asko, orain nire lankide zarete eta behar izan dudan guztietan egon da norbait laguntzeko eta animoak emateko prest.

Eta nola ez, eskerrak familiari zuen animo eta laguntzagatik eta bereziki Oier, Izaro, Ander, eskerrik asko etxea alaitzeagatik eta etxean gauzak ondo joan zitezen emandako laguntza guztiagatik. Kiki, ez naiz kapaz tesi hau aurrera atera zedin egin duzun guztia hitzez adierazteko, mila esker!

## Acknowledgements

This work would have been impossible to accomplish without the help of so many people. I would like to thank Maria José Santofimia for trying our methods with her students and giving us the results.

Also all the people in the ICER doctoral consortium that helped me by redirecting the objectives of the thesis. It was very nice to be able to talk to people that could perceive what I was doing from a different perspective. And the same acknowledgement goes also for the community of the Koli Calling conference. Thank you very much!

Capitolina, although finally it become very hard to add a gender perspective to this work (there are so few girls in our classrooms!) thank you for helping when you could and for understanding all the changes. This last acknowledgement was written also in Basque, but since some of the people will not be able to understand, here it goes again. Thank to the professors that accepted our request to draw concept maps for this research. I know that it was not an easy task, thanks therefore to Gonzalo, Teresa, Javi, Natxo, Iratxe, Txelo, Clemente and Nestor.

### "If we knew what we were doing, it wouldn't be called research."

Like so much of what Einstein said, this quotation communicates a very important idea in a very simple way. The path to discovery is seldom straight. Rarely does the reader of the final research have the opportunity to understand how the journey of discovery unfolded.

By Mark Cotteleer<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>At http://dupress.com/articles/its-called-research-the-exceptional-company-collection/

# Preface

Mark Cotteleer's previous quote gives me the opportunity to introduce the reader to the journey of this dissertation.

Most of the people I see around me do their research within a research group. Although a PhD dissertation is an individual work, many times it is necessary to explain which parts out of all the things reported in the dissertation are the PhD student's work and which are the group's work.

In this case there is also a group of people supporting the work, but it is not a research group, it is a group of teachers that have been teaching the computer I/O subsystem in the last years.

Thanks to that group, and also to two colleagues from the school of pedagogy, I have been able to get some funds from the Educational Counselling Service (SAE/HELAZ from its initials in Spanish and Basque) for two Educational Innovation Projects (PIE/HBP from its initials in Spanish and Basque) in which I have been the leader.

That group, where my PhD advisor can be found, has supported my decisions, has brought some ideas, and has helped writing some of the papers, but without any background on Computing Education Research, since each of them have their own research area.

Thanks to ITICSE, but mostly ICER and Koli Calling conferences I have been able to understand some of the intricacies of this research area, which I am sure will still surprise me many times.

I hope this short explanation can help the reader imagine the very twisted path of this dissertation.

Thanks again to my PIE colleagues and to the CER community.

### Piled Higher and Deeper by Jorge Cham

www.phdcomics.com

title: "Write in Pieces" - originally published 8/4/2010

# Contents

| 1 | Intr | oduction                                                | 1  |

|---|------|---------------------------------------------------------|----|

|   | 1.1  | The computer I/O subsystem - What is it?                | 1  |

|   | 1.2  | Why is it important to teach the computer I/O subsystem |    |

|   |      | to computer scientist and engineers?                    | 2  |

|   | 1.3  | What do the computing curricula recommendations say     |    |

|   |      | about the I/O subsystem topic?                          | 3  |

|   | 1.4  | The computer I/O subsystem topic at the University of   |    |

|   |      | the Basque Country (UPV/EHU)                            | 6  |

|   | 1.5  | Research questions                                      | 7  |

|   | 1.6  | Organization of the Document                            | 7  |

| 2 | Link | to relevant theory                                      | 9  |

|   | 2.1  | Content Knowledge (CK), Pedagogical Knowledge (PK)      |    |

|   |      | and Technological Knowledge (TK), the basic constructs. | 14 |

|   | 2.2  | Technological Content Knowledge (TCK)                   | 16 |

|   | 2.3  | Technological Pedagogical Knowledge (TPK)               | 16 |

|   | 2.4  | Pedagogical Content Knowledge (PCK)                     | 17 |

|   | 2.5  | Technological Pedagogical Content Knowledge (TPCK or    |    |

|   |      | TPACK)                                                  | 17 |

|   | 2.6  | Conclusions                                             | 18 |

| 3 | Bacl | kground and related work                                | 19 |

|   | 3.1  |                                                         |    |

|   |      | system                                                  | 20 |

|   |      | 3.1.1 The data gathering and analysis process           | 20 |

|   |      | 3.1.2 The purely descriptive approach (PDA)             | 21 |

|   |      |                                                         |    |

|   |                                                                                  | 3.1.3                                                                                                                                          | The performance approach (PeA)                                                                                    | 22                                                                    |

|---|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|   |                                                                                  | 3.1.4                                                                                                                                          | The programming approach (PrA)                                                                                    | 23                                                                    |

|   |                                                                                  | 3.1.5                                                                                                                                          | The datapath-signal approach (DSA)                                                                                | 23                                                                    |

|   | 3.2                                                                              | How d                                                                                                                                          | lo textbooks present the I/O topic?                                                                               | 24                                                                    |

|   |                                                                                  | 3.2.1                                                                                                                                          | Computer Organization and Architecture 9th Edi-                                                                   |                                                                       |

|   |                                                                                  |                                                                                                                                                | tion                                                                                                              | 24                                                                    |

|   |                                                                                  | 3.2.2                                                                                                                                          | Computer Organization and Design 4th Edition .                                                                    | 26                                                                    |

|   |                                                                                  | 3.2.3                                                                                                                                          | Computer Organization and Embedded Systems                                                                        |                                                                       |

|   |                                                                                  |                                                                                                                                                | 6th Edition                                                                                                       | 26                                                                    |

|   |                                                                                  | 3.2.4                                                                                                                                          | Computer System Architecture 3rd Edition                                                                          | 27                                                                    |

|   | 3.3                                                                              |                                                                                                                                                | is the community trying to do in order to improve                                                                 |                                                                       |

|   |                                                                                  | studen                                                                                                                                         | nts' understanding of the I/O topic?                                                                              | 28                                                                    |

|   |                                                                                  | 3.3.1                                                                                                                                          | Simulators                                                                                                        | 31                                                                    |

|   |                                                                                  | 3.3.2                                                                                                                                          | Real Machines                                                                                                     | 33                                                                    |

|   |                                                                                  | 3.3.3                                                                                                                                          | 0 11                                                                                                              | 36                                                                    |

|   | 3.4                                                                              | The I/                                                                                                                                         | O topic at several Spanish universities                                                                           | 37                                                                    |

|   | 3.5                                                                              | The ap                                                                                                                                         | pproach taken at the University of the Basque Country                                                             | 39                                                                    |

|   | 3.6                                                                              | Conclu                                                                                                                                         | 1sions                                                                                                            | 39                                                                    |

|   |                                                                                  |                                                                                                                                                |                                                                                                                   |                                                                       |

| Λ | Doo                                                                              | dingo                                                                                                                                          | n the advantional infrastructure                                                                                  | 11                                                                    |

| 4 |                                                                                  | -                                                                                                                                              | n the educational infrastructure                                                                                  | 41<br>42                                                              |

| 4 | 4.1                                                                              | Selecti                                                                                                                                        | ion of the handheld game console                                                                                  | 42                                                                    |

| 4 |                                                                                  | Selecti<br>The N                                                                                                                               | ion of the handheld game console                                                                                  | 42<br>43                                                              |

| 4 | 4.1                                                                              | Selecti<br>The N<br>4.2.1                                                                                                                      | ion of the handheld game console DS console                                                                       | 42<br>43<br>43                                                        |

| 4 | 4.1                                                                              | Selecti<br>The N<br>4.2.1<br>4.2.2                                                                                                             | ion of the handheld game consoleDS consoleThe memoryThe double processor                                          | 42<br>43<br>43<br>46                                                  |

| 4 | 4.1                                                                              | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3                                                                                                    | ion of the handheld game consoleDS consoleThe memoryThe double processorThe I/O registers                         | 42<br>43<br>43<br>46<br>47                                            |

| 4 | 4.1<br>4.2                                                                       | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                                                           | ion of the handheld game consoleDS consoleThe memoryThe double processorThe I/O registersThe interrupt management | 42<br>43<br>43<br>46<br>47<br>49                                      |

| 4 | 4.1                                                                              | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some                                                                                   | ion of the handheld game console                                                                                  | 42<br>43<br>43<br>46<br>47<br>49<br>50                                |

| 4 | 4.1<br>4.2                                                                       | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1                                                                          | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50                                |

| 4 | 4.1<br>4.2                                                                       | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2                                                                 | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50<br>51                          |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                    | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2<br>4.3.3                                                        | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50<br>51<br>52                    |

| 4 | 4.1<br>4.2                                                                       | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2<br>4.3.3                                                        | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50<br>51                          |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                        | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2<br>4.3.3<br>Conclu                                              | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50<br>51<br>52                    |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>The</li> </ul>      | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2<br>4.3.3<br>Conclu<br><b>Project</b>                            | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50<br>51<br>52                    |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>The</li> </ul>      | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2<br>4.3.3<br>Conclu<br><b>Project</b><br><b>System</b><br>The pr | ion of the handheld game console                                                                                  | 42<br>43<br>43<br>46<br>47<br>49<br>50<br>50<br>51<br>52<br>53        |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>The subs</li> </ul> | Selecti<br>The N<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Some<br>4.3.1<br>4.3.2<br>4.3.3<br>Conclu<br><b>Project</b><br><b>System</b><br>The pr | ion of the handheld game console                                                                                  | 42<br>43<br>46<br>47<br>49<br>50<br>50<br>51<br>52<br>53<br><b>55</b> |

|   |      | 5.1.3    | The assessment                                      | 59    |

|---|------|----------|-----------------------------------------------------|-------|

|   | 5.2  | The ne   | ew PBL methodology                                  | 59    |

|   |      | 5.2.1    | The first school year 2010-2011                     | 61    |

|   |      | 5.2.2    | The second school year 2011-2012                    | 64    |

|   |      | 5.2.3    | The third school year 2012-2013                     | 67    |

|   | 5.3  | The Pr   | rojects                                             | 68    |

|   |      | 5.3.1    | School year 2010/2011                               | 69    |

|   |      | 5.3.2    | School year 2011/2012                               | 71    |

|   |      | 5.3.3    | School year 2012/2013                               | 72    |

|   | 5.4  | Conclu   | usions                                              | 73    |

| 6 | Ana  | lysis of | the data obtained during the three years            | 77    |

|   | 6.1  | •        | sis of the grades obtained by the students in the   |       |

|   |      |          | ıter I/O subsystem topic                            | 77    |

|   | 6.2  | Analys   | sis of the satisfaction among the students while    |       |

|   |      | learnii  | ng the computer I/O subsystem                       | 80    |

|   |      | 6.2.1    | The satisfaction questionnaire                      | 80    |

|   |      | 6.2.2    | Data for a qualitative analysis of the satisfaction | 85    |

|   |      | 6.2.3    | Attraction and retention                            | 88    |

|   | 6.3  | Conclu   | usions                                              | 89    |

| 7 | Stuc | lents' u | inderstanding about the computer I/O subsystem      | ı? 91 |

|   | 7.1  |          | d work                                              | 92    |

|   | 7.2  | The pr   | reliminary study                                    | 94    |

|   | 7.3  |          | d used for the complete study                       | 98    |

|   |      | 7.3.1    | Subjects                                            | 98    |

|   |      | 7.3.2    | Procedure                                           | 99    |

|   | 7.4  | Quant    | itative analysis of the concept maps                | 105   |

|   |      | 7.4.1    | The system                                          | 108   |

|   |      | 7.4.2    | Connections inside the I/O controller subtopic .    | 109   |

|   |      | 7.4.3    | Connections inside the Synchronization subtopic     | 110   |

|   |      | 7.4.4    | Connections inside the DMA subtopic                 | 111   |

|   |      | 7.4.5    | Links between the "I/O controller" and the "syn-    |       |

|   |      |          | chronization" subtopics                             | 112   |

|   |      | 7.4.6    | Links between the "I/O controller" and the "DMA"    |       |

|   |      |          | subtopics                                           | 113   |

|     |        | 7.4.7    | Links between "DMA" and "synchronization" sub-    |     |

|-----|--------|----------|---------------------------------------------------|-----|

|     |        |          | topics                                            | 113 |

|     | 7.5    | A more   | e qualitative reading of the concept maps         | 113 |

|     |        | 7.5.1    | The system                                        | 114 |

|     |        | 7.5.2    | Connections inside the I/O controller subtopic .  | 114 |

|     |        | 7.5.3    | Connections inside the Synchronization subtopic   | 116 |

|     |        | 7.5.4    | Connections inside the DMA subtopic               | 118 |

|     |        | 7.5.5    | Links between the I/O controller and the synchro- |     |

|     |        |          | nization subtopics                                | 118 |

|     |        | 7.5.6    | Links between the DMA controller and the I/O      |     |

|     |        |          | controller                                        | 119 |

|     |        | 7.5.7    | Links between the DMA and the synchronization     |     |

|     |        |          | subtopics                                         | 120 |

|     | 7.6    | Conclu   | lsions                                            | 120 |

| 8   | Over   | all Cor  | nclusions and Future Work                         | 123 |

|     | 8.1    | Conclu   | lsions                                            | 123 |

|     | 8.2    | Future   | work                                              | 125 |

|     | 8.3    | Publica  | ations obtained from this work                    | 126 |

| D.1 | 1.     | 1        |                                                   | 100 |

| B1  | bliogi | aphy     |                                                   | 129 |

| Ар  | pend   | ices     |                                                   | 139 |

| Α   | Note   | es on th | ne theory of the computer I/O subsystem for the   | e   |

|     | stud   | ents     |                                                   | 143 |

|     | A.1    | Sarrera  | a/Irteera-ko interfazearen deskribapena           | 143 |

|     |        | A.1.1    | S/I-ko kontrolagailuaren ikuspegi funtzionala     | 144 |

|     |        | A.1.2    | Sarrera/irteera-ko kontrolagailuaren erregistroak | 145 |

|     |        | A.1.3    | Sarrera/Irteera memorian mapeatuta                | 146 |

|     |        | A.1.4    | Sarrera/Irteera bereiztua edo memorian ez ma-     |     |

|     |        |          | peatua                                            | 149 |

|     |        | A.1.5    | S/Iko kontrolagailuen sailkapena                  | 152 |

|     | A.2    | Komur    | nikazioa eta sinkronizazioa Sarrera/Irteerako er- |     |

|     |        | agikete  | etan                                              | 153 |

|     |        | A.2.1    | Inkesta bidezko Sarrera/irteera                   | 156 |

|     |        | A.2.1    | Etenen bidezko Sarrera/Irteera                    | 157 |

|   | A.3  | Etener   | n kudeaketa                                         | 158   |

|---|------|----------|-----------------------------------------------------|-------|

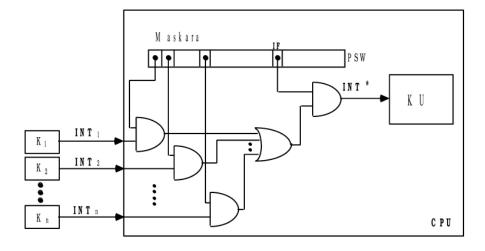

|   |      | A.3.1    | Eten-eskaeraren detekzioa                           | 159   |

|   |      | A.3.2    | Gorde etendako programaren egoera                   | 161   |

|   |      | A.3.3    | Zerbitzu-errutina edo periferikoaren identifikazioa | a 162 |

|   |      | A.3.4    | Zerbitzu-errutinaren exekuzioa                      | 164   |

|   |      | A.3.5    | Etendako programaren egoera berreskuratu            | 164   |

|   |      | A.3.6    | Maila anitzeko etenak                               | 165   |

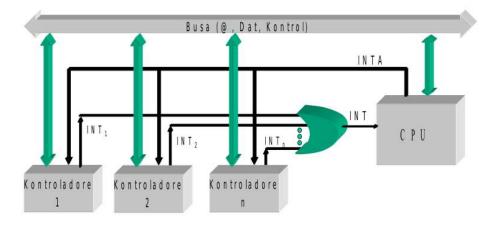

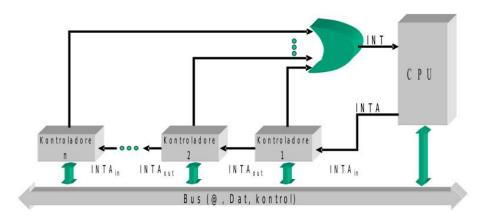

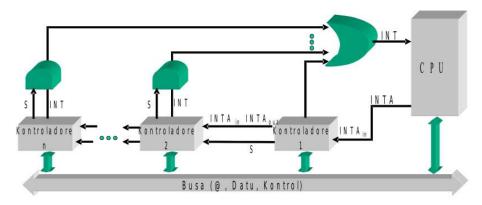

|   |      | A.3.7    | Etenen kontrolagailua                               | 166   |

|   | A.4  |          | riarako Atzipen Zuzena (DMA – Direct Memory         |       |

|   |      | Access   | :)                                                  | 166   |

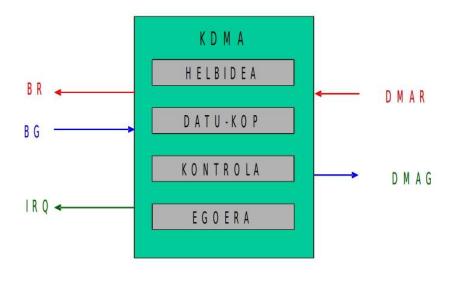

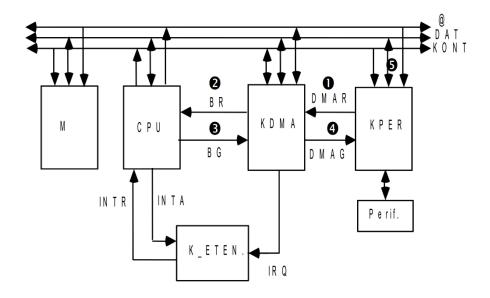

|   |      | A.4.1    | DMA kontrolagailua                                  | 169   |

|   |      | A.4.2    | DMA bidezko transferentzia                          | 170   |

| В | Not  | es on tl | he specifics of the Nintendo DS for the students    | 175   |

|   | B.1  |          | varearen deskribapena                               | 176   |

|   |      | B.1.1    | Prozesadoreak                                       | 176   |

|   |      | B.1.2    | Memoria                                             | 176   |

|   |      | B.1.3    | Pantailak                                           | 177   |

|   |      | B.1.4    | Teklatua                                            | 183   |

|   |      | B.1.5    | Denboragailuak                                      | 185   |

|   | B.2  | Etener   | n kudeaketa                                         | 188   |

|   |      | B.2.1    | Etenen kudeaketarako erregistroak (etenen kudeatz   | za-   |

|   |      |          | ilea)                                               | 188   |

|   |      | B.2.2    | Eten-bektore edo eten-taula                         | 189   |

|   |      | B.2.3    | Interrupt Dispatcher-a                              | 191   |

| С | Sou  | rce-cod  | le of one of the projects                           | 195   |

|   | C.1  |          | ain program                                         | 195   |

|   | C.2  |          | ng the Interrupt-table                              | 196   |

|   | C.3  |          | eyboard                                             | 196   |

|   | C.4  |          | mer                                                 | 196   |

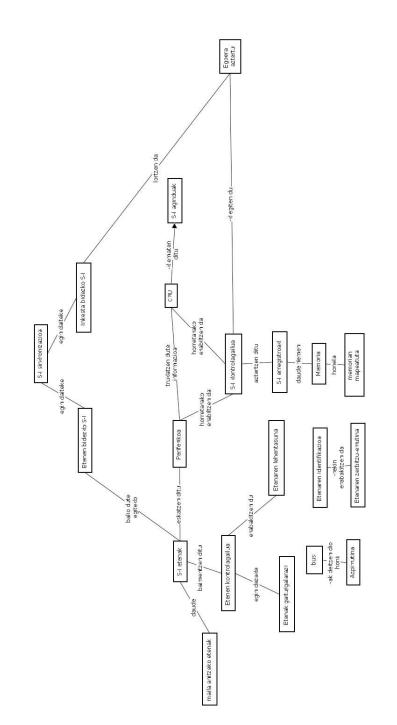

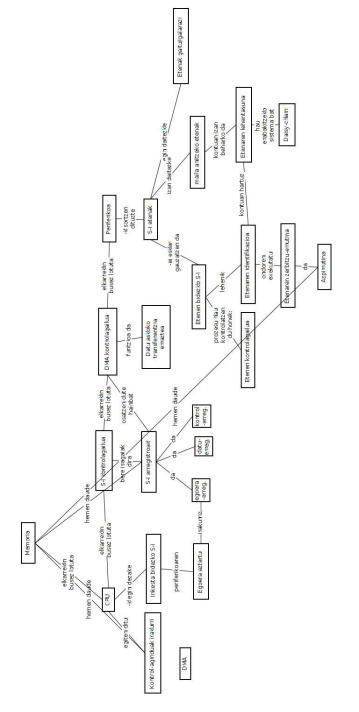

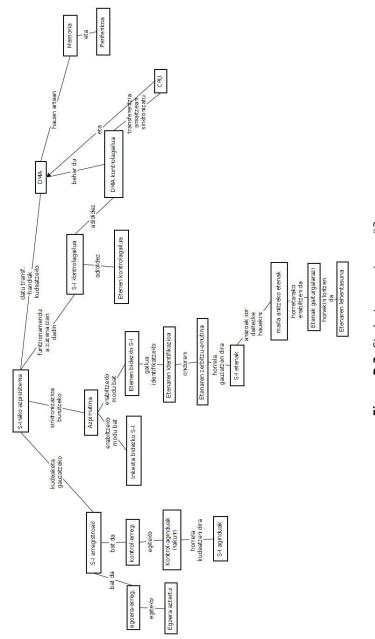

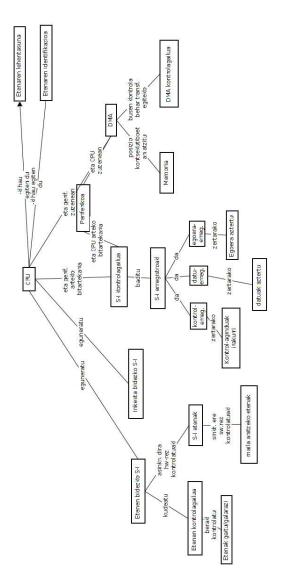

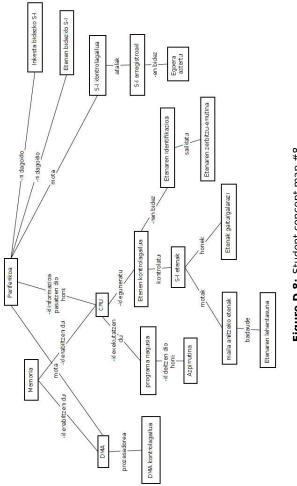

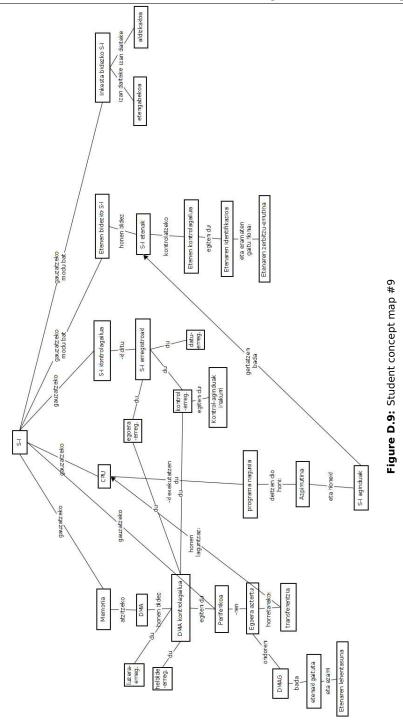

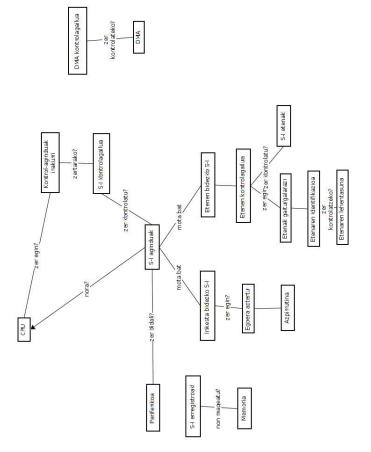

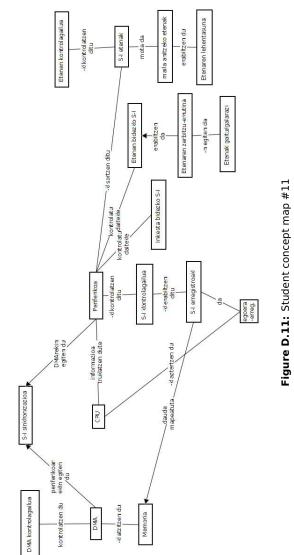

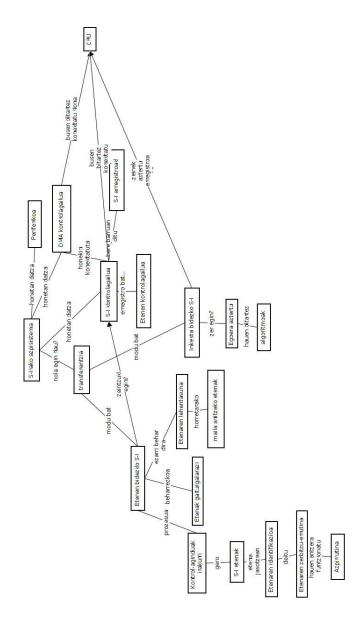

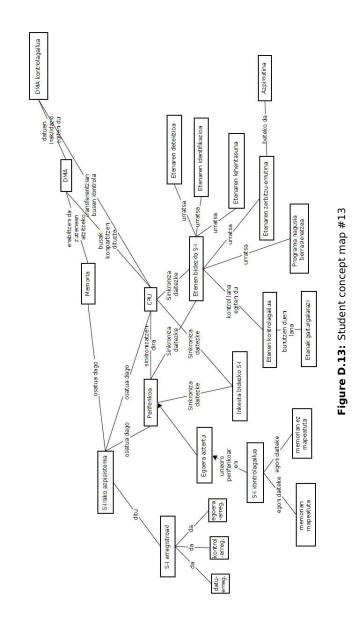

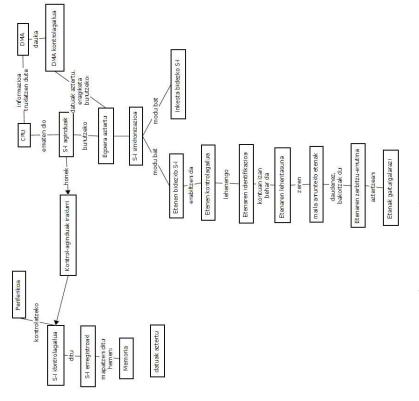

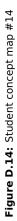

| D | Stuc | lents' c | concept maps                                        | 207   |

|   |      |          | · ·                                                 |       |

# List of Figures

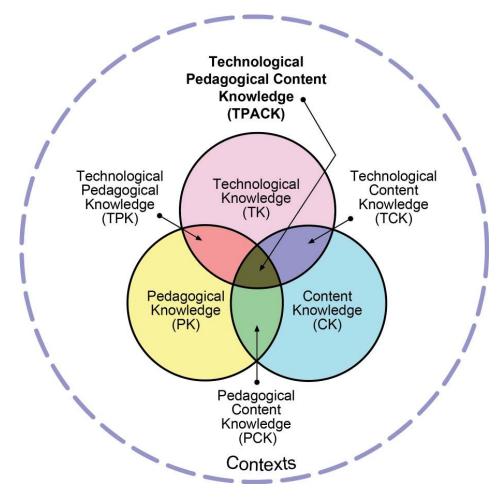

| 2.1        | The TPACK Image. Reproduced with permission of the publisher, © 2012 by tpack.org | 12 |

|------------|-----------------------------------------------------------------------------------|----|

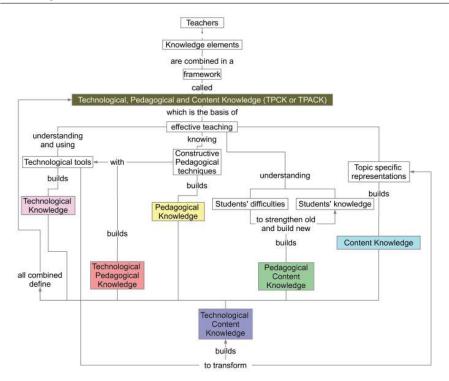

| 2.3        | Basic constructs                                                                  | 14 |

| 2.2        | The TPACK model as understood and used in this disser-                            | 11 |

| 2.2        | tation. For the constructs, the same colours have been                            |    |

|            | used as in Figure 2.1                                                             | 15 |

| 2.4        | TCK construct                                                                     | 16 |

| 2.4<br>2.5 |                                                                                   | 16 |

|            | TPK construct                                                                     |    |

| 2.6        | PCK construct                                                                     | 17 |

| 2.7        | TPACK construct                                                                   | 17 |

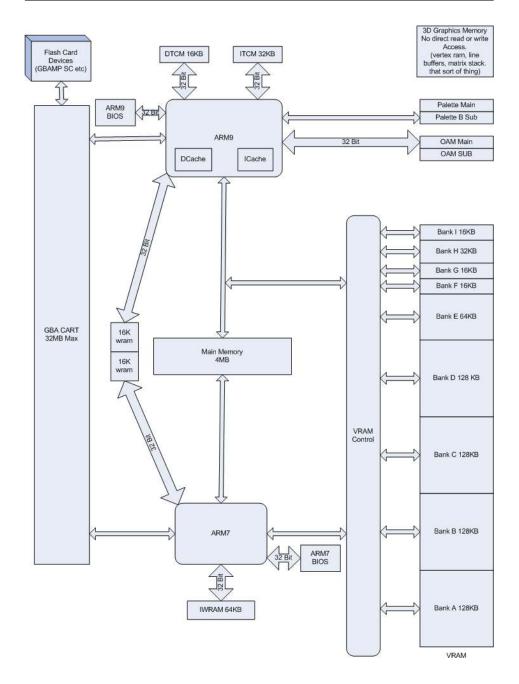

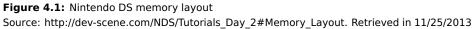

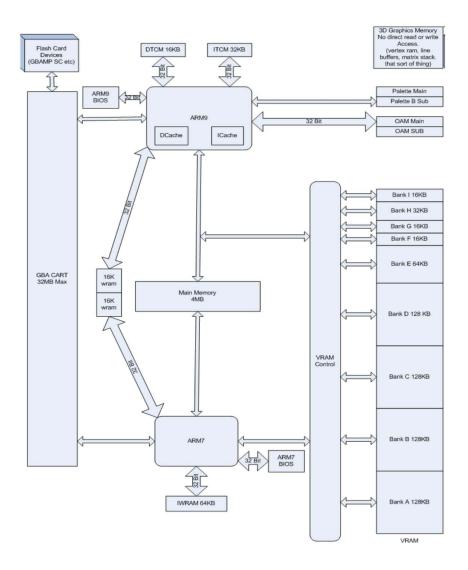

| 4.1        | Nintendo DS memory layout                                                         |    |

|            | Source: http://dev-scene.com/NDS/Tutorials Day 2#Mem                              | 1- |

|            | ory Layout. Retrieved in 11/25/2013                                               | 44 |

| 4.2        | Source code of the routine for initializing video memory,                         |    |

|            | from examples of Dovoto and Jaeden Ameron in the                                  |    |

|            | devkitPro environment [devkitPro]                                                 | 45 |

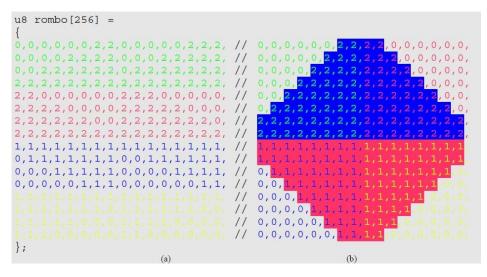

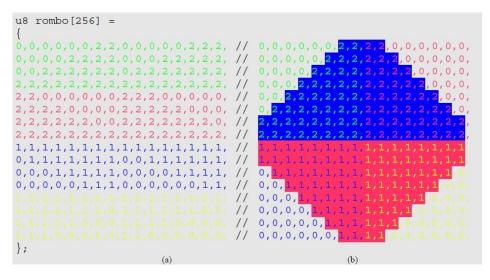

| 4.3        | Definition of a sprite, (a) array containing the value of                         |    |

| 1.0        | each pixel, (b) interpretation of the information con-                            |    |

|            | tained in the array.                                                              | 46 |

| 4.4        | Source code for saving the sprite in memory.                                      | 47 |

|            |                                                                                   |    |

| 4.5        | Definition of the I/O registers.                                                  | 48 |

| 4.6        | Setting interrupt service routines for each interrupt                             | 49 |

| 4.7        | Code in the Interrupt dispatcher that avoids multiple level                       |    |

|            | interrupts                                                                        | 50 |

| 4.8        | Formula to calculate the value of the timer data register                         | 50 |

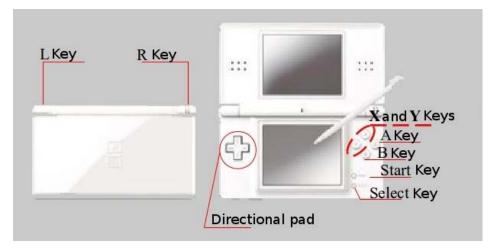

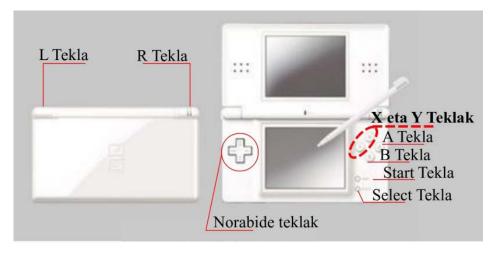

|      | Keyboard of the Nintendo DS                                                                                                                                                                                                                                                                        | 51 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | from the processor devoted to I/O                                                                                                                                                                                                                                                                  | 53 |

|      | Definition of a variable of the touchPosition type                                                                                                                                                                                                                                                 | 53 |

| 4.12 | Polling the touch-screen                                                                                                                                                                                                                                                                           | 54 |

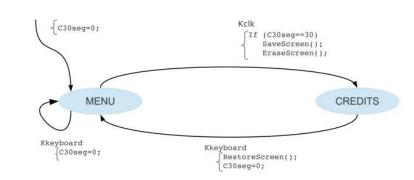

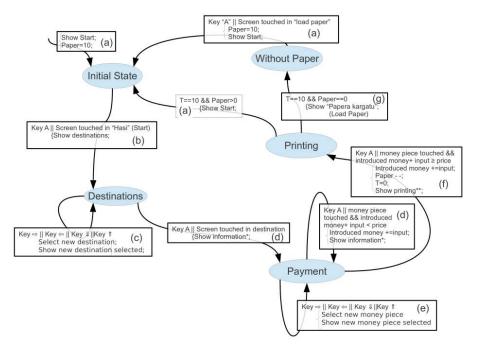

| 5.1  | The SM used in the fourth laboratory session (a screen saver)                                                                                                                                                                                                                                      | 58 |

| 5.2  | State machine for the train ticket vending machine de-<br>veloped for the NDS during the school year 2010-2011.<br>*The information shown is the destination, the ticket<br>price, the introduced quantity, and the quantity remain-<br>ing to be introduced. Letters in transitions are links for |    |

|      | screen-shots in Figure 5.3                                                                                                                                                                                                                                                                         | 69 |

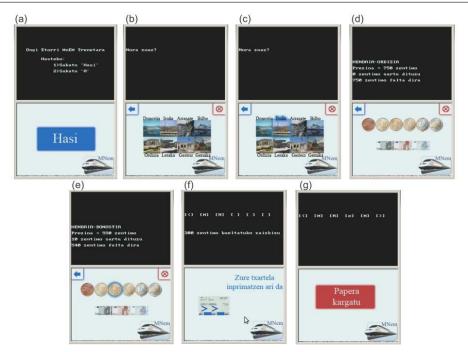

| 5.3  | Screen-shots for the train ticket vending machine devel-                                                                                                                                                                                                                                           |    |

|      | oped for the NDS during the school year 2010-2011                                                                                                                                                                                                                                                  | 70 |

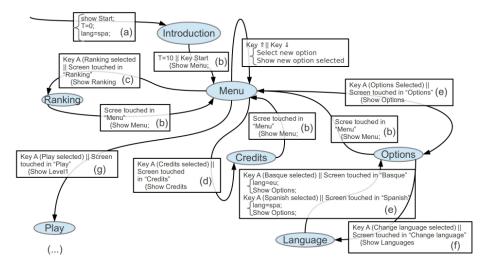

| 5.4  | State machine for the SuperNacho game developed for                                                                                                                                                                                                                                                |    |

|      | the NDS during the school year 2011-2012. Letters in transitions are links for screen-shots in Figure 5.5                                                                                                                                                                                          | 71 |

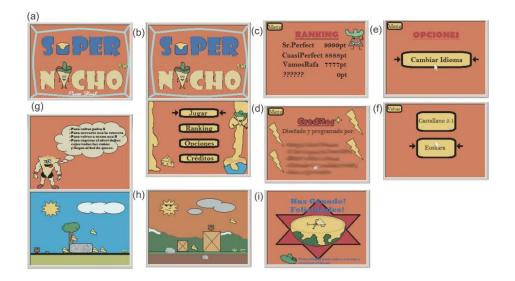

| 5.5  | Screen-shots for the train ticket vending machine devel-                                                                                                                                                                                                                                           | /1 |

| 0.0  | oped for the NDS during the school year 2011-2012                                                                                                                                                                                                                                                  | 73 |

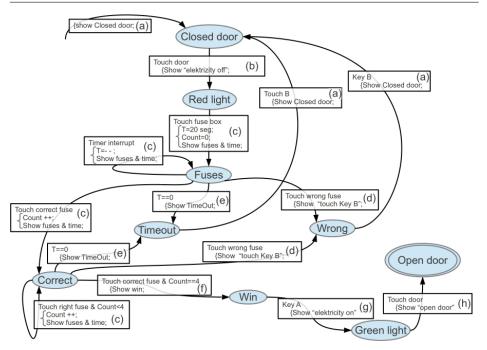

| 5.6  | State machine for the " <i>Elevator door</i> " minigame devel-<br>oped for the NDS during the school year 2012-2013.                                                                                                                                                                               |    |

|      | Letters in transitions are links for screen-shots in Figure 5.7                                                                                                                                                                                                                                    | 74 |

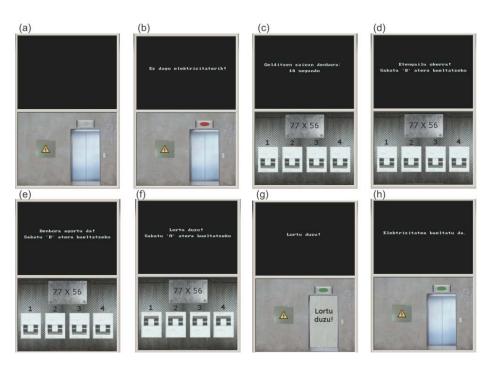

| 5.7  | Adapted state machine the "Elevator door" minigame                                                                                                                                                                                                                                                 |    |

|      | developed for the NDS during the school year 2012-2013.                                                                                                                                                                                                                                            | 75 |

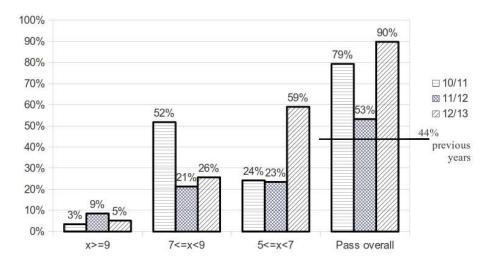

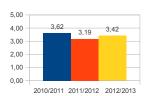

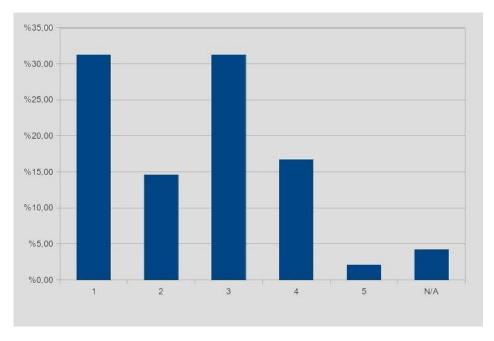

| 6.1  | Grades obtained by the students in the I/O subsystem topic                                                                                                                                                                                                                                         | 78 |

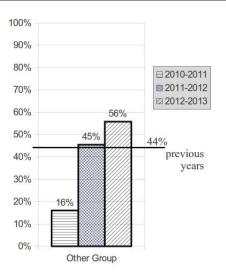

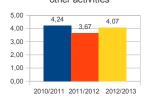

| 6.2  | Pass rates obtained in the I/O topic in the parallel group                                                                                                                                                                                                                                         | 79 |

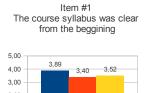

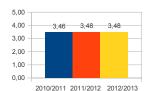

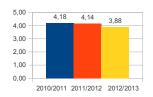

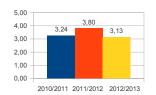

| 6.3  | Satisfaction questionnaire, charts for items $1 - 6 \dots$                                                                                                                                                                                                                                         | 81 |

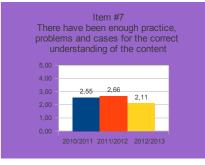

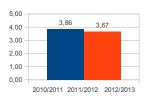

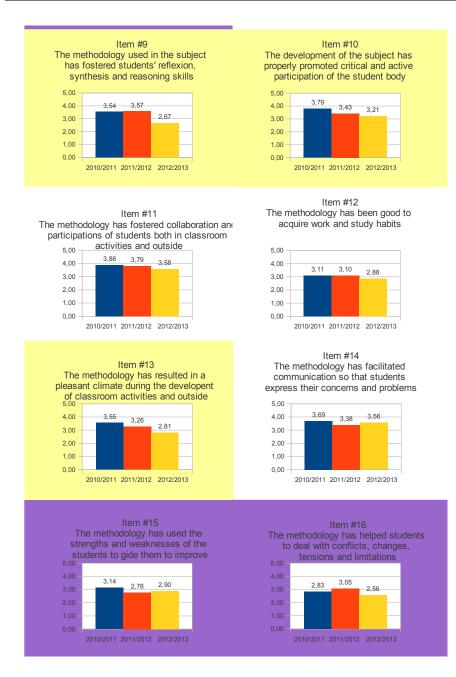

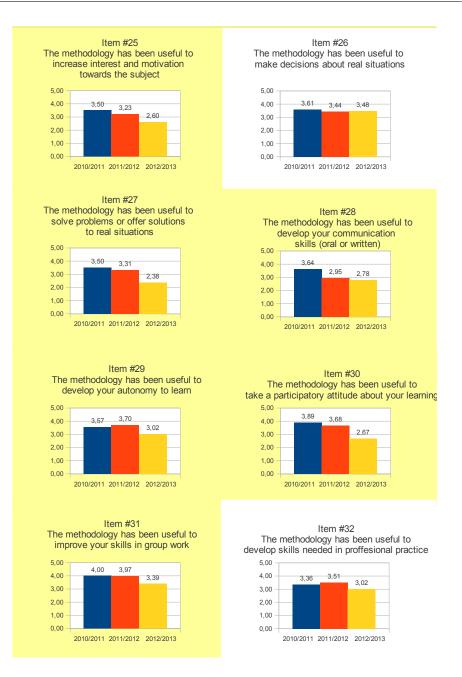

| 6.4  | Satisfaction questionnaire, charts for items $7 - 12 \dots$                                                                                                                                                                                                                                        | 82 |

| 6.5  | Satisfaction questionnaire, charts for items 13 – 18                                                                                                                                                                                                                                               | 83 |

| 6.6  | Satisfaction questionnaire, charts for items 19 – 24                                                                                                                                                                                                                                               | 84 |

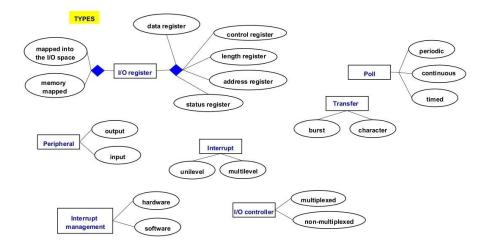

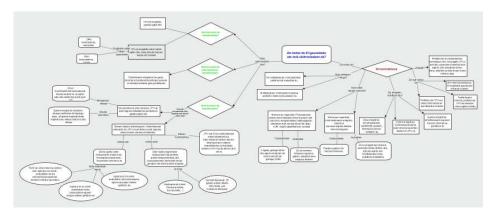

| 7.1  | Classification of I/O subsystem concepts                                                                                                                                                                                                                                                           | 95 |

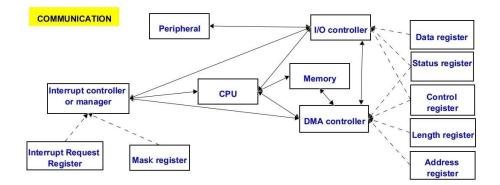

| 7.2  | Communication between the elements of the I/O subsystem                                                                                                                                                                                                                                            | 95 |

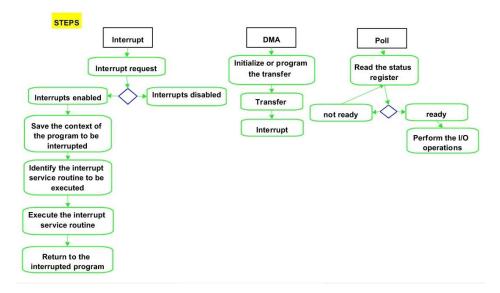

| 7.3  | Steps that must be followed while using different I/O                                                                                                                                                                                                                                              |    |

|      | techniques (polling, interrupt-driven I/O, and DMA)                                                                                                                                                                                                                                                | 96 |

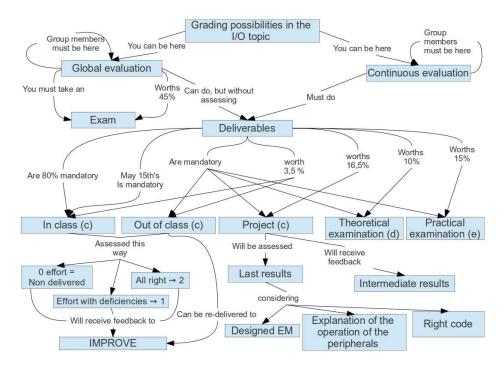

| 7.4  | Concept map handed out to the students to show the different evaluation options.                                   | 100   |

|------|--------------------------------------------------------------------------------------------------------------------|-------|

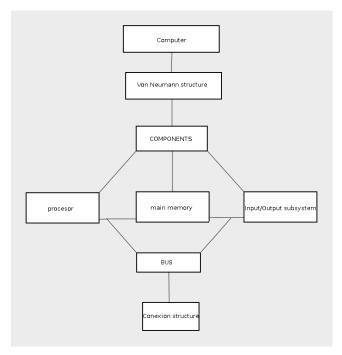

| 7.5  | A student's concept map to answer the question "What is<br>the Von Neumann structure", without any linking phrase. |       |

|      | Translated into English from the original in Basque                                                                | 101   |

| 7.6  | A student's trial concept map to answer the question                                                               |       |

|      | "What is the Von Neumann structure" that turned out to                                                             |       |

|      | be a block diagram. Translated into English from the                                                               |       |

|      | original in Basque.                                                                                                | 102   |

| 7.7  | Although impossible to read, this is a good example of                                                             |       |

|      | schema that looks like a concept map                                                                               | 102   |

| 7.8  | Answers to the question "Was concept mapping helpful                                                               |       |

|      | in your learning process?" in a Likert scale                                                                       | 104   |

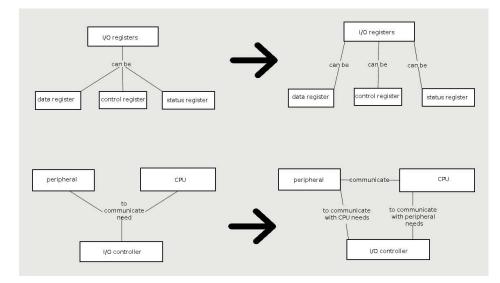

| 7.9  | Conversions needed to adapt the concept maps for social                                                            |       |

|      | network analysis.                                                                                                  | 105   |

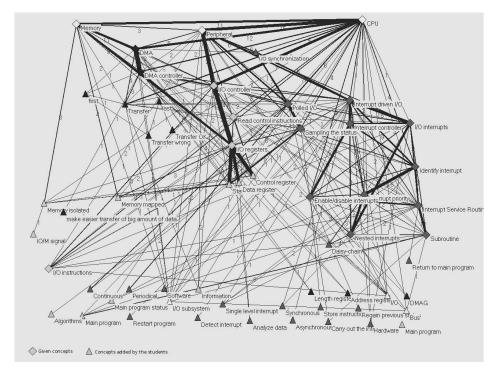

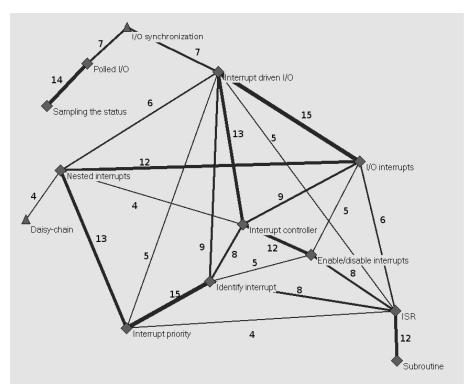

| 7.10 | Graph showing all the relationships of the students' con-                                                          |       |

|      | cept maps.                                                                                                         | 106   |

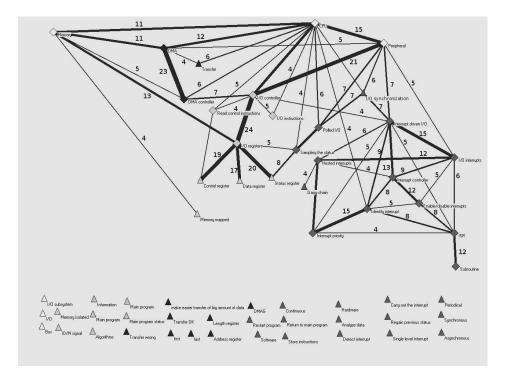

| 7.11 | Graph showing the concept map links used by more than                                                              |       |

|      | three students                                                                                                     | 107   |

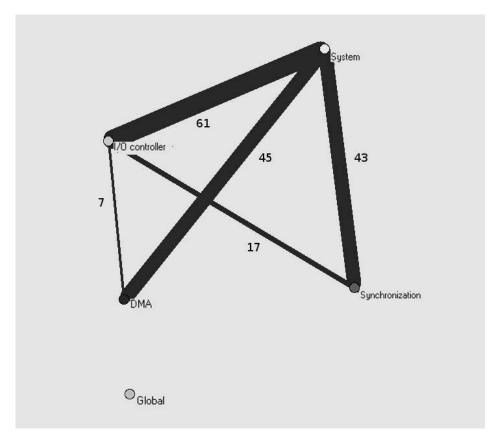

|      | Graph showing the links between subtopics                                                                          | 108   |

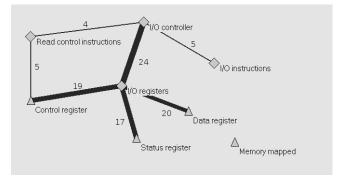

|      | Graph showing the links inside the I/O controller subtopic                                                         |       |

|      | Graph showing the links inside the synchronization subtopic                                                        | c.111 |

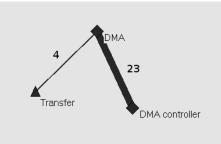

| 7.15 | Graph showing the links inside the DMA subtopic                                                                    | 112   |

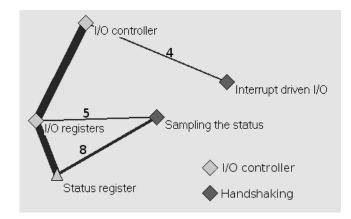

| 7.16 | Graph showing the links between the I/O controller and                                                             |       |

|      | the synchronization subtopics.                                                                                     | 112   |

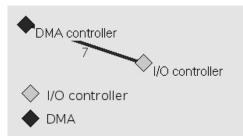

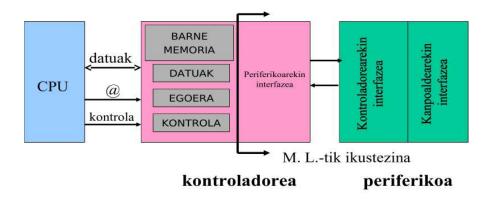

| 7.17 | Graph showing the links between the I/O controller and                                                             |       |

|      | the DMA subtopics                                                                                                  | 113   |

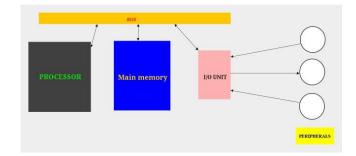

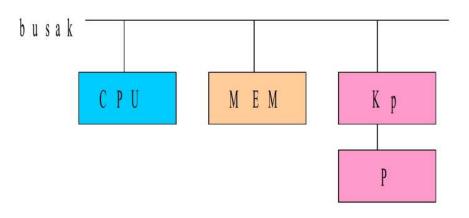

| A.1  | Sistemaren itxura periferikoaren kontrolagailua txertatu                                                           |       |

|      | ondoren.                                                                                                           | 144   |

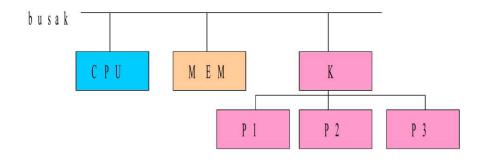

| A.2  | Sistemaren itxura periferikoaren kontrolagailua txertatu                                                           |       |

|      | ondoren.                                                                                                           | 145   |

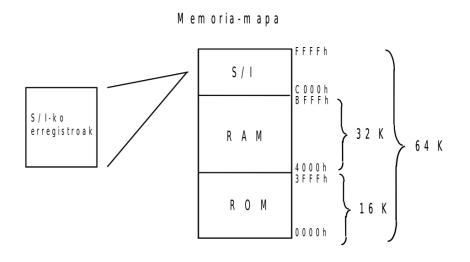

| A.3  | Memorian mapeatutako S/I erakusten duen memoria-                                                                   |       |

|      | mapa                                                                                                               | 147   |

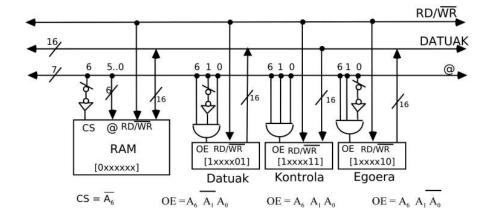

| A.4  | Erregistroen konexioaren eskema memorian mapeatuta                                                                 |       |

|      | daudenean                                                                                                          | 148   |

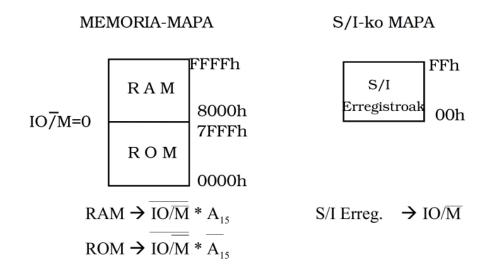

| A.5  | S/I bereiztua duen sistema baten memoria-mapa                                                                      | 149   |

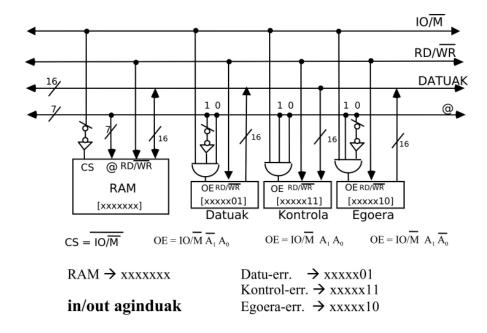

| A.6  | Erregistroen konexioaren eskema hauek ez daudenean        |       |

|------|-----------------------------------------------------------|-------|

|      | memorian mapeatuta                                        | 151   |

| A.7  | Kontrolagailu ez-multiplexatua erakusten duen eskema.     | 152   |

| A.8  | Kontrolagailu multiplexatua erakusten duen eskema         | 153   |

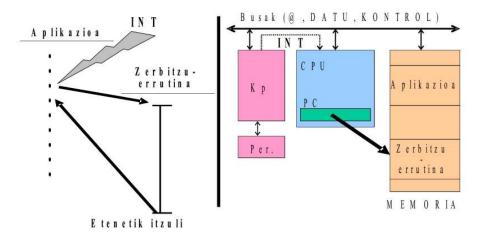

| A.9  | Etenei erantzuteko mekanismoaren eskema                   | 159   |

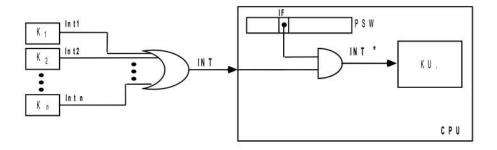

| A.10 | Eten-seinale bakarra dagoen kasurako hardware eskema      | 160   |

| A.11 | Eten-seinale bat baino gehiago dagoen kasurako hard-      |       |

|      | ware eskema                                               | 161   |

| A.12 | Kontrolagailuaren identifikazioa egiten duen hardwarearen |       |

|      | eskema                                                    | 163   |

|      | Margarita-katearen hardware eskema                        | 164   |

| A.14 | Daisy-chain hardwarea maila-anitzeko etenak jasateko      |       |

|      | aldaketekin                                               | 165   |

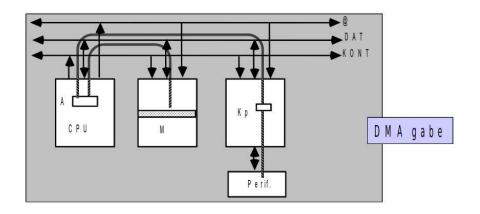

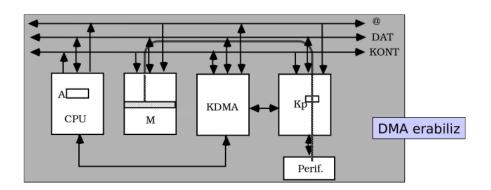

|      | Memoriako atzipena DMA gabe                               | 167   |

|      | Memoriako atzipena DMA erabiliz                           | 167   |

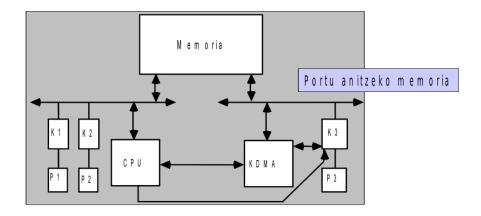

|      | Portu anitzeko memoria                                    | 168   |

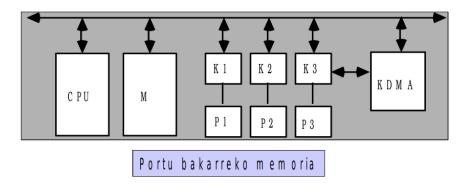

| A.18 | Portu bakarreko memoria                                   | 169   |

| A.19 | DMA kontrolagailuaren erregistroak                        | 171   |

| A.20 | DMA kontrolagailuaren funtzionamendua                     | 172   |

| B.1  | NDSaren hardwarearen eskema                               | 177   |

| B.2  | Pantaila grafikoak VRAM bankuetan mapeatzearen adibidea   | a.180 |

| B.3  | Sprite-n memoria hasieratzeko kodea                       | 181   |

| B.4  | Sprite-n koloreen paleta nola definitzen den ikusteko     |       |

|      | adibidea                                                  | 181   |

| B.5  | Sprite baten errepresentazioa osokoen bektore baten bidez | .182  |

| B.6  | Sprite baten pixelak spriten memoriara kopiatzen dituen   |       |

|      | adibidea                                                  | 182   |

| B.7  | Ukimen pantailaren kontrola inkesta bidez                 | 183   |

| B.8  | NDSaren teklak                                            | 184   |

| B.9  | Teklatuaren erregistroen helbideen definizioa             | 184   |

|      | Tenporizadorearen erregistroen helbideen definizioa       | 186   |

| B.11 | Zein baliotatik hasi behar den kontatzen eta zein maizta- |       |

|      | sunekin kontatu behar den kalkulatzeko formula            | 187   |

|      | Etenen kudeaketarako erregistroen definizioa              | 189   |

| B.13 | NDSaren eten-taula                                        | 191   |

| C.1  | The main program of one project. Code continues            | 197 |

|------|------------------------------------------------------------|-----|

| C.1  | The main program of one project. Code continued and        |     |

|      | continues                                                  | 198 |

| C.1  | The main program of one project. Code continued and        |     |

|      | continues                                                  | 199 |

| C.1  | The main program of one project. Code continued and        |     |

|      | continues                                                  | 200 |

| C.1  | The main program of one project. Code continued            | 201 |

| C.2  | Code to define the interrupt-table                         | 201 |

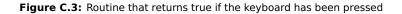

| C.3  | Routine that returns true if the keyboard has been pressed |     |

| C.4  | Routine that returns which key has been pressed            | 202 |

| C.5  | Routine that polls the keyboard and returns the pressed    |     |

|      | key                                                        | 203 |

| C.6  | Routine to enable keyboard interrupts                      | 203 |

| C.7  | Routine to disable keyboard interrupts                     | 203 |

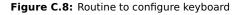

| C.8  | Routine to configure keyboard                              | 204 |

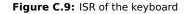

| C.9  | ISR of the keyboard                                        | 204 |

|      | Routine to enable timer interrupts                         | 204 |

| C.11 | Routine to disable timer interrupts                        | 205 |

|      | Routine to start timer                                     | 205 |

|      | Routine to stop timer                                      | 205 |

|      | Routine to configure timer                                 | 205 |

| C.15 | ISR of the timer                                           | 206 |

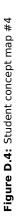

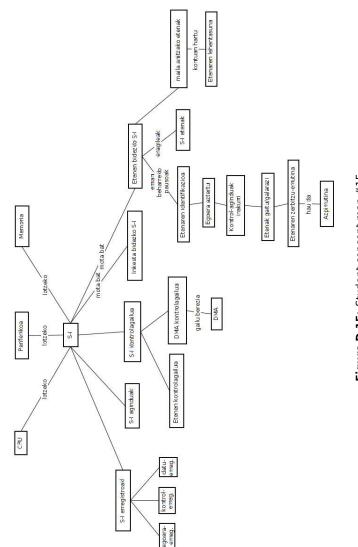

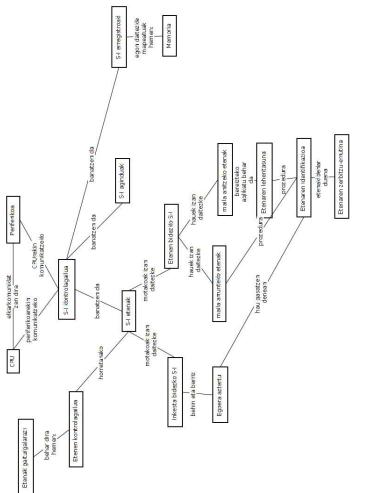

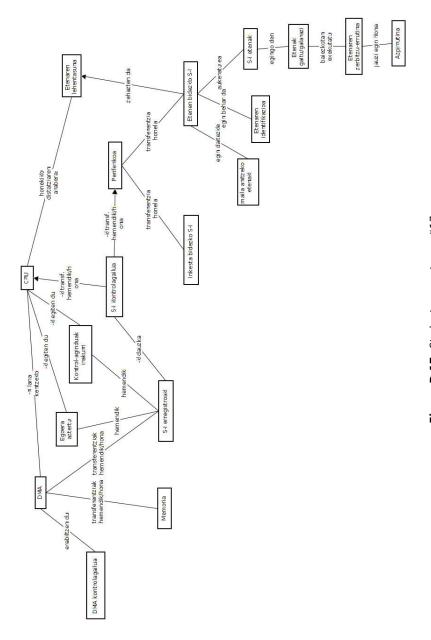

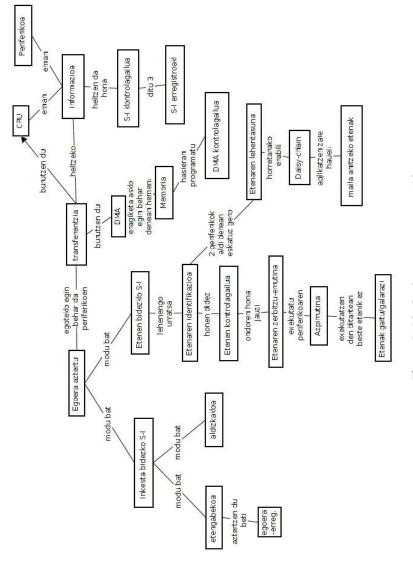

| D.1  | Student concept map #1                                     | 208 |

| D.2  | Student concept map #2                                     | 209 |

| D.3  | Student concept map #3                                     | 210 |

| D.4  | Student concept map #4                                     | 211 |

| D.5  | Student concept map #5                                     | 212 |

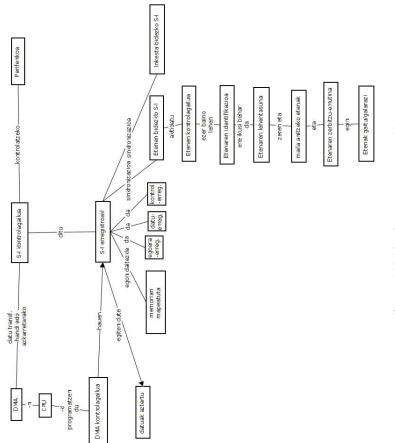

| D.6  | Student concept map #6                                     | 213 |

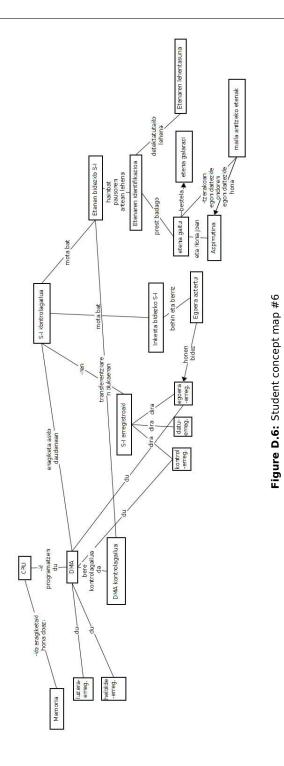

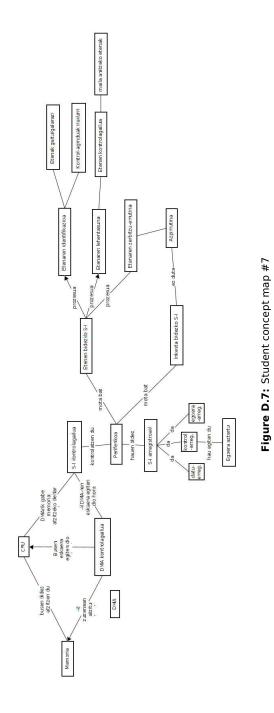

| D.7  | Student concept map #7                                     | 214 |

| D.8  | Student concept map #8                                     | 215 |

|      | Student concept map #9                                     | 216 |

| D.10 | Student concept map #10                                    | 217 |

|      | Student concept map #11                                    | 218 |

| D.12 | Student concept map #12                                    | 219 |

| D.13 | Student concept map #13                                    | 220 |

| D.14 Student concept map #14 | 221 |

|------------------------------|-----|

| D.15 Student concept map #15 | 222 |

| D.16 Student concept map #16 | 223 |

| D.17 Student concept map #17 | 224 |

| D.18 Student concept map #18 | 225 |

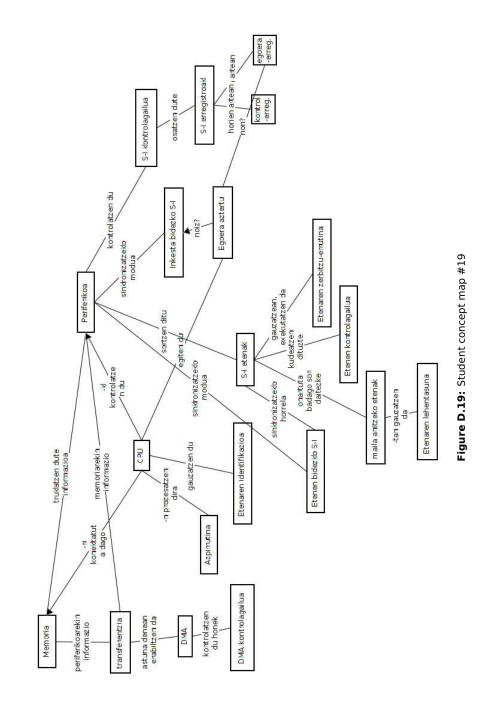

| D.19 Student concept map #19 | 226 |

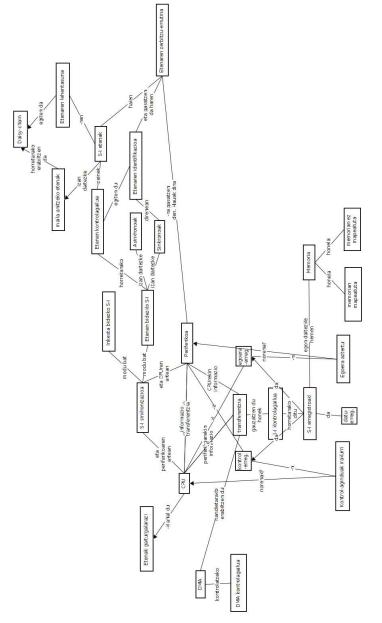

| D.20 Student concept map #20 | 227 |

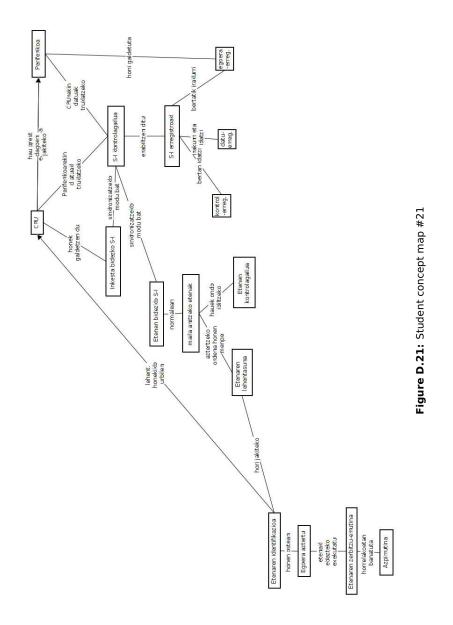

| D.21 Student concept map #21 | 228 |

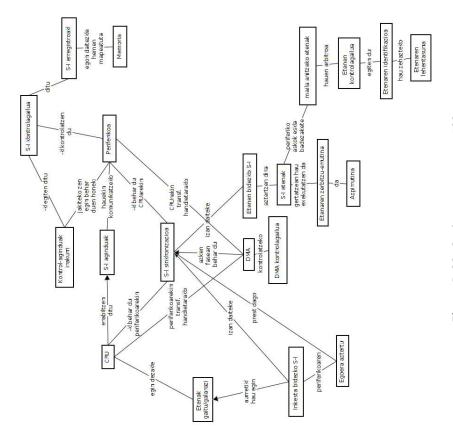

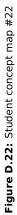

| D.22 Student concept map #22 | 229 |

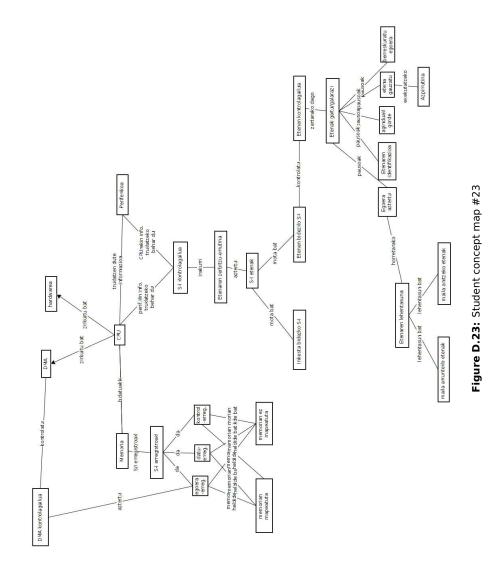

| D.23 Student concept map #23 | 230 |

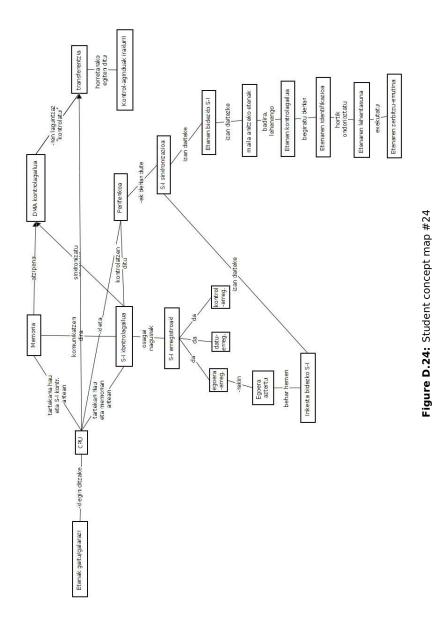

| D.24 Student concept map #24 | 231 |

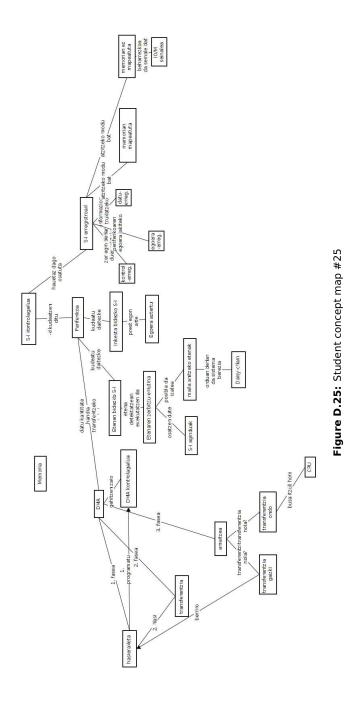

| D.25 Student concept map #25 | 232 |

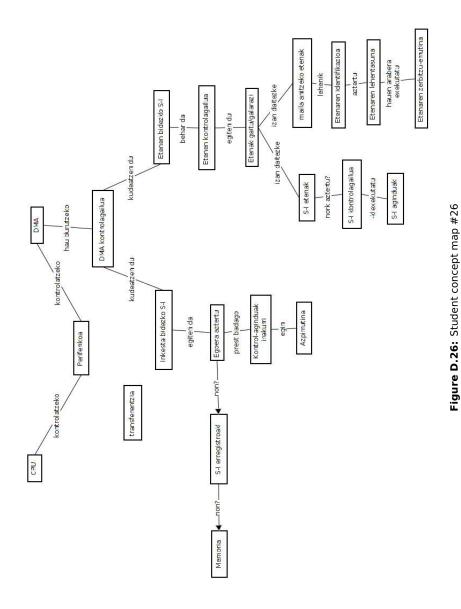

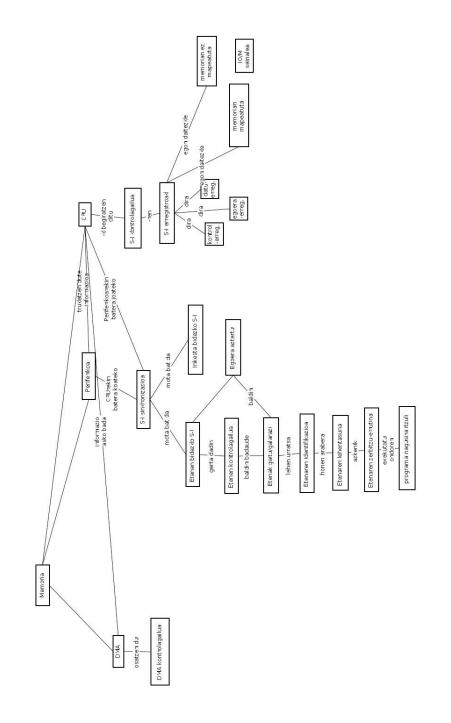

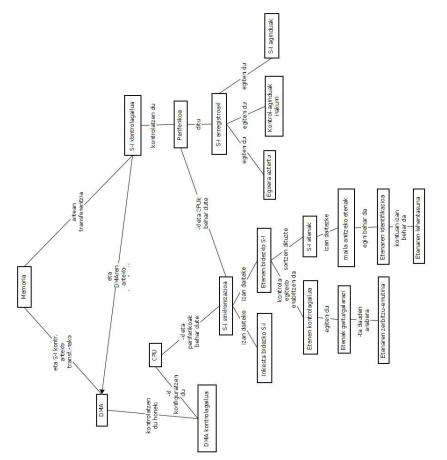

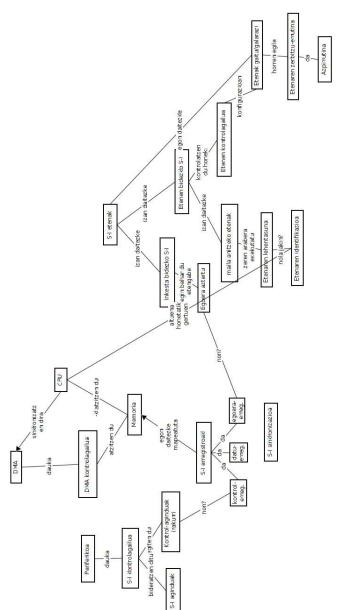

| D.26 Student concept map #26 | 233 |

| D.27 Student concept map #27 | 234 |

| D.28 Student concept map #28 | 235 |

| D.29 Student concept map #29 | 236 |

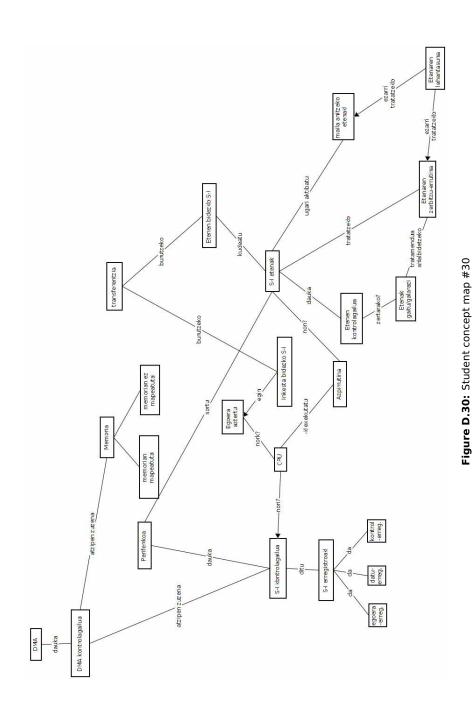

| D.30 Student concept map #30 | 237 |

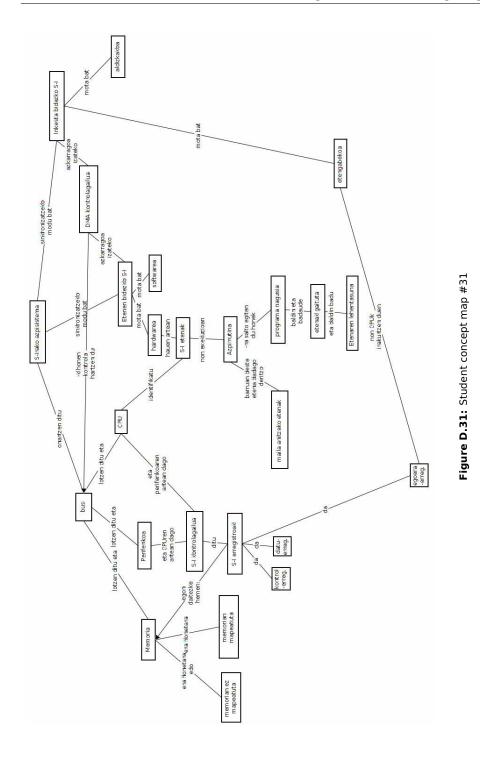

| D.31 Student concept map #31 | 238 |

| D.32 Student concept map #32 | 239 |

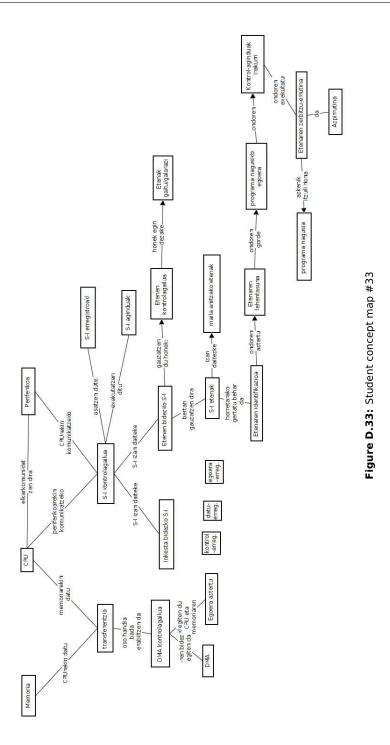

| D.33 Student concept map #33 | 240 |

# List of Tables

| 3.1 | Universities, courses, the approach they follow, and the<br>book from our list that they use (PatHen refers to [Pat-<br>terson and Hennessy, 2009]; Others means that the text-<br>books they use are not in our list; No textbook means<br>that the syllabus specifies that there is no textbook to |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | be followed; Not found means we have not found in the syllabus the textbook they follow.)                                                                                                                                                                                                            | 25 |

| 3.2 | Where in each book appear the topics and learning out-<br>comes of CC2013                                                                                                                                                                                                                            | 29 |

| 3.3 | Where in each book appears the topics and learning                                                                                                                                                                                                                                                   |    |

|     | outcomes of CC2004                                                                                                                                                                                                                                                                                   | 30 |

| 3.4 | Approach followed by each textbook                                                                                                                                                                                                                                                                   | 32 |

| 3.5 | How the I/O topic is taught in several Spanish universities                                                                                                                                                                                                                                          | 38 |

| 4.1 | Explanation of the bits in the control register of the timer                                                                                                                                                                                                                                         | 51 |

| 4.2 | Explanation of the bits in the control register of the key-<br>board. Bit 0 to 9 are the same in the data register                                                                                                                                                                                   | 52 |

| 6.1 | Items of the new questions in the questionnaire with their average responses (Likert scale [1–5])                                                                                                                                                                                                    | 85 |

| 6.2 | Students following and finishing in the PBL methodology                                                                                                                                                                                                                                              | 89 |

| 7.1 | Students' concept classification relations                                                                                                                                                                                                                                                           | 97 |

| 7.2 | Communication relations from the point of view of the students                                                                                                                                                                                                                                       | 97 |

| 7.3 | <i>Is_part_of</i> relations from the point of view of the students                                                                                                                                                                                                                                   | 98 |

|     |                                                                                                                                                                                                                                                                                                      |    |

| 7.4 | Order the students gave to the steps of an interrupt, a poll and a DMA transfer | 98   |

|-----|---------------------------------------------------------------------------------|------|

| 75  | The 20 concepts given to the students to build the last                         | 70   |

| 7.0 | concept map                                                                     | 103  |

| B.1 | VRAM memoriako bankuak eta beraien erabilera posibleak                          | .180 |

| B.2 | Teklatuaren kontrol erregitroaren biten erabilera                               | 185  |

| B.3 | Tenporizadoreen kontrol-erregistroaren biten erabilera.                         | 186  |

| B.4 | eten-lerroen identifikazio eta definizioa                                       | 190  |

# CHAPTER 1

# Introduction

$T^{\rm HIS}$  dissertation is all about the educational process of the computer I/O subsystem. Therefore it is important to have at least a rough idea of the topic itself, the reasons why it is important to teach the computer I/O subsystem to computer scientists and engineers, and what does the computing curricula say about the computer I/O subsystem.

Next, in this chapter some changes which took place at the University of the Basque Country (UPV/EHU) will be introduced, then the research questions proposed for the dissertation will be outlined, and finally, the organization of the document will be summarized.

#### 1.1 The computer I/O subsystem - What is it?

As Stallings [2012] defines, "The computer system's I/O architecture (or subsystem) is its interface to the outside world". "I/O subsystem architecture deals with the organization of concurrent processing activities within the devices, controllers, channels, and I/O processors that comprise an I/O subsystem. In addition, it deals with the coordination of I/O subsystem processing activity as a whole with respect to the activity of the central processor", say Buzen [1975]. A computer can not do anything without data from the outside world, and serves to nothing if it can not bring the results of its computations to the outside world.

The aim of the I/O subsystem, as an undergraduate introductory topic is to teach the basics of the communication between the computer system and the I/O architecture or subsystem, in order to reach the outside world.

It is very easy to see how a mechanical typewriter converts a key press into a letter in the paper, but most computer users will not be able to say which actions happen between the moment a person presses a key in a computer keyboard and the moment the letter appears in the display.

# 1.2 Why is it important to teach the computer I/O subsystem to computer scientist and engineers?

The I/O subsystem is one of the main parts of a computer system together with the CPU, the memory unit, and the buses which have the responsibility of linking all the three units, CPU, memory and I/O subsystem. The techniques used to synchronize the I/O subsystem with the CPU and memory, and the correct functioning of it can highly influence the performance of the computer. The ACM/IEEE-CS joint task force [CC2004] points out that: *"students must understand how various peripheral devices interact with, and how they are interfaced to a CPU"*.

The use of interrupts to synchronize the I/O subsystem with the CPU opens the door to introduce students to concepts such as multiprogramming and concurrency in the execution of the programs that run in computing systems.

This type of execution will increase the performance of the computer systems with respect to monoprogramming and synchronization via polling.

On the other hand, I/O subsystem can be considered as it forms the lowest level in Human Computer Interaction (HCI). When designing interfaces based on non-standard devices (those which are not the classical keyboard, screen and mouse), developers have to know other I/O devices and their characteristics [Garay-Vitoria, 2006].

1.3: What do the computing curricula recommendations say about the I/O subsystem topic? 3

The use of microprocessors is becoming ubiquitous. "Almost every electronic appliance and device today uses embedded systems. Cell phones, automobiles, toasters, televisions, airplanes, medical equipment, and a host of other devices, products, and applications use embedded systems" [CC2004]. In these embedded systems, the Input/Output (I/O) subsystem takes usually a considerable role. "The various I/O techniques are essential to software developers designing operating systems, network software, database systems, embedded systems, process control systems, and real-time systems" [Krishnaprasad, 2002]. However, lecturers in these embedded systems courses feel that in previous courses the I/O subsystem is not treated sufficiently: "Today's computer architecture courses spend more time on instruction set design and pipelining and less time on topics like I/O. As a result, before getting to the significant examples in embedded computing, a course must first cover some basic principles and techniques that have not been learned in other courses" [Wolf and Madsen, 2000].

# 1.3 What do the computing curricula recommendations say about the I/O subsystem topic?

The ACM/IEEE-CS Joint Task Force has been developing curriculum recommendations for the different and emerging computing disciplines since the 1960s. They developed a volume for Computer Science (CS) in 2001 [CC2001], a revision of it in 2008 [CC2008], and a new draft was published in February 2013 [CC2013].

The curricula for CS say that: "The computer lies at the heart of computing. Without it most of the computing disciplines today would be a branch of theoretical mathematics. To be a professional in any field of computing today, one should not regard the computer as just a black box that executes programs by magic. All students of computing should acquire some understanding and appreciation of a computer system's functional components, their characteristics, their performance, and their interactions." [CC2001; CC2008]. Moreover, the ACM/IEEE-CS joint task force's curriculum for Computer Engineering (CE) [CC2004] remarks that: "Computer architecture is a key component of computer engineering and the practising computer engineer should have a practical understanding of this topic. It is concerned with all aspects of the design and organization of the central processing unit and the integration of the CPU into the computer system itself.". But, Computer Architecture (CA) is a very wide area covering topics such as: Digital logic and digital systems, Machine level representation of data, Assembly level machine organization, Memory system organization and architecture, Interfacing and communication, Functional organization, Multiprocessing and alternative architectures, Performance enhancements, Architecture for networks and distributed systems, and much more. The subject that this curricula recommendations devote to the I/O topic is called "Interfacing and communication" [CC2001; CC2013] or "Interfacing and I/O Strategies" [CC2008].

In [CC2008] the ACM/IEEE-CS Joint Task Force tried a change, but since in the [CC2013] draft the subject comes back to be the same as in [CC2001], we will not consider here the [CC2008] proposal. The [CC2013] proposal has the same topics and learning outcomes as [CC2001], but with a little more detail. It devotes a minimum coverage time of 2 hours and states as follows:

"Topics:

- I/O fundamentals: handshaking, buffering, programmed I/O, interruptdriven I/O

- Interrupt structures: vectored and prioritized, interrupt acknowledgement

- External storage, physical organization, and drives

- Buses: bus protocols, arbitration, direct-memory access (DMA)

- Introduction to networks: networks as another layer of access hierarchy

- Multimedia support

- RAID architectures"

"Learning outcomes:

- 1. Explain how interrupts are used to implement I/O control and data transfers [Knowledge].

- 2. Identify various types of buses in a computer system [Knowledge].

- 3. Describe data access from a magnetic disk drive [Knowledge].

- 4. Compare common network organizations, such as ethernet/bus, ring, switched vs. routed [Knowledge].

*1.3: What do the computing curricula recommendations say about the I/O subsystem topic?* 5

- 5. Identify interfaces needed for multimedia support, from storage, through network, to memory and display [Knowledge].

- 6. Describe the advantages and limitations of RAID architectures [Knowledge]."

In 2004 the ACM/IEEE-CS Joint Task Force developed a curriculum for CE [CC2004]. It devotes a minimum coverage time of 10 hours and the differences with the CS curriculum can be seen in the topics and learning outcomes as follows:

"Topics:

- *I/O fundamentals: handshaking, buffering,*

- I/O techniques: programmed I/O, interrupt-driven I/O, DMA

- Interrupt structures: vectored and prioritized, interrupt overhead, interrupts and reentrant code

- Memory system design and interfacing

- Buses: bus protocols, local and geographic arbitration"

*"Learning outcomes:*

- 1. Explain how to use interrupts to implement I/O control and data transfers.

- 2. Write small interrupt service routines and I/O drivers using assembly language.

- 3. Identify various types of buses in a computer system.

- 4. Describe data access from a magnetic disk drive.

- 5. Analyze and implement interfaces."

As it can be seen, the major difference is that while the CS curriculum [CC2013] stays at the knowledge level, the CE curriculum [CC2004] demands as learning outcomes the ability to write small Interrupt Service Routine (ISR) and I/O drivers, and the ability to analyse and implement interfaces.

# 1.4 The computer I/O subsystem topic at the University of the Basque Country (UPV/EHU)

At the UPV/EHU the subject called "*Computer Architecture 1*" was taught in the third semester out of the ten semesters of the studies in Computer Engineering. This subject comprised the central processing unit (CPU) (the control unit and the arithmetic-logic unit), the memory organization, the computer I/O subsystem, and the interconnection buses, a detailed introduction to the Von Neumann architecture. The "*Computer Architecture 1*" subject concerned the lecturers because of its high dropout rates (31%) and low pass rates (50% out of the taken exams, 34% out of the enrolment). A problem area was detected in the course of the years: the computer I/O subsystem. Students drastically left the subject during the teaching of the computer I/O subsystem. Moreover, the 50% pass rate previously mentioned droped to 44% considering only the computer I/O subsystem part of the exam.

Due to the adoption of the European Higher Education Area (EHEA), the computing degree taught at the UPV/EHU has recently undergone several changes. Now the degree in Computer Engineering is eight semesters long. The "Computer Architecture 1" subject has disappeared, and the computer I/O subsystem has moved from a third semester subject "Computer Architecture 1" to a second semester subject "Computer Structure" (CSt to make it different from Computer Science (CS)). In this subject, the computer I/O subsystem shares centre stage with assembly language and low-level programming. At that point, the concern of the lecturers towards the computer I/O subsystem topic increased since the difficulty in understanding a topic would be greater in the first year.

A change was needed, and the aim of this dissertation is to report the changes made, the data obtained empirically, and the methods implemented in order to be able to know the real learning outcomes of the topic.

## 1.5 Research questions

In this chapter, the research questions that are going to be answered in the course of the dissertation are going to be expressed.

Q1: How well can a handheld game console be adapted to the teaching needs of the I/O subsystem topic?

Q2: How well can a PBL methodology help in the learning process of the I/O subsystem topic?

Q3: How do students understand the I/O subsystem topic?

### 1.6 Organization of the Document

**Chapter 1.** In the first chapter we offer some hints about general concepts of the computer I/O subsystem.