# Electrical Characterization and Modeling of Pulse-based Forming Techniques in RRAM Arrays

Alessandro Grossi<sup>1,\*</sup>, Cristian Zambelli<sup>1</sup>, Piero Olivo<sup>1</sup>, Enrique Miranda<sup>2</sup>, Valeriy Stikanov<sup>3</sup>, Christian Walczyk<sup>4</sup>, Christian Wenger<sup>4</sup>

Università degli Studi di Ferrara, Dip. di Ingegneria, Via Saragat 1, Ferrara, 44122, Italy

#### Abstract

The forming process, which corresponds to the activation of the switching filament in Resistive Random Access Memory (RRAM) arrays, has a strong impact on the cells' performances. In this paper we characterize and compare different pulse forming techniques in terms of forming time, yield and cell-to-cell variability on 4 kbits RRAM arrays. Moreover, post-forming modeling during Reset operation of correctly working and over formed cells has been performed. An incremental form and verify technique, based on a sequence of trapezoidal waveforms with increasing voltages followed by a verify operation that terminates when the expected switching behavior has been achieved, showed the best results. This procedure narrows the post-forming current distribution whereas reducing the reset switching voltage and the operative current. These advantages materialize in a better control of the cell-to-cell variability and in an overall time and energy saving at the system level.

Keywords: RRAM array, forming, read window, energy saving

#### 1. Introduction

Resistive Random Access Memories (RRAM) gathered increasing interest in the last few years [1]. However, an intensive research activity is still to be performed on this innovative technology in order to increase RRAM reliability and performance. After the concept validation on single cells [2, 3, 4], the characterization of array structures is mandatory to bring such technology to a maturity level [5]. RRAM behavior is based on the possibility of electrically modifying the conductance of a Metal-Insulator-Metal (MIM) stack: the Set operation moves the cell in a low resistive state (LRS), whereas Reset brings the cell back to a high resistive state (HRS). To activate such a switching behavior, some technologies require a preliminary forming operation [6, 7, 8, 9]. Even if forming process is performed just once, this initial state plays a fundamental role in determining the subsequent array and system performance [10]. The effectiveness of the forming process depends on its ability in creating homogeneous conductive conditions among the cells thus easing successive Set/Reset operations. Standard forming is performed by applying either a voltage ramp or a voltage/current pulse to each cell individually [7]. The former method has a major drawback due to the filament conductance

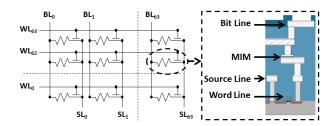

Figure 1: Schematic of the 4 kbits arrays characterized in this work and structure of a RRAM cell.

control being not tight enough. This results in larger cell-to-cell variability and larger disturb sensitivity [7, 11].

As an alternative, forming process can be performed through a sequence of pulses featuring the same voltage. While the forming time can be minimized using a single pulse with high compliance and voltage parameters, the forming yield is limited since the applied energy is not sufficient to complete the forming process in all cells [5]. Several pulse-based forming alternatives have been proposed to increase the applied energy and therefore the yield by using long pulses or sequences of short pulses at constant voltage [7].

In this paper different pulse-based forming techniques are compared in terms of forming time, yield and cell-to-cell variability on 4 kbits RRAM arrays. Considering the peculiarity of each cell in terms of the switching behavior activation, it is shown that a tight control of the forming process allows taking profit on a long term basis during the successive Set/Reset operations [12, 13]. Among all the investigated techniques, the best results have been obtained through a form and verify procedure, already proposed for Set/Reset operation [12], although form-

<sup>\*</sup>Corresponding author

Email address: alessandro.grossi@unife.it (Alessandro Grossi)

<sup>&</sup>lt;sup>1</sup>Università degli Studi di Ferrara, Dip. di Ingegneria, Via Saragat 1, Ferrara, 44122, Italy

<sup>&</sup>lt;sup>2</sup>Departament d'Enginyeria Electrónica, Universitat Autónoma de Barcelona, Campus UAB, Cerdanyola del Valles, 08193 Barcelona, Spain

<sup>&</sup>lt;sup>3</sup>IASA, 37 Prospect Peremogy, 03056 Kiev, Ukraine

<sup>&</sup>lt;sup>4</sup>IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

ing performance of such technique have not been evaluated yet. Such method, hereafter referred to as Incremental Form and Verify (IFV) leverages on the application, to any single cell, of a sequence of trapezoidal waveforms with increasing maximum voltages, each step being followed by a current read operation that monitor the cell resistance. When a cell reaches a predefined read current value after the pulse application the procedure is interrupted, so that all cells are brought into a comparable electrical condition. In fact, even if the cell requires longer forming time, IFV offers a superior advantage by significantly reducing the cumulative number of Set/Reset pulses during cycling and, consequently, the overall power consumption of the memory peripheral circuitry. After-forming modeling of Reset I-V operations has been performed through Quantum-Point Contact (QPC) model [14], showing that if a too high conductance is reached during forming the filament became hard to disrupt in the successive Reset operation, resulting in faulty behavior [11, 15]. Moreover, it is shown that thanks to the verify procedure implemented during forming such faulty behavior can be avoided.

# 2. Memory architecture

The architecture of the 4 kbits arrays and the structure of RRAM cell characterized in this work are depicted in Fig.1. The memory cells consist in a select NMOS transistor manufactured in  $0.25~\mu m$  BiCMOS technology, which also sets the current compliance, whose drain is in series to a variable resistor (i.e., the resistive switching element) connected to the bitlines. The variable resistor is a MIM stack constituted by: 150~nm TiN top and bottom electrode layers deposited by magnetron sputtering, a 10~nm metallic Ti layer acting as oxygen exchange layer, and a 9~nm HfO<sub>2</sub> AVD-deposited layer [5]. The resistor area is equal to  $1~\mu m^2$ .

### 3. Experimental setup

Tab. 1 summarizes the Forming, Set, Reset and Read parameters used in this work. Three different forming schemes have been characterized:

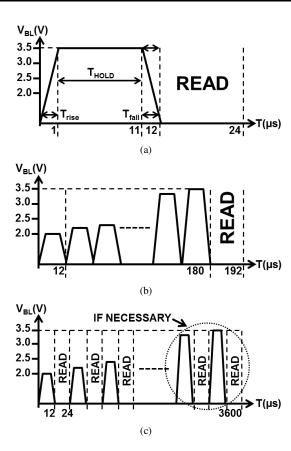

- a) Single pulse, denoted as *Pulse* in Fig. 2(a):  $V_{BL} = 3.5 \text{ V}$ ,  $V_{WL} = 1.4 \text{ V}$ , with pulse duration  $T_{pulse} = 10 \mu s$  and a finite  $t_{rise} = t_{fall} = 1\mu s$  to avoid overshoot effects [16].

- b) Incremental Form, denoted as *IF* in Fig. 2(b): the bitline voltage  $V_{BL}$  was increased with a sequence of increasing voltage pulses from 2 to 3.5 V with  $\Delta V_{BL}$  equal to 0.1 V, a wordline voltage  $V_{WL}$  of 1.4 V and  $T_{pulse} = 10 \ \mu s$ ,  $t_{rise} = t_{fall} = 1 \mu s$ .

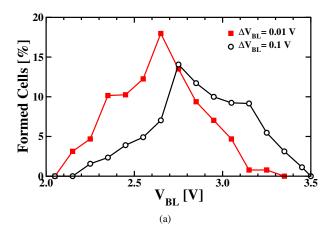

- c) Incremental Form and Verify (*IFV*), Fig. 2(c): pulses were applied with increasing  $V_{BL}$  from 2 V up to 3.5 V with two different  $\Delta V_{BL}$  equal to 0.1 V and 0.01 V, respectively,  $V_{WL} = 1.4$  V and  $T_{pulse} = 10~\mu s$ ,  $t_{rise} = t_{fall} = 1\mu s$ . After each forming pulse the cell read current  $I_{read}$  was measured: if  $I_{read} > 19~\mu A$  the forming process was interrupted and the cell marked as formed. Fig. 3 shows the distributions of the IFV forming voltages, confirming that the specific voltage conditions triggering the forming behavior are quite different for each cell within the array.

Table 1: Summary of Forming, Set, Reset and Read parameters.

| Operation                                     | $V_{BL}$ | $V_{SL}$ | $V_{WL}$ | $T_{pulse}$ |

|-----------------------------------------------|----------|----------|----------|-------------|

|                                               | [V]      | [V]      | [V]      | $[\mu s]$   |

| Pulse Form                                    | 3.5      | 0        | 1.4      | 10          |

| IF Form ( $\Delta V_{BL} = 0.1 \text{ V}$ )   | 2-3.5    | 0        | 1.4      | 10          |

| IFV Form ( $\Delta V_{BL} = 0.1 \text{ V}$ )  | 2-3.5    | 0        | 1.4      | 10          |

| IFV Form ( $\Delta V_{BL} = 0.01 \text{ V}$ ) | 2-3.5    | 0        | 1.4      | 10          |

| Set $(\Delta V_{BL} = 0.1 \text{ V})$         | 1.5-3.5  | 0        | 1.4      | 10          |

| Reset ( $\Delta V_{SL} = 0.1 \text{ V}$ )     | 0        | 1.5-3.5  | 2.8      | 10          |

| Read                                          | 0.2      | 0        | 1.4      | 10          |

Figure 2: Pulse (a), IF (b) and IFV (c) schemes.

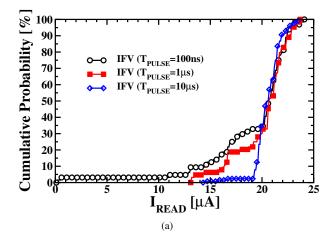

All the forming schemes considered in this paper base on pulse widths of  $10 \ \mu s$ . This is mainly due by two factors: performance/variability concerns, and technological limitations of the integrated array. Concerning the former factor, the authors have tried different pulse widths for IFV forming scheme using  $\Delta V_{BL} = 0.01$ V:  $100 \ ns$ ,  $1 \ \mu s$ , and  $10 \ \mu s$ . As shown in Fig. 4, the lower is the pulse width, the lower is the energy supplied to the cell for the forming operation, leading to poor forming yield and large inter-cell variability [17]. The trend of the results reported here applies also for IFV with larger  $\Delta V_{BL}$  and for IF, and Pulse scheme. From the technology viewpoint, it must be reminded that the developed 4kbits arrays feature a peripheral circuitry that drives and routes all the signals on the memory cells through large multiplexers and selectors that, along with the process-induced variability, limits the duration of pulse

Figure 3: Distributions of the forming voltages during *IFV* for the  $\Delta V_{BL} = 0.01$  V and  $\Delta V_{BL} = 0.1$  V cases.

Figure 4: Cumulative  $I_{read}$  distributions after IFV with  $\Delta V_{BL}=0.01$  V and different pulse widths.

width on a narrow range of values. However, the results shown in this paper and the experimental methodology, especially concerning the IFV scheme, apply without lack of generality to any optimized RRAM technologies, where shorter pulse widths can be adopted.

The cell current  $I_{read}$  was measured by applying  $V_{BL} = 0.2 \text{ V}$ ,  $V_{WL} = 1.4 \text{ V}$  and a read time  $T_{read} = 10 \,\mu\text{s}$ ,  $t_{rise} = t_{fall} = 1 \mu\text{s}$ . The Set/Reset operations were performed by using an Incremental Step Pulse algorithm [18, 19], by increasing  $V_{BL}$  from 1.5 V up to 3.5 V with  $\Delta V_{BL} = 0.1 \text{ V}$ ,  $V_{WL} = 1.4 \text{ V}$  and  $T_{pulse} = 10 \,\mu\text{s}$ ,  $t_{rise} = t_{fall} = 1 \mu\text{s}$  during Set and by increasing the sourceline voltage  $V_{SL}$  from 1.5 V up to 3.5 V with  $\Delta V_{SL} = 0.1 \text{ V}$ ,  $V_{WL} = 2.8 \text{ V}$  and  $T_{pulse} = 10 \,\mu\text{s}$ ,  $t_{rise} = t_{fall} = 1 \mu\text{s}$  during Reset. Forming, Set, Reset and Read pulse operations are performed by applying the  $V_{SL}$ ,  $V_{BL}$  and  $V_{WL}$  cell-by-cell, sequentially.

## 4. Forming Results

Cell forming time and yield obtained with each method are reported in Tab. 2. Forming yield is calculated as the cell percentage that shows a read verify current after forming  $I_{read} > 19$

Table 2: Forming Methods Timings and Yield.

|                                          | Time $[\mu s]$ Time $[\mu s]$ |            | Yield [ %] |

|------------------------------------------|-------------------------------|------------|------------|

|                                          | average                       | worst case |            |

| Pulse                                    | 12                            | 12         | 54         |

| IF $(\Delta V_{BL} = 0.1 \text{ V})$     | 180                           | 180        | 77         |

| IFV ( $\Delta V_{BL} = 0.1 \text{ V}$ )  | 216                           | 360        | 87         |

| IFV ( $\Delta V_{BL} = 0.01 \text{ V}$ ) | 1584                          | 3600       | 99         |

Table 3: Array average read currents and Inter-cell variability [17] after forming with different thresholds.

| Forming Threshold [μA] | Array average $I_{read} [\mu A]$ | Array inter-cell variability $[\mu A]$ |

|------------------------|----------------------------------|----------------------------------------|

| 19                     | 20.58                            | 1.26                                   |

| 20                     | 20.88                            | 1.77                                   |

$\mu$ A, ensuring the creation of a conductive filament. The choice of 19  $\mu$ A both as a read current threshold criterion to assess and claim the actual creation of a conductive filament during forming, and as a forming yield criterion is ascribed to stability and variability concerns that have been taken into account from previous results shown in literature [17, 20]. Concerning the stability, it is important to ensure that the creation process of the conductive filament in the HfO2 will be utmost homogeneous, and that the so formed filament would be easily disrupted in consecutive RESET operations. As demonstrated in [20], if it is not adopted a sufficiently high read current threshold, large oscillations during forming and unstable SET/RESET behavior may appear during the memory cell lifetime. In order to account for the intrinsic variability of the RRAM technology exploited in this work, it must be ensured also that the average  $I_{read}$  calculated on the entire array is in the range between 18  $\mu A$ and 24  $\mu$ A. Forming with read current threshold lower than 18  $\mu A$  generally produces unstable memory cells that will fail after few SET/RESET cycles [20], whereas forming with a threshold current higher than 20  $\mu$ A usually display larger array inter-cell variability, as indicated in the values provided in Table 3. IFV average and worst case time (i.e. requiring the highest number of pulses) are reported since IFV forming time is different from cell to cell. Even if Pulse forming is shown to be the fastest, the very low yield result confirms that the energy provided by this forming technique is insufficient for most of the memory cells in the array. For this reason this forming scheme will be no further considered in this paper. The highest forming yield is obtained using  $\Delta V_{BL} = 0.01 \text{ V}$  (about 99%), therefore only this IFV variant will be considered further on.

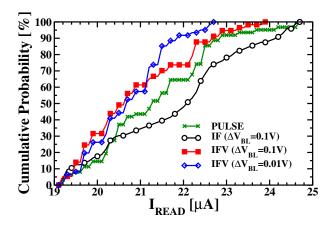

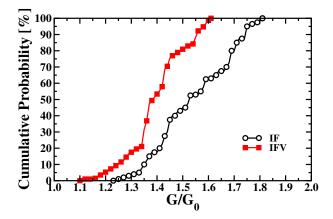

Fig. 5 shows  $I_{read}$  distributions of correctly formed cells (i.e. reaching the 19  $\mu$ A target) for all the schemes considered in this work. As it can be observed, the distributions related to the *IFV* scheme exhibit a lower dispersion of the current values, thus resulting in a better control of the cell-to-cell variability.

### 5. After-forming Set/Reset

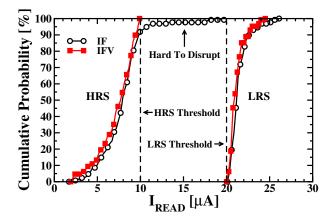

LRS and HRS read current cumulative distributions measured after the first Set and Reset operations are reported in

Figure 5: Cumulative  $I_{read}$  distributions of correctly formed cells after Pulse (54%), IF (77%), IFV with  $\Delta V_{BL} = 0.1$  V (87%) and IFV with  $\Delta V_{BL} = 0.01$  V (99%) forming operations.

Figure 6: IF and IFV cumulative  $I_{HRS}$  and  $I_{LRS}$  distributions measured at endurance cycle 1.

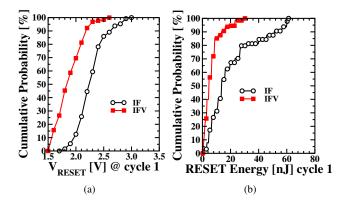

Figure 7: Cumulative distribution of the reset switching voltages (a) and overall Energy required to perform Reset operation (b) at Set/Reset cycle 1 for *IF* and *IFV* ( $\Delta V_{BL} = 0.01 \text{ V}$ ) forming schemes.

Fig. 6. It can be observed that Reset failed on some *IF* formed cells (denoted as *Hard to disrupt*) showing read current values above the HRS threshold fixed to  $I_{read} = 10 \,\mu\text{A}$ , whereas Reset operation has been correctly performed on all *IFV* formed cells.

Experimental results show that the IFV technique exhibits a lower Reset switching voltage and a reduced operation cur-

rent: Fig. 7 (a) show the cumulative distribution of the reset switching voltages measured on fresh devices for IF and IFV ( $\Delta V_{BL}=0.01~V$ ) forming schemes. The advantages are ascribed to a higher filament geometry control devised by the IFV scheme. Fig. 7 (b) shows the cumulative distribution of the energy required to perform Reset operations. The overall energy required to disrupt the conductive filament has been calculated as:

$$E = \sum_{i=1}^{n} V_{pulse,i} * I_{pulse,i} * T_{pulse} + V_{read} * I_{read,i} * T_{read}$$

(1)

Where n is the number of reset pulses applied during incremental pulse operation,  $V_{pulse,i}$  is the pulse voltage applied at step i,  $I_{pulse,i}$  is the current flowing through RRAM cell during pulse i application,  $T_{pulse} = 10\mu s$  is the pulse length,  $V_{read} = 0.2$  V is the read voltage applied during verify operation,  $I_{read,i}$  is the current read during read verify step i, and  $T_{read} = 10\mu s$  is the verify pulse length.

According to these results, the *IFV* advantages after forming are clear. As a matter of fact, as demonstrated in Fig. 3, each cell is formed with its proper filament geometry in order to achieve the 19  $\mu$ A current, thus allowing to counteract the intrinsic technological variability that would be impossible without a verify procedure.

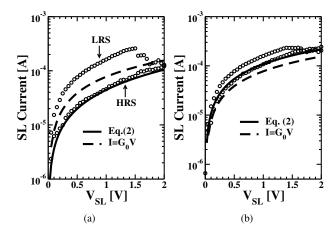

### 6. Post-Forming modeling

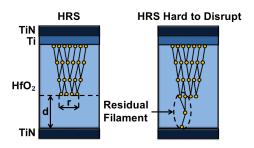

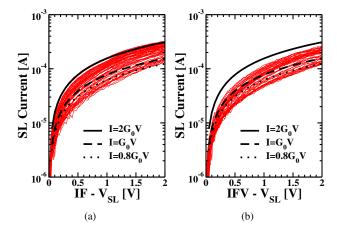

Reset I-V characteristics have been measured after-forming to analyze the conductive filament properties through QPC model [3, 14, 21]. Two different behaviors can be observed for correctly working cells (a) and hard to disrupt cells (b), reported in Fig. 8. The differences in the HRS current values can be ascribed to the differences in the filament size [4]. The black dashed line shows the limit  $I = G_0 V$  with  $G_0 = 2e^2/h$  the quantum conductance unit corresponding to the creation of a single mode nanowire, where e is the electron charge and h the Planck's constant. Within this framework,  $I = G_0V$  sets a limit: in case of  $I > G_0V$  more than a single conductive filament or a single filament with more than one mode must be taken into account: this means that on hard to disrupt cell a residual part of the conductive filament is still present after Reset operation since High Resistive State (HRS) curve measured is over the limit. HRS I-V curves fitting has been performed through QPC (lines). HRS current is calculated according to the expression:

$$I = \frac{2e}{h}G/G_0\left(eV + \frac{1}{\alpha}Ln\left[\frac{1 + e^{\alpha(\Phi - \beta eV)}}{1 + e^{\alpha[\Phi + (1 - \beta)eV]}}\right]\right)$$

(2)

where  $\Phi$  is the barrier height (bottom of the first quantized level),  $\alpha = t_B \pi^2 h^{-1} \sqrt{2m^*/\Phi}$  is a parameter related to the inverse of the potential barrier curvature (assuming a parabolic longitudinal potential),  $m^* = 0.44m_0$  is the effective electron mass and  $t_B$  is the barrier thickness at the equilibrium Fermi energy.  $\beta$  takes into account how the potential drops at the two ends of the filament: since the constriction is highly asymmetric  $\beta$ =1 has been used (almost all the applied voltage drops close to the Ti layer).  $G/G_0$  is a conductance parameter equivalent to

Figure 8: Reset I-V characteristics measured after forming and HRS fitting through eq.(2) on correctly working cells (a) and hard to disrupt cells (b).

Figure 9: Schematic showing the conductive filament shape after reset (HRS) for correctly working and hard to disrupt cells.

the number of filaments at very low voltages: in a very approximate way, a single highly conductive filament can be viewed as a parallel combination of elementary nanowires [22].

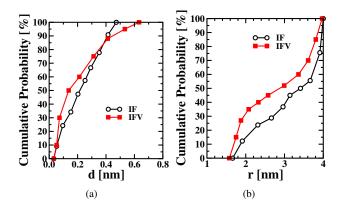

The conductive filament obtained after Reset on correctly working cells and hard to disrupt cells is depicted in Fig. 9: in case of good reset the presence of a potential barrier is assumed on HRS state, hence the average barrier length d and the radius of the constriction r have been calculated according to [14]. On the contrary, assuming the absence of a potential barrier on hard to disrupt cells, the normalized conductance of the filament  $G/G_0$  has been calculated using large negative values for  $\Phi$  in the above expression, since in such condition the barrier plays no role (neither  $\beta$  nor  $\alpha$  affect the results) and a large negative barrier is a trick to eliminate the barrier effect.

Fig. 10 shows the HRS curves obtained after Reset I-V operation on IF (a) and IFV (b) formed cells. It can be observed that IF show higher conductance values than IFV: only 39% of IF formed cells showed HRS curves below  $I = G_0V$  whereas 65% of IFV formed cells showed HRS curves below the limit. Even if such hard to disrupt cells percentages are very high, incremental step Reset algorithm allowed obtaining a strong reduction on both IF (around 9%) and IFV cells (0%), as shown in Fig. 6.  $I = 2 * G_0V$  and  $I = 0.8 * G_0V$  are reported as upper and lower limit, respectively.

Figure 10: HRS curves obtained after Reset I-V operation on IF (a) and IFV with  $\Delta V_{BL} = 0.01$  V (b) formed cells.

Figure 11: Cumulative distribution of  $\alpha$  and  $\Phi$  fitting parameters used on correctly working cells.

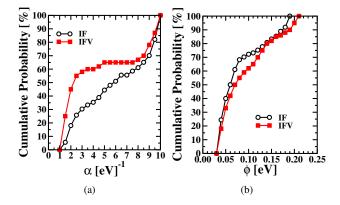

### 6.1. Good Reset fitting

In case of correct Reset operation (i.e. HRS curve below  $I = G_0V$ ) fitting has been performed assuming  $G/G_0 = 1$  and the presence of a potential barrier. The cumulative distributions of  $\alpha$  and  $\Phi$  fitting parameters used on correctly working cells are reported in Fig. 11. The cumulative distributions of calculated barrier length d and radius r of the constriction for correctly working cells are reported in Fig. 12: IFV cells show smaller r. These values are sensitive to the effective mass, which is unknown with certainty, so that they should be considered for comparative purposes only. The barrier in HRS is very low for both forming methods so it only affects the low voltage part of the I-V curve, after that a linear behavior can be observed.

### 6.2. Hard to disrupt fitting

In case of hard to disrupt cells fitting has been performed assuming large negative  $\Phi$  values,  $\alpha$  fixed to 1 (even if  $\alpha$  and  $\Phi$  play no role in such condition) and  $G/G_0 \geq 1$  due to the presence of the residual filament. Fig. 13 shows the cumulative distribution of  $G/G_0$  conductance values fitting parameters used on hard to disrupt cells: it can be observed that IF hard to disrupt cells resulted in higher conductance values.

Figure 12: Cumulative distribution of calculated barrier length d (a) and radius of the filament constriction r (b) on correctly working cells.

Figure 13: Cumulative distribution of  $G/G_0$  fitting parameters used on hard to disrupt cells.

#### 7. Endurance analysis

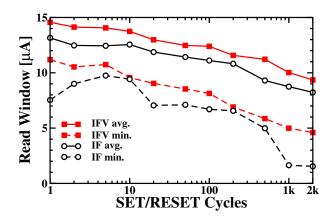

To quantify the advantages obtained through IFV forming during lifetime, 2k endurance cycles have been executed. Fig. 14 plots the IF and IFV average and minimum read windows, calculated as in [23], as a function of the Set/Reset cycles. The advantages of the IFV scheme are even appreciable during cycling: as far as the average criterion is considered, the average read window gain during cycling of the IFV scheme on the IF method sets around 7%, representing a marginal yet non negligible advantage. When the minimum criterion is considered, the average read window gain during cycling increases up to 37%. This represents once again a plus for the IFV scheme since it demonstrates its enhanced ability in Set/Reset tail bits (i.e., cells harder to be switched) reduction [24]. The read window closure due to endurance degradation [25] could be attributed to the impact of impurities in the metal-organic AVD precursor, in particular to carbon [26].

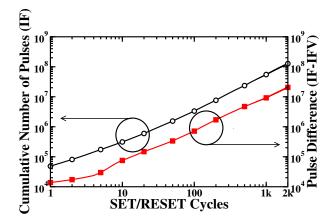

The ultimate advantage of the *IFV* is shown in Fig. 15, which exhibits the cumulative number of Set/Reset pulses applied to the entire memory array during the 2k cycles experiment as a function of the cycle number for the *IF* technique and the relative saving that can be obtained with *IFV*. The saving in terms of the total number of Set/Reset pulses during cycling is mainly

Figure 14: Average and minimum read windows as a function of the Set/Reset cycle number for IF and IFV ( $\Delta V_{BL} = 0.01 \text{ V}$ ) forming schemes.

Figure 15: Cumulative number of Set/Reset pulses applied to the entire memory as a function of the cycle number for the *IF* forming scheme (left axis) and cumulative pulse number saving for the *IFV* ( $\Delta V_{BL} = 0.01 \text{ V}$ ) forming scheme with respect to *IF* (right axis).

due to a lower Reset switching voltage required by cells formed with *IFV*.

All the described advantages translate, both during the design stage of larger arrays such as [27, 28] and at a system level, in shorter switching/operating times, less operative energy for the Reset operation, and in lower power consumption for the circuitry driving either the bitlines or the sourcelines.

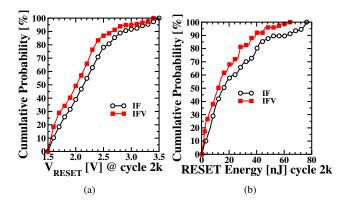

Experimental results show that even after 2k cycles *IFV* technique exhibits a lower Reset switching voltage and a reduced operation current: Fig. 16 (a) show the cumulative distribution of the reset switching voltages for *IF* and *IFV* ( $\Delta V_{BL} = 0.01 \text{ V}$ ) forming schemes.

Fig. 16 (b) shows the cumulative density function of the energy required to perform Reset operations: while the advantages after forming are clear, the energy gap is reduced during cycling because of device degradation.

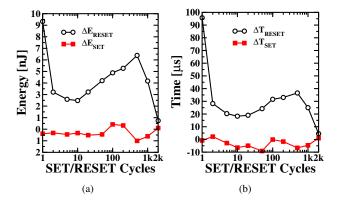

Fig. 17 shows the difference between *IF* and *IFV* average energy (a) and time (b) required to perform Set and Reset operations during cycling, calculated as

$$\Delta E_{Reset/Set} = E_{IF,Reset/Set} - E_{IFV,Reset/Set}$$

(3)

$$\Delta T_{Reset/Set} = T_{IF,Reset/Set} - T_{IFV,Reset/Set}$$

(4)

Figure 16: Cumulative distribution of the reset switching voltages (a) and overall Energy required to perform Reset operation (b) at Set/Reset cycle 2k for *IF* and *IFV* ( $\Delta V_{BL} = 0.01 \text{ V}$ ) forming schemes.

Figure 17: Average difference between IF and  $IFV(\Delta V_{BL}=0.01~V)$  Energy (a) and Time (b) required to perform Set and Reset operations as a function of the Set/Reset cycle number.

Set energy has been calculated as previously reported in (1) for Reset operation. Reset operation requires a higher number of pulses compared to Set, resulting in higher energy and time constraints. Even if *IFV* Set energy and time requirements are shown to be slightly higher, the advantages in terms of Reset energy and timing are clear until 2k cycles. After that, the device degradation reduces *IFV* advantages.

It is worth mentioning that the main drawback of the *IFV* forming technique could lie on the longer forming times for cells requiring high forming voltages compared to the *IF* scheme, mainly because of the verify operation between the forming steps. However, it must be pointed out that this operation is performed just once, therefore its latency increase is favourably traded with the time saved during the subsequent Set/Reset operations.

### 8. Conclusions

Different pulse forming techniques have been applied to form RRAM arrays and compared in terms of forming time, yield and cell-to-cell variability. After-forming modeling of correctly working and hard to disrupt cells has been performed through QPC, showing that thanks to a tight control during forming the creation of hard to disrupt filaments is avoided. A form and

verify technique, consisting in a sequence of trapezoidal waveforms with increasing voltages terminated when the expected switching behavior is achieved, showed the best results thanks to a tight control of the conductive filament creation. Its advantages in terms of the post-forming switching conditions homogenization, read window gain, operative current, cumulative number of pulses, energy and time required for switching during cycling have been demonstrated.

## Acknowledgments

This work was supported by the European Union's H2020 research and innovation programme under grant agreement  $N^o$  640073.

- S. F. Karg, G. I. Meijer, J. G. Bednorz, C. Rettner, A. G. Schrott, E. A. Joseph, C. H. Lam, M. Janousch, U. Staub, F. La Mattina, S. F. Alvarado, D. Widmer, R. Stutz, U. Drechsler, D. Caimi, Transition-metal-oxide-based resistance-change memories, IBM Journal of Research and Development 52 (4.5) (2008) 481–492.

- [2] Y. Y. Chen, B. Govoreanu, L. Goux, R. Degraeve, A. Fantini, G. S. Kar, D. J. Wouters, G. Groeseneken, J. A. Kittl, M. Jurczak, L. Altimime, Balancing SET/RESET pulse for >10<sup>10</sup> endurance in HfO<sub>2</sub>/Hf 1T1R bipolar RRAM, IEEE Transactions on Electron Devices 59 (12) (2012) 3243–3249.

- [3] Y. Y. Chen, R. Degraeve, S. Clima, B. Govoreanu, L. Goux, A. Fantini, G. Kar, G. Pourtois, G. Groeseneken, D. Wouters, M. Jurczak, Understanding of the endurance failure in scaled HfO<sub>2</sub>-based 1T1R RRAM through vacancy mobility degradation, in: IEEE International Electron Devices Meeting (IEDM), 2012, pp. 20.3.1–20.3.4.

- [4] G. Bersuker, D. C. Gilmer, D. Veksler, P. Kirsch, L. Vandelli, A. Padovani, L. Larcher, K. McKenna, A. Shluger, V. Iglesias, M. Porti, M. Nafra, Metal oxide resistive memory switching mechanism based on conductive filament properties, Journal of Applied Physics 110 (12) (2011) 1–12.

- [5] C. Zambelli, A. Grossi, D. Walczyk, T. Bertaud, B. Tillack, T. Schroeder, V. Stikanov, P. Olivo, C. Walczyk, Statistical analysis of resistive switching characteristics in ReRAM test arrays, in: IEEE International Conference on Microelectronics Test Structures (ICMTS), 2014, pp. 27–31.

- [6] D. Walczyk, T. Bertaud, M. Sowinska, M. Lukosius, M. A. Schubert, A. Fox, D. Wolansky, A. Scheit, M. Fraschke, G. Schoof, C. Wolf, R. Kraemer, B. Tillack, R. Korolevych, V. Stikanov, C. Wenger, T. Schroeder, C. Walczyk, Resistive switching behavior in TiN/HfO<sub>2</sub>/Ti/TiN devices, in: International Semiconductor Conference Dresden-Grenoble (ISCDG), 2012, pp. 143–146.

- [7] P. Lorenzi, R. Rao, F. Irrera, Forming kinetics in HfO<sub>2</sub>-based RRAM cells, IEEE Transactions on Electron Devices 60 (1) (2013) 438–443.

- [8] N. Raghavan, A. Fantini, R. Degraeve, P. Roussel, L. Goux, B. Govoreanu, D. Wouters, G. Groeseneken, M. Jurczak, Statistical insight into controlled forming and forming free stacks for HfOx RRAM, Microelectronic Engineering 109 (2013) 177 181.

- [9] C. Chen, H. Shih, C. Wu, C. Lin, P. Chiu, S. Sheu, F. Chen, RRAM defect modeling and failure analysis based on march test and a novel squeezesearch scheme, IEEE Transactions on Computers PP (99) (2014) 1–1.

- [10] T. Ninomiya, Z. Wei, S. Muraoka, R. Yasuhara, K. Katayama, T. Takagi, Conductive filament scaling of  $TaO_x$  bipolar ReRAM for improving data retention under low operation current, IEEE Transactions on Electron Devices 60 (4) (2013) 1384–1389. doi:10.1109/TED.2013.2248157.

- [11] H.-T. Liu, B.-H. Yang, H.-B. Lv, X.-X. Xu, Q. Luo, G.-M. Wang, M.-Y. Zhang, S.-B. Long, Q. Liu, M. Liu, Effect of pulse and dc formation on the performance of one-transistor and one-resistor resistance random access memory devices, Chinese Physics Letters 32 (02) (2015) 1–3.

- [12] A. Chen, M.-R. Lin, Variability of resistive switching memories and its impact on crossbar array performance, in: IEEE International Reliability Physics Symposium (IRPS), 2011, pp. MY.7.1–MY.7.4.

- [13] N. Raghavan, R. Degraeve, A. Fantini, L. Goux, D. Wouters, G. Groeseneken, M. Jurczak, Stochastic variability of vacancy filament configuration in ultra-thin dielectric RRAM and its impact on OFF-state reliability, in: IEEE International Electron Devices Meeting (IEDM), 2013, pp. 21.1.1–21.1.4.

- [14] E. A. Miranda, C. Walczyk, C. Wenger, T. Schroeder, Model for the resistive switching effect in HfO<sub>2</sub> MIM structures based on the transmission properties of narrow constrictions, IEEE Electron Device Letters 31 (6) (2010) 609–611.

- [15] H.-C. Shih, C.-Y. Chen, C.-W. Wu, C.-H. Lin, S.-S. Sheu, Training-based forming process for RRAM yield improvement, in: IEEE VLSI Test Symposium (VTS), 2011, pp. 146–151.

- [16] D. C. Gilmer, G. Bersuker, H.-Y. Park, C. Park, B. Butcher, W. Wang, P. D. Kirsch, R. Jammy, Effects of RRAM stack configuration on forming voltage and current overshoot, in: IEEE International Memory Workshop (IMW), 2011, pp. 1–4.

- [17] A. Grossi, D. Walczyk, C. Zambelli, E. Miranda, P. Olivo, V. Stikanov, A. Feriani, J. Sune, G. Schoof, R. Kraemer, B. Tillack, A. Fox, T. Schroeder, C. Wenger, C. Walczyk, Impact of intercell and intracell variability on forming and switching parameters in rram arrays, Electron Devices, IEEE Transactions on 62 (8) (2015) 2502–2509. doi:10.1109/TED.2015.2442412.

- [18] K. Higuchi, T. Iwasaki, K. Takeuchi, Investigation of verify-programming methods to achieve 10 million cycles for 50nm HfO<sub>2</sub> ReRAM, in: IEEE International Memory Workshop (IMW), 2012, pp. 1–4.

- [19] F. T. Chen, H. Y. Lee, Y. S. Chen, Y. Y. Hsu, L. J. Zhang, P. S. Chen, W. S. Chen, P. Y. Gu, W. H. Liu, S. M. Wang, C. H. Tsai, S. S. Sheu, M. J. Tsai, R. Huang, Operation of oxygen vacancy-based RRAMs, Science China Information Sciences 54 (5) (2011) 1073–1086.

- [20] A. Grossi, C. Zambelli, P. Olivo, E. Miranda, V. Stikanov, T. Schroeder, C. Walczyk, C. Wenger, Relationship among current fluctuations during forming, cell-to-cell variability and reliability in rram arrays, in: Memory Workshop (IMW), 2015 IEEE International, 2015, pp. 1–4. doi:10.1109/IMW.2015.7150303.

- [21] E. Miranda, D. Jimenez, J. Sune, The quantum point-contact memristor, IEEE Electron Device Letters 33 (10) (2012) 1474–1476.

- [22] X. Lian, X. Cartoix, E. Miranda, L. Perniola, R. Rurali, S. Long, M. Liu, J. Su, Multi-scale quantum point contact model for filamentary conduction in resistive random access memories devices, Journal of Applied Physics 115 (24) (2014) 1–8.

- [23] C. Zambelli, A. Grossi, P. Olivo, D. Walczyk, J. Dabrowski, B. Tillack, T. Schroeder, R. Kraemer, V. Stikanov, C. Walczyk, Electrical characterization of read window in ReRAM arrays under different SET/RESET cycling conditions, in: IEEE International Memory Workshop (IMW), 2014, pp. 146–149.

- [24] S. Yu, X. Guan, H.-S. P. Wong, On the switching parameter variation of metal oxide RRAM - part II: Model corroboration and device design strategy, IEEE Transactions on Electron Devices 59 (4) (2012) 1183–1188.

- [25] P. Huang, B. Chen, Y. Wang, F. Zhang, L. Shen, R. Liu, L. Zeng, G. Du, X. Zhang, B. Gao, J. Kang, X. Liu, X. Wang, B. Weng, Y. Tang, G.-Q. Lo, D.-L. Kwong, Analytic model of endurance degradation and its practical applications for operation scheme optimization in metal oxide based RRAM, in: IEEE International Electron Devices Meeting (IEDM), 2013, pp. 22.5.1–22.5.4.

- [26] M. Sowinska, T. Bertaud, D. Walczyk, S. Thiess, P. Calka, L. Alff, C. Walczyk, T. Schroeder, In-operando hard X-ray photoelectron spectroscopy study on the impact of current compliance and switching cycles on oxygen and carbon defects in resistive switching Ti/HfO2/TiN cells, Journal of Applied Physics 115 (20) (2014) 204509.

- [27] S.-S. Sheu, M.-F. Chang, K.-F. Lin, C.-W. Wu, Y.-S. Chen, P.-F. Chiu, C.-C. Kuo, Y.-S. Yang, P.-C. Chiang, W.-P. Lin, C.-H. Lin, H.-Y. Lee, P.-Y. Gu, S.-M. Wang, F.-T. Chen, K.-L. Su, C.-H. Lien, K.-H. Cheng, H.-T. Wu, T.-K. Ku, M.-J. Kao, M.-J. Tsai, A 4Mb embedded SLC resistive-RAM macro with 7.2ns read-write random-access time and 160ns MLC-access capability, in: IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011, pp. 200–202.

- [28] T.-Y. Liu, T. H. Yan, R. Scheuerlein, Y. Chen, J. K. Lee, G. Balakrishnan, G. Yee, H. Zhang, A. Yap, J. Ouyang, T. Sasaki, S. Addepalli, A. Al-Shamma, C.-Y. Chen, M. Gupta, G. Hilton, S. Joshi, A. Kathuria, V. Lai, D. Masiwal, M. Matsumoto, A. Nigam, A. Pai, J. Pakhale, C. H. Siau, X. Wu, R. Yin, L. Peng, J. Y. Kang, S. Huynh, H. Wang, N. Nagel, Y. Tanaka, M. Higashitani, T. Minvielle, C. Gorla, T. Tsukamoto, T. Yamaguchi, M. Okajima, T. Okamura, S. Takase, T. Hara, H. Inoue, L. Fasoli, M. Mofidi, R. Shrivastava, K. Quader, A 130.7 mm² 2-layer 32 Gb ReRAM Memory Device in 24 nm technology, in: Proc. ISSCC, 2013, pp. 210–212.