# POLITECNICO DI TORINO Repository ISTITUZIONALE

An Adaptive Method to Reduce Undershoots and Overshoots in Power Switching Transistors Through a Low Complexity Active Gate Driver

## Original

An Adaptive Method to Reduce Undershoots and Overshoots in Power Switching Transistors Through a Low Complexity Active Gate Driver / Raviola, Erica; Fiori, Franco. - In: IEEE TRANSACTIONS ON POWER ELECTRONICS. - ISSN 0885-8993. - STAMPA. - (2022). [10.1109/TPEL.2022.3221187]

Availability:

This version is available at: 11583/2972966 since: 2022-11-11T08:35:39Z

Publisher:

**IEEE**

Published

DOI:10.1109/TPEL.2022.3221187

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

## An Adaptive Method to Reduce Undershoots and Overshoots in Power Switching Transistors Through a Low Complexity Active Gate Driver

Erica Raviola, Member, IEEE, Franco Fiori, Member, IEEE

Abstract—Active gate drivers lend themselves well to reducing over- and under- voltages during the commutations of hard switched power transistors, as well as to damping resonances. However, their control strategy is a major challenge, as it should account for variations of operating condition, parameter spread, and non linearities of the driven transistor. This paper proposes an effective control method to reduce overshoots and undershoots in a power transistor driven by an active gate driver. The modulation pattern is modified on-the-fly and none a-priori characterization is required. The presented method modifies the timing parameter to attain almost zero over- and under- voltages with the lowest power losses. This is achieved by combining a low complexity active gate driver with the measurements of peak values of the drain-source voltage. The technique was experimentally assessed for a 48-12 V DC-DC converter, and resulted in better switching performance than standard solutions and open loop control.

*Index Terms*—Active Gate Driver (AGD), Electro-Magnetic Interference (EMI), switching waveforms, switching oscillations, power transistors.

#### I. INTRODUCTION

The growing demand for e-mobility is expected to push power electronics forward to meet the demand for efficiency and power density. Besides high voltage equipment, a large amount of on-board systems will continue to require mediumand low-voltage supplies [1], for which several design constraints should be met. The commutations of fast power transistors have become crucial, as they directly affect efficiency, Electro Magnetic Emission (EME), as well as reliability. These transients can lead to overshoots and oscillations superimposed onto the switching waveforms, which are tough to mitigate without affecting losses. Voltage and current overshoots reduce the device lifetime, resulting in less reliable systems [2]. At the same time, high dv/dt and di/dt, as well as the presence of oscillations triggered by fast commutations (voltage and current ringing), have a detrimental effect on the EME delivered by power converters [3].

The cause of ringing lies in the inductive and capacitive parasitics included in High Frequency (HF) switching loops. Packaging and interconnections contribute to the overall parasitic inductance, which may resonate with the output capacitances of active devices. Current and voltage steps, which are

This work was partially supported by the Power Electronics Innovation Center (PEIC), Politecnico di Torino, Italy. (*Corresponding author: Erica Raviola*).

The authors are with the Department of Electronics and Telecommunications, Politecnico di Torino, Turin 10129, Italy. (e-mail: erica.raviola@polito.it, franco.fiori@polito.it)

caused by the switching of power transistors, can excite such HF LC circuits, resulting in unwanted overshoots [4].

To limit such over-voltages and over-currents, the most popular approaches involve the tuning of the gate resistance [5] and the insertion of snubbers [6], [7]. Some recent investigations have explored the use of source inductance [8]. However, these solutions have proven not to be optimal. A better trade-off between overshoots and losses can be achieved by Active Gate Drivers (AGDs) [9].

AGDs are able to shape the switching trajectory of the driven transistor from the gate terminal by controlling the gate charge during transients. Depending on the aim of the designer, they can reduce overshoots [10], [11], di/dt and dv/dt [12], and the delivered EME [13]. A crucial aspect of AGDs is their control strategy, i.e., the method used to determine the modulation pattern, which can be classified into open loop, direct feedback, model-based, and sequential approach [9]-[12], [14], [15]. In open loop AGDs, such as in [9], the modulation profile is fixed and found a-priori. However, under operating condition or temperature variations, such a profile results in a degradation of switching performance [16]. To find the best suited parameters in a large solution space, [10] proposed an optimization platform based on a metaheuristic algorithm, which required from 165 to 572 s to run. The platform was developed using an oscilloscope, a controller PC module and a power analyzer, which are however not available in a practical implementation. Direct feedback AGDs are typically based on the sensing of di/dt, dv/dt, drain current and drain-source voltage to detect the different transient stages, and they can control each stage separately [17]. This can be achieved by an analog [18] or digital [17] controller. However, as transients are becoming faster, the sensing circuits and the AGD controller need to be fast as well, and the effectiveness of direct feedback AGDs can be limited. A different approach, which is usually referred to as modelestimator control, consists in building up a mathematical model to predict the switching trajectory. In [14], the current optimal profile was obtained in the s-domain. However, to account for non linear effects, the AGD timing parameters were obtained by simulation and stored in a Look Up Table (LUT) for the different values of load current. Similarly, the measurement of bus voltage and load current was exploited in [12], along with a mathematical model, to choose the most suited AGD voltage profile that optimizes the defined cost function. An analytical switching model and an optimization algorithm were proposed in [19] to trade off between losses

and EMI noise based on Matlab software. In order to be effective, such solutions require an accurate model to predict the switching trajectory, for which the values of parasitic elements, the parameters to active devices, e.g., threshold voltage and parasitic capacitances, and the delays of the AGD itself should be known. However, these parameters are affected by process variations. The threshold voltage depends on the thickness of the epitaxial layer, by the channel length and by the concentration of interface traps, resulting in up to 0.7 V variations [20]. The internal gate resistance and the parasitic capacitances show a 12 % and 10 % spread, respectively [21]. Moreover, several studies have reported the dependence of such parameters on temperature and and its effect on the switching trajectory [22], [23].

In order to address the above uncertainties, a sequential control strategy can be exploited [24]. In this case, the AGD modulation profile is adapted cycle by cycle depending on the switching performance attained in the previous transient. In such a way, high speed components can be avoided, as there is no need to be faster than the transient, and uncertainties related to the model are no longer a concern, since the actual switching performance is fed back. Such kind of control was experimentally assessed in [24]. However, the test setup was based on an oscilloscope, Matlab software, and an isolated signal generator to drive the power transistor, which is not a viable solution in practical applications. The work proposed in [11] is based on a sequential control including a model estimator, but the relation between load current and variations of the output resistance of AGD was experimentally fitted, meaning that it suffers from the same issues of a model-based control. More recently, with the aim of suppressing ringing, the duration of Miller's plateau was measured and exploited to modify the profile of the AGD output resistance cycle by cycle in [25]. However, only simulation results were provided, and a fitted function was exploited to vary the gate resistance. To sum up, existing AGDs controllers have so far not truly performed the required calculations on-the-fly. This means that some LUT or previously extrapolated relation are required to find the proper modulation profile.

This paper presents an adaptive method that is a true sequential digital control, and is not based on any switching model or a-priori function extrapolation. This is obtained by exploiting a minimum search algorithm applied to a low-complexity driver, which continuously runs on the AGD controller itself. With respect to previous works, the undershoot and overshoot affecting the drain-source voltage are exploited as an indirect estimation of the oscillations taking place. On the basis of these measurements only, the controller adapts the AGD parameters to attain the lowest over- under- voltages. The method is able to find and to track the best-suited AGD parameters with no external aid, which makes it robust against variations of operating conditions, of power transistor parameters, and of parasitic values. Moreover, the technique is well suited for a chip integration.

The paper is organized as follows. In Sect. II, the turn on and the turn off of a hard-switched power transistor are analyzed referring to a leg. Then, in Sect. III, the proposed AGD is introduced, and its effectiveness experimentally assessed in

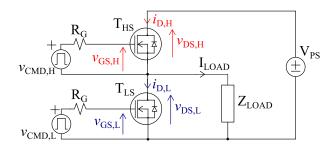

Fig. 1. Switching leg circuit. Transistors  $T_{\rm HS}$  and  $T_{\rm LS}$  are periodically turned on and off to supply an inductive load.

Fig. 2. Time domain waveforms referring to the circuit shown in Fig. 1. Solid lines refer to high side transistor ( $T_{\rm HS}$ ), dashed lines to low side one ( $T_{LS}$ ).

Sect. IV. The proposed method is then explained in Sect. V, and experimentally validated in Sect. VI. Concluding remarks are drawn in Sect. VII.

#### II. SWITCHING TRANSIENTS IN A HALF BRIDGE

Aiming to discuss the switching trajectories of power transistors, a hard switched leg is considered, as shown in Fig. 1. Such a circuit is of the utmost importance in power electronics as it is a basic building block for several topologies. It comprises of a high side  $(T_{HS})$  and a low side  $(T_{LS})$  power transistor, which are turned on and off to transfer power from the DC bus, modeled by an ideal voltage source  $(V_{PS})$ , to an inductive load ( $Z_{LOAD}$ ). The power transistors are driven by two Conventional Gate Drivers (CGDs), represented by their Thevenin's equivalent  $(v_{\rm CMD}, R_{\rm G})$ . The voltage and current waveforms of  $T_{\rm LS}$  and  $T_{\rm HS}$  are shown in Fig. 2 by dashed and solid lines, respectively. The turn on and turn off commands  $(v_{\rm CMD,L})$  and  $v_{\rm CMD,H}$  are not overlapped, but some dead time is inserted in between to avoid cross conduction. At time  $t=t_1,\,T_{

m HS}$  is turned off by a high to low transition of  $v_{\rm CMD,H}$ . As  $T_{\rm LS}$  is still off, the drain source voltage of  $T_{\rm HS}$  ( $T_{\rm LS}$ ) increases (decreases) to  $V_{\rm PS}$  (zero), causing the turning on of the  $T_{\rm LS}$  body diode. At this point, the load current is entirely diverted from  $T_{\rm HS}$  to the  $T_{\rm LS}$  body diode. Then, after a dead time equals to  $t_2 - t_1$ ,  $T_{LS}$  is turned on, meaning that its body diode turns off and  $T_{LS}$  enters the triode region in the third quadrant, provided that  $I_{LOAD}$  is positive. When  $T_{LS}$  is turned off  $(t = t_3)$ ,  $T_{HS}$  is still interdicted,

Fig. 3. Half bridge circuit complemented with parasitic elements of active switches, DC link and inductive load. Capacitive and inductive parasitics have been highlighted to be found at a glance.

therefore the body diode of  $T_{\rm LS}$  turns on again, allowing the load current to flow. Finally,  $T_{\rm HS}$  is turned on at  $t=t_4$  to charge the load inductance, resulting in a  $V_{\rm PS}$  and  $I_{\rm LOAD}$  variation on the switching voltage and current, respectively. During this transient, the turning off of the low side switch is not immediate, as its body diode experiences reverse recovery. Although both  $T_{\rm HS}$  and  $T_{\rm LS}$  are turned on and turn off every half switching period, this brief analysis shows that only the  $T_{\rm HS}$  commutations should be of interest for the the control of the output switching waveforms.

However, the curves shown in Fig. 2 refer to a rather ideal circuit, as parasitic elements have not been considered. To account for them, the circuit shown in Fig. 1 was modified, resulting in that shown in Fig. 3, with the parasitic elements highlighted. More precisely, inductances related to the packaging and interconnects of power transistor terminals  $(L_S, L_G, L_D)$  and to the DC link  $(L_{\rm DC})$  have been included. Capacitances of active devices have been highlighted as well  $(C_{\rm GS}, C_{\rm GD}, C_{\rm DS})$ , together with those related to the switching node and the supply rails  $(C_{\rm t,H}, C_{\rm t,L})$ . Also the inductive load  $(L_L)$  was complemented with its series resistance (ESR), parallel resistance (EPR) and capacitance (EPC) [26].

The value of these parasitic elements is strictly related to the specific layout and to the exploited power switches. In medium-voltage automotive applications, power circuits are supplied by the 48 V bus, and their typical power rating is around 1 kW. Thus, MOSFET transistors are usually preferred. As far as 80-150 V power MOSFETs encapsulated in an SMD package, e.g., TO-263, are concerned, their output capacitance is around a few nF. The overall parasitic inductance is mainly determined by the size of the switching loop, i.e., the one encompassing  $T_{\rm HS}, T_{\rm LS}$  and the DC link. For a square loop, such an inductance can be estimated as

$$L_{\rm SQ} \approx 2\frac{\mu_0}{\pi} l \left( \ln \frac{l}{r_w} - 0.774 \right),\tag{1}$$

where l is the side of the square,  $r_w$  the wire radius and it is assumed that  $l >> r_w$  [27]. For a loop with a side of a few centimeters, it results an  $L_{\rm SQ}$  of approximately tens nH. The frequency of oscillations triggered at the turn on and the turn off of  $T_{\rm HS}$  depends on the loop inductance and the output

3

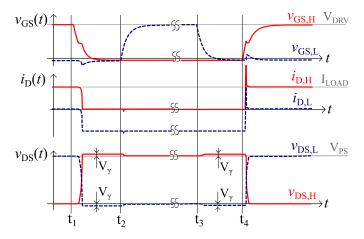

Fig. 4. (a) Simplified model for the turn on and turn off analysis of  $T_{\rm HS}$  for the considered application. Such circuit can be further rearranged in that shown in (b).

capacitance of active devices. Thus, this simple count results in an oscillation frequency of 10s MHz, which is in good agreement with the 10-60 MHz range found in the literature [4], [28]. With the purpose of discussing more in details the  $T_{\rm HS}$  transients, the circuit shown in Fig. 3 can be simplified in the model reported in Fig. 4(a). The low side transistor has been replaced by an ideal diode (D) in parallel with a capacitance  $C_{\rm D}$  to account for the junction capacitance of the  $T_{\rm LS}$  body diode. For the sake of simplification,  $L_{\rm D,L}, L_{\rm S,L}$  shown in Fig. 3 have been neglected as for the considered application they are typically much smaller than the loop inductance. About the inductive load (see Fig. 3), it is modeled by the impedance

$$Z_{\rm LOAD}(\omega) = ESR + \frac{j\omega L_{\rm L}}{1 + j\omega \frac{L_{\rm L}}{EPD} - \omega^2 L_{\rm L}EPC}.$$

(2)

Thus, low frequency components of the load current flow though  $L_{\rm L}$ , whether high frequency ones through EPC. However, in practical applications EPC is typically much smaller then the output capacitance of active switches, meaning that it can be neglected. As transients are much shorter than the switching period, this means that the current flowing in  $L_{\rm L}$  can be approximated as constant and equals to its DC value ( $I_{\rm LOAD}$ ). Therefore, the load is modeled by a constant current source  $I_{LOAD}$ . Similarly to the EPC, the parasitic capacitances  $C_{t,H}, C_{t,L}$ , which are related to the PCB layout, have not been considered as they are usually much lower than those of the switches. The model shown in Fig. 4(a) can be rearranged in that of Fig. 4(b), as high side and low elements are in series. Indeed, the turn on and turn off of the high side transistor shown in Fig. 3 can be analyzed referring to the simplified model reported in Fig. 4(b), as the  $T_{\rm HS}$  switching trajectory is the same experienced by T.

## A. Turn on and turn off oscillations

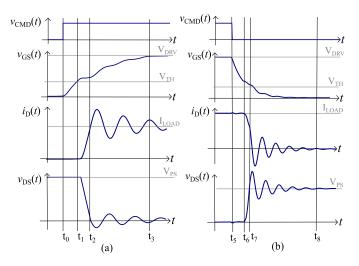

The turn on transient of transistor T can be analyzed referring to the switching waveforms reported in Fig. 5(a). At  $t=t_0$ , the  $v_{\rm CMD}$  command goes high, and the  $v_{\rm GS}$  voltage increases exponentially. As soon as  $v_{\rm GS}$  reaches the T threshold voltage  $(V_{\rm TH})$  at  $t=t_1$ , the transistor enters the saturation region, causing the drain current  $(i_{\rm D})$  to increase. The drain source voltage  $v_{\rm DS}$  decreases because of the voltage drop

Fig. 5. Switching waveforms related to the (a) turn on and (b) turn off of the T transistor in the simplified model shown in Fig. 4.

across  $L_D, L_S, L_{DC}$  and of the discharge of  $C_{\rm GD}$  through  $R_{\rm G}$ . More precisely, as far as T is in the Miller region, one can write

$$\frac{dv_{\rm DS}(t)}{dt} = -\frac{V_{\rm DRV} - V_{\rm GS}}{R_{\rm G}C_{\rm GD}} = -\frac{i_{\rm G}(t)}{C_{\rm GD}}.$$

(3)

For  $t < t_2$ , the load current flows in the diode D. However, with the  $i_{\rm D}$  current equals to  $I_{\rm LOAD}$  at  $t=t_2$ , the diode turns off. Capacitance  $C_D$  has to be charged to  $V_{\rm PS}$ , and this voltage step can excite the resonant circuit comprising the parasitic inductances and the capacitances to be charged. Such oscillations have been extensively studied, and several models are available in the literature [4], [6], according to which the circuit shown in Fig. 4(b) can be simplified to a second-order RLC series. In that case, by defining  $L_{\rm LOOP}$  and  $R_{\rm LOOP}$  as the overall inductance and resistance included in the output loop, one can derive  $i_{\rm D}(t)$  under undamped conditions as

$$i_{\rm D}(t) = e^{-\alpha t} (A_1 \cos \omega_{\rm d} t + A_2 \sin \omega_{\rm d} t), \tag{4}$$

where the attenuation  $(\alpha)$  and the damped natural frequency  $(\omega_d)$  can be expressed as

$$\alpha = \frac{R_{\text{LOOP}}}{2L_{\text{LOOP}}}, \quad \omega_d = \sqrt{\frac{1}{(C_{\text{D}}L_{\text{LOOP}})^2} - \alpha^2}.$$

(5)

Coefficients  $A_1,A_2$  depend on boundary conditions, i.e., initial values of  $i_{\rm D}(t)$  and  $di_{\rm D}(t)/dt$  [4]. Eqn. (4) quantifies the exponentially decaying oscillations shown in Fig. 5(a) for  $t>t_2$ . It is worth noticing that, although T is in the ohmic region,  $v_{\rm DS}$  is affected by oscillations due to  $L_{\rm D},L_{\rm S}$ .

Similarly to the turn on, also the turn off of transistor T can be discussed referring to the circuit shown in Fig. 4(b) and to the waveforms in Fig. 5(b). With  $v_{\rm CMD}$  turned off  $t=t_5$ , the output waveforms remain constant until  $t=t_6$ . At this point, the channel current equals the load one, thus the output capacitance of the free wheeling diode discharges to zero. The drain current, which is the sum of load current (constant) with the one flowing in  $C_{\rm D}$ , decreases as  $C_{\rm D}$  is discharging. At  $t=t_7$ , the voltage  $v_{\rm DS}$  equals the input supply voltage, meaning

that D turns on, shorting  $C_{\rm D}$ . The load current is now flowing in the diode, and  $i_{\rm D}$  should step down to zero. However, the parasitic inductance in the power loop is still charged, and this current step can trigger the resonance with the output capacitance of the transistor. Also in this case one can derive  $i_{\rm D}(t)$  as (4), with the foresight to substitute  $C_{\rm D}$  with the T output capacitance in (5). Both for turn on and turn off, the higher the overshoot and undershoots on  $v_{\rm DS}$ , the higher the oscillation amplitude is.

## B. Sensitivity to switching parameters

From the previous analysis, it appears that frequency and decaying factor of oscillations depend on the equivalent inductance, capacitances and resistance characterizing the switching loop. Coefficients  $A_1, A_2$  include both initial and final values, i.e.,  $I_{\rm LOAD}$  and  $V_{\rm PS}$  for  $i_{\rm D}$  and  $v_{\rm DS}$ , as well as the initial di/dt. This current derivative in turn depends on the threshold voltage, the transconductance and the capacitance values of the transistor. As previously mentioned, these parameters are affected by process variations, temperature, and they are strongly related to the considered test case. Overshoot, ringing and switching losses are affected and, consequently, a spread of the switching trajectories occurs [29]. As the above mentioned parameters are not typically under the designers' control, model-based and sequential AGDs proposed so far exploit some interpolated relations or LUTs to get the most suited modulation pattern.

In previous investigations, the AGD control parameters were obtained by simulation to attain non oscillating waveforms with minimum switching losses [30], [31]. However, such a method failed when applied to a real test case, due discrepancies of simulation models. A different approach was later investigated. It is not based on models, and it does not require parameters related to the active devices or to the particular power circuit. The result of this second approach is the method presented in this paper, which is entirely implemented by the AGD controller on-the-fly. This is based on the  $v_{\rm DS}$  undershoot and overshoot reduction at the turn on and turn off, respectively. By combining the developed algorithm with a low complexity AGD, oscillations amplitude can be reduced independently from variations of operating conditions or parameter spread.

## III. PROPOSED ACTIVE GATE DRIVER

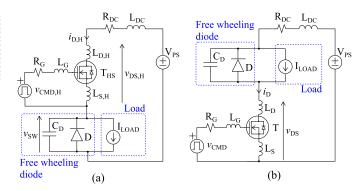

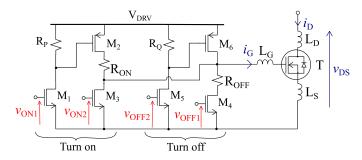

In order for the proposed method to control overshoots and undershoot cycle by cycle, a low complexity AGD is required. In such a way, the controller can tune the AGD parameters onthe-fly. From the previous transient analysis, an AGD should be able to slow down the driven transistor when turn on and turn off oscillations are being triggered. This means that the power transistor is exploited as a dissipative element to damp oscillations. Independently from the actual topology, AGDs are based on the modulation of gate charge. The exploited circuit, which was previously introduced in [32], [33], is shown in Fig. 6. Such an AGD is controlled by four on-off signals, named  $v_{\rm ON1}, v_{\rm ON2}$  and  $v_{\rm OFF1}, v_{\rm OFF2}$ . The former are active during the turn on, the latter during the turn off, and they

Fig. 6. Circuit of the proposed AGD, which is able to slow down the power transistor during its turn on and turn off.

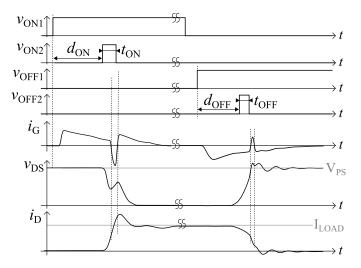

Fig. 7. Timing of the AGD control signals and output switching waveforms. By activating  $v_{\rm ON2}$  ( $v_{\rm OFF2}$ ) during the turn on (off) commutation, it is possible to sink (inject) current from (to) the gate terminal to slow down T.

are all generated by the AGD controller (not shown in Fig. 6). Referring to Fig. 7, one can discuss the working principle of such an AGD for the turn on (left) and turn off (right) of the power transistor. It is assumed a suitable timing of the control signals, and that the AGD circuit is inserted in the simplified model shown in Fig.4(b). As far as the T turn on is concerned, the rising edge of  $v_{ON1}$  causes  $M_1, M_2$  to switch from interdiction to the ohmic region, resulting in a positive gate current  $(i_G)$ . Thus, T enters the saturation region and a drain current  $(i_D)$  flows. After a delay  $d_{ON}$ , the  $v_{ON2}$  signal is activated too, turning on transistor  $M_3$ . Due to the presence of  $R_{\rm ON}$ , the current provided by  $M_2$  is lower than that sunk by  $M_3$ , meaning that the gate current decreases even though  $M_1, M_2$  are on. Transistor  $M_3$  is kept on for a period  $t_{ON}$ , thus resulting in  $i_{\rm G} < 0$ , as shown in Fig. 7. Recalling (3), the time derivative of voltage  $v_{\rm DS}$  is directly controlled by the gate current with T in saturation. Thus, a negative gate current causes  $v_{\rm DS}$  to increase locally during its fall transient. In such a way T is slowed down, as its extra power losses are exploited to increase the resulting damping factor. When  $v_{\rm ON2}$  is driven low,  $M_3$  turns off and  $M_2$  continues to inject an  $i_G > 0$ until the gate-source voltage reaches  $V_{\rm DRV}$ . As far as the turn off of the driven transistor is concerned,  $v_{\rm ON1}$  is turned off, and  $v_{\rm OFF1}$  is driven high, leading the T input capacitance to discharge. The control signal  $v_{\mathrm{OFF2}}$  is then activated after a

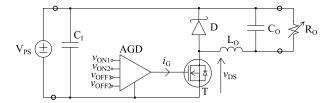

Fig. 8. DC-DC converter designed assess the AGD shown in Fig. 6. It is an asynchronous low side Buck converter.

Fig. 9. Photograph of (a) the prototyped AGD and the switching loop, (b) the test bench exploited.

delay  $d_{\rm OFF}$  when  $v_{\rm DS}$  is approximately  $V_{\rm PS}$ , as shown in Fig. 7 on the right. More precisely, with  $i_{\rm G}>0$ , the drain current increases, and it counteracts the  $i_{\rm D}$  step, which would cause the oscillation triggering. As a result, the  $v_{\rm DS}$  voltage locally decreases, and its overshoot is reduced. In such a way, the AGD can damp the turn off oscillation as well. Then, after a  $t_{\rm OFF}$ , as shown in Fig. 7,  $v_{\rm OFF}$ 2 is driven low and the turn off process end through  $M_4$ . The timing of the control signals, i.e., the value of  $t_{\rm ON}, d_{\rm ON}, t_{\rm OFF}, d_{\rm OFF}$ , determines the amount of charge injected and sunk in the different stages of the turn on and turn off. Therefore, the timing of these signal is crucial in shaping the switching trajectory of T.

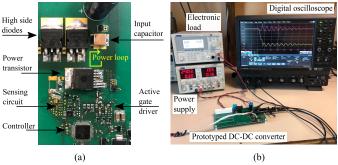

## IV. UNDERSHOOT MAPPING

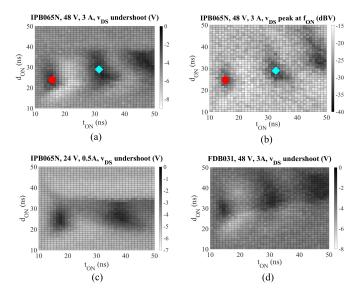

With the purpose of assessing such an AGD, it was included in an asynchronous low side Buck converter to drive the power transistor T, as shown in Fig. 8. A photograph of the experimental test bench is shown in Fig. 9(b), with the main components labeled. The proposed AGD is located close to T, and it was prototyped exploiting discrete components only, as shown in Fig. 9(a). With the AGD parameters  $d_{\rm ON}$ ,  $t_{\rm ON}$  in the (10,50) ns range, all combinations were tested. The resulting color maps are shown in Fig. 10, in which (a) refers to the  $v_{\rm DS}$  undershoot with the Buck operating at  $I_{\rm LOAD}$ =3 A and  $V_{\rm PS}$ =48 V, and (b) to the magnitude of the  $v_{\rm DS}$  spectrum at the turn on oscillation frequency ( $f_{\rm ON}$ =36 MHz). From Fig. 10(a), more than a darker region, i.e., characterized by a small value of  $v_{\rm DS}$  undershoot, occur.

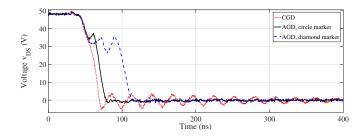

The waveform corresponding to the central point of the leftmost darker region (circle marker in Fig. 10(a)) is shown in Fig. 11(a) by solid line and that related to the center region (diamond marker) by dashed line. Both of them are characterized by a  $v_{\rm DS}$  local increase, as predicted in Sect. III, and resulted in non-oscillating waveforms. Such a local

Fig. 10. Color maps reporting (a) the  $v_{\rm DS}$  undershoot and (b) the magnitude of the  $v_{\rm DS}$  frequency spectrum at  $f_{\rm ON}$  with  $V_{\rm PS}$ =48 V and  $I_{\rm LOAD}$ =3 A. The undershoot is also reported in (c) in case of  $V_{\rm PS}$ =24 V and  $I_{\rm LOAD}$ =0.5 A, and in (d) with a different power transistor exploited.

Fig. 11. Comparison between the  $v_{\rm DS}$  waveforms for the CGD (dotted) and the AGD with different set of parameters. Solid and dashed lines refer to the circle and diamond marker of Fig. 10(a), respectively.

increase is the effect of the gate current modulation, and the solid line is in agreement with the  $v_{\rm DS}$  shown in Fig. 7. Finally, the  $v_{\rm DS}$  voltage obtained by exploiting the proposed AGD as a CGD, i.e., with  $v_{ON,2}$  not turned on, is reported in dotted line for comparison. The solid curve should be preferred as its  $v_{\rm DS}$ fall time is lower than that related to the dashed curve, meaning that oscillations are damped with a lower losses increase. Such an aspect can be explained as the longer the  $v_{\rm DS}$  local increase, the longer the switching time will be. Similarly, with a  $d_{ON}$ too small, the current sinking is ineffective, as T is interdicted, whether with  $d_{ON}$  too high, T is already in the ohmic region. As a consequence, the AGD parameters affect the switching losses of the power transistor, thus the conversion efficiency of the converter. Indeed, with  $(d_{ON}, t_{ON})$  corresponding to the diamond marker, the measured efficiency was equal to 91.2 %, and with those corresponding to the circle marker, the efficiency dropped to 90.7 %. The darker regions in the  $v_{\rm DS}$ undershoot also corresponds to minima in the corresponding frequency spectrum, as the color map shown in Fig. 10(a) is in good agreement with that in Fig. 10(b). Indeed, the position of local minima, which is identified by markers in the two subplots, is the same. With the operating conditions modified, such local minima still occur, but their position is

Fig. 12. Scheme representing the sub-blocks of the proposed adaptive method.

different. For example, with  $I_{\rm LOAD}$ =0.5 A and  $V_{\rm PS}$ =24 V, the undershoot color map is shown in Fig. 10(c). This is quite different from that in (a), and it is in accordance with the results reported in [33]. Recalling Sect. II-A, different  $I_{\rm LOAD}$  and  $V_{\rm PS}$  result in a different oscillation amplitude, meaning that the T trajectory should be modified accordingly. Finally, the driven power transistor [34] was substituted with a different one, which is in the same package but is characterized by a higher input capacitance [35]. In this case, the undershoot color map is reported in Fig. 10(d), and similarly to (c), the local minima occur with different set of AGD parameters.

To sum up, the AGD effectiness was assessed, as it was able to damp oscillations. Several combinations of AGD parameter resulting in non oscillating waveforms occur. However, they are not equivalent in terms of power losses. By considering the left most minimum, i.e., that corresponding to the lowest  $t_{\rm ON}$ , the set of AGD parameters is not fixed, but it is affected by several parameters, which can be hardly considered analytically altogether.

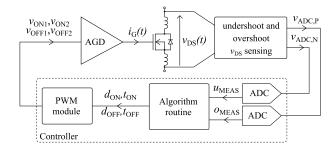

### V. SEQUENTIAL ADAPTIVE METHOD

The developed adaptive method combines the measurement of the  $v_{\rm DS}$  undershoot with a minimum search algorithm. This can be implemented on a resource-limited digital controller, e.g., a microcontroller. As previously discussed, the  $v_{\rm DS}$  undershoot depends on the amplitude of oscillations, meaning that it can be exploited to assess the presence of ringing. The block scheme of the proposed architecture is shown in Fig. 12. A sensing circuit is exploited to measure the undershoot and overshoot affecting the  $v_{\rm DS}$  voltage, which are then converted into a digital value by means of two Analog-To-Digital Converters (ADCs). The measured values of undershoot  $(u_{meas})$  and overshoot  $(o_{meas})$  are fed to the minimum search algorithm, which exploits such data to modify the AGD timing parameters. A Pulse-Width Modulator (PWM) outputs the AGD control signals, eventually. For the sake of concisenesses, the proposed method is discussed referring to the turn on only, but the same procedure holds at the turn off as well.

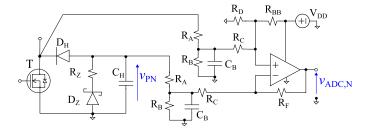

## A. Undershoot/overshoot voltage sensing

A negative peak detector  $(D_{\rm H}, C_{\rm H})$  followed by a differential amplifier is exploited, as shown in Fig. 13, to measure the  $v_{\rm DS}$  undershoot. When the power transistor is steadily off, the voltage across the hold capacitance  $(v_{\rm PN})$  is about zero as

Fig. 13. Sensing circuit exploited to measure the  $v_{\rm DS}$  undershoot.

$C_{\rm H}$  has discharged through  $R_{\rm Z}$ . This means that the opamp output  $(v_{\rm ADC,N})$  is saturated to the positive supply voltage as  $v_{\rm DS}=V_{\rm PS}$ . As T is turned on and the  $v_{\rm DS}$  undershoot occurs, the voltage  $v_{\rm PN}$  decreases equaling the  $v_{\rm DS}$  minimum expect for the voltage drop across the diode  $D_{\rm H}$ , which is named  $V_{\rm Dh}$  hereinafter. With the turn on oscillation decaying exponentially, the voltage across  $C_{\rm H}$  remains constant. At the same time, the opamp experiences an under damped transient due to its limited slew rate. Then, as long as the power transistor is steadily on, the amplifier output equals the difference between  $v_{\rm DS}$ , which is approximately zero, and  $v_{\rm PN}$ .

Once the power transistor is turned off,  $v_{\rm ADC,N}$  saturates again. In order to acquire a meaningful value of  $v_{\rm PN}$ , the voltage  $v_{\rm ADC,N}$  should be sampled with T is steadily on. Thus, with  $v_{\rm ADC,N}$  acquired  $\Delta t_{\rm ADC}$  after the  $v_{\rm ON1}$  rising edge, it is

$$u_{\text{MEAS}} = \frac{v_{\text{ADC,N}}(t_1) - V_{\text{B}}}{\left(\frac{R_{\text{A}}}{R_{\text{A}} + R_{\text{B}}} \frac{R_{\text{F}}}{R_{\text{C}} + (R_{\text{A}}||R_{\text{B}})}\right) \left(1 - \frac{\Delta t_{\text{ADC}}}{R_{\text{Z}}C_{\text{H}}},\right)} + V_{\text{Dh}},$$

(6)

where  $V_{\rm B}$  is an offset added to the opamp output, the discharge of the hold capacitance is linearly approximated, and it is assumed  $R_{\rm F}=R_{\rm BB}||R_{\rm D}$ .

## B. Minimum search algorithm

On the basis of  $u_{\rm MEAS}, o_{\rm MEAS}$ , the algorithm should determined the AGD parameters to attain non oscillating transients. As suggested in previous works, this problem can be thought of as a minimum search [10], [11], for which several algorithms are available [36]. Those methods require the definition of a cost function, which should include both the switching energy and the oscillation amplitude for the considered application. Referring to Fig. 10(a) and 11, the selection of the left-most local minimum resulted in a non oscillating waveform. The resulting switching trajectory is characterized by the lowest losses, as the  $v_{\rm DS}$  fall time is lower. Thus, it is possible to exploit the  $v_{\rm DS}$  undershoot itself as the cost function to be minimized, provided that the algorithm can track the left most minimum. To this purpose, the method is divided into two steps, which are described in what follows.

1) Left-most minimum detection: This step is executed once at the power on with the aim of approximately locating the left most minimum. The AGD controller tests all possible values of  $d_{\rm ON}, t_{\rm ON}$  in the  $(d_{\rm ON,MIN}, d_{\rm ON,MAX}), (t_{\rm ON,MIN}, t_{\rm ON,MAX})$  ranges with a coarse time step, and store the corresponding  $u_{\rm MEAS}$  values in the microcontroller. Then, such a matrix

Fig. 14. Flowchart of the control algorithm during the minimum tracking phase.

Fig. 15. Timing of the control algorithm during the tracking phase applied to the power transistor turn on.

is scanned to find all local minima by exploiting an  $O(N^2)$  algorithm. The minimum with the lowest  $t_{\rm ON}$  is considered, and its coordinates are taken as the starting point of the next step. It is worth noticing that such an operation is performed only once at the power on, and it is required to account for parameter spread. By choosing a fixed initial set of AGD parameters, e.g., by inspection of the color map shown in Fig. 10(a), or a random set, the algorithm may converge to a local minimum different than the left-most one, and result in higher switching losses. As the position of such minimum is affected by several parameters, this first step allows the AGD to detect it autonomously.

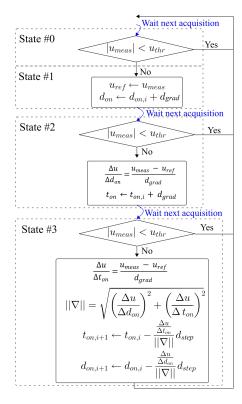

2) Minimum tracking: With the initial set of AGD parameters defined, a gradient method can be applied to refine them further and to track the minimum undershoot under variations of operating conditions. By defining a target  $u_{\rm THR}$ ,

Fig. 16. Oscilloscope screen shot showing the convergence of the proposed algorithm at the power on. Channel 1 was connected to measure  $v_{\rm DS}$ , 3 and 4 to debug outputs of the microcontroller.

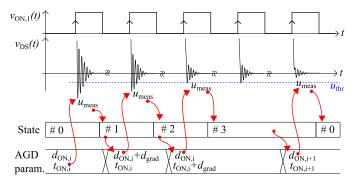

the gradient method modifies the AGD parameters to attain a  $u_{\rm MEAS}$  lower or equal than  $u_{\rm THR}$ . This algorithm can be discussed referring to the flowchart shown in Fig. 14, and to the timing diagram reported in Fig. 15. After a  $\Delta t_{\rm ADC}$ delay from each T turn on transient, a new  $u_{MEAS}$  sample is available from the ADC peripheral. With  $u_{\rm MEAS} > u_{\rm THR}$  and AGD parameters equal to  $d_{ON,i}, t_{ON,i}$ , the algorithm moves from state #0 to #1, and the current undershoot is stored in  $u_{\rm REF}$  as reference. Before the next T turn on, the  $d_{\rm ON}$ parameter of the AGD is increased by  $d_{grad}$ . As the new  $u_{\rm MEAS}$  is available, the discrete partial derivative of  $u_{\rm MEAS}$ with respect to  $d_{\rm ON}$  is evaluated, and the  $t_{\rm ON}$  value increased by  $d_{\text{grad}}$ . At the next switching cycle, the partial derivative of  $u_{\rm MEAS}$  with respect to  $t_{\rm ON}$  is evaluated, and the local gradient  $(||\nabla||)$  can be estimated. Thus, the new AGD parameters are modified according to the direction, which minimizes the undershoot the most. Finally, the algorithm moves back to state # 0. Such a procedure is performed  $k_{\text{item}}$  times, i.e., until an undershoot value lower than the threshold is found.

## VI. EXPERIMENTAL VALIDATION

The DC-DC converter and the experimental setup introduced in Sect. IV were used again to validate the adaptive method. With the algorithm converged to a proper solution, a comparison with the same AGD exploited in an open loop manner, is carried out under load current variations. Then, the transient response of the proposed method is investigated to estimate the convergence time of the algorithm. Finally, the proposed method is set against the use of a standard technique to suppress ringing.

## A. Assessment of the proposed algorithm

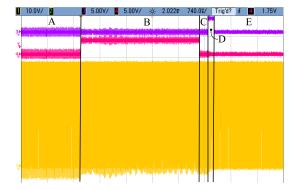

The search algorithm described in Sect. V-B was implemented on the microcontroller enslaved to the AGD. This controller can output  $v_{\mathrm{ON},1}, v_{\mathrm{ON},2},...$  with a 250 ps time resolution, and it was set  $\Delta t_{\mathrm{ADC}}=1~\mu\mathrm{s}.$  In Fig. 16, the waveforms related to the proposed algorithm are shown, and each step identified by a letter (A,..,E). During step A, the AGD was not tuned, and when the algorithm started to run, it detected the position of left most minimum. To this purpose, it was set  $d_{\mathrm{ON},\mathrm{MAX}}=t_{\mathrm{ON},\mathrm{MAX}}=50$  ns and a coarse time step of 2

Fig. 17. Comparison of the  $v_{\rm DS}$  in (a) time and (b) frequency domain for the AGD exploiting the adaptive method with 1 A (solid), and 5 A (dashed) load current. Dotted line refers to an open loop AGD tuned at 1 A and then exploited at 5 A.

ns exploited. As the power transistor is turned on and off with a 100 kHz switching frequency, the time required to test all  $d_{\rm ON}, t_{\rm ON}$  values was equal to 3.3 ms. This is the duration of step B indeed. It is worth noticing that the  $v_{\rm DS}$  undershoot is not constant, but it varies as the AGD parameters are modified cycle by cycle. The algorithm scanned the matrix in step C and found an approximated position of the left most local minimum. It resulted a  $d_{ON}$ =25 ns and  $t_{ON}$ =13 ns for the Buck operating at  $V_{PS}$ = 48 V and  $I_{LOAD}$ = 1 A. Then, the undershoot affecting the  $v_{\rm DS}$  voltage was reduced from 1.54 V to 1.4 V during the tracking phase (D step) in 170  $\mu$ s. The parameters of the gradient method were set to  $u_{\rm THR}$ =1.4 V,  $d_{\rm grad}$ =1.5 ns,  $d_{\rm step}$ =1.5 ns. The time required by the microcontroller to execute one iteration of the procedure depicted in Fig. 14 was equal to  $t_{\text{iter}}$ =40  $\mu$ s, as three  $u_{\text{meas}}$  measurements are needed to evaluate a new set of AGD parameters and the last step (state #3) requires an extra switching cycle to complete the calculations. Indeed, four iterations of the procedure were required to obtain  $u_{\rm meas}$  <  $u_{\rm thr}$  (step D in Fig. 16). As the algorithm was able to converge, it monitored the  $v_{\rm DS}$ undershoot during step E.

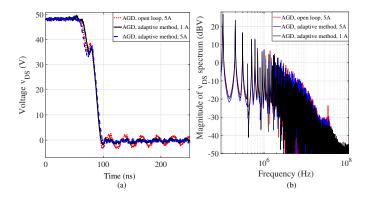

### B. Comparison with open loop AGD

The proposed adaptive method was later validated against load current variations, and compared to an open loop control. More precisely, at the end of step D, the resulting  $v_{\rm DS}$  is shown in Fig. 17(a) by solid line for an initial current of 1 A. By increasing  $I_{LOAD}$  to 5 A, the algorithm modifies the  $d_{\rm ON}, t_{\rm ON}$  values, resulting in the  $v_{\rm DS}$  waveform shown by dotted line. Both curves are not affected by oscillations, and the corresponding frequency spectra, are not characterized by a peak at  $f_{ON}$ , as shown in Fig. 17(b). On the contrary, with the AGD exploited in open loop, its parameters have been tuned at 1 A, and then the load current was increased. It resulted in the  $v_{\rm DS}$  shown in Fig. 17(a) by dashed line. The corresponding undershoot is higher than in case of the adaptive method. By comparing the  $v_{\rm DS}$  spectrum at 5 A, the peak related to the open loop control is 9 dB higher than with the adaptive method. Thus, the effectiveness of the presented technique was assessed under operating condition variations.

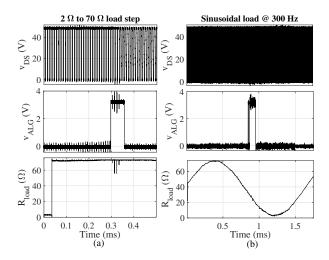

Fig. 18. Transient response of the adaptive method under (a) step and (b) sinusoidal variations of the load resistance.

TABLE I Comparison between CGD and AGD, at 48 V, 5 A

| Setup                          | $v_{ m DS}$ fall time | $v_{ m DS}$ undershoot | $ V_{DS}(j\omega) $ @ $f_{\mathrm{ON}}$ | η      |

|--------------------------------|-----------------------|------------------------|-----------------------------------------|--------|

| CGD, $R_{\rm G}$ =4.7 $\Omega$ | 23.5 ns               | -5.62 V                | -18 dBV                                 | 91.2 % |

| CGD, $R_{\rm G}$ =40 $\Omega$  | 58 ns                 | -2.5 V                 | -27.5 dBV                               | 88 %   |

| AGD, $R_{\rm G}$ =4.7 $\Omega$ | 31 ns                 | -1.1 V                 | -31 dBV                                 | 91 %   |

## C. Transient response under load variations

With the proposed method outperforming an open loop control of the AGD in steady state conditions, as discussed in Sect. VI.B, the transient response of the system was investigated. The time required by the algorithm to find a new set of AGD parameters depends on  $t_{iter}$ , which for the considered setup is equal to 40  $\mu$ s as discussed in Sect. VI.A, and on the number of iterations  $(k_{\text{iter}})$  required. The latter is in turn affected by the parameters of the gradient algorithm, i.e.,  $u_{\rm thr}, d_{\rm grad}, d_{\rm step}$  reported in Fig. 14, and by the initial set of  $d_{\rm ON}, t_{\rm ON}$ . Step and sinusoidal variations of the load were considered, as they are both of practical interest, resulting in the waveforms shown in Fig. 18(a) and (b), respectively. A digital output of the microcontroller ( $v_{ALG}$ ), which is driven high as long as the measured undershoot is higher than the threshold, was acquired by a digital oscilloscope to measure the time  $k_{\text{iter}}t_{\text{iter}}$ , i.e., the convergence time for load variations. As far as Fig. 18(a) is concerned, it corresponds to a 5 A to 0.2 A load current variations. In that case, the algorithm took 60  $\mu$ s to find a new set of suitable AGD parameters. However, this time is not constant as it depends on the starting  $d_{\rm ON}, t_{\rm ON}$  values. It was found that the convergence time spread in the [20  $\mu$ s, 450  $\mu$ s] range for both positive and negative current steps. Then, sinusoidal variations of the load were also investigated, as shown in Fig. 18(b). Also in this case, the algorithm was able to track the load variations on time, with the undershoot being higher than the threshold for approximately 10 % of the sine wave period.

Fig. 19. Comparison of the  $v_{\rm DS}$  in (a) time and (b) frequency domain for the AGD (solid) and the CGD with a gate resistance equal to 4.7 (dotted) and 40  $\Omega$  (dashed line) with 5 A load current.

Fig. 20. Conversion efficiency of the Buck converter with the AGD (solid) and the CGD with a low (dotted) and high (dashed lines) gate resistance.

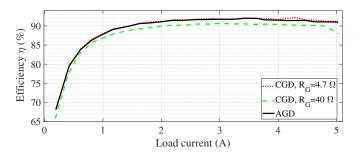

### D. Comparison with standard solution

The method was also compared to a standard solution to limit over- and under- voltages, i.e., the tuning of the gate resistance. Indeed, with  $v_{\rm ON2}, v_{\rm OFF2}$  not activated during transients, the designed AGD can be exploited as CGD, where the gate resistance  $(R_G)$  is set by  $R_{ON}$ ,  $R_{OFF}$  shown in Fig. 6 for the turn on and turn off, respectively. The resulting waveforms are shown in Fig. 19 for (a) the time domain, and (b) the frequency domain with a 5 A load current. These curves have been experimentally acquired and then combined for convenience. With the lowest gate resistance, i.e.,  $R_G$ =4.7  $\Omega$ , the  $v_{\rm DS}$  (dotted line) is affected by oscillations. The ringing is partially damped when a higher value (40  $\Omega$ ) is exploited, as shown by dashed line. The  $v_{\rm DS}$  curve is reported in solid line when the AGD is tuned by the adaptive method. This last waveforms is characterized by no peak at  $f_{ON}$  in the frequency domain. In order to compare further the two solutions, the values of  $v_{\rm DS}$  fall time (90% to 10%), undershoot, magnitude of the frequency spectrum at  $f_{ON}$ , and efficiency of the overall power converter are reported in Table I for a 5 A load current. More precisely, the efficiency was evaluated as the ratio between the power delivered to the load by the Buck converter and the input one. Although the last two cases ( $R_G$ =40  $\Omega$ and AGD) are similar in terms of undershoot and frequency peak reduction, the corresponding  $v_{\rm DS}$  fall time differs by 27 ns, which in turn results in a 3% lower efficiency than in case of the AGD. This aspect was further investigated, and the efficiency of the converter was measured for load current ranging from 0.2 A to 5 A. The results are shown in Fig. 20 for the AGD (solid) and the CGD with  $R_G$ =4.7  $\Omega$  (dotted) and 40  $\Omega$  (dashed line). The efficiency curve with the AGD exploited is overlapped with that with the oscillating CGD ( $R_{\rm G}$ =4.7  $\Omega$ ). Therefore, the proposed technique does not affect the conversion efficiency adversely. In contrast, with the CGD exploiting a 40  $\Omega$  gate resistance, the efficiency is lower than in case of the AGD for all load current higher than 1 A. To conclude, the discussed method resulted a better trade off between oscillations and losses than traditional solution.

#### VII. CONCLUSION

To limit over- and under- voltages during the transients of hard-switched power transistor, a low complexity AGD controlled by a novel adaptive method is described. Through the sensing of the  $v_{\rm DS}$  undershoot and overshoot, the technique tunes the AGD parameters to attain damped waveforms with minimum switching losses. As the method was entirely implemented on a resource-limited microcontroller, the technique described in this paper is more robust than those proposed in literature, as it is not based on any a-priori calculations or on some knowledge of the particular case study. Indeed, with respect to previous work, a true adaptive control of the AGD modulation pattern is achieved, which can be exploited to address parameter spread due to process variation, aging and temperature, as well as variations of operating condition. Delays of the AGD are automatically compensated too, meaning that the method is robust against different power transistors or different performance of the AGD in a hard-switched leg. The method was experimentally assessed, and it resulted in better switching performance with respect to open loop AGDs and traditional solutions. The transient response of the method was assessed too, resulting in a convergence time which allows the proposed technique to be applied in practical applications. Moreover, the proposed system lends itself well to integrating the AGD, the sensing circuit and the required logic in a single chip.

#### REFERENCES

- [1] A. Stippich, C. H. Van Der Broeck, A. Sewergin, A. H. Wienhausen, M. Neubert, P. Schülting, S. Taraborrelli, H. van Hoek, and R. W. De Doncker, "Key components of modular propulsion systems for next generation electric vehicles," *CPSS Transactions on Power Electronics* and Applications, vol. 2, no. 4, pp. 249–258, Dec. 2017.

- [2] O. Alatise, I. Kennedy, G. Petkos, K. Heppenstall, K. Khan, J. Parkin, A. Koh, and P. Rutter, "The Impact of Repetitive Unclamped Inductive Switching on the Electrical Parameters of Low-Voltage Trench Power nMOSFETs," *IEEE Transactions on Electron Devices*, vol. 57, no. 7, pp. 1651–1658, Jul. 2010.

- [3] Y. Zhang, S. Wang, and Y. Chu, "Analysis and Comparison of the Radiated Electromagnetic Interference Generated by Power Converters With Si MOSFETs and GaN HEMTs," *IEEE Transactions on Power Electronics*, vol. 35, no. 8, pp. 8050–8062, Aug. 2020.

- [4] T. Liu, R. Ning, T. T. Y. Wong, and Z. J. Shen, "Modeling and Analysis of SiC MOSFET Switching Oscillations," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 747–756, Sep. 2016.

- [5] N. Oswald, P. Anthony, N. McNeill, and B. H. Stark, "An Experimental Investigation of the Tradeoff between Switching Losses and EMI Generation With Hard-Switched All-Si, Si-SiC, and All-SiC Device Combinations," *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2393–2407, May 2014.

- [6] Y. Wu, S. Yin, H. Li, and W. Ma, "Impact of \$RC\$ Snubber on Switching Oscillation Damping of SiC MOSFET With Analytical Model," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 163–178, Mar. 2020.

- [7] F. Fiori, "On the use of Magnetically Coupled Resonant Snubbers to Mitigate the Electromagnetic Emission of Power Switching Circuits," *IEEE Transactions on Electromagnetic Compatibility*, vol. 64, no. 1, pp. 259–262, Feb. 2022.

- [8] E. Raviola and F. Fiori, "Investigations on the use of the power transistor source inductance to mitigate the electromagnetic emission of switching power circuits," *Signals*, vol. 2, no. 3, pp. 586–603, 2021. [Online]. Available: https://www.mdpi.com/2624-6120/2/3/36

- [9] H. C. P. Dymond, J. Wang, D. Liu, J. J. O. Dalton, N. McNeill, D. Pamunuwa, S. J. Hollis, and B. H. Stark, "A 6.7-GHz Active Gate Driver for GaN FETs to Combat Overshoot, Ringing, and EMI," *IEEE Transactions on Power Electronics*, vol. 33, no. 1, pp. 581–594, Jan. 2018.

- [10] Y. S. Cheng, D. Yamaguchi, T. Mannen, K. Wada, T. Sai, K. Miyazaki, M. Takamiya, and T. Sakurai, "High-Speed Searching of Optimum Switching Pattern for Digital Active Gate Drive to Adapt to Various Load Conditions," *IEEE Transactions on Industrial Electronics*, vol. 69, no. 5, pp. 5185–5194, May 2022.

- [11] R. Wang, L. Liang, Y. Chen, Y. Pan, J. Li, L. Han, and G. Tan, "Self-Adaptive Active Gate Driver for IGBT Switching Performance Optimization Based on Status Monitoring," *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 6362–6372, Jun. 2020.

- [12] S. Zhao, X. Zhao, A. Dearien, Y. Wu, Y. Zhao, and H. A. Mantooth, "An Intelligent Versatile Model-Based Trajectory-Optimized Active Gate Driver for Silicon Carbide Devices," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 429–441, Mar. 2020.

- [13] C. Krause, A. Bendicks, and S. Frei, "Frequency-Selective Reduction of Power Electronic Switching Noise by Applying Synthesized Gate Signals," in 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, Jul. 2021, pp. 100–105.

- [14] Y. Sukhatme, V. K. Miryala, P. Ganesan, and K. Hatua, "Digitally Controlled Gate Current Source-Based Active Gate Driver for Silicon Carbide MOSFETs," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 12, pp. 10121–10133, Dec. 2020.

- [15] S. Zhao, X. Zhao, Y. Wei, Y. Zhao, and H. A. Mantooth, "A Review of Switching Slew Rate Control for Silicon Carbide Devices Using Active Gate Drivers," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 4, pp. 4096–4114, Aug. 2021.

- [16] E.Raviola and F.Fiori, "A Critical Assessment of Open-Loop Active Gate Drivers Under Variable Operating Conditions," in 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, Jul. 2021, pp. 94–99.

- [17] Y. Ling, Z. Zhao, and Y. Zhu, "A Self-Regulating Gate Driver for High-Power IGBTs," *IEEE Transactions on Power Electronics*, vol. 36, no. 3, pp. 3450–3461, Mar. 2021.

- [18] Y. Noge, M. Shoyama, and M. Deng, "Active Gate Driver for High Power SiC-MOSFET Module with Source Current Feedback and P-D controller," in 2021 IEEE 12th Energy Conversion Congress & Exposition - Asia (ECCE-Asia), May 2021, pp. 1350–1353.

- [19] X. Du, Y. Wei, A. Stratta, L. Du, V. S. Machireddy, and A. Mantooth, "A Four-level Active Gate Driver with Continuously Adjustable Intermediate Gate Voltages," in 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2022, pp. 1379–1386.

- [20] J. Müting, P. Natzke, A. Tsibizov, and U. Grossner, "Influence of Process Variations on the Electrical Performance of SiC Power MOSFETs," *IEEE Transactions on Electron Devices*, vol. 68, no. 1, pp. 230–235, Jan. 2021.

- [21] J. Ke, Z. Zhao, P. Sun, H. Huang, J. Abuogo, and X. Cui, "Influence of Device Parameters Spread on Current Distribution of Paralleled Silicon Carbide MOSFETs," *Journal of Power Electronics*, vol. 19, no. 4, pp. 1054–1067, 2019.

- [22] C. Leonardi, A. Raciti, F. Frisina, R. Letor, and S. Musumeci, "A new power MOSFET model including the variation of parameters with the temperature," in *Proceedings of the 1998 Second IEEE International* Caracas Conference on Devices, Circuits and Systems. ICCDCS 98. On the 70th Anniversary of the MOSFET and 50th of the BJT. (Cat. No.98TH8350), Mar. 1998, pp. 261–266.

- [23] S. Liu, Y. Jiang, W. Sung, X. Song, B. Baliga, W. Sun, and A. Q. Huang, "Understanding high temperature static and dynamic characteristics of 1.2 kV SiC power MOSFETs," in 2016 European Conference on Silicon Carbide & Related Materials (ECSCRM), Sep. 2016, pp. 1–1.

- [24] D. J. Rogers and B. Murmann, "Digital Active Gate Drives using sequential optimization," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2016, pp. 1650–1656.

- [25] W. T. Cui, W. J. Zhang, J. Y. Liang, H. Nishio, H. Sumida, H. Nakajima, Y.-T. Hsieh, H.-H. Tsai, Y.-Z. Juang, W.-K. Yeh, and W. T. Ng, "A

- Dynamic Gate Driver IC with Automated Pattern Optimization for SiC Power MOSFETs," in 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD), May 2022, pp. 33–36.

- [26] G. Dadanema, M. Delhommais, F. Costa, J. L. Schanen, Y. Avenas, and C. Vollaire, "Analytical model for SiC based power converter optimization including EMC and thermal constraints," in 2017 International Symposium on Electromagnetic Compatibility EMC EUROPE, Sep. 2017, pp. 1–6.

- [27] C.Paul, Inductance: Loop and Partial. Wiley, 2009.

- [28] Y. Yang, Y. Wen, and Y. Gao, "A Novel Active Gate Driver for Improving Switching Performance of High-Power SiC MOSFET Modules," IEEE Transactions on Power Electronics, vol. 34, no. 8, pp. 7775–7787, Aug. 2019.

- [29] J. Wang, H. S.-h. Chung, and R. T.-h. Li, "Characterization and Experimental Assessment of the Effects of Parasitic Elements on the MOSFET Switching Performance," *IEEE Transactions on Power Electronics*, vol. 28, no. 1, pp. 573–590, Jan. 2013.

- [30] M. V. Quitadamo, E. Raviola, and F. Fiori, "A Criterion for an Optimal Switching of Power Transistors," in 2019 12th International Workshop on the Electromagnetic Compatibility of Integrated Circuits (EMC Compo), Oct. 2019, pp. 174–176.

- [31] M. Quitadamo, E. Raviola, and F. Fiori, "Investigation on the Switching Waveforms of GaN Power Devices to Gate Current Profiles," in 2019 International Conference on Power Electronics, Control and Automation (ICPECA), Nov. 2019, pp. 1–6.

- [32] Z. Li, J. Chai, H. Lu, and Y. Li, "An Active Gate Driver for Suppressing the Current Oscillation of SiC MOSFET," in 2021 IEEE 4th International Electrical and Energy Conference (CIEEC), May 2021, pp. 1–5.

- [33] E.Raviola and F.Fiori, "Experimental Investigations on the Tuning of Active Gate Drivers under Load Current Variations," in 2021 International Conference on Applied Electronics (AE), Sep. 2021, pp. 1–4.

- [34] IPB065N15N3 Datasheet, Accessed on: Dec.28, 2020. [Online]. Available: https://www.infineon.com/dgdl/Infineon-IPB065N15N3G-DS-v02\_01-en.pdf?fileId=db3a30432662379201266a0379d1225c

- [35] FDB031N08 Datasheet, Accessed on: Jun.24, 2022. [Online]. Available: https://www.onsemi.com/products/discrete-power-modules/mosfets/fdb031n08

- [36] E. M. Zakharova and I. K. Minashina, "Review of multidimensional optimization methods," *Journal of Communications Technology and Electronics*, vol. 60, no. 6, pp. 625–636, Jun. 2015.

Erica Raviola was born in Asti, Italy, in 1993. She received the M.Sc. and Ph.D. degrees in electronic engineering from Politecnico di Torino, Torino, Italy, in 2017 and 2021, respectively. She is currently a Researcher at Politecnico di Torino. Her research interests include power electronics analysis and design, electromagnetic compatibility, and internet of things application.

Franco Fiori received the Ph.D. degree in electronic engineering from the Polytechnic University of Torino, Turin, Italy, in 1997. From 1997 to 1998, he was with the Research and Development EMC Group, STMicroelectronics, Milan, Italy, as a Leader. In 1999, he joined as a Researcher with the Polytechnic University of Torino, where he is currently a Professor in electronics and the Scientific Director of the Microelectronics EMC Laboratory. In his academic career, he has served as a PI in several national and international research projects,

mostly on chip level EMC and power electronics. He has authored or coauthored more than 200 papers published in international journals and conference proceedings. His research interests include analog circuit design, power electronics, smart power devices, and electromagnetic compatibility.