# STATUS OF THESIS

Title of thesis

I,

# STUDY OF HIGH FREQUENCY RESONANT GATE DRIVER FOR ZERO VOLTAGE SWITCHED SYNCHRONOUS RECTIFIER BUCK CONVERTER (ZVS-SRBC) CIRCUIT

### NOR ZAIHAR YAHAYA

hereby allow my thesis to be placed at the Information Resource Center (IRC) of Universiti Teknologi PETRONAS (UTP) with the following conditions:

- 1. The thesis becomes the property of UTP

- 2. The IRC of UTP may make copies of the thesis for academic purposes only.

- 3. This thesis is classified as

|   | Co |

|---|----|

| Х | No |

onfidential

Non-confidential

If this thesis is confidential, please state the reason:

The contents of the thesis will remain confidential for \_\_\_\_\_ years.

Remarks on disclosure:

Endorsed by:

Permanent address:

517 KG MERAWAN INDAH SIMPANG PULAI, 31300 KG KEPAYANG, PERAK. Name of Supervisor:

ASSOC. PROF. DR. MUMTAJ BEGAM

Date : \_\_\_\_\_

Date : \_\_\_\_\_

# UNIVERSITI TEKNOLOGI PETRONAS

# STUDY OF HIGH FREQUENCY RESONANT GATE DRIVER FOR ZERO VOLTAGE SWITCHED SYNCHRONOUS RECTIFIER BUCK CONVERTER (ZVS-SRBC) CIRCUIT

by

# NOR ZAIHAR YAHAYA

The undersigned certify that they have read, and recommend to the Postgraduate Studies Programme for acceptance this thesis for the fulfillment of the requirements for the degree stated.

| Signature:          |                                   |

|---------------------|-----------------------------------|

| Main Supervisor:    | ASSOC. PROF. DR. MUMTAJ BEGAM     |

| Signature:          |                                   |

| Co-Supervisor:      | ASSOC. PROF. DR. MOHAMMAD AWAN    |

| Signature:          |                                   |

| Head of Department: | ASSOC. PROF. DR. NOR HISHAM HAMID |

| Date:               |                                   |

| Date.               |                                   |

# STUDY OF HIGH FREQUENCY RESONANT GATE DRIVER FOR ZERO VOLTAGE SWITCHED SYNCHRONOUS RECTIFIER BUCK CONVERTER (ZVS-SRBC) CIRCUIT

by

# NOR ZAIHAR YAHAYA

# A Thesis

Submitted to the Postgraduate Studies Programme

as a Requirement for the Degree of

DOCTOR OF PHILOSOPHY

# ELECTRICAL AND ELECTRONIC ENGINEERING DEPARTMENT

UNIVERSITI TEKNOLOGI PETRONAS

BANDAR SERI ISKANDAR, PERAK

AUGUST 2011

## DECLARATION OF THESIS

Title of thesis

I,

## STUDY OF HIGH FREQUENCY RESONANT GATE DRIVER FOR ZERO VOLTAGE SWITCHED SYNCHRONOUS RECTIFIER BUCK CONVERTER (ZVS-SRBC) CIRCUIT

# NOR ZAIHAR BIN YAHAYA

hereby declare that the thesis is based on my original work except for quotations and citations which have been duly acknowledged. I also declare that it has not been previously or concurrently submitted for any other degree at UTP or other institutions.

Witnessed by:

Signature of Author

Permanent address:

Name of Supervisor:

ASSOC. PROF. DR. MUMTAJ BEGAM

Signature of Supervisor

517 KG MERAWAN INDAH

SIMPANG PULAI

31300 KG KEPAYANG, PERAK

| Date : | Date : |  |

|--------|--------|--|

|        |        |  |

# DEDICATION

Above all I want to dedicate this work

To my **PARENTS** for their loving care

To my wife, NOR ADELA DINYATI for her caring love

To my children:

NAIM ZAFRAN

NAZRIN AQASHAH

### ACKNOWLEDGEMENTS

I would like to express my sincere appreciation to my supervisors, Assoc. Prof. Dr. Mumtaj Begam and Assoc. Prof. Dr. Mohammad Awan, who have never given up guiding me and correcting the mistakes I made, encouraged me to broaden my viewpoint and taught me the direction of my project. Their patience and dedication in directing to success and their goal of providing a reliable research working environment have helped me to complete my work successfully. Under their supervision, I grew professionally and they have showed me new challenges in my career.

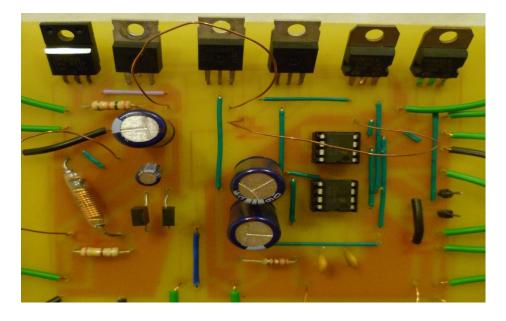

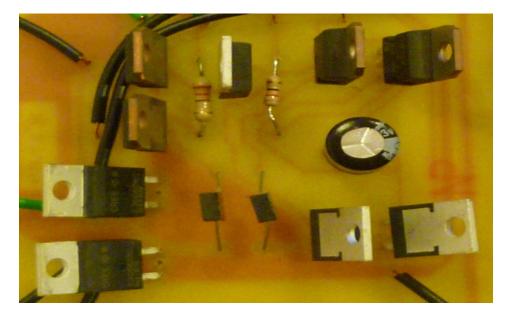

Great thanks also go to Assoc. Prof. Dr. Nor Hisham Hamid and all my electrical engineering technicians for their critiques and suggestion in my work and specially to Mr. Isnani Alias for his assistance in preparing the printed circuit board.

I am very grateful to my parents who taught me the meaning of struggle in this life. I would also like to express my deep indebtedness to my wife and my children for their true love and support. Their love is the power in my life and always makes my life more colorful. Finally, I would like to acknowledge the Staff Development Program (SDP) for allowing me to further my studies at Universiti Teknologi PETRONAS.

### ABSTRACT

In this work, a new Synchronous Rectifier Buck Converter (SRBC) circuit is proposed that reduces low switching and conduction losses. Moreover, the Miller effect has also been reduced. The limitations of existing single-channel resonant gate driver (S-CRGD) is studied to determine the optimized parameter values in terms of duty cycle, dead time and resonant inductance. The findings result in designing the new SRBC circuit's symmetrical dual-channel resonant gate drive (D-CRGD). The aim is to generate low switching and gate drive losses by operating in Zero Voltage Switching (ZVS) and lower on-state drain voltage conditions. It is found that the SRBC can operate effectively at 1 MHz compared to the conventional SRBC in solving the issues of dead time and effect of switching frequency. Experimental results are presented to validate the analysis of the proposed design procedure and to demonstrate the performance of the proposed approach. In addition, several gate drive control schemes such as Fixed Dead Time (FDT), Adaptive Gate Drive (AGD) and Predictive Gate Drive (PGD) have been simulated and the results show that FDT can operate SRBC correctly with shorter dead time and eventually reduce body diode conduction loss. Even though FDT is prone to cross-conduction effect, the design stage is simple. Apart from this, AGD and PGD control schemes have also shown high level of efficiency. However, AGD generates more losses which makes PGD preferable in achieving a highly efficient converter although there are advantages in FDT scheme.

Keywords:GateDrive,HighFrequency,ResonantSnubberNetwork,SynchronousRectifierBuckConverter.

### ABSTRAK

Di dalam hasil kerja ini, litar peronta segerak penerus (SRBC) yang baru telah dicadangkan bagi mengurangkan kehilangan pengaliran. Selain itu, kesan Miller juga telah berkurangan. Tujuan utama hasil kerja ini adalah untuk memahami keterbatasan reka bentuk litar get pemacu yang boleh menjejaskan prestasi litar. Penyelaku Pspice digunakan untuk menentukan nilai optimum pemacu galah tiang elu yang meliputi kitaran suis hidup, waktu mati dan kearuhan salunan. Litar saluran tunggal pemacu get resonans (S-CRGD) dinilai yang memberikan hasil dalam reka bentuk get pemacu salunan saluran simetri (D-CRGD) untuk litar SRBC. Tujuannya adalah untuk menghasilkan pensuisan rendah dan pengurangan get pemacu beroperasi di penguisan voltan sifar (ZVS). Ini menunjukkan bahawa SRBC boleh beroperasi secara efektif pada julat 1 MHz berbanding dengan litar lazim. Keputusan kajian berdasarkan prototaip 15-W diusulkan untuk mengesahkan analisis tatacara rekabentuk yang dicadangkan dan untuk menunjukkan prestasi dari pendekatan yang dicadangkan. Selain itu, beberapa skim kawalan get pemacu telah diselakukan dan hasilnya menunjukkan bahawa waktu mati tetap (FDT) dapat membantu mendorong SRBC mengurangkan kerugian pengaliran tubuh diod. Walaupun FDT terdedah terhadap kesan lintas pengaliran, tahap reka bentuknya adalah mudah. Selain itu, pemacu get suai (AGD) dan pemacu get ramalan (PGD) skim kawalan juga menunjukkan tahap kecekapan yang tinggi. Namun, AGD terdapat beberapa kekurangan. Hal ini menjadikan PGD lebih baik walaupun terdapat kelebihan dalam skim FDT.

Kata kunci: Skim Litar Get Pemacu, Frekuensi Tinggi, Rangkaian Resonan, Litar Peronta Segerak Penerus

### COPYRIGHT

In compliance with the terms of the Copyright Act 1987 and the IP Policy of the university, the copyright of this thesis has been reassigned by the author to the legal entity of the university,

Institute of Technology PETRONAS Sdn Bhd.

Due acknowledgement shall always be made of the use of any material contained in, or derived from, this thesis.

© Nor Zaihar Yahaya, 2011 Institute of Technology PETRONAS Sdn Bhd All rights reserved.

# TABLE OF CONTENTS

| STATU  | JS OF | THESIS                                                             | i |

|--------|-------|--------------------------------------------------------------------|---|

| APPRO  | OVAL  | PAGE i                                                             | i |

| TITLE  | PAGI  | E ii                                                               | i |

| DECLA  | ARAT  | 'ION iv                                                            | V |

|        |       | )N                                                                 |   |

| ACKN   | OWL   | EDGEMENT v                                                         | i |

| ABST   | RACT  | vi                                                                 | i |

| ABST   | RAK   | vii                                                                | i |

|        |       | Г х                                                                |   |

|        |       | CONTENTS                                                           |   |

| LIST C | OF TA | BLESxii                                                            | i |

|        |       | SURES xv                                                           |   |

| LIST C | OF AB | BREVIATIONS xix                                                    | K |

| LIST C | OF SY | MBOLS xx                                                           | K |

|        |       |                                                                    |   |

| CHAP   |       |                                                                    |   |

| 1.     | INTR  | RODUCTION                                                          |   |

|        | 1.1   | Chapter Overview                                                   |   |

|        |       | Research Rationale                                                 |   |

|        | 1.3   | Research Objectives                                                |   |

|        | 1.4   | Research Scope                                                     |   |

|        | 1.5   | Chapter Summary                                                    | 3 |

| 2.     | LITE  | RATURE REVIEW                                                      | 5 |

|        | 2.1   | Chapter Overview                                                   |   |

|        | 2.2   | 1                                                                  | 5 |

|        | 2.3   | Review of Gate Drive Techniques                                    |   |

|        |       | 2.3.1 Hard Switching Conventional Gate Drive Circuit               |   |

|        |       | 2.3.2 Switching Requirement and Losses in SRBC 10                  |   |

|        |       | 2.3.2.1 Switching Characteristics of MOSFET                        |   |

|        |       | 2.3.2.2 Turn-On and Off Characteristics                            |   |

|        | 2.4   | Resonant Gate Drive Circuit                                        | 5 |

|        |       | 2.4.1 S-CRGD Circuit                                               |   |

|        |       | 2.4.2 Alternatives on S-CRGD Circuit Topologies                    |   |

|        | 2.5   | Resonant Switching                                                 |   |

|        | 2.6   | Q-Factor, Inductor Size and Performance of S-CRGD Circuit          | 3 |

|        | 2.7   | Summary of S-CRGD Topology Characteristics                         |   |

|        | 2.8   | Synchronous Rectifier Buck Converter (SRBC) Power Stage Circuit 28 | 3 |

|    |       | 2.8.1 Switching of SRBC Circuit                            |     |

|----|-------|------------------------------------------------------------|-----|

|    |       | 2.8.2 Dead Time and Cross Conduction                       | 32  |

|    |       | 2.8.3 <i>S</i> <sub>2</sub> Body Diode Conduction          | 33  |

|    |       | 2.8.4 MOSFET's Switching and Conduction Losses             |     |

|    |       | 2.8.5 Gate and Reverse Recovery Losses of Driving MOSFET i |     |

|    |       | SRBC                                                       | 36  |

|    | 2.9   | Ideal Operating Waveforms of SRBC                          |     |

|    |       | 2.9.1 Soft-Switching Technique in SRBC                     |     |

|    |       | 2.9.2 Selection of Operating Resonance Condition           | 40  |

|    | 2.10  | Gate Drive Control Scheme for SRBC                         |     |

|    |       | 2.10.1 Fixed Dead Time                                     |     |

|    |       | 2.10.2 Adaptive Gate Drive                                 |     |

|    | 0.11  | 2.10.3 Predictive Gate Drive                               |     |

|    | 2.11  | Load Variation on SRBC.                                    |     |

|    |       | 2.11.1 Continuous Conduction Mode                          |     |

|    | 2 1 2 | 2.11.2 Discontinuous Conduction Mode                       |     |

|    |       | Improving SRBC Weaknesses                                  |     |

|    | 2.13  | Chapter Summary                                            | 51  |

| 3. | мет   | HODOLOGY                                                   | 52  |

| 5. | 3.1   | Chapter Overview                                           |     |

|    | 3.2   | Parameter Limitations on S-CRGD Circuit                    |     |

|    | 5.2   | 3.2.1 Power Stage Simulation Setup                         |     |

|    |       | 3.2.1.1 Effects of Duty Ratio                              |     |

|    |       | 3.2.1.2 Effects of Dead Time                               |     |

|    |       | 3.2.1.3 Effects of Resonant Inductor                       |     |

|    |       | 3.2.2 Experimental Setup of S-CRGD Circuit                 |     |

|    | 3.3   | New D-CRGD Circuit                                         |     |

|    | 0.0   | 3.3.1 Experimental Setup of D-CRGD Circuit                 |     |

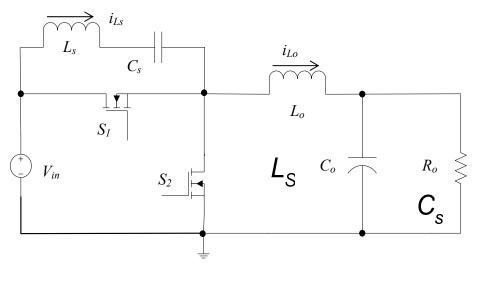

|    | 3.4   | New SRBC Circuit                                           |     |

|    | 3.5   | Chapter Summary                                            |     |

|    |       | 1 5                                                        |     |

| 4. | RES   | ULTS AND DISCUSSIONS                                       | 65  |

|    | 4.1   | Chapter Overview                                           | 65  |

|    | 4.2   | Simulation of S-CRGD Circuit                               | 65  |

|    |       | 4.2.1 Optimization of Duty Ratio                           | 67  |

|    |       | 4.2.2 Optimization of Resonant Inductor                    | 69  |

|    |       | 4.2.3 Optimization of Dead Time                            |     |

|    |       | 4.2.4 Q-Factor Vs Inductor                                 |     |

|    |       | 4.2.5 Loss Analysis of S-CRGD Circuit                      |     |

|    | 4.3   | Operation of S-CRGD: Experimental Results                  |     |

|    | 4.4   | Operation of D-CRGD: Simulation Results                    |     |

|    | 4.5   | Operation of SRBC: Simulation Results                      |     |

|    |       | 4.5.1 Resonant Configuration of New SRBC Circuit           |     |

|    | 4.6   | New SRBC Circuit: Experimental Results                     |     |

|    | 4.7   | Chapter Summary                                            | 100 |

| -  |       |                                                            | 101 |

| 5. |       | ENDED SIMULATION WORK: RESULTS AND DISCUSSIONS             |     |

|    | 5.1   | Chapter Overview                                           | 101 |

|    |       |                                                            |     |

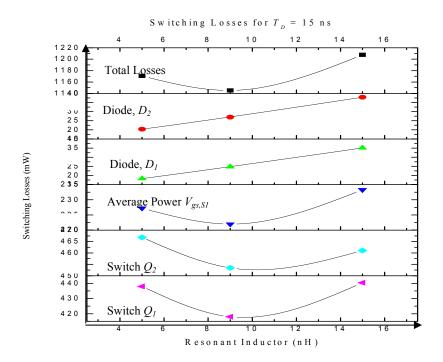

| 5.2 Switching Loss Analysis and Loading Effects of Three SRBC         | .101 |

|-----------------------------------------------------------------------|------|

| 5.2.1 Switching Loss Analysis                                         |      |

| 5.2.2 Load Effects Analysis                                           | .107 |

| 5.3 Dead Time Variation in New SRBC Circuit                           | .110 |

| 5.3.1 Circuit Performance for Several Dead Time of New SRBC           | .111 |

| 5.4 Resonant Inductor Current and Gate Voltage Analyses for Different | nt   |

| Dead Times                                                            | .113 |

| 5.5 Effects of Switching Frequency on New SRBC Circuit                | .114 |

| 5.5.1 Simulation Data: Effects of Switching Frequency                 | .115 |

| 5.6 Effects of Duty Ratio on New SRBC Circuit                         | .119 |

| 5.7 Numerical Verification on New SRBC Performance for $T_D$ of 15 ns | .120 |

| 5.8 Comparative Assessments of Gate Drive Control Scheme              | .121 |

| 5.8.1 Delay Controller Circuit                                        |      |

| 5.8.2 Comparison between FDT and AGD Control Schemes                  | .127 |

| 5.8.3 Comparison between FDT and PGD Control Schemes                  | .129 |

| 5.9 Efficiency Analyses of S-CRGD, SRBC and Gate Drive Control        | .135 |

| 5.10 Chapter Summary                                                  | .141 |

| 6. CONCLUSIONS                                                        | .143 |

| 6.1 Resonant Gate Drive Circuit                                       |      |

| 6.2 Synchronous Rectifier Buck Converter Circuit                      | .144 |

| 6.3 Gate Drive Control Schemes                                        |      |

| 6.4 Contribution of Work                                              | .145 |

| 6.5 Future Work                                                       | .146 |

| REFERENCES                                                            | .147 |

| LIST OF PUBLICATIONS                                                  |      |

| APPENDICES                                                            | .158 |

# LIST OF TABLES

| Table 2.1  | Summary of S-CRGD                                                              |

|------------|--------------------------------------------------------------------------------|

| Table 2.2  | Issues of Auxiliary Circuits in SRBC 40                                        |

| Table 2.3  | Summary of Resonant Operation in DC/DC Converter 42                            |

| Table 2.4  | Advantages and Disadvantages of Gate Drive Control Schemes                     |

| Table 3.1  | Simulation Parameters of S-CRGD for $f_s = 1$ MHz                              |

| Table 3.2  | Experimental Parameters of S-CRGD for $f_s = 1$ MHz                            |

| Table 3.3  | Simulation Parameters of D-CRGD for $f_s = 1$ MHz                              |

| Table 3.4  | Experimental Parameters of D-CRGD for $f_s = 1$ MHz                            |

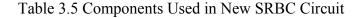

| Table 3.5  | Components Used in New SRBC Circuit                                            |

| Table 4.1  | Q-Factor Comparison of S-CRGD Performance                                      |

| Table 4.2  | S-CRGD: Comparison of Simulated and Experimental Data 81                       |

| Table 4.3  | New SRBC: Comparison of Simulated and Experimental Results100                  |

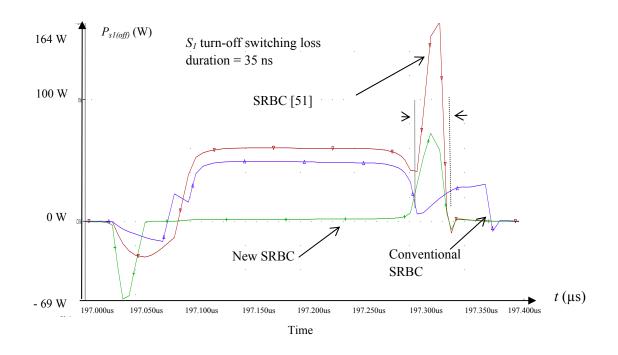

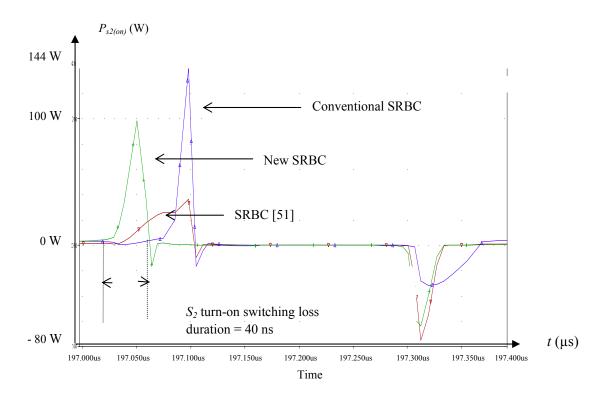

| Table 5.1  | Comparison in Switching Losses of SRBC at 10 $\Omega$ Load104                  |

| Table 5.2  | Average Switching Loss and Output Power of SRBC at 10 $\Omega$ Load110         |

| Table 5.3  | Dead Time Variation Settings for $f_s = 1$ MHz                                 |

| Table 5.4  | Parameter Evaluation for Different Dead Time of New SRBC111                    |

| Table 5.5  | Comparison in Power Losses for Different Dead Time of New SRBC112              |

| Table 5.6  | Total Switching Loss for Different <i>L<sub>s</sub></i> of New SRBC112         |

| Table 5.7  | $i_{LI}$ , Peak Time, Rise Time, Recovery Time and $di_{LI}/dt$ of $L_I$ for   |

|            | Different Dead Time of New SRBC113                                             |

| Table 5.8  | Rise time, Fall Time and $dv/dt$ of $S_1$ and $S_2$ for Different Dead Time of |

|            | New SRBC113                                                                    |

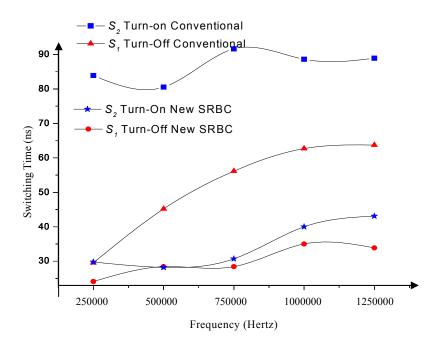

| Table 5.9  | Switching Time Comparison of Conventional and New SRBC115                      |

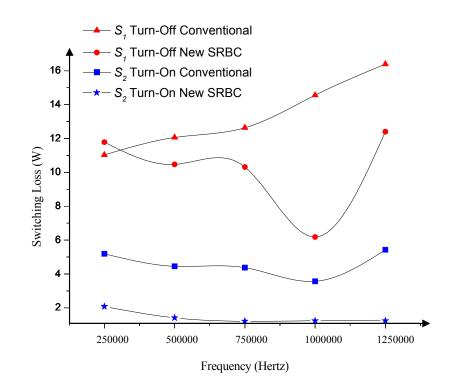

| Table 5.10 | Average Switching Loss Comparison of Conventional and New SRBC117              |

| Table 5.11 | Average Output Current and Body Diode Conduction Comparison of                 |

| Conventional and New SRBC |  |

|---------------------------|--|

|---------------------------|--|

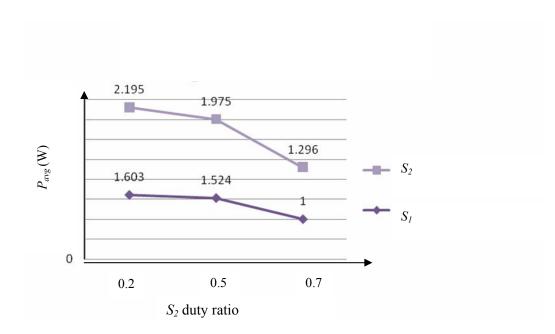

| Table 5.12 Switching Loss Analysis for Different S <sub>2</sub> Duty Ratio of New SRBC at   |

|---------------------------------------------------------------------------------------------|

| $T_D = 15 \text{ ns.}$                                                                      |

| Table 5.13 Comparison in Mathcad and PSpice Calculation at $T_D = 15$ ns of New             |

| SRBC                                                                                        |

| Table 5.14 Delay Line Settings of Adaptive SRBC Gate Drive    122                           |

| Table 5.15 PSpice Parameter Settings for $V_{tri}$ of Predictive SRBC Gate Drive126         |

| Table 5.16 PSpice Parameter Settings for $V_{pulse}$ of Predictive SRBC Gate Drive126       |

| Table 5.17 FTD, AGD- $Q_4$ and AGD- $S_2$ Analysis for $D = 0.20$                           |

| Table 5.18 Switching Loss Measurement Adopting PGD- $S_2$ for $D = 0.20$ 130                |

| Table 5.19 Comparison of PGD- $Q_4$ and PGD- $S_2$ for $V_{ref} = 0.27$ V, $D = 0.20$ and   |

| $T_D = 0$ ns                                                                                |

| Table 5.20 Comparison of FDT and PGD-S <sub>2</sub> at $V_{ref} = 0.3$ V for $D = 0.20$ and |

| $T_D = 15 \text{ ns.}$ 134                                                                  |

# LIST OF FIGURES

| Figure 2.1(a) Voltage Driven                                     | 7  |

|------------------------------------------------------------------|----|

| Figure 2.1(b) Resonant Driven                                    | 7  |

| Figure 2.2(a) Hard Switching Conventional Gate Drive             | 8  |

| Figure 2.2(b) Conventional Gate Drive Waveforms                  | 9  |

| Figure 2.3(a) Ideal Switch in Chopper Circuit                    | 11 |

| Figure 2.3(b) Turn-On and Off Characteristics of an Ideal Switch | 11 |

| Figure 2.4(a) MOSFET in Chopper Circuit                          | 12 |

| Figure 2.4(b) Turn-On and Off Characteristics of MOSFET          | 13 |

| Figure 2.5 MOSFET Parasitic Capacitances                         | 14 |

| Figure 2.6(a) Conventional S-CRGD                                | 19 |

| Figure 2.6(b) S-CRGD Waveforms                                   | 19 |

| Figure 2.7(a) Resonant Switching Turn-On                         | 22 |

| Figure 2.7(b) Resonant Switching Turn-Off                        | 22 |

| Figure 2.8 Center-Tapped D-CRGD                                  | 27 |

| Figure 2.9 Buck Converter                                        | 28 |

| Figure 2.10 Conventional SRBC Circuit                            | 29 |

| Figure 2.11 Switching in SRBC                                    | 31 |

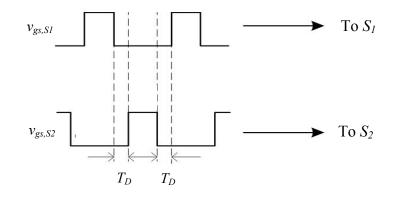

| Figure 2.12 Application of $T_D$ on Driving Pulses               | 32 |

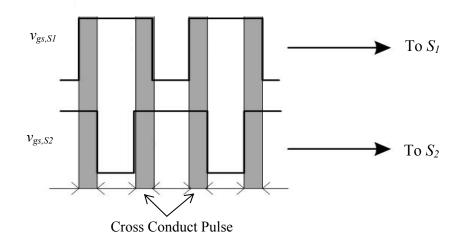

| Figure 2.13 Cross Conduction Waveform                            | 33 |

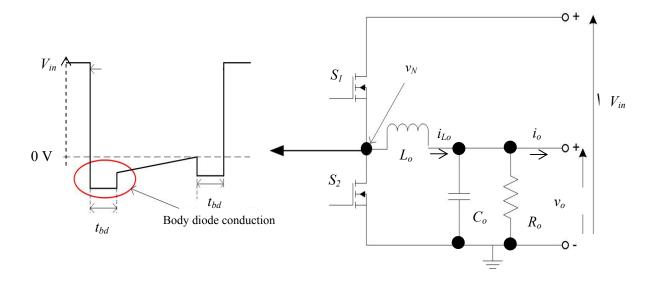

| Figure 2.14 Body Diode Conduction of <i>S</i> <sub>2</sub>       | 34 |

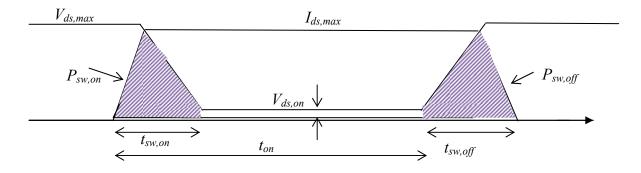

| Figure 2.15 MOSFET Switching Power Dissipation                   | 35 |

| Figure 2.16 MOSFET Turn-Off Model                                | 37 |

| Figure 2.17 Zero Delay SRBC Waveforms                            | 37 |

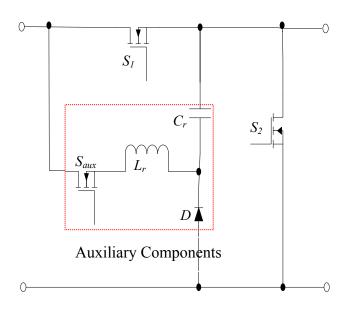

| Figure 2.18 ZVS-SRBC Auxiliary Components                        | 39 |

| Figure 2.19 SRBC Switch Node Voltage        | 44 |

|---------------------------------------------|----|

| Figure 2.20 Fixed Dead Time SRBC Gate Drive | 45 |

| Figure 2.21 | Adaptive Delay SRBC Gate Drive                                              | 46 |

|-------------|-----------------------------------------------------------------------------|----|

| Figure 2.22 | Predictive Control Timing                                                   | 47 |

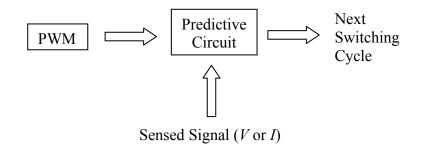

| Figure 2.23 | PGD Control Block Diagram                                                   | 47 |

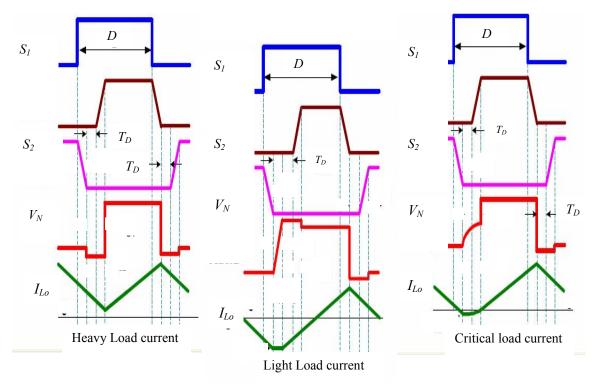

| Figure 2.24 | SRBC Load Effects                                                           | 49 |

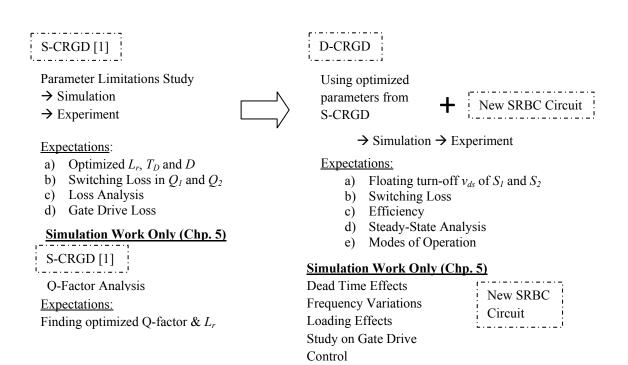

| Figure 3.1  | Summary of Methodology                                                      | 53 |

| Figure 3.2  | S-CRGD                                                                      | 54 |

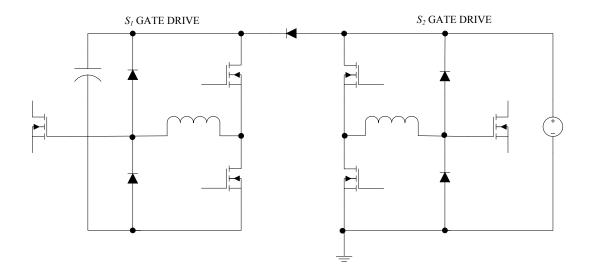

| Figure 3.3  | New D-CRGD                                                                  | 59 |

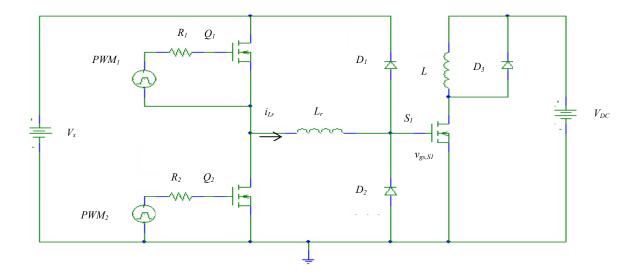

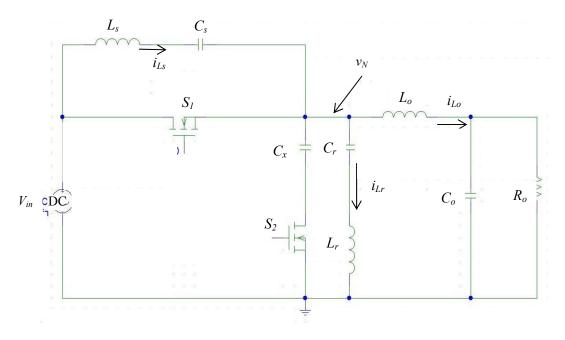

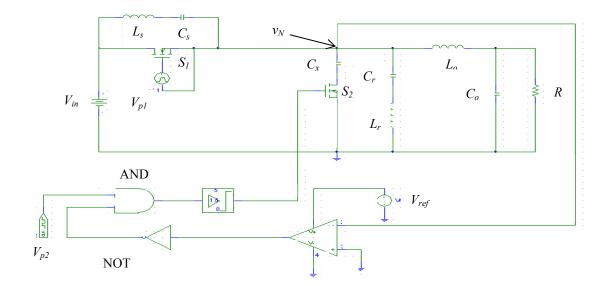

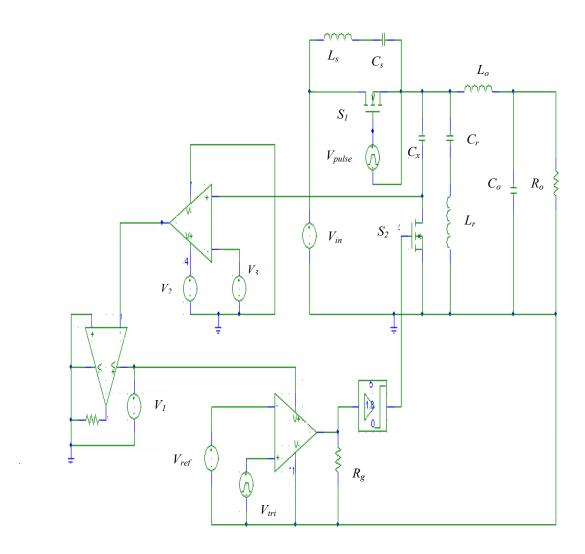

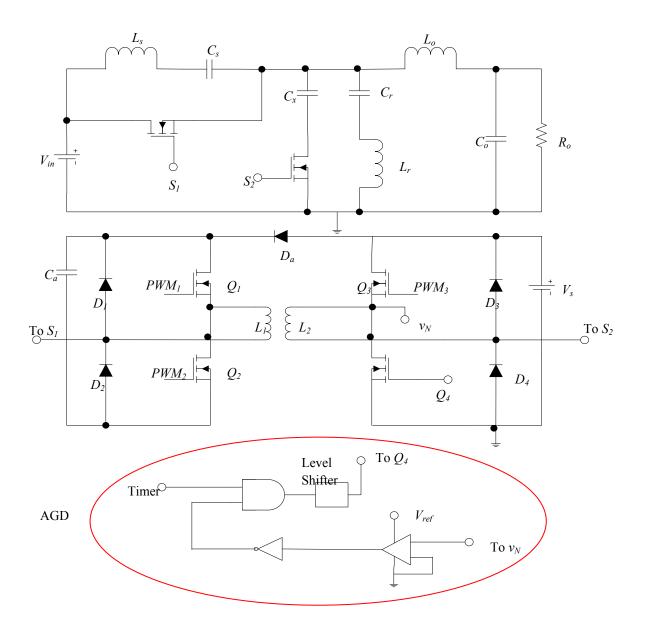

| Figure 3.4  | New SRBC                                                                    | 61 |

| Figure 4.1  | S-CRGD PSpice Simulated Waveforms                                           | 66 |

| Figure 4.2  | Charging and Discharging of $i_{Lr}$ with Respect to $Q_I$ Turn-On          | 68 |

| Figure 4.3  | S-CRGD $i_{Lr}$ versus $L_r$ (200 ns pulse, 15 ns $T_D$ ) PSpice Simulation | 70 |

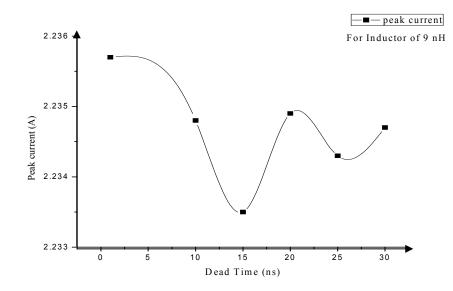

| Figure 4.4  | S-CRGD $I_{peak}$ versus $T_D$ (200 ns pulse, 9 nH inductor)                | 71 |

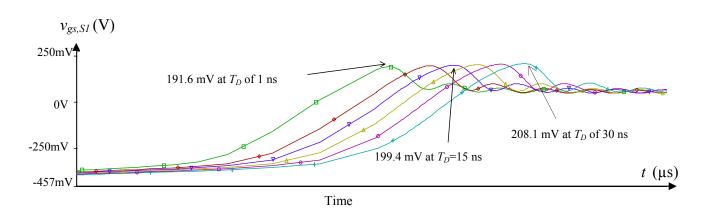

| Figure 4.5  | S-CRGD 9 nH $i_{Lr}$ Ringing versus $T_D$ PSpice Simulation                 | 72 |

| Figure 4.6  | S-CRGD 9 nH $v_{gs,SI}$ Ringing versus $T_D$ PSpice Simulation              | 72 |

| Figure 4.7  | S-CRGD 9 nH $i_{Lr}$ Peak Optimization versus $T_D$ PSpice Simulation       | 73 |

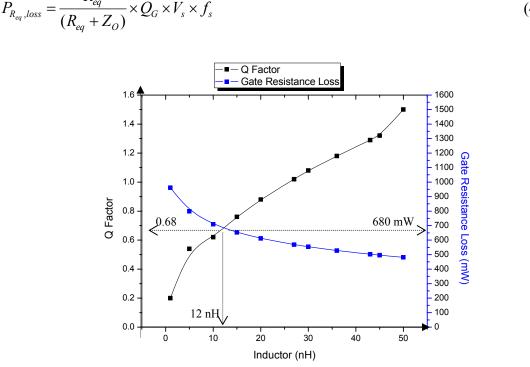

| Figure 4.8  | S-CRGD $L_r$ Inductance and Q Factor PSpice Simulation                      | 74 |

| Figure 4.9  | S-CRGD PSpice Simulation Switching Loss Distribution                        | 76 |

| Figure 4.10 | S-CRGD PWM Experimental Waveforms                                           | 77 |

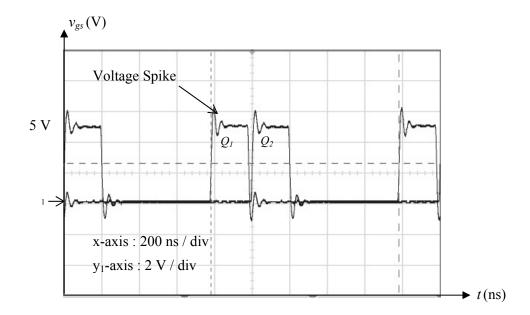

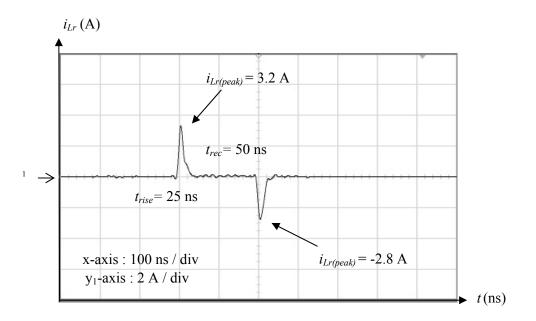

| Figure 4.11 | S-CRGD <i>i</i> <sub>Lr</sub> Experimental Waveform                         | 78 |

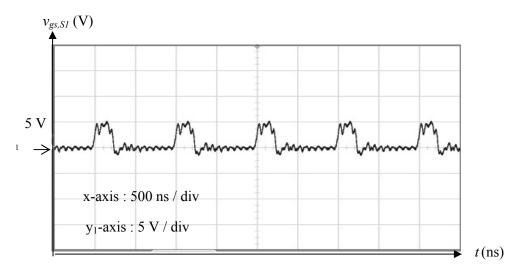

| Figure 4.12 | S-CRGD v <sub>gs,S1</sub> Experimental Waveform                             | 79 |

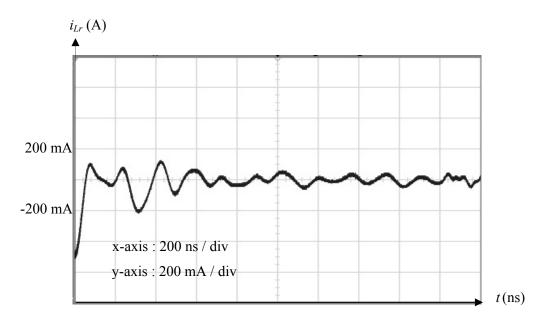

| Figure 4.13 | S-CRGD <i>i</i> <sub>Lr</sub> Experimental Turn-Off Oscillation             | 79 |

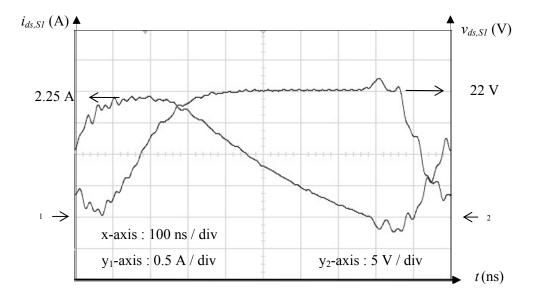

| Figure 4.14 | S-CRGD Experimental <i>i</i> <sub>ds</sub> versus <i>v</i> <sub>ds</sub>    | 80 |

| Figure 4.15 | S-CRGD $i_{ds}$ versus $v_{ds}$ PSpice Simulation                           | 81 |

| Figure 4.16 | New D-CRGD PSpice Simulation Waveforms                                      | 83 |

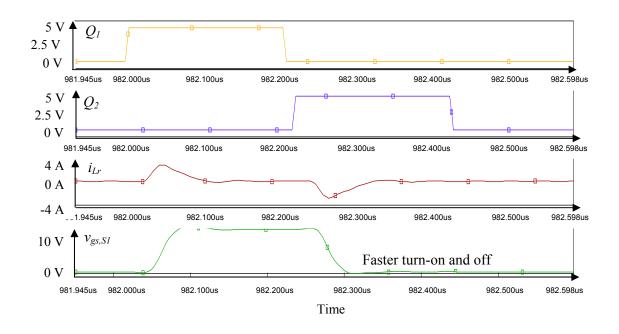

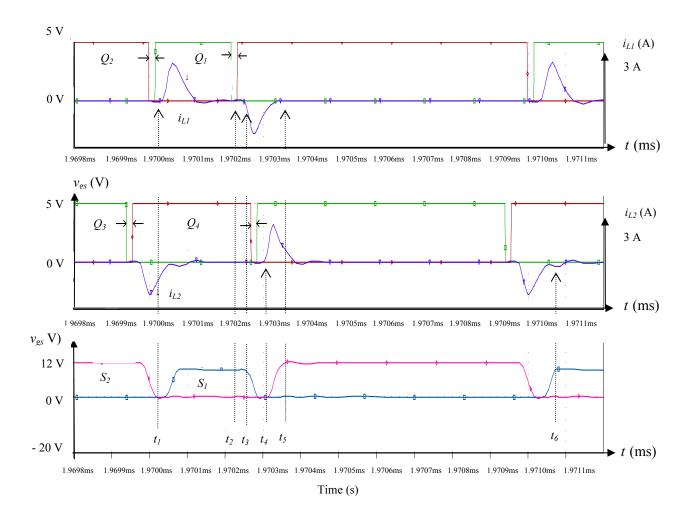

| Figure 4.17 | New SRBC 15 ns Delay Switch Gate Pulse PSpice Simulation                    | 84 |

| Figure 4.18 | New SRBC Waveforms                                                          | 87 |

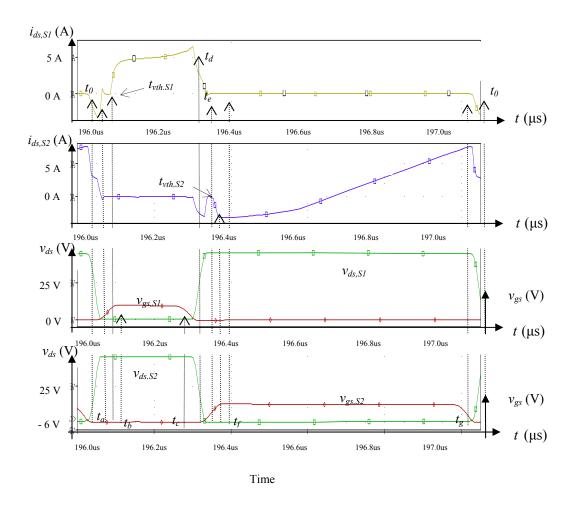

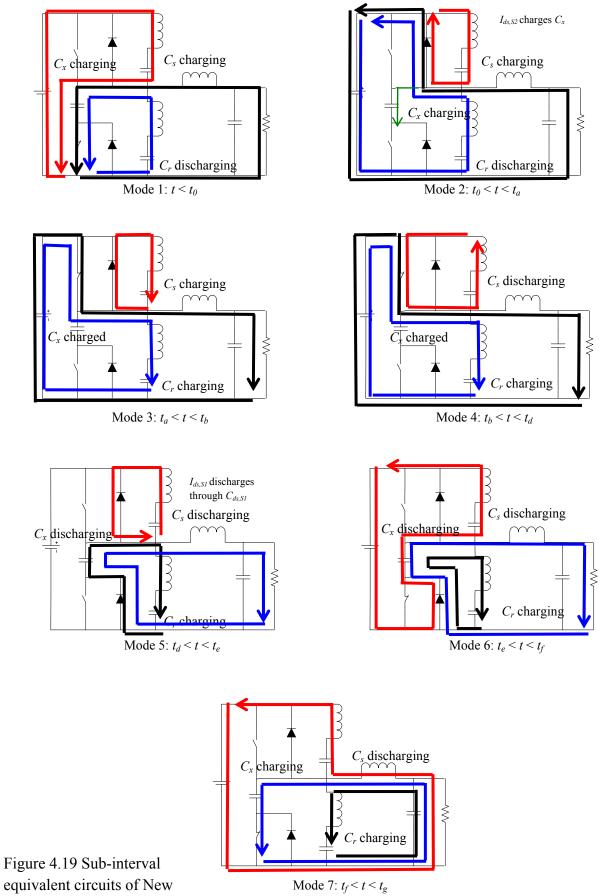

| Figure 4.19 | Sub-interval equivalent Circuit of New SRBC                                 | 89 |

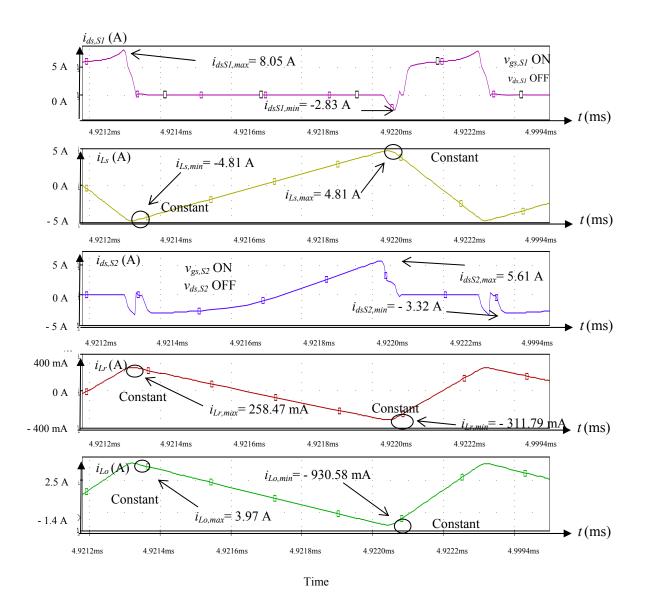

| Figure 4.20 | Currents of New SRBC Circuit                                                | 91 |

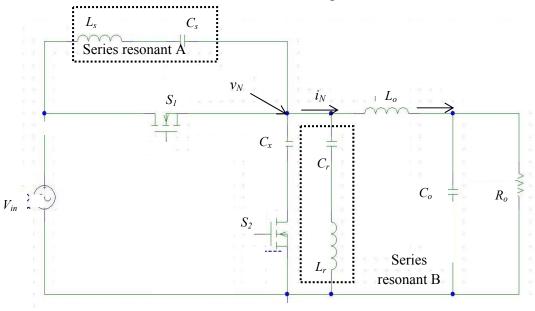

| Figure 4.21 | Series Resonant of New SRBC Circuit                                         | 92 |

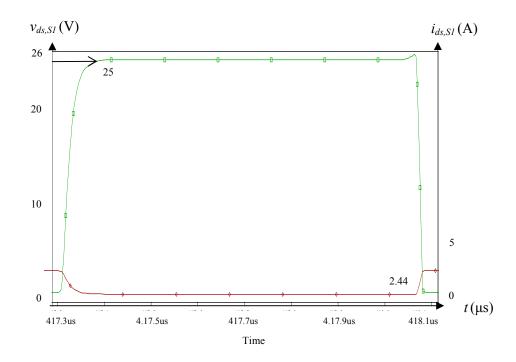

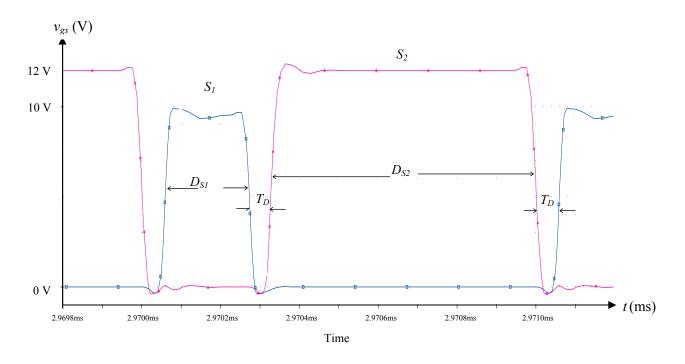

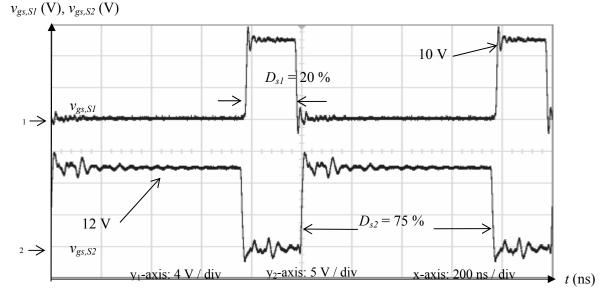

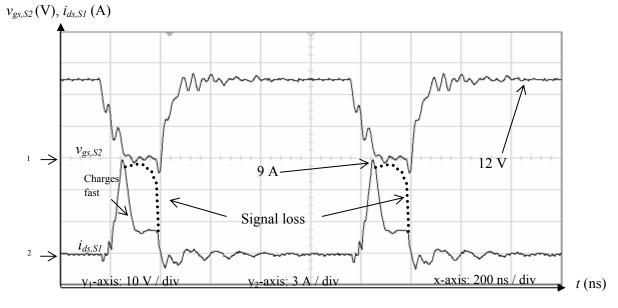

| Figure 4.22 | Gate Voltage of $S_1$ and $S_2$ Experimental Waveforms of New SRBC          | 94 |

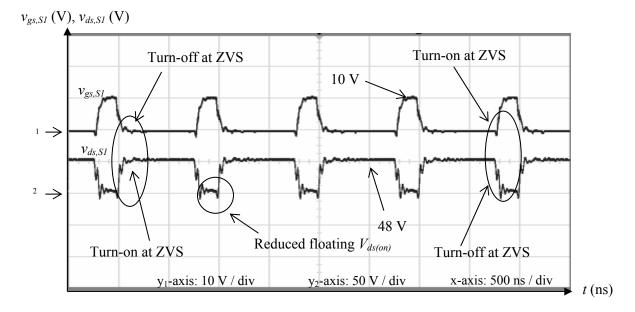

| Figure 4.23 | Gate | and | Drain | Voltages | of $S_I$ | Experimental | Waveforms | of New | V  |

|-------------|------|-----|-------|----------|----------|--------------|-----------|--------|----|

|             | SRBC | 2   |       |          |          |              |           |        | 94 |

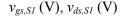

| Figure 4.24 | Gate and Drain Voltages of S <sub>2</sub> Experimental Waveforms of New                                   |   |

|-------------|-----------------------------------------------------------------------------------------------------------|---|

|             | SRBC                                                                                                      | 5 |

| Figure 4.25 | Gate Voltage of $S_2$ and Drain Current Experimental Waveforms of $S_1$                                   |   |

|             | of New SRBC                                                                                               | 6 |

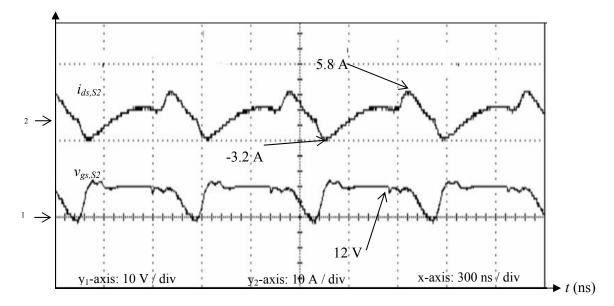

| Figure 4.26 | Gate Voltage and Drain Current Experimental Waveforms of $S_2$ of                                         |   |

|             | New SRBC                                                                                                  | 7 |

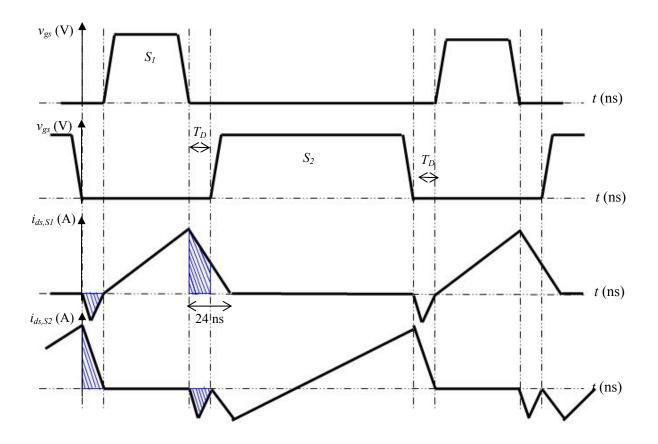

| Figure 4.27 | Body Diode Conduction of New SRBC                                                                         | 8 |

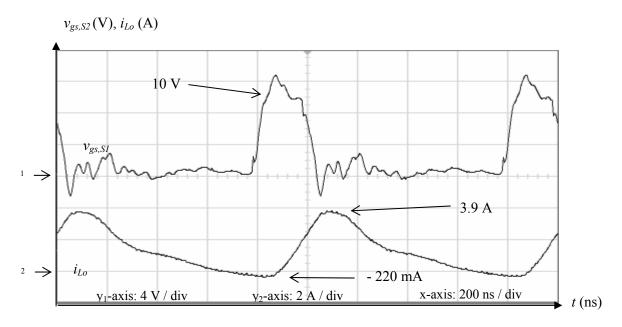

| Figure 4.28 | Gate Voltage of $S_I$ and Inductor Current Experimental Waveforms of                                      |   |

|             | New SRBC                                                                                                  | 9 |

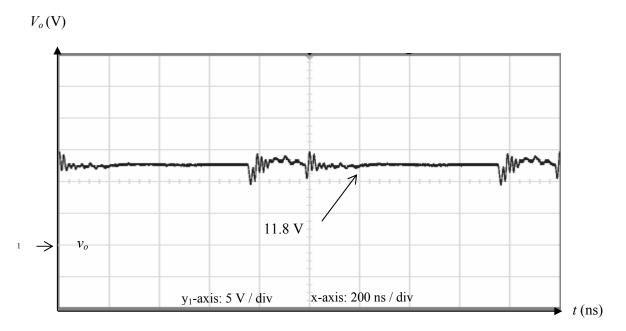

| Figure 4.29 | Output Voltage Experimental Waveform of New SRBC                                                          | 9 |

| Figure 5.1  | SRBC [51]102                                                                                              | 2 |

| Figure 5.2  | Simulated Turn-Off Switching Loss of Three Different SRBC102                                              | 3 |

| Figure 5.3  | Simulated Turn-On Switching Loss of Three Different SRBC102                                               | 3 |

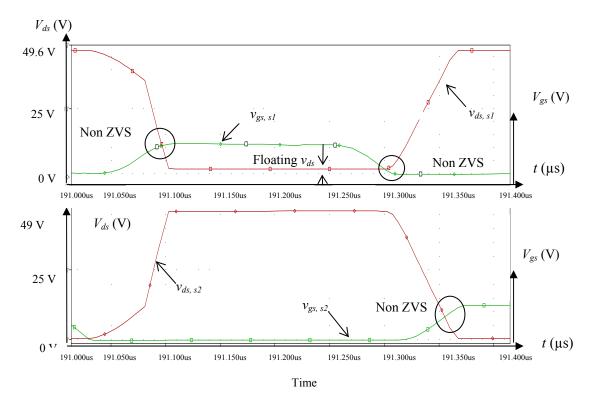

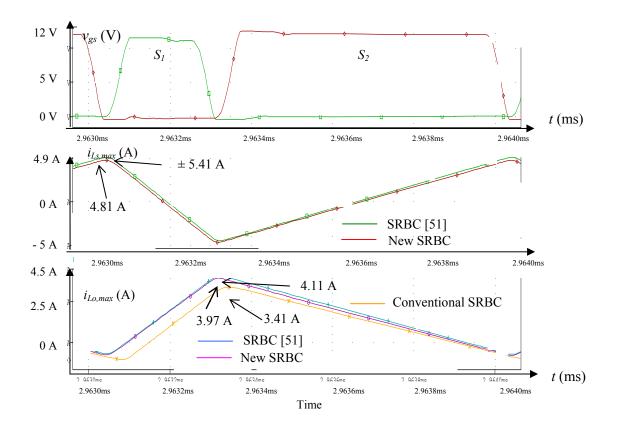

| Figure 5.4  | Simulated Gate and Drain Voltages of Conventional SRBC                                                    | 5 |

| Figure 5.5  | Simulated Gate and Drain Voltages of SRBC [51]10                                                          | 5 |

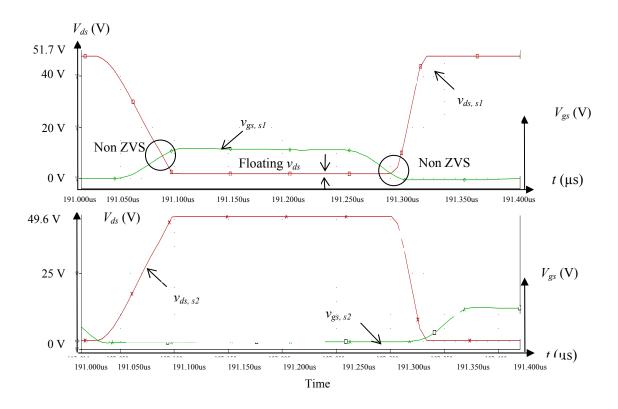

| Figure 5.6  | Simulated Gate and Drain Voltages of New SRBC                                                             | 6 |

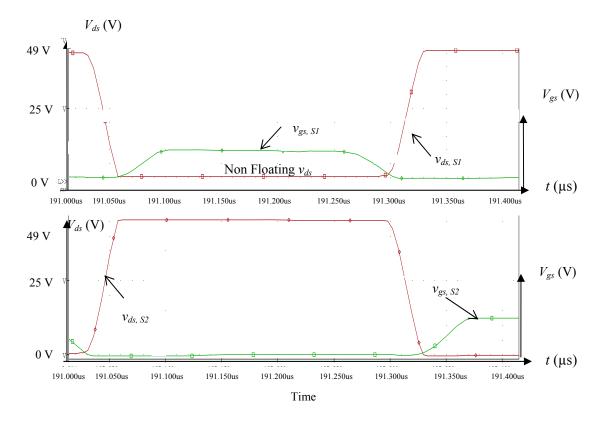

| Figure 5.7  | Comparison of $i_{Ls}$ and $i_{Lo}$ of Three Different SRBC                                               | 7 |

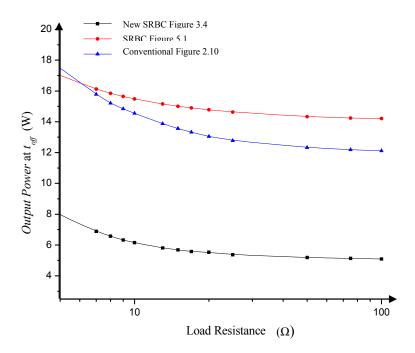

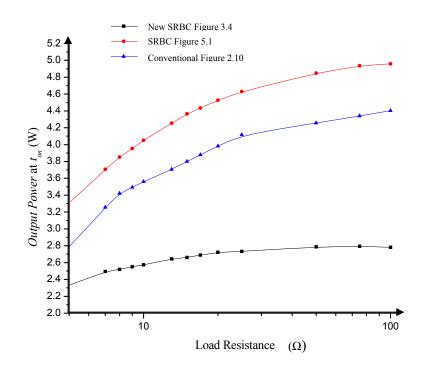

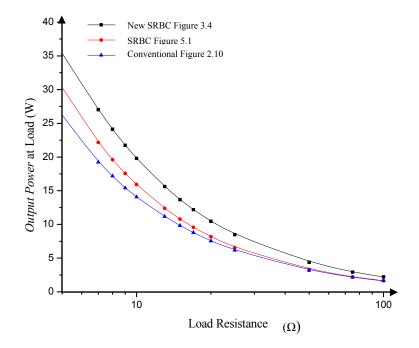

| Figure 5.8  | Average Turn-Off Power Loss of <i>S</i> <sub>1</sub> at Different Loads10                                 | 8 |

| Figure 5.9  | Average Turn-On Power Loss of S <sub>2</sub> at Different Loads109                                        | 9 |

| Figure 5.10 | Average Load Output Power at Different Loads                                                              | 9 |

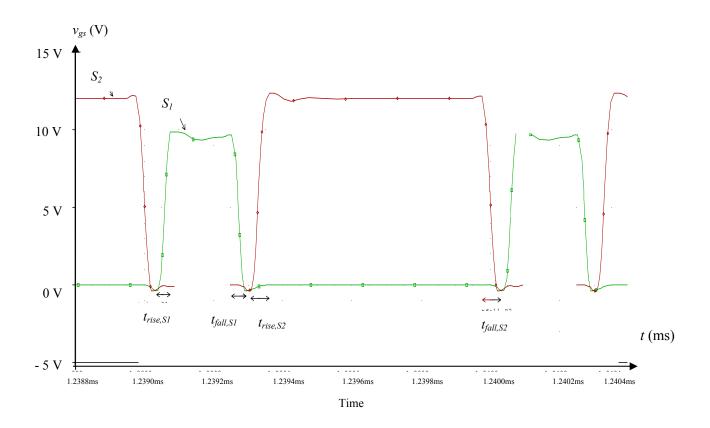

| Figure 5.11 | Simulated Gate Voltages of $S_1$ and $S_2$ at $T_D = 15$ ns of New SRBC114                                | 4 |

| Figure 5.12 | Turn-On and Turn-Off Switching Times of Conventional and New                                              |   |

|             | SRBC                                                                                                      | 6 |

| Figure 5.13 | Average Turn-On and Turn-Off Switching Losses of Conventional and                                         |   |

|             | New SRBC                                                                                                  | 7 |

| Figure 5.14 | S <sub>1</sub> Turn-Off and S <sub>2</sub> Turn-On Power Losses at Different S <sub>2</sub> Duty Ratio.12 | 0 |

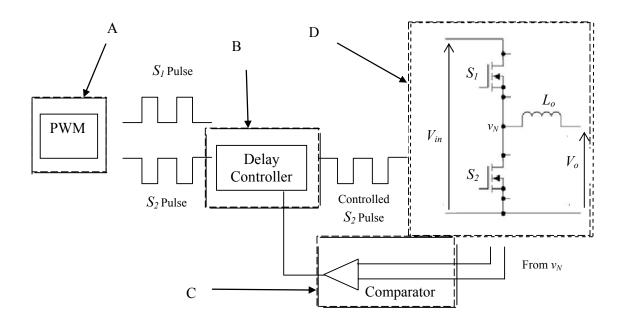

| Figure 5.15 | SRBC Adaptive Gate Drive                                                                                  | 1 |

| Figure 5.16 | SRBC Predictive Gate Drive                                                                                | 3 |

| Figure 5.17 | PGD Control Block Diagram                                                                                 | 4 |

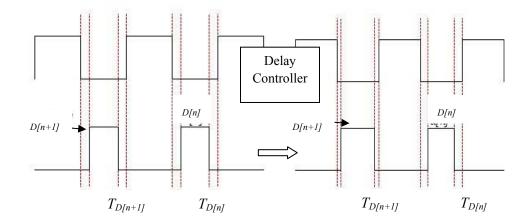

| Figure 5.18 | S <sub>2</sub> Pulse Width Delay Adjustment                                                               | 5 |

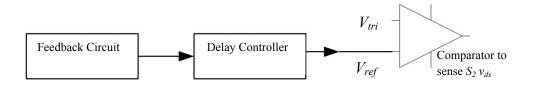

| Figure 5.19 PGD Delay Controller Block Diagram              | 125 |

|-------------------------------------------------------------|-----|

| Figure 5.20 D-CRGD Circuit with AGD Control at Switch $Q_4$ | 128 |

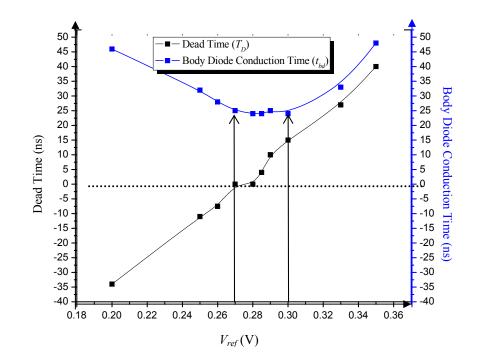

| Figure 5.21 | Relationship between Dead time and Body Diode Conduction Time                     |

|-------------|-----------------------------------------------------------------------------------|

|             | versus Reference Voltage of PGD-S <sub>2</sub> 131                                |

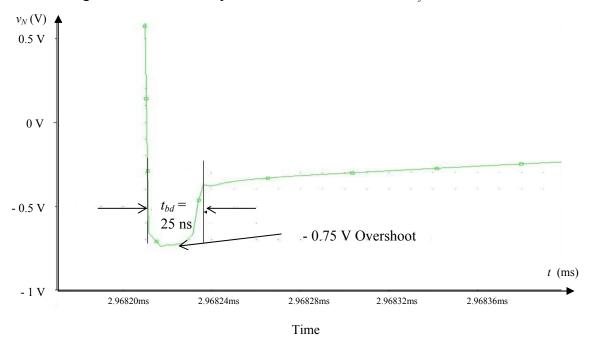

| Figure 5.22 | Negative Overshoot of Node Voltage in PGD- $S_2$ at $V_{ref}$ of 0.29 V131        |

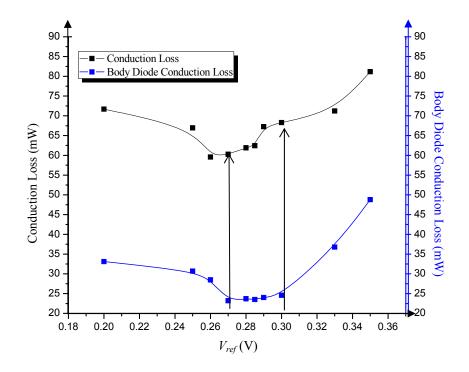

| Figure 5.23 | Relationship between Conduction and Body Diode Conduction Losses                  |

|             | versus $V_{ref}$ of PGD- $S_2$                                                    |

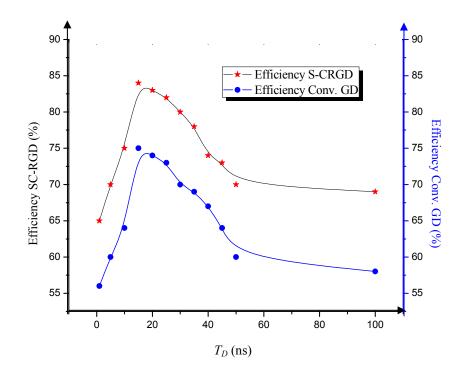

| Figure 5.24 | Efficiency versus Dead time for $L_r = 9$ nH and $D = 0.20$ of S-CRGD135          |

| Figure 5.25 | Efficiency versus Duty Ratio of $Q_1$ for $L_r = 9$ nH and $T_D = 15$ ns of S-    |

|             | CRGD                                                                              |

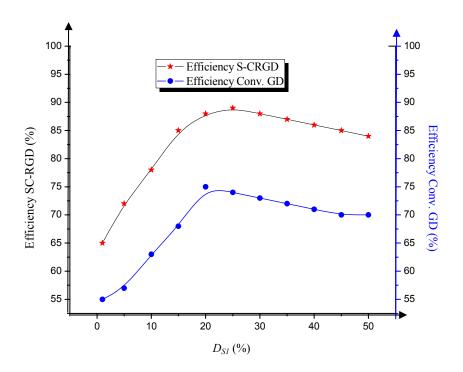

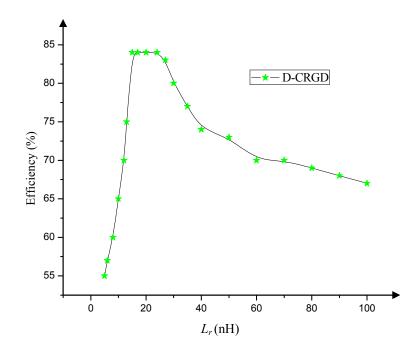

| Figure 5.26 | Efficiency versus Resonant Inductor for $D = 0.20$ and $T_D = 15$ ns of           |

|             | New D-CRGD                                                                        |

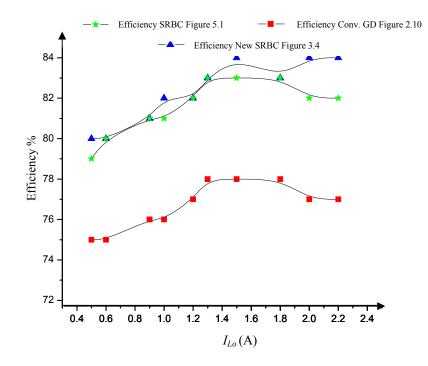

| Figure 5.27 | Efficiency versus Inductor Load Current for $D_{SI} = 0.20$ , $D_{S2} = 0.75$ and |

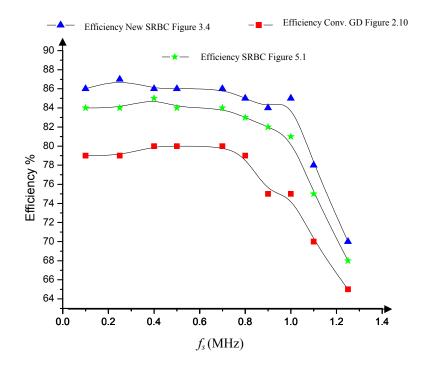

|             | $T_D = 15$ ns of Three SRBC                                                       |

| Figure 5.28 | Efficiency versus Switching Frequency for $D_{S1} = 0.20$ , $D_{S2} = 0.75$ and   |

|             | $T_D = 15$ ns of Three SRBC                                                       |

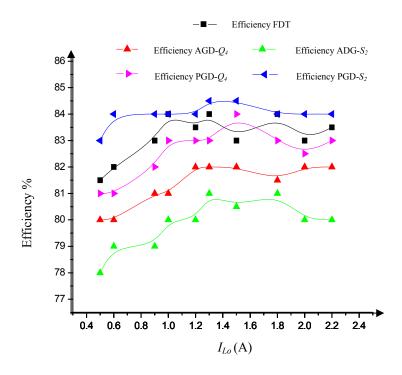

| Figure 5.29 | Efficiency versus Inductor Load Current for $D_{SI} = 0.20$ , $D_{S2} = 0.75$ and |

|             | $T_D$ = 15ns on New SRBC of Three Gate Drive Control Schemes140                   |

# LIST OF ABBREVIATIONS

| AGD    | Adaptive Gate Drive                               |

|--------|---------------------------------------------------|

| ССМ    | Continuous Conduction Mode                        |

| DCM    | Discontinuous Conduction Mode                     |

| D-CRGD | Dual-channel Resonant Gate Drive                  |

| EMI    | Electromagnetic Interference                      |

| ESR    | Equivalent Series Resistance                      |

| FDT    | Fixed Dead Time                                   |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| РСВ    | Printed Circuit Board                             |

| PGD    | Predictive Gate Drive                             |

| PWM    | Pulse Width Modulation                            |

| RGD    | Resonant Gate Drive                               |

| SRBC   | Synchronous Rectifier Buck Converter              |

| S-CRGD | Single-channel Resonant Gate Drive                |

| TTL    | Transistor Transistor Logic                       |

| ZCS    | Zero Current Switching                            |

# LIST OF SYMBOLS

| Ciss                | Input Capacitance    | (F)               |

|---------------------|----------------------|-------------------|

| D                   | Duty Ratio           | (between 0 and 1) |

| $f_r$               | Resonant Frequency   | (Hz)              |

| $f_s$               | Switching Frequency  | (Hz)              |

| P <sub>diss</sub>   | Power Dissipation    | (W)               |

| R <sub>ds(on)</sub> | On-state Resistance  | (Ω)               |

| $T_D$               | Dead Time            | (s)               |

| $T_s$               | Switching Period     | (s)               |

| V <sub>ds</sub>     | Drain-source Voltage | (V)               |

| $V_{gs}$            | Gate-source Voltage  | (V)               |

| $V_N$               | Node Voltage         | (V)               |

| $V_{ref}$           | Reference Voltage    | (V)               |

| V <sub>th</sub>     | Threshold Voltage    | (V)               |

| $Z_0$               | Impedance            | $(\Omega)$        |

### CHAPTER 1

### INTRODUCTION

### 1.1 Chapter Overview

This chapter introduces the importance of the research in high frequency operation. The synchronous rectifier buck converter (SRBC) is adopted as the test circuit. The work is divided into simulation and experimentation. The aim is to investigate the performance of several gate drive and control techniques on the new SRBC.

### **1.2** Research Rationale

With switching frequency increased more than 1 MHz mark, the new state of the art converters have to be developed. For example, switching mode converters are required to provide power processing for applications ranging from computing and communications to medical electronics, powering microprocessors, cost effective, meet EMC (Electromagnetic Compliance) and the same time

- i) reduce size and weight,

- ii) improve load transient response,

- iii) increase efficiency.

In recent years, there have been many studies focused on how to find better ways in regulating output current and voltage at variable loads, specifically in megahertz switching frequency. To achieve this, different types of resonant topologies have been proposed with an aim to achiev there power schemes such as phase-shifted fullbridge, flyback, forward converters and many more. Nevertheless, the study only looks at the fixed load condition.

For instance, the synchronous rectifier buck converter (SRBC) can be adopted with the advancement of soft-switched topology. Switching aid networks such as ZVS and zero-current switching (ZCS) may be used to help improve converter's performance and hence further reduce switching loss. Moreover, low switching losses in the driving switches are required to design a high frequency gate drive circuit for SRBC.

#### **1.3 Research Objectives**

The primary objective of the research was to evaluate a "new" "Zero Voltage Switching Synchronous Rectifier Buck Converter (ZVS SRBC)" by comparing PSpice simulations with experimental measurements.

The secondary objective of the research was to demonstrate by PSpice simulations and experimental measurements the improved performance of the proposed system in terms of reduced gate drive loss and two SRBC MOSFET's power loss when compared to the Dual-Channel Resonant Gate Drive SRBC (D-CRGD SRBC)" and the conventional hard switched Synchronous Rectifier Buck Converter (SRBC).

#### 1.4 Research Scope

The research will concentrate on the simulation of conventional and new dualchannel resonant gate driver (D-CRGD) for the new low-loss ZVS SRBC circuit. The PSpice circuit simulator is adopted in this work to observe the switching and circuit operating waveforms where the switching related losses will be determined for both circuits. The experimentation work is also carried out to verify the simulation. In addition, the simulation study on different gate drivers, effects on switching frequency, dead time and loads are the extension of the work which will be the preliminary results for further validation.

### 1.5 Chapter Summary

In the design of high frequency converter, the issue in getting the gate drive to operate accurately is important for the development of new low power SRBC. To do this, a comprehensive literature review is required to gather important data and evidences. The details are discussed in Chapter 2.

#### **CHAPTER 2**

### LITERATURE REVIEW

### 2.1 Chapter Overview

This chapter looks into the history in the development of high frequency converter. It starts with techniques in gate drive design and its application in the converter. The importance, advantages and issues in resonant topologies are reviewed along with the implication on the performance of the converter, for example in terms of switching loss, body diode conduction loss and etc. There are also design constraints which include the role of limiting parameters in the gate driver as well as its control schemes and the switching MOSFET consideration. In addition, the effects of dead time, switching frequency, soft-switching technique on the converter are also explored in detail.

## 2.2 Gate Drive Circuit

The selection of gate drive circuit is crucial in high frequency converter design since it requires fast switching response and precise timing sequence that corresponds to power delivery capability. Fundamentally, a good gate driver must have high energy savings properties. Even though conventional gate driver is easy to implement, it generates high power dissipation.

On the other hand, resonant gate drive (RGD) circuit is preferred due to its low

power loss. However, it normally involves complex circuit topologies which may eventually add to additional power loss in the circuit. With the attention in reducing the losses, the state-of-the-art RGD circuit is significant for the application of SRBC circuit. At high frequency, the effect of gate drive on overall performance and efficiency of converter becomes more critical since this can degrade power density of the converter [1].

Most of high frequency applications use silicon based devices such as Metal Oxide Semiconductor Field Effect Transistor (MOSFET). In discrete and surface mount device implementation, MOSFET is commonly chosen because of its superior operation in high switching frequency. Nevertheless, there exists constraint and issues pertaining circuit development where comprehensive design and analyses have to be carried out.

#### 2.3 Review of Gate Drive Techniques

Most of the time, the design of gate drive circuit has trade-offs between the level of voltage applied to the gate and level of switching frequency required for the switch. The other parameters include determination of dead time delay  $T_D$ , in the switching transition, duty ratio, D, resonant inductor,  $L_r$ , size of the transistor and isolation technique used to control the signal between input source and power MOSFET.

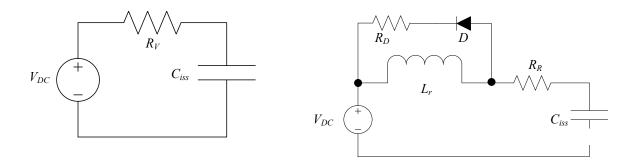

There are three basic types of driving sources in gate drive circuits. They are voltage driven and resonant topologies as shown in Figure 2.1(a, b) respectively [2]. First, in voltage driven topology, large energy will be dissipated and since there is no energy recovery, this topology is not suitable for high frequency operation. Power dissipation,  $P_v$  is given by Eq. (1).

$$P_{v} = f_{s} \times C_{iss} \times V_{s}^{2} \tag{1}$$

where  $C_{iss}$  is the gate capacitance of power MOSFET and  $V_s$  is the input voltage source. From Figure 2.1(a), the maximum value of  $R_v$  given by Eq. (2) [2].

$$R_{\nu} = \frac{\Delta t}{1.6 \times f_s \times C_{iss}} \tag{2}$$

where it is determined by required  $f_s$  whereas the minimum value, by  $C_{iss}$ .  $\Delta t$  is the time taken for  $C_{iss}$  to charge to maximum. Hence, there exists a maximum operating frequency which limits the charging capability of the gate [3]. Thus the voltage driven has limited capability in operating at high switching frequency.

Figure 2.1(a) Voltage Driven

Figure 2.1(b) Resonant Driven

The resonant circuit shown in Figure 2.1(b) implies that all energy from resonant inductor  $L_r$  will be transferred to gate capacitance. As series resistance increases, only half of energy will be dissipated when the gate voltage reaches supply voltage. At this time, the resonant drive circuit operates in full resonance mode and this is comparable to voltage driven topology. Even though careful measures are taken to determine the suitability of topology, obviously there are tradeoffs between component counts, input voltage supply range, switching related losses and switching frequency.

### 2.3.1 Hard Switching Conventional Gate Drive Circuit

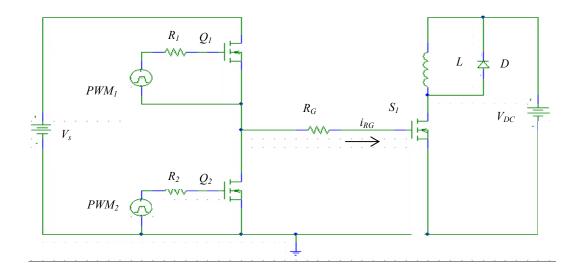

The conventional gate drive circuit was developed in 1970s. The issues related to the power dissipation loss and efficiency degradation had been discussed intensively by scholars especially in high frequency region. The circuit has limitations due to high switching frequency. As frequency increases, the driving loss is high causing high power dissipation in the external resistor  $R_G$  as indicated in Figure 2.2 (a). In hard switching, the dissipation of power loss in the switch is caused by rapid change in drain voltage and drain current which produce high stress in the switch. Even though switching loss can be reduced by minimizing these rapid changes in voltage and current, the effects of stray parameters such as inductance and capacitance in the circuit become obvious compared to low switching operation. Therefore, some energy is lost every time switches commutate [4].

The charging and discharging activities of input gate capacitance,  $C_{iss}$  of  $S_1$  becomes very fast indicating longer turn-off transient. In addition, the discharging current in  $R_G$  becomes smaller which results in slower switching speed [5]. The conventional gate driver which consists of a resistor in the DC link has proven to have significant power losses [6]. Using PSpice circuit simulator, Figure 2.2(a) shows the conventional gate drive circuit driven by a totem-poled MOSFET configuration and its operating waveforms as indicated in Figure 2.2(b).

Figure 2.2(a) Hard Switching Conventional Gate Drive

Figure 2.2(b) Conventional Gate Drive Waveforms

The two totem-poled driving MOSFETs  $Q_1$  and  $Q_2$  are used to drive signal to the power MOSFET,  $S_1$  supplied by input  $V_s$ . Resistor,  $R_G$  is used as the RC-link for the pulses to flow. When PWM is applied, gate will draw current for a very short time to fully charge the gate of MOSFET. This draws the peak current to turn on gate with maximum voltage across it. During charging, the current will flow through  $R_G$  and  $R_{ds(on),Q1}$  to charge  $C_{iss}$  of  $S_1$  until gate level reaches  $V_s$ . During discharging of  $C_{iss}$ , the current is then drawn out from the gate through the reverse path until gate voltage reaches zero. Thus, double resistive power loss appears in the gate driver. The loss is much greater at a higher switching frequency.

Normally, the gate voltage takes a longer time to turn off as shown in Figure 2.2(b) than turn-on because it relies on resistive charging through gate and driver's resistance. This results in lower switching power loss during turn-on. The reason is that, the parasitic inductances provide a current snubbing effect which decreases the switching loss [7]. On the other hand, these inductances increase turn-off time by prolonging the recovery time. This can be observed when the load current

is increased as the turn-off loss is proportional to  $i^2 R$  [8]. In summary, some of the issues in conventional hard switching gate driver are listed below:

- a) A longer turn-off time is not desirable to reduce switching loss as it is based on RC charge and discharge.

- b) Higher / faster driving speed requires higher driving current that may increase loss.

- c) Discharged current during switching transition becomes smaller than its peak. This will influence the charging and discharging of  $C_{iss}$  and hence the gate drive loss.

- d) Charging and discharging of gate capacitance of the switch becomes fast causing malfunction of driver.

- e) Induced turn-on dv/dt of the switch is dominant where it will not reduce with a shorter gate charging time.

- Gate driving loss is high comparable to conduction loss at frequency higher than 200 kHz.

- g) Cannot meet requirement of switching speed in high frequency application.

### 2.3.2 Switching Requirement and Losses in SRBC

In SRBC circuit operation, MOSFETs have to fulfill the system requirement in reducing loss and cost. The selection of MOSFET is based upon the following criteria:

- a) Low power dissipation of switching device in megahertz range.

- b) Figure of Merit of  $R_{ds(on)}$  and gate charge.

- c) Turn-on delay time  $(t_{d(on)})$ , rise time  $(t_{rise})$ , turn-off delay time  $(t_{d(off)})$  and fall time  $(t_f)$  which have to be small for possible good switching performance.

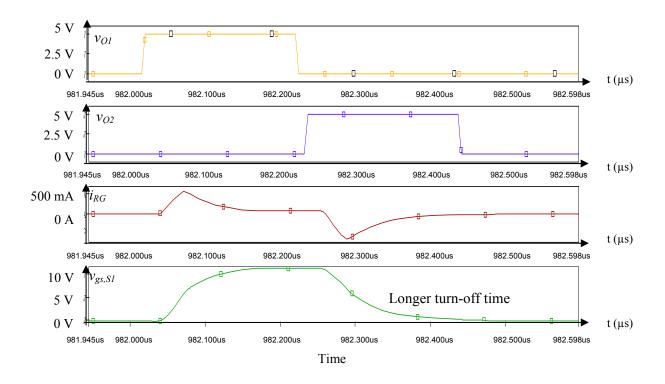

On the other hand, the ideal switch in circle cannot satisfy the above criteria. When looking with the switching intervals during turn-on and off, it is obvious that significant differences compared to the MOSFET. Figure 2.3(a) shows the chopper circuit using ideal switch and its switching waveforms are indicated in Figure 2.3(b).

Figure 2.3(b) Turn-On and Off Characteristics of an Ideal Switch

Figure 2.3(b) clearly shows that there is no power loss (instant turn-on and off)

during both switching transitions. This can be seen from the zero product of drain current and voltage of the ideal switch. Due to this, there are no turn-on and turn-off losses which are not realistic for real application. Even though the simulation result of Figure 2.3(a) successfully represents the suitability in high current and frequency, the actual operation will yet to require better switching device: the MOSFET.

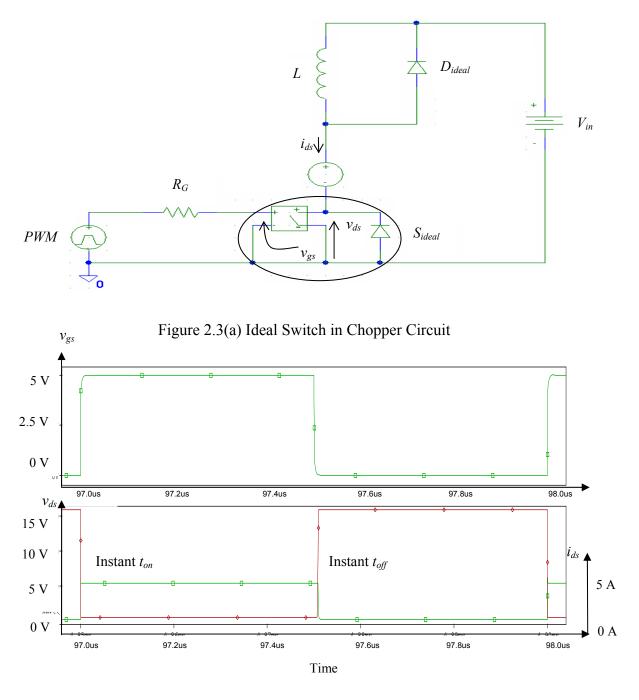

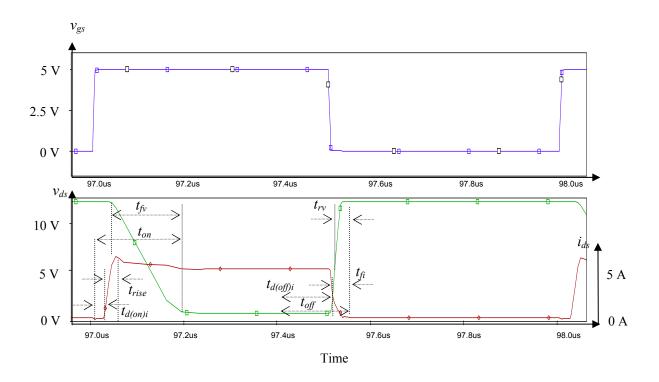

### 2.3.2.1 Switching Characteristics of MOSFET

In MOSFET switching, the most important operational conditions are gate-source voltage ( $v_{gs}$ ), drain-source voltage ( $v_{ds}$ ) and drain current ( $i_{ds}$ ). Figure 2.4(a) shows the inductive load test circuit for MOSFET and Figure 2.4(b) shows general switching characteristics of the MOSFET which explains the operation of turn-on and turn-off. The waveforms are generated using PSpice circuit simulator. The circuit is chosen because it is normally used for switching characterization and measurement.

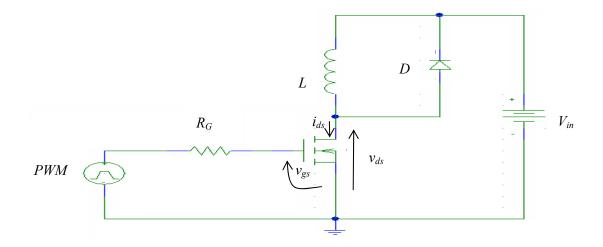

Figure 2.4(a) MOSFET in Chopper Circuit

Figure 2.4(b) Turn-On and Off Characteristics of MOSFET

### 2.3.2.2 Turn-On and Off Characteristics

Turn-on time  $(t_{on})$  and current turn-on delay time  $(t_{d(on)i})$  indicate how fast MOSFET reacts during turn-on switching transient which gives total turn-on time. Increased delay time will eventually limit the maximum switching frequency. A longer turn-on delay can prolong the PWM signal received at the gate terminal of the MOSFET. In addition, the Miller effect [9] may affect the signal. It is a capacitive feedback where  $C_{gd}$  appears to be larger capacitance as seen from gate within small variation in  $V_{gs}$  value. Current rise time  $(t_{rise})$  on the other hand contributes to how fast drain current reaches the load indicating the speed of the circuit. Other parameters such as voltage fall time  $(t_{fv})$ , di/dt of turn-on current, dv/dt turn-off voltage, current overshoot and turn-on energy loss  $(E_{on})$  are included in the total turn-on duration.

The turn-off characteristics exhibit the same characteristics as the turn-on except for the behavior of voltage, current and their related switching times and losses which depend on turn-off duration. Among the parameters are turn-off time ( $t_{off}$ ), current turn-off delay time ( $t_{f(off)}$ ), current fall time ( $t_{fi}$ ), voltage rise time ( $t_{rv}$ ), di/dt of turn-off current, dv/dt of turn-on voltage, voltage overshoot and its respective turn-off energy loss as indicated in Figure 2.4(b). Since the switching loss in MOSFET is critical in high frequency operation, these turn-on and turn-off characteristics must be understood as they contribute to considerable switching losses in the MOSFET.

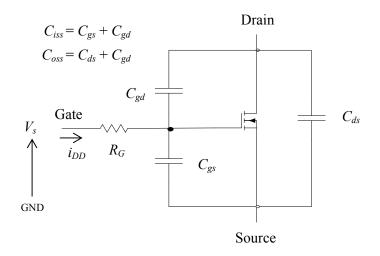

Figure 2.5 MOSFET Parasitic Capacitances

Figure 2.5 shows the parasitic capacitances of the power MOSFET. During switching cycle of the driving MOSFETs, the  $C_{iss}$  of  $S_1$  will be charged by the energy from  $V_s$  and discharged to the ground leading to generation of pulses [10]. The total power supplied by the  $V_s$  is derived as

$$P = \frac{1}{T_s} \times \int_0^{T_s} (V_s \times i_{DD}) dt = f_s \times V_s \times \int_0^{T_s} i_{DD} dt$$

(3)

where  $T_s$  is the switching period,  $f_s$  is he switching frequency of the circuit and  $i_{DD}$  is Vcc supply via 2 Rg the instantaneous current flowing out from Keintesthatige power MOSFET's  $v_{gs}$  of  $S_I$  is charged by the same current  $i_{DD}$  for Mi to  $S_{aad}$  gast frame of  $S_I$  from 0 to  $Q_G$  following the typical  $Q_G$  versus  $v_{gs}$  characteristic in the datasheet.

Cgs

The equation is given by

$$Q_G(t) = \int_{0}^{T_s} i_{DD} \, dt$$

(4)

When combining Eq. (3) and Eq. (4), this gives the well known MOSFET gate driver loss equation given in Eq. (1).

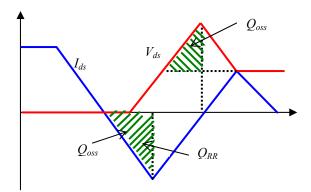

In order to reduce this loss, RGD techniques have been introduced. For example, the techniques utilize LC resonance to charge and discharge the gate capacitance of main power MOSFET,  $S_1$ . The idea is to recover the energy stored in the gate capacitance,  $C_{iss}$  of main power MOSFET. From Figure 2.2(b), the switching power loss can be calculated using Eq. (1) and gate drive loss by replacing  $C_{iss}$  with  $C_{oss}$ . Since there are two driving MOSFETs of same type in the driver, the losses are approximately doubled.

From Figure 2.4(a),  $R_G$  limits the maximum gate current flow and allows root mean square (RMS) losses between  $R_G$  and internal drain-source on-resistance of power MOSFET,  $R_{ds(on)}$ . Reducing  $R_G$  brings no reduction in gate drive loss since it just shortens the charging and discharging times [11]. However, increasing effective gate resistance will reduce the switching speed.

On contrary, the impact of parasitic inductance is also important in the driver. For example, the parasitic common-source inductance creates a serious propagation effect during switching transitions and therefore increases switching loss, especially turn-off loss [12]. Consequently, the actual charged and discharged currents are much smaller resulting in higher switching loss [13, 14]. Thus, several methods have been introduced to solve the issues related to power dissipation and switching speed. Hence, the development of RGD circuit is pursued to help further improve the capability, reliability and performance of the driver.

### 2.4 Resonant Gate Drive Circuit

Generally, RGD circuit has evolved to overcome the issues when operating at high switching frequency. It is practically suitable to recover part or all of the energy stored in  $C_{iss}$  of  $S_1$ . The RGD circuit is designed only for specific applications and sometimes may not be suitable for others. If the application circuit uses only one switch, single-channel RGD can be applied. On the other hand, if the circuit has two switching devices, the applicable RGD circuits have to be designed to tailor the need for that circuit.

Until now, many studies have been conducted for the improvement of RGD circuits however they still require further development. The MOSFET's  $C_{iss}$  charges and discharges during the switching stage and thus significant energy losses are dissipated. Due to this, some of the dissipated energy must be recovered. Moreover, any RGD circuit which is incapable of fast cycle dynamics will not be suitable for high frequency applications. Below are the main requirements in designing a good RGD circuit:

- a) Ability to have fast duty cycle dynamics.

- b) Gate impedance of the switching device should be low after turning on and off to prevent false triggering.

- c) Gate voltage must be well controlled after turning on and off.

- Ability to have fast gate drive speed and at the same time produce low driving power losses.

In addition, there are also several other considerations to accommodate for high performance RGD, such as:

- a) Propagation delay of input signal through switches' gate terminals.

- b) Pulse width distortion of input gate signal.

- c) PCB layout parasitic of power converter.

- d) Device switching voltage swings and related EMI.

- e) Determination of minimum pulse width for power MOSFET.

- f) Protection features such as trip out and trip trigger input.

- g) Drain voltage overdrive control to optimize efficiency.

- h) Selection of gate capacitance value and Miller effect and start-up consideration

There are many RGD techniques have been introduced to solve technical issues in the design [1, 15, 16-20]. Unlike the conventional gate driver, only portion of energy in RGD circuit becomes thermal loss with the rest is stored in inductor [16]. Besides reducing the gate driving loss, some of the topologies suffer from at least one of the problems:

- a) Suitable only for low-side (single-channel) and ground-referenced drives [1, 21-28].

- b) Has bulky transformer or coupled inductance [1, 19, 22, 29-31].

- c) Slower turn-on and/or off transition times leading to high conduction and switching losses [1, 21-23, 28-29].

- d) Can only recover gate drive energy but limits total power savings.

- e) Difficult to achieve high side driver [32].

- f) Unable to effectively clamp the gate voltage of power MOSFET to driving voltage level during on-time and to ground during off-time which gives result in false triggering of gate conduction [1, 19, 21-23, 27-28].

Therefore, some designs such as ZCS-ZVS mixed-mode snubber, automatic energy recovery system, power efficient gate control, universal gate drive, hybrid gate drive, self-powered RGD, using leakage inductance of transformer and many more have been introduced. There are three important characteristics of RGD [10]:

- a) Zero circulating current in order to minimize conduction loss in driver during turn-on of MOSFET.

- b) Fast turn-on and off transition times to minimize conduction and switching losses in MOSFET.

- c) Ability to clamp MOSFET gate to input voltage during turn-on and to ground during turn off in order to avoid false triggering and reduce induced dv/dt.

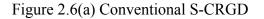

#### 2.4.1 S-CRGD Circuit

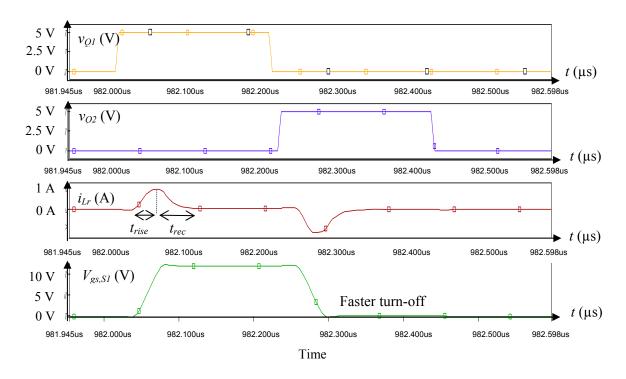

As switching frequency increases, the S-CRGD circuit should be fast but also requires precise timing that corresponds to power delivery periods. In addition, good driver should have excellent loss saving properties. However, fast turn-on after  $C_{iss}$  is charged to  $V_s$  may block peak inductor current,  $i_{Lr,peak}$  from flowing through reverse body diode of MOSFETs, which may result in higher power loss [33]. Any over voltage or under voltage of  $v_{gs,Ql}$  and  $v_{gs,Q2}$  is caused by voltage drop across parasitic reverse body diodes of the transistors. Figure 2.6(a) shows the conventional S-CRGD circuit. Unlike in Figure 2.2(a), the inductor,  $L_r$  is used as the link instead of resistor,  $R_G$ . The operating waveforms are shown in Figure 2.6(b).

Figure 2.6(b) S-CRGD Waveforms

The operating condition of this circuit is similar to the conventional  $R_G$  gate driver, except the charging and discharging of gate capacitance of MOSFET is through inductor,  $L_r$ . One important remark is that  $Q_2$  pulse width plays an important role in power energy savings in addition to the controlled  $Q_1$  pulse. The turn-on speed

depends on reverse recovery of body diode of the switch and for turn-off, it depends on gate drive circuit. A higher turn-off current may discharge  $C_{iss}$  of  $S_I$  faster, providing shorter switching times and hence lower switching loss. On the other hand, oscillation during turn-off may reduce the turn-off speed due to higher di/dt and dv/dt of  $S_I$ .

# 2.4.2 Alternatives on S-CRGD Circuit Topologies

The S-CRGD circuit introduced in [34] is claimed to have full capability in recovering full energy with low dissipation. It has managed to recover some energy during both charging and discharging transitions. In addition, the circuit is independent on duty cycle of switch and hence driving frequency. Nevertheless, this S-CRGD circuit experiences an additional stress due to the additional switches used as auxiliary. Therefore, there are limitations in the parameter values which require optimization of duty cycle, D, dead time,  $T_D$  and  $L_r$  which are essential in achieving high frequency gate drive operation.

Another type of S-CRGD circuit uses the role of continuous inductor current in complete cycle to charge and discharge the gate of power MOSFET [16]. The resonant inductor is connected in series with an external capacitor. Here, the capacitor is used as a DC component of voltage across inductor. With the requirement of large capacitance value, this leads to the disadvantage on overall space limitation in circuit board despite of the advantages in operating independently with varying D and frequency. However, a constant circulating current during switching transitions results in higher power dissipation.

In designing a good S-CRGD circuit, the  $f_s$  and D have become the primary parameters. The switching speed of power device has to be as high as possible in order to reduce switching loss in power stage. However, the increase in switching speed will increase the power losses in RGD system. As a result, there must be an optimized switching speed that minimizes overall power losses especially in ZVS resonant network.

#### 2.5 Resonant Switching

ZVS and ZCS are generated based on turn-on or turn-off, overvoltage snubber or even any combination of them. In high frequency operation, ZVS is preferred in high frequency power converter circuits because it can reduce the switching loss by maintaining low or zero voltage across the switch during switching transitions [35-36]. Fundamentally, it shapes the switch voltage waveform during the off time to create a zero-voltage condition for the switch to turn on [37]. This eventually leads to the benefits of reduction in EMI. Nevertheless, ZVS normally incurs losses that do not scale back with the output load, leading to difficulty in achieving light-load operation effectively. Having an improved ZVS design may solve this issue.

On the other hand, operating in ZCS can also minimize the switching loss. However, there is a greater concern in choosing this mode as it inhibits greater limitations in designing high frequency circuits. The upper limit of 2 MHz switching frequency is one of the limitations in ZCS mode [38] when operating off-line where slower transient response is reported especially in half-mode condition [39]. Even though full-mode operation can solve this limitation, it is difficult to implement at high frequency due to high body diode conduction loss experienced by the switch [40]. Thus, this leads to ZVS preference in high frequency converter design. In order to realize megahertz switching operation, the converter requires the following:

- a) To have zero-voltage or zero-current in the switches at the instant of turn-on and turn-off, respectively.

- b) To have diode's stored charge removed in the event of turn-off condition before next subsequent turn-on executes.

- c) To ensure that the switching surge due to drain-source capacitance of the switch removed.

More importantly, the condition of ZVS is a function of duty ratio, *D*. In general, soft-switched DC-DC converters can have an advantage in lowering most of the related losses. However, drawbacks such as load dependent soft-switching range [41],

complex control scheme [42] and high component stress make the design practically require accurate consideration.

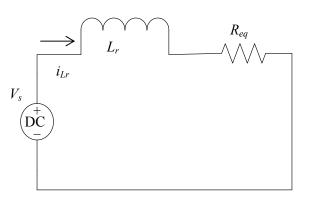

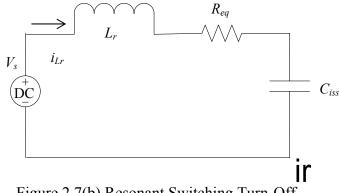

Generally, there are two switching sub interval circuits of resonant transitions: one is during turn-on and the other during turn-off. The circuits are shown in Figure 2.7(a) and Figure 2.7(b) respectively.  $R_{eq}$  is the sum of all resistance in the path that includes resistance in wire and ESR of  $L_r$  and  $V_s$  is the voltage source. The initial inductor current and gate capacitor voltage are denoted as  $I_{Lr0}$  and  $V_{gs0}$ . In Figure 2.7(a),  $i_{Lr}$  (turn-on stage) can be expressed as Eq. (5) [19]:

$$i_{L_r}(t) = (I_{L_{r_0}} - \frac{V_s}{R_{eq}})e^{-\frac{R_{eq}}{L_r}t} + \frac{V_s}{R_{eq}}$$

(5)

Figure 2.7(a) Resonant Switching Turn-On

Figure 2.7(b) Resonant Switching Turn-Off

Lr

Vs

By solving turn-off system in Figure 2.7(b),  $i_{Lr}$  and  $V_{gs}$  can be expressed as:

$$i_{L_{r}}(t) = \frac{V_{s} - V_{gs0} - 0.5R_{eq}I_{L_{r0}}}{\omega L_{r}}e^{-\alpha t}\sin(\omega t) + I_{L_{r0}}e^{-\alpha t}\cos(\omega t)$$

(6)

where

$$\alpha = \frac{R_{eq}}{2L_r}$$

,  $\omega = \frac{\sqrt{4L_r C_{iss} - R_{eq}^2}}{2L_r C_{iss}}$

$V_{gs}(t) = \frac{1}{C_{iss}} \int_{0}^{t} i_{Lr} (t) dt + V_{gs0}$  (7)

Then the resistive power,  $P_r(t)$  can be given as:

$$P_{r}(t) = \frac{R_{eq}}{T_{s}} \int_{0}^{T_{s}} i_{Lr}^{2}(t) dt$$

(8)

## 2.6 Q-Factor, Inductance and Performance of S-CRGD Circuit

Q-factor is a quality indicator which characterizes the rate of energy dissipation in resonant system. A high Q does not always represent better performance and high quality converter because it depends on the type of circuit topology used [43]. Generally, a high performance S-CRGD circuit should have a high value of Q so that more energy will be stored in the resonant components rather than being dissipated as power loss.

It can be determined from the resonant inductor value directly where size of inductor is important in high frequency operation. Here, the inductor value is proportional to Q-factor. In S-CRGD circuit [1], increasing inductance too high will increase switching loss. Therefore, the optimization between Q-factor and resonant inductance is required to ensure high performance of the gate driver.

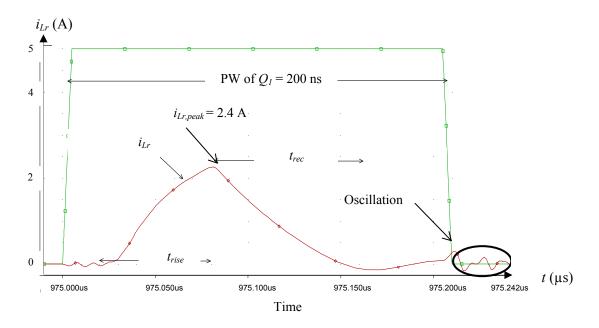

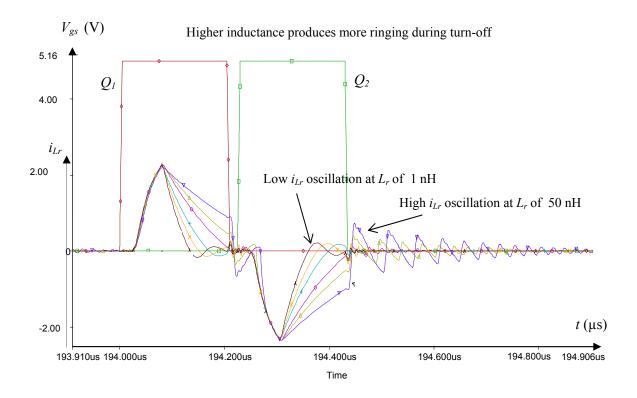

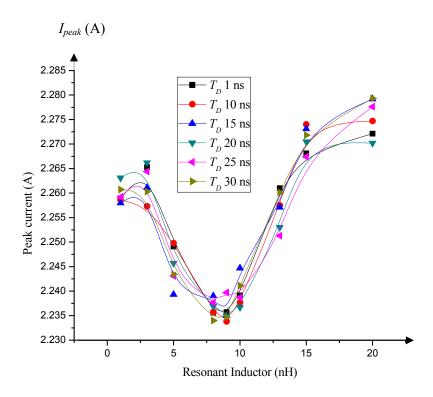

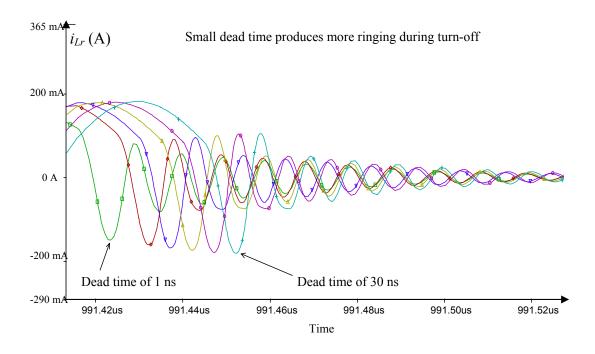

The switching time in S-CRGD is determined from the value of  $L_r$ ,  $t_{rise}$  and  $t_{fall}$  during the charging and discharging phases. This eventually determines the switching capability of the driver. From Figure 2.6(b), theoretically, the  $t_{rise}$  and  $t_{rec}$  will increase

when  $L_r$  increases. For high switching application,  $t_{rise}$  should be small enough so that the power MOSFET can turn on faster.

The  $t_{rec}$  of the inductor current should not exceed the on-time of switching MOSFETs'  $Q_1$  and  $Q_2$ . This is because, if  $t_{rec}$  is too long, the inductor current,  $i_{Lr}$  and  $v_{gs,S1}$  will start to oscillate heavily and this is not favorable for the S-CRGD circuit. Besides, the relationship between the Q-factor and the switching response can be seen in the Q-factor Eq. (9) where it is proportional to  $L_r$ . This indicates that a higher  $L_r$  will eventually increase the  $t_{rise}$  and  $t_{rec}$  and hence reduce the switching speed as shown in Figure 2.6(b).

$$Q = \frac{1}{R_{eq}} \times \sqrt{\frac{L_r}{C_{iss}}}$$

<sup>(9)</sup>

$$P_{diss} = \frac{\pi}{2} \times \frac{V_s^2 \times R_{eq} \times C_{iss}^{\frac{3}{2}}}{\sqrt{L_r}}$$

(10)

A high value of Q-factor is required to improve the performance of S-CRGD in terms of power losses. It can be derived from a higher  $L_r$  but it will add to the board layout size and consequently, reduce the ability of S-CRGD to operate in high frequency switching application. From Eq. (10), a lower  $L_r$  will increase the power dissipation. It indicates that there will be a tradeoff in selecting this value. The selections for maximum value of inductor and the driving time of MOSFET have to be determined [12]. Usually 1-5 % of overall switching period time is taken for driving and by taking 5 % as the maximum value of driving time, an inequality of maximum value of inductor is given by Eq. (11).

$$L_{r,\max} \le \frac{1}{C_{iss}} \times \left(\frac{5\%}{\pi \times f_s}\right)^2 \tag{11}$$

# 2.7 Summary of S-CRGD Topology Characteristics

Most of S-CRGD designs are at best for a single MOSFET but for dual MOSFETs, circuit complexity and cost constraint [44-46] are becoming the issues. For example, in D-CRGD developed by K. Yao et al. [19], issues of floating gate remain open during off and on states leading to massive noise generation. Complete understanding of S-CRGD circuit is required prior to designing a D-CRGD. Some issues and advantages of S-CRGDs are presented in Table 2.1.

| Description of Gate<br>Driver (GD)                                                                                      | Magnetic Used for<br>Resonance | Issues                                                                                                                                                                                                                        | Advantages                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Conventional GD<br>[Lopez et al., 2003]:<br>Gate capacitance is<br>charged through<br>push-pull totem-<br>poled circuit | None. It is a RC configuration | GD loss is<br>independent on load<br>current so efficiency<br>is affected in light<br>load conditions                                                                                                                         | Simple and can<br>easily be embedded<br>in IC, offering high<br>power density                                              |

| Voltage clamped S-<br>CRGD<br>[Jacobson, 1993]                                                                          | Coupled inductors              | <ul> <li>Using leakage<br/>inductance may<br/>result in<br/>manufacturing<br/>variation</li> <li>Cannot use a<br/>standard push-pull<br/>driver configuration</li> </ul>                                                      | Fast turn-on can be<br>achieved                                                                                            |

| Linear turn-off<br>current S-CRGD<br>[Strydom, 2004]                                                                    | Large inductor                 | <ul> <li>Poor transient<br/>response</li> <li>High switching loss<br/>due to constant<br/>circulating current</li> <li>Large capacitor<br/>required</li> </ul>                                                                | <ul> <li>Simple with less<br/>component count</li> <li>Using push-pull<br/>driver</li> </ul>                               |

| S-CRGD using gate<br>capacitance as main<br>energy storage<br>[De Vries, 2002]                                          | Small inductor                 | <ul> <li>Increases turn-on<br/>time due to large bi-<br/>directional voltage<br/>swing at MOSFET<br/>gate</li> <li>Switching loss is<br/>high in driving<br/>switches</li> <li><i>R</i><sub>ds(on)</sub> dependent</li> </ul> | <ul> <li>Simple in circuit<br/>construction</li> <li>Energy in gate<br/>capacitance is<br/>effectively recycled</li> </ul> |

| Complete energy<br>recovery S-CRGD<br>[Chen et al., 2004]                                                               | Small inductor                 | - Inductor current<br>depends on switch's<br>conduction time                                                                                                                                                                  | - Fast turn-on to<br>allow for low<br>driver's conduction<br>loss                                                          |

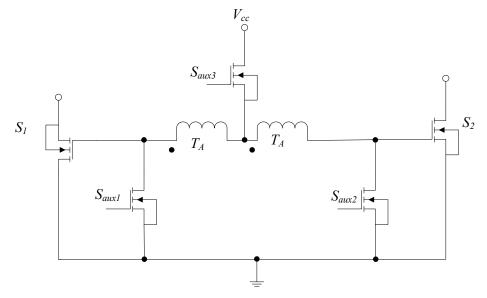

One of the examples of D-CRGD circuit is shown in Figure 2.8. The centertapped transformer is used to boost the switch gate voltage as high as input source value. By controlling the timing of both MOSFETs, each of them can be turned on right after the other is turned off. Here, the charging and discharging of  $C_{iss}$  is by constant current source which may speed up the switching transition especially during turn-off. Ultimately, both  $S_1$  and  $S_2$  switches can turn on and turn off in complementary mode [47].

Figure 2.8 Center-Tapped D-CRGD [47]

Nevertheless, this D-CRGD does not have much of power saving property due to core loss of transformer. So, there are many other D-CRGD circuits proposed which have better driving capability to drive two MOSFETs in one switching cycle. However, there are lots of drawbacks in ensuring that  $S_1$  and  $S_2$  can properly conduct without incurring cross conduction. One of the solutions is by integrating the soft switching technique with gate drive control scheme for power loss reduction within low  $T_D$ .

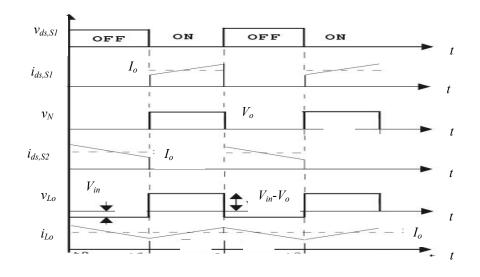

#### 2.8 Synchronous Rectifier Buck Converter (SRBC) Power Stage Circuit

In most low-voltage power module, switching power losses are dominant in the converter in addition to body diode conduction loss produced by two switches in SRBC, namely control switch and synchronous switch. Therefore, the switching waveforms for these switches must be operating in ZVS and the ideal finite on-state drain-voltage of  $S_2$  has to be close to zero in ensuring minimum losses throughout the switching interval.

In SRBC circuit, a high current may be required to turn off control switch with low switching loss. Besides, incorrect choice of drain-source on-resistance ( $R_{ds(on)}$ ) of the device will impose a constraint on the converter's performance. Even though resonant topology is employed, the turn-off issue remains unsolved. In contrast, synchronous switch needs a lower current in order to switch the device rapidly leading to difficulty in clamping the gate voltages. In addition, an independent bias supply can be allowed to optimally drive the switches using a simple voltage feed. This may help reduce the effect of stray capacitance in the converter which eventually lowers the switching loss. More importantly, issues related to dead time will greatly result in lower efficiency and affect the performance of the converter.

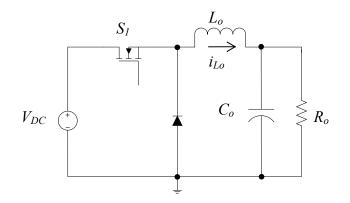

Figure 2.9 Buck Converter

A buck converter is shown in Figure 2.9. In this circuit, the freewheeling diode

turns on shortly after the switch turns off which results in a voltage rise across the diode. Since the diode only conducts during  $S_1$  turn-off, during continuous conduction mode (CCM), some energy will dissipate which gives power dissipation,  $P_d$  in diode given by Eq. (12). At this time, the diode will experience reverse recovery and it is related to voltage drop,  $V_d$  as defined by Eq. (13).  $D_{S1}$  is the duty ratio of  $S_1$  switch and  $C_{diode}$  is capacitance of the diode during its reverse bias in CCM.

$$P_{d(on)} = \frac{1}{2} \times C_{diode} \times V_{DC}^{2} \times f_{s}$$

(12)

$$P_{d(on)} = V_d \times (1 - D_{S1}) \times I_{Lo}$$

(13)

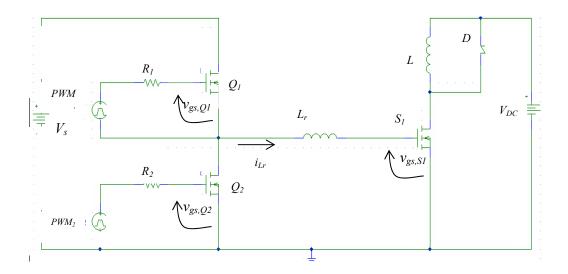

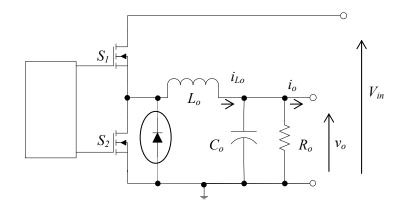

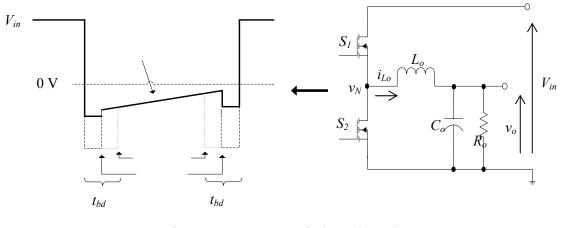

Figure 2.10 shows the SRBC as a modified version of the buck converter circuit topology where the diode is replaced with a second switch,  $S_2$ . This modification is a tradeoff between the increased cost and improved efficiency.

Figure 2.10 Conventional SRBC Circuit

In this circuit, a control switch,  $S_1$  and synchronous switch,  $S_2$  are conducting in complementary manner. Here, the charging and discharging of inductor current,  $i_{Lo}$ will produce output voltage based on duty cycle set by  $S_1$ . Replacing the diode (in circle) with switch  $S_2$ , may lower conduction loss, reduce the voltage spike of gate voltage of  $S_2$  and improve the performance of converter. Some of the advantages when utilizing  $S_2$  are as follows [48]:

- a) Allows bidirectional power flow.

- b) Efficiency can be increased because on-state drain voltage drop of  $S_2$  is less than forward voltage of the diode in buck converter.

However, using  $S_2$  may also introduce some drawbacks such as:

- a) Both  $S_1$  and  $S_2$  could accidently conduct if cross conduction occurs.

- b) Higher losses are present in  $S_1$  and  $S_2$  and also in  $L_o$ .

- c) May cause additional ripple overshoot in drain voltage of  $S_2$ .

- d) Will introduce an induced dv/dt switching, which may degrade the performance of SRBC [49].

- e) Feedback control circuit is complex

The power loss in  $S_2$  is strongly dependent on the duty ratio, D and therefore proportional to its on-time. When power is transferred in the "reverse" direction, it acts much like a boost converter instead. Nevertheless, the advantage of this converter does not come without cost. Firstly,  $S_2$  typically costs more than the freewheeling diode in buck converter circuit. Secondly, the complexity of the converter is vastly increased due to the need for a complementary-output switch driver. Other losses such as reverse recovery and body diode conduction losses during  $T_D$  also reduce the performance of the SRBC.

Moreover, when  $S_2$  is used, it may degrade the efficiency of the converter at light load by disallowing  $i_{Lo}$  from entering the discontinuous conduction mode (DCM) and maintaining operation in CCM. This is due to the MOSFET bidirectional flow of  $i_{Lo}$ . In order to block any negative  $i_{Lo}$ , a good gate drive control scheme must be able to detect the current through the MOSFET and then switch it off when it is zero. Hence, this enables the SRBC to operate in DCM operation at light load and thus reduce the switching loss.

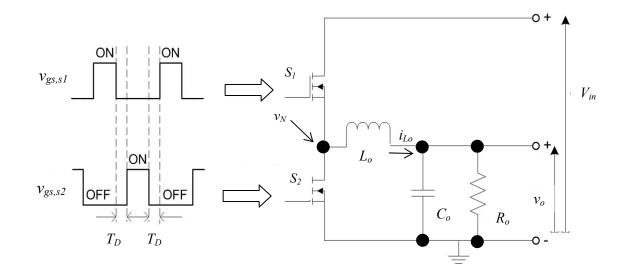

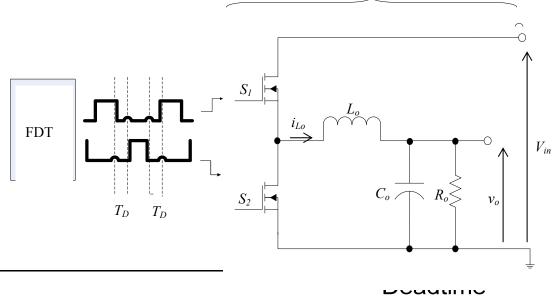

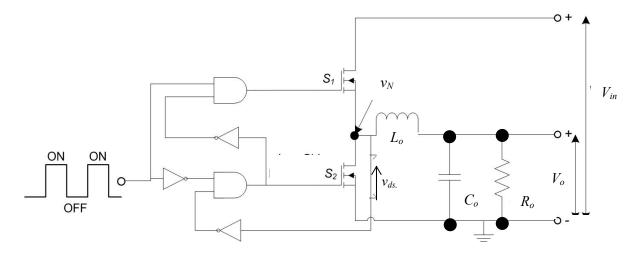

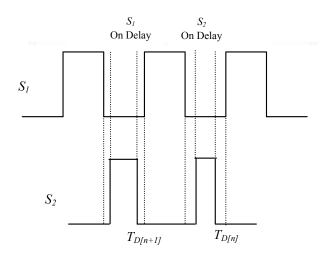

Generally, the faster  $S_1$  turns on and off, the lower switching losses become.