# Novel Approach For Hybrid-Multi Level Filter Design For Wireless Applications

### KASI DEEPIKA

Research Scholar, Department of ECE, International School Of Technology and Sciences (Women), Affiliated to JNTUK, NH-16, Eastgonagudem, Rajanagaram, Rajamahendravaram, AndhraPradesh, 533294, India. J. KIRAN CHANDRASEKHAR M.Tech, Assistant Professor, Department of ECE, International School Of Technology and Sciences (Women), Affiliated to JNTUK, NH-16, Eastgonagudem, Rajanagaram, Rajamahendravaram, Andhra Pradesh 533294, India.

*Abstract:* Less time and less delay is required for fast processing for filter. The one challenge in processing of image we design a matched filter based algorithm. That is resilient to variation in position determination. The second challenge is to fast process of filter. The match filter works to identify the passion of beam result and compared to that obtaining using the centroiding technique. This process required extra processing time for each beam. So, for fast implementation processing and less delay time we explore the possibility of using a field programming logic array and parallels combination of each delay block to speed up this computation. The second objective can achieve by the parallel hardware used that provides significant performance improvement over processing. This paper describes the development of match filter with less delay and fast processing.

### I. INTRODUCTION

Because of their finite impulse response (FIR) filter structures, adaptive filter-based receivers are computationally demanding, requiring a great deal of complex-number multiplications and additions. Another restriction imposed by the receivers is that they cannot tolerate much output latency due to the dependency of the operations on the previous output. Thus, the involved calculations must be performed in real-time with relatively low latency. Traditional DSP processors, which adopt a traditional von Neuman architecture, are not well suited to deliver such computational power. Even though DSP processors have wide internal data paths, which positively impact the accuracy and usability of the implemented algorithm, the processors must perform each operation sequentially. Thus maximum throughput decreases as the numbers of operations increases. Even though multiple DSP processors can be used, the partitioning of algorithms is difficult and requires substantial overhead, and for some algorithms this approach may not be possible. Another disadvantage is that the number of input/output interfaces available is limited for software radio applications. FPGA-based computing platforms, on the other hand, allow designers to implement customized architectures. By using pipelining techniques, the receiver algorithm can be divided into smaller operations, which can be run in parallel. Thus, the throughput is increased and the output latency is decreased. This thesis addresses the practical implementation of an adaptive filter singleuser receiver. The selected technique is called the differentially coherent adaptive receiver, which has been proven to perform well in mobile environments [1]. The implemented receiver employs a stream-based architecture [2]. In this architecture, user data is processed serially through

a string of processing pipelines, which run in parallel. This increases the throughput and also minimizes the overall routing and communication requirements between pipelines. The architecture also provides some flexibility. By allowing users to reconfigure the parameters of the processing pipelines, the functionality of the receiver can be changed.

### **II. LITERATURE REVIEW**

Digital filters are used for two general purposes: (1) separation of signals that have been combined, and (2) restoration of signals that have been distorted in some way. Analog (electronic) filters can be used for these same tasks; however, digital filters can achieve far superior results.

Filter Basics: Digital filters are a very important part of DSP. In fact, their extraordinary performance is one of the key reasons that DSP has become so popular. As mentioned in the introduction, filters have two uses: signal separationand signal restoration. Signal separation is needed when a signal has been contaminated with interference, noise, or other signals. For example, imagine a device for measuring the electrical activity of a baby's heart (EKG) while still in the womb. The raw signal will likely be corrupted by the breathing and heartbeat of the mother. A filter might be used to separate these signals so that they can be individually analyzed.

Signal restoration is used when a signal has been distorted in some way. For example, an audio recording made with poor equipment may be filtered to better represent the sound as it actually occurred. Another example is the deblurring of an image acquired with an improperly focused lens, or a shaky camera.

These problems can be attacked with either analog or digital filters. Which is better? Analog filters are cheap, fast, and have a large dynamic range in both amplitude and frequency. Digital filters, in comparison, are vastly superior in the level of performance that can be achieved. For example, a low-pass digital filter presented in Chapter 16 has a gain of 1 +/- 0.0002 from DC to 1000 hertz, and a gain of less than 0.0002 for frequencies above 1001 hertz. The entire transition occurs within only 1 hertz. Don't expect this from an op amp circuit! Digital filters can achieve thousands of times better performance than analog filters. This makes a dramatic difference in how filtering problems are approached. With analog filters, the emphasis is on handling limitations of the electronics, such as the accuracy and stability of the resistors and capacitors. In comparison, digital filters are so good that the performance of the filter is frequently ignored. The emphasis shifts to the limitations of the signals, and the theoretical issues regarding their processing.

It is common in DSP to say that a filter's input and output signals are in the time domain. This is because signals are usually created by sampling at regular intervals of time. But this is not the only way sampling can take place. The second most common way of sampling is at equal intervals in space. For example, imagine taking simultaneous readings from an array of strain sensors mounted at one centimeter increments along the length of an aircraft wing. Many other domains are possible; however, time and space are by far the most common. When you see the term time domain in DSP, remember that it may actually refer to samples taken over time, or it may be a general reference to any domain that the samples are taken in.

### III. MATCHED FILTER AND ITS DESIGN TECHNIQUES

The signal is mainly affected by the strong noise in digital Communication. So, the receiver system must have the capability to reduce this noise before decoding. Hence Matched Filters are used to maximize the SNR at the receiver. Matched filter are used in many areas, such as radar and image processing to improve SNR. The matched filter and pulse compression concepts are the basic of radar processing algorithms. Since radar return is always susceptible to noise and interference from all kinds of objects illuminated by the antenna beam, the receiver must be optimized. Pulse Compression involves using a matched filter to compress the energy in a signal into a relative narrow pulse. Pulse compression is the classical signal processing techniques to increase the range resolution of transmitted pulse without having to increase the peak transmit power. The LFM, or chirp waveform, has superior performance in pulse compression radar since they can be easily generated and

processed. Many diverse techniques and devices have been developed to provide the required pulse compression processing for these signals. However, the LFM has large side lobes with respect to the main lobe. Reducing the side lobes can be accomplished by linear filtering the output, i.e. applying window functions which are known as the spectrum weighting. TheDistributed Arithmetic (DA) based higher order Matched FIR filter is implemented. For FIR filters, output is a linear convolution of weights and inputs. For an Nthorder FIR filter, the generation of each output sample takes N+1 multiply accumulate (MAC) operations. Multiplication is strongest operation because it is repeated addition. It requires large portion of chip area. Power consumption is more. Memory-based structures are more regular compared with the multiply accumulate structures; and have many other advantages. Memory based structures are well-suited for many digital signal processing (DSP) algorithms, which involve multiplication with a fixed set of coefficients. For this Distributed Arithmetic architecture used in FIR filter. Distributed arithmetic is one way to implement convolution with multiplier less unit, where the MAC operations are replaced by a series of LUT access and summations. Basically, each look up table is a bunch of single bit memory cells storing individual bit values in each of the cells. Distributed Arithmetic provides cost-effective and area-time efficient computing structures.

### **IV. DESIGN TOOLS**

In this mentioned about the software used and coding language. For the proposed design HDL designer software is used and to know the simulation result Modelsim software is utilized. In VLSI technology design we use different languages like VHDL, Verilog, System verilog etc. Verilog language is used for the design. In this the creation of a project in HDL designer, how to simulate the design implementation and about the verilog language with some examples are explained. To establish tools for the execution of designs by utilizing VHDL, HDL designer is launched. The tools we'll use are Modelsim from Mentor Graphics for VHDL simulation and HDL designer that additionally return from Mentor Graphics for design and architectural/graphical design approach.

### HDL Designer:

We 1st outline the fundamentals of the hdl designer atmosphere and element ideas. To demonstrate the chance of hierarchic design we have a tendency to utilize the flexibility to form one or a lot of views to every element. We have a tendency to 1st add the component symbol and a behavioural design. The design is then simulated and valid.

### Top down design:

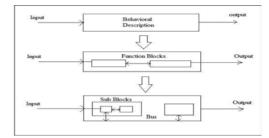

Here the overview of a model as a step within the design flows of sequential clarification. To every model variety of sub blocks exist, that are achieved as sufficiently outlined blocks are obtained. The objectives for every model are declared before in design. In top-down design we tend to develop the system stepwise by synthesizing and confirming every level. The design levels are in turn divide into sub blocks. This method for decomposition is continuous till sufficiently small blocks are obtained, as shown in

Figure. The process of putrefaction with ordered clarification additionally guarantees that larger and much of necessary problems are rectified before the flowery problems.

Figure. Top down design flow

Since the issue that modifies the structure of every level within the design method, the design will at all levels are attainable to prove against the highest model with same validation strategies.

### **Creating a Project:**

- ♣ Begin Mentor graphics hdl designer.

- ◆ Open the terminal (Start->Accessories->Terminal)

♣ Set up the atmosphere by writing the following to the terminal

♣ \$ source /share/tktprog/mentor/hds-2008.1a/hds.sh

- ♣ The HDL designer is start by writing \$ hds&

- ✤ If you begin the program for the first time, press "Cancel" to exit the HDS setup assistant

- ♣ Generate a new project by giving name.

- ♣ Give the name for project and set directory.

| Browse |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

### 4.3 Modelsim Software:

- The designs are compiled into a library in modelsim. You typically start a new simulation in Modelsim by making an operating library referred to as "work". "Work" is the library name employed by compiler.

- Compiling Your Design: After making the operating library, you compile your architectural components into it. You'll be able to simulate your design on any platform without having to recompile your design.

- Load the simulator with your design and run the simulation with the design compiled, you load the simulator together with your design by bringing the simulator on a top module.

- By supposing the design loads with favorable outcomes, the simulation time is ready to made zero, after that you go into a run command to start simulation.

- Debugging results, if you don't get the results you expect, you can use ModelSim's robust debugging environment to track down the cause of the problem. 4.3.1 Introduction to Model Simulator:

**Basic Simulation Flow:** The figure 4.2 gives the idea for simulating a design in Modelsim tool.

Figure 4.2 Basic simulation flow

**Project Design Flow:** As you will saw, the flow is exact as the basic simulation flow. However, the twomain dissimilarities are given.

- You don't have to be compelled togenerate an operating library within the project flow, it's done for you automatically.

- They'll open on every occasion you requestModelsim unless you specifically shut them.

- Thebelow diagram gives the basic steps for simulating a design among a Modelsim project.

Figure 4.3 Project design flow

# **4.3.2 Introduction to XILINX ISE (Integrated Software Environment):**

The Xilinx tool may utilize to create, implement, simulate and synthesize verilog design to execute on FPGA.

- Domain for the implementation and checking the digital systems design aims to FPGA or CPLD.

- Integrated collection of tools attainable through a GUI

- Based on a logical synthesis design

- XST hold up dissimilar languages

- ≻ Verilog

> VHDL

- ➤ XST generate a net list united with restriction

- Supports all the steps required to complete the design

- ➤ Convert, map, place and route

- ➤ Generating bit stream

- Bear up confirmation at non identical pace of the design

- To check the functionality of design, test bench is written by utilizing files on the host computer. Implementation:

- Synthesis (XST): Produce a net list file beginning from an HDL description

- Translate (NGD Build): Change all input then write the results on one integrated file, that describes logic and constraints.

- ➤ Mapping (MAP): Device elements are mapped with logic. Takes a net list and teams the logical components into CLBs and IOBs. □ Place and route (PAR): Locate FPGA cells and then join cells.

### XILINX Design Process:

- Step1: Design entry HDL (Verilog or VHDL, ABEL x CPLD), Schematic Drawings, and Bubble Diagram.

- Step2: Synthesis Converts to .v, .vhd, .sch files into a net list file (.ngc)

- Step3: Implementation FPGA: Translate/Map/Place & Route, CPLD: Fitter

- Step4: Configuration/Programming Download a BIT file into the FPGA – Program JEDEC file into CPLD – Program MCS file into Flash PROM Simulation can occur after steps 1, 2, 3

### 4.4 Verilog Language:

Verilog hdl is the one in every of the two commonest Hardware Description Languages (HDL) utilized by integrated circuit (IC) designers. Another coding language is VHDL. HDL is permits the design to be replicated advance within the design cycle so as to rectify mistakes or test with dissimilar design. Architectures represented in hdl are not depends on technology, simple to implement and correct, and are normally more understandable than schematics. Verilog are often describing styles at four levels of abstraction.

- 1. Algorithmic level

- 2. Register transfer level

- 3. Gate level

- 4. Switch level

The language additionally explains erects that may be worn to restraint the input and output of simulation. Some Verilog constructs don't seem to be producing electronically.Most readers can need

to produce electronically their circuits, thus non synthesizable constructs ought to be used just for test benches. The words "not synthesizable" will be used for examples and constructs as needed that do not synthesize. The types of code in most HDLs are two types;

Structural, the diagrams in structural are verbal wiring which are with the absence of memory.

assign a=b | c & d; /\* "|" is a OR \*/ assign p = (~q) & (r); The orders of the statements are not a matter. Change in **a**will occur by changing in **c**.

Procedural which is utilized to the circuits with memory, or a correct method to scribble conditional logic.

always @(posedgeclk) // Execute the next statement on every rising clock edge.

Count <= count+1;

For composite, with flip-flop memory, this way of idea creates an excessive quantity of memory. But folks like procedural code as a result of it's typically abundant easier to put in writing, as an example, **if** and **case** statements square measure solely allowed in procedural code. As a result, the synthesizers are created which might acknowledge bound kinds of procedural code as truly combinatory. But if you digress from this vogue, beware.

### 4.4.1 Lexical tokens:

- $\succ$  White space

- > Comments

- > Numbers

- ➤ Identifiers

- $\succ$  Operators  $\Box$  Key words

**Numbers:** Number of bits is used to represent number storage, in the verilog language the numbers are represented in binary, octal, decimal and hexadecimal.

Examples are 3'b110, a 4-bit number, 5'd20, (=5'b1010 0), and 16'h6ED4,

### (=16**'d**28372)

**Identifiers:** Identifiers are user defined words for function names, variables, block names, module names and instance names. An underscore or a letter (not with a \$ or a number) is used to start the identifiers and may add any number of letters, digits and underscores. Verilog has case sensitive identifiers.

**Operators:** To perform some operations on variables operators are used. The operators are one, two and three characters.

- Arithmetic operators

- Relational operators

- Bitwise operators

- Logical operators

- Reduction operators

- Shift operators

- Concatenation operators

- Replication operators

- Conditional operators

**Key words:** These are the words which have special meaning in Verilog. Some examples of the key words are assign, case, while, wire, reg, and, or, nand, and module.

### 4.4.2 Verilog modelling:

Verilog has four types of modelling. They are

- 1. The switch level of modelling.

- 2. The gate level of modelling.

- 3. The Data flow modelling.

- 4. The Behavioral modelling.

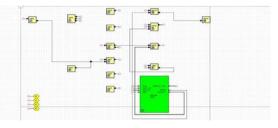

## V. RESULTS AND DISCUSSIONS

# Fig. Test Bench for the DA based FIR matched filter

#### VI. CONCLUSION:

This paper has discussed an effective method for designing FIR filter and match filter of isolated less power consume and less delay time. It presents a parallel designing of filter for image recognition recent years there has been a steady movement towards the development of image recognition technologies to replace or enhance text input called as have Mobile, video Search Applications. Recently NASA is working search applications. Future work can include improving the recognition filter design of the individual image reorganization by combining the multiple classifiers. Matched filters are designed to extract the maximum SNR of a signal that is buried in noise.

#### REFERENCES

- [1] Fast Implementation of Matched Filter Based Automatic Alignment Image Processing, A.A. S. Awwal, K. Rice, T. Taha ,LLNL JRNL 4028821,April 9, 2008,

- [2] K. C. Wilhlelmsen, A. A. S. Awwal, S. W. Ferguson, B. Horowitz, V. J. Miller Kamm, C.A. Reynolds October 5, 2007, International Conference on Accelerator and Large, Knoxville, TN, United States Experimental Physics Control Systems, October 5, 2007

- [3] Implementation of Accelerated Beam-Specific Matched-Filter-Based OPTICAL ALIGNMENT A. A. S. Awwal, K. L. Rice, T. M. Taha ,February 9, 2009

- [4] A. Awwal et al., "Uncertainty Detection for NIF Normal Pointing Images," in Optics and Photonics for Information Processing, Proc. SPIE Vol. 6695,66950R (Sep. 20, 2007).

- [5] Introduction to matched filters, John C. Bancroft

- [6] Ziemer, R.E., and Tranter, W.H., 1988, Principles of Communications, John Wiley and Sons, pages 465-468.

- [7] A Novel Design of Matched Filter for Digital Receivers in IJRTE,ISSN: 2277-3878,Volume -8, Issue-3, September 2019.

- [8] Fast Implementation of Matched Filter with Less Power and Less Delay in IJERT ISSN: 2278-0181,Vol.2 Issue-6, June 2013.

- [9] Matched -Filter Loss from Time -varying Rough -surface Reflection with a Small Effective Ensonified Area by Douglas A Abraham,senior member,IEEE, Stefan M.Murphy,Paul C.Hines,and Anthony, p.lyons, member IEEE in february 2017.

- [10] Detecting Signals with Known Form:Matched Filters by Douglas A

Abraham, published in Under water Acoustic Signal Processing, 2019.

[11] Robust Matched Filters for Target Detection in Hyperspectral Imaging Data by J Jacobson, in IEEE 1-4244-0728-1/07,2007.