# Design of Efficient DNN Accelerator Architectures

A thesis submitted to the College of Graduate and Postdoctoral Studies (CGPS) in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical & Computer Engineering University of Saskatchewan Saskatoon, Canada

> By Mohammadreza Asadikouhanjani

© Copyright Mohammadreza Asadikouhanjani, July 2022. All rights reserved. Unless otherwise noted, copyright of the material in this thesis belongs to the author.

# **Permission to Use**

In presenting this thesis/dissertation in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis/dissertation in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis/dissertation work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis/dissertation or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis/dissertation.

# Disclaimer

Reference in this thesis to any specific commercial products, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement, recommendation, or favoring by the University of Saskatchewan. The views and opinions of the author expressed herein do not state or reflect those of the University of Saskatchewan, and shall not be used for advertising or product endorsement purposes

Request for permission to copy or to make any other use of material in this thesis in whole or in part should be addressed to:

Head of the Division of Biomedical Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan, Canada S7N 5A9

OR

Dean College of Graduate and Postdoctoral Studies University of Saskatchewan 116 Thorvaldson Building, 110 Science Place Saskatoon, Saskatchewan S7N 5C9 Canada

# Abstract

Deep Neural Networks (DNNs) are the fundamental processing unit behind modern Artificial Intelligence (AI). Accordingly, expecting a future with smart devices that are able to monitor, decide, and take action seems reasonable. However, DNNs are computation and power-hungry, which makes deployment of them into edge devices challenging. The focus of this dissertation is on designing architectures to perform the inference of DNNs efficiently. The contents of this dissertation can be divided into four specific areas: (1) early detection of the ineffectual computations inside the computation engine; (2) enhancing the utilization of Processing Elements (PEs) inside the computation (MAC) operations; (4) the design of approximate DNN accelerators.

In most DNNs, an activation function follows a convolutional or a fully connected layer. Several popular activation functions involve setting all negative inputs to zero. In this dissertation, firstly, the characteristics of activation layers that are considered for adding non-linearity to DNNs are studied. Then, a novel architecture in which the activation function is merged with the prior computational layer is proposed. To add more detail, the proposed architecture coordinates early sign detection of output features. When compared to the original design, our method achieves a speedup of  $\times 2.19$  and reduces energy consumption by  $\times 1.94$ . The average reduction in the number of multiply-accumulate (MAC) operations is 10.64% and the average reduction in the number of the load operations is 3.86%. These improvements are achieved while maintaining classification accuracy in two popular benchmark networks.

One of the main challenges that DNN accelerator developers face is keeping all the PEs busy with performing effectual computations while running DNNs. In this dissertation, a Twin-PE for spatial DNN accelerators is introduced that increases the utilization of the PEs and the performance of the whole computation engine. In more detail, the proposed architecture which comes with a negligible area overhead is implemented based on sharing the scratchpads between the PEs to use the available slack time caused by applying computation-pruning techniques. When compared to the reference design, our proposed method achieves a speedup of  $\times 1.24$  and an energy efficiency of  $\times 1.18$  per inference.

Decomposing the MAC operations down to bit-level provides the chance of skipping bit-wise and word-wise sparsity. However, there is still room for pruning the effectual computations without reducing the accuracy of DNNs. In this dissertation, a novel real-time architecture by decomposing multiplications down to bit level and pruning identical computations while running benchmark networks. Our proposed design achieves an average per layer speedup of  $\times 1.4$  and an energy efficiency of  $\times 1.21$  per inference while maintaining the accuracy of benchmark networks.

Applying approximate computing techniques reduces the cost of the underlying circuits so that DNN inference would be performed more efficiently. However, applying approximation to DNNs is somehow different from other applications. In this dissertation, a step-wise approach for implementing a re-configurable Booth multiplier suitable for inference of DNNs is proposed. In addition, the tolerance of different layers of DNNs to approximation is evaluated and the effect of applying various degrees of approximation on inference accuracy is explored. The proposed design achieves an area efficiency of  $\times 1.19$  and energy efficiency of  $\times 1.28$  compared to the exact design while running benchmark DNNs.

## Acknowledgments

I would like to express my sincere appreciation to my supervisor Dr. Seok-Bum Ko for his continuous support throughout the course of my Ph.D. studies. His immense knowledge and experience in the field has given him an excellent eye for worthwhile research opportunities, and I can not thank him enough for the patience, compassion, and encouragement he has shown me. Without his guidance, this dissertation would not have been possible.

I would also like to express sincere gratitude to my lab-mate Hao Zhang for his vast technical knowledge and the prompt assistance he always gave me when troubleshooting issues in the lab. My lab-mates have continuously taken the extra step to help me out when I need it, and I can not overstate how much I appreciate their support.

I thank my mom, my dad, my sister, and my brothers for their endless patience throughout my studies. It goes without saying that research can impose a sense of intimidation and frustration from time to time. I am so incredibly grateful for the support provided by my family and friends during those times that I was feeling under confident. It was because of their encouraging words that I was also able to experience the joy and accomplishment of seeing my research through.

Last but not the least, my sincere thanks to the Natural Sciences and Engineering Research Council of Canada (NSERC), the R&D program of the Korean Ministry of Trade, Industry and Energy (MOTIE), the Korea Evaluation Institute of Industrial Technology (KEIT), and the Department of Electrical and Computer Engineering, University of Saskatchewan. To all those who are patient and persistent in encouraging me, you have shown me that I am much more capable than I thought myself to be.

# **Table of Contents**

| Pe | ermiss          | sion to Use                                          |   |     |  |  |     |     | i   |

|----|-----------------|------------------------------------------------------|---|-----|--|--|-----|-----|-----|

| Al | Abstract        |                                                      |   |     |  |  | iii |     |     |

| Ac | Acknowledgments |                                                      |   |     |  |  | v   |     |     |

| Ta | able of         | f Contents                                           |   |     |  |  |     |     | vii |

| Li | st of A         | Abbreviations                                        |   |     |  |  |     |     | xii |

| Li | st of ]         | Tables                                               |   |     |  |  |     |     | xiv |

| Li | st of l         | Figures                                              |   |     |  |  |     |     | xvi |

| 1  | Intr            | oduction                                             |   |     |  |  |     |     | 1   |

|    | 1.1             | Overview of DNNs                                     |   | • • |  |  |     | ••• | 1   |

|    |                 | 1.1.1 The Basics                                     |   | • • |  |  |     | ••• | 2   |

|    | 1.2             | Motivations of Research Works                        | • |     |  |  | •   | • • | 8   |

|    |                 | 1.2.1 Ineffectual MAC Operations in DNNs             | • |     |  |  | •   | • • | 8   |

|    |                 | 1.2.2 Divergence of the Workloads in Spatial Designs | • |     |  |  |     |     | 8   |

|    |                 | 1.2.3 Skipping Identical Bit-wise Computations       | • |     |  |  |     |     | 9   |

|    |                 | 1.2.4 Applying Approximation into DNNs               | • |     |  |  | •   | • • | 10  |

|    | 1.3             | Overview of Research Works                           | • |     |  |  | •   | • • | 11  |

|    | 1.4             | Contributions of This Dissertation                   | • |     |  |  |     |     | 14  |

|    | 1.5             | Publications During Ph.D. Research                   | • |     |  |  |     |     | 15  |

|    |                 | 1.5.1 Published Journal Papers                       | • |     |  |  |     |     | 15  |

|   |      | 1.5.2   | Other publications                                   | 15 |

|---|------|---------|------------------------------------------------------|----|

|   |      | 1.5.3   | Other publications not included in this dissertation | 16 |

| 2 | Revi | ew of C | contemporary DNN Accelerators                        | 17 |

|   | 2.1  | Spatial | Designs vs Temporal Designs                          | 17 |

|   | 2.2  | DNN A   | Accelerators                                         | 18 |

| 3 | Earl | y Detec | tion of Negative Output Features                     | 28 |

|   | 3.1  | Introdu | action                                               | 29 |

|   | 3.2  | Contri  | butions of this chapter                              | 30 |

|   | 3.3  | Propos  | ed Computation Technique                             | 30 |

|   | 3.4  | Propos  | ed Architecture                                      | 32 |

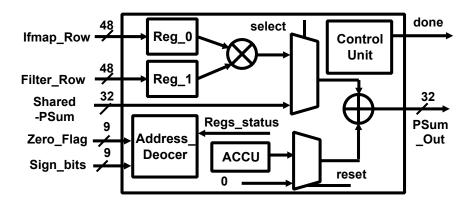

|   |      | 3.4.1   | PE Specification                                     | 32 |

|   |      | 3.4.2   | Loading Ifmaps and Filters Into the PEs              | 33 |

|   |      | 3.4.3   | Address Decoder Unit                                 | 33 |

|   |      | 3.4.4   | MAC Operation                                        | 33 |

|   |      | 3.4.5   | Computation Reordering by the Main Control Unit      | 34 |

|   |      | 3.4.6   | Computation Engine Size and NoC Specifications       | 34 |

|   | 3.5  | Propos  | ed Dataflow                                          | 35 |

|   |      | 3.5.1   | Energy Cost of Basic Operations and Data Movement    | 35 |

|   |      | 3.5.2   | 2-D PE Sets and Processing Pass                      | 36 |

|   |      | 3.5.3   | Local Reuse of Ifmap Rows, Filter Rows, and Psums    | 37 |

|   |      | 3.5.4   | Computation Engine Configuration and Mapping Formats | 37 |

|   |     | 3.5.5    | Convolution Direction and Global Buffer Access           | 37 |

|---|-----|----------|----------------------------------------------------------|----|

|   |     | 3.5.6    | PE Set Synchronization                                   | 37 |

|   | 3.6 | Results  | s and Discussion                                         | 38 |

|   |     | 3.6.1    | Mapping Benchmark Networks to the Proposed Accelerator   | 38 |

|   |     | 3.6.2    | Implementation                                           | 39 |

|   |     | 3.6.3    | Hardware Performance Evaluation                          | 39 |

| 4 | Enh | ancing   | the Utilization of PEs in Spatial DNN Accelerators       | 42 |

|   | 4.1 | Introdu  | action                                                   | 43 |

|   | 4.2 | Propos   | ed Computation Technique                                 | 44 |

|   | 4.3 | Propos   | ed Architecture                                          | 46 |

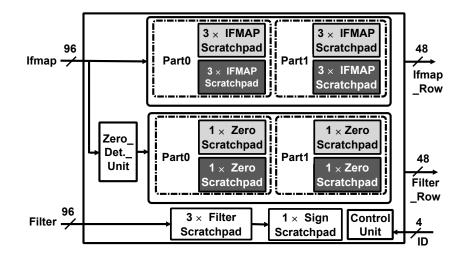

|   |     | 4.3.1    | MAC Unit Specifications                                  | 46 |

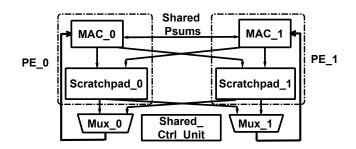

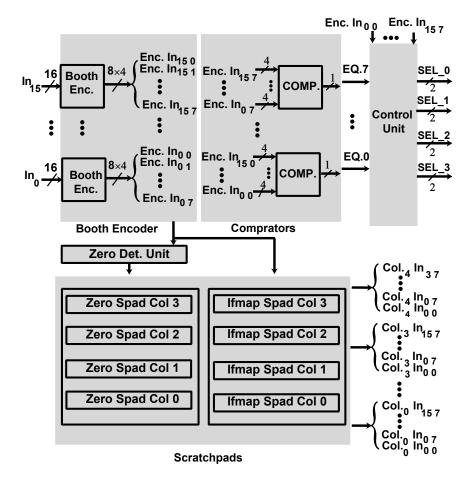

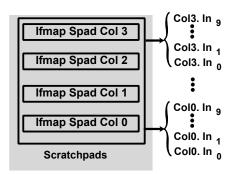

|   |     | 4.3.2    | Scratchpad Unit Specifications                           | 48 |

|   |     | 4.3.3    | Twin-PE                                                  | 49 |

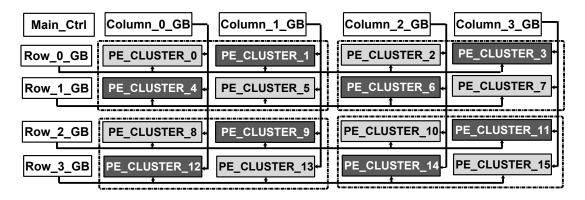

|   |     | 4.3.4    | Computation Engine Architecture and NoC Specifications   | 49 |

|   | 4.4 | Propos   | ed Dataflow                                              | 51 |

|   |     | 4.4.1    | Sharing The Scratchpads of the PEs of Different Clusters | 51 |

|   |     | 4.4.2    | Negative Output Detection                                | 52 |

|   | 4.5 | Results  | s and Discussion                                         | 52 |

|   |     | 4.5.1    | Implementation                                           | 52 |

|   |     | 4.5.2    | Hardware Performance Evaluation                          | 52 |

| 5 | Pru | ning the | Effectual Computations in DNNs                           | 55 |

| 5.1   | Introd   | uction                                                                 | 56  |

|-------|----------|------------------------------------------------------------------------|-----|

| 5.2   | Identic  | cal Effectual Computations                                             | 58  |

|       | 5.2.1    | Identical bit values among filter weights                              | 59  |

|       | 5.2.2    | Identical bit values among ifmaps                                      | 62  |

| 5.3   | Propos   | sed Computation Technique                                              | 62  |

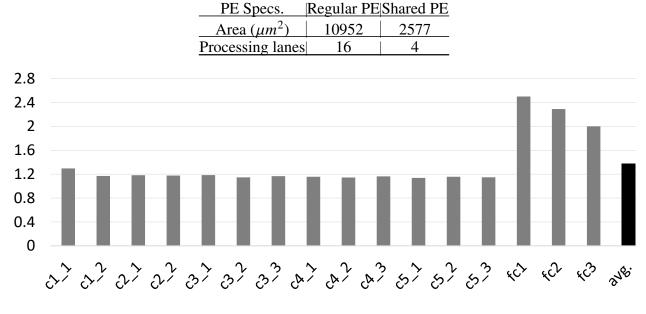

| 5.4   | The A    | rchitectures of Regular and Shared PEs                                 | 67  |

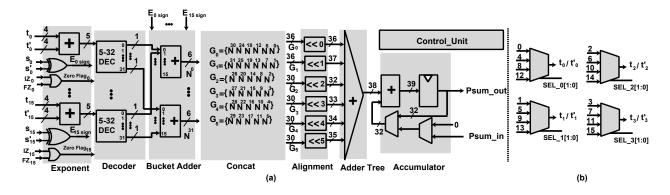

|       | 5.4.1    | Regular PE Unit Specifications                                         | 67  |

|       | 5.4.2    | Shared PE Unit Specifications                                          | 68  |

| 5.5   | Genera   | al Architecture of Our Proposed Accelerator                            | 69  |

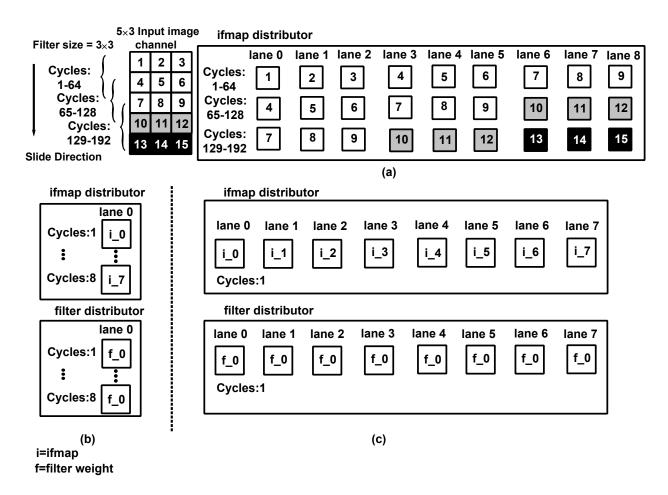

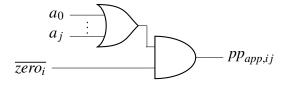

|       | 5.5.1    | Distributor Units                                                      | 71  |

|       | 5.5.2    | Global Buffers                                                         | 73  |

| 5.6   | Propos   | sed Dataflow                                                           | 73  |

| 5.7   | Result   | s and Discussion                                                       | 76  |

|       | 5.7.1    | Implementation                                                         | 76  |

|       | 5.7.2    | Hardware Performance Evaluation                                        | 77  |

| Effic | cient Ap | oproximate DNN Accelerators for Edge Device                            | 83  |

| 6.1   | Re-con   | nfigurable Approximate MAC Unit                                        | 84  |

|       | 6.1.1    | Introduction                                                           | 84  |

|       | 6.1.2    | Designing a Re-Configurable Approximate Booth Multiplier for Inference |     |

|       |          | of DNNs                                                                | 86  |

|       | 6.1.3    | Proposed Architecture                                                  | 105 |

|       | 6.1.4    | Experimental Results and Discussion                                    | 108 |

6

|   |     | 6.1.5                                                                    | Hardware Implementation                               | 111 |

|---|-----|--------------------------------------------------------------------------|-------------------------------------------------------|-----|

|   | 6.2 | 6.2 Applying Various Degrees of Approximation to Different layers of DNN |                                                       | 114 |

|   |     | 6.2.1                                                                    | Introduction                                          | 114 |

|   |     | 6.2.2                                                                    | Applying Various Degrees of Approximation at Run-Time | 115 |

|   |     | 6.2.3                                                                    | Proposed Architecture                                 | 120 |

|   |     | 6.2.4                                                                    | Experimental Results and Discussion                   | 122 |

| 7 | Con | clusions                                                                 | s and Future Works                                    | 129 |

|   | 7.1 | Summ                                                                     | ary & Conclusions                                     | 129 |

|   | 7.2 | Future                                                                   | Works                                                 | 131 |

# List of Abbreviations

| ADC   | Analog to Digital Converters             |

|-------|------------------------------------------|

| AI    | Artificial Intelligence                  |

| ASIC  | Application-Specific Integrated Circuits |

| CPU   | Central Processing Unit                  |

| DAC   | Digital to Analog Converters             |

| DNN   | Deep Neural Network                      |

| DRAM  | Dynamic Random-Access Memory             |

| FFNNs | Feed Forward Neural Networks             |

| FPGA  | Field Programmable Gate Array            |

| GANs  | Generative Adversarial Networks          |

| GB    | Global Buffer                            |

| GPU   | Graphical Processing Unit                |

| Ifmap | Input feature map                        |

| LUT   | Look-up Table                            |

| MAC   | Multiply and Accumulate                  |

| MLP   | multi-layer perceptron                   |

| MXU   | Matrix Multiply Unit                     |

| NFU   | Neural Functional Unit                   |

| nlp   | natural language processing              |

| NN   | Neural Network                   |

|------|----------------------------------|

| NoC  | Network on Chip                  |

| PDP  | Power Delay Product              |

| PE   | Processing Element               |

| Psum | Partial sum                      |

| ReLU | Rectified Linear Unit            |

| RNNs | Recurrent Neural Networks        |

| SIMD | Single Instruction Multiple Data |

| VPU  | Vector Processing Unit           |

# List of Tables

| 3.1 | Energy cost of basic operations for the proposed accelerator.                                                | 34  |

|-----|--------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Mapping parameters for proposed dataflow.                                                                    | 34  |

| 3.3 | Reduction in MAC operations and speedup of the proposed dataflow compared to [1] while running AlexNet       | 40  |

| 3.4 | Reduction in MAC operations and speedup of the proposed dataflow compared to [1] while running VGG-16.       | 41  |

| 3.5 | Comparison of throughput and energy consumption                                                              | 41  |

| 4.1 | Comparison of throughput and energy consumption                                                              | 54  |

| 5.1 | Comparison of computation delay and number of MAC operations before and after pruning identical computations | 66  |

| 5.2 | Comparison of area consumption of regular and shared PEs                                                     | 78  |

| 5.3 | Comparison of throughput and energy consumption                                                              | 82  |

| 6.1 | Radix-4 Booth terms corresponding to various inputs and encoded signal values.                               | 88  |

| 6.2 | Accuracy report of the explored approximate designs while running benchmark                                  |     |

|     | DNNs                                                                                                         | 111 |

| 6.3 | Synthesis report of the explored multipliers                                                                 | 112 |

| 6.4 | Synthesis report of the explored DNN accelerators                                                            | 113 |

| 6.5 | Implementation report of the explored approximate computation engines                                        | 123 |

| 6.6 | Accuracy report of the explored approximate computation engines                                              | 126 |

| 6.7 | Performance report of the explored approximate computation engines while ac- |     |

|-----|------------------------------------------------------------------------------|-----|

|     | cepting 2% accuracy loss.                                                    | 128 |

# **List of Figures**

| 1.1 | Internal architecture of a Deep Neural Network                                                                                                                            | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | A simple 2D convolution example                                                                                                                                           | 5  |

| 1.3 | Overview of the architecture of VGG16                                                                                                                                     | 5  |

| 1.4 | Overview of the ReLU activation function                                                                                                                                  | 6  |

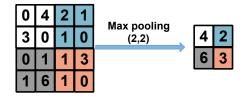

| 1.5 | A $2 \times 2$ Max pooling example $\ldots \ldots \ldots$ | 6  |

| 1.6 | The internal architecture of a simple Recurrent Neural Network                                                                                                            | 7  |

| 2.1 | Overview of (a) temporal architecture vs (b) spatial architectures [1]                                                                                                    | 18 |

| 2.2 | Row stationary dataflow [1]                                                                                                                                               | 19 |

| 2.3 | The general architecture of TPU V3 [2]                                                                                                                                    | 20 |

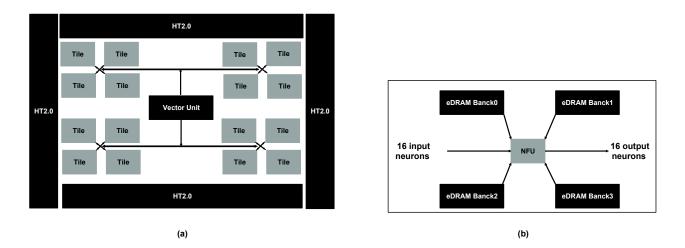

| 2.4 | The general architecture of (a) a node and (b) a tile in [3]                                                                                                              | 21 |

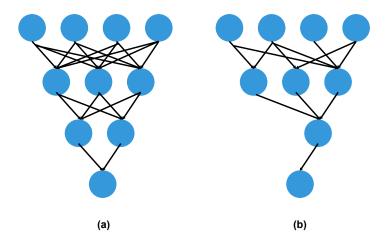

| 2.5 | The architecture of a simple DNN (a) before pruning, and (b) after pruning [4].                                                                                           | 22 |

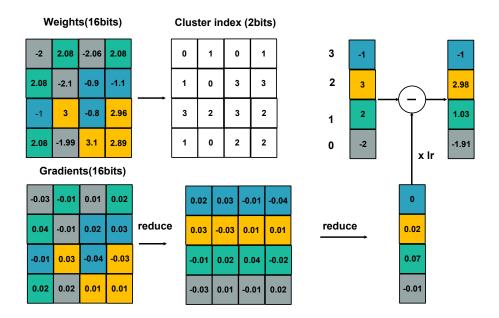

| 2.6 | A simple example to clarify the proposed weight sharing method in [4] for a $4 \times 4$ weight matrix                                                                    | 23 |

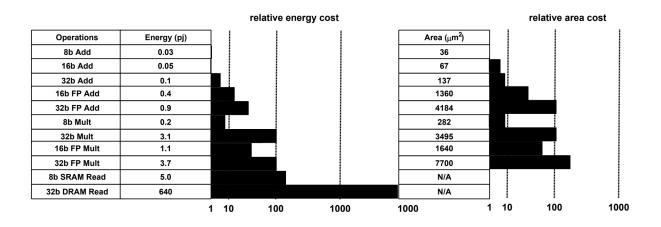

| 2.7 | Relevant cost of accessing to different levels of memory and performing a single                                                                                          |    |

|     | MAC operation in 45 nm technology                                                                                                                                         | 24 |

| 2.8 | A simple example on how to convert the weights of a DNN to ternary weights [5].                                                                                           | 24 |

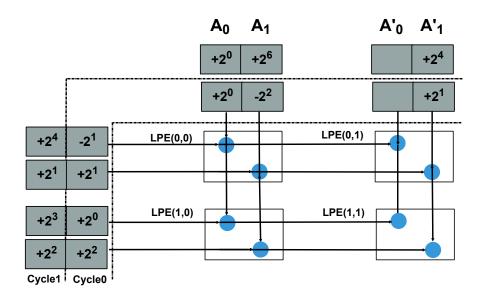

| 2.9 | Each Laconic PE in [6] processes weights and input feature maps as a series of                                                                                            |    |

|     | signed powers of two                                                                                                                                                      | 25 |

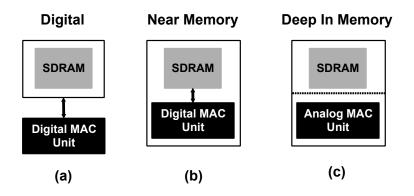

| 2.10 | There are three general architectures for DNN accelerators based on the place of                     |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | performing the computations, where in a (a) digital architecture, the processing unit                |    |

|      | and the memory chip are two different chips, in a (b) near memory architecture,                      |    |

|      | the processing unit and the memory both are on the same die, in a (c) deep in                        |    |

|      | memory architecture, the same technology is used for manufacturing both memory                       |    |

|      | and processing unit.                                                                                 | 26 |

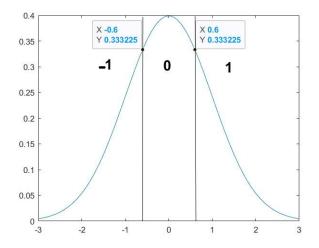

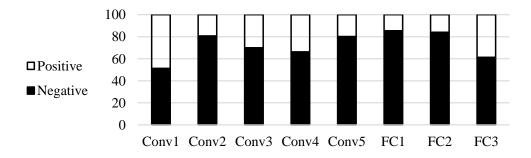

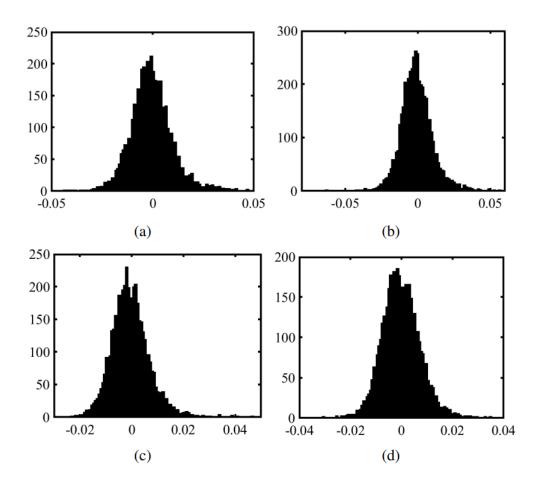

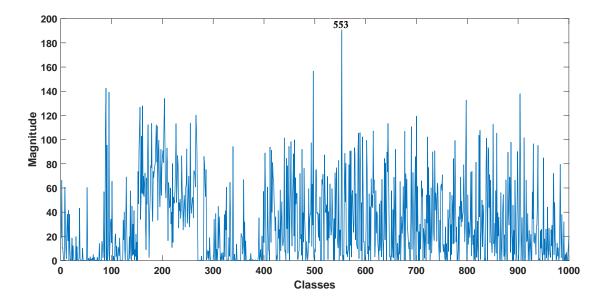

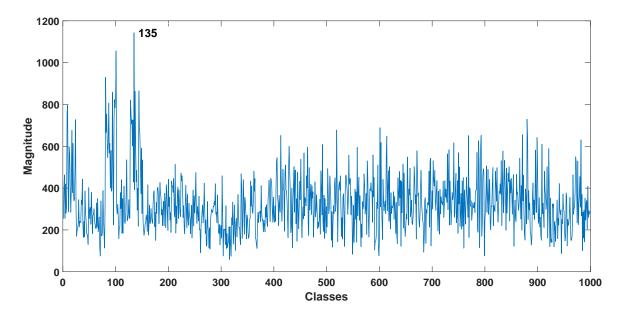

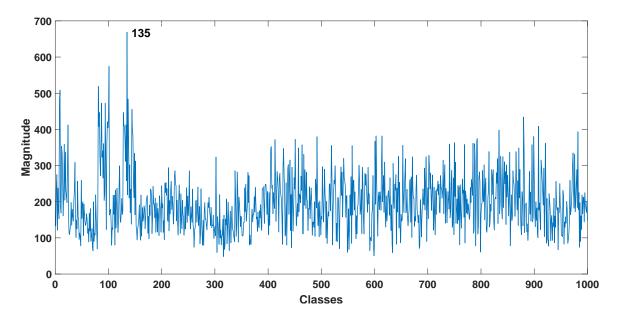

| 3.1  | Sign-based distribution of output features of various layers of AlexNet                              | 31 |

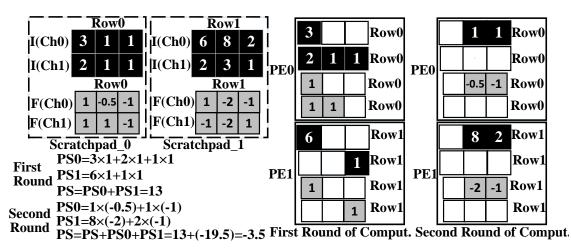

| 3.2  | A 2-D reordered convolution example in a spatial computation engine with two PEs.                    | 31 |

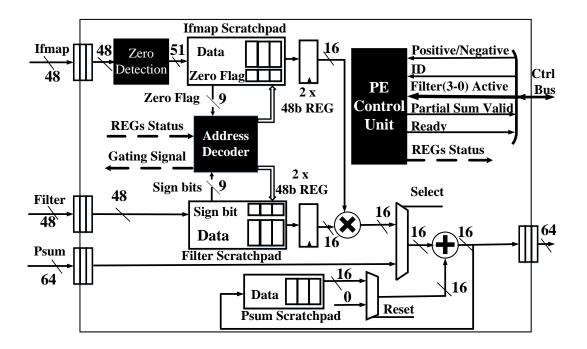

| 3.3  | The internal architecture of the proposed PE.                                                        | 32 |

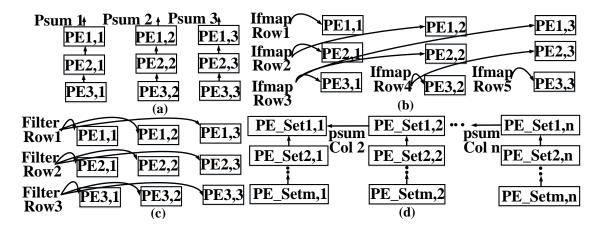

| 3.4  | Local reuse of data via (a) vertical reuse of psums, (b) diagonal reuse of ifmap                     |    |

|      | rows, (c) horizontal reuse of filter rows, and (d) horizontal reuse of psums across                  |    |

|      | the first row of the computation engine.                                                             | 35 |

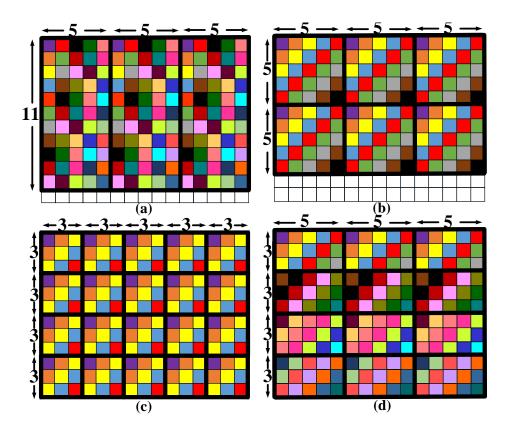

| 3.5  | Different configurations of the computation engine for calculating (a) 5 output                      |    |

|      | features for $11 \times 11$ filters and stride 4, (b) 5 output features for $5 \times 5$ filters and |    |

|      | stride 1, (c) 3 output features for $3 \times 3$ filters and stride 1, and (d) 3 output features     |    |

|      | for $3 \times 3$ filters and stride 1                                                                | 36 |

| 3.6  | If map reuse while loading the PE sets via (a) reusing the if maps diagonally, and                   |    |

|      | (b) reusing the ifmaps in a depthwise method                                                         | 38 |

|      |                                                                                                      |    |

| 4.1  | A 2×2 computation engine with horizontal and vertical 1D multi-cast NoC                              | 46 |

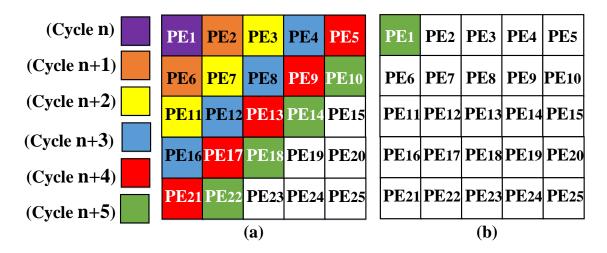

| 4.2  | Idleness of clusters in a $2 \times 2$ computation engine, where (a) shows the computations          |    |

|      | in cycles 0-3, and (b) shows the computations in cycles 4-7                                          | 46 |

| 4.3  | The status of clusters and their dataflow when (a) the scratchpads are not shared                    |    |

|      | compared to when (b) the scratchpads are shared                                                      | 47 |

| 4.4  | The internal architecture of the proposed MAC unit.                                                  | 47 |

| 4.5  | The internal architecture of the proposed Scratchpad                                                                                                                                                    | 48 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6  | The internal architecture of the proposed Twin-PE                                                                                                                                                       | 48 |

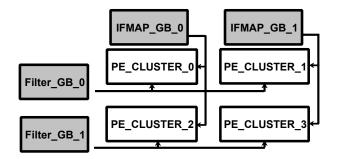

| 4.7  | The general architecture of the proposed accelerator.                                                                                                                                                   | 50 |

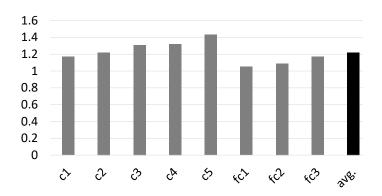

| 4.8  | Speedup of layers of AlexNet by sharing the scratchpads                                                                                                                                                 | 53 |

| 4.9  | Speedup of layers of VGG16 by sharing the scratchpads                                                                                                                                                   | 54 |

| 4.10 | Speedup of some layers of MobileNet V2 by sharing the scratchpads                                                                                                                                       | 54 |

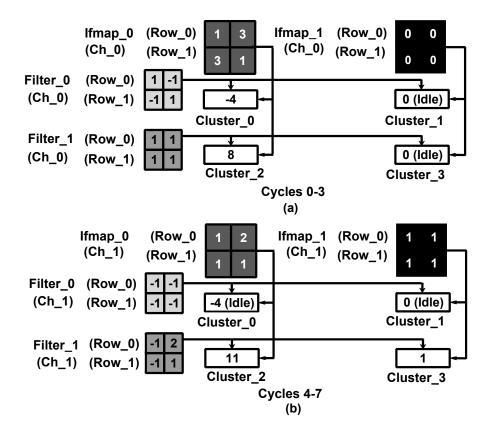

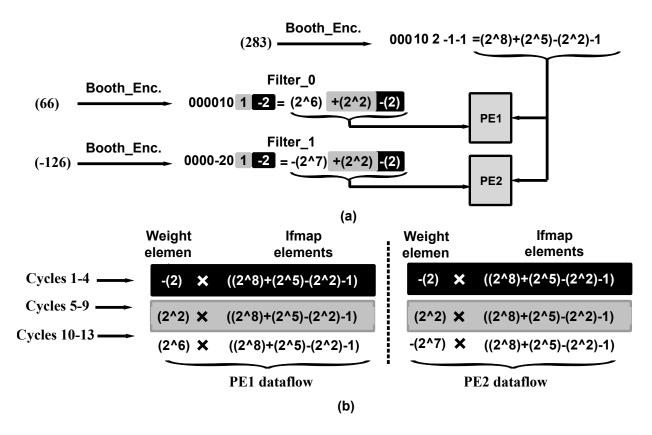

| 5.1  | The identical MAC operations by identifying (a) identical elements of the corresponding Booth-encoded weights and (b) their associated identical dataflow in a $2 \times 1$ spatial computation engine. | 60 |

| 5.2  | Distribution of the weights of filters (a) 17 (b) 244 (c) 245 (d) 421 of 9th convolu-<br>tional layer of VGG16.                                                                                         | 61 |

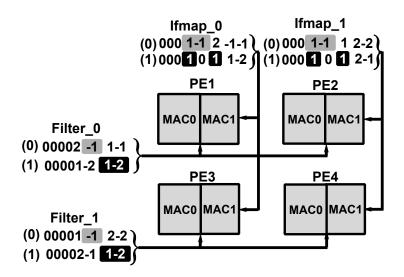

| 5.3  | A $2\times 2$ spatial computation engine that performs the computations of Booth-<br>encoded ifmaps and filter weights using regular PEs                                                                | 63 |

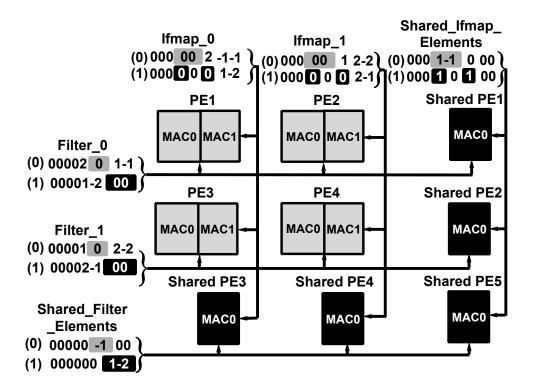

| 5.4  | A $3\times3$ spatial computation engine that prunes the computations by identifying identical bit values in ifmaps and weights only once using regular and shared PEs.                                  | 64 |

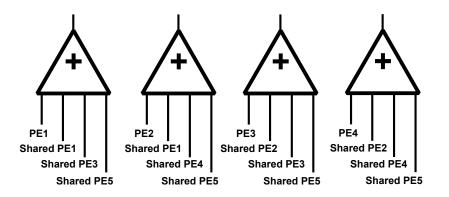

| 5.5  | Adder trees that are considered to calculate the final partial sums out of the com-<br>puted partial sums by both regular and shared PEs in a 3×3 spatial computation<br>engine                         | 64 |

| 5.6  | The internal architecture of the (a) regular PEs and the (b) considered multiplexers in the shared PEs for selecting the corresponding ifmaps or filter weights                                         | 67 |

| 5.7  | The general architecture of the proposed accelerator.                                                                                                                                                   | 70 |

| 5.8  | The internal architecture of the ifmap distributor unit.                                                                                                                                                | 70 |

| 5.9  | The proposed dataflow for (a) local reuse of the ifmaps in a PE while running con-                                                                                                        |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | volutional layers, performing the computations of fully connected and depth-wise                                                                                                          |    |

|      | convolutional layers when (b) intra-level parallelism is not supported compared to                                                                                                        |    |

|      | (c) when intra-level parallelism is supported                                                                                                                                             | 74 |

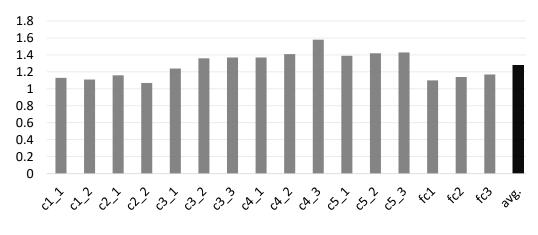

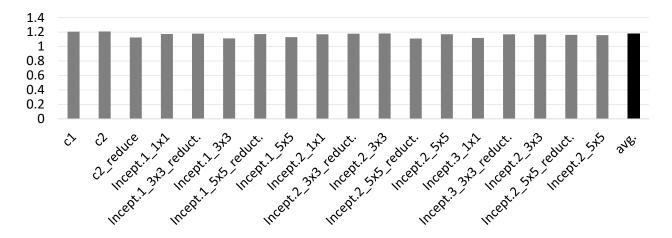

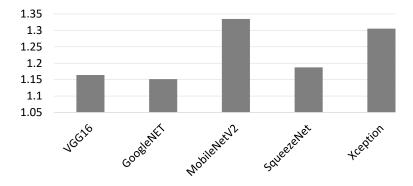

| 5.10 | Speedup of layers of VGG16 by pruning the identical effectual computations                                                                                                                | 78 |

| 5.11 | Speedup of a few layers of GoogleNet by pruning the identical effectual computations.                                                                                                     | 78 |

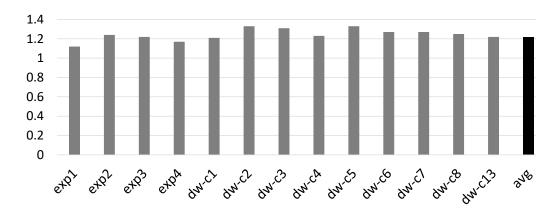

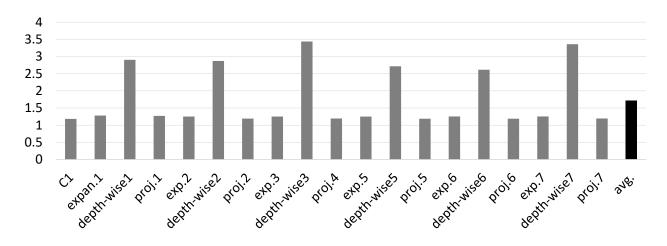

| 5.12 | Speedup of a few layers of MobileNet by pruning the identical effectual computations.                                                                                                     | 79 |

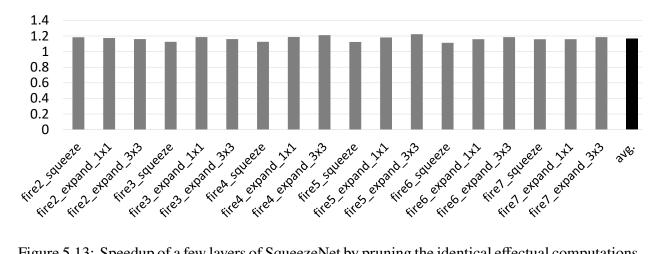

| 5.13 | Speedup of a few layers of SqueezeNet by pruning the identical effectual compu-<br>tations                                                                                                | 79 |

| 5.14 | Speedup of a few layers of Xception by pruning the identical effectual computations.                                                                                                      | 79 |

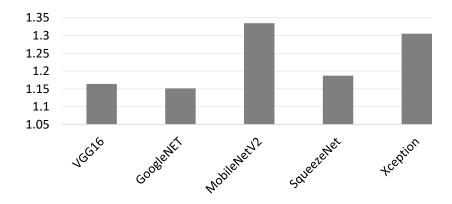

| 5.15 | The average energy efficiency of the proposed architecture over the reference design while running benchmark networks.                                                                    | 81 |

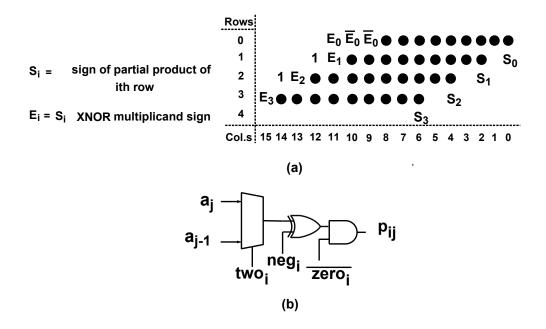

| 6.1  | The (a) dot-diagram of a signed 8×8 radix-4 Booth multiplier and the (b) internal architecture of the partial product generator in a radix-4 Booth multiplier. •: exact partial products. | 87 |

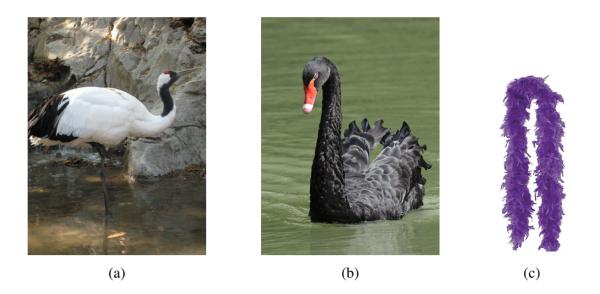

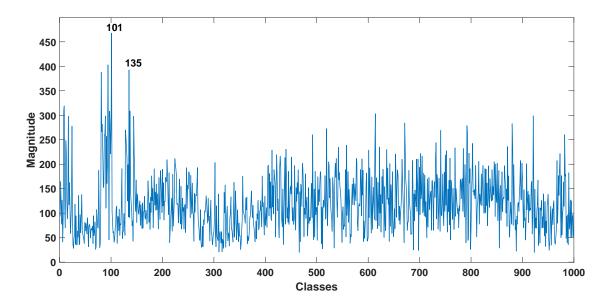

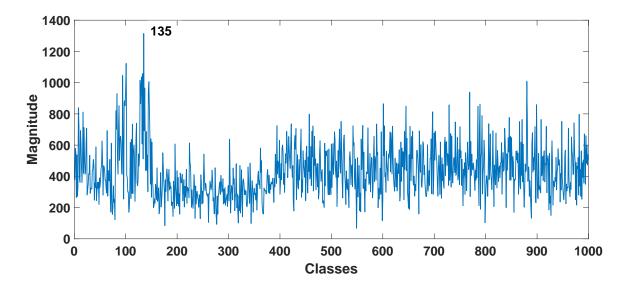

| 6.2  | Output of the proposed accelerator in Subsection 6.1.3 when a picture of a Crane is fed into this accelerator that runs Squeezenet in exact mode.                                         | 89 |

| 6.3  | Pictures of a (a) Crane, a (b) Black Swan, and a (c) Feather Boa.                                                                                                                         | 89 |

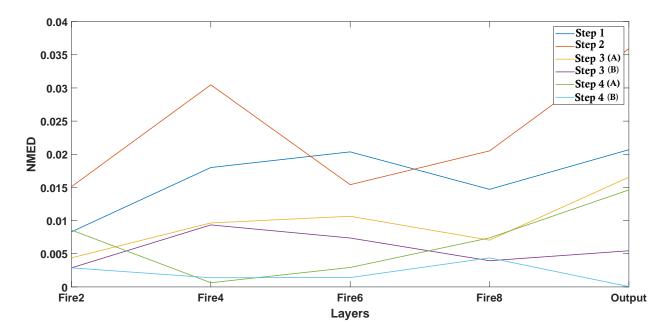

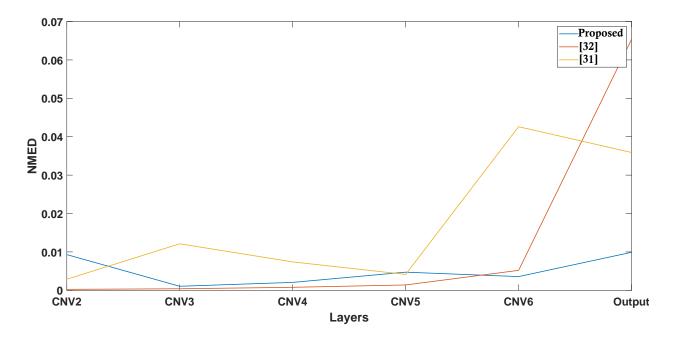

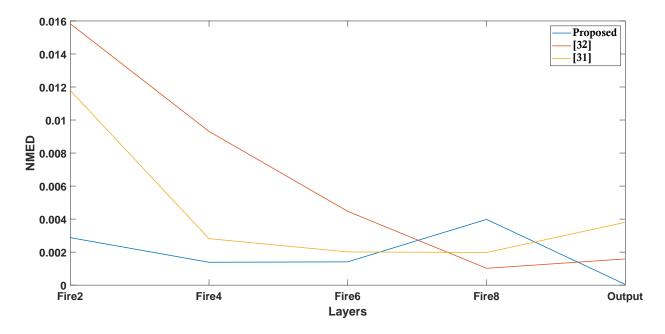

| 6.4  | The computed NMED of a few layers of SqueezeNet [7] for the variuos approxi-<br>mation techniques explored in Subsection 6.1.2 while running ImageNet dataset [8].                        | 90 |

| 6.5  | Output of the proposed accelerator when a picture of a Crane is fed into this accelerator, and all the correction terms are removed in all the Booth multipliers.                         | 92 |

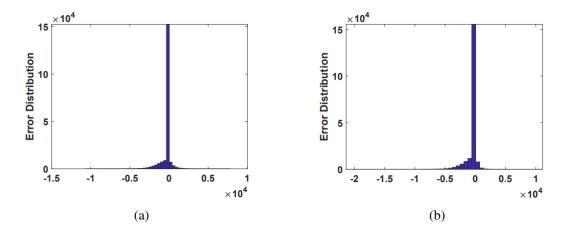

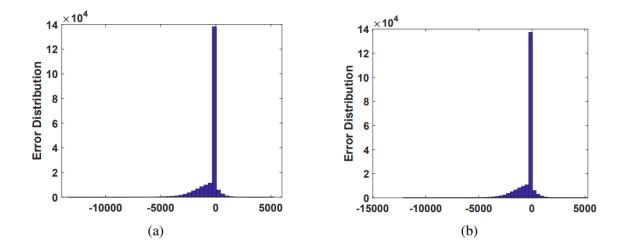

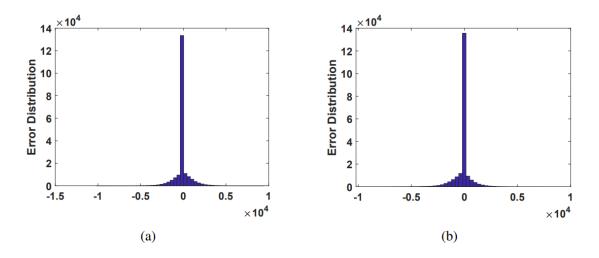

| 6.6  | The error distribution of Layer Fire 4 when (a) all the correction terms are removed,             |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | and when (b) the 5 least significant partial product columns are truncated in all the             |    |

|      | Booth multipliers.                                                                                | 92 |

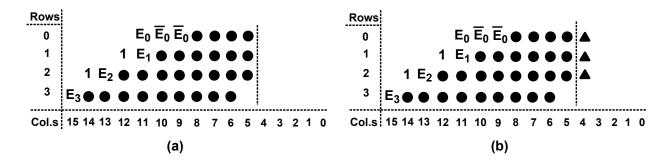

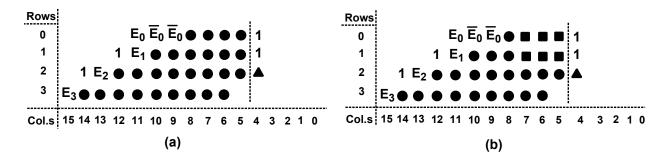

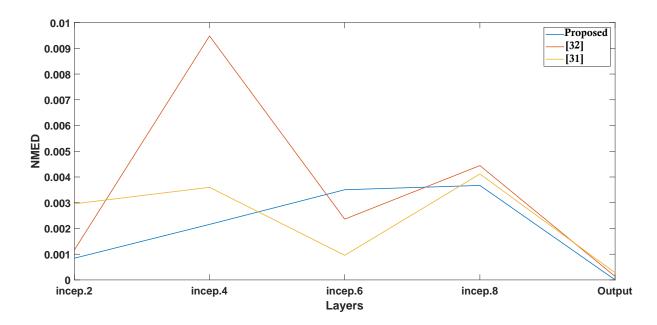

| 6.7  | The dot-diagram of an approximate signed radix-4 Booth multiplier explored in                     |    |

|      | step 1, when (a) the 5 least significant partial product columns are truncated, and               |    |

|      | (b) the partial products in the 5 least significant columns are replaced with a single            |    |

|      | inexact partial product [9]. $\blacktriangle$ : inexact compressed partial products using an $OR$ |    |

|      | reduction operation. ● : exact partial products                                                   | 93 |

| 6.8  | Output of the proposed accelerator when a picture of a Crane is fed into this                     |    |

|      | accelerator, and the introduced approximation in steps 1 and 2 are applied into the               |    |

|      | Booth multipliers                                                                                 | 94 |

| 6.9  | The gate-level architecture of the approximate partial product generator which                    |    |

|      | compresses a few partial products into a single inexact partial product using an $OR$             |    |

|      | reduction operation [9]                                                                           | 95 |

| 6.10 | The error distribution of Layer Fire 4 when (a) the partial products in the 5                     |    |

|      | least columns are compressed to a single inexact partial product using an $OR$                    |    |

|      | reduction operation, and when (b) the 5 least significant partial product are replaced            |    |

|      | with a constant logical value "1" in all the Booth multipliers. The mentioned                     |    |

|      | approximation is applied in excess of the explored approximation in step 1                        | 96 |

| 6.11 | The output of the proposed accelerator when a picture of a Crane is fed into this                 |    |

|      | accelerator, and the partial products in the 5 least columns are compressed to a                  |    |

|      | single inexact partial product using an $OR$ reduction operation in all the Booth                 |    |

|      | multipliers. The mentioned approximation is applied in excess of the explored                     |    |

|      | approximation in step 1                                                                           | 97 |

| 6.12 | The output of our proposed accelerator when a picture of a Crane is given to this                 |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | accelerator, and the partial products in the 5 least columns are replaced with a single           |     |

|      | constant logical value "1". The mentioned approximation is applied in excess of                   |     |

|      | the explored approximation in step 1                                                              | 98  |

| 6.13 | The dot-diagram of an approximate signed radix-4 Booth multiplier explored in                     |     |

|      | step 1, when (a) the 5 least significant partial product columns are replaced with a              |     |

|      | constant logical value "1", and when (b) approximate partial product generators are               |     |

|      | used in the columns 5 to 7 of the 2 least significant rows. $\blacktriangle$ : inexact compressed |     |

|      | partial products using an $OR$ reduction operation. $\blacksquare$ : inexact partial product      |     |

|      | generator by removing the multiplexers considered for shifting two adjacent partial               |     |

|      | product bits. • : exact partial products.                                                         | 98  |

| 6.14 | The error distribution of Layer Fire 4 when (a) the fixed version of the approxima-               |     |

|      | tion introduced in step 4 (A), and when (b) the dynamic version of the approxima-                 |     |

|      | tion introduced in step 4 (B) is applied to all the Booth multipliers of the proposed             |     |

|      | accelerator.                                                                                      | 102 |

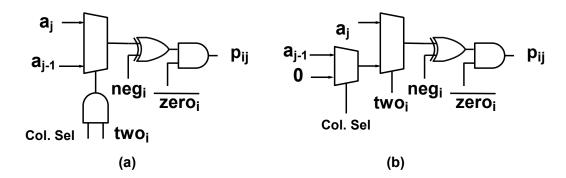

| 6.15 | The gate-level architecture of the approximate partial product generator (a) which                |     |

|      | can avoid shift operation dynamically, and (b) which can coordinate to shift a                    |     |

|      | specific logical value dynamically.                                                               | 102 |

| 6.16 | The output of the proposed accelerator, when a picture of a Crane is fed to this                  |     |

|      | accelerator, and the dynamic version of the approximation introduced in step 4 (B),               |     |

|      | is applied to all the Booth multipliers in excess of the applied approximation in the             |     |

|      | previous steps                                                                                    | 103 |

| 6.17 | The general architecture of the proposed accelerator.                                             | 105 |

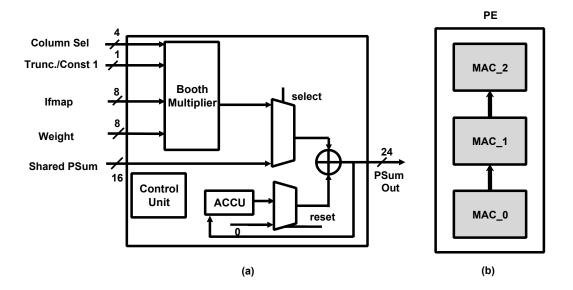

| 6.18 | The internal architecture of (a) the proposed re-configurable MAC unit that supports              |     |

|      | all the approximation methods explored in Subsection 6.1.2 dynamically, and (b)                   |     |

|      | each PE inside the computation engine.                                                            | 106 |

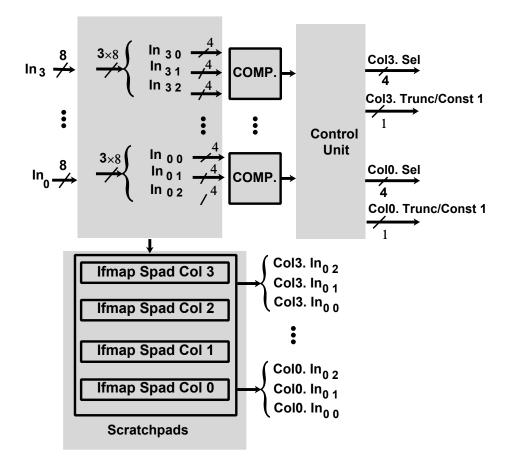

| 6.19 | The internal architecture of the ifmap distributor unit of the proposed accelerator.                                                                                                                                                                                                                                                                                            | 108 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.20 | The computed NMED of a few layers of the speech command detector network for different approximate multipliers                                                                                                                                                                                                                                                                  | 109 |

| 6.21 | The computed NMED of a few layers of SqueezeNet for different approximate multipliers.                                                                                                                                                                                                                                                                                          | 110 |

| 6.22 | The computed NMED of a few layers of GoogleNet for different approximate multipliers.                                                                                                                                                                                                                                                                                           | 110 |

| 6.23 | The dot-diagram of an approximate signed radix-4 Booth multiplier when (a) approximate partial product generators in the columns 0 to 4 of the 2 least significant rows are replaced with a constant "1" logical value, and when (b) partial product bits of the in the columns of 4 to 7 of the design shown in (a) are accumulated using OR gates. • : exact partial products | 116 |

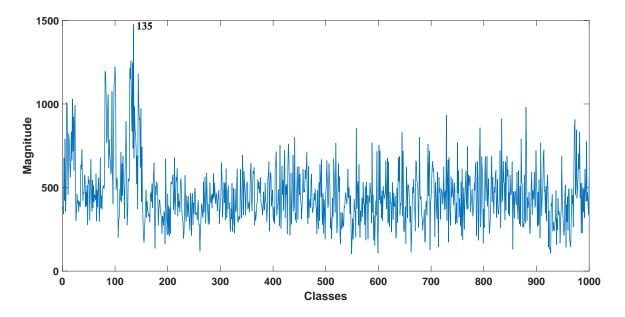

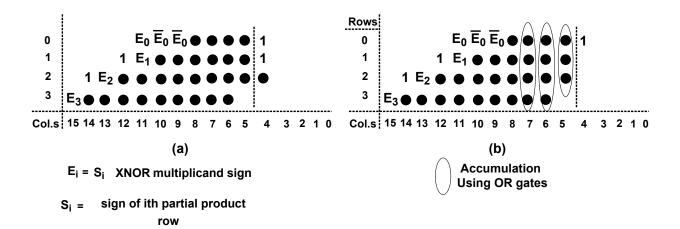

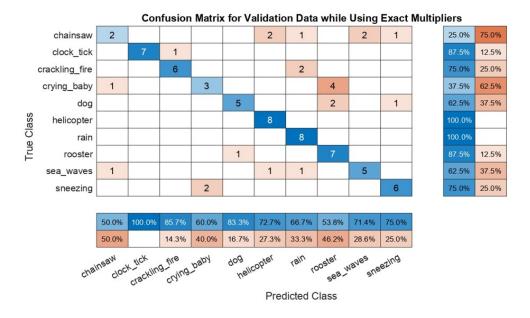

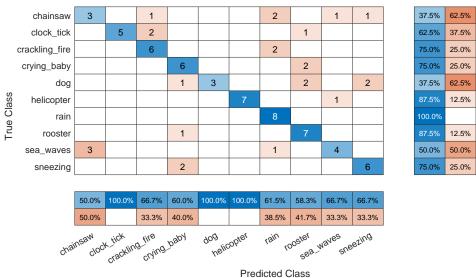

| 6.24 | The inference accuracy of the environment sound classifier computed by Matlab which uses pre-trained 32bit floating-point weights to perform the inference                                                                                                                                                                                                                      | 117 |

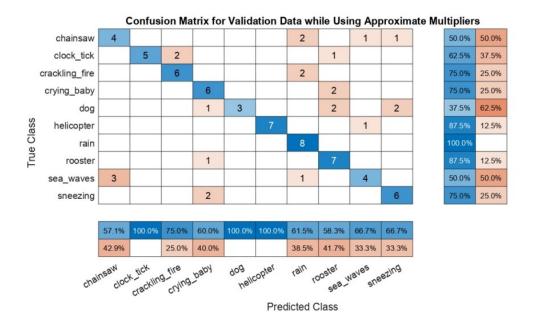

| 6.25 | The inference accuracy of the environment sound classifier when approximate 8-bit Booth multiplier shown in Figure 6.23 (a) is used to perform the inference computations                                                                                                                                                                                                       | 118 |

| 6.26 | The inference accuracy of the environment sound classifier when approximate 8-<br>bit Booth multiplier shown in Figure 6.23 (b) is used to perform the inference<br>computations                                                                                                                                                                                                | 118 |

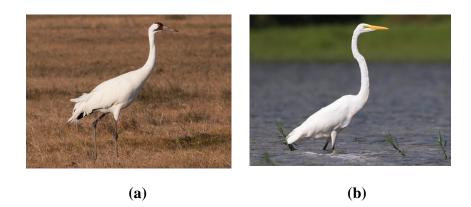

| 6.27 | The picture of (a) a Crane vs (b) an American Egret                                                                                                                                                                                                                                                                                                                             | 119 |

| 6.28 | The general architecture of the proposed accelerator.                                                                                                                                                                                                                                                                                                                           | 120 |

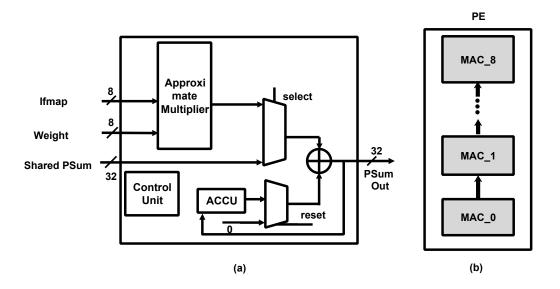

| 6.29 | The internal architecture of (a) the proposed MAC unit which includes an approx-<br>imate multiplier, and (b) each PE inside the computation engine.                                                                                                                                                                                                                            | 121 |

6.30 The internal architecture of the ifmap distributor unit of the proposed accelerator. 122

## 1. Introduction

This chapter introduces the research works proposed in this dissertation. This chapter presents the popularity of deep learning in many fields of applications. Due to the revolutionary improvements that come with Artificial Intelligence (AI) based applications that are equipped with a Deep Neural Network (DNN), optimizing hardware deep learning operations becomes necessary. This motivates the research works to be presented in this dissertation that is to design computation engines based on the requirements of the deep learning computation. Section 1.1 presents the overview of the computation complexity of DNNs. The motivation of the proposed works is presented in Section 1.2. Section 1.3 provides an overview of the research works in this dissertation. Section 1.4 presents the contributions of the proposed works. Finally, Section 1.5 lists the publications and submissions made during the course of the Ph.D. study.

#### **1.1 Overview of DNNs**

Modern Artificial Intelligence (AI) applications are equipped with DNNs that caused a revolutionary improvement in those applications. With the new advancement in the DNNs, the performance of the applications such as speech recognition [10], environment sound classification [11], object detection [12], and self-driving cars [13] is increasing as well. Although DNNs are introduced 60 years ago, it has been roughly a decade that big data are available, and processing the big data in a reasonable amount of time is possible. A big portion of the past decade was spent on increasing the accuracy and performance of DNNs. Accuracy improvement of DNNs comes with a significant computation complexity. It takes 22.6G multiply and accumulate (MAC) operations to perform one inference using ResNet-152 [14] and 46.04G MAC operations to perform one inference using VGG16 [15]. Using an Intel Core i7 CPU, it takes roughly 800 ms to perform one inference while running VGG16 [15]. The input size of VGG16 is  $224 \times 224$ . A self driving car that includes 8 (1920×1280) pixels cameras (30 frames per second), requires hardware platform to perform 8 × (46.06(*GigaMAC*) ÷ (800)) × 30 × ((1920 × 1280) ÷ (224 × 224)) = 676 Tera MAC operations per second. Using multiple DNNs enlarges the computation complexity even more.

Researchers have been required to use Graphical Processor Units (GPUs) and Central Processing Units (CPUs) platforms to develop and run DNNs at the beginning of the past decade. The price, large power consumption, and the large latency of such platforms have been a critical challenge for the deployment of the advanced DNNs into edge-devices. Accordingly, researchers have been pushed toward Application-Specific Integrated Circuits (ASICs) for hardware implementation.

Although ASIC platforms are optimized in terms of price and power consumption compared to GPU and CPUs. Many of the AI solutions are battery-dependent, which makes the implementation of DNN accelerators challenging. Advanced DNN models need large Global buffers (GBs). Accessing GBs is 6× more expensive than performing a single 16 bit MAC operation in 65nm technology [1]. in terms of energy consumption. Large DNNs even need DRAM. Accessing DRAM is 200× more expensive than performing a single 16-bit MAC operation in 65nm technology in terms of energy consumption.

#### 1.1.1 The Basics

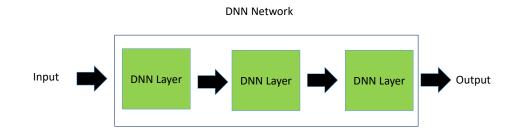

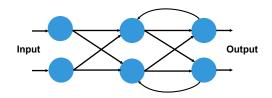

Deep learning is a subcategory of machine learning that itself is a subcategory of AI. Neural Networks (NNs) and their connection are inspired by the human brain. It turns out that adding more layers improves the accuracy of these networks significantly. Technically, the NNs that include hidden layers are called DNNs. Figure 1.1 shows the internal architecture of DNNs. In more detail, the idea of DNNs is to use many layers to hierarchically extract meaningful information from the input data. This transformation, called inference, involves multiple stages, each of which is often referred to as a layer. A DNN often has dozens to hundreds of layers.

In [16], deep learning is defined as representation learning. In other words, deep learning is the automated formation of useful representations from data. In addition, as explained in [16], at a high-level, neural networks could be encoders, decoders, or a combination of both. To give

Figure 1.1: Internal architecture of a Deep Neural Network

more detail, encoders find patterns in raw data to form compact, useful representations. However, decoders generate high-resolution data from those representations and the generated data is either new examples or descriptive knowledge.

Within AI and machine learning, there are three basic approaches. One is supervised learning, the second one is unsupervised learning and the last one is reinforcement learning. The main difference between the first two approaches is that supervised learning uses labeled data to help predict classes, while unsupervised learning does not. In what follows these approaches are in more detail.

#### What is supervised learning?

Supervised learning is a subcategory of machine learning which is defined by its use of labeled datasets. These datasets are designed to train or supervise algorithms into classifying data with high accuracy. By using labeled inputs and outputs, the developed model can measure its accuracy and learn over time.

#### Feed Forward Neural Networks (FFNNs)

A network wherein all its connections between the nodes do not form a cycle, is called a feed forward neural network. The history of these types of networks goes back to 1940s. These types of networks also count as the first and simplest type of artificial neural network proposed. These types of networks are also called deep networks, multi-layer perceptron (MLP), or simply neural networks. When input data goes down through the network, each layer processes a specific aspect of the data. Feed forward neural networks are made up of the following:

- **Input layer:** This layer consists of the neurons that receive inputs and pass them on to the other layers.

- **Output layer:** This layer is the predicted feature. Depending on the application, the output could be in continuous or discrete format.

- **Intermediate layer:** These types of layers that usually come with a vast number of neurons are referred to all the layers between input layer and the output layer.

- Neuron weights: This term refers to the amplitude of a connection between two neurons.

In what follows, some other types of networks which are modified feed forward neural networks are introduced. Accordingly, many of the fundamental concepts are identical.

#### **Convolutional Neural Networks (CNNs)**

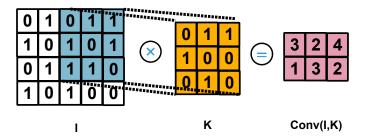

Convolutional neural networks are distinguished from other neural networks by their superior performance with image, speech, or audio signal inputs. The fundamental layer in these networks is convolutional layer. In more detail, each convolution layer convolves the input and each filter and passes the results to the next layer. One of the most common types of convolution that is used in DNNs is 2-D convolution. In a 2-D convolution, 2-D filters or kernels, slide over a 2-D input data. The 2-D input data is also called 2-D feature map. For every location of the input that each filter slides over, the summation of the element-wise multiplication of the filter weights and the input feature maps (ifmaps) will be computed. Accordingly, the output of a 2-D convolution would be a 2-D output feature which is also called output feature map. Figure 1.2 shows a simple 2-D convolution example. In this figure, I refers to a 2D input feature map and K refers to a 2D filter channel. The intermediate values generated by the many 2-D convolutions for each output activation called partial sums (psums). When the size of the filter and the input data is identical, that layer is called a fully connected layer. Fully connected layers usually are used as the last layers of advanced DNNs.

Each 2-D filter is called a channel. The same thing is true with each 2-D feature map. In practice, the number of channels of each filter and the input data is way more than one (e.g., up to

Figure 1.2: A simple 2D convolution example

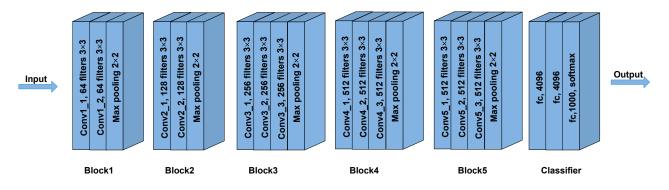

Figure 1.3: Overview of the architecture of VGG16

512 in VGG16). The overview of the architecture of VGG16 is shown in Figure 1.3. Accordingly, it is possible to show each filter and each input data as a 3D matrix. Furthermore, the number of filters of each layer is way more than one (e.g., up to 512 in VGG16). Each channel of the output feature map is the result of the convolution of each filter and its relevant channels and the input feature map and its relevant channel.

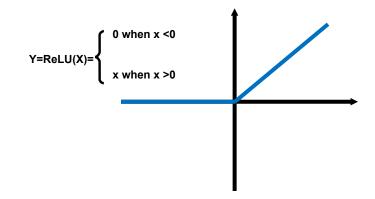

Usually, each convolution layer is followed by an activation and a pooling layer in DNNs. The activation layer also known as the activation function is considered to add non-linearity to the network. The activation functions are at the very core of Deep Learning. They determine the output of a model, its accuracy, and computational efficiency. In some cases, activation functions have a major effect on the model's ability to converge and the convergence speed while training. There are different activation functions such as Sigmond or Rectified Linear Unit (ReLU). The ReLU layer, which is very common in most well-known DNNs involves setting all the negative values to zero. The overview of this activation function is shown in Figure 1.4. A pooling layer is another building block of a CNN. Its function is to progressively reduce the spatial size of the

Figure 1.4: Overview of the ReLU activation function

Figure 1.5: A  $2 \times 2$  Max pooling example

representation to reduce the number of parameters and computation in the network.

The most common approach used in pooling is Max pooling. Figure 1.5 shows  $2 \times 2$  Max pooling using an example. As shown in this figure, a  $4 \times 4$  matrix is considered as the input. The pooling operation involves sliding a two-dimensional filter over the input matrix. Considering a stride size of 2 for the given example, there are only 4 regions that the filter runs over the input matrix. These regions are distinguished with different colors in Figure 1.5. When performing Max pooling operation for the given input, the maximum of each of the 4 distinguished regions would be selected and considered as an element of the output matrix. Therefore, for the given example, the output matrix has 4 elements.

#### A Recurrent Neural Network (RNN)

In some application such as language translation, memory is required to process the data. So the main question is that how a feed forward neural network would able to use previous information to affect later ones? A recurrent neural network (RNN) is a type of artificial neural network which uses sequential data or time-series data. The architecture of these types of networks is shown

Figure 1.6: The internal architecture of a simple Recurrent Neural Network

in Figure 1.6. As shown in Figure 1.6, there are connections with both forward and backward directions. There are more applications that this architectural paradigm is commonly used for, such as language translation, natural language processing (nlp), speech recognition, and image captioning.

#### What is unsupervised learning?

The unsupervised learning term refers to machine learning approaches that try discover hidden patterns and cluster unlabeled datasets. The data clustering, association, and dimensionality reduction are the main applications of unsupervised learning.

#### What is reinforcement learning?

Reinforcement learning algorithms define how agents should take actions in an environment in order to get rewards or maximize the number of rewards. The agent will get positive feedback for good actions and it will get a penalty for bad actions. To add more detail, reinforcement learning algorithms can make sequential decisions and learn from their experience.

#### **1.2** Motivations of Research Works

### 1.2.1 Ineffectual MAC Operations in DNNs

As mentioned in the previous sections, DNNs have enhanced the accuracy of many AI applications unprecedentedly. However, DNNs require hundreds of megabytes of storage and involve high computational complexity. There are many DNN accelerators available implemented on ASIC and field-programmable gate array (FPGA) platforms [17, 18] which are better optimized in terms of power consumption compared to GPU architectures [19].

To reduce the number of MAC operations in DNNs, [20] showed that neighboring output feature map elements tend to have similar values and leveraged this to reduce the required MAC operations by 30.4% with a 1.7% accuracy loss. Authors in [21] equipped processing units with an approximate processing mode and achieved improvements in energy efficiency of 34.11% to 51.47% with an accuracy drop of 5%. In [22], an accelerator is proposed which performs early detection of negative output features via the use of the inverse two's complement format of the filter elements. The design presented in [22] reduces the number of required MAC operations, however, the proposed approach comes with several weak points. For example, by using the proposed architecture in [22], the speedup decreases for the high depth layers since these layers come with more channels. In more detail, in the proposed method in [22], the computations start only when all the relevant input feature maps and filter elements are loaded into the PEs. Furthermore, no results were included in [22] in regards to the first fully connected layer of the benchmark network since it is not possible to map this layer into the proposed accelerator.

#### **1.2.2** Divergence of the Workloads in Spatial Designs

Designing an efficient computation engine enhances the performance of these platforms while running DNNs. Energy-efficient DNN accelerators use skipping sparsity and early negative output feature detection to prune the computations. Authors in [23] introduced NoC-based DNN accelerator. They showed that efficient PE and NoC designs are both critically important to keep the system performance high in the NoC-based DNN accelerators. Compared with the conventional DNN accelerators, the number of memory accesses in NoC-based design is reduced by 88% up to

99%.

Eyeriss V2 [24] is a state-of-the-art energy-efficient DNN accelerator that exploits a flexible NoC which provides the required bandwidth of the computation engine while running various DNNs. With the use of the proposed NoC types in [23] and [24] and data reuse techniques, it is possible to decrease the NoC based stalls in sparse DNNs. However, these accelerators perform non-effectual computations for negative outputs. Furthermore, even by providing such NoC for the PEs, applying computation-pruning techniques still causes stalls inside spatial designs. Spatial DNN accelerators in principle can support computation-pruning techniques compared to other common architectures such as systolic arrays. These accelerators need a separate data distribution fabric like buses or trees with support for high bandwidth to run the mentioned techniques efficiently and avoid Network on Chip (NoC) based stalls. Spatial designs suffer from divergence and unequal work distribution. Therefore, applying computation-pruning techniques into a spatial design, which is even equipped with an NoC that supports high bandwidth for the PEs, still causes stalls inside the computation engine.

#### **1.2.3** Skipping Identical Bit-wise Computations

Some efficient DNN accelerators apply techniques that target sparsity. Zero computations are considered as ineffectual MAC operations which can be safely eliminated, saving energy and/or storage and communication [1, 25, 26]. In [27], the authors presented a method for transparently identifying ineffectual computations during inference with deep learning models. Specifically, by decomposing multiplications down to the bit level. This work targets bit sparsity, that is zero bits since processing zero bits in a MAC operation does not affect the outcome. As shown in [27], the number of multiplications during inference can be potentially reduced by at least 40× across a wide selection of neural networks. Furthermore, the authors in [27] proposed a novel PE that is 5× smaller and much more energy-efficient than the most competitive works [3]. The proposed architecture in [28] only skips computation cycles for zero-valued weights and the proposed architecture in [29] only skips computation cycles for zero-valued ifmaps. However, in these types of accelerators, the focus is on skipping the ineffectual computations [30, 31].

### 1.2.4 Applying Approximation into DNNs

One of the promising solutions to perform inference of DNNs efficiently is utilizing approximate multipliers inside the computation engine of DNN accelerators [32]. The previous researches have reported that DNNs are resilient against small arithmetic errors [33]. Authors in [32] showed that one of the promising solutions to perform inference of DNNs efficiently is utilizing approximate multipliers inside the computation engine of DNN accelerators. In [34], authors have introduced approximate multipliers based on alphabet-set multiplication. In more detail, the weights are divided into parts, having 4 bits. Multiplication by each 4-bit part of the weight is implemented by shifting a pre-computed input value and followed by summation.

#### **1.3** Overview of Research Works

In this dissertation, based on the computation characteristics discussed in Section 1.2, several computation engines optimized for deep learning computation are proposed. We provide the solutions both to optimize the state-of-the-art accelerators for deep learning computation and to design deep learning specific computation units. The computation engines proposed in this dissertation support running different DNN architectures out there. This is different from the design of an architecture that is optimized for a specific model or operation. Therefore, the proposed computation engines are more useful in both ASIC and FPGA based processor designs that are used in servers and datacenters. The whole dissertation is composed of seven chapters explained as follows:

**Chapter 1 Introduction:** covers the basics of different architectural paradigms of machine learning approaches and then describes the motivation behind the research presented in this dissertation, the contributions provided in this dissertation, the publications made during over the course of the Ph.D. study, and the organization of this dissertation.

**Chapter 2 Review of Contemporary DNN Accelerators:** provides a review of contemporary works in the literature which features a broad range of architectures. The efficient architectures reviewed include efficient data-flow, pruning, quantization, skipping sparsity, near memory computation, and approximate MAC units.

**Chapter 3 Early Detection of Negative Output Features:** introduces a novel architecture for reordering the computations in the computation engines. Among the previously proposed architectures that tried to reduce the number of MAC operations while performing inference of DNNs, some come with accuracy loss, which is not always acceptable. In more detail, in some applications such as safety-critical applications, the accuracy loss beyond a certain threshold, while performing inference of DNNs is not acceptable [35]. Some other works maintain the accuracy. However, their considered dataflow is designed poorly that can not coordinate to run all the DNN layers efficiently such as high depth layers [22]. In addition, some other proposed algorithms recommend reordering the computations using indexes, without considering the extra high-level memory access needed for loading those indexes from DRAM, and also the extra needed storage for

keeping those indexes inside the computation engine. Therefore, although efficient early detection of output features come with benefits like less number of MAC operations and less number of accesses to memory, but still there are some challenges that need to be resolved to equip DNN accelerators out there with the discussed technique.

**Chapter 4 Enhancing the Utilization of PEs in Spatial DNN Accelerators** focuses on increasing the utilization of PEs in spatial computation engines. In a spatial architecture, the PEs that perform their tasks earlier have a slack time compared to others. Spatial DNN accelerators come with an array of PEs that are considered for performing the MAC operations of DNNs. Therefore, due to the divergence of workloads, each specific PE might finish its task sooner or later than other PEs. In other words, the PEs that finish their given task earlier have a slack time. However, to avoid designing a complex control unit and also utilizing the chance of local data reuse while distributing the ifmaps and filter weights among the PEs, the main control unit waits until all the PEs are done with their given tasks, then loads the PEs with new tasks. Accordingly, there is a need to assess the conventional architectures out there to evaluate the chance of using the available slack times inside the spatial computation engines to balance the divergence of the workload inside the whole computation engine.

Chapter 5 Pruning the Effectual Computations in DNNs: optimizes the available bit-level computation engines. Although skipping sparsity bit-wise and word-wise comes with both energy efficiency and speedup while running different layers of DNNs especially high depth layers. There is still room to skip effectual identical computations while decomposing the ifmaps and filter weights down to bit-level. In more detail, as authors in [20] showed, neighboring output feature map elements tend to have similar values. In addition, the wights of each layer have a Gaussian distribution around zero. To add more information, there is a high chance that the high significant bits in close values to be identical.

**Chapter 6 Efficient Approximate DNN Accelerators for Edge Device:** explores applying approximation into the computation engine of DNN accelerators. There are many approximate multipliers proposed for various applications until now. However, the function of only a few of these approximate designs has been explored while performing inference of DNNs. Furthermore, little attention has been given to applying various approximation techniques to different layers

of DNNs. Lastly, for most of the current approximate neural network implementation, single approximate arithmetic is used for the whole model process. However, a single type of approximate arithmetic unit may not be an optimal solution for DNNs.

Chapter 7 Conclusions and Future Work: provides a summary of this dissertation and discusses potential future works.

# **1.4** Contributions of This Dissertation

By considering all the requirements mentioned in Section 1.2, efficient DNN accelerator architectures are proposed in this dissertation. In what follows, the contributions of the proposed accelerators are provided in this dissertation:

- An area-efficient architecture for the early detection of negative output features in hardware while maintaining the accuracy of DNNs is proposed.

- A novel dataflow is introduced that can map various fully connected and convolutional layers and keeps the computation engine busy with effectual computations while reordering the computations.

- A novel real-time architecture for the spatial DNN accelerators which uses the slack time caused by computation-pruning techniques and the used NoC format is developed and explored.

- A novel real-time architecture for spatial DNN accelerators is proposed which not only skips the ineffectual computations but also it prunes the effectual computations during inference while maintaining the accuracy.

- A novel dataflow is proposed for the layers with a limited chance of reuse of the ifmaps and filter weights such as fully connected and depth-wise convolutional layers.

- A detailed step-wise approach for designing a re-configurable approximate Booth multiplier is proposed. Accordingly, it is possible to re-configure the multiplier dynamically at run-time.

- The effect of applying various degrees of approximation to different layers of DNNs is evaluated.

# 1.5 Publications During Ph.D. Research

# **1.5.1** Published Journal Papers

M. Asadikouhanjani and S. -B. Ko, "A Novel Architecture for Early Detection of Negative Output Features in Deep Neural Network Accelerators," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 12, pp. 3332-3336, Dec. 2020, doi: 10.1109/TC-SII.2020.2977015.

A major portion of this paper is included in Chapter 3 : Early Detection of Negative Output Features.

M. Asadikouhanjani and S. -B. Ko, "Enhancing the Utilization of Processing Elements in Spatial Deep Neural Network Accelerators," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 40, no. 9, pp. 1947-1951, Sept. 2021, doi: 10.1109/TCAD.2020.3031240.

A major portion of this paper is included in Chapter 4: Enhancing the Utilization of PEs in Spatial DNN Accelerators.

M. Asadikouhanjani, H. Zhang, L. Gopalakrishnan, H.-J. Lee and S.-B. Ko, "A Real-Time Architecture for Pruning the Effectual Computations in Deep Neural Networks," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 5, pp. 2030-2041, May 2021, doi: 10.1109/TCSI.2021.3060945.

A major portion of this paper is included in Chapter 5 : Pruning the Effectual Computations in DNNs.

# **1.5.2** Other publications

• **M. Asadikouhanjani**, H. Zhang, and S.-B. Ko, "Efficient Approximate DNN Accelerators for Edge Devices: An Experimental Study," Submitted as a book chapter to Springer (to appear by August 30th, 2022).

A major portion of this paper is included in Chapter 6: Efficient Approximate DNN Accelerators for Edge Device

# **1.5.3** Other publications not included in this dissertation

• H. Zhang, **M. Asadikouhanjani**, and S.-B. Ko, "Approximate Computing for Efficient Neural Network Computation: A Survey," Submitted as a book chapter to Springer (to appear by August 30th, 2022).

# 2. Review of Contemporary DNN Accelerators

Section 2.1 introduces and compares spatial and temporal architectures. Section 2.2 introduces contemporary state-of-the-art DNN architectures out there.

#### **2.1** Spatial Designs vs Temporal Designs

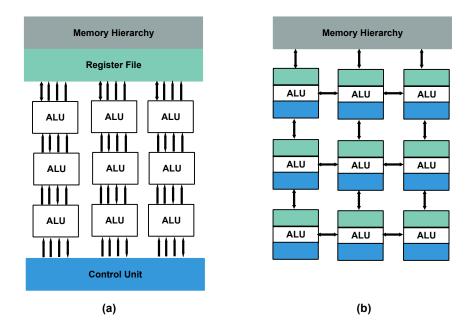

There are different categories considered for classifying the proposed DNN accelerators until now. One classification is in terms of general architecture considered for designing the computation engine of DNN accelerators. In more detail, depending on whether the internal architecture of PEs inside the computation engine contains a specific local control unit and register file or not, it is possible to classify a DNN accelerator as a spatial or temporal architecture. The overview of these architectures is shown in Figure 2.1.

In spatial designs, each Processing Element (PE) has its own control unit and register files. However, a temporal architecture includes one shared large register file and one shared control unit. Spatial architectures are efficient since smaller register files inside the PEs come with less static power consumption and shorter data travel path. However, the internal architecture of each PE is more complex since they have their own control unit. The control unit in each PE coordinates performing the computations in each PE and interactions with neighbor PEs. In more detail, spatial designs are a class of accelerators that can exploit high compute parallelism using communication between an array of relatively simple PEs. This type of architecture is suitable for implementing different dataflows such as reordering the computations, skipping sparsity, and various formats of data distribution among the PEs. Eyeriss [1] is a state-of-the-art energy-efficient DNN accelerator that exploits local reuse of filter weights and ifmaps to lessen memory accesses. Eyeriss [1] counts as a spatial DNN accelerator. There are also other accelerators that belong to this category [36,37].

Figure 2.1: Overview of (a) temporal architecture vs (b) spatial architectures [1].

Temporal designs, also called Single Instruction Multiple Data (SIMD) architectures are another common architecture proposed for DNN accelerators. In temporal architectures, all the PEs share a control unit and a register file. One of the common temporal-based architecture is systolic array [38]. Systolic arrays are 2-D grids of homogeneous PEs that perform only nearest-neighbor communication, thus obviating the overhead for input buffering and complex routing. One of the advantages of this type of architecture is that the computation engine implementation is easier compared to spatial design. Google's Tensor Processing Unit (TPU) DNN accelerator belongs to this category [39].

# 2.2 DNN Accelerators

Regardless of the two main architectures explained in Section 2.1, there are other ways to classify contemporary DNN accelerators. For example, it is possible to classify them based on the considered techniques to improve the energy efficiency of the DNN accelerators while performing the MAC operations. Such techniques fairly fall into at least five categories depending on the property they target: dataflow, near-memory computing, pruning, data types and quantization, and approximate computing. the dataflow category itself includes a broad range of techniques such as

Figure 2.2: Row stationary dataflow [1]

skipping sparsity, re-configurable quantization, local data reuse. In what follows we explore some of the state-of-the-art accelerators.

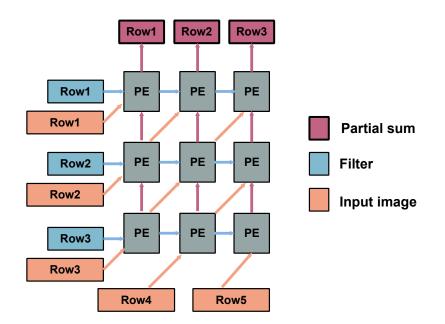

Eyeriss [1] introduced row stationary dataflow which increases throughput and comes with energy efficiency. It works on both convolutional and fully-connected layers, and optimizes all types of data movement in the storage hierarchy. The overview of this dataflow is shown in Figure 2.2. As shown in Figure 2.2, input feature maps are shared diagonally, filter weights are shared horizontally and partial sums are shared vertically. In other words, all data types are reused locally. In more detail, authors in [1] showed that row stationary dataflow is more efficient compared to when only one data type is reused locally inside the computation engine. Furthermore, along with a highly flexible NoC that can adapt to a wide range of bandwidth requirements while still being able to exploit available data reuse, they can efficiently support a wide range of layer shapes to maximize the number of active PEs and keep the PEs busy for high performance. The authors in [40,41], exploit local data reuse to reduce the energy needed by data movement [40,41].

TPU [39] is an Artificial Intelligence (AI) accelerator developed by Google specifically for neural network machine learning, particularly using Google's own TensorFlow software. To add more detail, a systolic array architecture is implemented, enabling data transfer between processing

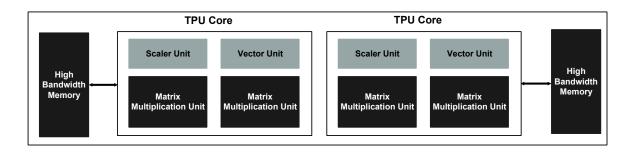

Figure 2.3: The general architecture of TPU V3 [2]

elements and thus reducing the requirement of external memory bandwidth. A single TPU [39] device contains 4 chips, each of which contains 2 TPU cores. A TPU core contains one or more Matrix Multiply Units (MXU), a Vector Processing Unit (VPU), and a Scalar Unit. The MXU is composed of 128 x 128 MACs in a systolic array. The MXUs provide the bulk of the compute power in a TPU chip. Each MXU is capable of performing 16K multiply-accumulate operations in each cycle using the bfloat16 number format. The VPU is used for general computation such as activations, softmax, and so on. The scalar unit is used for control flow, calculating memory address, and other maintenance operations. The new TPU V4 infrastructure is the fastest system ever deployed at Google. The general architecture of TPU V3 is shown in Figure 2.3.