Dalibor Barri, *member, IEEE* Department of Microelectronics STMicroelectronics Prague, Czech Republic dalibor.barri@st.com

Miloš Vacula Department of Microelectronics STMicroelectronics Prague, Czech Republic milos.vacula@st.com Patrik Vacula Department of Microelectronics STMicroelectronics Prague, Czech Republic patrik.vacula@st.com

Jiří Jakovenko Department of Microelectronics Czech Technical University, FEE, Prague, Czech Republic jakovenk@fel.cvut.cz Vlastimil Kotě Department of Microelectronics STMicroelectronics Prague, Czech Republic vlastimil.kote@st.com

Jan Voves, *senior member*, *IEEE* Department of Microelectronics Czech Technical University, FEE, Prague, Czech Republic voves@fel.cvut.cz

Abstract—This paper presents an interesting phenomenon related to the effective threshold voltage changes ( $\delta V_{\text{th,eff}}$ ) in the diamond layout shape MOS transistors (DLS MOSFETs). Besides it, its analytical expression is presented here for the first time. The analytical approximative expression has been defined based on the results of the 3-D TCAD simulations for the different effective aspect ratio  $(W/L)_{eff}$  and different angle  $\alpha$  of DLS MOSFET. The effective aspect ratio has been set to 2.0, 1.5, 1.0, 0.5 with the angle α varied from 180° to 80° with the step 20°. Furthermore, for purpose to verify the 3-D TCAD simulation results and measurement results, 1 124 samples were fabricated, which were proportionally divided into rectangle layout shape (RLS) MOSFETs and DLS MOSFETs with the angles  $\alpha$  equal to 120°, 100°, and 80°. All the samples have been fabricated in the 160 nm BCD technology process. The mentioned phenomenon described by the proposed expression fits the measured data with a very high level of accuracy equal to 99.995 %. Thus, the presented analytical expression proves its quality. Thanks to the high level of the expression quality, the given expression is recommended to use for the analog designs with high-level precision requests and DLS MOSFET components.

*Keywords*—BCD Technology, Diamond Layout Shape MOS Transistor, Effective Threshold Voltage, Rectangular Layout Shape MOS Transistor

# I. INTRODUCTION

THRESHOLD voltage  $(V_{th})$  of the Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) [1], is a crucial electrical parameter, which defines the MOSFET turn on voltage and influence the transfer between the linear and saturation region [2]. Therefore, the threshold voltage plays a key role in the semiconductor industry, and any unpredictable behavior or its high sensitivity causes problems

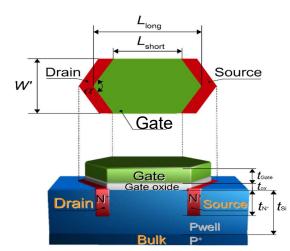

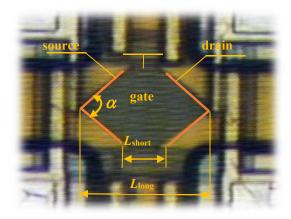

Fig. 1. A 2-D and 3-D top-view of the general N channel MOSFET structure with the Diamond Layout Shape [4]

during front-end analog design [3]. Such as, in the case of the high-precise voltage references [5]. These unpredictable behaviors and  $V_{\text{th}}$  high sensitivities are present, for example, in the case of a hump effect [6], TID effect [7], etc., but also in the case of the DLS MOSFET (Fig. 1), which is the subject of this article. The unpredictable behavior of DLS MOSFET has not been described yet, and therefore this article focuses on it.

Generally, the  $V_{\text{th}}$  is the value of the MOSFET gate-source voltage  $V_{\text{GS}}$  that will cause the interface potential to be equal in magnitude and opposite in sign to the substrate potential  $\Phi_{\text{p}}$  [8]. Physically, for the N-channel MOSFET, it means that there would now be a concentration of mobile electrons at the surface equal in magnitude to a concentration of mobile holes in the P-substrate.

In common, the threshold voltage equals to the sum of the flatband voltage  $V_{\rm FB}$ , twice the bulk potential  $\Phi_{\rm p}$  and the voltage across the oxide [9], such it is described in [10] by the following expression:

$$V_{\rm th} = V_{\rm FB} + \gamma \sqrt{2(-\phi_{\rm p})} - 2\phi_{\rm p} \tag{1}$$

where the  $V_{\rm FB}$  is the flatband voltage, the  $\Phi_{\rm p}$  is a workfunction of a substrate, and the  $\gamma$  is a body effect. After a routine operation, we will get the following expression with basic technology parameters:

$$V_{\rm th} = \frac{T \log\left(\frac{N_{\rm A}}{n_{\rm i}}\right) k_{\rm B}}{q} - \frac{T \log\left(\frac{N_{\rm D}}{n_{\rm i}}\right) k_{\rm B}}{q} + \frac{2\sqrt{\frac{T \log\left(\frac{N_{\rm A}}{n_{\rm i}}\right) k_{\rm B}}{q}} t_{\rm ox} \sqrt{q N_{\rm A} \varepsilon_{\rm Si}}}{\varepsilon_{\rm ox}}$$

(2)

where the *T* is the temperature,  $k_{\rm B}$  is the Boltzmann constant ( $k_{\rm B} = 1.38 \cdot 10^{23}$  J K<sup>-1</sup>), and *q* is the magnitude of the electron charge ( $q = 1.602 \cdot 10^{-19}$  C).  $N_{\rm A}$  is the net ionized acceptor density,  $N_{\rm D}$  is the donor impurity density in silicon, and  $n_{\rm i}$  is the intrinsic doping concentration of silicon ( $n_{\rm i} = 1.45 \cdot 10^{10}$  cm<sup>-3</sup> at T = 300 K).  $\varepsilon_{\rm Si}$  is the permittivity of silicon, and  $\varepsilon_{\rm ox}$  is the permittivity of oxide.

As we can see, the final expression (2) does not consider the geometry settings of the MOSFETs. In the case of DLS MOSFETs, it could be a problem in terms of circuits accuracy. For this reason, we present an innovative expression of the changes in the effective threshold voltage based on simulation data, which are compared with measured data with excellent results.

In this work, the sub-threshold drain current method [11] has been used to extract the effective threshold voltage. This method is a function of gate-source voltage below the threshold voltage and plotted as  $\log(I_{DS})$  versus  $V_{GS}$  [12]. All measurements have been adjusted for the four-points measurement approach [13]. The measurements have been performed in the linear region with drain voltage set to 0.05 V and with the gate voltage step size of 10 mV.

#### II. EXPERIMENTAL RESULTS AND DISCUSSION

### A. Simulated Structures

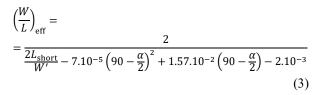

In this research, the gate areas of MOSFETs have been set to  $A = 10 \,\mu\text{m}^2$  with effective aspect ratios (*W/L*)<sub>eff</sub> varied from 0.5 to 2.0 with a step equal to 0.5. The DLS MOSFET's effective aspect ratio is described in [14] by the following expression:

where an angle  $\alpha$  is in degrees and is accurate to within 1 percent provided  $2L_{\text{short}}/W' > 1.4$ . A  $L_{\text{short}}$  is a shorter parallel

#### 978-1-6654-9482-3/22/\$31.00 ©2022 IEEE

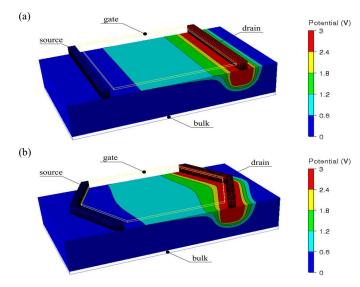

Fig. 2: Potential examples of the RLS, and DLS MOS transistor structures: (a) RLS MOSFET (b) DLS MOSFET [18]

side of the trapezoid, and a W' is a geometrical width of the trapezoid.

The technological parameters of the DLS MOSFET (Fig. 1) have been set as follows, a gate polysilicon thickness  $t_{\text{gate}}$  is equal to 0.2 µm, a gate oxide thickness  $t_{\text{ox}}$  is equal to 8.5 nm, drain/source thicknesses  $t_{\text{N+}}$  is equal to 0.4 µm, and a silicon thickness  $t_{\text{si}}$  has been set to 1.0 µm. A Pwell and N<sup>+</sup> drain/source doping concentrations have been set to  $1 \cdot 10^{16} \text{ cm}^{-3}$  and  $1 \cdot 10^{20} \text{ cm}^{-3}$ , respectively.

The Atlas, 3-D TCAD device simulation tool [15] from Silvaco company, has been used to realize and simulate the DLS MOSFETs considering the same effective aspect ratio  $(W/L)_{eff}$  with the same gate area A for any angle  $\alpha$ . The 3-D numerical simulations were run with a lateral electric fielddependent model, a concentration-dependent mobility model, Selberherr impact ionization model, and Shockley-Read-Hall model for generation-recombination processes [16]. In the TCAD simulations, the mesh grid has a direct effect on the accuracy and time of simulations. To find the proper grid is essential, and it has been considered for our simulations. In section III, the correct setting of the grid has also been proved by measurements.

Tab. 1: The simulated effective threshold voltage changes ( $\delta V_{\text{th,eff,TCAD}}$ ) of DLS MOSFETs for different effective aspect ratios (W/L)<sub>eff</sub>

|     |                                 | 1                               | ( ) ( )                         |                                 |

|-----|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| α   | $\delta V_{\text{th,eff,TCAD}}$ | $\delta V_{\text{th,eff,TCAD}}$ | $\delta V_{\text{th,eff,TCAD}}$ | $\delta V_{\text{th,eff,TCAD}}$ |

|     | $(W/L)_{\rm eff} = 2.0$         | $(W/L)_{\rm eff} = 1.5$         | $(W/L)_{\rm eff} = 1.0$         | $(W/L)_{\rm eff} = 0.5$         |

| (°) | (%)                             | (%)                             | (%)                             | (%)                             |

| 180 | 0.00                            | 0.00                            | 0.00                            | 0.00                            |

| 160 | -0.11                           | -0.07                           | 0.01                            | -0.03                           |

| 140 | -0.30                           | -0.17                           | -0.04                           | -0.07                           |

| 120 | -0.63                           | -0.33                           | -0.13                           | -0.10                           |

| 100 | -1.16                           | -0.59                           | -0.23                           | -0.15                           |

| 80  | -1.92                           | -0.92                           | -0.39                           | -0.19                           |

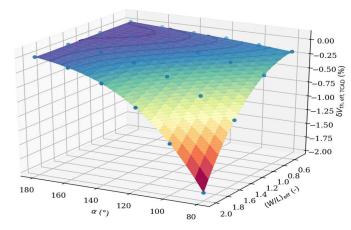

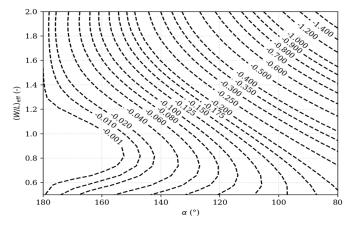

Fig. 3: Comparison of the effective threshold voltage decreasing for DLS MOSFETs with the different effective aspect ratio  $(W/L)_{eff}$

The examples of the simulated structures are depicted in Fig. 2., and all their inputs and outputs data are shown in Tab. 1 and illustrated in Fig. 3.

The Tab. 1 presents simulated changes in the effective threshold voltage ( $\delta V_{\text{th,eff,TCAD}}$ ) calculated by the following expression:

$$\delta V_{\text{th,eff,TCAD}} = \left(\frac{V_{\text{th,eff,TCAD,DLS}} - V_{\text{th,TCAD,RLS}}}{\cdot 100}\right)$$

(4)

where  $V_{\text{th},\text{TCAD},\text{RLS}}$  is a threshold voltage of conventional rectangular layout shape MOSFET, and the  $V_{\text{th},\text{eff},\text{TCAD},\text{DLS}}$  is an effective threshold voltage of DLS MOSFETs.

The Fig. 3 illustrates the comparison of the changes in the effective threshold voltage for RLS and DLS MOSFET devices. It has been studied at different effective aspect ratios  $(W/L)_{eff}$  equal to 2.0, 1.5, 1.0, and 0.5. As we can see, the simulated effective threshold voltage  $(V_{th,eff,TCAD})$  decreases if the angle  $\alpha$  of the DLS MOSFETs decreases, too. And moreover, if the effective aspect ratio  $(W/L)_{eff}$  increases, the  $V_{th,eff,TCAD}$  decreases more significantly. It is an interesting point that can be useful for the effective threshold voltage trimming of MOSFET devices in integrated circuits (ICs).

$$\begin{split} \delta V_{\text{th,eff,approx}} &= -1.349 + \alpha \, 7.57 \cdot 10^{-2} + \left(\frac{W}{L}\right)_{\text{eff}} 5.244 \\ &- \alpha \left(\frac{W}{L}\right)_{\text{eff}} 0.387 - \alpha^2 1.62 \cdot 10^{-3} + \alpha^2 \left(\frac{W}{L}\right)_{\text{eff}} 9.2 \cdot 10^{-3} \\ &- \alpha^2 \left(\frac{W}{L}\right)_{\text{eff}}^2 1.39 \cdot 10^{-2} - \left(\frac{W}{L}\right)_{\text{eff}}^2 7.09 + \alpha \left(\frac{W}{L}\right)_{\text{eff}}^2 0.554 \\ &+ \left(\alpha^3 1.052 - \alpha^3 \left(\frac{W}{L}\right)_{\text{eff}} 6.152 + \alpha^3 \left(\frac{W}{L}\right)_{\text{eff}}^2 9.573\right) \cdot 10^{-5} \\ &- \alpha^3 \left(\frac{W}{L}\right)_{\text{eff}}^3 3.614 \cdot 10^{-5} - \left(\frac{W}{L}\right)_{\text{eff}}^3 5.232 \\ &+ \alpha \left(\frac{W}{L}\right)_{\text{eff}}^3 6.702 \cdot 10^{-3} + \alpha^2 \left(\frac{W}{L}\right)_{\text{eff}}^3 3.832 \cdot 10^{-3} \end{split}$$

In the case of trimming effective threshold voltage, there is important to know how much the  $V_{\text{th,eff}}$  will be changed. Therefore, in this article, we have simulated  $V_{\text{th,eff}}$  variation  $\delta V_{\text{th,eff,TCAD}}$  (Fig. 3), which has been approximated by the third

Fig. 4: Contour plot of effective threshold voltage variation ( $\delta V_{\text{th,eff,approx}}$ ) as a function of angle  $\alpha$  and effective aspect ratio (W/L)<sub>eff</sub>

order polynomial fitting function (5). It describes the decreases of the effective threshold voltage as a function of angle  $\alpha$  and effective aspect ratio  $(W/L)_{eff}$ . This trend is valid independently on MOSFET physical characteristics such as a gate material, a gate oxide thickness, and so on, because it defines just a variation of the effective threshold voltage of DLS relative to RLS. In case of needs, an absolute value of the DLS MOSFET effective  $V_{\rm th}$  can be derived from (4), where  $V_{\text{th},\text{TCAD},\text{RLS}}$  is close to  $V_{\text{th}}$  ( $V_{\text{th},\text{TCAD},\text{RLS}} \cong V_{\text{th}}$ ) defined by the analytical expression (2). It could be also important in analog design with DLS MOSFETs [17]. The final expression fits the simulated data with excellent results, where RMSE parameter is equal to 0.00307, and R-squared parameter is equal to 0.99995. The innovative expression (5) is illustrated in Fig. 3 as a 3-D surface plot and its contour plot is illustrated in Fig. 4.

# B. Measured Structures

The measured test structures for this study are N-channel DLS MOSFET devices with 1.8V operating voltages fabricated in a 160 nm BCD technology process [18] with a triple well isolation [19]. A 2-D top-view and 3-D front-view of the general N-channel DLS MOSFET is depicted in Fig. 1, and an example of the measured sample is depicted in Fig. 5.

Fig. 5. Photography of the DLS NMOS transistor with the angle  $\alpha = 100^{\circ}$  [5]

#### 978-1-6654-9482-3/22/\$31.00 ©2022 IEEE

For this study, 1 124 samples were fabricated, which were proportionally divided into four different structures

. The first structures are reference conventional rectangular layout shape (RLS) MOS transistors ( $\alpha$ =180°) and the other structures are DLS MOS transistors with the angles  $\alpha$  equal to 120°, 100°, and 80°. All the fabricated devices have a similar area equal to 500 µm<sup>2</sup>, and effective aspect ratio (*W/L*)<sub>eff</sub> equal to 2.004 ( $\alpha$ =180°; RLS MOSFET), 1.892 ( $\alpha$ =120°), 1.834 ( $\alpha$

Tab. 2: The measured effective threshold voltage changes ( $\delta V_{\text{th,eff,meas}}$ ) of DLS MOSFETs for different effective aspect ratios (*W/L*)

| α   | W'    | L <sub>short</sub> | $L_{\text{long}}$ | А                  | $\delta V_{\text{th,eff,meas}}$ $(W/L)_{\text{eff}} = 2.0$ |

|-----|-------|--------------------|-------------------|--------------------|------------------------------------------------------------|

| (°) | (µm)  | (µm)               | (µm)              | (µm <sup>2</sup> ) | (%)                                                        |

| 180 | 31.62 | 15.81              | 15.81             | 500                | 0.00                                                       |

| 120 | 28.24 | 9.28               | 25.24             | 487                | -0.63                                                      |

| 100 | 26.34 | 7.68               | 29.28             | 487                | -1.16                                                      |

| 80  | 23.94 | 6.42               | 34.22             | 486                | -1.94                                                      |

= 100°), and 1.758 ( $\alpha$  = 80°). The

presents measured threshold voltage changes ( $\delta V_{\text{th,eff,meas}}$ ) calculated by the following expression:

$$\delta V_{\text{th,eff,meas}} = \left(\frac{V_{\text{th,eff,meas,DLS}} - V_{\text{th,meas,RLS}}}{V_{\text{th,meas,RLS}}}\right) \cdot 100 \quad (6)$$

where  $V_{\text{th,meas,RLS}}$  is a measured threshold voltage of conventional RLS MOSFET, and  $V_{\text{th,eff,meas,DLS}}$  is a measured effective threshold voltage of DLS MOSFETs. Both  $V_{\text{th,meas,RLS}}$ , and  $V_{\text{th,eff,meas,DLS}}$  have been measured by subthreshold drain current extraction method [11]. This method is a common practice reference method for a long time, and it has been sequentially applied on RLS MOSFETs ( $\alpha = 180^\circ$ ), and DLS MOSFETs with angle  $\alpha$  equal to 120°, 100°, and 80°.

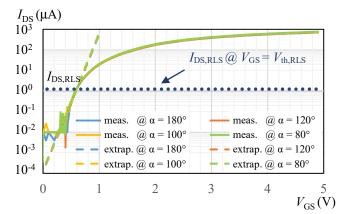

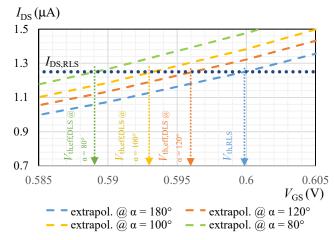

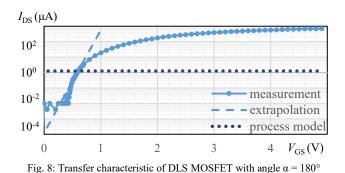

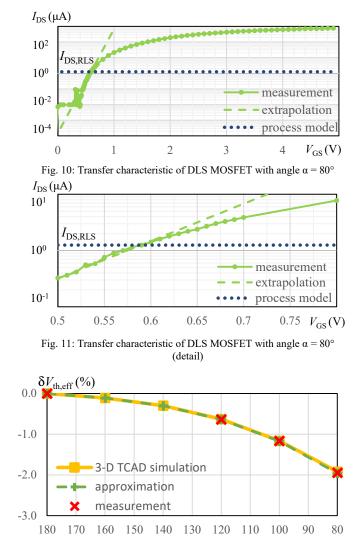

All the measured data of the experimental devices and their details are depicted in plots, Fig. 6 and Fig. 7, respectively. The Fig. 6 and Fig. 7 illustrate the measured data (solid lines), the sub-threshold drain current extraction data (dashed lines), and the constant drain-source current level I<sub>DS,RLS</sub> (dot line). The extracted threshold voltage of the RLS MOSFET ( $V_{\text{th,RLS}}$ ) defines I<sub>DS,RLS</sub>. Both, the extracted values are in accordance with the technological process data, and thus they confirm the correctness of the method used. To maintain the same  $I_{DS,RLS}$ level also for DLS MOSFETs, the lower gate-source voltage level, i.e.  $V_{\text{th,eff,DLS}}$  is required. If the angle  $\alpha$  of DLS MOSFETs decreases, the effective threshold voltage decreases, too. This means that in order to achieve the same drain-source current level for both RLS and DLS MOSFETs, the required effective threshold voltage is lower for DLS MOSFETs than for RLS MOSFETs.

The examples of measured data and post-processed results are independently depicted in Fig. 8 - Fig. 11. There are shown transfer characteristics and detail of the transfer

Fig. 6: Transfer characteristics of DLS MOSFETs with angle  $\alpha = 180^{\circ}$  (blue),  $120^{\circ}$  (brown),  $100^{\circ}$  (orange), and  $80^{\circ}$  (green)

Fig. 7: Transfer characteristics of DLS MOSFETs with angle  $\alpha = 180^{\circ}$  (blue),  $120^{\circ}$  (brown),  $100^{\circ}$  (orange), and  $100^{\circ}$  (green) – in details

characteristics for the RLS MOSFET and DLS MOSFET with angle  $\alpha$  equal to 80°.

## III. EXPERIMENTAL RESULTS COMPARISON & DISCUSSION

The following Tab. 3 summarizes  $\delta V_{\text{th,eff,TCAD}}$ ,  $\delta V_{\text{th,eff,approx}}$ , and  $\delta V_{\text{th,eff,meas}}$  data with the excellent conformity depicted in Fig. 12. All the results fit very well together, and therefore, in the case of the IC analog design with DLS MOSFETs, it is recommended to use the innovative expression (5). Only in this way we can ensure the high accuracy level of the calculated drain-source current.

| Tab. 3: Summarv | of the effective threshol | d voltage changes |

|-----------------|---------------------------|-------------------|

|                 |                           |                   |

| α<br>(°) | $\delta V_{\text{th,eff,TCAD}} (@) \\ (W/L)_{\text{eff}} = 2.0 \\ (\%)$ | $\delta V_{\text{th,eff,approx}} (a) \\ (W/L)_{\text{eff}} = 2.0 \\ (\%)$ | $ \delta V_{\text{th,eff,meas}} @ \\ (W/L)_{\text{eff}} = 2.0 \\ (\%) $ |

|----------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 180      | 0.000                                                                   | 0.000                                                                     | 0.000                                                                   |

| 160      | -0.11                                                                   | -0.11                                                                     | -                                                                       |

| 140      | -0.30                                                                   | -0.30                                                                     | -                                                                       |

| 120      | -0.62                                                                   | -0.63                                                                     | -0.63                                                                   |

| 100      | -1.16                                                                   | -1.16                                                                     | -1.16                                                                   |

| 80       | -1.91                                                                   | -1.95                                                                     | -1.94                                                                   |

The threshold voltage variation, which has been confirmed by the measurement, is relatively small. But due to a quadratic dependence of the drain-source current on  $V_{\text{th}}$  in the above-

$I_{DS}^{0}(\mu A)$   $10^{0}$  measurement  $10^{-1}$  measurement 0.5 0.55 0.6 0.65 0.7 0.75  $V_{GS}(V)$

Fig. 9: Transfer characteristic of DLS MOSFET with angle  $\alpha = 180^{\circ}$  (detail)

Fig. 12: A Comparison of changes threshold voltage given by TCAD simulation, analytical approximation, and measurement  $\alpha$  (°)

978-1-6654-9482-3/22/\$31.00 ©2022 IEEE

threshold region and exponential dependence of the

drain-source current on  $V_{\text{th}}$  in the sub-threshold region, each  $V_{\text{th}}$  modification should be considered. Moreover, in the case where the  $V_{\text{GS}}$  is close to  $V_{\text{th}}$ , the consequence of the  $V_{\text{th}}$  variation is even more significant. This is the case, when the circuits operate in an ultra-low voltage domain, such as operating voltage below 1.0 V, and low temperatures [20]. In the case when the angle  $\alpha$  is set to 80° and respecting [20], the  $V_{\text{th}}$  variation may be up to 18 mV, which is a relatively a lot. The presented possibility to change  $V_{\text{th}}$  can help to complete the design comfortably.

In the case of drain-source current calculation, we also should respect different hole and electron mobility ( $\mu_{0,P}$ ,  $\mu_{0,N}$ ) in MOSFETs affected by the different MOSFET channel orientation [21]. In [22], the drain-source current can be varied up to 42 % dependently on the channel and silicon orientation. In the case of this article, there has been used CMOS standard (100) silicon wafers [23] and N-channel DLS MOSFETs have a top and bottom edge of the channel aligned with <110> direction. Crystalline orientations in channel area varied dependently on the geometry settings of DLS MOSFET due to curved current trajectory. For the drainsource current calculation of N-channel DLS MOSFET devices, the following fitting function (7) should be used. In this way, we can respect different channel orientations and electron mobility.

$$\mu_{0,\text{N,eff}} = (-9.8235 \cdot 10^{-4} \,\alpha^2 + 1.9913 \cdot 10^{-1} \,\alpha - 3.0154) \,\mu_{0,\text{N}} \tag{7}$$

where  $\mu_{0,N,eff}$  is effective electron mobility as a function of angle  $\alpha$  of DLS MOSFET devices and electron mobility for N-channel RLS MOSFET devices  $\mu_{0,N}$ .

The presented effective threshold voltage phenomenon could be explained such as consequence of the multithreshold transistor consists of infinitive numbers of curved narrows MOSFETs with different channel lengths [24].

To have the above-mentioned DLS MOSFETs' advantages, it is essential to respect conditions in which the DLS MOSFETs can work. The first one is to avoid using the DLS MOSFET with small geometric sizes, because it may cause a high peak field and current concentration at the local angle region of the DLS MOSFET topology. The second condition is using the DLS MOSFET in low-voltage and low-power applications which is a trend of nowadays ICs. In this way, we can reduce the total die area up to 36.9 % compared to the same circuit using the conventional MOSFETs [17]. These conditions are typically requested in real applications [25]. Moreover, in this case, another non-conventional MOSFET shape topology with sharp angles has been successfully used as well [25].

Furthermore, this approach is very useful in terms of  $V_{\rm th}$  modification for the selectively requested components. In general, the  $V_{\rm th}$  can be changed by process modification (2), as an example modification of the gate insulator's thickness. Nevertheless, in this case, this approach modifies the effective  $V_{\rm th}$  of one type of component and not selectively, such as the presented approach enables it.

## IV. CONCLUSION

This paper presents the changes in the effective threshold voltage of the DLS MOSFET devices dependently on its shapes. For this reason, the DLS MOSFET structures have been simulated in 3-D Silvaco TCAD simulator as well as they have been verified by measurement on samples. Moreover, the described phenomenon has been for the first time numerically approximated by the expression with a very high accuracy level equal to 99.995 %.

There has been observed, if the angle  $\alpha$  of the DLS MOSFETs decreases, the effective threshold voltage  $V_{\text{th,eff,DLS}}$  decreases too. In additional, if the effective aspect ratio  $(W/L)_{\text{eff}}$  of DLS MOSFETs increases, the effective threshold voltage decreases more significantly.

In both measurement and simulation cases, the effective threshold voltage for the DLS MOSFET with the effective aspect ratio  $(W/L)_{\text{eff}}$  equal to 2.0, and angle  $\alpha$  set to 80° has been decreased close to by -2 %.

This article apprises us about the interesting phenomena in IC DLS MOSFETs that can be used for both effective threshold voltage trimming as well as for the analog ICs design using DLS MOSFETs.

### References

- I. M. Ross, "The invention of the transistor," *Proceedings of the IEEE*, vol. 86, no. 1, pp. 7-28, January 1998., doi: 10.1109/5.658752.

- [2] P. R. Gray, P. J. Hurst, S. H. Lewis and R. G. Meyer, Analysis and Design of Analog Integrated Circuits - 5th Edition, New York, USA: John Wiley & Sons, Inc., January 2009, p. 896., ISBN: 978-0-470-24599-6.

- [3] R. Baker, CMOS Circuit Design, Layout, and Simulation, 3rd Edition, Wiley-IEEE Press, September 2010., ISBN: 978-0-470-88132-3.

- [4] D. Barri, P. Vacula, T. Gresl, P. Švancara, V. Kotě, J. Jakovenko and J. Voves, "MOSFETs Electrical Performance in 160 nm BCD Technology Process with the Diamond Layout Shape," *IEEE Transactions on Electron Devices*, pp. 1-8, 2020, doi: 10.1109/TED.2020.3000744.

- [5] L. Liu, J. Mu and Z. Zhu, "A 0.55-V, 28-ppm/°C, 83-nW CMOS Sub-BGR With UltraLow Power Curvature Compensation," *IEEE Transactions on Circuits and Systems*, vol. 65, no. 1, pp. 95 - 106, January 2018, doi: 10.1109/TCSI.2017.2711923.

- [6] Y. Joly, L. Lopez, J. Portal, H. Aziza, Y. Bert, F. Julien and P. Fornara, "Impact of hump effect on MOSFET mismatch in the sub-threshold area for low power analog applications," in 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 1.-4. November, 2010, doi: 10.1109/ICSICT.2010.5667684.

- [7] C.-M. Zhang, F. Jazaeri, G. Borghello, S. Mattiazzo, A. Baschirotto and C. Enz, "Bias Dependence of Total Ionizing Dose Effects on 28nm Bulk MOSFETs," in 2018 IEEE Nuclear Science Symposium and Medical Imaging Conference Proceedings (NSS/MIC), Sydney, Australia, 10-17 November, 2018, doi: 10.1109/NSSMIC.2018.8824379.

- [8] S. Sze and K. K. Ng, Physics of Semiconductor Devices, 3rd edition, Canada: John Wiley & Sons, Inc., 2007, p. 832., ISBN: 978-0-471-14323-9.

- [9] A. Bakibillah and N. Rahman, "Effect of Threshold Voltage and Channel Length on Drain Current of Silicon N-MOSFET," *European Scientific Journal*, vol. 11, no. 27, pp. 169-175, September 2015

- [10] D. Barri, "Modeling of a Hump Effect Using a Three-Dimensional TCAD Device Simulator," in *International Student Scientific Conference POSTER - 23/2019*, Prague, May 23, 2019, ISBN: 978-80-01-06581-5.

- [11] D. K. Schroder, "Series Resistance, Channel Length and Width, and Threshold Voltage," in *Semiconductor Material and Device*

*Characterization*, 3rd ed., Hoboken, New Jersey, USA, IEEE Press, John Wiley & Sons, Inc., 2006, p. 790., ISBN: 978-0-471-73906-7.

- [12] Y.-H. Cheng, "Comparison of MOSFET Threshold Voltage Extraction Methods with Temperature Variation," in 2019 IEEE 32nd International Conference on Microelectronic Test Structures (ICMTS), Kita-Kyushu City, Fukuoka, Japan, 2019, doi: 10.1109/ICMTS.2019.8730978.

- [13] D. Barri and J. Jakovenko, "Comparison of Measured Data Given by Automatized Measurement Methodology with the Analytical Expression of DLS MOSFET"., ISBN: 978-80-261-0813-9.

- [14] D. Barri, P. Vacula, V. Kotě, J. Jakovenko and J. Voves, "Improvements in the Electrical Performance of IC MOSFET Components Using Diamond Layout Style Versus Traditional Rectangular Layout Style Calculated by Conformal Mapping," *IEEE Transactions on Electron Devices*, vol. 66, no. 9, pp. 3718-3725, September, 2019, doi: 10.1109/TED.2019.2931090.

- [15] Silvaco TCAD simulation Tool, DeckBuild Deck Editor Version 4.4.3.R: Synopsys Inc., 2019.

- [16] Silvaco TCAD simulation tool, "https://www.silvaco.com," Atlas User's Manual, Device Simulation Software, 2015 [Online].

- [17] J. Júnior, R. Moreto, G. Silva, C. Thomaz and S. Gimenez, "An innovative strategy to reduce die area of robust OTA by using iMTGSPICE and diamond layout style for MOSFETs," in *Proceedings* of SBCCI'19, , Sao Paulo, SP, Brasil, August, 2019, doi: 10.1145/3338852.3339865.

- [18] R. Roggero, G. Croce, P. Gattari, E. Castellana, A. Molfese, G. Marchesi, L. Atzeni, C. Buran, A. Paleari, G. Ballarin, S. Manzini, F. Alagi and G. Pizzo, "BCD8sP: An advanced 0.16 μm technology platform with state of the art power devices," in 2013 25th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Kanazawa, Japan, 26-30 May 2013, ISBN: 978-1-4673-5134-8., doi: 10.1109/ISPSD.2013.6694422.

- [19] N. Borrel, C. Champeix, M. Lisart, A. Sarafianos, E. Kussener, W. Rahajandraibe and J.-M. Dutertre, "Electrical model of an NMOS body biased structure in triple-well technology under photoelectric laser stimulation," in 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19-23 April 2015, ISBN: 978-1-4673-7362-3., doi: 10.1109/IRPS.2015.7112799.

- [20] K. N. Leung and P. Mok, "A sub-1-V 15-ppm °C CMOS bandgap voltage reference without requiring low threshold voltage device," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 4, pp. 526-530, 07 August 2002, doi: 10.1109/4.991391.

- [21] W. Jiang, H. Yin, Y. Zhang, Y. Liu, W. Yu, J. Xu and H. Zhu, "Study of electron mobility on silicon with different crystalline orientations," in 2012 IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, Xi'an, China, 29 Oct.-1 Nov. 2012, doi: 10.1109/ICSICT.2012.6467830.

- [22] L. Silvestri, S. Reggiani, E. Gnani, A. Gnudi and G. Baccarani, "Unified model for low-field electron mobility in bulk and SOI-MOSFETs with different substrate orientations and its application to quantum drift-diffusion simulation," in 2008 IEEE 9th International Conference on Ultimate Integration of Silicon, Udine, Italy, 12-14 March 2008, doi: 10.1109/ULIS.2008.4527156.

- [23] N. André, T. P. Delhaye, M. A. K. Jazairli, B. Olbrechts, P. Gérard, L. A. Francis, J.-P. Raskin and D. Flandre, "Ultra-low-power SOI CMOS pressure sensor based on orthogonal PMOS gauges," in 22nd IMEKO TC4 International Symposum & 20th International Workshop on ADC Modelling and Testing, Lasi, Romania, September 14-15th 2017

- [24] Y. Ye, F. Liu, M. Chen and Y. Cao, "Variability analysis under layout pattern-dependent Rapid-Thermal Annealing process," in 2009 46th ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 26-31 July 2009, ISBN: 978-1-6055-8497-3., doi: 10.1145/1629911.1630054.

- [25] P. Vacula, V. Kotě, D. Barri, M. Vacula, M. Husák and J. Jakovenko, "Comparison of MOSFET Gate Waffle Patterns Based on Specific On-Resistance," *Radioengineering*, vol. 27, no. 3, pp. 598-609, September 2019, doi: 10.13164/re.2019.0598.

978-1-6654-9482-3/22/\$31.00 ©2022 IEEE