# STOCHASTIC COMPUTING SYSTEM HARDWARE DESIGN FOR CONVOLUTIONAL NEURAL NETWORKS OPTIMIZED FOR ACCURACY, AREA AND ENERGY EFFICIENCY

# HAMDAN USAMAH HAMDAN ABDELLATEF

A thesis submitted in fulfilment of the requirements for the award of the degree of Doctor of Philosophy

> School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia

> > JANUARY 2020

# DEDICATION

This thesis is dedicated to my wonderful parents who have raised me to be the person I am today, my beloved wife who supported me through my study, my lovely daughter, and my family.

#### ACKNOWLEDGEMENT

The past three years were the most challenging but productive in my life. Now, the Ph.D. journey comes to an end. I am blessed with the completion of this thesis. Alhamdulillah, I am deeply grateful and thankful to Almighty Allah, who made me able and gave me the strength to overcome the hardships and complete this thesis. I would like to express my appreciation to the people that have involved directly or indirectly in my work.

I would like to express my sincere gratitude to my supervisor, Prof. Dr. Mohamed Khalil Mohd. Hani for his guidance, enthusiastic encouragement, and useful critiques of this research work. I have gained valuable knowledge during his supervision. My very high appreciation for him is not only for academic supervision but also for sharing his philosophy of life and treating me as his son.

My sincere appreciation also goes to my co-supervisor Assoc. Prof. Dr. Shaikh Nasir Bin Shaikh Husin for his guidance and dedication towards my research work. It was also a privilege to work closely with the members of VeCAD Lab, namely Sayed Omid Ayat, Mohd Ikmal Fitri bin Maruzuki, Arbab Alamgir, and Shehryar Masud Rizvi.

Most importantly, I would like to thank my family, especially my dear parents and my beloved wife, for their love and the boundless supports during this journey. Also, I thank my daughter for creating happiness and motivation during the past year. I am thankful to my friends for making me feel at home while being too far away. This Ph.D. journey would have been impossible without all of you. Thank you.

#### ABSTRACT

Stochastic computing (SC) is an alternative computing paradigm that can lead to designs that offer lower area and power consumption compared to that of the conventional binary-encoded (BE) deterministic computing. In SC, numbers are encoded as a bit-stream of '0's and '1's, where SC computation elements (or functions) operate on one or more bit-streams. To obtain accurate results, some functions require the bit-streams to be correlated, while others require uncorrelated bit-streams or a combination of both. The relationship between SC function accuracy and correlation is not well studied in previous works. Thus, managing the correlation across the SC system is a key challenge in the effort to achieve optimum accuracy. In addition, to perform SC computation, the input values are converted from BE domain to SC; then on the completion of the computation, back to BE to obtain the results. The conversion processes require circuitry that typically consume over 80% of the overall SC system area, hence this is another key challenge of the problem. To address the above mentioned challenges, this thesis proposes a framework of an end-to-end system design optimized for accuracy and area. The framework provides guidelines to design an effective SC function or system that exploit correlation. This framework is applied in designing the SC functional units and the complete SC system for convolutional neural network (CNN), which is the dominant approach in the implementation of recognition systems. This thesis shows that although CNN is a compute-intensive and resource-demanding algorithm, through the proposed SC design framework, it is possible to implement CNN in an embedded system with limited area and power budget. Several novel SCbased functions are proposed that outperform previous works and obtain significant area savings and high accuracy to replace the BE equivalent functions. These functions include inner product, max pooling, ReLU activation function, and average pooling. Then, some training considerations are specified to enable achieving low error rates for SC-based CNN. Experimental results show that the SC-based CNN attained no or minor accuracy degradation compared to BE counterpart. SC-based CNN achieves 99.6% and 96.25% classification accuracy using MNIST digit classification and AT&T face recognition datasets, respectively. Moreover, the SC-based CNN of ResNet-20 model achieves 86.5% classification accuracy using CIFAR-10 object dataset. To rapidly map an SC system into FPGA, a generic design strategy for high-level synthesis of SC computation engines is proposed. The SC-based CNN hardware on FPGA obtains the lowest resource utilization compared to previous works on FPGA-based CNN accelerators. In addition, the proposed hardware architecture achieves 277.46 GOP/s/W energy efficiency, which outperforms previous works.

#### ABSTRAK

Pengkomputeran stokastik (SC) merupakan sebuah paradigma pengkomputeran alternatif yang dapat membawa kepada reka bentuk yang menawarkan penggunaan ruang dan kuasa yang lebih rendah berbanding dengan pengkomputeran berketentuan binari terkod (BE) konvensional. Dalam SC, nombor dikodkan sebagai strim-bit '0' dan '1', dengan elemen pengiraan (atau fungsi) beroperasi pada satu atau lebih strimbit. Untuk mendapatkan keputusan yang tepat, beberapa fungsi memerlukan strimbit yang berkorelasi, sementara yang lain memerlukan strim-bit tak berkorelasi atau gabungan kedua-duanya. Hubungan antara ketepatan dan korelasi fungsi SC tidak dikaji dengan baik dalam kajian terdahulu. Oleh itu, menguruskan korelasi seluruh sistem SC merupakan cabaran utama untuk mencapai ketepatan optimum. Selain itu, untuk melaksanakan pengiraan SC, nilai input ditukar daripada domain BE kepada SC; setelah selesai pengiraan, kembali kepada BE untuk mendapatkan keputusan. Proses penukaran ini memerlukan jalan kerja litar yang biasanya menggunakan lebih 80% daripada keseluruhan kawasan sistem SC; oleh itu, ini adalah satu lagi cabaran utama masalah ini. Bagi menangani cabaran yang dinyatakan di atas, tesis ini mencadangkan satu rangka kerja reka bentuk sistem hujung-ke-hujung yang dioptimumkan untuk ketepatan dan kawasan. Rangka kerja ini menyediakan garis panduan untuk mereka bentuk fungsi SC atau sistem berkesan yang mengeksploitasi korelasi. Rangka kerja ini digunakan dalam mereka bentuk unit berfungsi SC dan sistem SC yang lengkap bagi rangkaian neural konvolusi (CNN) yang merupakan pendekatan dominan dalam pelaksanaan sistem pengecaman. Kami menunjukkan bahawa walaupun CNN merupakan pengiraan intensif dan algoritma menuntut sumber daya, menerusi rangka kerja reka bentuk SC yang dicadangkan ini, CNN dapat dilaksanakan dalam satu sistem terbenam dengan kawasan dan bajet kuasa yang terhad. Beberapa fungsi berasaskan SC terbaharu dicadangkan yang mengatasi kajian terdahulu dan mencapai penjimatan kawasan yang ketara dan ketepatan yang tinggi untuk menggantikan BE yang setara. Fungsi ini termasuk produk dalaman, pengumpulan maksimum, fungsi pengaktifan ReLU dan pengumpulan purata. Kemudian, kami menentukan beberapa pertimbangan latihan supaya boleh mencapai kadar ralat rendah untuk CNN berasaskan SC. Keputusan eksperimen menunjukkan bahawa CNN berasaskan SC tidak menunjukkan penurunan ketepatan atau penurunan ketepatan yang kecil berbanding BE. CNN berasaskan SC masing-masing mencapai 99.6% dan 96.25% ketepatan klasifikasi menggunakan klasifikasi digit MNIST dan set data pengecaman wajah AT&T. Selain itu, CNN berasaskan SC bagi model ResNET-20 mencapai 86.5% ketepatan klasifikasi menggunakan set data objek CIFAR-10. Untuk memetakan sistem SC ke dalam FPGA dengan cepat, kami mencadangkan satu strategi reka bentuk generik untuk sintesis peringkat tinggi enjin pengiraan SC. Perkakasan CNN berasaskan SC pada FPGA memperoleh penggunaan sumber paling rendah berbanding dengan semua kajian terdahulu berkenaan pemecut CNN berasaskan FPGA. Di samping itu, seni bina perkakasan kami mencapai kecekapan tenaga 277.46 GOP/s/W yang mengatasi semua kajian terdahulu.

# TABLE OF CONTENTS

| TITLE                 | PAGE |

|-----------------------|------|

| DECLARATION           | iii  |

| DEDICATION            | iv   |

| ACKNOWLEDGEMENT       | v    |

| ABSTRACT              | vi   |

| ABSTRAK               | vii  |

| TABLE OF CONTENTS     | viii |

| LIST OF TABLES        | xiii |

| LIST OF FIGURES       | xvi  |

| LIST OF ABBREVIATIONS | xxi  |

| LIST OF SYMBOLS       | xxiv |

| LIST OF APPENDICES    | xxvi |

| CHAPTER 1 | INTRO | DUCTIO    | N                                      | 1  |

|-----------|-------|-----------|----------------------------------------|----|

|           | 1.1   | Backgro   | ound of research                       | 1  |

|           |       | 1.1.1     | Stochastic computing                   | 1  |

|           |       | 1.1.2     | Convolutional neural network           | 3  |

|           |       | 1.1.3     | FPGA design using HLS tools            | 6  |

|           | 1.2   | Problem   | 1 Statements                           | 7  |

|           |       | 1.2.1     | Summary of problems in existing CNN    |    |

|           |       |           | based on stochastic computing          | 7  |

|           |       | 1.2.2     | Limitations of existing techniques     |    |

|           |       |           | of SC system design that exploit       |    |

|           |       |           | correlation                            | 9  |

|           |       | 1.2.3     | The issue of energy efficiency achiev- |    |

|           |       |           | able in conventional CNN accelerators  | 11 |

|           | 1.3   | Objectiv  | ves                                    | 12 |

|           | 1.4   | Scope o   | f work                                 | 13 |

|           | 1.5   | Researc   | h contributions and achievements       | 14 |

|           | 1.6   | Thesis of | organization                           | 15 |

| CHAPTER 2 | LITER | ATURE    | REVIEW                                   | 17 |

|-----------|-------|----------|------------------------------------------|----|

|           | 2.1   | Basics   | of Stochastic Computing circuits and     |    |

|           |       | system   |                                          | 17 |

|           |       | 2.1.1    | SNs, encoding, and basic arithmetic      |    |

|           |       |          | elements                                 | 17 |

|           |       | 2.1.2    | BE-to-SC and SC-to-BE conversion         | 19 |

|           |       | 2.1.3    | Correlation in SC circuits — concepts    |    |

|           |       |          | and definitions                          | 22 |

|           |       | 2.1.4    | RNG sharing scheme in generation of      |    |

|           |       |          | SNs                                      | 24 |

|           |       | 2.1.5    | Top-level structural view of an SC       |    |

|           |       |          | system                                   | 25 |

|           |       | 2.1.6    | Sources of inaccuracy in SC systems      | 26 |

|           | 2.2   | Stochas  | tic functions                            | 28 |

|           |       | 2.2.1    | Prelude                                  | 28 |

|           |       | 2.2.2    | SC inner product function                | 30 |

|           |       | 2.2.3    | SC adder and multiplier functions — a    |    |

|           |       |          | review                                   | 31 |

|           |       | 2.2.4    | Previous work on SC inner product        | 33 |

|           |       | 2.2.5    | Previous work on SC maximum and          |    |

|           |       |          | minimum functions                        | 37 |

|           | 2.3   | Optimiz  | zation of circuit area in an SC system — |    |

|           |       | a review | V                                        | 41 |

|           | 2.4   | Optimiz  | zation of accuracy of SC circuits - a    |    |

|           |       | review   |                                          | 42 |

|           | 2.5   | Stochas  | tic functions exploiting correlation     | 44 |

|           |       | 2.5.1    | Overview                                 | 44 |

|           |       | 2.5.2    | Management of SNs correlation            | 46 |

|           |       | 2.5.3    | Previous work on SC median filter        | 48 |

|           |       | 2.5.4    | Previous work on SC Robert Cross         |    |

|           |       |          | edge detection                           | 48 |

|           | 2.6   | Convol   | utional neural network (CNN)             | 50 |

|           |       | 2.6.1    | Basics of CNN - architectures and        |    |

|           |       |          | algorithms                               | 50 |

|           |       | 2.6.2    | Previous related work on CNN                | 57        |

|-----------|-------|----------|---------------------------------------------|-----------|

|           |       | 2.6.3    | Previous work on FPGA-based CNN             |           |

|           |       |          | implementation                              | 59        |

|           |       | 2.6.4    | CNN accelerators using alternative          |           |

|           |       |          | computing paradigms                         | 66        |

|           | 2.7   | CNN ba   | ased on stochastic computing (SC CNN)       | 68        |

|           |       | 2.7.1    | Previous works on SC CNN                    | 68        |

|           |       | 2.7.2    | Previous works on hybrid SC CNN             | 72        |

|           | 2.8   | Summa    | ry of the outstanding issues in SC circuits |           |

|           |       | and syst | tems for CNN                                | 73        |

|           |       | 2.8.1    | Issues of effective multi-stage SC          |           |

|           |       |          | system design                               | 73        |

|           |       | 2.8.2    | Design of effective functional units for    |           |

|           |       |          | SC CNN                                      | 75        |

|           |       | 2.8.3    | High-level synthesis of FPGA-based          |           |

|           |       |          | SC CNN                                      | 76        |

|           |       |          |                                             |           |

| CHAPTER 3 | RESEA | RCH MF   | ETHODOLOGY                                  | 77        |

|           | 3.1   | Researc  | h approach                                  | 77        |

|           | 3.2   | Design   | of experiment                               | 79        |

|           |       | 3.2.1    | Software tools and validation platform      | 79        |

|           |       | 3.2.2    | Random number generator                     | 87        |

|           |       | 3.2.3    | Measurement metrics                         | 88        |

|           |       | 3.2.4    | Datasets                                    | 91        |

|           | 3.3   | Summa    | ry                                          | 92        |

| CHAPTER 4 | FRAM  | FWORK    | FOR DESIGN OF SC SYSTEMS                    | 95        |

|           | 4.1   |          | erization of correlation in SC functions    | 95        |

|           | 7.1   | 4.1.1    | Definitions of correlation-sensitivity      | )5        |

|           |       | 7.1.1    | and correlation-induced properties          | 95        |

|           |       | 4 1 2    | Relationship between correlation and        | 75        |

|           |       |          |                                             |           |

|           |       | 4.1.2    |                                             | 07        |

|           |       |          | accuracy in SC functions                    | 97        |

|           |       | 4.1.2    |                                             | 97<br>104 |

х

|           |                                           | 4.1.4                                                                                                  | How to use independent RNGs in SC                                                                                                                                                                                                                                                                                        |                                                                                                                                 |

|-----------|-------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|           |                                           |                                                                                                        | system                                                                                                                                                                                                                                                                                                                   | 105                                                                                                                             |

|           | 4.2                                       | Correlat                                                                                               | ion manipulation circuits                                                                                                                                                                                                                                                                                                | 109                                                                                                                             |

|           |                                           | 4.2.1                                                                                                  | How to re-correlate uncorrelated SNs                                                                                                                                                                                                                                                                                     | 109                                                                                                                             |

|           |                                           | 4.2.2                                                                                                  | SC min/max function                                                                                                                                                                                                                                                                                                      | 110                                                                                                                             |

|           |                                           | 4.2.3                                                                                                  | How to relocate positions of ones in a                                                                                                                                                                                                                                                                                   |                                                                                                                                 |

|           |                                           |                                                                                                        | SN bit-stream                                                                                                                                                                                                                                                                                                            | 110                                                                                                                             |

|           |                                           | 4.2.4                                                                                                  | The correlator                                                                                                                                                                                                                                                                                                           | 113                                                                                                                             |

|           |                                           | 4.2.5                                                                                                  | Performance evaluation of correlator                                                                                                                                                                                                                                                                                     | 113                                                                                                                             |

|           |                                           | 4.2.6                                                                                                  | Correlated stochastic number generator                                                                                                                                                                                                                                                                                   | 117                                                                                                                             |

|           | 4.3                                       | RNG sh                                                                                                 | aring scheme                                                                                                                                                                                                                                                                                                             | 120                                                                                                                             |

|           | 4.4                                       | Guidelir                                                                                               | nes on design of SC systems                                                                                                                                                                                                                                                                                              | 124                                                                                                                             |

|           |                                           | 4.4.1                                                                                                  | Guidelines on design of SC functions                                                                                                                                                                                                                                                                                     | 125                                                                                                                             |

|           |                                           | 4.4.2                                                                                                  | Guidelines on design of a multistage                                                                                                                                                                                                                                                                                     |                                                                                                                                 |

|           |                                           |                                                                                                        | SC system with correlation                                                                                                                                                                                                                                                                                               | 127                                                                                                                             |

|           | 4.5                                       | Summar                                                                                                 | у                                                                                                                                                                                                                                                                                                                        | 132                                                                                                                             |

|           |                                           |                                                                                                        |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                 |

|           |                                           |                                                                                                        |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                 |

| CHAPTER 5 | SC-BAS                                    | SED CO                                                                                                 | NVOLUTIONAL NEURAL NET-                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

| CHAPTER 5 |                                           |                                                                                                        | NVOLUTIONAL NEURAL NET-<br>TECTURE, DESIGN, AND HIGH-                                                                                                                                                                                                                                                                    |                                                                                                                                 |

| CHAPTER 5 | WORK                                      |                                                                                                        | TECTURE, DESIGN, AND HIGH-                                                                                                                                                                                                                                                                                               | 135                                                                                                                             |

| CHAPTER 5 | WORK                                      | : ARCHI<br>, SYNTHI                                                                                    | TECTURE, DESIGN, AND HIGH-                                                                                                                                                                                                                                                                                               | <b>135</b><br>135                                                                                                               |

| CHAPTER 5 | WORK<br>LEVEL                             | : ARCHI<br>SYNTHI<br>Propose                                                                           | TECTURE, DESIGN, AND HIGH-<br>ESIS                                                                                                                                                                                                                                                                                       |                                                                                                                                 |

| CHAPTER 5 | WORK<br>LEVEL<br>5.1                      | : ARCHI<br>SYNTHI<br>Propose                                                                           | <b>TECTURE, DESIGN, AND HIGH-</b><br>ESIS<br>d SC CNN architecture model                                                                                                                                                                                                                                                 | 135                                                                                                                             |

| CHAPTER 5 | WORK<br>LEVEL<br>5.1                      | : ARCHI<br>SYNTHI<br>Propose<br>SC func                                                                | <b>ITECTURE, DESIGN, AND HIGH-</b><br><b>ESIS</b><br>d SC CNN architecture model<br>tions for SC CNN inference                                                                                                                                                                                                           | 135<br>137                                                                                                                      |

| CHAPTER 5 | WORK<br>LEVEL<br>5.1                      | : ARCHI<br>SYNTHI<br>Propose<br>SC func<br>5.2.1                                                       | <b>ITECTURE, DESIGN, AND HIGH-<br/>ESIS</b><br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function                                                                                                                                                                                    | 135<br>137<br>138                                                                                                               |

| CHAPTER 5 | WORK<br>LEVEL<br>5.1                      | : ARCHI<br>SYNTHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2                                              | <b>TECTURE, DESIGN, AND HIGH-<br/>ESIS</b><br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function                                                                                                                                                      | 135<br>137<br>138<br>144                                                                                                        |

| CHAPTER 5 | WORK<br>LEVEL<br>5.1                      | : ARCHI<br>SYNTHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2<br>5.2.3                                     | <b>TECTURE, DESIGN, AND HIGH-<br/>ESIS</b><br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function<br>SC pooling functions                                                                                                                              | 135<br>137<br>138<br>144                                                                                                        |

| CHAPTER 5 | WORK<br>LEVEL<br>5.1                      | : ARCHI<br>SYNTHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                            | TECTURE, DESIGN, AND HIGH-<br>ESIS<br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function<br>SC pooling functions<br>Verification of convolution-ReLU-                                                                                                 | 135<br>137<br>138<br>144<br>147                                                                                                 |

| CHAPTER 5 | <b>WORK</b><br><b>LEVEL</b><br>5.1<br>5.2 | : ARCHI<br>SYNTHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                            | TECTURE, DESIGN, AND HIGH-<br>ESIS<br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function<br>SC pooling functions<br>Verification of convolution-ReLU-<br>pooling dataflow                                                                             | <ul> <li>135</li> <li>137</li> <li>138</li> <li>144</li> <li>147</li> <li>150</li> </ul>                                        |

| CHAPTER 5 | <b>WORK</b><br><b>LEVEL</b><br>5.1<br>5.2 | : ARCHI<br>SYNTHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>SC CNN                  | TECTURE, DESIGN, AND HIGH-<br>ESIS<br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function<br>SC pooling functions<br>Verification of convolution-ReLU-<br>pooling dataflow<br>V training considerations                                                | <ul> <li>135</li> <li>137</li> <li>138</li> <li>144</li> <li>147</li> <li>150</li> <li>152</li> </ul>                           |

| CHAPTER 5 | <b>WORK</b><br><b>LEVEL</b><br>5.1<br>5.2 | : ARCHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>SC CNN<br>5.3.1<br>5.3.2          | TECTURE, DESIGN, AND HIGH-<br>ESIS<br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function<br>SC pooling functions<br>Verification of convolution-ReLU-<br>pooling dataflow<br>V training considerations<br>Normalization                               | <ul> <li>135</li> <li>137</li> <li>138</li> <li>144</li> <li>147</li> <li>150</li> <li>152</li> <li>152</li> </ul>              |

| CHAPTER 5 | <b>WORK</b><br><b>LEVEL</b><br>5.1<br>5.2 | : ARCHI<br>Propose<br>SC func<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>SC CNN<br>5.3.1<br>5.3.2<br>MATLA | TECTURE, DESIGN, AND HIGH-<br>ESIS<br>d SC CNN architecture model<br>tions for SC CNN inference<br>Inner product SC function<br>SC ReLU activation function<br>SC pooling functions<br>Verification of convolution-ReLU-<br>pooling dataflow<br>Vtraining considerations<br>Normalization<br>Modified backward functions | <ul> <li>135</li> <li>137</li> <li>138</li> <li>144</li> <li>147</li> <li>150</li> <li>152</li> <li>152</li> <li>153</li> </ul> |

|           |       | 5.6.1    | The SC convolutional layer hardware   |     |

|-----------|-------|----------|---------------------------------------|-----|

|           |       |          | architecture overview                 | 164 |

|           |       | 5.6.2    | Applying HLS design technique in      |     |

|           |       |          | creating the implementation of SC     |     |

|           |       |          | CNN                                   | 167 |

|           | 5.7   | Summa    | ry                                    | 174 |

| CHAPTER 6 | RESUL | TS, ANA  | LYSIS, AND DISCUSSION                 | 177 |

|           | 6.1   | Perform  | ance analysis of SC functions for CNN | 177 |

|           |       | 6.1.1    | SC inner product                      | 177 |

|           |       | 6.1.2    | SC ReLU                               | 188 |

|           |       | 6.1.3    | SC Pooling                            | 190 |

|           | 6.2   | Validati | on of complete SC CNN model           | 196 |

|           |       | 6.2.1    | Digit classification dataset          | 197 |

|           |       | 6.2.2    | Face classification dataset           | 200 |

|           |       | 6.2.3    | Object recognition dataset            | 200 |

|           | 6.3   | Perform  | aance analysis of SC CNN on FPGA      | 202 |

|           |       | 6.3.1    | Performance of the SC system hard-    |     |

|           |       |          | ware                                  | 203 |

|           |       | 6.3.2    | Comparison of SC versus BE CNN        | 205 |

|           |       | 6.3.3    | Benchmarking and discussion           | 207 |

|           | 6.4   | Summa    | ry                                    | 212 |

| CHAPTER 7 | CONCI | LUSION   |                                       | 213 |

|           | 7.1   | Achieve  | ments of research objectives          | 214 |

|           | 7.2   | Researc  | h contributions                       | 215 |

|           | 7.3   | Future v | work                                  | 218 |

|           |       |          |                                       |     |

|           |       |          |                                       |     |

| REFERENCES           | 221 |

|----------------------|-----|

| LIST OF PUBLICATIONS | 234 |

# LIST OF TABLES

| TABLE NO.  | TITLE                                                     | PAGE |

|------------|-----------------------------------------------------------|------|

| Table 2.1  | SN encoding                                               | 18   |

| Table 2.2  | Correlation sensitivity of SC elements (logic functions)  | 23   |

| Table 2.3  | XNOR gate logic function                                  | 29   |

| Table 2.4  | Previous works on SC Inner product compared to            |      |

|            | conventional SC inner product                             | 38   |

| Table 2.5  | Previous works on SC min and max functions                | 40   |

| Table 2.6  | Previous works on RNG sharing scheme                      | 41   |

| Table 2.7  | Previous works on designing accurate SC circuits          | 43   |

| Table 2.8  | Functions of a two input $f(x,y)$ combinational circuit   | 44   |

| Table 2.9  | Previous works on decorrelation                           | 46   |

| Table 2.10 | Common CNN activation functions                           | 56   |

| Table 2.11 | List of previous work on deep CNN using ImageNet dataset  | 58   |

| Table 2.12 | The ResNet model for CIFAR-10                             | 59   |

| Table 2.13 | Previous works on accelerating CNN on FPGAs               | 65   |

| Table 2.14 | The SC CNN previous works                                 | 71   |

| Table 2.15 | Hybrid SC CNN previous works                              | 74   |

| Table 3.1  | The LFSR polynomials used in this thesis                  | 87   |

| Table 3.2  | The amount of FPGA device resources used in the reviewed  |      |

|            | works                                                     | 90   |

| Table 4.1  | Correlation sensitivity and variation when inputs are     |      |

|            | correlated                                                | 103  |

| Table 4.2  | Timing diagram to compare the correlator performance      |      |

|            | with regeneration                                         | 114  |

| Table 4.3  | Resource utilization of the conversion circuits           | 115  |

| Table 4.4  | Resource utilization comparison for different correlators | 117  |

| Table 4.5  | Resource utilization for the proposed CSNG                | 118  |

| Table 4.6  | The correlation $\rho(LFSR, CS(LFSR, k))$ between random  |      |

|            | number sequences produced using circular shift            | 121  |

| Table 4.7  | The proposed RNG sharing scheme correlation                           |     |

|------------|-----------------------------------------------------------------------|-----|

|            | $\rho(LFSR, FCS(LFSR, k))$                                            | 122 |

| Table 4.8  | The 16 input APC-based inner product accuracy with                    |     |

|            | respect to RNG sharing                                                | 124 |

| Table 4.9  | The correlation variation $\delta_{SCC}$ of the different SC elements |     |

|            | and functions                                                         | 126 |

| Table 5.1  | The used SC max function according to the input SCC                   |     |

|            | estimation                                                            | 149 |

| Table 5.2  | The purpose of the derivatives                                        | 154 |

| Table 5.3  | The dimensions of the backward function operands                      | 156 |

| Table 5.4  | The proposed SC layers for the SC CNN                                 | 156 |

| Table 5.5  | The Double Buffering Timing                                           | 174 |

| Table 6.1  | The proposed inner product function absolute error $(\times 10^{-2})$ |     |

|            | with different N and stochastic number length $(L = 256)$             | 179 |

| Table 6.2  | PSNR of the APC-based and the proposed inner product                  |     |

|            | function                                                              | 180 |

| Table 6.3  | Comparison of the proposed SC inner product resource                  |     |

|            | utilization with BE equivalent using $f = 100 \text{ MHz}$            | 183 |

| Table 6.4  | The proposed $N = 32$ SC inner product area ( $\mu$ m <sup>2</sup> )  |     |

|            | compared to previous work                                             | 184 |

| Table 6.5  | Comparison of the proposed inner product function with                |     |

|            | previous methods                                                      | 186 |

| Table 6.6  | The output SNR (dB) of SC FIR filters using the proposed              |     |

|            | SC inner product for different orders and cutoff frequencies          | 187 |

| Table 6.7  | Comparison of output SNR (dB) of 3rd order low-pass SC                |     |

|            | FIR filters using proposed inner product with previous work           |     |

|            |                                                                       | 187 |

| Table 6.8  | The MAE of the proposed SC ReLU with respect to different             |     |

|            | SN lengths                                                            | 188 |

| Table 6.9  | Resource utilization of SC ReLU                                       | 189 |

| Table 6.10 | Comparison of resource utilization of the proposed SC                 |     |

|            | neuron for $L = 256$ and $f = 100$ MHz                                | 189 |

| Table 6.11 | Resource utilization of SC max functions                              | 193 |

| Table 6.12 | Resource utilization of SC addition operation                         | 196 |

| Table 6.13 | The CNN model used for digit classification using MNIST       |     |

|------------|---------------------------------------------------------------|-----|

|            | dataset                                                       | 197 |

| Table 6.14 | The proposed SC CNN error rate using MNIST dataset            | 198 |

| Table 6.15 | The proposed SC CNN error rate using MNIST dataset            |     |

|            | compared with previous works                                  | 199 |

| Table 6.16 | The proposed SC CNN error rate using AT&T dataset             | 200 |

| Table 6.17 | The ResNet-20 test error rate in BE computation               | 201 |

| Table 6.18 | The proposed SN CNN error rate using CIFAR-10 dataset         |     |

|            | compared with previous work on SC CNN for CIFAR-10            | 202 |

| Table 6.19 | The #op for SC computation                                    | 204 |

| Table 6.20 | Performance, resource utilization, and energy efficiency of   |     |

|            | the SC CNN convolution hardware architecture for different    |     |

|            | degrees of parallelism $Tm \times Tn$ using 100 MHz frequency | 205 |

| Table 6.21 | Performance, and resource utilization of the fixed point      |     |

|            | CNN convolution accelerator at 100 MHz frequency              | 205 |

| Table 6.22 | Power comparison (in W) between SC and BE hardware            |     |

|            | using Vivado power analysis tool                              | 206 |

| Table 6.23 | Resource utilization, performance, and energy-efficiency      |     |

|            | comparison with previous works using BE computation           | 208 |

| Table 6.24 | Resource utilization, performance, and energy-efficiency      |     |

|            | comparison with previous works using other types of           |     |

|            | computation                                                   | 211 |

| Table 6.25 | Output throughput comparison with our BE implementation       |     |

|            | and previous works                                            | 212 |

| Table B.1  | The absolute errors of each filter                            | 249 |

| Table C.1  | The definitions of variables and parameters in Equation       |     |

|            | (C.1)                                                         | 251 |

# LIST OF FIGURES

| FIGURE NO.  | TITLE                                                                                      | PAGE |

|-------------|--------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Using AND gate to perform SC multiplication                                                | 2    |

| Figure 1.2  | Processes covered by ANN and CNN in a recognition                                          |      |

|             | system                                                                                     | 4    |

| Figure 2.1  | SC basic circuits                                                                          | 20   |

| Figure 2.2  | SC conversion circuits                                                                     | 21   |

| Figure 2.3  | SC multiplier (using AND gate). Note: inputs are UP-                                       |      |

|             | encoded, but not uncorrelated, hence $p_{x'} = \frac{6}{8}$ , $p_{y'} = \frac{4}{8}$ , and |      |

|             | $p_{z',} = \frac{2}{8}$ , i.e. $p_{z'} \neq p_{x'} \times p_{y'}$                          | 22   |

| Figure 2.4  | Generating stochastic numbers with respect to correlation                                  |      |

|             | and sharing                                                                                | 24   |

| Figure 2.5  | Generic structure of an SC system                                                          | 26   |

| Figure 2.6  | Random number fluctuation when generating a SN of                                          |      |

|             | probability 0.65 using LFSR and Halton random number                                       |      |

|             | sequences. $p_x^*$ represents the actual probability of the SN                             |      |

|             | generated.                                                                                 | 27   |

| Figure 2.7  | The conventional SC inner product                                                          | 31   |

| Figure 2.8  | Accurate SC adder                                                                          | 32   |

| Figure 2.9  | SC inner product using weighted summation method                                           | 33   |

| Figure 2.10 | 16-input APC                                                                               | 34   |

| Figure 2.11 | Two-line SC multiplication                                                                 | 36   |

| Figure 2.12 | Correlation loss problem. $p_A = \frac{4}{8}, p_B = \frac{6}{8}, p_C = \frac{6}{8}$ , and  |      |

|             | $p_D = \frac{2}{8}$ . The probability of the MUXs output SNs are                           |      |

|             | $\frac{5}{8}$ and $\frac{4}{8}$ , where these SNs had lost their correlation. The          |      |

|             | output SN probability $p_Z = \frac{6}{8}$ is not correct $(\neq \frac{5}{8})$ because      |      |

|             | of the issue of variation in correlation.                                                  | 47   |

| Figure 2.13 | The median filter process and circuit                                                      | 49   |

| Figure 2.14 | SC Robert-Cross edge detection                                                             | 50   |

| Figure 2.15 | A modern deep CNN ResNet-20 model , Each convolutional                                                      |     |

|-------------|-------------------------------------------------------------------------------------------------------------|-----|

|             | layer performs convolution and ReLU activation function.                                                    |     |

|             | Input image size is $32 \times 32$ . The subsampling is included                                            |     |

|             | in the convolutional layer by using stride of 2 (/2)                                                        | 52  |

| Figure 2.16 | A typical ANN                                                                                               | 53  |

| Figure 2.17 | The convolution operation                                                                                   | 55  |

| Figure 2.18 | The pooling operation                                                                                       | 56  |

| Figure 3.1  | The research overview                                                                                       | 77  |

| Figure 3.2  | Zynq simplified architecture                                                                                | 81  |

| Figure 3.3  | Vivado HLS design flow                                                                                      | 84  |

| Figure 3.4  | Sample of MNIST images                                                                                      | 92  |

| Figure 3.5  | Samples of the AT&T face database                                                                           | 93  |

| Figure 3.6  | CIFAR-10 sample images                                                                                      | 93  |

| Figure 4.1  | The SC circuit used in the test experiment                                                                  | 97  |

| Figure 4.2  | Generating SNs with a controlled level of correlation                                                       |     |

|             | (SNG_CC)                                                                                                    | 98  |

| Figure 4.3  | Characteristics of SC T flip-flop adder and traditional SC                                                  |     |

|             | adder                                                                                                       | 99  |

| Figure 4.4  | Characteristics of SC multiplier and the multiplier with one                                                |     |

|             | input decorrelated using D flip flop                                                                        | 100 |

| Figure 4.5  | Characteristics of SC min/max                                                                               | 100 |

| Figure 4.6  | Characteristics of SC division and absolute subtraction                                                     | 101 |

| Figure 4.7  | Characteristics of SC functions when $SCC_{in} = 1$                                                         | 102 |

| Figure 4.8  | SCC variation due to SC absolute subtraction (using XOR                                                     |     |

|             | gate) where all inputs are correlated ( $SCC_{in} = 1$ ). $p_x = \frac{7}{8}$ ,                             |     |

|             | $p_y = \frac{3}{8}, p_a = \frac{5}{8}, \text{ and } p_b = \frac{2}{8}.$ The outputs $p_z = \frac{4}{8}$ and |     |

|             | $p_c = \frac{3}{8}$ represent $  p_x - p_y  $ and $  p_a - p_b  $ , respectively.                           |     |

|             | $SCC_{out} \neq 1$ , so the function is correlation-induced.                                                | 103 |

| Figure 4.9  | The correlation between two random number sequences                                                         |     |

|             | generated by LFSR using the same polynomial with                                                            |     |

|             | different seeds                                                                                             | 107 |

| Figure 4.10 | The correlation between two random number sequences                                                         |     |

|             | generated by LFSR using different polynomials with                                                          |     |

|             | different seeds                                                                                             | 108 |

|             |                                                                                                             |     |

| Figure 4.11 | SCC and relation to '1's position                          | 109 |

|-------------|------------------------------------------------------------|-----|

| Figure 4.12 | The correlator experimental setup                          | 114 |

| Figure 4.13 | Proposed Correlator for different counter bit-width and    |     |

|             | initial correlation (SCC <sub>in</sub> )                   | 115 |

| Figure 4.14 | Comparison of correlator output MAE                        | 116 |

| Figure 4.15 | The CSNG experimental setup                                | 119 |

| Figure 4.16 | The CSNG output error and correlation                      | 119 |

| Figure 4.17 | Example of RNG sharing types                               | 121 |

| Figure 4.18 | $f_1$ is not CI, and $f_2$ is either CS or not (case 1)    | 129 |

| Figure 4.19 | $f_1$ is CI, and $f_2$ is CS (case 2)                      | 129 |

| Figure 4.20 | Case 3: correlator is required to be added                 | 130 |

| Figure 4.21 | Case 4: CSNG is required to generate a correlated SN       | 131 |

| Figure 4.22 | Matching degree pf parallelism between functional units to |     |

|             | preserve SC dataflow nature                                | 132 |

| Figure 4.23 | Example of matching the parallelism for maintaining SC     |     |

|             | dataflow                                                   | 132 |

| Figure 5.1  | The top-level view of CNN in SC                            | 136 |

| Figure 5.2  | Proposed inner product circuit                             | 140 |

| Figure 5.3  | Generalized coefficients BE/SC conversion                  | 143 |

| Figure 5.4  | N = 4 coefficient BE/SC example                            | 143 |

| Figure 5.5  | Creating a correlation-insensitive and accurate SC-ReLU    |     |

|             | function                                                   | 145 |

| Figure 5.6  | The SC-ReLU circuit                                        | 146 |

| Figure 5.7  | Using the counter-based max function (Function 1) for max- |     |

|             | pooling                                                    | 147 |

| Figure 5.8  | The case study used to verify the dataflow of convolution- |     |

|             | ReLU-pooling layers and evaluate the overall accuracy      | 151 |

| Figure 5.9  | The forward and backward phases in the ANN or CNN          | 154 |

| Figure 5.10 | Overview of the hardware architecture for the SC           |     |

|             | convolutional layer                                        | 165 |

|             |                                                            |     |

| Figure 5.11 | SC computation engine with Tm=2 and Tn=4. The input            |     |

|-------------|----------------------------------------------------------------|-----|

|             | SNGs share one random number sequence, and the weights         |     |

|             | SNGs shares another sequence. Both random number               |     |

|             | sequences are generated by one RNG via FCSh sharing            |     |

|             | scheme.                                                        | 173 |

| Figure 6.1  | The proposed SC inner product absolute error with different    |     |

|             | number of inputs $N$ and SN length $L$                         | 178 |

| Figure 6.2  | Absolute error comparison of FEB using the proposed            |     |

|             | functions with previous work                                   | 181 |

| Figure 6.3  | SNR for different filter orders $(N)$ and different normalized |     |

|             | cutoff frequency $(\pi)$                                       | 182 |

| Figure 6.4  | Correlation variation of the proposed SC inner product         |     |

|             | function                                                       | 185 |

| Figure 6.5  | The SC FIR filter                                              | 186 |

| Figure 6.6  | Results of the proposed SC ReLU using different SN length      |     |

|             | L                                                              | 188 |

| Figure 6.7  | Accuracy of SC neuron for various $N$ and $L$ parameters       | 189 |

| Figure 6.8  | The max operation testing                                      | 190 |

| Figure 6.9  | The accuracy of proposed SC max functions for different        |     |

|             | SCC and SN lengths                                             | 191 |

| Figure 6.10 | Comparison of the proposed max function with previous          |     |

|             | works for L=1024                                               | 192 |

| Figure 6.11 | The absolute error of the system using different SC max        |     |

|             | approaches                                                     | 194 |

| Figure 6.12 | The absolute error of the system using different SC addition   |     |

|             | approaches for average pooling for different L                 | 196 |

| Figure B.1  | Image processing case study in testing the effectiveness of    |     |

|             | the proposed SC design framework                               | 241 |

| Figure B.2  | The Gaussian filter kernel and SC circuit                      | 242 |

| Figure B.3  | Correlation management of the SC system                        | 245 |

| Figure B.4  | The SC system after applying the proposed guidelines           | 245 |

| Figure B.5  | Test setup for evaluating the SC system case study             | 246 |

| Figure B.6  | The experimental setup input image                             | 247 |

| Figure B.7 | The SC and BE noise reduction results of the experimental            |     |

|------------|----------------------------------------------------------------------|-----|

|            | setup                                                                | 248 |

| Figure B.8 | The edge detection output images                                     | 248 |

| Figure B.9 | The threshold and the SC system output with and without              |     |

|            | using the proposed correlating circuits                              | 249 |

| Figure C.1 | Convolution layer example                                            | 252 |

| Figure C.2 | Illustration of partial derivatives of loss with respect to          |     |

|            | selected inputs                                                      | 255 |

| Figure C.3 | Illustration of partial derivatives of loss with respect to $w_{11}$ | 257 |

# LIST OF ABBREVIATIONS

| ANN   | - | Artificial Neural Network               |

|-------|---|-----------------------------------------|

| APC   | _ | Accumulative Parallel Counter           |

| ASIC  | _ | Application-Specific Integrated Circuit |

| BE    | _ | Binary-Encoded deterministic computing  |

| BISC  | _ | Binary-Interfaced Stochastic computing  |

| BNN   | _ | Binarized Neural Network                |

| BP    | _ | BiPolar encoding                        |

| BRAM  | _ | On-chip Block RAM                       |

| CNN   | _ | Convolutional Neural Network            |

| CI    | _ | Correlation-induced                     |

| CS    | _ | Correlation-sensitive                   |

| CSh   | _ | Circular Shift                          |

| CSNG  | _ | Correlated Stochastic Number Generator  |

| CTR   | _ | Counter                                 |

| DFF   | _ | D Flip-Flop                             |

| DNN   | _ | Deep Neural Network                     |

| DSP   | _ | Digital Signal Processing               |

| DTE   | _ | Data Transfer Engine                    |

| BE/SC | _ | Binary encoded-to-stochastic computing  |

| FCSh  | _ | Flip Circular Shift                     |

| FEB   | _ | Feature Extraction Block                |

| FIR   | _ | Finite Impulse Response                 |

| FF    | _ | Flip-Flop                               |

| FFT   | _ | Fast Fourier Transform                  |

| FPGA  | _ | Field Programmable Gate Array            |

|-------|---|------------------------------------------|

| FSM   | _ | Finite State Machine                     |

| GOP   | _ | Giga OPerations                          |

| GPGPU | _ | General-Purpose Graphics Processing Unit |

| GPP   | _ | General-Purpose Processor                |

| GPU   | _ | Graphics Processing Unit                 |

| HDL   | _ | Hardware Description Language            |

| HLL   | _ | High-Level Language                      |

| HLS   | _ | High-Level Synthesis                     |

| II    | _ | Initiation Interval                      |

| IOBD  | _ | Input Output Block Diagram               |

| LCTR  | _ | Local down-counter                       |

| LFSR  | - | Linear Feedback Shift Register           |

| LUT   | _ | LookUp Table                             |

| MAC   | _ | Multiply-accumulate                      |

| MAE   | _ | Mean Absolute Error                      |

| MSE   | _ | Mean Squared Error                       |

| MUX   | _ | MUltipleXer                              |

| ORL   | _ | Olivetti Research Laboratory             |

| PE    | _ | Processing Element                       |

| PL    | _ | Programmable Logic                       |

| PP    | _ | Progressive Precision                    |

| PS    | _ | Processing System                        |

| PDT   | _ | Probability Domain Transformation        |

| PSNR  | _ | Peak-Signal-to-Noise Ratio               |

| ReLU  | _ | Rectified Linear Unit                    |

| RC    | _ | Robert Cross                             |

| RNG   | _ | Random Number Generator                |

|-------|---|----------------------------------------|

| RTL   | _ | Register Transfer Level                |

| SC    | - | Stochastic Computing                   |

| SCC   | _ | Stochastic Computing Correlation       |

| SDK   | - | Software Development Kit               |

| SGD   | - | Stochastic Gradient Descent            |

| SN    | - | Stochastic Number                      |

| SNG   | _ | Stochastic Number Generator            |

| SNR   | - | Signal-to-Noise Ratio                  |

| SoC   | _ | System-on-Chip                         |

| SC/BE | - | Stochastic computing-to-binary encoded |

| TFF   | _ | Toggle Flip-Flop                       |

| UP    | _ | UniPolar encoding                      |

# LIST OF SYMBOLS

| α                               | - | Learning Rate                                                              |

|---------------------------------|---|----------------------------------------------------------------------------|

| η                               | - | Energy-efficiency                                                          |

| ρ                               | - | Correlation Coefficient                                                    |

| $\delta_{SCC}$                  | - | Variation in stochatic computing correlation                               |

| τ                               | _ | Clock period                                                               |

| conv()                          | - | Convolution function                                                       |

| corr()                          | _ | Cross-correlation function                                                 |

| dB                              | _ | deciBel                                                                    |

| $\frac{\partial L}{\partial x}$ | - | derivative of loss with respect to input                                   |

| $\frac{\partial L}{\partial w}$ | - | derivative of loss with respect to weights                                 |

| $\frac{\partial L}{\partial z}$ | _ | gradient from next layer                                                   |

| k <sub>CS</sub>                 | - | Amount of bit-wise circular shift                                          |

| L                               | - | Stochastic number Length                                                   |

| max()                           | - | The maximum function                                                       |

| min()                           | _ | The minimum function                                                       |

| n                               | - | Binary number bit-width                                                    |

| Tn                              | _ | Input feature maps Tile size                                               |

| Tm                              | - | Output feature maps Tile size                                              |

| Tr                              | _ | Feature map height (rows) Tile size                                        |

| Tc                              | - | Feature map width (columns) Tile size                                      |

| $X_b$                           | - | The $b^{th}$ bit in the stochastic number (bit-stream) $X$                 |

| $X_{b,i}$                       | _ | $b^{th}$ bit of SN of probability $x_i$ ( $i^{th}$ element in vector $x$ ) |

| ٨                               | _ | AND logic operator                                                         |

| V                               | - | OR logic operator                                                          |

$\oplus$  – XOR logic operator

# LIST OF APPENDICES

| APPENDIX   | TITLE                                                 | PAGE |

|------------|-------------------------------------------------------|------|

| Appendix A | MATLAB Deep Learning Toolbox                          | 235  |

| Appendix B | SC system design case study of image processing — An  |      |

|            | illustration of the application of proposed framework | 241  |

| Appendix C | Backward Function Derivation                          | 251  |

| Appendix D | MATLAB functions code                                 | 259  |

| Appendix E | High-Level Synthesis Code                             | 263  |

# **CHAPTER 1**

## INTRODUCTION

## 1.1 Background of research

Stochastic Computing (SC) is an alternative paradigm of computation that considers data as probabilities. Low-area/power cost and error tolerance are some of SC advantages. However, many challenges should be overcome before SC becomes widespread [1]. In this thesis, many SC challenges have been addressed.

The case study used to show the applicability of SC paradigm is object classification using convolutional neural network (CNN). CNN is the state-of-the-art algorithm for object recognition applications. Designing an Field Programmable Gate Array (FPGA) accelerator based on the conventional binary arithmetic calculations for deep CNNs incurs high hardware cost and energy-efficiency achievable is low. Since deep CNNs are both compute and memory intensive, it is impractical to use deep CNN accelerators in embedded system platforms that typically has limited area and power budget. Therefore, novel alternative computing paradigm such as SC is urgently needed to overcome this hurdle. In this thesis, a low-area and energy-efficient CNN hardware is designed using a High-Level Synthesis (HLS) tool targeting FPGA.

#### 1.1.1 Stochastic computing

Stochastic computing is a computing paradigm, which was first introduced by Gaines [2] in the 1960s, as an alternative to the conventional binary-encoded deterministic computing technique. From hereon in this thesis, for convenience, the abbreviation, BE, is used to refer to this conventional binary-encoded deterministic computing method. In SC, data being processed are represented by bit-streams (referred to as stochastic numbers (SN)), and the value of the data is encoded as the probability of 1s appearing in the bit-stream. For example, the data bit-stream X = 1001 encodes the value of 0.5 since the probability of 1s appearing in X is 0.5 (=2/4); there are two 1s and the bit-stream is 4 bits long.

The main advantage of an SC element is its low hardware cost and posses a high tolerance for soft errors. SC elements of multiplication, addition, and subtraction can be performed using simple logic functions. For example, as shown in Figure 1.1, the SC multiplier is an AND gate. Referring to Figure 1.1, the SNs *X* and *Y* are multiplied to obtain the SN *Z*. *X* is 11010111, hence  $p_x = \frac{6}{8}$ . *Y* is 11001010, hence  $p_y = \frac{4}{8}$ . Therefore, the output of the AND gate is Z = 11000010, which means  $p_z = \frac{3}{8}$ . Now,  $\frac{6}{8} \times \frac{4}{8} = \frac{3}{8}$ ; therefore, this is a multiplication operation in SC domain.

Today there is renewed interest in SC for applications in mobile and embedded devices that usually demand error-tolerant solutions with low area and low power. Consequently, in recent years, there have been more active research conducted to adopt SC in a wide range of embedded solutions for image processing [3], neural networks [4], digital filters [5], and CNNs [6, 7].

Figure 1.1: Using AND gate to perform SC multiplication

However, SC has significant drawbacks that have to be addressed before it can be viable for application in designing complex practical circuits [1]. One fundamental weakness is that an SC implementation can have a long latency arising from long input bit-streams. Data precision depends on bit-stream length; hence, higher precision requires a longer bit-stream. The crucial second drawback of SC is due to the fact that, unlike BE computation, SC operations (which are based on random numbers) do not necessarily yield consistent results, giving rise to the issue of accuracy. Moreover, the SC circuit might lose the low-area advantage when many stochastic number generators (SNGs) are required to generate uncorrelated bit-streams. SNGs are complex circuits and can account for as much as 80% of the total circuit cost [8].

Aside from quantization errors, the correlation between SNs is also a source of inaccuracy in SC circuits. To operate correctly, some SC circuits require uncorrelated data inputs; others require correlated inputs. Hence, the inaccuracies due to correlation arise because of over-correlated operands in the former case, and in the latter case, because of operands that are not sufficiently correlated. Research work in [9] has shown that circuits that exploit correlation can result in improved accuracy in SC-based designs. It also showed that, by exploiting correlation, further gains can be made in area and delay reductions.

Previous works on utilizing correlation in SC designs were limited to the design of basic circuits or functional units, such as an edge detection filter in [10]. Typically, a large complex system, such as CNN, consists of massive amount of successive computations. For example, CNN consists of a series of layers that include convolutions, activation functions, and pooling. Such a system could not be realized previously (by exploiting correlation), because the SC-based functional units induces the correlation. Consequently, the correlation between SNs after each computation is reduced or lost, resulting in significant errors. To prevent these errors from occurring, the correlation has to be maintained end-to-end across the complete system. One may think that there is an on-the-fly solution. The designer simply regenerates the SNs by inserting conversion circuits whenever inputs have to be correlated to restore any lost correlation. However, this solution is infeasible since it introduces long conversion latency and significantly increases area cost.

#### **1.1.2** Convolutional neural network

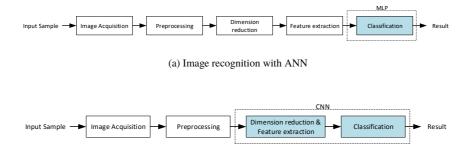

Deep learning has emerged as a new area of machine learning research, which enables a system to automatically learn complex information and extract representations at multiple levels of abstraction. CNN is recognized as one of the most promising types of artificial neural networks (ANNs) taking advantage of deep learning and has become the dominant approach for almost all recognition and detection tasks [11]. Originally inspired by biological processes, CNN is a special case of feed-forward ANN, which requires minimal preprocessing, and combines the feature extraction and classification tasks in one trainable block as shown in Figure 1.2. In CNN, the number of trainable parameters (weights) are reduced significantly because the weights are shared by some neurons. Recently, various CNNs have been used in image and video recognition tasks and have been successfully applied to computer vision and machine learning applications such as object recognition [12, 13], face recognition [14, 15], handwritten character and digit recognition [16, 17].

(b) Image recognition with CNN combine dimension reduction, feature extraction, and classification processes

Figure 1.2: Processes covered by ANN and CNN in a recognition system