## This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Zhou, Wenzhi

Title:

Reflected wave phenomenon in inverter-fed machines with fast-switching (high dv/dt) wide bandgap power converters

causes, consequences and solutions

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

Take down policy Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

Your contact details

Bibliographic details for the item, including a URL

An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Reflected Wave Phenomenon in Inverter-fed Machines with Fast-Switching (high dv/dt) Wide Bandgap Power Converters: Causes, Consequences and Solutions

Wenzhi Zhou

A thesis submitted to the University of Bristol in accordance with the requirements of the degree of Doctor of Philosophy in Electrical Engineering.

Department of Electrical and Electronic Engineering UNIVERSITY OF BRISTOL Merchant Venturers Building Woodland Road Bristol BS8 1UB UNITED KINGDOM

June 2022

### Abstract

Power density, efficiency and reliability are key design drivers and central concerns for adjustable speed drive systems in a plethora of applications including industrial automation and robotics, and transportation systems. The commercially available of Wide Bandgap (WBG) power semiconductors such as Silicon Carbide (SiC) MOSFETs with extremely fast switching speed are pushing the boundaries of power converter performance to meet the aggressive power density and efficiency targets (e.g., 25kW/kg, 99% +) for existing and emerging applications.

However, these steep voltage transients (high dv/dt) of SiC inverters are expected to accelerate the degradation of the connected motor stator winding insulation, which significantly affects the reliability and lifetime of the motor drive system. In a typical SiCbased cable-fed motor drive system, the fast-fronted Pulse-Width Modulation (PWM) voltage pulses generated by the SiC inverter make cables act like transmission lines, with waves travelling along the cables back and forth. Since the characteristic impedance of the motor is much higher than that of the cable in the motor drive system, the inverter PWM voltage pulses experience reflections at motor terminals, leading to excessive overvoltage oscillations that can be twice the inverter voltage. This phenomenon is known as the reflected wave phenomenon (RWP). The resultant overvoltage stress adversely affects the reliability and lifetime of the motor by accelerating the motor stator winding insulation ageing through the inception of partial discharges, progressively yielding to the degradation of motor winding insulation, while raising the Electromagnetic Interference (EMI) problems.

The aim of this PhD thesis is to investigate the RWP in SiC-based cable-fed motor drive systems and explore the overvoltage mitigation techniques without compromising the benefits of SiC switching devices. The RWP is systematically investigated in both the time domain and frequency domain, providing the foundation for developing the active waveform shaping techniques. The impact of parasitic of SiC switching devices on the motor terminal overvoltage due to the RWP in a three-phase motor drive system is investigated and experimentally verified. Moreover, two active waveform shaping techniques, i.e., the Quasi-Three-Level (Q3L) PWM scheme and the voltage slew-rate (dv/dt) profiling, are proposed to address the motor terminal overvoltage oscillations in SiC-based long cable-fed motor drive systems. The proposed active waveform shaping

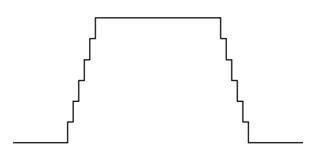

techniques are supported by theoretical analysis and experimental verification. The essence of the overvoltage mitigation mechanism of the proposed active waveform shaping techniques is crystallized in both the time domain and frequency domain. The philosophy used here is addressing the motor terminal overvoltage oscillations at the source by actively mitigating the excitation source for the overvoltage oscillations. The theoretical and experimental results indicate that when the dwell time for the Q3L PWM scheme is set as  $2t_p$  ( $t_p$  is the wave propagation time), the motor terminal overvoltage oscillations can be attenuated since there is no excitation source invoking the overvoltage oscillations. In addition, the proposed Q3L PWM using the SiC module-parallel inverter can extend the switching devices' current capacity. The proposed voltage slew rate (dv/dt) profiling is implemented on the SiC Auxiliary Resonant Commutated Pole Inverter (ARCPI) to verify its effectiveness. The theoretical analysis and experimental results show that the ARCPI can entirely mitigate the motor terminal overvoltage oscillations when the rise and fall times of the PWM voltage pulses are shaped as  $4t_p$ . Also, the voltage slew rate profiling inherits the advantages of the soft-switching inverter including high power efficiency and EMI performance.

Dedicated to my parents

### Acknowledgements

I would like to thank and acknowledge the people who contributed to this research both directly and indirectly.

First and foremost, I would like to thank my supervisors, Prof. Xibo Yuan and Prof. Phil Mellor for their invaluable advice, guidance, and timely technical input. I could not have completed this work without their unwavering support. I greatly appreciate their contribution.

I would like to acknowledgement my PhD viva committee members: Prof. Andrew Forsyth and Dr Christian Klumpner, and Dr David Drury for their support, comments, and suggestions.

I would like to thank Dr. Mohamed Diab for his constant support, and technical discussion throughout the PhD work.

I would also like to thank the UK Research and Innovation (UKRI) and the University of Bristol for funding my PhD project.

I am grateful to all my colleagues and friends in the EEMG for their support and help, and to all my friends in Bristol whose help got me to the end of this arduous but enriching journey.

Special thanks are owed to my parents, my sister and my partner Pangya for their steadfast support, encouragement, and kindness.

### Declaration

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

SIGNED: ..... DATE:....

### Memorandum

The accompanying thesis "Reflected Wave Phenomenon in Inverter-fed Machines with Fast-Switching (high dv/dt) Converters: Causes, Consequences and Solutions" is based on work carried out by the author in the Department of Electrical and Electronic Engineering of the University of Bristol.

The main contributions claimed by the author are as follows:

- 1. Investigated the reflected wave phenomenon in SiC-based cable-fed motor drive system.

- Crystallized the underlying cause of motor terminal overvoltage oscillations in both the time domain and frequency domain, providing foundations for developing overvoltage mitigation techniques through active waveform shaping.

- 2) Investigated the impact of switching devices' parasitic on motor terminal overvoltage. Systematically analysed and experimentally verified the switching commutation processes for a three-phase SiC-based cable-fed motor drive system, considering the impacts of parasitic elements of the switching devices and load current during the switching transitions.

2. Addressed the motor terminal overvoltage oscillations at the source by using the active waveform shaping technique, i.e., the quasi-three-level (Q3L) PWM scheme.

- Revealed the essence of the overvoltage mitigation mechanism of the Q3L PWM in both the time domain and frequency domain.

- 2) Investigated the impact of the parasitic of switching devices of the Q3L PWM Ttype inverter on the mitigation of motor terminal overvoltage oscillations.

- 3) Proposed the Q3L PWM using the module-parallel inverter to mitigate the motor terminal overvoltage and extend the switching devices' current capacity.

- 4) Experimental implemented the Q3L PWM scheme on a SiC-based T-type inverter and a SiC-based module-parallel inverter, respectively.

3. Addressed the motor terminal overvoltage oscillations at the source by using the active waveform shaping technique, i.e., soft-switching voltage slew rate (dv/dt) profiling, without sacrificing the benefits of SiC devices.

- 1) Proposed and derived the optimum rise and fall times of the PWM voltage pulses for entirely mitigating the motor terminal overvoltage.

- 2) Revealed the essence of the overvoltage mitigation mechanism of the voltage slew rate profiling in both the time domain and frequency domain.

- Experimental implemented the voltage slew rate profiling concept with a softswitching inverter, i.e., the SiC Auxiliary Resonant Commutated Pole Inverter (ARCPI).

### Publications

#### **Journal Articles**

- W. Zhou, M. Diab, X. Yuan and C. Wei, "Mitigation of Motor Overvoltage in SiC-Based Drives using Soft-Switching Voltage Slew-Rate (*dv/dt*) Profiling," *IEEE Transactions on Power Electronics*, vol. 37, no. 8, pp. 9612-9628, Aug. 2022, doi: 10.1109/TPEL.2022.3157395.

- W. Zhou, M. Diab and X. Yuan, "Impact of Parasitic and Load Current on the Attenuation of Motor Terminal Overvoltage in SiC-Based Drives," *IEEE Transactions on Industry Applications*, vol. 58, no. 2, pp. 2229-2241, March-April 2022, doi: 10.1109/TIA.2022.3141703.

- W. Zhou and X. Yuan, "Experimental Evaluation of SiC MOSFETs in Comparison to Si IGBTs in a Soft-Switching Converter," *IEEE Transactions on Industry Applications*, vol. 56, no. 5, pp. 5108-5118, Sept.-Oct. 2020, doi: 10.1109/TIA.2020.2999440.

- M. Diab, W. Zhou, C. Emersic, X. Yuan and I. Cotton, "Impact of PWM Voltage Waveforms on Magnet Wire Insulation Partial Discharge in SiC-Based Motor Drives," *IEEE Access*, vol. 9, pp. 156599-156612, 2021, doi: 10.1109/ACCESS.2021.3129266.

- X. Yuan, J. Wang, I. Laird and W. Zhou, "Wide-Bandgap Device Enabled Multilevel Converters With Simplified Structures and Capacitor Voltage Balancing Capability," *IEEE Open Journal of Power Electronics*, vol. 2, pp. 414-423, 2021, doi: 10.1109/OJPEL.2021.3094713.

#### **Conference Proceedings**

- W. Zhou, M. Diab and X. Yuan, "Impact of Parasitics and Load Current on the Switching Transient Time and Motor Terminal Overvoltage in SiC-Based Drives," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 225-232, doi: 10.1109/ECCE44975.2020.9235417.

- 2. **W. Zhou**, M. Diab and X. Yuan, "Mitigation of Motor Overvoltage in SiC-Device-Based Drives using a Soft-Switching Inverter," in *2020 IEEE Energy Conversion*

*Congress and Exposition (ECCE)*, 2020, pp. 662-669, doi: 10.1109/ECCE44975.2020.9236099.

- W. Zhou, X. Yuan and I. Laird, "Performance Comparison of the Auxiliary Resonant Commutated Pole Inverter (ARCPI) using SiC MOSFETs or Si IGBTs," in 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 1981-1987, doi: 10.1109/ECCE.2019.8912876.

- W. Zhou, X. Yuan and I. Laird, "Elimination of Overshoot and Oscillation in the Auxiliary Branch of a SiC Auxiliary Resonant Commutated Pole Inverter (ARCPI)," in 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia), 2019, pp. 1-7, doi: 10.23919/ICPE2019-ECCEAsia42246.2019.8797163.

- M. Diab, W. Zhou and X. Yuan, "Evaluation of Topologies and Active Control Methods for Overvoltage Mitigation in SiC-Based Motor Drives," in 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 4867-4873, doi: 10.1109/ECCE47101.2021.9595730.

- M. Diab, W. Zhou, C. Emersic, X. Yuan and I. Cotton, "Impact of PWM Waveforms on Partial Discharge in SiC-Based Motor Drives," in *IECON 2021 –* 47th Annual Conference of the IEEE Industrial Electronics Society, 2021, pp. 1-7, doi: 10.1109/IECON48115.2021.9589431.

- C. Wei, X. Yuan, W. Zhou and J. Wang, "Derivation of Flying-Type Multilevel Converter Topologies with a Voltage-Level Extension Method," in 2021 IEEE 12th Energy Conversion Congress & Exposition-Asia (ECCE-Asia), 2021, pp. 688-695, doi: 10.1109/ECCE-Asia49820.2021.9479046.

- J. Wang, I. Laird, X. Yuan and W. Zhou, "A 1.2 kV 100 kW Four-level ANPC Inverter with SiC Power Modules and Capacitor Voltage Balance for EV Traction Applications," in 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 5202-5209, doi: 10.1109/ECCE47101.2021.9595038.

- 9. J. Wang, C. Wei, **W. Zhou** and X. Yuan, "Capacitor Voltage Balancing Algorithm with Redundant Level Modulation for a Five Level Converter with Reduced Device Count," in 2020 IEEE 9th International Power Electronics and Motion

Control Conference (IPEMC2020-ECCE Asia), 2020, pp. 1758-1764, doi: 10.1109/IPEMC-ECCEAsia48364.2020.9367875.

X. Yuan, C. Wei, W. Zhou and G. Wang, "A Novel Five-Level Converter for Medium-Voltage Power Conversion Systems," in *IECON 2019 - 45th Annual Conference of the IEEE Industrial Electronics Society*, 2019, pp. 4953-4958, doi: 10.1109/IECON.2019.8927260.

#### **Other Publications**

- 1. **W. Zhou**, M. Diab and X. Yuan, "Comparison of Motor Neutral Point Overvoltage Oscillation in SiC-Based Adjustable Speed Drives using Two-Level and Three-Level Inverters," in 2022 IEEE Energy Conversion Congress and Exposition (ECCE), 2022. (Accepted)

- W. Zhou, M. Diab and X. Yuan, "Mitigation of Motor Overvoltage and Extending Switching Devices' Current Capacity with Module Parallel Power Converter in SiC-Based Adjustable Speed Drives," (in preparation)

- 3. **W. Zhou**, M. Diab and X. Yuan, "Evaluation of Active Control Methods for Mitigation of Antiresonance Overvoltage Phenomenon in SiC-Based Motor Drives," (in preparation)

## Table of Contents

| Abstract                                                                                                 | i      |

|----------------------------------------------------------------------------------------------------------|--------|

| Acknowledgements                                                                                         | v      |

| Declaration                                                                                              | vii    |

| Memorandum                                                                                               | ix     |

| Publications                                                                                             | xi     |

| Table of Contents                                                                                        |        |

| List of Figures                                                                                          |        |

| List of Tables                                                                                           |        |

|                                                                                                          |        |

| List of Symbols                                                                                          |        |

| List of Abbreviations and Acronyms                                                                       |        |

| Chapter 1 Introduction<br>1.1 Background and Motivation<br>1.2 Research Objectives<br>1.3 Thesis Outline | 1<br>4 |

| Chapter 2 Literature Review                                                                              | 9      |

| 2.1 Introduction                                                                                         |        |

| 2.2 WBG Semiconductor Power Devices                                                                      |        |

| 2.2.1 Overview                                                                                           |        |

| 2.3 Impact of the Fast-Switching WBG Converter on the Connected N                                        |        |

| Adjustable Speed Drives                                                                                  |        |

| 2.3.1 Uneven Voltage Distribution within Motor Stator Windings                                           |        |

| 2.3.2 Motor Terminal Overvoltage Oscillations                                                            |        |

| 2.3.3 Issues Related to the Overvoltage Stress                                                           |        |

| 2.4 Mitigation of Motor Terminal Overvoltage using Passive Filters                                       |        |

| 2.4.1 Impedance Matching Filter Installed at Motor Terminals                                             |        |

| 2.4.2 L Filter Installed at Inverter Side                                                                |        |

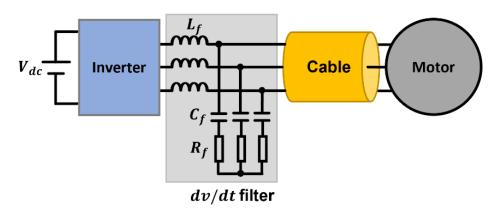

| 2.4.3 Dv/dt Filter Installed at Inverter Side                                                            |        |

| 2.5 Mitigation of Motor Terminal Overvoltage using Active Mitigation Metho<br>2.5.1 Q3L PWM Scheme       |        |

| 2.5.1 Q5D I Will Scheme                                                                                  |        |

| 2.6 Mitigation of Motor Terminal Overvoltage using Other Methods                                         |        |

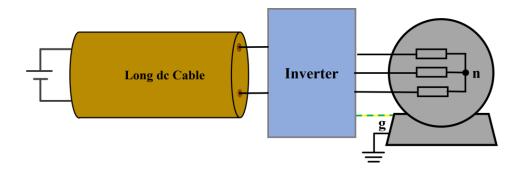

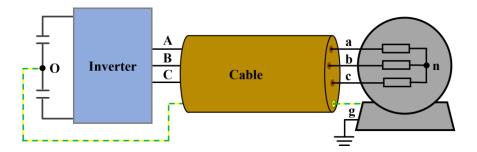

| 2.6.1 Long dc Cable + Integrated Motor                                                                   |        |

| 2.6.2 Multilevel converter                                                                               |        |

| 2.7 Limitations of the Literature and Research Opportunities                                             |        |

| Chapter 3 Modelling of the Reflected Wave Phenomenon                                                     |        |

| 3.1 Introduction                                                                                         |        |

| 3.2 The Adjustable Speed Drive System with Long Cables                                                   |        |

| 3.2.1 Motor Terminal Overvoltage Oscillations (DM & CM)                                                  |        |

| 3.2.2 Motor Neutral Point Overvoltage Oscillations                                                       |        |

| 3.3 Analysis of the Reflected Wave Phenomenon                                                            |        |

| 3.3.1 Analysis in Time Domain<br>3.3.2 Analysis in Frequency Domain                                      |        |

| 5.5.2 Finalysis in Frequency Domain                                                                      |        |

| 3.4 Simulation Study                                                       |          |

|----------------------------------------------------------------------------|----------|

| 3.4.1 Cable Model                                                          |          |

| 3.4.2 Impact of the Rise Time and Cable Length                             |          |

| 3.4.3 Double Pulsing Effects                                               |          |

| 3.5 Conclusion                                                             | 50       |

| Chapter 4 Impact of Parasitic Capacitance of Switching Devices and Load    | Curront  |

| on the Switching Transient and Motor Terminal Overvoltage Oscillations     |          |

| 4.1 Introduction                                                           |          |

| 4.2 Modelling of the Switching Transitions                                 |          |

| 4.2.1 Switching Transitions of SiC MOSFETs in the Half-bridge Circuit      |          |

| 4.2.2 Line Voltages of Three-phase SiC Inverter                            |          |

| 4.3 Experimental Verification.                                             |          |

| 4.4 Conclusion                                                             |          |

|                                                                            |          |

| Chapter 5 Waveform Shaping to Combat the Motor Terminal Overvoltag         |          |

| PWM Scheme                                                                 |          |

| 5.1 Introduction                                                           |          |

| 5.2 The Concept of the Q3L PWM Scheme                                      |          |

| 5.2.1 Analysis in Time Domain                                              |          |

| 5.2.2 Analysis in Frequency Domain                                         |          |

| 5.2.3 The Impact of Dwell Time                                             |          |

| 5.3 Implementation of the Q3L PWM Scheme using a T-type Inverter           |          |

| 5.3.1 T-type Inverter                                                      |          |

| 5.3.2 The Implementation of the Q3L PWM Scheme                             |          |

| 5.3.3 The Impact of Parasitic on the Overvoltage Mitigation                |          |

| 5.3.4 Experimental Results                                                 |          |

| 5.4 Implementation of the Q3L PWM using a Module-parallel Inverter         |          |

| 5.4.1 The Module-parallel Power Inverter                                   |          |

| 5.4.2 The Implementation of the Q3L PWM Scheme                             |          |

| 5.4.3 Experimental Results                                                 |          |

| 5.5 Conclusion                                                             | 101      |

| Chapter 6 Waveform Shaping to Combat the Motor Terminal Overvoltag         | e: Soft- |

| Switching Voltage Slew Rate $(dv/dt)$ Profiling                            | 103      |

| 6.1 Introduction                                                           |          |

| 6.2 The Concept of the Voltage Slew Rate Profiling                         | 104      |

| 6.2.1 Analysis in Time Domain                                              | 104      |

| 6.2.2 Analysis in Frequency Domain                                         | 108      |

| 6.3 Simulation Study                                                       | 110      |

| 6.4 Implementation of the Voltage Slew Rate Profiling with the Auxiliary H | Resonant |

| Commutated Pole Inverter                                                   |          |

| 6.4.1 Principle of Operations                                              | 113      |

| 6.4.2 The Control of the ARCPI                                             | 118      |

| 6.4.3 Parameters Design                                                    |          |

| 6.5 Experimental Verification                                              |          |

| 6.5.1 Experimental Set-up                                                  |          |

| 6.5.2 Experimental Results                                                 |          |

| 6.6 Conclusion                                                             |          |

|                                                                            |          |

| Chapter 7 Conclusion and Potential Future Work                             |          |

| 7.1 Thesis Summary                                                         |          |

| 7.2 Conclusions                                                            |          |

| 7.3 Future Work                                                            | 142      |

| 7.3.1 Evaluation of Waveform Shaping Techniques on Motor Stator Win         | ding Voltage |

|-----------------------------------------------------------------------------|--------------|

| Distribution                                                                | 142          |

| 7.3.2 Mitigation of Motor Neutral Point Overvoltage Oscillations            | 143          |

| 7.3.3 Evaluation of Partial Discharge Activity                              | 143          |

| References                                                                  |              |

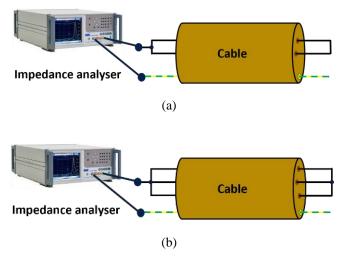

| Appendix 1 Cable Parameter Measurement Method                               | 157          |

| A1.1 Cable per Meter Capacitance ( <i>Cc</i> ) and Inductance ( <i>Lc</i> ) | 157          |

| A1.2 Wave Propagation Time Calculation                                      |              |

## List of Figures

| Figure 1.1 A two-level three-phase VSI                                                         |

|------------------------------------------------------------------------------------------------|

| Figure 1.2 Voltage and current waveform of the switching device in a VSI during the            |

| switching transitions [23]                                                                     |

| Figure 1.3 Voltages measured at the inverter side $V_{inv}$ and motor terminals $V_m$ when the |

| motor is supplied by the fast-switching SiC inverter in a cable-fed motor drive system [33].   |

| Figure 2.1 Development of power electronics and power electronics technology [50], [51].       |

| Figure 2.2 Comparison of the voltage and current waveform at the turn-OFF transient of         |

| SiC, Si-SiC and Si measured in a DPT experiment. The dc-link voltage is 600V and load          |

| current is 10A. All-Si represents Si IGBT and Si diode (Infineon IKW15T120, "IGBT3"            |

| and "EmCon HE" device generations), Si-SiC represents Si IGBT (IKW15T120) and SiC              |

| Schottky diode (SemiSouth SDA10S120) combination, All-SiC represents SiC MOSFET                |

| (Cree CMF20120D) and SiC Schottky diode (SemiSouth SDA10S120) combination [78].                |

|                                                                                                |

| Figure 2.3 Efficiency comparison of the power converter using Si IGBT and SiC MOSFET           |

| at different switching frequency [81]11                                                        |

| Figure 2.4 SiC-based traction inverter developed by Mitsubishia in 2013 [91]                   |

| Figure 2.5 Inverter developed by Toyota for use in PCU in 2014 [92]                            |

| Figure 2.6 SiC Inverter developed by Tesla in 2018 [93]13                                      |

| Figure 2.7 John Deere 200 kW inverter prototypes [96]                                          |

| Figure 2.8 The main challenges of the high $dv/dt$ on motors in WBG-based motor drive          |

| systems                                                                                        |

| Figure 2.9 Simulation results of the coil-to-core voltage distribution when the motor is       |

| feed by high <i>dv/dt</i> voltage, the dc-link voltage is 560 V [105]16                        |

| Figure 2.10 Experimental measured voltage distribution within winding turns of first coil      |

| of phase A winding when the motor is supplied by a two-level SiC power converter through       |

| 70-feet long cable. [108]                                                                      |

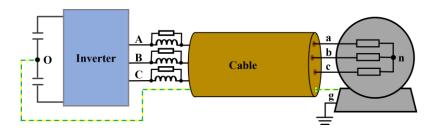

| Figure 2.11 A typical WBG-based long cable-fed adjust speed drive system. The dotted           |

| yellow-green line represents the earth wire connecting the converter and the motor case.       |

|                                                                                                |

| Figure 2.12 Motor overvoltage with the cable length and rise time [114]                        |

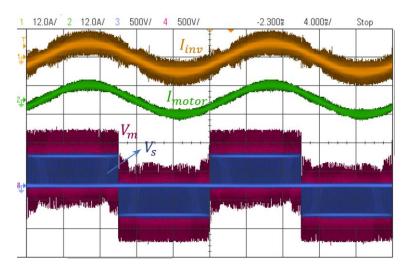

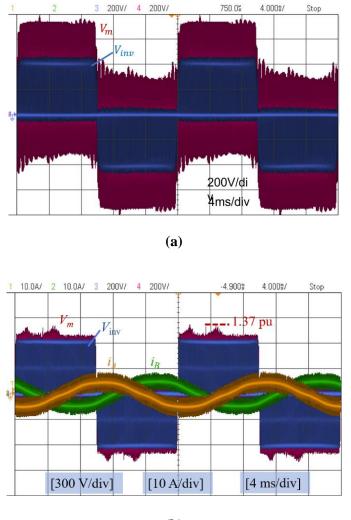

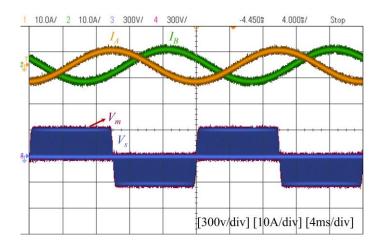

| Figure 2.13 Voltage and current measured in a SiC-based 10m long cable-fed motor drive               |

|------------------------------------------------------------------------------------------------------|

| system for two fundamental cycles, $I_{inv}$ and $V_s$ are the current and voltage measured the      |

| inverter side, $I_{motor}$ and $V_m$ are the current and voltage measured the motor terminals. The   |

| dc-link voltage is 500V, voltage: 500V/div, current: 12A/div, time: 4ms/div18                        |

| Figure 2.14 the zoomed-in view of the voltage and current measured in a SiC-based 10m                |

| long cable-fed motor drive system at switching transient, $I_{inv}$ and $V_s$ are the current and    |

| voltage measured the inverter side, $I_{motor}$ and $V_m$ are the current and voltage measured the   |

| motor terminals. The dc-link voltage is 500V, voltage: 300V/div, current: 5A/div, time:              |

| 0.5µs/div19                                                                                          |

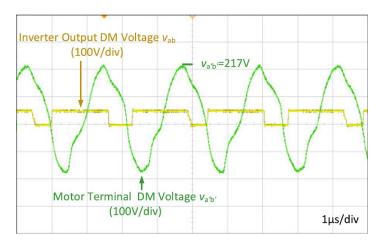

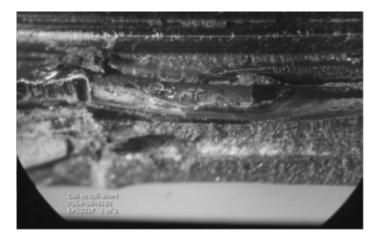

| Figure 2.15 Motor terminal voltage measured at different switching frequency in a SiC-               |

| based 70m long cable-fed motor drive system [30]                                                     |

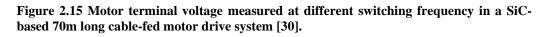

| Figure 2.16 PD activity in motor stator windings [106]21                                             |

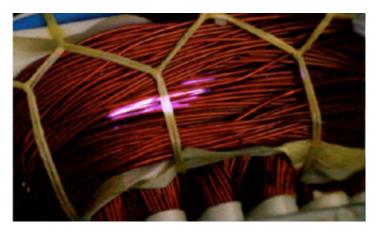

| Figure 2.17 An example of the insulation breakdown of motor stator windings [107]21                  |

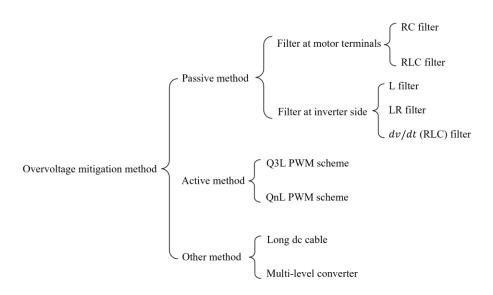

| Figure 2.18 Summaries of the main motor terminal overvoltage mitigation methods22                    |

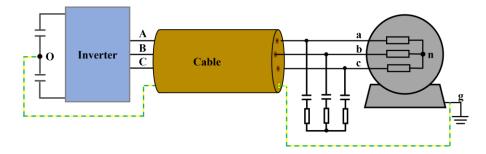

| Figure 2.19 RC filter installed at the motor terminals in cable-fed motor drive system [126].        |

|                                                                                                      |

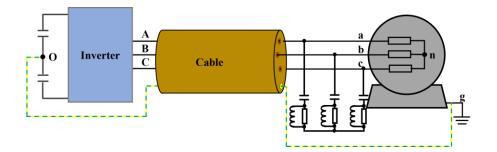

| Figure 2.20 RLC filter installed at the motor terminals in long cable-fed motor drives [126].        |

|                                                                                                      |

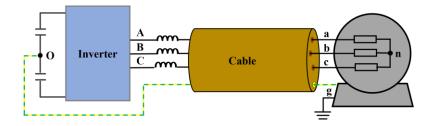

| Figure 2.21 L filter installed at the inverter side in long cable-fed motor drives [126]25           |

| Figure 2.22 LR filter installed at the inverter side in long cable-fed motor drives [131]26          |

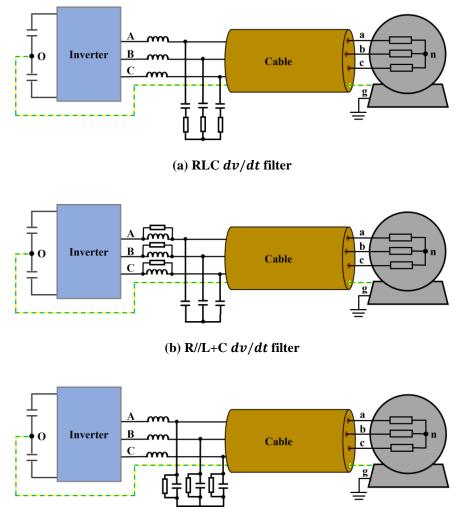

| Figure 2.23 RLC $dv/dt$ filter installed at the inverter side in long cable-fed motor drives         |

| [126]                                                                                                |

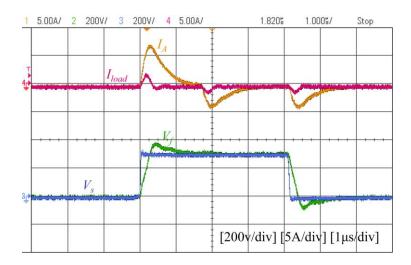

| Figure 2.24 The inverter output voltage $V_s$ and the filter output voltage $V_f$ , the load current |

| $I_{load}$ and the inverter output current $I_A$ measured in the inverter + $dv/dt$ filter [33]27    |

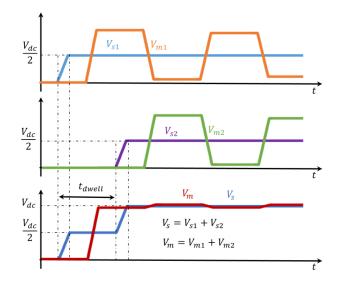

| Figure 2.25 Q3L PWM Scheme                                                                           |

| Figure 2.26 Three-phase T-type inverter                                                              |

| Figure 2.27 Single-phase inverter for the Q3L PWM [134]                                              |

| Figure 2.28 Q3L PWM generation in the single-phase inverter [134]                                    |

| Figure 2.29 Open-winding motor for the Q3L PWM [137]                                                 |

|                                                                                                      |

| Figure 2.30 ARWC for Q3L PWM [139]                                                                   |

|                                                                                                      |

| Figure 2.30 ARWC for Q3L PWM [139]                                                                   |

| Figure 2.30 ARWC for Q3L PWM [139]                                                                   |

| Figure 2.35 Motor terminal overvoltage when the motor is supplied by a three-level SiC               |

|------------------------------------------------------------------------------------------------------|

| inverter [32]                                                                                        |

| Figure 3.1 A typical WBG-based long cable-fed adjust speed drive system                              |

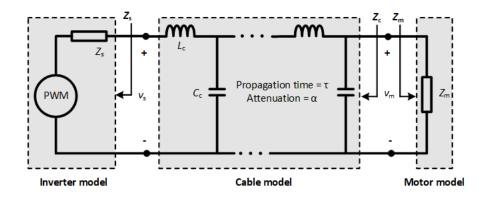

| Figure 3.2 Equivalent differential mode circuit of the long cable-fed motor drive system.            |

|                                                                                                      |

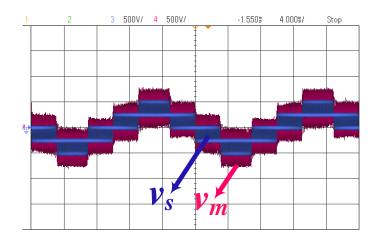

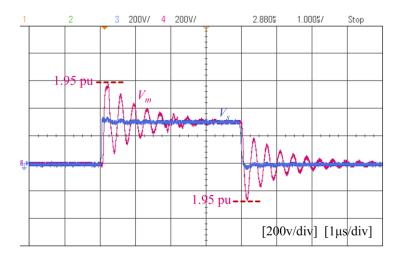

| Figure 3.3 Experimental measured inverter line voltage $V_s$ and motor terminal line volage          |

| $V_m$ in SiC-based long cable-fed motor drive system. dc-link voltage: 300V; Cable: 12m              |

| long, 12 AWG, PVC cable; SiC MOSFET: Wolfspeed C2M0040120D; Motor: 3-phase 4-                        |

| pole 2.2kW induction motor                                                                           |

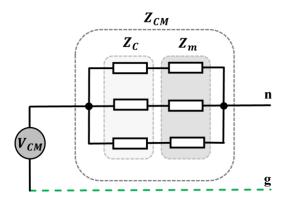

| Figure 3.4 The equivalent CM circuit of the motor drive system                                       |

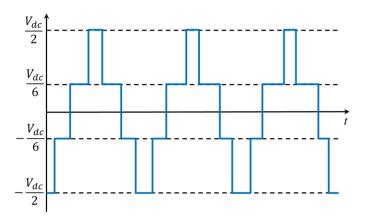

| Figure 3.5 The CM voltage waveform of a three-phase 2L inverter modulated under                      |

| conventional PWM                                                                                     |

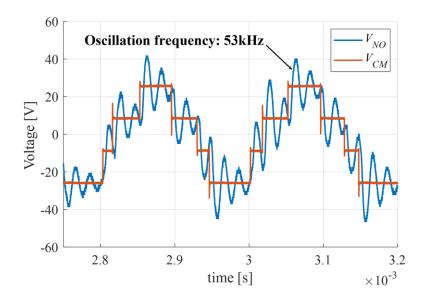

| Figure 3.6 The inverter CM voltage $V_{CM}$ and motor neutral point voltage $V_{NO}$ when the        |

| motor is supplied by a three-phase two-level inverter at modulation index 0.2, switching             |

| frequency 20kHz, and dc-link voltage 50V. Cable: 12.5m long, four-core unshielded 13                 |

| AWG PVC cable; SiC MOSFET: Wolfspeed C2M0040120D; Motor: 3-phase 4-pole                              |

| 2.2kW induction motor                                                                                |

| Figure 3.7 A bounced diagram for the reflected wave phenomenon in the long cable-fed                 |

| motor drive system                                                                                   |

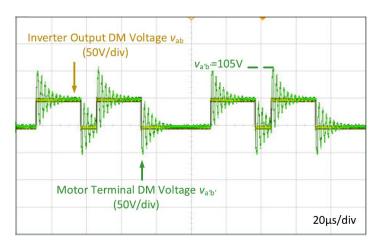

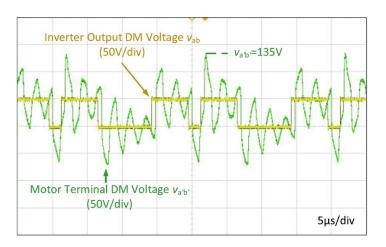

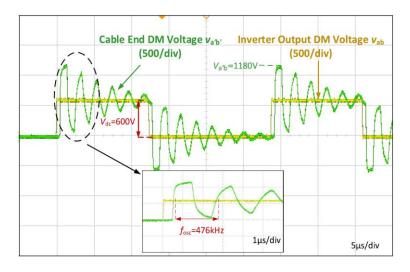

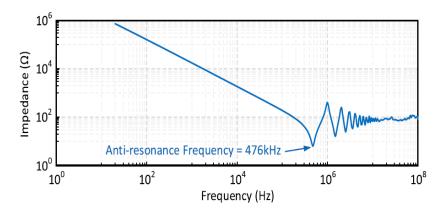

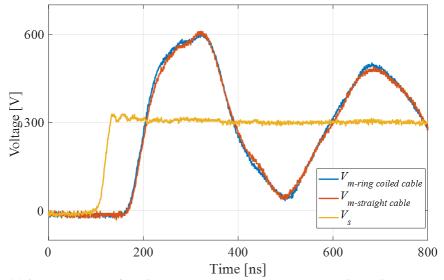

| Figure 3.8 Voltages at the inverter side $V_{ab}$ and the cable end $V_{a'b'}$ with a 70m long cable |

| [30]                                                                                                 |

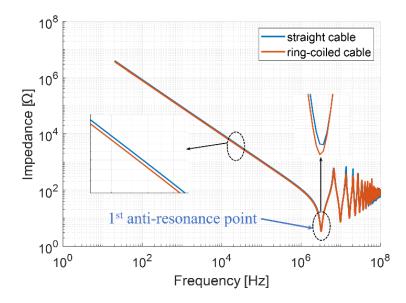

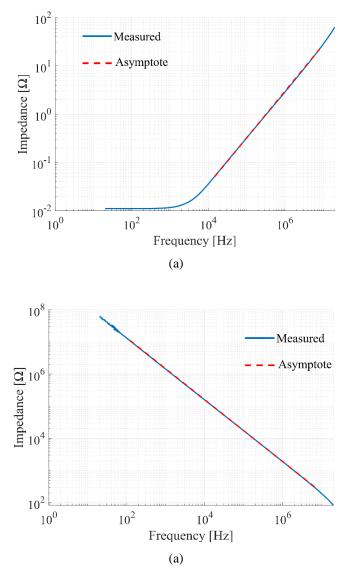

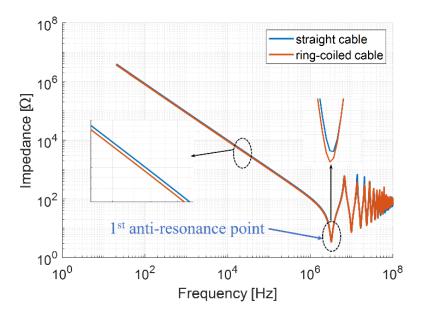

| Figure 3.9 The 70m long cable impedance characteristics [30]46                                       |

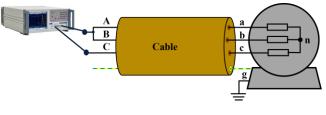

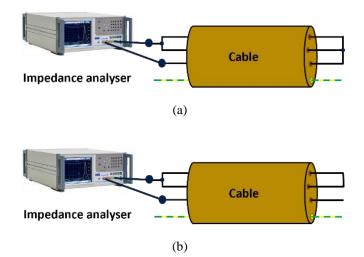

| Figure 3.10 Impedance measurement for the long cable-fed motor drive system                          |

| Figure 3.11 The impedance of ring-coiled cable and straight cable                                    |

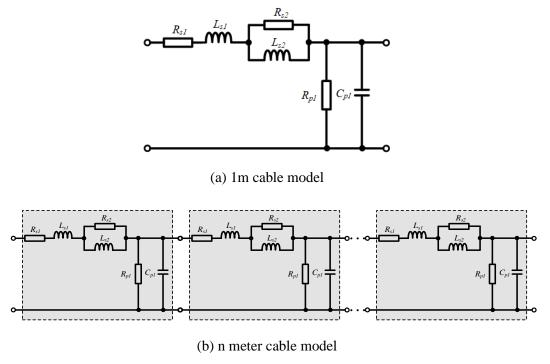

| Figure 3.12 The cable model proposed in [150]                                                        |

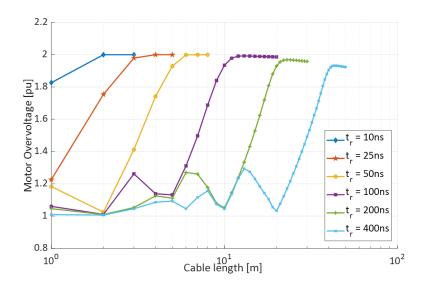

| Figure 3.13 Motor terminal voltage at rise and fall times $t_r$ , and different cable lengths in     |

| the long cable-fed motor drive system                                                                |

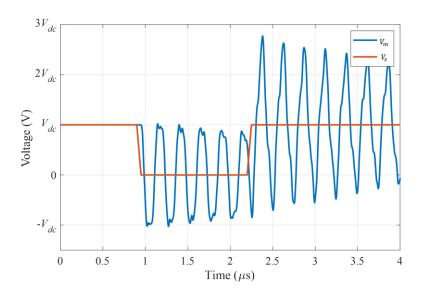

| Figure 3.14 Double pulsing effect in adjustable speed drives                                         |

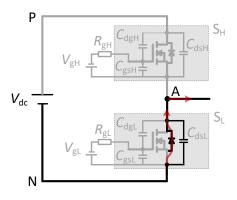

| Figure 4.1 A SiC-based half-bridge circuit                                                           |

| Figure 4.2 Switching transitions of SiC half-bridge inverter                                         |

| Figure 4.3 The output waveform $V_{AN}$ of the half bridge inverter                                  |

| Figure 4.4 Three-phase SiC inverter-fed motor drive system                                           |

| Figure 4.5 Classification of phase currents based on their polarities                                |

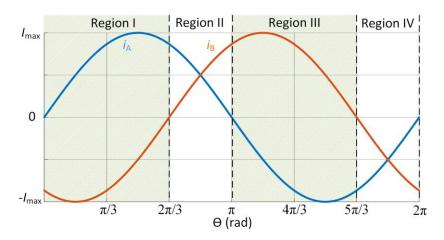

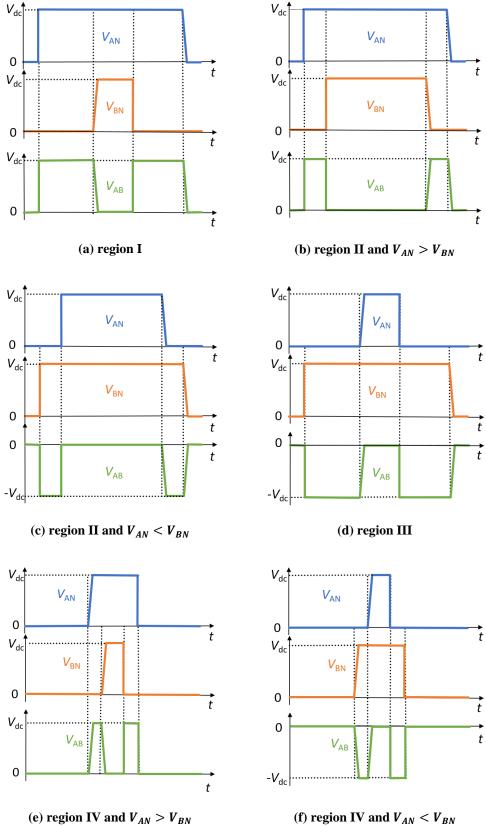

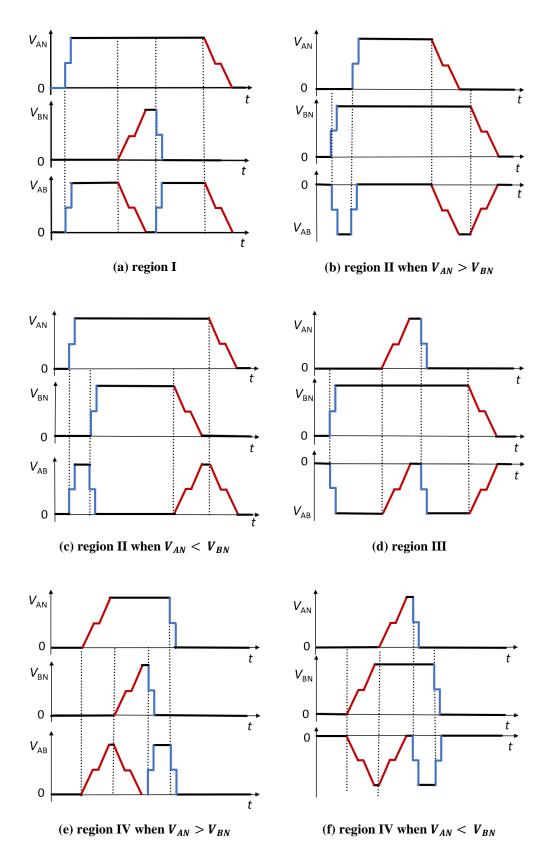

| Figure 4.6 Switching transitions of the line voltage $V_{AB}$ in different region                    |

| Figure 4.7 The three-phase SiC inverter prototype                                                    |

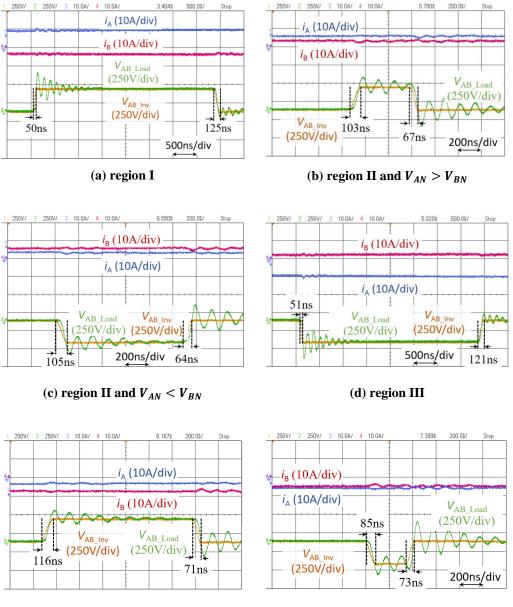

| Figure 4.8 Experimental results of switching transitions of the line voltage $V_{AB}$ of a three-        |

|----------------------------------------------------------------------------------------------------------|

| phase SiC inverter supplying a three-phase load through power cables in different region.                |

|                                                                                                          |

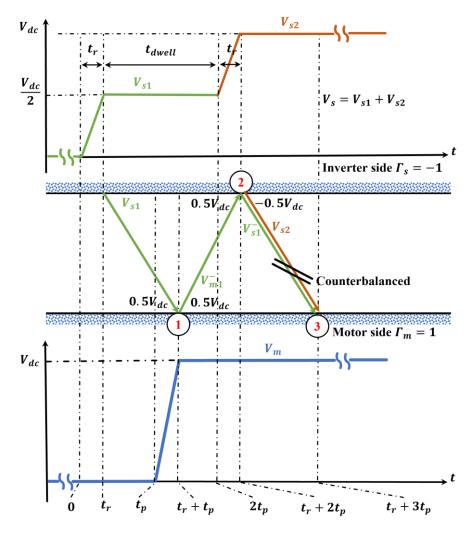

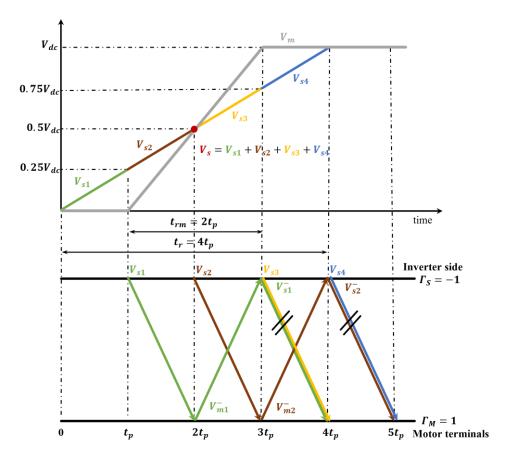

| Figure 5.1 A bounced diagram of the Q3L PWM scheme69                                                     |

| Figure 5.2 Overvoltage mitigation of the Q3L PWM using the superposition principle71                     |

| Figure 5.3 Q3L PWM voltage pulse train72                                                                 |

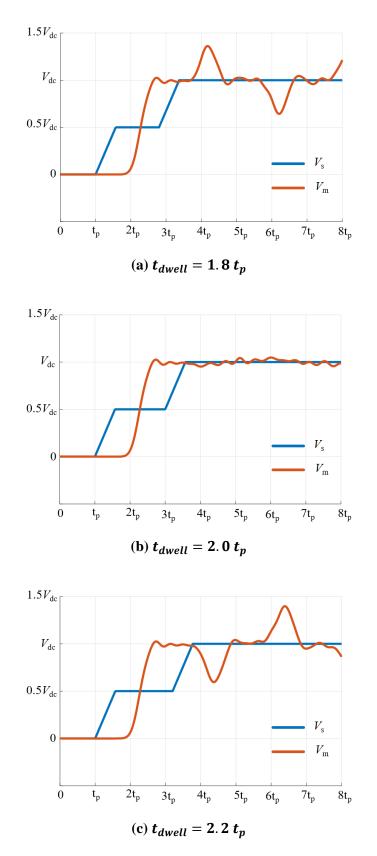

| Figure 5.4 Simulation result of the inverter and motor voltages under the Q3L PWM                        |

| scheme for different dwell time setting75                                                                |

| Figure 5.5 A three-phase SiC T-type inverter76                                                           |

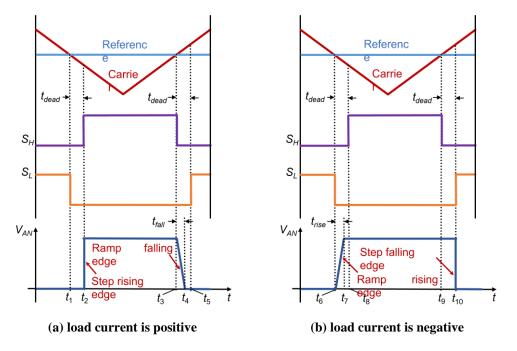

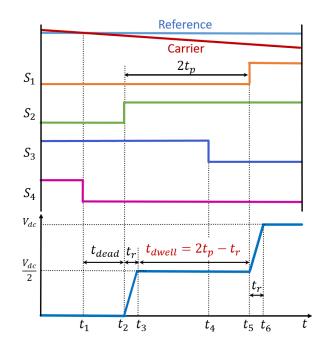

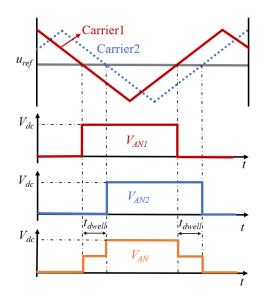

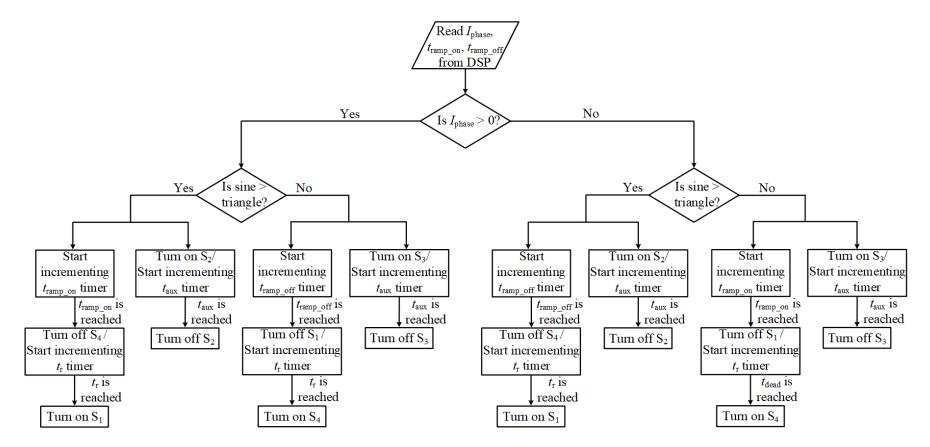

| Figure 5.6 Gate signal generation of Q3L PWM in T-type inverters77                                       |

| Figure 5.7 Gate signals and output voltage of Q3L T-type inverter under different load                   |

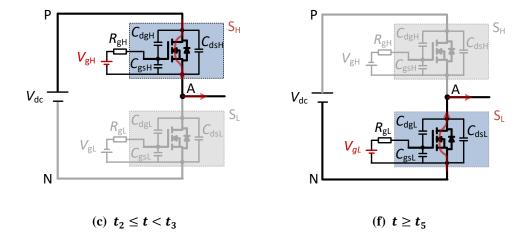

| current polarities                                                                                       |

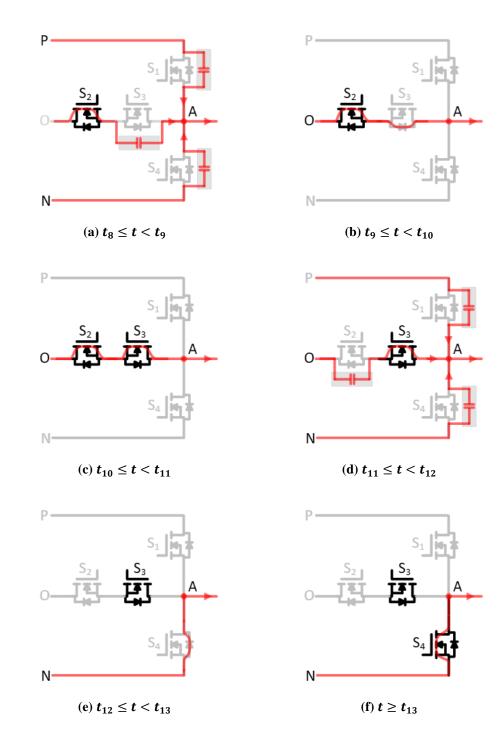

| Figure 5.8 The switching commutation processes for $V_{AN}$ from 0 to $V_{dc}$ when the load             |

| current is positive79                                                                                    |

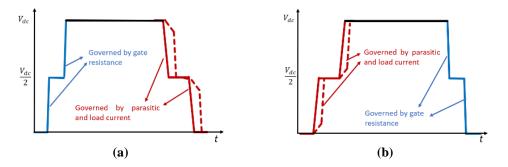

| Figure 5.9 The output voltage during the commutation process for $V_{AN}$ from zero to $V_{dc}$          |

| when the phase current is positive                                                                       |

| Figure 5.10 The commutation processes for $V_{AN}$ from $V_{dc}$ to zero when the load current is        |

| positive                                                                                                 |

| Figure 5.11 The output voltage $V_{AN}$ during the commutation process from $V_{dc}$ to zero85           |

| Figure 5.12 The output voltage of the T-type inverter under Q3L PWM when the load                        |

| current is (a) positive and (b) negative                                                                 |

| Figure 5.13 Switching transitions of the line voltage $V_{AB}$ of T-Type inverter under the Q3L          |

| PWM in different current regions                                                                         |

| Figure 5.14 The experimental setup                                                                       |

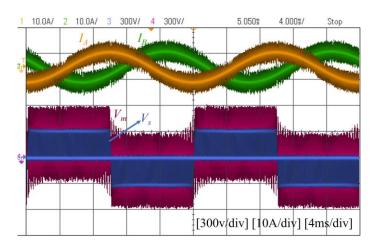

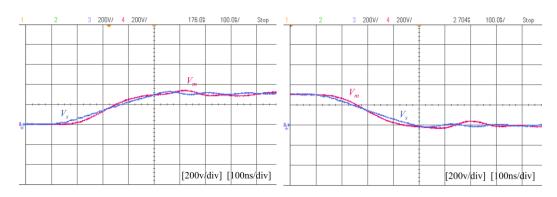

| Figure 5.15 Inverter and motor line voltages under two-level SPWM                                        |

| Figure 5.16 Inverter and motor line voltages under the Q3L PWM                                           |

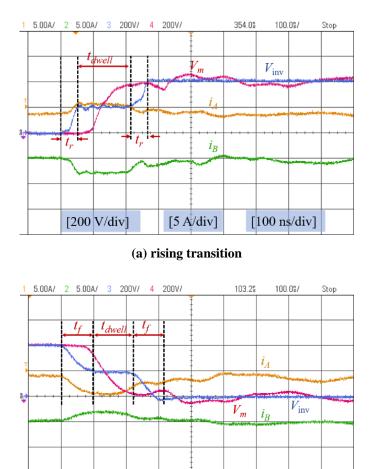

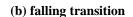

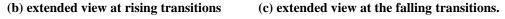

| Figure 5.17 Switching The line voltages at the inverter side Vinv and motor terminals Vm                 |

| in (a) the hard-switching inverter-fed system (b) the Q3L T-type inverter-fed system 90                  |

| Figure 5.18 Phase currents <i>iA</i> and <i>iB</i> , and the line voltages at the inverter side Vinv and |

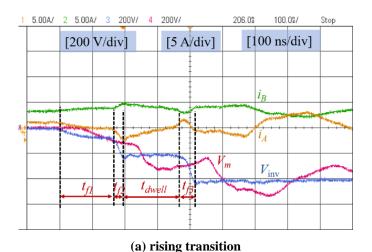

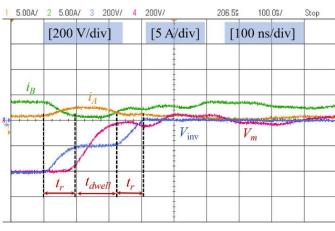

| motor terminals $Vm$ under the Q3L PWM during the switching transitions in region I91                    |

| Figure 5.19 Phase currents $iA$ and $iB$ , and the line voltages at the inverter side $Vinv$ and         |

| motor terminals $Vm$ under the Q3L PWM during the switching transitions in region III.92                 |

| Figure 5.20 Phase currents <i>iA</i> and <i>iB</i> , and the line voltages at the inverter side Vinv and |

| motor terminals $Vm$ under the Q3L PWM during the switching transitions in region II. 93                 |

| inguie 5.21 Thuse currents in and ib, and the fine voltages at the involver side v inv and              |

|---------------------------------------------------------------------------------------------------------|

| motor terminals $Vm$ under the Q3L PWM during the switching transitions in region IV.                   |

|                                                                                                         |

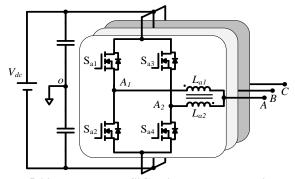

| Figure 5.22 Three-phase SiC bridge-leg parallel inverter                                                |

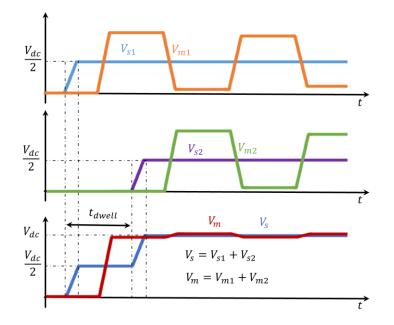

| Figure 5.23 Q3L wave generation using module-parallel inverter                                          |

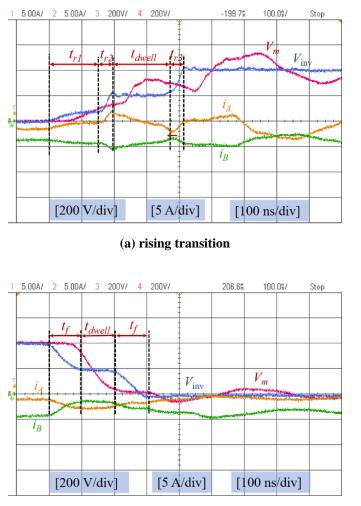

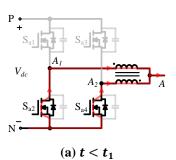

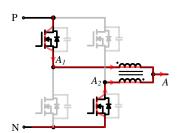

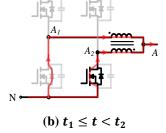

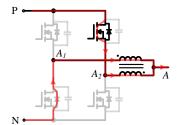

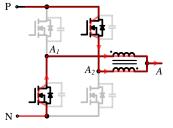

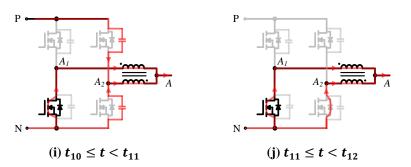

| Figure 5.24 Switching commutation process of the module-parallel power inverter 98                      |

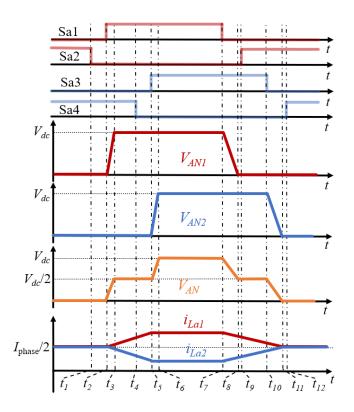

| Figure 5.25 The gate signals, the output voltages (VAN1 and VAN2) and currents (iLa1                    |

| and iLa2) for bridge-legs (A1 and A2), the inverter output voltage during switching                     |

| transitions                                                                                             |

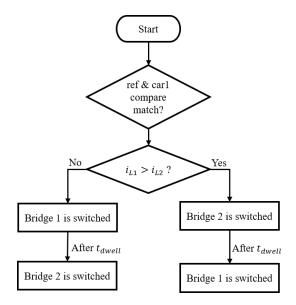

| Figure 5.26 Flow chart for active current control                                                       |

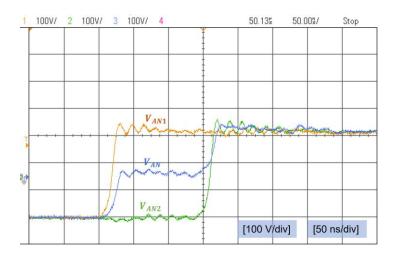

| Figure 5.27 Output voltages of the bridge-legs A1 and A2, and the module-parallel inverter.             |

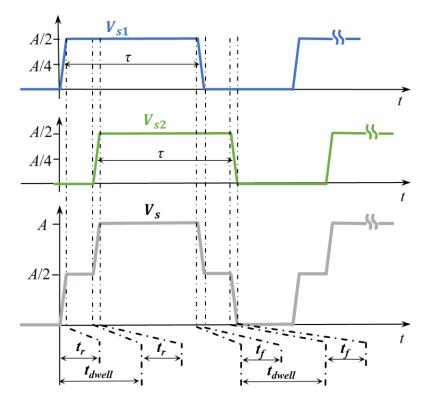

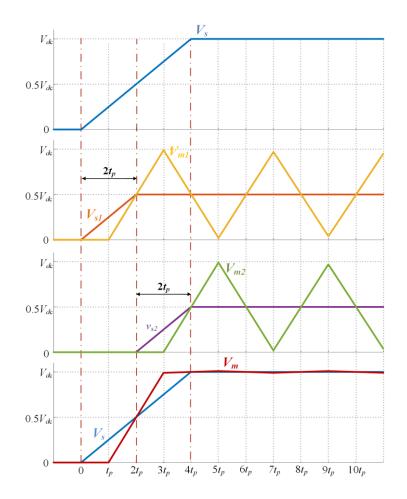

| Figure 6.1 A bounced diagram of the voltage slew rate profiling approach                                |

| Figure 6.2 Overvoltage mitigation mechanism of the voltage slew-rate profiling approach                 |

| in time domain using the superposition principle                                                        |

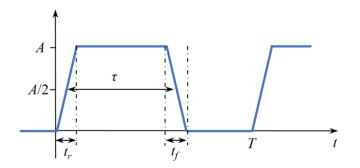

| Figure 6.3 Trapezoidal pulse-train                                                                      |

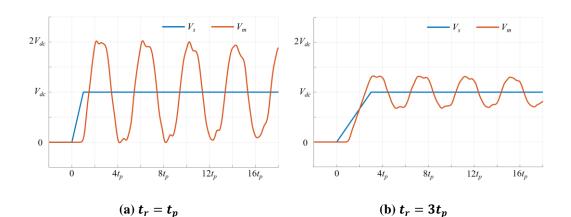

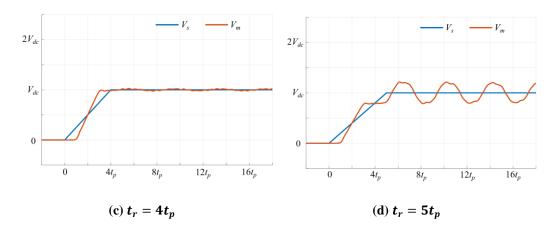

| Figure 6.4 Inverter and motor voltage waveforms at different rise time setting. In order to             |

| emulate the worst case of the drive system, the motor side is regarded as an open circuit.              |

| The cable length $l_c=10$ m, the wave propagation time $t_p = 51$ ns                                    |

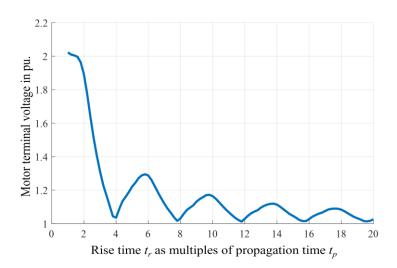

| Figure 6.5 Variation of the maximum motor terminal voltage with the rise time                           |

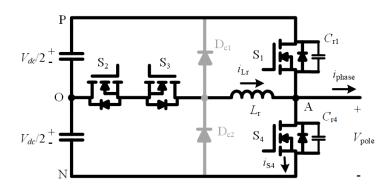

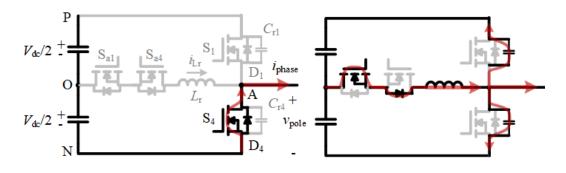

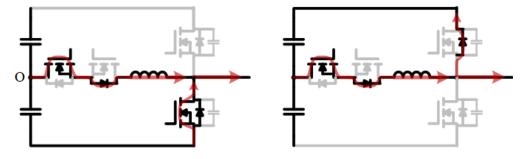

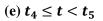

| Figure 6.6 A single-phase SiC-based ARCPI circuit diagram113                                            |

| Figure 6.7 The turn-ON switching commutation process of the ARCPI when the load                         |

| current is positive                                                                                     |

| Figure 6.8 The gate signals, the resonant inductor current $i_{Lr}$ , and the output voltage $V_{pole}$ |

| during the turn-ON commutation process when the load current is positive115                             |

| Figure 6.9 The gate signals, the resonant inductor current $i_{Lr}$ , and the output voltage $V_{pole}$ |

| during the turn-OFF process when the load current is positive                                           |

| Figure 6.10 The trip current for the variable-timing control and fixed-timing control in the            |

| fundament cycle, where $L_r = 2.7 \mu H$ , $C_r = 8.2 nF$ , $V_{dc} = 500 V$                            |

| Figure 6.11 The resonant interval for the variable-timing control and fixed-timing control              |

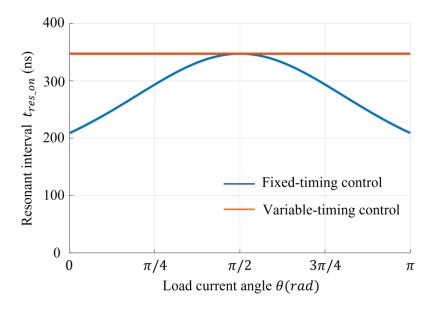

| in the fundament cycle, where $L_r = 2.7 \mu H$ , $C_r = 8.2 nF$ , $V_{dc} = 500 V$                     |

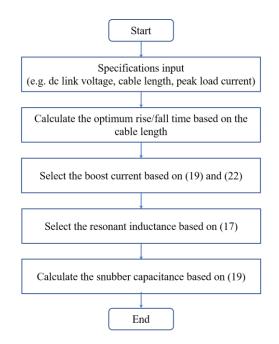

| Figure 6.12 A The flow chart for the ARCPI design                                                       |

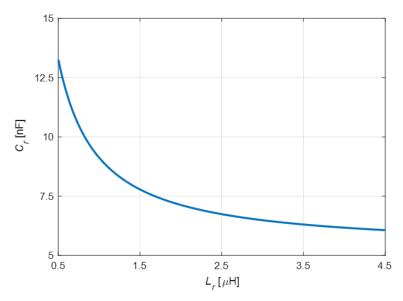

| Figure 6.13 The relationship between the resonant capacitance $C_r$ and resonant inductance             |

| $L_r$ for the designed rise time                                                                        |

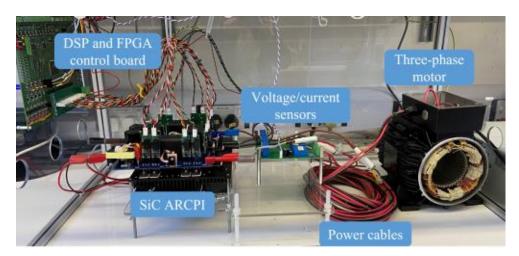

| Figure 6.14 Experimental setup                                                                          |

| Figure 6.15 The RLC filter for SiC-based adjustable speed drives124                                       |

|-----------------------------------------------------------------------------------------------------------|

| Figure 6.16 The flow chart of the variable-timing control method for the ARCPI125                         |

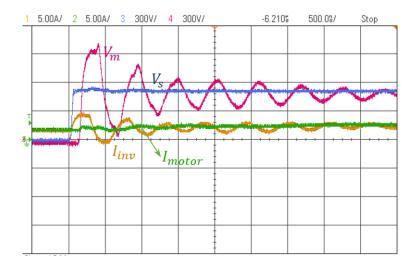

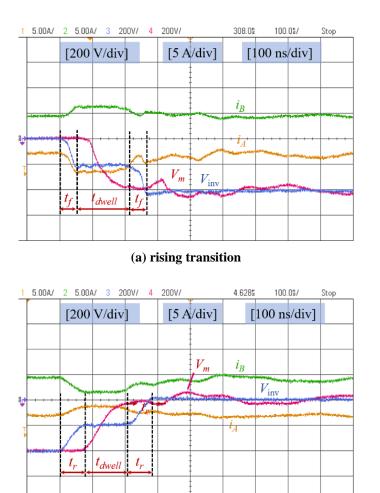

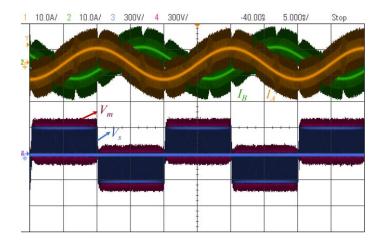

| Figure 6.17 Experimental results of the phase currents and line voltage at the inverter sides             |

| and motor terminals for two fundamental cycles when the motor is supplied by (a) the hard-                |

| switching inverter and (b) the hard-switching inverter $+ \frac{dv}{dt}$ filter and (c) the ARCPI.        |

|                                                                                                           |

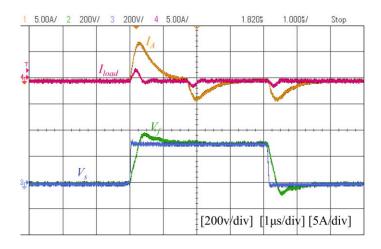

| Figure 6.18 The load current $I_{load}$ , the inverter output current $I_A$ , the inverter output voltage |

| $V_s$ and the filter output voltage $V_f$ during the switching transient for the hard-switching           |

| inverter + $dv/dt$ filter                                                                                 |

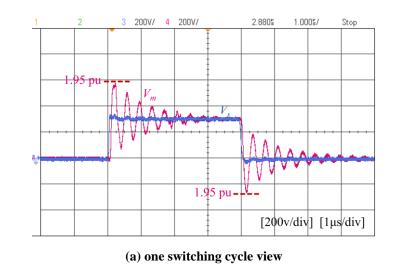

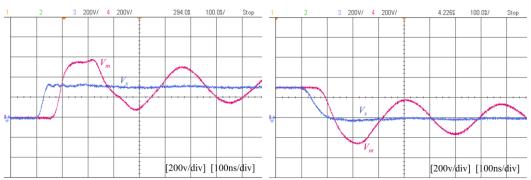

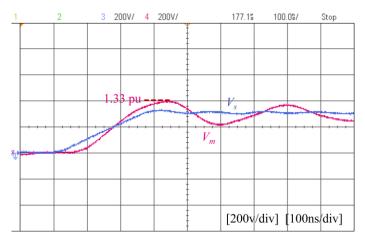

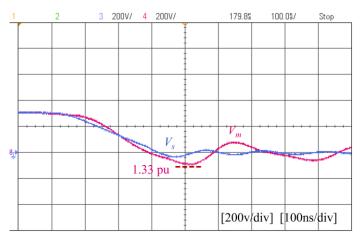

| Figure 6.19 Inverter and motor voltages when the motor is supplied by the hard-switching                  |

| inverter                                                                                                  |

| Figure 6.20 Inverter output voltage $V_s$ , the filter output voltage $V_f$ and motor voltage $V_m$       |

| when the motor is supplied by the hard-switching inverter $+ \frac{dv}{dt}$ fitler                        |

| Figure 6.21 Inverter and motor voltages when the motor is supplied by the ARCPI 131                       |

| Figure 6.22 Inverter and motor voltages when the rise and fall times are faster than the                  |

| optimum value                                                                                             |

| Figure 6.23 The rising edge of the output voltage of the ARCPI at different dc-link voltage.              |

|                                                                                                           |

| Figure 6.24 Frequency spectrum of the motor voltage using the hard-switching inverter and                 |

| the ARCPI                                                                                                 |

| Figure 6.25 The device current and voltage during the turn-off switching transients of (a)                |

| the hard-switching converter and (b) the ARCPI                                                            |

| Figure 6.26 The efficiency at different load conditions                                                   |

## List of Tables

| Table 2.1 The properties of Si and SiC material [14], [61], [76], [77] | 10  |

|------------------------------------------------------------------------|-----|

| Table 3.1 Main cable parameters of one meter cable [33]                |     |

| Table 5.1 Main experimental parameters                                 |     |

| Table 6.1 The ARCPI parameters.                                        | 122 |

| Table 6.2 The motor parameters.                                        | 124 |

| Table 6.3 The cable parameters.                                        | 124 |

| Table 6.4 The dv/dt filter parameters.                                 | 124 |

## List of Symbols

| Α                       | Voltage pulse amplitude                           |

|-------------------------|---------------------------------------------------|

| C <sub>ds</sub>         | Drain-source capacitance                          |

| C <sub>dg</sub>         | Drain-gate capacitance                            |

| C <sub>gs</sub>         | Gate-source capacitance                           |

| C <sub>c</sub>          | Cable per unit length capacitance                 |

| Coss                    | Output capacitance                                |

| $c_n, c_{n1}, c_{n2}$   | Fourier series coefficient                        |

| Γ <sub>m</sub>          | Reflection coefficient at the motor terminals     |

| $\Gamma_{s}$            | Reflection coefficient at the power inverter side |

| D                       | Duty ratio                                        |

| <i>f</i> <sub>rwp</sub> | Oscillation frequency                             |

| f <sub>osc</sub>        | Anti-resonance frequency                          |

| L <sub>c</sub>          | cable per unit length inductance                  |

| L <sub>r</sub>          | Resonant inductance                               |

| $L_f$                   | Filter inductance                                 |

| $i_A, i_B, i_C$         | Phase current                                     |

| i <sub>Lr</sub>         | Resonant current                                  |

| i <sub>phase</sub>      | Inverter output current                           |

| I <sub>load</sub>       | Load current                                      |

| ω                     | Angular frequency                               |

|-----------------------|-------------------------------------------------|

| τ                     | Pulse width                                     |

| t <sub>dead</sub>     | Deadtime                                        |

| $t_f, t_{fall}$       | Fall time                                       |

| $t_p$                 | Propagation time                                |

| t <sub>r</sub>        | Rise time                                       |

| t <sub>ramp</sub>     | Ramp up time                                    |

| υ                     | Wave propagation velocity                       |

| V <sub>AB</sub>       | Line voltage between phase A and B              |

| V <sub>AB_inv</sub>   | Line voltage between phase A and B for inverter |

| V <sub>AB_laod</sub>  | Line voltage between phase A and B for load     |

| $V_{AN}, V_{BN}$      | Output voltage for phase A and B                |

| V <sub>dc</sub>       | dc-link voltage                                 |

| $V_s, V_{s1}, V_{s2}$ | Inverter output voltage                         |

| $V_m, V_{m1}, V_{m2}$ | Motor terminal voltage                          |

| Z <sub>c</sub>        | Cable characteristic impedance                  |

| Z <sub>cm</sub>       | Common mode impedance                           |

| Z <sub>m</sub>        | Motor characteristic impedance                  |

| Zs                    | Inverter characteristic impedance               |

## List of Abbreviations and Acronyms

| AC     | Alternating Current                               |

|--------|---------------------------------------------------|

| ARCPI  | Auxiliary Resonant Commutated Pole Inverter       |

| СМ     | Common Mode                                       |

| DC     | Direct Current                                    |

| DM     | Differential Mode                                 |

| DPT    | Double Pulse Test                                 |

| EMI    | Electromagnetic Interference                      |

| HVDC   | High-Voltage Direct Current                       |

| IGBT   | Insulated-Gate Bipolar Transistors                |

| MOSFET | Metal–Oxide–Semiconductor Field-Effect Transistor |

| PD     | Partial Discharge                                 |

| PDIV   | Partial Discharge Inception Voltage               |

| PWM    | Pulse-Width Modulation                            |

| Q3L    | Quasi-Three-Level                                 |

| RWP    | Reflected Wave Phenomenon                         |

| SiC    | Silicon Carbide                                   |

| VSI    | Voltage Source Inverter                           |

| WBG    | Wide Bandgap                                      |

| ZCS    | Zero Current Switching                            |

| ZVS    | Zero Voltage Switching                            |

## Chapter 1 Introduction

### **1.1 Background and Motivation**

Power electronics converters are core elements in a plethora of applications including industrial automation and robotics [1], transportation systems [2], [3], and renewable energy [4], where they transform the electrical power, i.e., voltages and currents, from an available form to the desired form in a highly efficient and controllable manner. They are one of the critical enabling technologies for the electrification of automotive [5], railway [6], aerospace [7], and marine propulsion [8], and open the way for carbon footprint reduction, creating low emission and environment friendly transportation systems with high efficiency, flexible and smart control [9]. Furthermore, many emerging applications such as renewable energy [10], i.e., wind [11], solar [12], and tidal power generators [13], would not be possible without power electronics converters. In a nutshell, power electronics converters deeply permeate a huge range of industrial sectors, promoting remarkable technological progress as well as offering a green and sustainable development [14]–[17].

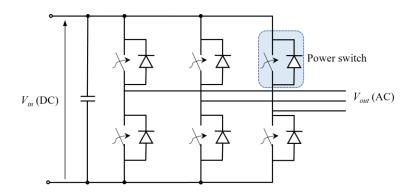

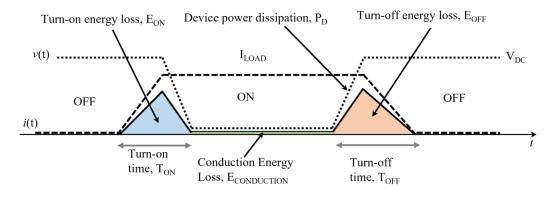

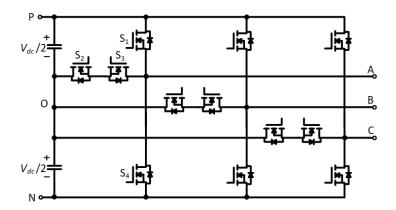

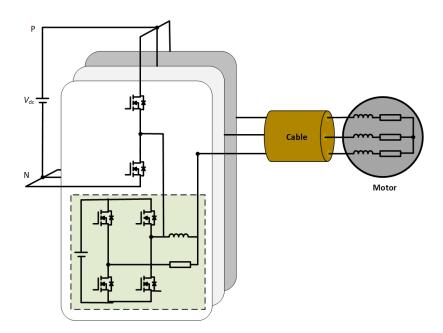

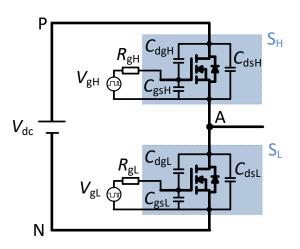

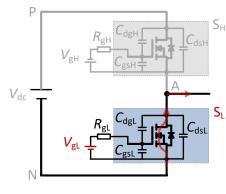

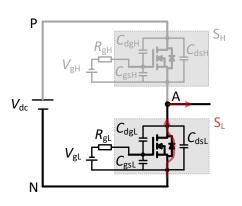

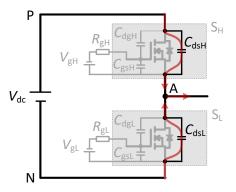

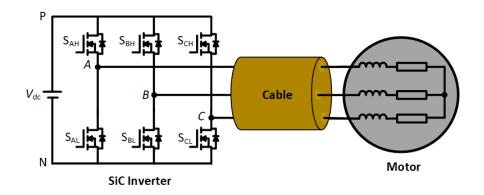

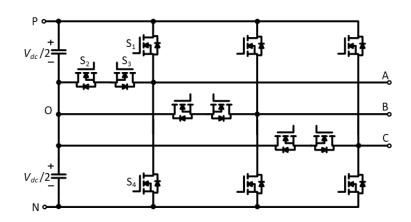

Power semiconductor devices, especially power switching devices, are at the heart of power converters to handle the electrical power conversion [18], [19]. Figure 1.1 shows the circuit diagram of a typical two-level three-phase Voltage Source Inverter (VSI) for the Direct Current (DC) to Alternating Current (AC) power conversion, where it consists of six switching devices [20]. These switching devices in the power inverter are operated in either the conduction state (on) or blocking state (off) to generate the required output voltages and currents. Since the switching devices have very low on-state and high off-state resistance [21], the main power loss of the VSI comes from the switching transients, which is known as the switching loss [22]. This can be explained by Figure 1.2 showing the voltage and current across the switching device in the VSI [23]. As can be noticed, the switching loss is determined by the time spend at switching transitions, where faster switching speed allows the switching loss reduction and power density improvement for the power inverter [24].

Figure 1.1 A two-level three-phase VSI.

Figure 1.2 Voltage and current waveform of the switching device in a VSI during the switching transitions [23].

The commercial availability of fast-switching speed Wide-Bandgap (WBG) material based power semiconductor devices such as Silicon Carbide (SiC) Metal–Oxide–Semiconductor Field-Effect Transistors (MOSFETs) are pushing the boundaries of power converter performance to meet the aggressive power density and efficiency targets for existing and emerging applications [14]. WBG devices are considered to be the game-changing technologies, strongly contributing to all sectors of low-carbon industry, advancing transformative technological breakthorugh in highly compact and efficient power converter systems [25]. Compared with the conventional Silicon (Si) based switching devices, WBG devices are capable of switching at faster switching speeds, withstanding higher voltage level and operating at higher temperature [26]. Faster switching speed enables the switching loss reduction at a given switching frequencies which can reduce the cooling frequencies while maintaining high efficiency which can reduce the filter size [27]. Due to the reduction of passive components, the system's power density can be significantly improved. [28]. In addition, the elavated temperature capabilities of WBG devices enable

the reduction of coolling requirement for power converters as well as working in harsh enviroments [29].

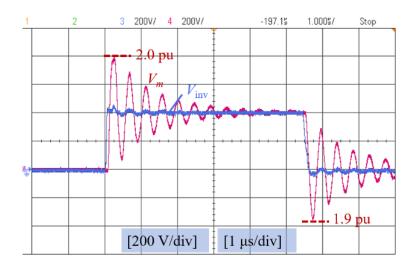

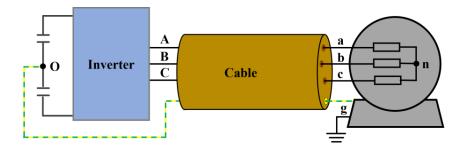

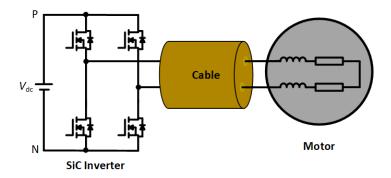

Though WBG power semiconductor switching devices offer an abundance of benefits, the fast-switching speed (high dv/dt) of WBG devices is expected to bring about a set of challenges for both the inverter and the connected electric motor in inverter-fed motor drive systems [14]. One of the serious issues is the motor overvoltage oscillations due to the Reflected Wave Phenomenon (RWP) caused by the high dv/dt and the impedance mismatch in the motor drive system [30]. In a typical WBG inverter-fed motor drive system, the fast-switched Pulse-Width Modulation (PWM) voltage pulses make power cables act like transmission lines [31]. Since the motor impedance is usually several times higher than the cable's, the inverter voltage pulses experience back and forth voltage reflections across the cables [32]. This results in overvoltage oscillations at motor terminals that can be twice the inverter voltage, as shown in Figure 1.3 [33].

Figure 1.3 Voltages measured at the inverter side  $V_{inv}$  and motor terminals  $V_m$  when the motor is supplied by the fast-switching SiC inverter in a cable-fed motor drive system [33].

It is well established in the literature that fast-switched inverter voltage pulses result in the non-uniform voltage distribution within the motor stator winding turns with peak voltage stress across the first few turns close to the motor terminals [34]–[36]. This overstress is further exacerbated when long power cables are used to connect the inverter to the motor due to the RWP [37]. The resultant overvoltage stress across motor stator winding adversely affects the motor lifetime by accelerating the winding insulation aging through the inception of Partial Discharges (PDs) that progressively yield to the degradation and local heating of organic coatings of motor coils, which significantly affects the reliability

of the motor drive system [38]–[41]. Since PDs are frequency dependent, the occurrence of PD would increase with switching frequency [38]. According to an industrial survey, the additional voltage stresses at the motor stator windings in conventional Si based motor drive system accounted for 30%-40% of induction motor breakdown [42]. With the adoption of the fast-switching speed, high frequency WBG power inverter in motor drive systems, the motor winding insulation breakdown is predicted to increase significantly, which dramatically reduces the reliability and lifetime of the motor drive systems. In addition, the overvoltage oscillations due to the RWP and electromagnetic emissions due to the PDs further deteriorate the Electromagnetic Interference (EMI) performance which cannot satisfy the stringent requirement of many applications such as defence and aerospace [43], [44].

The above issues associated with the RWP due to the high dv/dt may hinder the application of WBG devices in motor drive systems. Therefore, it is necessary to devote more efforts to investigate the RWP in WBG inverter cable-fed motor drive system and explore potential mitigation techniques to effectively utilise WBG devices.

#### **1.2 Research Objectives**

The main goal of this PhD thesis is to investigate in-detail the RWP as well as to explore motor terminal overvoltage mitigation techniques without compromising the benefits of WBG devices in cable-fed motors with fast-switching SiC inverters. The research consists of both theoretical analysis and detailed experimental verification, which is focussed around four research objectives:

**Research Objective 1**: Gain deep understanding of the RWP and crystallize the underlying cause of motor terminal overvoltage oscillations in cable-fed motors using fast-switching SiC inverters, providing the foundation for developing overvoltage mitigation techniques through active waveform shaping.

**RO 1.1** Investigate the RWP in time domain using a bounced diagram to visually illustrate the voltage reflection process in cable-fed motor drive systems, providing the foundation for developing active waveform shaping techniques to address the motor terminal overvoltage oscillations.

**RO 1.2** Analyse the RWP in frequency domain to identify the motor terminal overvoltage oscillation frequency in cable-fed motor drive systems, providing the

foundation for revealing the overvoltage mitigation mechanism of the proposed active waveform shaping techniques.

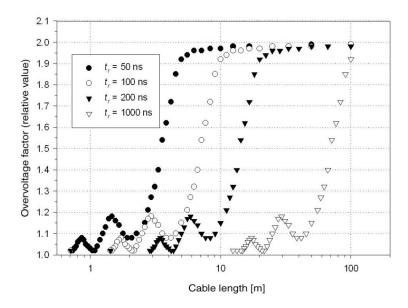

**RO 1.3** Assess how the motor terminal voltage is affected by the cable length and rise/fall times of the inverter voltage through simulation study.

**Research Objective 2**: Investigate the impact of parasitic capacitance of switching devices on motor terminal overvoltage in cable-fed motors using SiC inverters.

**RO 2.1** Systematically analyse the switching commutation processes for a three-phase SiC based motor drive system, considering the impacts of parasitic elements of the switching devices and load current during the switching transitions.

RO 2.2 Experimental verification of the analysis.

**Research Objective 3**: Address the motor terminal overvoltage oscillations at the source by using the active waveform shaping technique, i.e., quasi-three-level (Q3L) PWM scheme.

**RO 3.1** Reveal the essence of the overvoltage mitigation mechanism of the Q3L PWM in both the time domain and frequency domain.

**RO 3.2** Investigate the impact of the parasitic capacitance of switching devices on the mitigation of motor terminal overvoltage oscillations using the Q3L PWM T-type inverter.

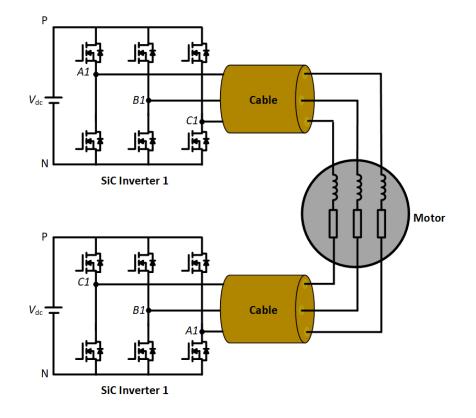

**RO 3.3** Develop the Q3L PWM scheme using the SiC module-parallel inverter to mitigate the motor terminal overvoltage and extend the device current capacity.

**RO 3.4** Experimental verification of the Q3L PWM scheme using SiC T-type inverter and SiC module-parallel inverter.

**Research Objective 4**: Address the motor terminal overvoltage oscillations at source using the active waveform shaping technique, i.e., soft-switching voltage slew rate (dv/dt) profiling without sacrificing the benefits of SiC devices.

**RO 4.1** Derive the optimum rise and fall times for entirely mitigation of the motor terminal overvoltage.

**RO 4.2** Reveal the essence of the overvoltage mitigation mechanism of the proposed slew rate profiling in both time domain and frequency domain.

**RO 4.3** Experimental demonstration of the slew rate profiling concept with a SiC softswitching inverter, i.e., the Auxiliary Resonant Commutated Pole Inverter (ARCPI).

### **1.3 Thesis Outline**

This thesis consists of seven chapters. Following this introduction chapter (Chapter 1), **Chapter 2** presents a review of existing literatures relating to the PhD work. WBG power switching devices and their application in adjustable speed drive system are briefly introduced. The issues associated with the high dv/dt on the motors in WBG inverter-fed motor drive systems, and existing mitigation methods to address the RWP are described in this chapter. Moreover, the limitations of existing literature and research opportunities are summarised and discussed.

**Chapter 3** investigates the RWP in both time domain and frequency, as well as assesses how the motor terminal voltage is affected by the cable length and rise/fall times of the inverter voltage through simulation study. This chapter is the foundation for developing active waveform shaping techniques including the Q3L PWM and the voltage slew rate (dv/dt) profiling to mitigate motor terminal overvoltage oscillations, as proposed in Chapters 5 and 6.

**Chapter 4** investigates the motor terminal overvoltage oscillations in a three-phase motor drive system, considering the impacts of parasitic elements of the switching devices and load current during the switching transitions. Also, the analysis is experimentally verified in this chapter.

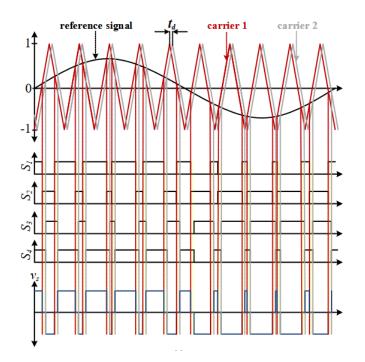

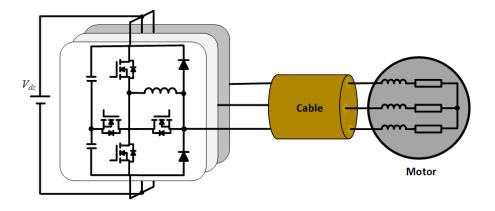

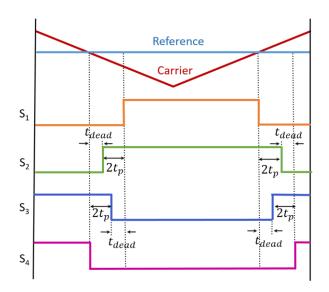

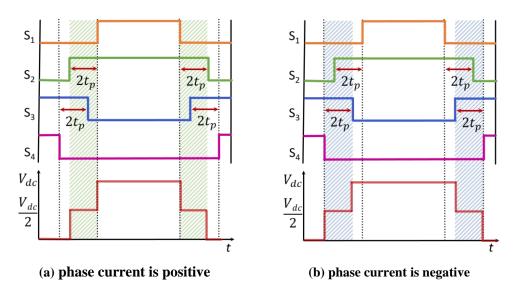

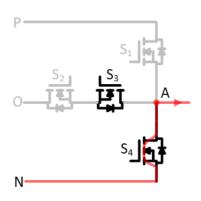

**Chapter 5** develops the active waveform shaping technique, i.e., Q3L PWM scheme. The essence of overvoltage mitigation mechanism of the Q3L PWM scheme is crystallized in both the time domain and frequency domain. The impact of parasitic capacitance of switching device in SiC T-type inverter on the motor terminal overvoltage mitigation is analysed and experimentally verified. Furthermore, the Q3L PWM using module-parallel inverter is proposed to mitigate the motor terminal overvoltage as well as extend the switching devices current capacity. The SiC T-type inverter and the SiC module-parallel inverter are built to experimentally implement the Q3L PWM scheme.

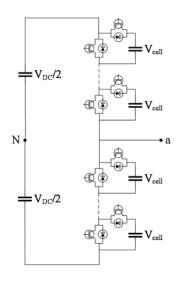

**Chapter 6** proposes the active waveform shaping technique, i.e., the voltage slew rate (dv/dt) profiling to address the motor terminal overvoltage. The essence of overvoltage mitigation mechanism of the voltage slew rate profiling is crystallized in both the time domain and frequency domain. The philosophy used here is addressing the motor terminal overvoltage oscillations at the source by actively mitigating the excitation source for the motor terminal overvoltage oscillations. The SiC ARCPI is used as an example of the softswitching inverter to experimentally verify the effectiveness of the proposed approach.

**Chapter 7** concludes the main findings of this PhD work and presents possible future research topics.

# Chapter 2 Literature Review

# **2.1 Introduction**

WBG devices due to their beneficial attributes such as the fast-switching speed have been widely adopted in a plethora of applications, offering transformative technological breakthrough in power electronics and adjustable speed drives [45]–[47]. However, the fast-switching speed (high dv/dt) of WBG devices is expected to result in excessive voltage stress on the connected motor stator windings due to the RWP, accelerating the degradation of motor windings insulation and causing premature failure of the motor drive system [9], [14], [48].

This chapter presents a review of existing literatures relating to the tittle of this PhD work. WBG power switching devices, i.e., SiC MOSFETs, and their application in adjustable speed drive system are briefly described. The issues associated with the high dv/dt of switching devices on the motors in inverter-fed motor drive systems, and existing mitigation methods including the passive and active approaches to address the RWP are presented in this chapter. Also, limitations of existing literature and research opportunities are summarised.

### 2.2 WBG Semiconductor Power Devices

#### 2.2.1 Overview

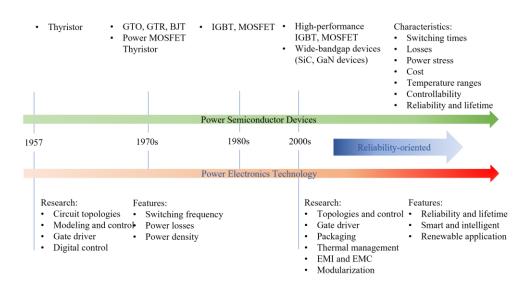

In the past 60+ years, the continued rapid development of power electronics technology is driven by the advent of new generation power semiconductor devices [49], as demonstrated in Figure 2.1 [50], [51]. The invention of thyristor in 1957 elicited the deployment of High-Voltage Direct Current (HVDC) systems [52], the advent of Si based MOSFETs and Insulated-Gate Bipolar Transistors (IGBTs) in 1980s led to the PWM converters, advancing development of the modern adjustable speed drives and smart grid [53]–[59]. With the relentless research for more than 40 years, the conventional Si power semiconductor switching devices have become mature and are reaching their material performance limits [60]–[65].

Figure 2.1 Development of power electronics and power electronics technology [50], [51].

The commercial availability of WBG materials based power semiconductor devices such as SiC MOSFETs is advancing transformative technological breakthrough in power electronics [66], [67]. WBG devices are considered to be the game-changing technologies, they are pushing the boundaries beyond the conventional Si based devices limits in power and switching frequency making it possible to dramatically increase the power density and efficiency for existing and emerging applications [14]. Compared with Si based switching devices, SiC MOSFETs can operate at faster switching speeds [68]–[70], higher voltage levels [67], [71], [72], and higher operating termperatues [73]–[75]. These enhanced performance of SiC MOSFETs are due to the superior material characteristics, as given in Table 2.1 [14], [61], [76], [77].

Table 2.1 The properties of Si and SiC material [14], [61], [76], [77].

|                                    | Si                             | 4H-SiC                         | Property              |

|------------------------------------|--------------------------------|--------------------------------|-----------------------|

| Energy bandgap $E_g$               | 1.12 eV                        | 3.26 eV                        | Operating temperature |

| Breakdown electric field           | 0.25 MV/cm                     | 2.2 MV/cm                      | Breakdown voltage     |

| strength <i>E</i> <sub>bk</sub>    |                                |                                | ON-resistance         |

| Saturation Velocity V <sub>s</sub> | $1.0 \times 10^7  \text{cm/s}$ | $2.7 \times 10^7  \text{cm/s}$ | Switching speed       |

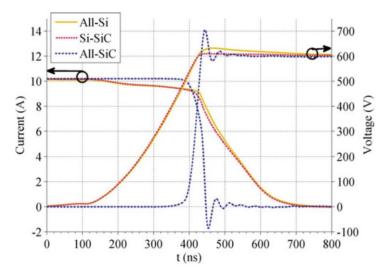

Figure 2.2 compares the voltage and current waveforms of the conventional Si IGBT and SiC MOSFET at the turn-OFF switching transient measured in a double pulse test (DPT) experiment [78]. As shown, the switching speed of SiC MOSFET is about 10 times faster than that of Si IGBT, where the turn-OFF times of Si IGBT and SiC MOSFETs are about

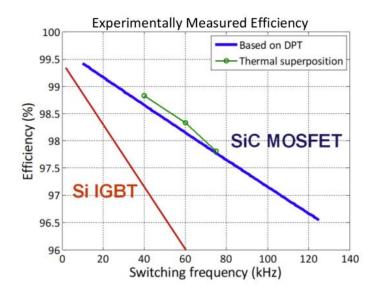

500ns and 50ns, resepectively. Note that the switching speed at the turn-ON switching transient of SiC MOSFETs is much faster than Si IGBTs as well [27]. Since the power loss of the converter is mainly from the switching loss [79], the fast switching speed of SiC MOSFETs singnificantly reduces the switching loss and improves the efficiency of the power converters for a given switching frequency [80], as evidenced in Figure 2.3 [81]. This allows the reduction of cooling requirement and hence improve the power density of the power converter [82].

Figure 2.2 Comparison of the voltage and current waveform at the turn-OFF transient of SiC, Si-SiC and Si measured in a DPT experiment. The dc-link voltage is 600V and load current is 10A. All-Si represents Si IGBT and Si diode (Infineon IKW15T120, "IGBT3" and "EmCon HE" device generations), Si-SiC represents Si IGBT (IKW15T120) and SiC Schottky diode (SemiSouth SDA10S120) combination, All-SiC represents SiC MOSFET (Cree CMF20120D) and SiC Schottky diode (SemiSouth SDA10S120) combination [78].

Figure 2.3 Efficiency comparison of the power converter using Si IGBT and SiC MOSFET at different switching frequency [81].

On the other hand, referring to Figure 2.3, with the switching loss reduction, the power converter can work at higher switching frequencies while maintaining the high efficiency. This can singinicantly shrink the size and reduce the weight of power converter as a result of the reduction of passive components [83], [84].

Furthermore, when the high frequency power converter is used to drive electric motors, several benefits can be achieved for the motor drive system [9], [14], [85]. For example, the increased switching frequeny enables higher control bandwidth and lower torque ripple, compared with Si counterpart. The increased switching frequency of the power converter leads to the reduction in current and voltage ripple [86], hence reduces the associated power loss due to the current ripple for the motors.

In terms of thermal performance, most of the commercial Si IGBTs operte below 150°C due to the limitation of material characteristics, while SiC MOSFETs can operate up to 250 °C or even high with the development of packaging techniques [14], [87], [88]. The elavated temperature capabilities of SiC MOSFETs enable the reduction of cooling requirement for power converters as well as working in harsh environments [89], [90].

#### 2.2.2 Applications in Adjustable Speed Drive Systems

With relentless research in last 20 years, WBG power semiconductor switching devices have shown the technological readiness and are becoming the devices of choice to replace their Si predecessors in a growing number of power converters used to control electric motors in adjustable speed drive systems [14].

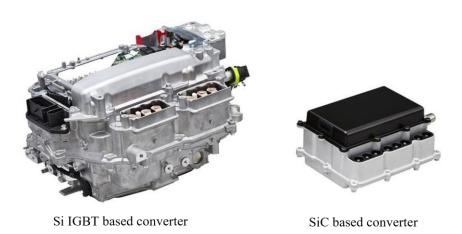

Mitsubishi Electric released the world's first all SiC 1.5kV dc, 180 kW tracton inverter in 2013, as shown in Figure 2.4 [91]. Mitsubishi claimed that compared with the Mitsubishi Electric's conventional the equivalently power-rating inverter system incorporating conventional Si IGBTs, the SiC power converter achieved about 55% reduction in switching loss.

In 2014, Toyota and Denso developed the SiC based power converter for use in automotive power control units in hybrid vehicles, as shown in Figure **2.5** [92]. Refering to Figure **2.5**, Compared to the conventional Si based power converter, the SiC based power control unit reduces the volume by 40% [92].

Figure 2.4 SiC-based traction inverter developed by Mitsubishia in 2013 [91].

Figure 2.5 Inverter developed by Toyota for use in PCU in 2014 [92].

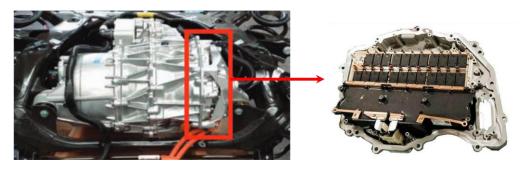

In 2018, Tesla used SiC MOSFETs in its Model 3 power converter for the motor drive system leading to more than 50% overall weight reduction when compared with conventional Si based power converter [93]. In addition, the performance advantages of WBG power converter such as high-power density and low power loss, make it possible to integrate the power converter inside the motor housing, as shown in Figure 2.6, allowing further reductions in the cost, size, and improvements in fault tolerance of the motor drive system [93].

Figure 2.6 SiC Inverter developed by Tesla in 2018 [93].

In addition to the advantage of the fast-switching speed, SiC power converters benefit from the high operating temperature attribute of SiC MOSFETs [25], [94], [95]. Figure 2.7 shows the power converter prototype using Si IGBTs and SiC MOSFETs for hybridelectric construction vehicles developed by John Deere in 2019 [96]. It is worth noting that the SiC power converter can operate at high temperature where the coolant temperature for SiC power converter can be 115°C due to the advanced internal cooling and packaging techniques which allows for full-power capabilities using engine coolant on even the hottest days. Referring to Figure 2.7, the size of power converter is reduced significantly when using SiC MOSFETs, where the power density for Si and SiC power converter are 11kW/L and 43kW/L, respectively.

Figure 2.7 John Deere 200 kW inverter prototypes [96].

Indeed, WBG power semiconductor devices are unfolding the technology revolution in inverter-fed motor drive systems. While the adoption of SiC power devices significantly improves the performance of power converters, the fast-switching speeds and high switching frequencies, resulting in several design challenges and technological issues, which will be described in next section.

# 2.3 Impact of the Fast-Switching WBG Converter on the Connected Motors in Adjustable Speed Drives

In addition to the design challenges for the converter itself, the fast-switching speed WBG converter is expected to significantly affect the reliability and lifetime of the connected electric motor in WBG based cable-fed motor drive systems [14]. Figure 2.8 summarises the main issues and challenges for motors when using the fast-switching speed WBG semiconductor in the inverter-fed motor drive systems.

Issues of high dv/dt on motors How with the set of the set of

# Figure 2.8 The main challenges of the high dv/dt on motors in WBG-based motor drive systems.

Since the PhD work aims to explore techniques to address the excessive voltage stress on the motor due to the fast-switching WBG inverter, the issues caused by the high dv/dt, i.e., uneven voltage distribution within the motor stator windings and the RWP will be reviewed in the following section.

#### 2.3.1 Uneven Voltage Distribution within Motor Stator Windings

In inverter-fed motor drive systems, the fast-switched PWM voltage pulses result in uneven voltage distribution within motor stator windings [97]–[103]. In fact, the uneven voltage distribution arises from the propagation of the fast-switched PWM voltage pulses through the motor stator winding itself emulating the same effect of long cables. The faster the rise time, the more significant this effect and even greater the uneven voltage distribution along motor stator windings [104], [105]. As a consequence, the insulation failures most commonly occur in the first few turns of the first coil connected to the main terminals [106], [107].

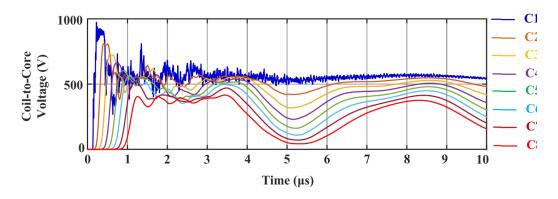

Figure **2.9** shows the simulation result of the coil-to-core voltage when the motor is supplied by fast-switched PWM voltage pulses, where the dc-link voltage is 560V [105]. As can be noticed, the voltage distributes nonlinearly among the motor coils, where the voltage decreases from the first coil to the last coil in a monotonic manner. It is worth noting that the first coil endures the highest voltage stress among the stator winding coils, as shown in Figure 2.9.

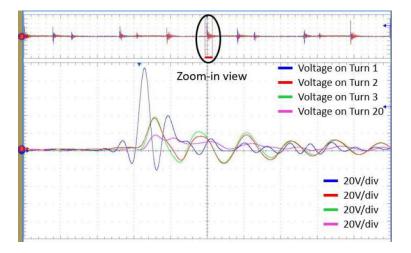

Figure 2.10 compares the voltages across winding turns in the first coil of a motor stator measured in an experimental test [108]. As can be noticed, the voltage distributes unevenly among the motor stator winding turns, where the first several stator winding turns endure the higher voltages. Referring to Figure 2.10, the voltage across the first turn is about five times higher than that across the 20<sup>th</sup> turn [108].

Figure 2.9 Simulation results of the coil-to-core voltage distribution when the motor is feed by high dv/dt voltage, the dc-link voltage is 560 V [105].

Figure 2.10 Experimental measured voltage distribution within winding turns of first coil of phase A winding when the motor is supplied by a two-level SiC power converter through 70-feet long cable. [108].

Note that the overstress across the first few winding turns closes to the motor terminals is further exacerbated when long power cables are used to connect the inverter to the motor due to the RWP in the motor drive system [32].

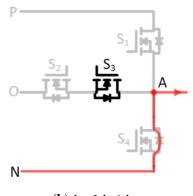

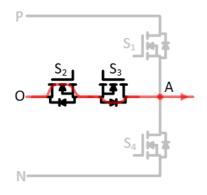

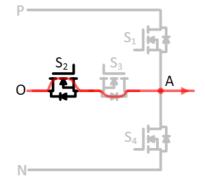

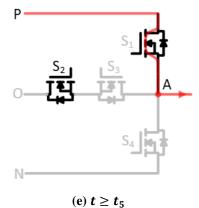

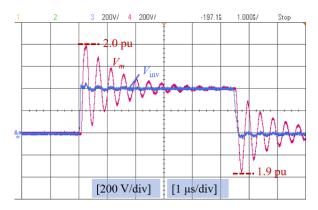

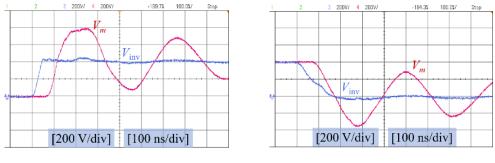

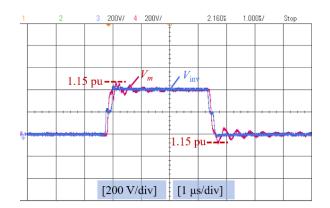

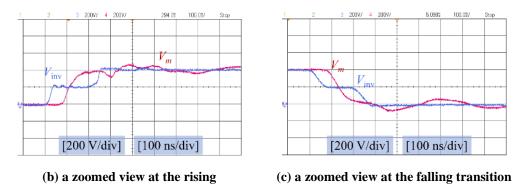

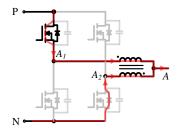

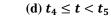

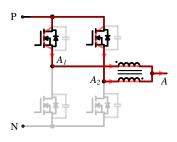

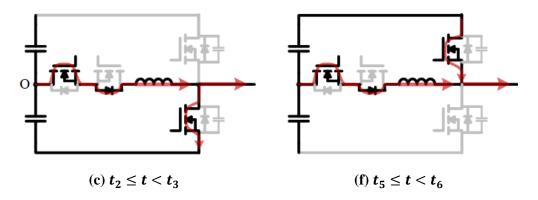

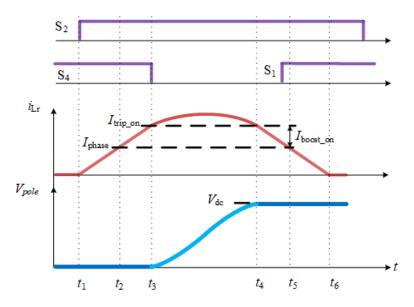

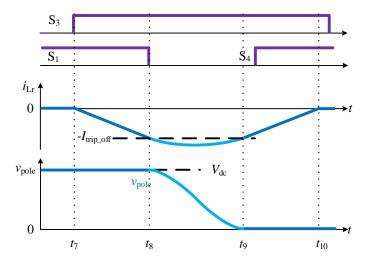

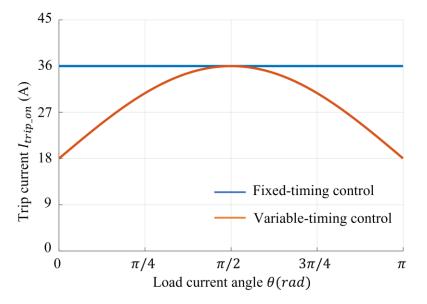

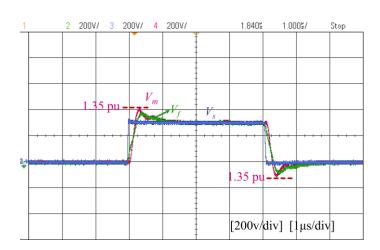

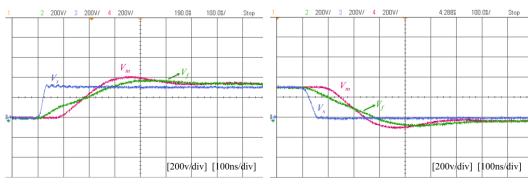

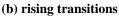

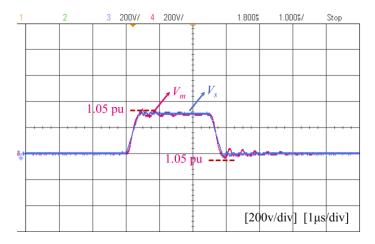

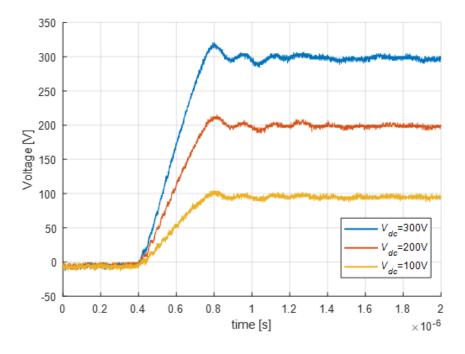

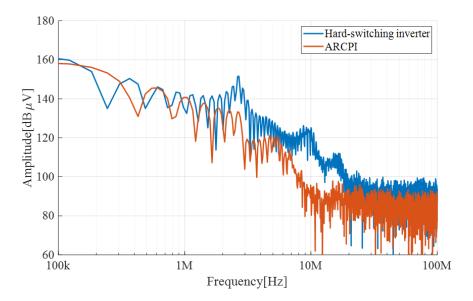

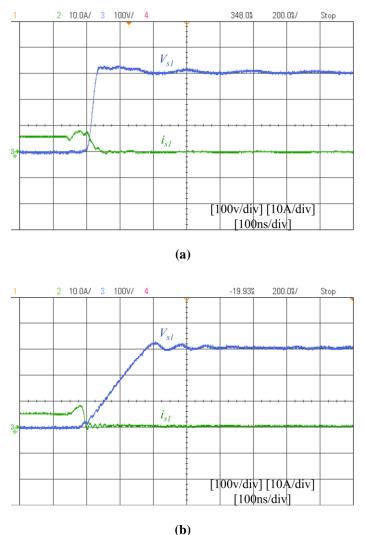

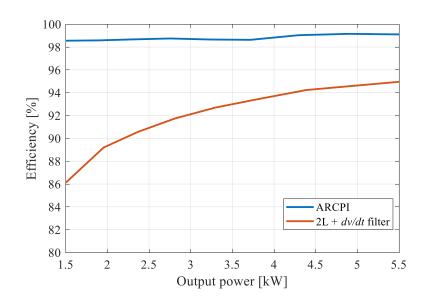

#### 2.3.2 Motor Terminal Overvoltage Oscillations