# Computational and Communication Architectures for Modular Multilevel Converter Construction

A thesis submitted to The University of Manchester for the degree of **Doctor of Philosophy**

in the Faculty of Science and Engineering

2022

Jack Andrews

Department of Electrical and Electronic Engineering

Blank Page

# **Table of Contents**

| Tab  | le of C | Contents                                                | 3  |

|------|---------|---------------------------------------------------------|----|

| List | of Fig  | ures                                                    | 8  |

| List | of Ta   | bles                                                    | 12 |

| List | of Sou  | ırce Code Listings                                      | 13 |

| Non  | nencla  | ture                                                    | 14 |

| Abs  | tract   |                                                         | 21 |

| Dec  | laratio | on                                                      | 22 |

| Сор  | yright  | Statement                                               | 22 |

| Ack  | nowle   | dgements                                                | 23 |

| 1    | Intro   | luction                                                 | 24 |

| 1.   | 1 B     | ackground                                               | 24 |

|      | 1.1.1   | Offshore Wind Farm Grid Connections                     | 24 |

|      | 1.1.2   | Renewable Electricity Generation Integration Challenges | 26 |

|      | 1.1.3   | Voltage Source Converter HVDC                           | 27 |

| 1.   | 2 A     | ims and Objectives                                      | 29 |

| 1.   | 3 N     | Iain Contributions                                      | 29 |

| 1.   | 4 T     | hesis Structure                                         | 31 |

| 2    | MMC     | Structure and Control                                   | 34 |

| 2.   | 1 C     | ircuit Structure                                        | 34 |

|      | 2.1.1   | Selection of Nominal Submodule Capacitor Voltage        | 37 |

| 2.   | 2 C     | ontrol Structure                                        | 39 |

|      | 2.2.1   | dq Current Control                                      | 40 |

|      | 2.2.2   | High-level (PQ) Control                                 | 43 |

|      | 2.2.3   | Low-level Control                                       | 43 |

| 2.   | .3 S    | ummary                                                  | 47 |

| 3    | Cana    | citor Balancing Control                                 | 48 |

|   | 3.1 | Ter   | minology                                          | .48  |

|---|-----|-------|---------------------------------------------------|------|

|   | 3.1 | .1    | Modulation Algorithm                              | .49  |

|   | 3.1 | .2    | Capacitor Balancing Control Method                | .49  |

|   | 3.1 | .3    | Sorting Algorithm                                 | . 50 |

|   | 3.2 | Rev   | view of Capacitor Balancing Control Methods       | . 50 |

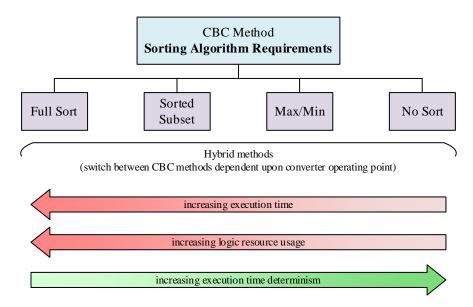

|   | 3.2 | .1    | Sorting Algorithm Requirement                     | . 50 |

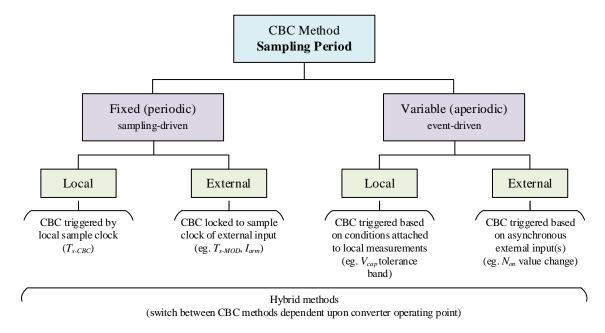

|   | 3.2 | .2    | Sampling Period                                   | . 54 |

|   | 3.3 | Sur   | nmary                                             | . 57 |

| 4 | Sor | ting  | Algorithms                                        | .58  |

|   | 4.1 | Cor   | mparison Metrics                                  | . 58 |

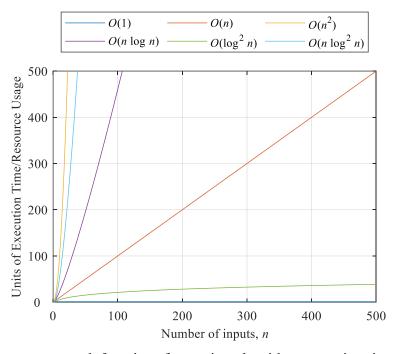

|   | 4.1 | .1    | Bachmann-Landau (Big-O) Notation                  | . 59 |

|   | 4.1 | .2    | Time Complexity                                   | . 60 |

|   | 4.1 | .3    | Space Complexity                                  | .61  |

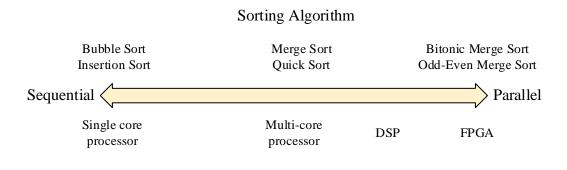

|   | 4.1 | .4    | Sequential vs. Parallel Sorting Algorithms        | . 62 |

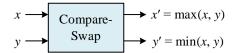

|   | 4.2 | Sor   | ting Networks                                     | . 63 |

|   | 4.3 | Sur   | nmary                                             | . 64 |

| 5 | Sin | ıulat | tion Model Overview                               | . 65 |

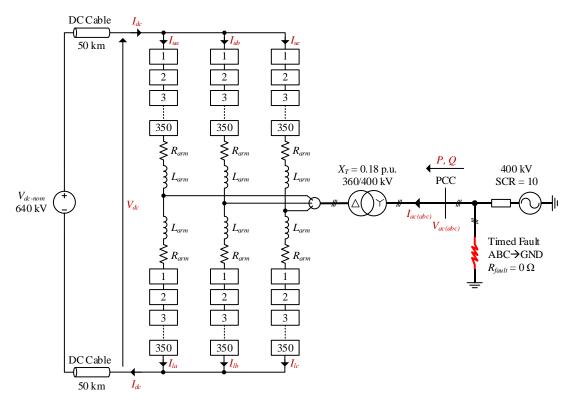

|   | 5.1 | Cir   | cuit Structure                                    | . 65 |

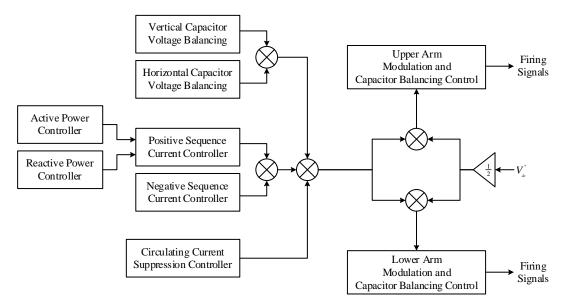

|   | 5.2 | Cor   | ntrol Structure                                   | . 67 |

|   | 5.3 | Cap   | pacitor Balancing Control Custom Component        | . 69 |

|   | 5.3 | .1    | Capacitor Balancing Control Method Implementation | .71  |

|   | 5.4 | Sur   | nmary                                             | .74  |

| 6 | Sor | ting  | Algorithms for Capacitor Balancing Control        | .75  |

|   | 6.1 | Mo    | tivations                                         | .75  |

|   | 6.1 | .1    | Sorting Algorithm Execution Time                  | .76  |

|   | 6.1 | .2    | Sorting Algorithm Implementation Resource Usage   | .76  |

|   | 6.2 | Sor   | ting Algorithm Implementation                     | .77  |

|   | 6.2 | . 1   | Control Hardware Targets                          | .77  |

|   | 6.2  | 2.2   | Programming Methods                                            | 78  |

|---|------|-------|----------------------------------------------------------------|-----|

|   | 6.2  | 2.3   | Sorting Algorithm Implementation Summary                       | 80  |

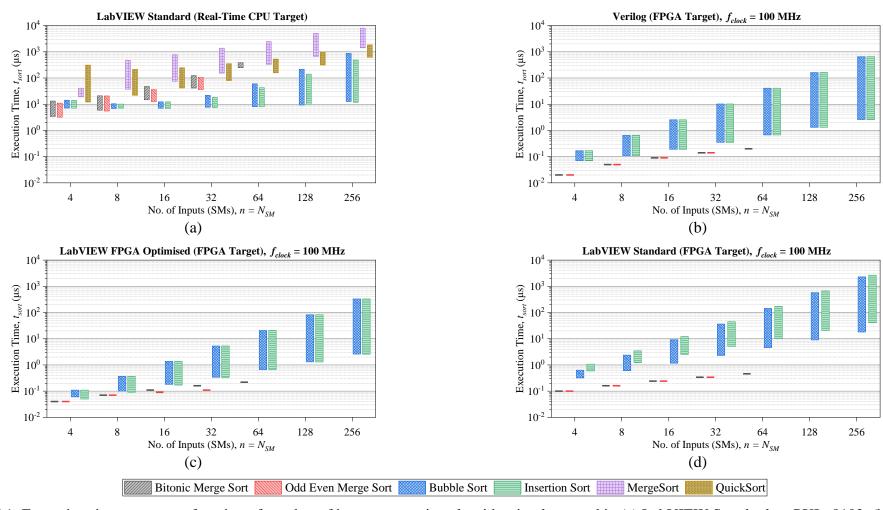

|   | 6.3  | Son   | ting Algorithm Execution Time Range                            | 83  |

|   | 6.3  | 3.1   | Real-Time CPU Target                                           | 85  |

|   | 6.3  | 3.2   | FPGA Target                                                    | 86  |

|   | 6.4  | Co    | mparison of Balancing Method Execution Time Window and Sorting |     |

|   | Algo | rithn | n Execution Time                                               | 87  |

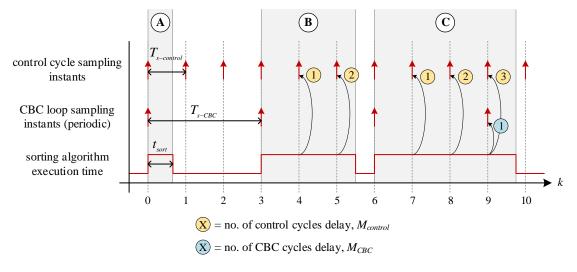

|   | 6.4  | 1.1   | Terminology                                                    | 88  |

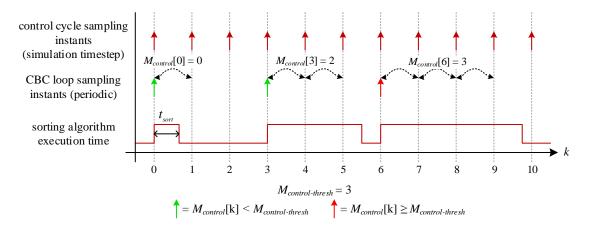

|   | 6.4  | 1.2   | Selection of Maximum Allowable Sample Delay                    | 90  |

|   | 6.4  | 1.3   | Execution Time Results                                         | 91  |

|   | 6.5  | Son   | ting Algorithm FPGA Logic Resource Usage                       | 102 |

|   | 6.5  | 5.1   | FPGA Synthesis Process                                         | 102 |

|   | 6.5  | 5.2   | Logic Resource Usage Results                                   | 106 |

|   | 6.6  | Sui   | nmary                                                          | 112 |

| 7 | Co   | nver  | ter Hardware Prototype                                         | 114 |

|   | 7.1  | De    | sign Objectives                                                | 114 |

|   | 7.2  | Ha    | rdware Overview                                                | 115 |

|   | 7.2  | 2.1   | Submodule Overview                                             | 117 |

|   | 7.2  | 2.2   | Hardware Modifications                                         | 120 |

|   | 7.3  | Co    | ntrol Architecture Overview                                    | 121 |

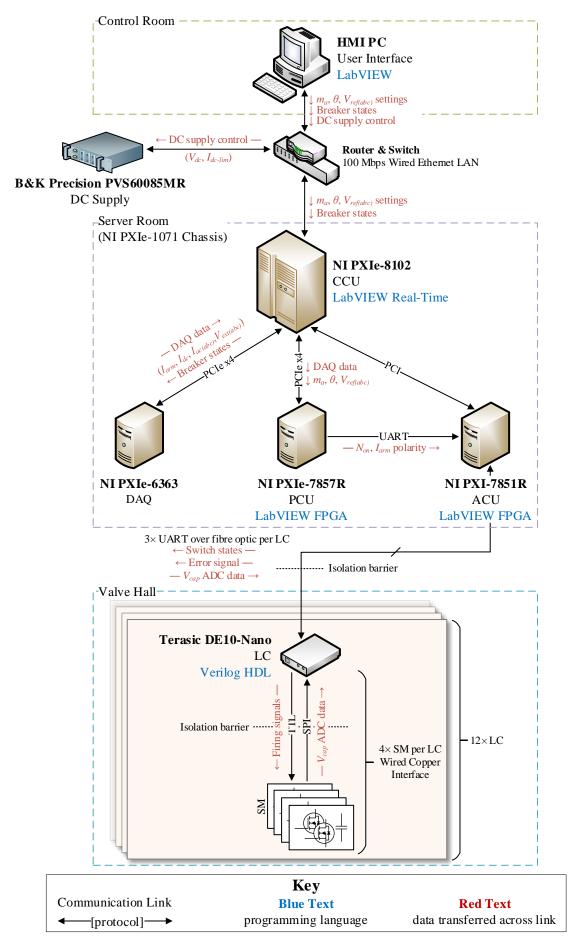

|   | 7.3  | 3.1   | Human-Machine Interface (HMI)                                  | 124 |

|   | 7.3  | 3.2   | Local Area Network (LAN)                                       | 124 |

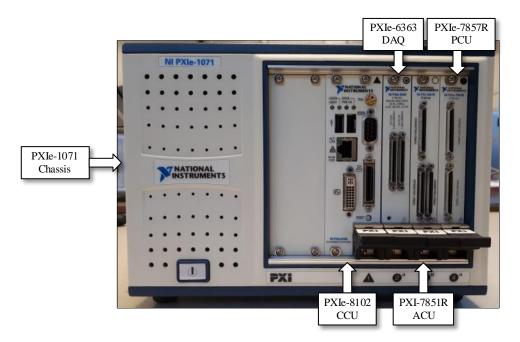

|   | 7.3  | 3.3   | Converter Control Unit (CCU)                                   | 124 |

|   | 7.3  | 3.4   | Data Acquisition (DAQ)                                         | 125 |

|   | 7.3  | 3.5   | Phase Control Unit (PCU)                                       | 125 |

|   | 7.3  | 3.6   | Arm Control Unit (ACU)                                         | 125 |

|   | 7.3  | 3.7   | Local Controller (LC)                                          | 126 |

|   | 7.4  | Cir   | nmary                                                          | 127 |

| 8 | Co    | ntrol | System Software Development128               | } |

|---|-------|-------|----------------------------------------------|---|

|   | 8.1   | Ove   | erview of the LabVIEW Programming Language   | } |

|   | 8.2   | Rev   | view of Existing CHP Control Software        | ) |

|   | 8.3   | Des   | sign Objectives                              |   |

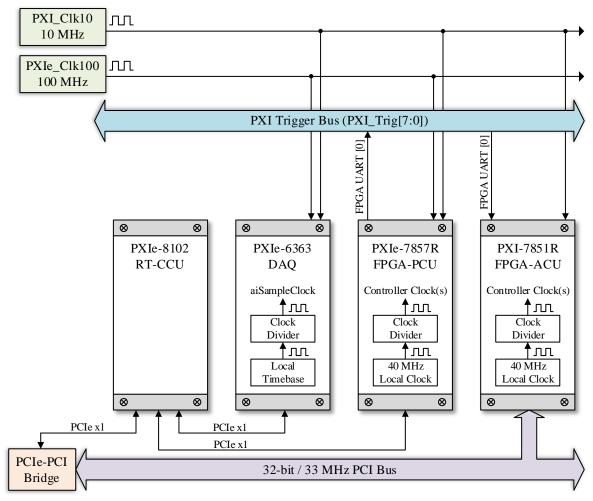

|   | 8.4   | PX    | Ie System Internal Architecture              | l |

|   | 8.4   | 4.1   | CCU Host Communication Buses                 | 2 |

|   | 8.4   | 4.2   | Clock Sources                                | 3 |

|   | 8.4   | 4.3   | Other Connections                            | 1 |

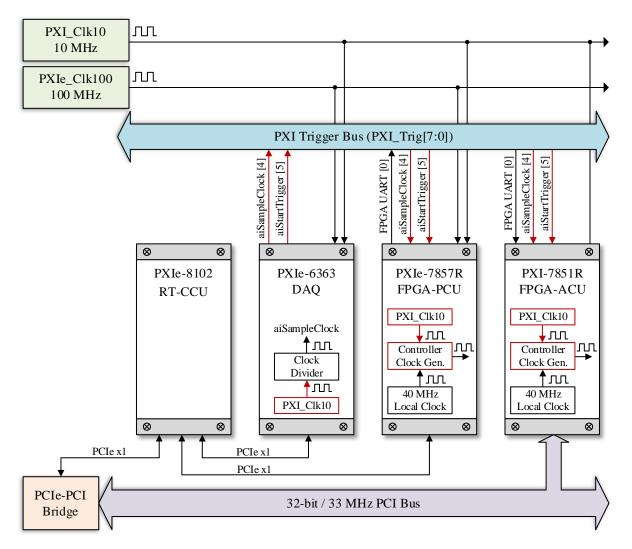

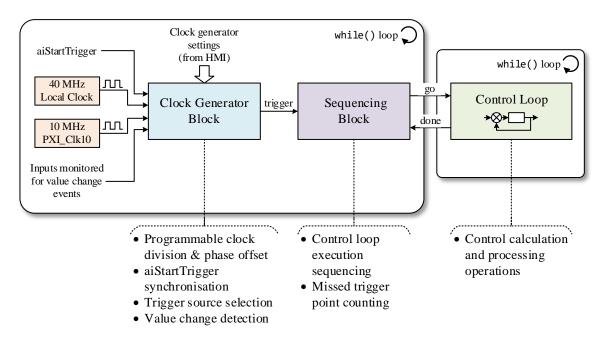

|   | 8.5   | Cor   | ntroller Sample Clock Generation             | 5 |

|   | 8.5   | 5.1   | PXI_Clk10 Clock Divider Block Operation      | 7 |

|   | 8.5   | 5.2   | Event-Driven Mode Value Change Event Sources | ) |

|   | 8.6   | Har   | dware Delay Measurement                      | 3 |

|   | 8.7   | Dat   | a Acquisition and Logging144                 | 1 |

|   | 8.7   | 7.1   | ACU Capacitor Voltage Data Transfer to CCU   | 5 |

|   | 8.7   | 7.2   | Data Transfer to HMI PC                      | 5 |

|   | 8.7   | 7.3   | Data Plotting and Logging on HMI PC          | 5 |

|   | 8.7   | 7.4   | Measurement Timestamping                     | 5 |

|   | 8.8   | Coc   | le Optimisation                              | 7 |

|   | 8.9   | Sun   | nmary                                        | } |

| 9 | Co    | nclus | sion and Future Work150                      | ) |

|   | 9.1   | Cor   | nclusion                                     | ) |

|   | 9.2   | Fut   | ure Work                                     | 3 |

|   | 9.2   | 2.1   | Capacitor Balancing Control Loop             | 3 |

|   | 9.2   | 2.2   | Converter Hardware Prototype                 | 5 |

| R | efere | nces. |                                              | 7 |

| A | ppen  | dix A | - Pseudocode for Sorting Algorithms166       | Ó |

|   | A-1   | Buł   | oble Sort                                    | 5 |

|   | Δ_2   | Ince  | ertion Sort                                  | 7 |

| A-3    | Merge Sort                                                           | 168 |

|--------|----------------------------------------------------------------------|-----|

| A-4    | Quick Sort                                                           | 170 |

| Append | lix B - Source Code for Custom PSCAD/EMTDC Component                 | 172 |

| B-1    | Common Source Code                                                   | 173 |

| B-2    | Periodic CBC Method Source Code                                      | 176 |

| B-3    | Average Tolerance Band CBC Method Source Code                        | 176 |

| B-4    | Cell Tolerance Band CBC Method Source Code                           | 176 |

| B-5    | Bubble Sort Subroutine Source Code                                   | 177 |

| Append | lix C - Selection of Maximum Allowable Control Cycle Delay Threshold | 179 |

| Append | lix D - Supplementary Plots for Chapter 6                            | 188 |

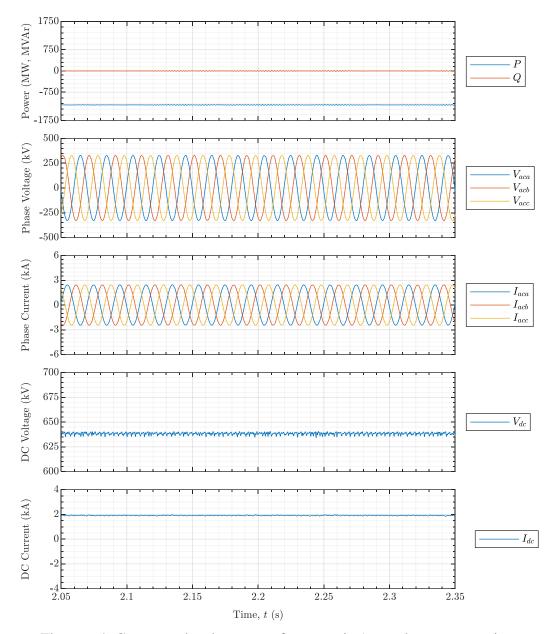

| D-1    | Scenario 1: Steady State Power Import                                | 189 |

| D-2    | Scenario 2: Power Flow Reversal                                      | 195 |

| D-3    | Scenario 3: AC 3 Phase-ground Fault                                  | 201 |

| Annend | lix E - CHP Sensing and Measurement Circuit Modifications            | 207 |

# **List of Figures**

| Figure 1.1: | Subsea HVAC vs. HVDC transmission scheme break-even distance                                 | 5 |

|-------------|----------------------------------------------------------------------------------------------|---|

| Figure 2.1: | Circuit diagram of (a) modular multilevel converter, and (b) a half-bridge                   |   |

|             | submodule3                                                                                   | 5 |

| Figure 2.2: | Modular multilevel converter equivalent circuit for a single phase3                          | 6 |

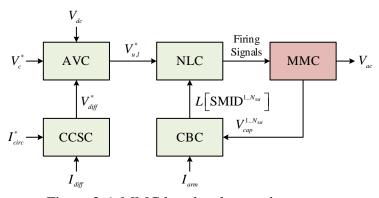

| Figure 2.3: | MMC cascaded control system overview                                                         | 9 |

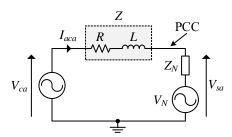

| Figure 2.4: | MMC connection to AC system, one phase shown4                                                | 0 |

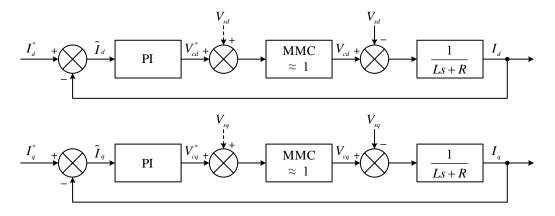

| Figure 2.5: | State feedback system block diagrams for MMC dq current control loop4                        | 2 |

| Figure 2.6: | MMC low-level control structure                                                              | 3 |

| Figure 2.7: | Equivalent circuit for a single phase of an MMC4                                             | 4 |

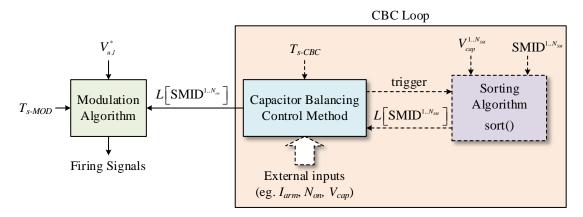

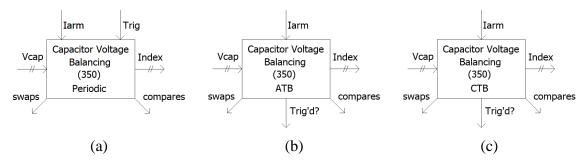

| Figure 3.1: | Block diagram showing relationship between modulation algorithm, CBC                         |   |

|             | method, and sorting algorithm4                                                               | 9 |

| Figure 3.2: | CBC method taxonomy based upon sorting algorithm requirements5                               | 1 |

| Figure 3.3: | CBC method taxonomy based upon CBC loop sampling period properties5                          | 5 |

| Figure 4.1: | Common growth functions for sorting algorithm execution time and resource                    |   |

|             | usage5                                                                                       | 9 |

| Figure 4.2: | Compare-swap operator                                                                        | 2 |

| Figure 4.3: | Categorisation of sorting algorithms and processing hardware on sequential vs.               |   |

|             | parallel sliding scale6                                                                      | 3 |

| Figure 5.1: | MMC model circuit diagram6                                                                   | 6 |

| Figure 5.2: | Block diagram showing MMC model control structure                                            | 7 |

| Figure 5.3: | PSCAD/EMTDC custom capacitor balancing control component mask 6                              | 9 |

| Figure 5.4: | Flowchart showing periodic capacitor balancing control method sequence of                    |   |

|             | operations                                                                                   | 2 |

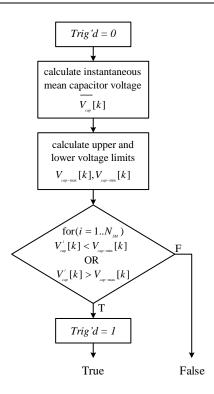

| Figure 5.5: | Flowchart showing trigger decision tree for average tolerance band CBC                       |   |

|             | method                                                                                       | 3 |

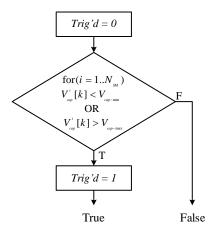

| Figure 5.6: | Flowchart showing trigger decision tree for cell tolerance band CBC method 7                 | 4 |

| Figure 6.1: | Execution time range as a function of number of inputs vs. sorting algorithm 8               | 4 |

| Figure 6.2: | Timing diagram showing the relationship between $T_{s-control}$ , $T_{s-CBC}$ , $t_{sort}$ , |   |

|             | $M_{control}$ , $M_{CBC}$ , against sampling instant number, $k$                             | 8 |

| Figure 6.3: | Timing diagram showing the relationship between $M_{control}[k]$ ,                           |   |

|             | $M_{control-thresh}$ , and total number of CBC loop sampling instants9                       | 1 |

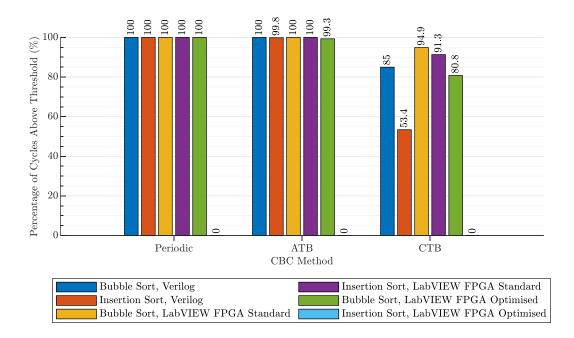

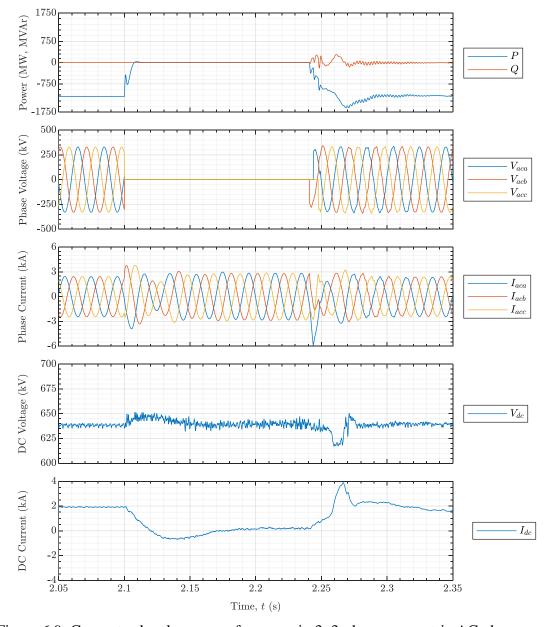

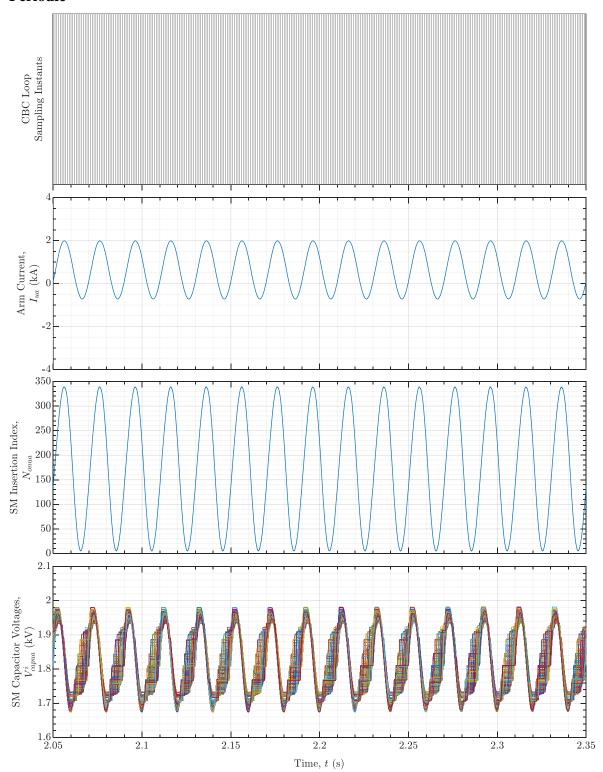

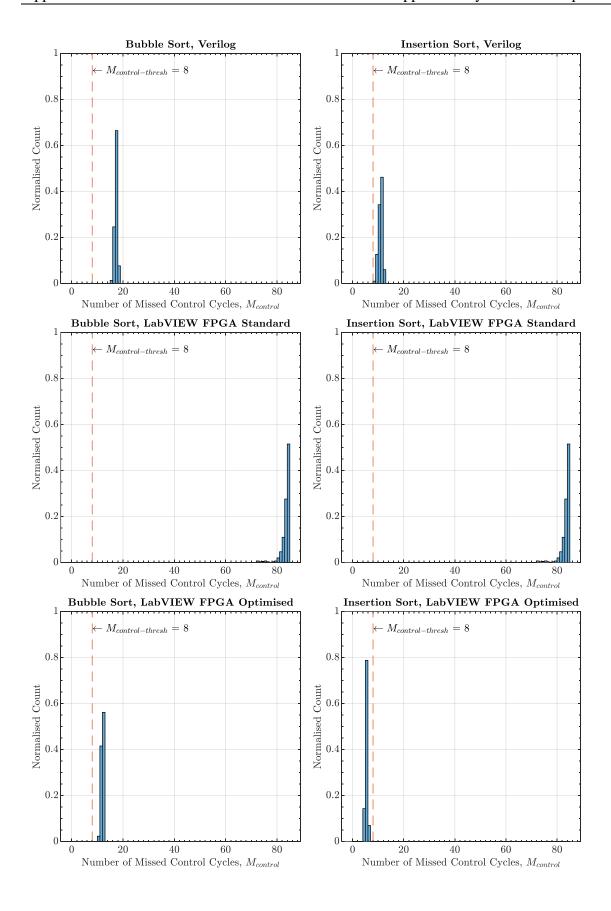

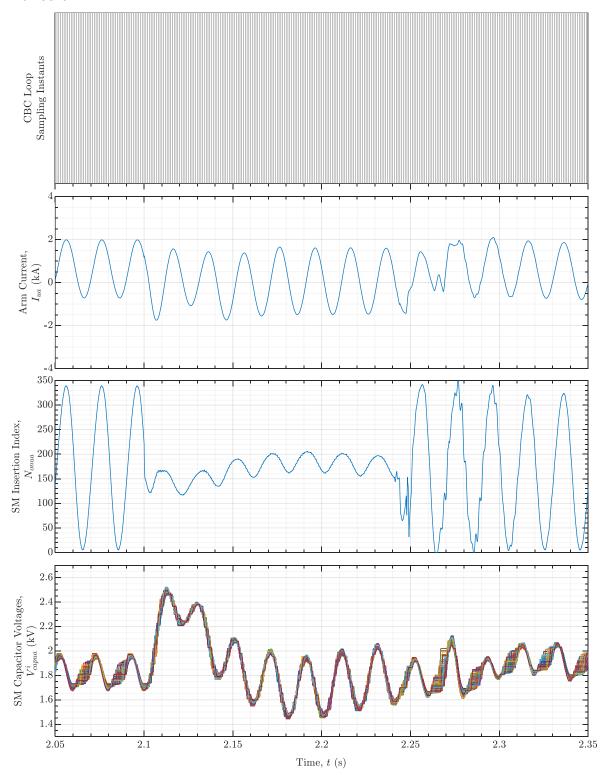

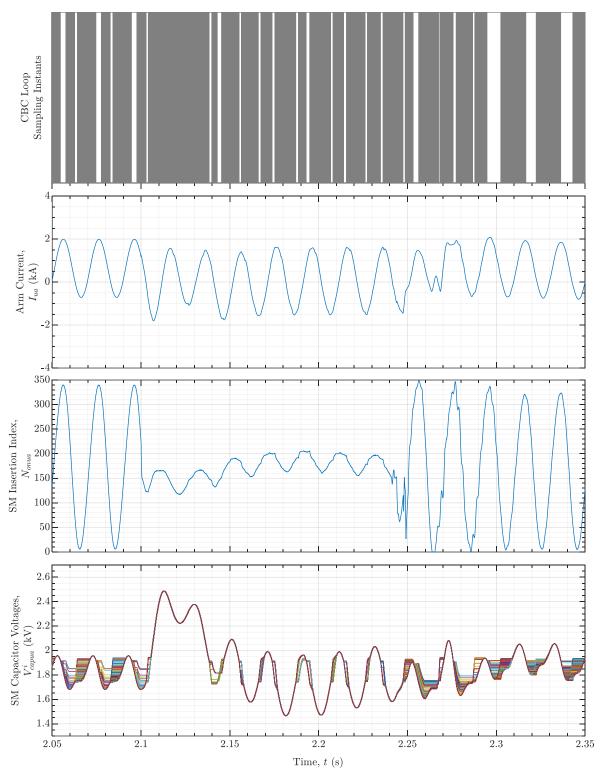

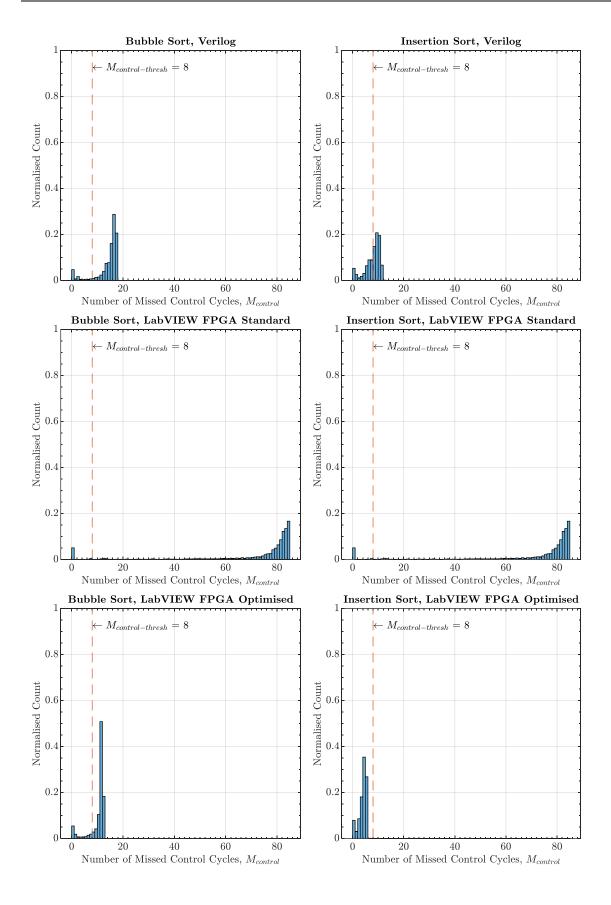

| Figure 6.4: | Converter-level response for scenario 1                                                      | 3 |

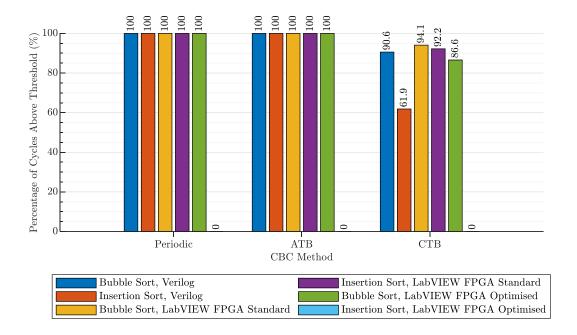

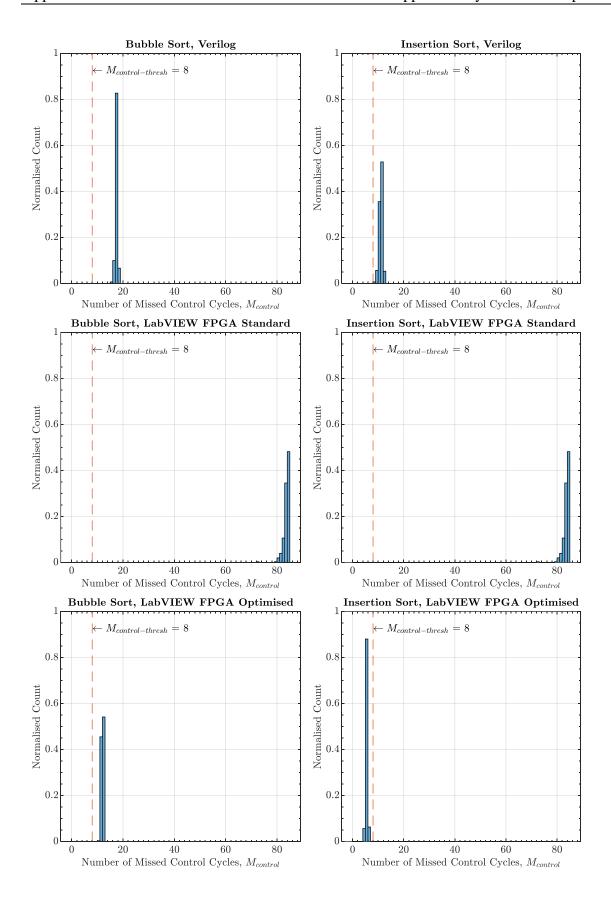

| Figure 6.5: Percentage of CBC loop cycles where $M_{control-thresh} = 8$ was exceeded for   |

|---------------------------------------------------------------------------------------------|

| scenario 194                                                                                |

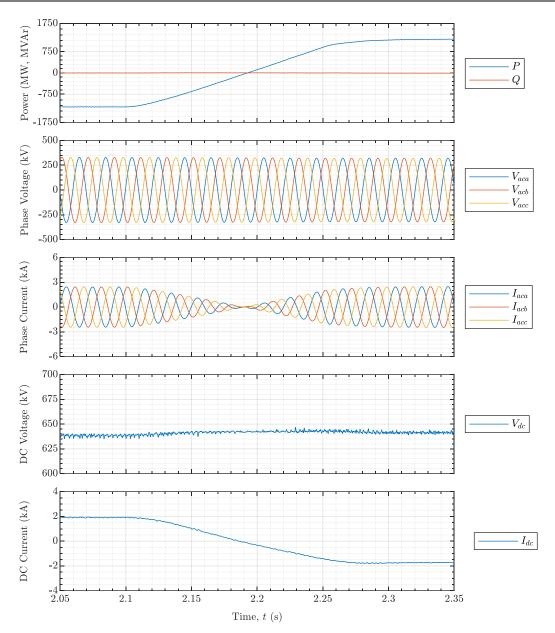

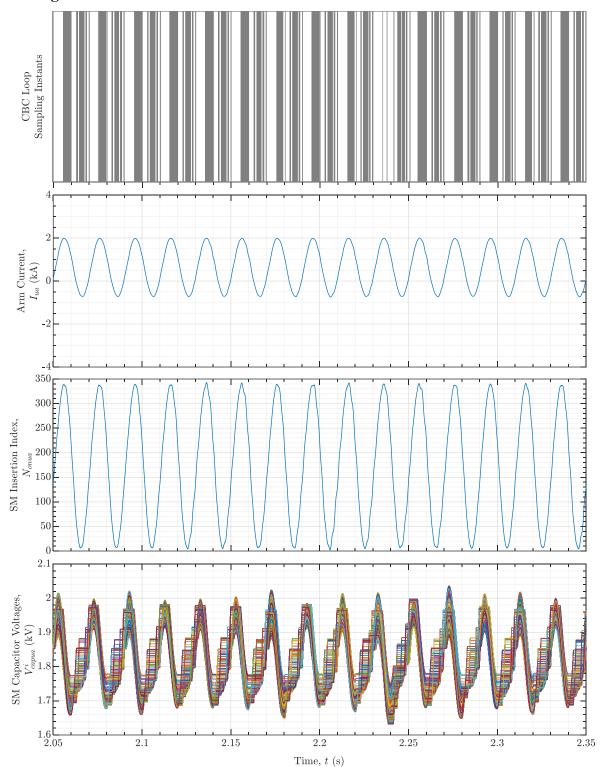

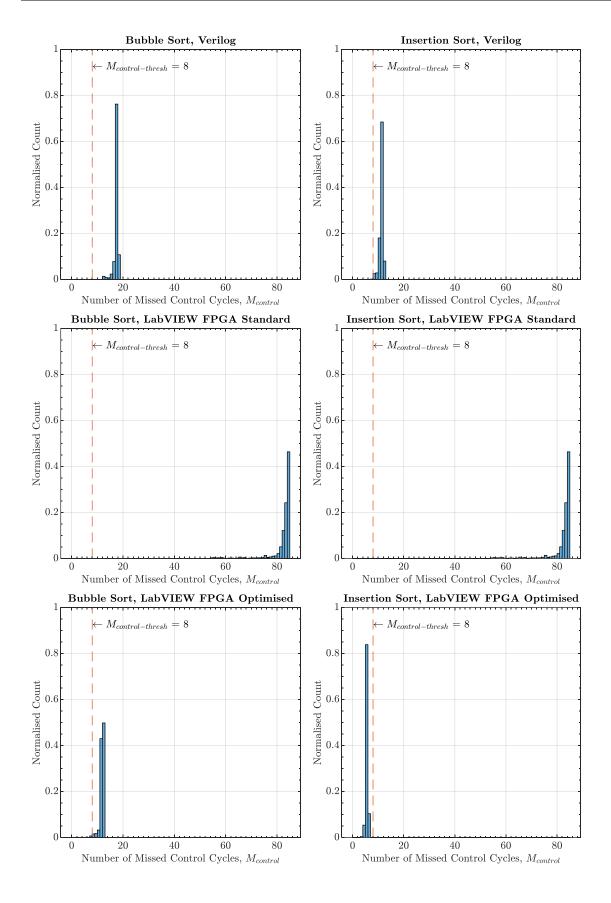

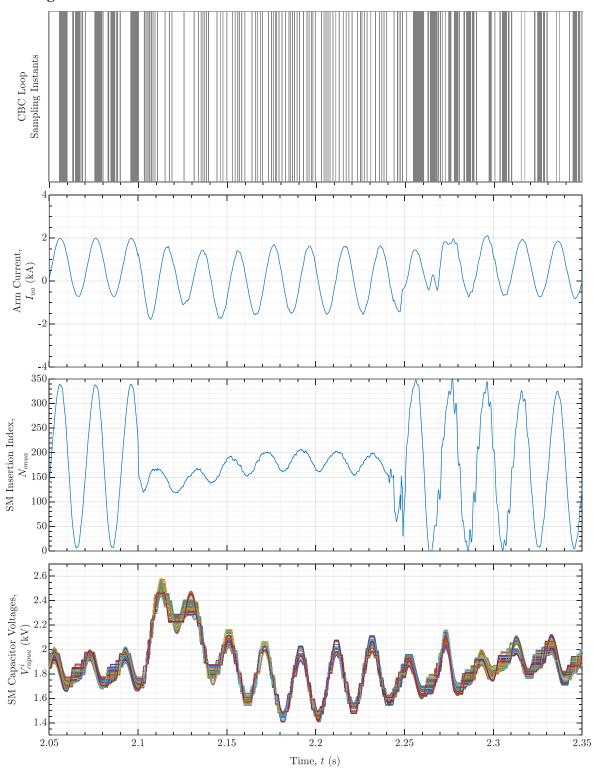

| Figure 6.6: Converter-level response for scenario 2                                         |

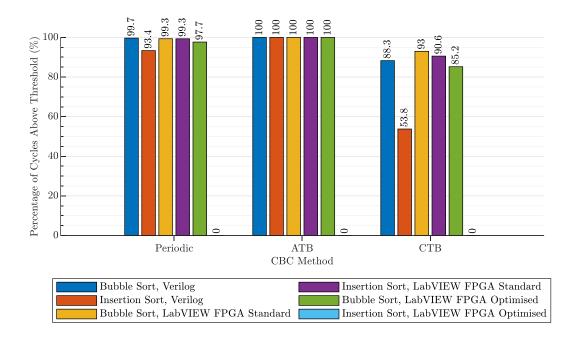

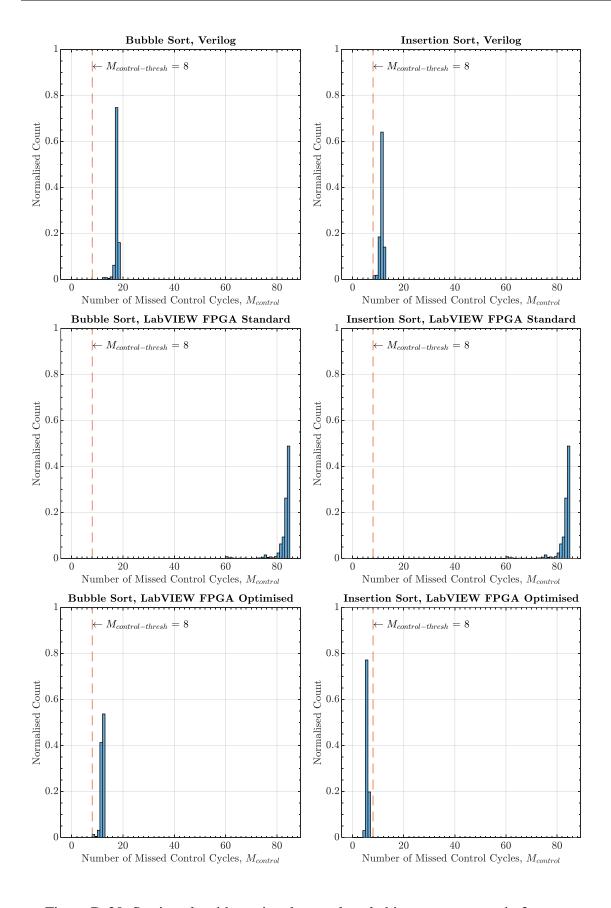

| Figure 6.7: Percentage of CBC loop cycles where $M_{control-thresh} = 8$ was exceeded for   |

| scenario 296                                                                                |

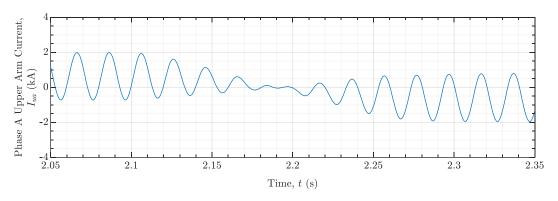

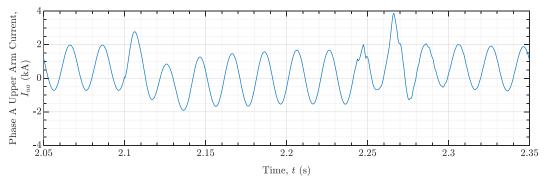

| Figure 6.8: Phase A, upper arm current for scenario 2                                       |

| Figure 6.9: Converter-level response for scenario 3                                         |

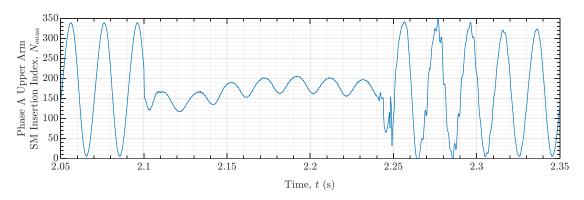

| Figure 6.10: Percentage of CBC loop cycles where $M_{control-thresh} = 8$ was exceeded for  |

| scenario 399                                                                                |

| Figure 6.11: Phase A, upper arm current for scenario 3                                      |

| Figure 6.12: Phase A, upper arm SM insertion index for scenario 3                           |

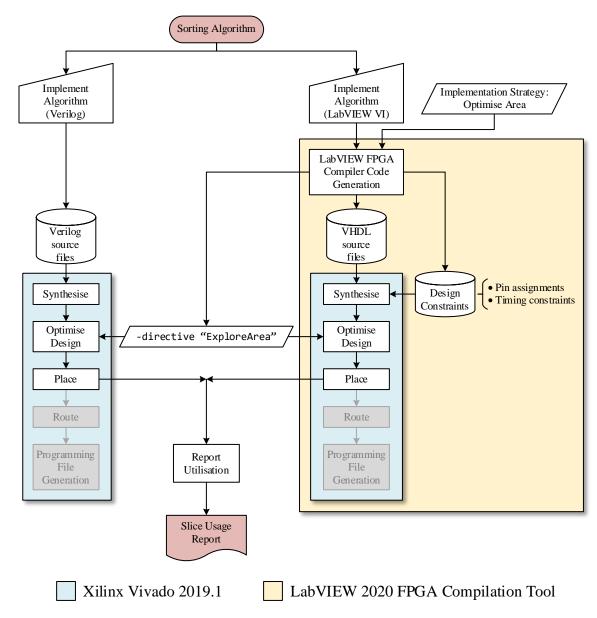

| Figure 6.13: Synthesis process for sorting algorithm logic resource usage measurements      |

|                                                                                             |

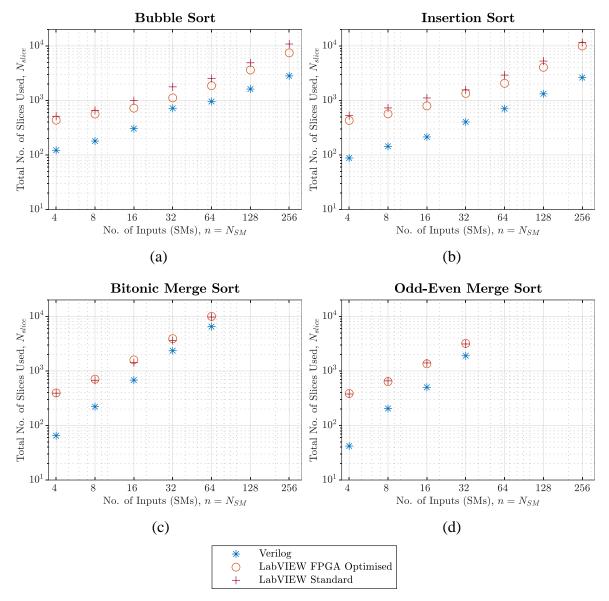

| Figure 6.14: Plot of total number of slices used vs. number of inputs vs. programming       |

| method107                                                                                   |

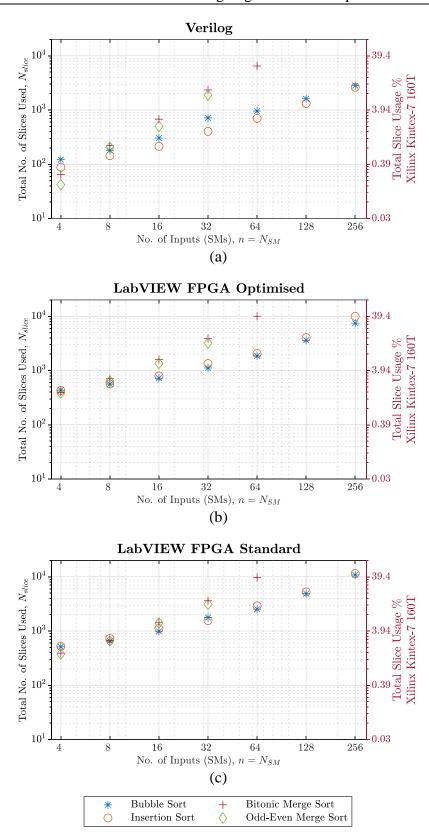

| Figure 6.15: Plot of total number of slices used vs. number of inputs vs. sorting algorithm |

| 110                                                                                         |

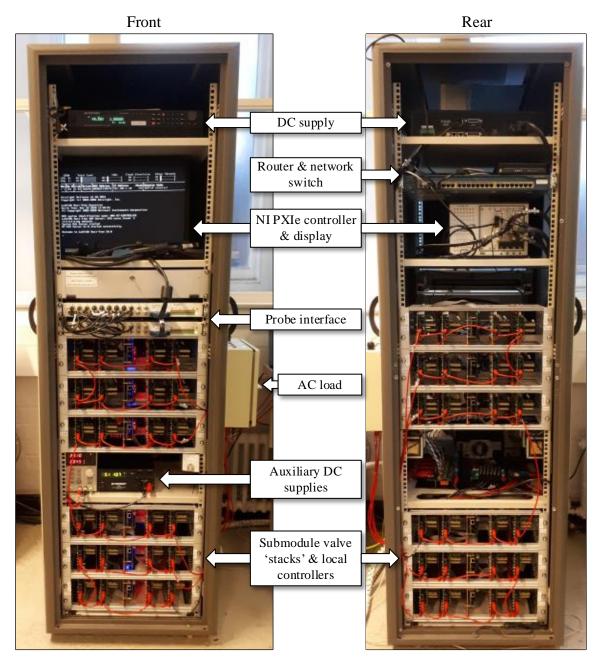

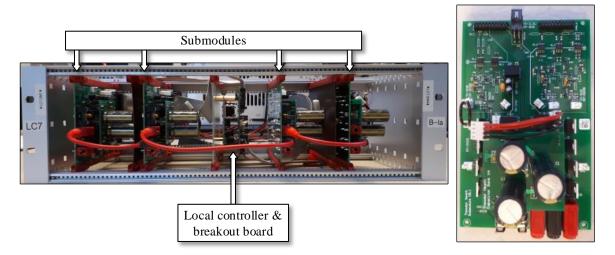

| Figure 7.1: Annotated CHP system hardware layout, front (left) and rear (right)116          |

| Figure 7.2: CHP submodule simplified schematic                                              |

| Figure 7.3: Four SM valve 'stack' and local controller (left) and individual SM (right)120  |

| Figure 7.4: CHP distributed control architecture overview                                   |

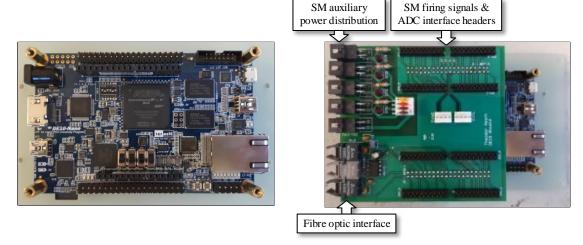

| Figure 7.5: NI PXIe system with CCU, DAQ, ACU, and PCU cards (left to right)126             |

| Figure 7.6: Terasic DE-10 Nano Local Controller (left), with breakout board installed       |

| (right)126                                                                                  |

| Figure 8.1: CHP PXIe system internal architecture (existing control software)132            |

| Figure 8.2: CHP PXIe system internal architecture (new control software)135                 |

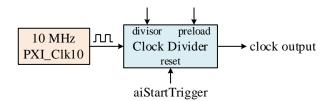

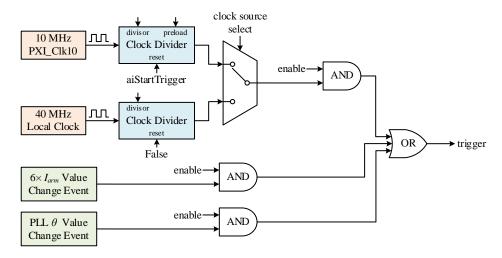

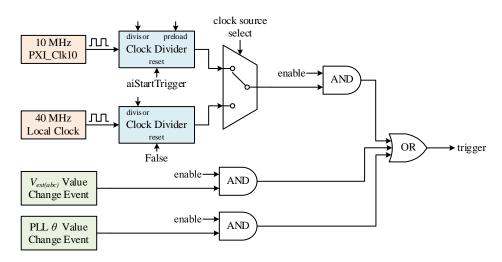

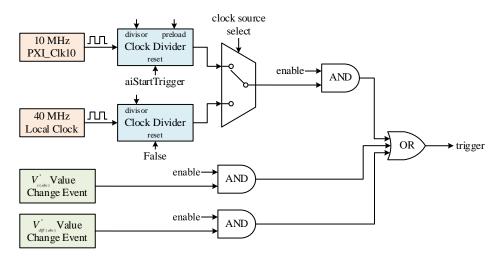

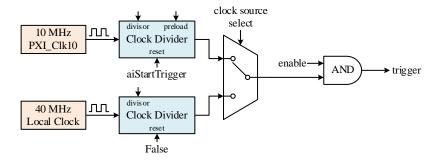

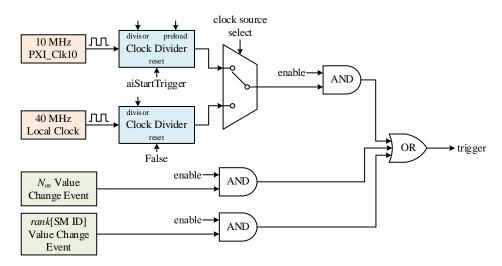

| Figure 8.3: Controller sample clock generator functional overview                           |

| Figure 8.4: <i>PXI_Clk10</i> clock divider block architecture                               |

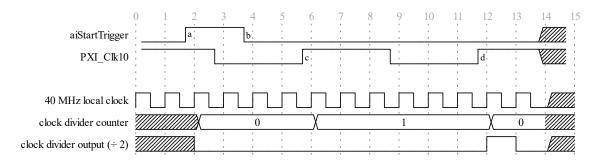

| Figure 8.5: Timing diagram of global PXIe system synchronisation signals and PCU/ACU        |

| FPGA internal signals                                                                       |

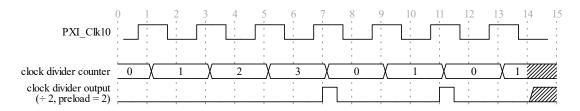

| Figure 8.6: Timing diagram showing operation of the clock divider block preload input       |

| terminal139                                                                                 |

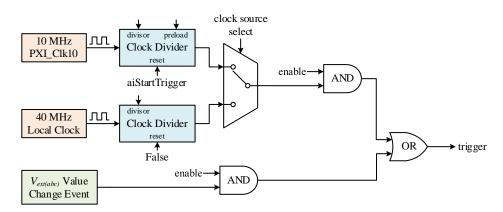

| Figure 8.7: External reference voltage PLL sample clock sources                             |

| Figure 8.8: Circulating current suppression control loop sample clock sources141            |

| Figure 8.9: Output voltage control loop sample clock sources                            | 141  |

|-----------------------------------------------------------------------------------------|------|

| Figure 8.10: Arm balancing and NLC sample clock sources                                 | 142  |

| Figure 8.11: Capacitor balancing control loop sample clock sources                      | 142  |

| Figure 8.12: Firing signal generation loop sample clock sources                         | 143  |

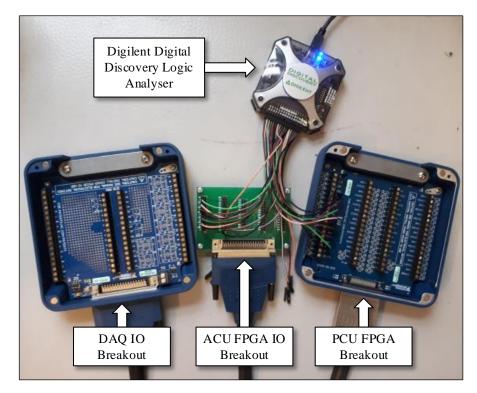

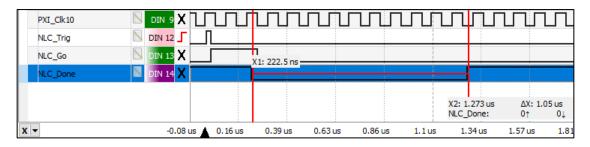

| Figure 8.13: CHP control loop hardware delay measurement set up                         | 144  |

| Figure 8.14: NLC loop timing data acquisition from logic analyser                       | 144  |

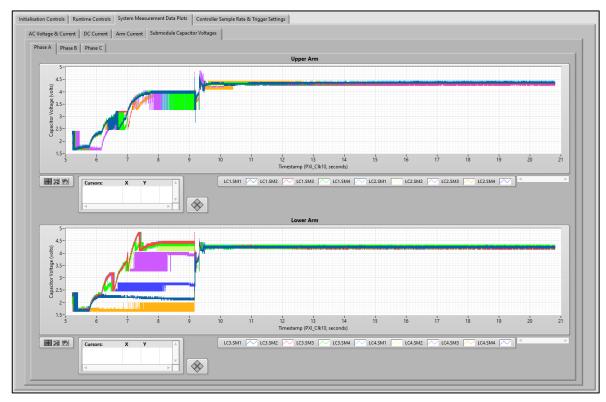

| Figure 8.15: Screen capture of HMI PC user interface showing CHP SM capacitor vol       | tage |

| plots using data transferred from ACU FPGA                                              | 146  |

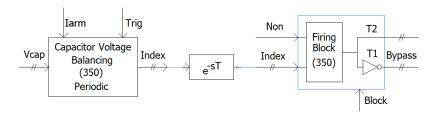

| Figure C-1: PSCAD/EMTDC MMC model $e^{-sT}$ delay block location                        | 183  |

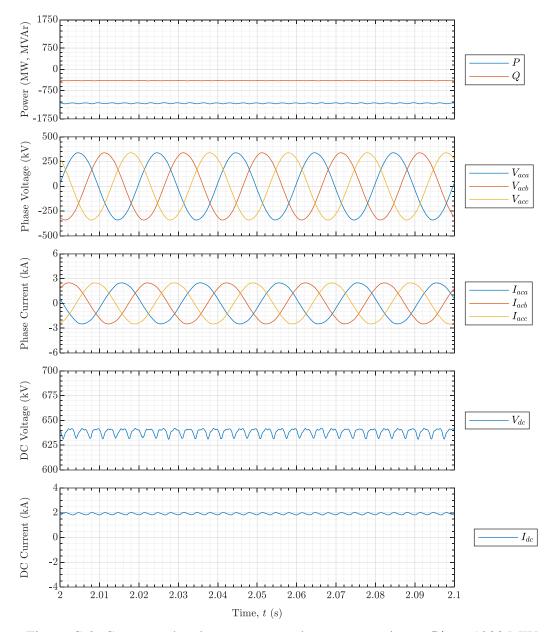

| Figure C-2: Converter level response, steady state operation at $P^* = -1200$ MW,       |      |

| $Q^* = -400$ MVAr (import, inverter mode)                                               | 184  |

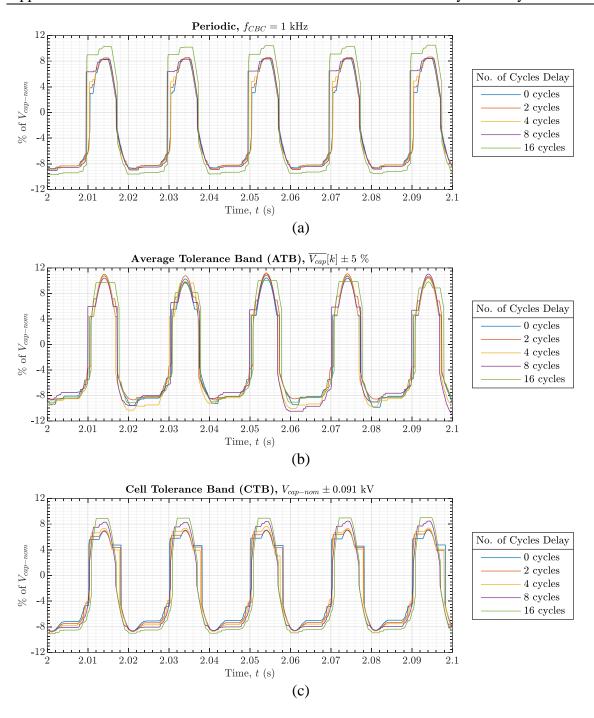

| Figure C-3: Maximum instantaneous capacitor voltage deviation from $V_{cap-nom}$ as a   |      |

| percentage of $V_{cap-nom}$ at different delay lengths                                  | 185  |

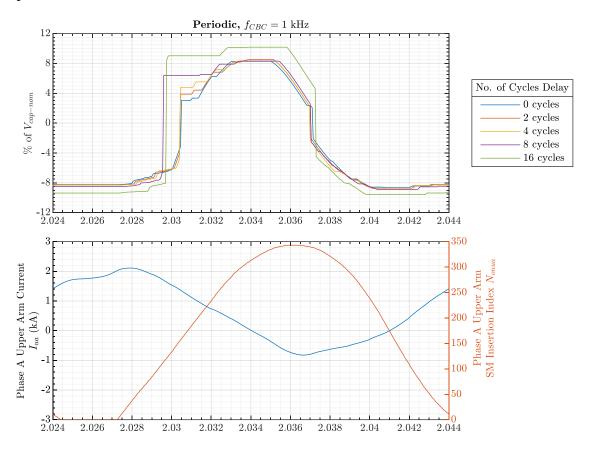

| Figure C-4: Zoomed-in plot of maximum instantaneous deviation from $V_{cap-nom}$ as a   |      |

| percentage of $V_{cap-nom}$ at different delay lengths (top), and phase A upper         | arm  |

| current (bottom, left-hand y-axis) and phase A upper arm SM insertion inc               | lex  |

| (bottom, right-hand y-axis)                                                             | 186  |

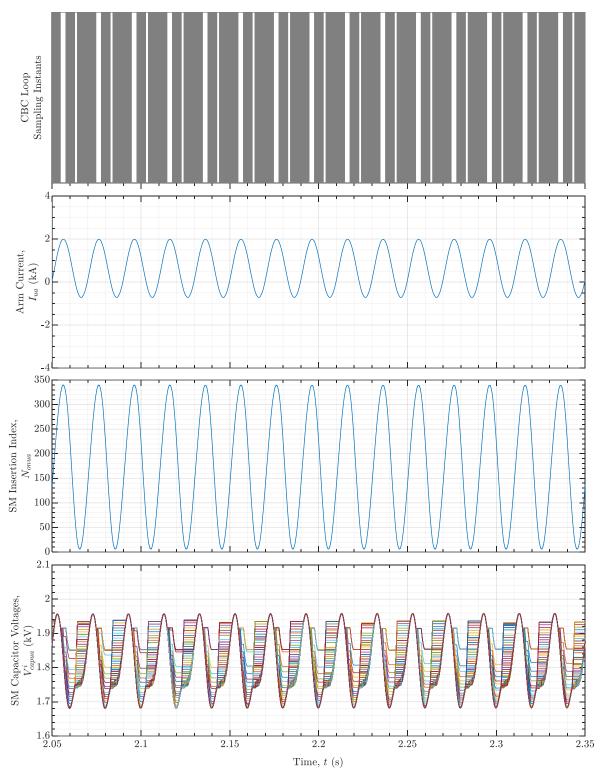

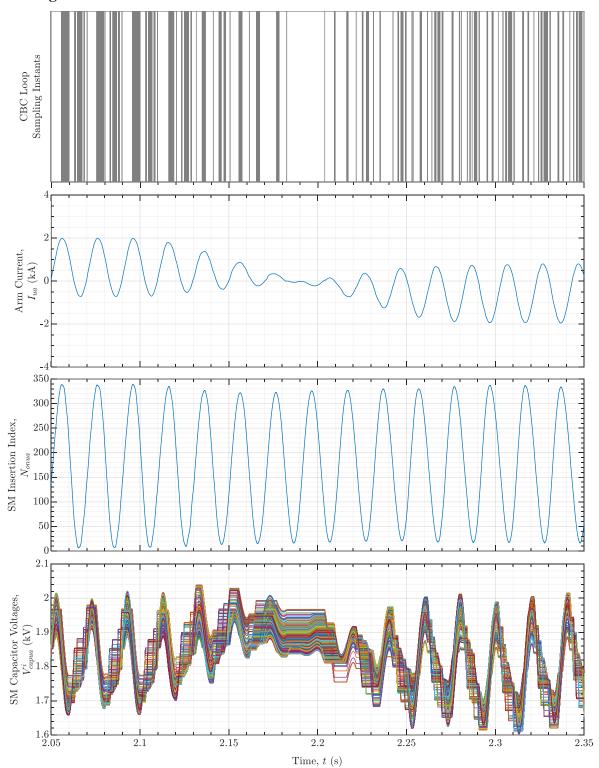

| Figure D-5: Upper arm electrical quantities, scenario 1, periodic CBC                   | 189  |

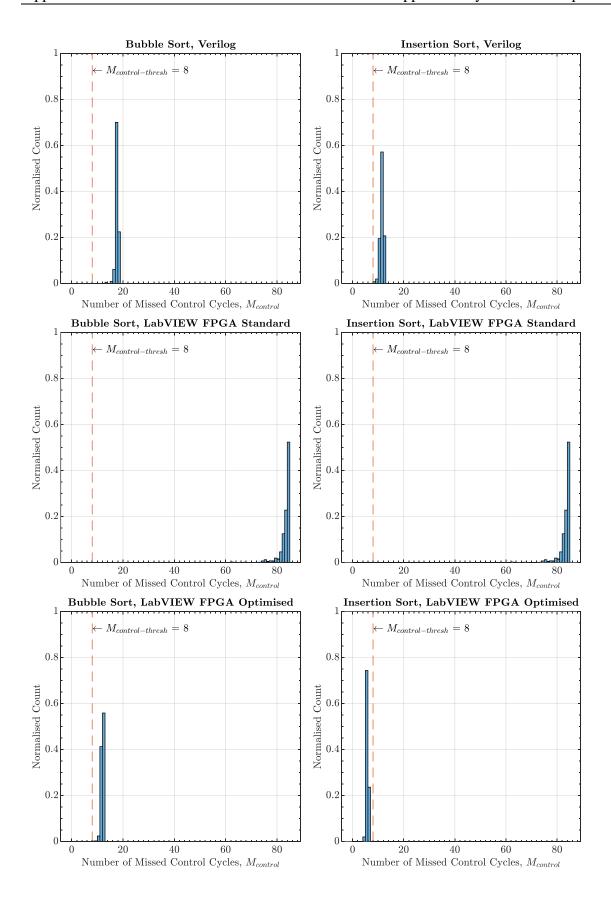

| Figure D-6: Sorting algorithm missed control cycle histograms, scenario 1, periodic C   | BC   |

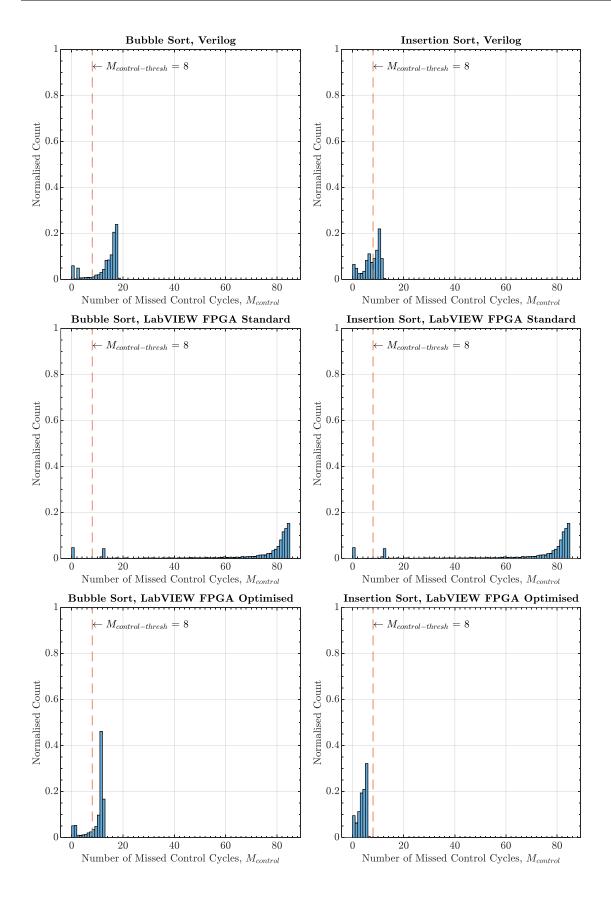

|                                                                                         | 190  |

| Figure D-7: Upper arm electrical quantities, scenario 1, average tolerance band CBC     | 191  |

| Figure D-8: Sorting algorithm missed control cycle histograms, scenario 1, average      |      |

| tolerance band CBC                                                                      | 192  |

| Figure D-9: Upper arm electrical quantities, scenario 1, cell tolerance band CBC        | 193  |

| Figure D-10: Sorting algorithm missed control cycle histograms, scenario 1, cell tolera | ance |

| band CBC                                                                                | 194  |

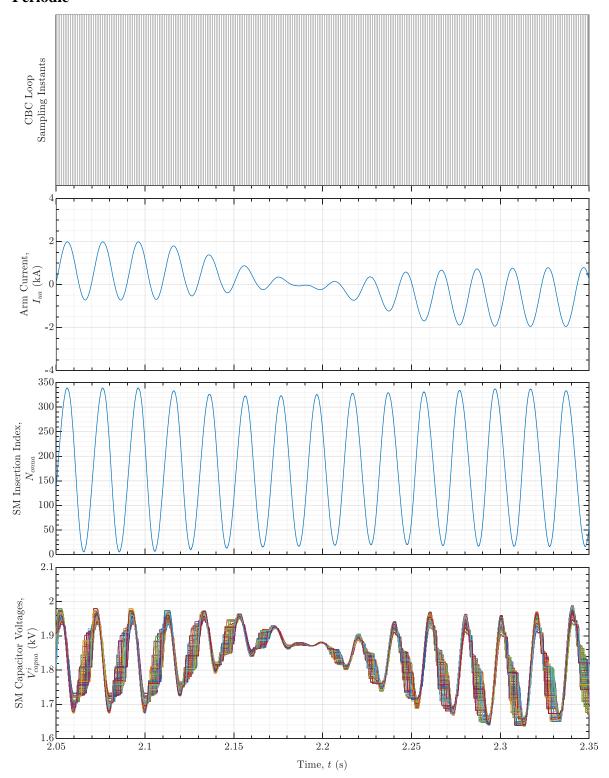

| Figure D-11: Upper arm electrical quantities, scenario 2, periodic CBC                  | 195  |

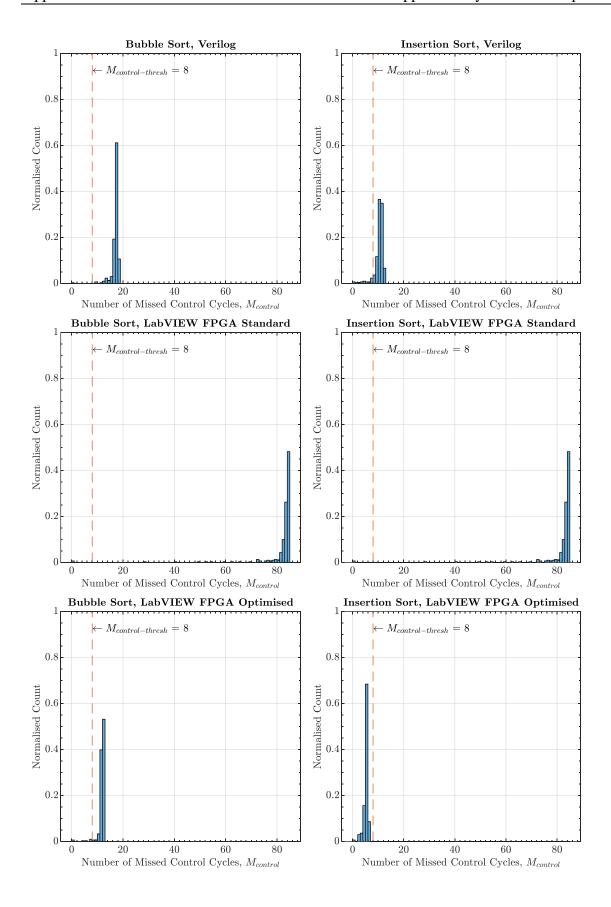

| Figure D-12: Sorting algorithm missed control cycle histograms, scenario 2, periodic C  | СВС  |

|                                                                                         | 196  |

| Figure D-13: Upper arm electrical quantities, scenario 2, average tolerance band CBC    | 197  |

| Figure D-14: Sorting algorithm missed control cycle histograms, scenario 2, average     |      |

| tolerance band CBC                                                                      | 198  |

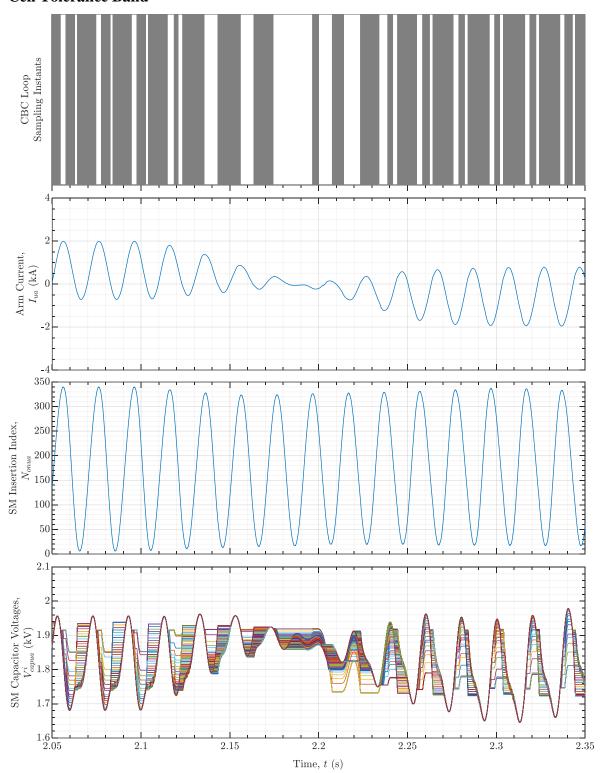

| Figure D-15: Upper arm electrical quantities, scenario 2, cell tolerance band CBC       | 199  |

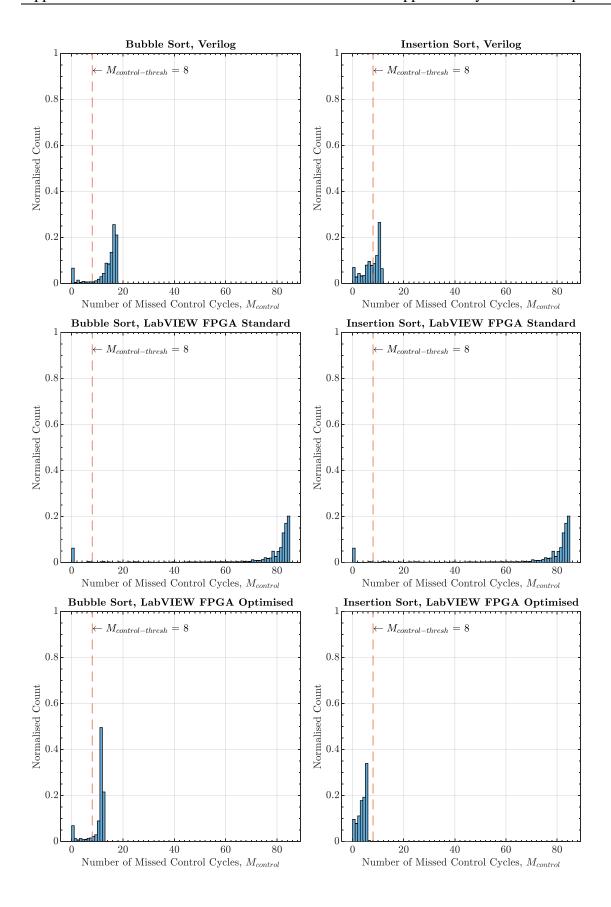

| Figure D-16: Sorting algorithm missed control cycle histograms, scenario 2, cell tolerance |

|--------------------------------------------------------------------------------------------|

| band CBC200                                                                                |

| Figure D-17: Upper arm electrical quantities, scenario 3, periodic CBC201                  |

| Figure D-18: Sorting algorithm missed control cycle histograms, scenario 3, periodic CBC   |

| 202                                                                                        |

| Figure D-19: Upper arm electrical quantities, scenario 3, average tolerance band CBC203    |

| Figure D-20: Sorting algorithm missed control cycle histograms, scenario 3, average        |

| tolerance band CBC204                                                                      |

| Figure D-21: Upper arm electrical quantities, scenario 3, cell tolerance band CBC205       |

| Figure D-22: Sorting algorithm missed control cycle histograms, scenario 3, cell tolerance |

| band CBC200                                                                                |

# **List of Tables**

| Table 2.1: Half-bridge submodule switch states                                          |

|-----------------------------------------------------------------------------------------|

| Table 4.1: Best- and worst-case time complexities for several common sorting algorithms |

| for sorting-based CBC methods                                                           |

| Table 4.2: Worst-case space complexities for several common sorting algorithms for      |

| sorting-based CBC methods                                                               |

| Table 5.1: MMC model parameters                                                         |

| Table 6.1: Summary of key specifications for control hardware targets                   |

| Table 6.2: Comparison of sorting algorithm programming methods                          |

| Table 6.3: Matrix of sorting algorithms, control hardware targets and programming       |

| languages tested                                                                        |

| Table 6.4: List of sorting algorithms and programming method combinations tested91      |

| Table 6.5: Total number of CBC loop sampling instances per CBC method, scenario 1 94    |

| Table 6.6: Total number of CBC loop sampling instances per CBC method, scenario 2 97    |

| Table 6.7: Total number of CBC loop sampling instances per CBC method, scenario 3 . 101 |

| Table 7.1: CHP nominal electrical ratings (present configuration)                       |

| Table 7.2: List of CHP auxiliary hardware and functions                                 |

| Table 7.3: CHP submodule electrical ratings                                             |

| Table 7.4: CHP submodule component key specifications                                   |

| Table 8.1: Summary of CHP control hardware targets and LabVIEW variants129              |

| Table 8.2: CHP LabVIEW FPGA control software FPGA slice resource usage summary          |

| 147                                                                                     |

# **List of Source Code Listings**

| Listing A-1: Bubble Sort algorithm pseudocode                                     | .166 |

|-----------------------------------------------------------------------------------|------|

| Listing A-2: Insertion Sort algorithm pseudocode                                  | .167 |

| Listing A-3: Merge Sort algorithm pseudocode                                      | .169 |

| Listing A-4: Quick Sort algorithm pseudocode                                      | .171 |

| Listing B-1: Custom component common FORTRAN source code, part 1                  | .174 |

| Listing B-2: Custom component common FORTRAN source code, part 2                  | .175 |

| Listing B-3: Periodic CBC method FORTRAN source code                              | .176 |

| Listing B-4: Average Tolerance Band CBC method FORTRAN source code                | .176 |

| Listing B-5: Cell Tolerance Band CBC method FORTRAN source code                   | .176 |

| Listing B-6: Bubble Sort algorithm FORTRAN source code, ascending sort direction  | .177 |

| Listing B-7: Bubble Sort algorithm FORTRAN source code, descending sort direction | .178 |

# Nomenclature

# **List of Acronyms**

| Acronym      | Definition                                                                       |

|--------------|----------------------------------------------------------------------------------|

| AC           | Alternating Current                                                              |

| ACU          | Arm Control Unit                                                                 |

| ADC          | Analogue-to-Digital Converter                                                    |

| ATB          | Average Tolerance Band (capacitor balancing control method)                      |

| AVC          | Arm Voltage Control                                                              |

| CAGR         | Compound Annual Growth Rate                                                      |

| CBC          | Capacitor Balancing Control                                                      |

| CCSC         | Circulating Current Suppression Control                                          |

| CCU          | Converter Control Unit                                                           |

| CHP          | Converter Hardware Prototype                                                     |

| CPU          | Central Processing Unit                                                          |

| CSC          | Current Source Converter                                                         |

| СТВ          | Cell Tolerance Band (capacitor balancing control method)                         |

| CTBoptimised | Cell Tolerance Band Optimised (capacitor balancing control method)               |

| CTBsequence  | Cell Tolerance Band with Sequence Reversing (capacitor balancing control method) |

| DAQ          | Data Acquisition                                                                 |

| DC           | Direct Current                                                                   |

| DMA          | Direct Memory Access                                                             |

| DSP          | Digital Signal Processor                                                         |

| EMT          | Electromagnetic Transient                                                        |

| ESO          | Electricity System Operator                                                      |

| FB-SM        | Full-Bridge Submodule                                                            |

**Acronym** Definition

FF Flip-Flop

FIFO First-In First-Out

FOBB Fibre Optic Breakout Board

FPGA Field Programmable Gate Array

FSM Finite-State Machine

GB/s Gigabytes per second

GUI Graphical User Interface

HB-SM Half-Bridge Submodule

HDL Hardware Description Language

HMI Human-Machine Interface

HVAC High Voltage Alternating Current

HVDC High Voltage Direct Current

IGBT Insulated Gate Bipolar Transistor

IO Input-Output

KVL Kirchoff's Voltage Law

LAN Local Area Network

LC Local Controller

LUT Lookup Table

MB/s Megabytes per second

Mbps Megabit per second

MMC Modular Multilevel Converter

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MPI Multi-Purpose Interconnector

MSa/s Mega samples per second

MT-HVDC Multi-Terminal High Voltage Direct Current

**Acronym** Definition

NI National Instruments

NLC Nearest Level Control

OS Operating System

OTNR Offshore Transmission Network Review

P Proportional (control)

PCB Printed Circuit Board

PCC Point of Common Coupling

PCI Peripheral Component Interconnect

PCIe PCI Express

PCU Phase Control Unit

PD-PWM Phase Disposition Pulse-Width Modulation

PI Proportional Integral

PIB Power Interface Board

PLL Phase-Locked Loop

PR Proportional Resonant

PSC-PWM Phase-Shifted Carrier Pulse-Width Modulation

PV Photo-Voltaic

PWM Pulse-Width Modulation

PXI PCI eXtensions for Instrumentation

PXIe PCIe eXtensions for Instrumentation

RAM Random-Access Memory

RSF Reduced Switching Frequency

RT Real-Time

RTL Register Transfer Level

RTOS Real-Time Operating System

**Acronym Definition**

SCR Short-Circuit Ratio

SCTL Single-Cycle Timed Loop

SM Submodule

SMID Submodule Identifier

SoC System-on-Chip

SPI Serial Peripheral Interface

TSO Transmission System Operator

UART Universal Asynchronous Receiver-Transmitter

VCO Voltage-Controlled Oscillator

VI Virtual Instrument

VSC Voltage Source Converter

# List of Symbols

| Symbol          | Definition                                                                                                     | S.I. Units |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------|------------|--|--|

| $C_{SM}$        | Submodule capacitance                                                                                          | F          |  |  |

| $f_0$           | AC system fundamental frequency                                                                                | Hz         |  |  |

| $f_{clock}$     | FPGA clock frequency                                                                                           | Hz         |  |  |

| $f_{s-control}$ | Control cycle sampling frequency $(1/T_{s-control})$                                                           |            |  |  |

| $f_{s-CBC}$     | Capacitor balancing control method sampling frequency $(1/T_{s-CBC})$                                          |            |  |  |

| $f_{s-MOD}$     | Modulation algorithm sampling frequency $(1/T_{s-MOD})$                                                        | Hz         |  |  |

| $I_{dc}$        | DC bus current                                                                                                 | A          |  |  |

| $I_{ac(abc)}$   | AC output current, per phase                                                                                   | A          |  |  |

| $I_{u(abc)}$    | Upper arm current, per phase                                                                                   | A          |  |  |

| $I_{l(abc)}$    | Lower arm current, per phase                                                                                   | A          |  |  |

| $I_{circ(abc)}$ | Circulating current, per phase                                                                                 |            |  |  |

| $I_{diff(abc)}$ | Difference current                                                                                             | A          |  |  |

| $I_{DS}$        | MOSFET drain-source current                                                                                    |            |  |  |

| k               | Sampling instant number                                                                                        | _          |  |  |

| $L_{arm}$       | Arm inductance                                                                                                 |            |  |  |

| $m_{a-(abc)}$   | Modulation index, per phase                                                                                    |            |  |  |

| $M_{control}$   | Number of samples delay due to sorting algorithm, relative to control cycle sampling period                    |            |  |  |

| $M_{CBC}$       | Number of samples delay due to sorting algorithm, relative to capacitor balancing control loop sampling period |            |  |  |

| $N_{SM}$        | Number of submodules per arm                                                                                   | _          |  |  |

| $N_{level}$     | Number of output voltage levels                                                                                | _          |  |  |

| $N_{onu(abc)}$  | Upper arm submodule insertion index, per phase                                                                 | _          |  |  |

| $N_{onl(abc)}$  | Lower arm submodule insertion index, per phase                                                                 | _          |  |  |

| Symbol          | Definition                                                         | S.I. Units |

|-----------------|--------------------------------------------------------------------|------------|

| n               | Number of array elements to sort                                   | _          |

| $N_{slice}$     | Total number of FPGA slices used                                   | _          |

| P               | Active power                                                       | W          |

| p               | Derivative operator $(d/dt)$                                       | _          |

| Q               | Reactive power                                                     | VAr        |

| $R_{arm}$       | Arm resistance                                                     | Ω          |

| $R_{load}$      | Load resistance                                                    | Ω          |

| $R_{DS(on)}$    | MOSFET on resistance                                               | Ω          |

| $R_{dis}$       | Discharge resistance                                               | Ω          |

| S               | Apparent power                                                     | VA         |

| $S_T$           | Transformer apparent power                                         | VA         |

| $T_{s-MOD}$     | Modulation algorithm sampling period $(1/f_{s-MOD})$               | s          |

| $T_{s-CBC}$     | Capacitor balancing control method sampling period $(1/f_{s-CBC})$ | s          |

| $T_{s-control}$ | Control cycle sampling period $(1/f_{s-control})$                  | s          |

| $t_{sort}$      | Sorting algorithm execution time                                   | S          |

| $V_{dc}$        | DC bus voltage (pole-pole)                                         | V          |

| $V_{ac(abc)}$   | AC phase-neutral voltage, per-phase                                | V          |

| $V_{s(abc)}$    | AC system voltage at point of common coupling, per phase           | V          |

| $V_{c(abc)}$    | Internal converter voltage, per phase                              | V          |

| $V_N$           | AC network voltage, per phase                                      | V          |

| $V_{diff(abc)}$ | Difference voltage                                                 | V          |

| $V_{ext(abc)}$  | External voltage reference, per phase                              | V          |

| $V_{SM}$        | Submodule output voltage                                           | V          |

| $V_{u(abc)}$    | Upper arm voltage, per phase                                       | V          |

| Symbol                   | Definition                                                           | S.I. Units |

|--------------------------|----------------------------------------------------------------------|------------|

| $V_{l(abc)}$             | Lower arm voltage, per phase                                         | V          |

| $V^i_{capu(abc)}$        | Upper arm capacitor voltage, $i^{th}$ capacitor, per phase           | V          |

| $V_{capl(abc)}^{i}$      | Lower arm capacitor voltage, $i^{th}$ capacitor, per phase           | V          |

| $V_{cap-nom}$            | Nominal submodule capacitor voltage                                  | V          |

| $V_{capu,l}^{\Sigma}(t)$ | Instantaneous sum capacitor voltage                                  | V          |

| $\overline{V_{cap}}$     | Mean capacitor voltage                                               | V          |

| $\overline{V_{cap}}(t)$  | Instantaneous mean capacitor voltage                                 | V          |

| $V_{DS}$                 | MOSFET drain-source voltage                                          | V          |

| $X_T$                    | Transformer leakage reactance                                        | Ω          |

| <i>x</i> *               | Reference                                                            | _          |

| $\overline{x}$           | Mean                                                                 | _          |

| $\widetilde{x}$          | Error                                                                | _          |

| $Z_L$                    | Load impedance                                                       | $\Omega$   |

| $Z_N$                    | AC network impedance                                                 | Ω          |

| $\delta_{ATB}$           | Tolerance band for average tolerance band capacitor balancing method | V          |

| $	heta_{abc}$            | Phase angle, per phase                                               | rad        |

### **Abstract**

Name of University: The University of Manchester

Candidate's Name: Jack Andrews

Degree Title: Doctor of Philosophy

Thesis Title: Computational and Communication Architectures for Modular Multilevel

Converter Construction

Date: November 2022

Renewable sources of electricity generation currently provide 47 % of the UK's total installed capacity. Offshore wind accounts for 13 % of the total and is set to increase significantly over the next decade, driven by the UK Government's target to reach net zero by the year 2050. An increasing number of offshore wind farms will use voltage source converter (VSC) high voltage direct current (HVDC) transmission schemes to transfer power to the onshore electricity grid. VSC-HVDC transmission is also being used to support the integration of renewables into future electricity grids. Given the rapid rollout of VSC-HVDC links, a thorough understanding of the technology is required.

At present, much of the research into VSC-HVDC in the public domain fails to capture the complexities of real-world control hardware, leading to inaccuracies in simulation models. Limited research has been carried out into the effect of controller implementation in software upon real-world processing delays in modular multilevel converters (MMC). The research presented in this thesis addresses these shortcomings by providing a detailed analysis of the delays in the capacitor balancing control (CBC) loop of an MMC.

Several sorting algorithms for use in the CBC loop have been implemented across a range of industrially representative control hardware and software platforms. The processing resource usage and execution delay have been measured to guide the algorithm selection process. A link between execution delay, choice of CBC method, and controller performance has been identified and is discussed. A simple method for incorporating this execution delay into a PSCAD/EMTDC simulation is then presented as a means of improving simulation model fidelity. A full suite of control software has been developed for a reduced-scale converter hardware prototype (CHP) MMC for future research into control loop delay and synchronisation. The implementation techniques developed are applicable to MMCs with a distributed control architecture in academia and industry.

# **Declaration**

I hereby confirm that no portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# **Copyright Statement**

The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made *only* in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=24420), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.library.manchester.ac.uk/about/regulations/) and in The University's policy on Presentation of Theses.

# Acknowledgements

Firstly, I would like to express my gratitude to my two supervisors, Professor Peter R Green and Professor Mike Barnes, without whom this PhD would not have been possible. It has been a pleasure and a privilege to work alongside Peter and Mike for the past 3.75 years, and their insight and guidance has been invaluable throughout my research. I am thankful for the opportunities they have given me over the course of this project, and I look forward to continuing our collaboration and friendship in the years to come.

It would not have been possible to for me to undertake this research without financial support, therefore I wish to acknowledge the Engineering and Physical Sciences Research Council for their assistance in this area.

During this PhD, I have had many opportunities to work alongside numerous inspiring and talented colleagues. I would like to thank my fellow researchers in the Power and Energy Division for their stimulating discussions and technical assistance which helped guide this research and debug hardware problems on several occasions. A special thanks must go to Theo, Iñaki, and Paul for their support, not only in solving research-related problems, but also personally during the times when progress has felt slow.

I am forever thankful for the support of friends outside electrical engineering. In particular I would like to thank Josh, Ben, and Martin for their faithful friendship and support throughout the years during both good and bad times.

I must, of course, thank my family, especially my parents, to whom I owe a huge debt of gratitude. They have been unwavering in their support and encouragement throughout my entire life and have sacrificed so much to make me the person I am today. Thank you.

Above all, I thank God. I thank him for forgiving me and giving me life to the full, neither of which I deserve.

"But God demonstrates his own love for us in this: While we were still sinners, Christ died for us."

Romans 5:8 NIVUK

# 1 Introduction

### 1.1 Background

On 26<sup>th</sup> June 2019, the UK Government committed to a legally binding target to achieve net zero greenhouse gas emissions by 2050 [1]. An important part of the strategy to reach this target is increasing the proportion of renewable electricity generation in the UK's generation mix. Offshore wind will form a major contribution, with the UK Government setting a target of 40 GW of active generation by the year 2030, an increase from the previous target of 30 GW [2].

These targets are borne out in the allocation of 8 GW and 25 GW of generation capacity in the most recent leasing rounds of The Crown Estate and Crown Estate Scotland respectively [3, 4], increasing the total generating capacity of planned UK offshore wind projects to 86 GW as of March 2022 [5]. Going forwards, it is clear that offshore wind will play an increasingly important role in the generation of clean energy for the United Kingdom.

Worldwide, the picture is similar, with new installed offshore wind capacity showing a compound annual growth rate (CAGR) of 22 % in the decade up to the year 2020, and a forecast CAGR of nearly 30 % until the year 2025 [6]. At present, the growth in capacity is being led by China, the Netherlands, and Germany, however other countries are expected to play an increasing role in the next decade, as governments around the world raise their renewable energy ambitions [6].

#### 1.1.1 Offshore Wind Farm Grid Connections

A key decision in the design of an offshore wind farm is the connection type used to transmit generated electricity to the onshore alternating current (AC) grid for distribution. This connection can be made using either high voltage alternating current (HVAC) or high voltage direct current (HVDC) along a subsea cable to shore. HVAC is a mature and well-understood technology, and as a result is often simpler and cheaper to implement than an equivalent HVDC scheme. HVDC transmission is more efficient for bulk power transfer, however can be significantly more expensive and complex to implement [7].

An important factor when choosing the connection type is the distance of the wind farm from the shore. Where HVAC is used to transfer power over a subsea cable, a large proportion of the cable's current carrying capacity is used to charge and discharge the cable capacitance every cycle. This reduces the amount of active and reactive power which can be transferred over the link, reducing its efficiency, and may require additional reactive power compensation, which increases costs [7]. Conversely, in a HVDC transmission system, once the cable capacitance is charged, almost the full current carrying capacity of the cable can be used for active power transfer.

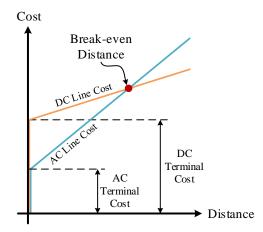

Additional considerations include the subsea cable cost per kilometre, which is slightly higher for HVAC transmission, and the cost of the terminal substations, which are higher for HVDC transmission. As a result, a break-even point exists, based upon total system cost and transmission distance. For subsea transmission links such as those used for offshore wind farms, the break-even distance is typically in the range of 50-100 km, above which HVDC becomes more favourable [8]. This relationship is shown in Figure 1.1. The equivalent distance for HVDC using overhead lines is typically 300-800 km [8].

Figure 1.1: Subsea HVAC vs. HVDC transmission scheme break-even distance

In the UK, a number of consented Round 3 offshore wind farm developments will use HVDC for power transfer to shore, operating at distances between 75-215 km from shore [9]. Looking ahead to future projects, the six preferred sites selected by The Crown Estate in the Round 4 leasing process are at distances ranging from approximately 40-120 km from shore [10]. In the recent ScotWind leasing process, Crown Estate Scotland selected 17 projects with distances ranging from 5-80 km [11, 12]. At the time of writing, these projects are in early-stage planning and the transmission scheme (HVAC or HVDC) has not been decided.

There is a clear trajectory towards increasing the number of HVDC-connected offshore wind farms. In July 2020, the UK Government launched the Offshore Transmission Network Review (OTNR) [13], which aims to address the barriers to increasing offshore wind capacity. Central to this is the development of a strategy to coordinate the connection of offshore wind farms to the onshore grid. This may require the sharing of transmission assets by wind farm operators and construction of multi-purpose interconnectors (MPI) to connect neighbouring wind farms and countries using long-distance subsea cables. These requirements can be met by HVDC transmission links.

#### 1.1.2 Renewable Electricity Generation Integration Challenges

Increasing the percentage of renewables in the generation mix, including other sources such as solar photo-voltaic (PV), hydroelectric, and tidal, brings with it additional challenges. Chief among these is maximising the utilisation of renewable generation when it is available, thereby avoiding costly curtailment fees and reducing overall dependence upon non-renewable sources of generation. The average curtailed GB wind generation across 2020-2021 was 2.9 TWh; enough energy to power 800,000 households [14]. In 2020, wind generation curtailment cost National Grid Electricity System Operator (ESO) £282 million in payments to wind farm operators, representing an additional cost of around £10 to each household [15].

Insufficient capacity on the existing transmission network has been identified as a primary cause of curtailment [14, 15]. During periods of high wind generation in the UK, a large amount of power is exported from generation sites in Scotland to demand centres in England, putting strain upon the existing transmission network. Without the installation of additional transmission capacity, the need to curtail generation will only be exacerbated by the planned connection of a further 30 GW of offshore wind generation by 2030.

Maximising the utilisation of renewable generation is dependent upon the ability to transfer large amounts of power from generation sites to demand centres. Within a country, these are often far apart and reinforcement of the grid using overhead AC transmission lines may be undesirable due to visual impact or planning concerns. In addition, interconnections between countries allow exporting of power during periods of excess renewable generation and vice-versa during times of low generation.

HVDC transmission links can satisfy both requirements and are a key enabler in the integration of renewable generation into the future electricity grid. Within a synchronous AC grid, subsea HVDC interconnectors can be used to strengthen the existing grid and increase power transfer capacity. Where interconnection of two asynchronous AC grids is required, HVDC transmission allows efficient, bi-directional bulk power transfer whilst maintaining a degree of isolation between the interconnected grids.

#### 1.1.3 Voltage Source Converter HVDC

Two main types of converter technology are available commercially for HVDC transmission systems: current source converter (CSC) and voltage source converter (VSC). VSC-HVDC is better suited than CSC-HVDC for offshore wind farm grid connections and subsea interconnectors for several reasons. These include independent control of active and reactive power, and the ability to change power flow direction by reversing the direction of current flow, rather than the voltage polarity on the HVDC link [7]. This allows for easier integration into multi-terminal HVDC (MT-HVDC) schemes. Furthermore, VSC-HVDC can operate with a weak or inactive AC grid at one end of the transmission link, a critical requirement for offshore wind farm grid connections.

The first commercial VSC-HVDC scheme was the 3 MW Hellsjön-Grängesberg HVDC test system in Sweden, which was brought online in 1997 and used a two-level VSC [16]. All VSC-HVDC schemes used two- or three-level VSCs until 2010, when the modular multilevel converter (MMC) topology was used for the first time by Siemens on the Trans Bay Cable project in the United States [17]. MMC-based VSCs offer several advantages when compared to two- and three-level VSCs, including lower converter losses and a reduction in AC side harmonic content. The reduction in harmonic content reduces or eliminates the need for output filtering, leading to lower costs and a smaller converter footprint, which is desirable for VSCs installed on offshore platforms [18]. VSC-HVDC is currently employed in at least 51 HVDC schemes around the world, with approximately a further 60 projects scheduled to reach operational status in the next decade [19].

The internal operation of the MMC is more complex than previous two- and three-level VSCs and at present, much of the detailed understanding of the internal converter control is held by the manufacturers, who are unwilling to share for commercial reasons. In recent years, there has been a growing interest in more-open converter models, driven in part by electricity transmission system operators (TSO) who require accurate models which can be maintained for the lifetime of the converter to enable system studies to be carried out [20-22]. Despite this, more work is required to develop a better public domain understanding of the internal converter dynamics and implications of different control implementations.

Much of the public domain research and development fails to account for complexities in the underlying control hardware of the MMC. In particular, the processing delay introduced by the capacitor balancing control (CBC) loop in the MMC has been the subject of limited research in the public domain [23]. Failure to account for these delays can lead to unexpected consequences such as instability in control loops, premature aging of system components, or catastrophic component failure [24]. With the rapid roll-out of MMC-based HVDC links across the UK and globally, a better understanding of CBC loop dynamics in the presence of time delays is required, to identify and resolve sources of delay which could affect converter reliability. Furthermore, a more robust method to analyse the performance of the CBC loop in the presence of delays is required, so that effective comparisons can be made between different CBC methods.

The MMC topology has been chosen to investigate these issues since it has been the focus of much research and development in academia and industry over the last 15 years and is the dominant multilevel converter topology employed in industry at present. Furthermore, selecting the MMC topology for study allows use of a reduced-scale MMC converter hardware prototype (CHP) available in the department [25] for investigations on industrially-representative control hardware.

This research will focus on the internal control delays present in an MMC. In particular, the CBC loop will be studied and the implications of different control algorithm programming and implementation methods upon control delays will be investigated. The analysis techniques developed can be used to evaluate the performance of different CBC methods, with future extension to other time-critical control loops. The findings of this research can be used to inform the control algorithm implementation process for MMCs and improve the fidelity of electromagnetic transient (EMT) simulation models of MMCs.

### 1.2 Aims and Objectives

The aim of this thesis is to provide a detailed insight into internal control delays and controller implementation techniques for an MMC, to guide hardware and software development and improve simulation model fidelity. To achieve this broad aim, the following objectives have been identified:

- 1. Review and categorise CBC methods for an MMC and identify constraints on CBC loop execution delay.

- 2. Measure and compare the **resource usage** of a selection of sorting algorithms for CBC implemented on a range of industrially representative control hardware.

- Measure and compare the execution delay of a selection of sorting algorithms for CBC implemented on a range of industrially representative control hardware.

- 4. Develop and validate a new suite of control software for the reduced-scale CHP which is suitable for investigating control loop delay and synchronisation.

#### 1.3 Main Contributions

#### **Thesis**

The work contained in this thesis has made a number of contributions, predominantly in the area of MMC internal control delay measurement and modelling. The main contributions detailed in this thesis and associated conference [C] and journal [J] publications are summarised below:

- A thorough review of capacitor balancing control methods was carried out. The

terminology around CBC methods has been clarified and a taxonomy of CBC

methods has been developed as a basis for this work. This terminology and

taxonomy developed for this work is also applicable more widely and is able to

resolve some of the confusion around the literature on CBC.

- A range of sorting algorithms were implemented across three industrially representative control hardware platforms and three programming methods. The resource usage of each algorithm was measured and compared, providing a guide to sorting algorithm selection to meet control hardware resource constraints [J1, P1].

- The execution delay of the sorting algorithms was measured using representative capacitor voltage data as an input to the sorting algorithm. The results from this work can be used to guide sorting algorithm selection for time-constrained control loops [C1, P1] and to improve the fidelity of simulation models.

A methodology to analyse the performance of the CBC loop in the presence of non-zero processing delays has been developed. The methodology has been applied to several simulation scenarios and has shown that delays above a certain time period degrade the performance of the CBC loop. The analysis method can also be applied to other control loops to evaluate their performance when processing or communication delays are present.

A ground-up rewrite of the control software running on the reduced-scale MMC CHP was carried. The new control software resolves several issues with the previous control software, reduces processing resource usage, and allows configuration and measurement of internal control delays. The control implementation described in this thesis can be used to inform control software development for other prototype MMCs in academia and industry [J1].

#### **Conference Papers [C]**

J. Andrews, P. R. Green, M. Barnes, "A PSCAD Processor-in-the-loop System for Hardware Evaluation of Power Converter Control Algorithms", presented at the 10th IET International Conference on Power Electronics, Machines and Drives (PEMD), Online, Dec. 15-17, 2020, doi: 10.1049/icp.2021.1060.

#### Journal Papers [J]

T. Heath, M. Barnes, P. D. Judge, G. Chaffey, P. Clemow, T. C. Green, P. R. Green, J. Wylie, G. Konstantinou, S. Ceballos, J. Pou, M. M. Belhaouane, H. Zhang, X. Guillaud, J. Andrews, "Cascaded-and Modular-Multilevel Converter Laboratory Test System Options: A Review", *IEEE Access*, Vol. 9. pp. 44718-44737, Mar. 2021, doi: 10.1109/ACCESS.2021.3066261.

#### Additional

- Co-editor of the monthly "VSC-HVDC Newsletter" alongside M. Barnes. The

newsletter focusses upon all aspects of VSC-HVDC technology including projects

and novel technologies.

- Developed a public outreach demonstrator for the Holistic Operation and Maintenance for Energy from Offshore Wind Farms (HOME Offshore) project (Engineering and Physical Sciences Research Council grant EP/P009743/1).

- Developed a wireless underwater optical communication system for the Autonomous Aquatic Inspection and Intervention (A2I2) project (Innovate UK project number 104822).

#### Papers in Progress [P]

J. Andrews, T. Heath, P. R. Green, M. Barnes, "A Review and Performance Evaluation of Sorting Algorithms for Capacitor Balancing Control in Modular Multilevel Converters", *Journal*

#### 1.4 Thesis Structure

#### **Chapter 2 – MMC Structure and Control**

This chapter introduces the MMC topology as a foundation for the rest of the thesis. The circuit structure of a typical three-phase MMC employing half-bridge submodules is presented and analysed, followed by an explanation of the submodule capacitor voltage dynamics which will be recalled later in the thesis. An overview of the control structure of an industrial-scale HVDC MMC is then provided, focussing upon internal converter control loops.

#### **Chapter 3 – Capacitor Balancing Control**

A comprehensive review of capacitor balancing control methods is presented in this chapter. The terminology used to discuss the components of the CBC loop is defined, both as a basis for subsequent chapters and to clarify the often-confusing terminology used in the literature on CBC. A taxonomy of CBC methods is then developed based upon CBC loop sampling rate and sorting algorithm requirements. The results from the literature review have been used to guide selection of the CBC methods and sorting algorithms for study in Chapter 6.

#### **Chapter 4 – Sorting Algorithms**

This chapter provides an overview of sorting algorithms, their comparison metrics, and classification to ensure that the reader is sufficiently familiar with these for the discussion presented in Chapter 6. The comparison metrics are linked to the CBC loop execution delay and control hardware resource usage requirements.

#### **Chapter 5 – Simulation Model Overview**

In this chapter, the simulation model used to generate the synthetic capacitor voltage measurement data for the work in Chapter 6 is introduced and explained. The model used is an open-access PSCAD/EMTDC model developed by The National HVDC Centre and the University of Strathclyde [22]. The circuit structure of the model is introduced first, followed by the control structure and additional controllers which were not described in the MMC overview in Chapter 2. The operation of the custom PSCAD/EMTDC capacitor balancing control component developed for this work is also explained.

#### Chapter 6 – Sorting Algorithms for Capacitor Balancing Control

The results from the research into sorting algorithm execution delay and resource usage are presented in this chapter. The motivations for focussing upon the CBC loop are outlined first, followed by a description of the control hardware targets and programming languages used to implement the sorting algorithms. The execution delay results for each hardware target and programming method are then plotted and discussed, with reference to sorting algorithm structure and capacitor voltage dynamics. Finally, the field-programmable gate array (FPGA) logic resource usage of a sub-set of the sorting algorithms is measured, and the results are explained, identifying trade-offs between ease of implementation and logic resource usage.

#### **Chapter 7 – Converter Hardware Prototype**

This chapter provides an overview of the reduced-scale converter hardware prototype which has been used for hardware development in this research, with reference to [25]. The converter ratings and hardware structure are introduced first, followed by a description of the hardware modifications carried out during this work. Finally, a detailed description of the CHP control architecture is provided, as a basis for understanding the development carried out in Chapter 8.

#### **Chapter 8 – Control Software Development**

In this chapter, the ground-up rewrite of the CHP control software is described in detail. The limitations of the existing control software are identified first, and from these, a list of design objectives for the new control software are derived. The internal architecture of the CHP control system hardware is then described, with a particular focus upon data transfer, communication delays, and synchronisation between system components. The control software developed for the CHP is then documented, with descriptions of each component and how these operate together to ensure that the design objectives were met.

The CHP and the practical development work described in Chapters 7 and 8 forms the basis of a hardware platform for further study of the sorting algorithm execution delay in Chapters 3 to 6.

#### **Chapter 9 – Conclusion and Future Work**

This chapter provides a summary of the work presented in this thesis, and the main outcomes of the research are discussed. Opportunities for future research avenues which follow on from this work are also outlined.

#### **Appendices and Supplementary Online Repository**

Additional technical material, supplementary plots, and some of the source code developed during this project are included as appendices in this thesis. Other source code which is unsuitable for print is available for download in a supplementary online repository hosted by Mendeley Data. This data is accessible following [26], replicated here for ease of access.

[26] J. Andrews. Supplementary Online Repository for Computational and Communication Architectures for Modular Multilevel Converter Construction, Mendeley Data, 2022, doi: https://dx.doi.org/10.17632/fr2jrff9w3.1

### 2 MMC Structure and Control

This chapter provides an overview of the MMC topology as a foundation for subsequent chapters. The circuit structure of a three-phase HVDC MMC is presented, followed by a description of the half-bridge submodule (HB-SM) topology and the SM capacitor voltage dynamics. The circuit structure is then analysed and the control inputs to the voltage control loop of the converter are derived. A typical control structure representative of that used in a HVDC MMC is then introduced, with a focus on low-level converter control loops which are the subject of this research.

#### 2.1 Circuit Structure

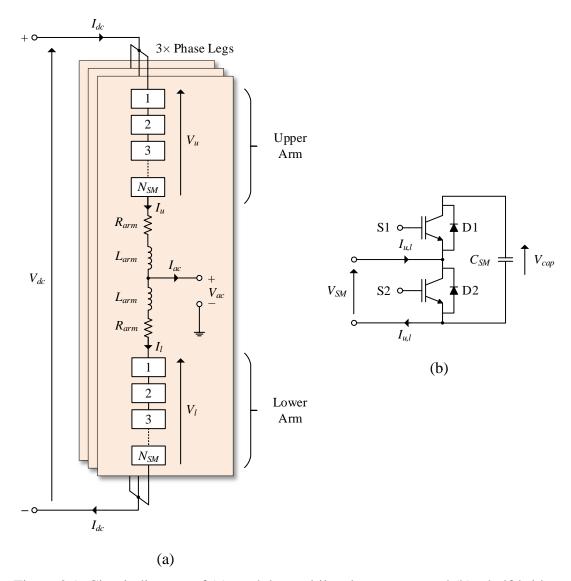

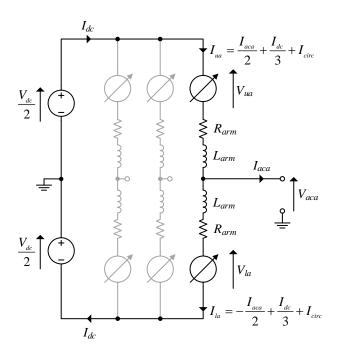

The circuit structure of a three-phase MMC is shown in Figure 2.1(a). Only one phase is shown for clarity; the other phases are identical. An MMC consists of three phase 'legs' connected in parallel across the DC link, which operates at a voltage,  $V_{dc}$ . Each phase leg comprises an upper and lower 'arm' which contain a number of submodules (SM),  $N_{SM}$ , connected in series with an arm inductor,  $L_{arm}$ . The arm inductor serves to limit the circulating current component of the arm current and the fault current rise rate [27]. A parasitic arm resistance,  $R_{arm}$ , is also shown in Figure 2.1(a); this represents the sum of the resistive losses in the SMs. The AC output voltage,  $V_{ac(abc)}$ , is taken from the midpoint of the upper and lower arms of each phase.

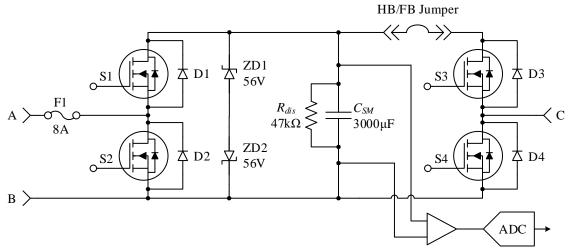

Each submodule contains two insulated-gate bipolar transistors (IGBT) and an energy storage capacitor and operates as a two-level converter; this is the half-bridge submodule topology and is shown in Figure 2.1(b). It is possible to use multiple IGBTs connected in series to increase the voltage across each SM; this is the cascaded two-level SM topology [28] and is not the subject of this explanation. Other SM topologies have been proposed in the literature and are implemented in industrial-scale MMCs [18, 29]; however, these are outside the scope of this work and will not be discussed here.

In the case of the HB-SM topology, the voltage at the SM terminals,  $V_{SM}$ , can be switched between 0 V and the voltage across the SM capacitor,  $V_{cap}$ , by controlling the two switches, S1 and S2. When S1 is closed and S2 is open, neglecting semiconductor device voltage drops,  $V_{SM}$  is equal to  $V_{cap}$  and the SM is 'inserted'. In this state, the SM capacitor,  $C_{SM}$ , will charge or discharge dependent upon the direction of the arm current,  $I_{u,l}$ . Conversely, when S1 is open and S2 is closed,  $V_{SM}$  is equal to 0 V and the SM is

'bypassed'. In this state, the SM capacitor voltage remains stable, neglecting selfdischarge.

Figure 2.1: Circuit diagram of (a) modular multilevel converter, and (b) a half-bridge submodule

Two additional states exist. The 'blocked' state is formed when both switches are open and is typically only used during converter start-up to charge the SM capacitor via the freewheeling diode, D1. The state where both switches are closed is not permitted since this will short-circuit the SM capacitor and cause a large fault current to flow through S1 and S2, which may damage the switches or other SM components. The switch state combinations for a HB-SM are summarised in Table 2.1.

| Arm Current   | S1 | <b>S2</b> | $V_{SM}$  | $C_{SM}$                | State Name    |

|---------------|----|-----------|-----------|-------------------------|---------------|

|               | 0  | 0         | $V_{cap}$ | Charge                  | Blocked       |

| $I_{u,l} > 0$ | 0  | 1         | 0 V       | Stable                  | Bypassed      |

|               | 1  | 0         | $V_{cap}$ | Charge                  | Inserted      |

|               | 0  | 0         | 0 V       | Stable                  | Blocked       |

| $I_{u,l} < 0$ | 0  | 1         | 0 V       | Stable                  | Bypassed      |

|               | 1  | 0         | $V_{cap}$ | Discharge               | Inserted      |

| _             | 1  | 1         | _         | Short-circuit discharge | Not Permitted |

Table 2.1: Half-bridge submodule switch states

By switching SMs in sequence, the string of SMs in each converter arm behaves as a controllable voltage source, with the smallest voltage step being equal to the SM capacitor voltage.

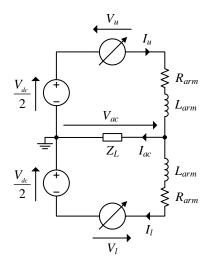

Figure 2.2: Modular multilevel converter equivalent circuit for a single phase

With reference to the equivalent circuit diagram for a single phase shown in Figure 2.2, two relationships for  $V_{ac}$  can be derived by applying Kirchoff's Voltage Law (KVL) around the upper and lower loops. These are shown in Equation 2.1 and Equation 2.2 for upper and lower loops, respectively.

$$V_{ac} = \frac{V_{dc}}{2} - V_u - R_{arm}I_u - L_{arm}\frac{dI_u}{dt}$$

2.1

$$V_{ac} = -\frac{V_{dc}}{2} + V_l + R_{arm}I_l - L_{arm}\frac{dI_l}{dt}$$

2.2

The upper and lower arm currents,  $I_{u,l}$ , are made up of three main components as shown in Equation 2.3 and Equation 2.4. The AC output current,  $I_{ac}$ , is divided equally between upper and lower arms. The remaining two terms are common to both arms and comprise of DC bus current,  $I_{dc}$ , shared across the three phases, and a double fundamental frequency circulating current,  $I_{circ}$ , which is caused by the voltage imbalance between phases [30].

$$I_u = \frac{I_{ac}}{2} + \frac{I_{dc}}{3} + I_{circ}$$

2.3

$$I_l = -\frac{I_{ac}}{2} + \frac{I_{dc}}{3} + I_{circ}$$

2.4

Substituting Equations 2.3 and 2.4 into Equations 2.1 and 2.2 respectively, then summing the resulting equations allows the AC output voltage to be expressed in terms of the upper and lower arm voltages,  $V_{u,l}$ , and the AC output current, as shown in Equation 2.5.

$$V_{ac} = \frac{V_l - V_u}{2} - \frac{R_{arm}}{2} I_{ac} - \frac{L_{arm}}{2} \frac{dI_{ac}}{dt}$$

2.5

A further quantity, the internal converter voltage,  $V_c$ , can be defined according to Equation 2.6 and is the voltage which drives the AC output current. Assuming a negligible voltage drop across the arm inductance and resistance, the internal converter voltage is approximately equal to the AC output voltage. The internal converter voltage is manipulated by the converter control loops to achieve the desired control objectives.

$$V_{ac} \approx V_c = \frac{V_l - V_u}{2}$$

2.6

#### 2.1.1 Selection of Nominal Submodule Capacitor Voltage

The maximum AC output voltage is generated by bypassing all SMs in the upper arm and inserting all SMs in the lower arm. In this scenario, the AC output terminal is effectively directly connected to the positive pole of the DC bus ( $V_u = 0 \text{ V}$ ), and AC output voltage is equal to  $V_{dc}/2$ , ignoring the voltage drop across the arm inductance and resistance. The required lower arm voltage is calculated according to Equation 2.7.

$$V_u = 0$$

,  $V_{ac-max} = \frac{V_{dc}}{2} = \frac{V_l}{2}$   $\Rightarrow$   $V_l = V_{dc}$  2.7

The minimum AC output voltage is generated by the opposite operation: inserting all SMs in the upper arm and bypassing all SMs in the lower arm. In this scenario, the lower arm voltage is equal to 0 V and the required upper arm voltage is calculated according to Equation 2.8.

$$V_l = 0$$

,  $V_{ac-max} = \frac{V_{dc}}{2} = \frac{V_u}{2}$   $\Rightarrow$   $V_u = V_{dc}$  2.8

As can be seen from Equation 2.7 and Equation 2.8, the upper and lower arms must each be capable of generating a voltage equal to  $V_{dc}$ . This is achieved by ensuring that the sum of the SM capacitor voltages in the upper and lower arms,  $V_{capu,l}^{\Sigma}$ , are each equal to  $V_{dc}$ . As stated previously, the capacitors of inserted SMs are charged or discharged dependent upon the direction of the arm current, leading to a ripple on each SM capacitor voltage. The capacitor voltage ripples in an arm add up to produce a sum capacitor voltage ripple and as a result, only the long-term mean value of the sum SM capacitor voltage can equal  $V_{dc}$ . Ignoring the sum capacitor voltage ripple, the ideal nominal SM capacitor voltage,  $V_{cap-nom}$ , can be calculated according to Equation 2.9.

$$V_{cap-nom} = \overline{V_{cap}} = \frac{V_{capu,l}^{\Sigma}}{N_{SM}} = \frac{V_{dc}}{N_{SM}}$$

2.9

#### **Generation of Arm Voltages**

The voltage generated by an arm is equal to the number of inserted SMs in the arm (also known as the SM insertion index),  $N_{onu,l}$ , multiplied by the nominal SM capacitor voltage as shown in Equation 2.10. This forms the basis for controlling the arm voltage in an MMC.

$$V_u = N_{onu} \times V_{cap-nom}$$

$V_l = N_{onl} \times V_{cap-nom}$  2.10

By appropriate control of the SM insertion index the output voltage magnitude and phase can be controlled independently. The number of output voltage levels,  $N_{level}$ , is equal to  $N_{SM} + 1$ .

## **Instantaneous Sum and Mean Submodule Capacitor Voltage**

As stated previously, each arm exhibits a sum capacitor voltage ripple, leading to a corresponding ripple in the mean capacitor voltage – that is,  $V_{capu,l}^{\Sigma}$  and  $\overline{V_{cap}}$  vary with time. In this work, the time-varying version of  $V_{capu,l}^{\Sigma}$  and  $\overline{V_{cap}}$  are named the instantaneous sum capacitor voltage and instantaneous mean capacitor voltage, respectively, and are denoted by the (t) or [k] suffix.

The instantaneous sum and mean capacitor voltages are introduced here since they are used by several capacitor balancing control (CBC) methods. Furthermore, the instantaneous versions of each variable can be used to quantify the effectiveness of CBC methods in ensuring that capacitor voltages remain balanced. These will be discussed further in Chapter 6.

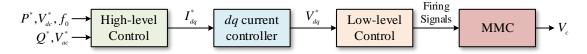

## 2.2 Control Structure

Control of an MMC is typically achieved using several cascaded control loops. These control converter behaviour from power system-level dynamics such as active and reactive power transfer, down to low-level firing signals for the switches on individual submodules. The control objectives are dictated by the application scenario, for example, whether the converter is operating at the onshore or offshore end of an offshore wind farm HVDC link. A generalised representation of a cascaded control structure for an MMC is shown in Figure 2.3.