# **OPEN**

# Temperature and Size Effect on the Electrical Properties of Monolayer Graphene based Interconnects for Next Generation MQCA based Nanoelectronics

Sanghamitra Debroy<sup>1,4</sup>, Santhosh Sivasubramani<sup>1,4</sup>, Gayatri Vaidya<sup>2</sup>, Swati Ghosh Acharyya<sup>3</sup> & Amit Acharyya<sup>1\*</sup>

Graphene interconnects have been projected to out-perform Copper interconnects in the next generation Magnetic Quantum-dot Cellular Automata (MQCA) based nano-electronic applications. In this paper a simple two-step lithography process for patterning CVD monolayer graphene on SiO<sub>2</sub>/Si substrate has been used that resulted in the current density of one order higher magnitude as compared to the state-of-the-art graphene-based interconnects. Electrical performances of the fabricated graphene interconnects were evaluated, and the impact of temperature and size on the current density and reliability was investigated. The maximum current density of  $1.18 \times 10^8$  A/cm<sup>2</sup> was observed for 0.3 µm graphene interconnect on SiO<sub>2</sub>/Si substrate, which is about two orders and one order higher than that of conventionally used copper interconnects and CVD grown graphene respectively, thus demonstrating huge potential in outperforming copper wires for on-chip clocking. The drop in current at 473 K as compared to room temperature was found to be nearly 30%, indicating a positive temperature coefficient of resistivity (TCR). TCR for all cases were studied and it was found that with decrease in width, the sensitivity of temperature also reduces. The effect of resistivity on the breakdown current density was analysed on the experimental data using Matlab and found to follow the power-law equations. The breakdown current density was found to have a reciprocal relationship to graphene interconnect resistivity suggesting Joule heating as the likely mechanism of breakdown.

Interconnects are going to play an important role in the next generation Magnetic Quantum-dot Cellular automata (MQCA) based nano-electronics<sup>1-3</sup>. Copper being the state-of-art interconnect material is facing severe challenges while being scaled down to nano dimensions due to its increased resistivity that is mainly because of its surface and grain boundary scatterings<sup>4</sup> and also susceptibility to electromigration effect<sup>5</sup>. Moreover, copper as an on-chip clocking material requires high currents and large dimensions<sup>6</sup> in order to generate the external field in MQCA. To illustrate, copper interconnects (CI) used in MQCA occupies more than 2000 nm in order to generate the required external field for data propagation between the nano-magnets<sup>7</sup>. Therefore CI impose limitations on the emerging nanoelectronic applications leading to extensive research in finding an alternate material that can replace the CI.

Thus in this context, graphene<sup>8-14</sup> can be envisaged as a potential interconnect which could replace copper. Moreover, graphene is projected to be an excellent candidate material for interconnects due to its high carrier mobility  $(2 \times 10^5 \text{ cm}^2/\text{V-s})^{15}$ , ballistic transport<sup>16</sup>, high current carrying capacity<sup>17</sup> and high thermal conductivity<sup>18</sup>. On the other hand, the length of the nanomagnets used in typical MQCA devices are more than 100 nm and therefore the underline interconnects should be in size ranging from more than 100 nm and less than the CI which are currently used.

<sup>1</sup>Department of Electrical Engineering, Indian Institute of Technology, Hyderabad, India. <sup>2</sup>Department of Electronic Materials Engineering, Research School of Physics, The Australian National University, ACT 2601, Australia. <sup>3</sup>School of Engineering Sciences and Technology, University of Hyderabad, Hyderabad, India. <sup>4</sup>These authors contributed equally: Sanghamitra Debroy and Santhosh Sivasubramani. \*email: amit\_acharyya@iith.ac.in

CVD based multilayer and monolayer graphene interconnects have been investigated in  $^{19,20}$  resulting in the maximum current density of  $4\times10^7 {\rm A/cm^2}$  and  $1.2\times10^7 {\rm A/cm^2}$  on  ${\rm SiO_2}$  substrate respectively. This is an order of magnitude less than the state-of-the-art Graphene Nanoribbon where the size is typically much less than 100 nm hence, it is not suitable as interconnects in MQCA  $^{17,21,22}$ . Thus in an attempt to increase the current density in the CVD grown graphene, several hybrid structures have been reported  $^{23-27}$  with an additional overhead of significant increase in the fabrication complexity. To address these issues we introduce here a simple fabrication procedure of patterning graphene interconnects in the context of next-generation MQCA, still retaining an order of magnitude higher current density as compared to the present CVD graphene interconnects.

Furthermore, in order to analyse the problem of integrating graphene interconnects in next-generation MQCA based nano-electronics, it is necessary to understand the effect of temperature and size impact on the electrical parameters. Graphene being projected as a potential alternative for interconnect material, the assessment of temperature and size would be of utmost importance. However, published literature lacks data on symbiotic effect of temperature and size on the electrical conductivity of graphene. Hence an organised attempt has been made here to understand the combined effect of temperature and size on the electrical behaviour of CVD grown monolayer graphene on SiO<sub>2</sub>/Si substrate. Thus in this paper we report-

- 1. a simple two-step lithography process for patterning CVD monolayer graphene interconnects resulting in one order of magnitude higher current density and

- 2. effect of temperature and size on the breakdown current density of CVD-monolayer graphene interconnects.

The rest of the paper is organised as follows: Section 2 describes the experimental setup, section 3 describes the results followed by its discussions and the section 4 draws the conclusion.

# **Experimental details**

State of the art, patterning of CVD based graphene interconnects involves a minimum of five lithographic processes i.e. two times optical and three times electron beam lithography<sup>20</sup>. This results in the usage of different polymer resist that leaves behind the resist residues in each step of the lithographic process thus reducing the current carrying capacity of the graphene interconnects.

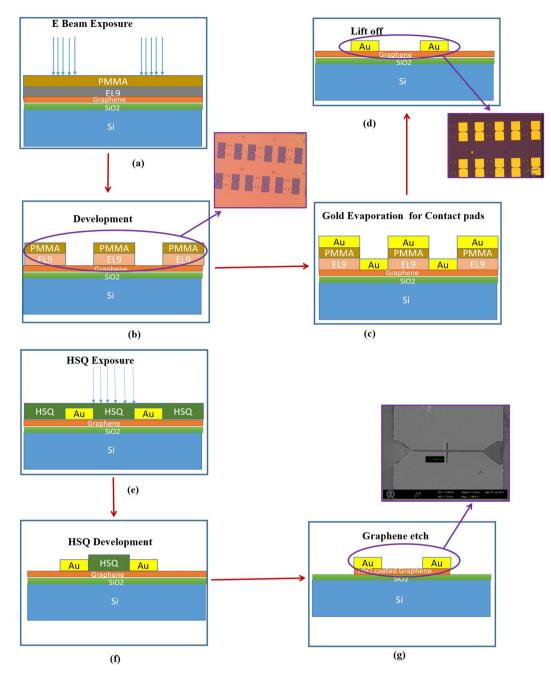

In this paper, we report a novel two-step lithography process for CVD monolayer graphene patterning. A detailed description with pictorial representation has been given in Fig. 1 so that it can be reproduced in future fabrication work with less experimental rigour compared to the state-of-the-art techniques.

Initially, we started with graphene monolayer ( $10\,\mathrm{mm} \times 10\,\mathrm{mm}$ ) produced by CVD on copper catalyst and transferred to a SiO<sub>2</sub> ( $300\,\mathrm{nm}$  thickness)/Si substrate using wet transfer process that was procured from M/s. Graphenea Inc. USA. The grain size was approximately  $10\,\mathrm{\mu m}$  for monolayer graphene with greater than 95% coverage and with small multilayer islands.

The first lithography step involved patterning the metal contacts and the alignments marks. The alignment marks and the metal contacts Cr/Au ( $10\,\text{nm}/70\,\text{nm}$ ) were fabricated by electron-beam lithography (EBL). Bilayer EBL resist, has been used in the reported experiment in order to achieve better liftoff of Gold (Au). PMMA - a high-resolution e-beam resist and Copolymer EL9 is selected as the bilayer resist material for the EBL. The sample is exposed to an electron beam of acceleration voltage  $16\,\text{kV}$  and a dose of  $180\,\mu\text{C/cm}^2$ . Figure 1(a) shows the detailed structure of the Bi-layer resist used in this experiment for better lift-off. EL9 was spun at 3200 rpm for 60 sec and Pre-Baked at  $180\,^{\circ}\text{C}$  for 7 minutes followed by PMMA 950 K (4%) at 4000 rpm for 45 sec and bake it at  $180\,^{\circ}\text{C}$  for 2 mins. The exposed resist was then developed in the MIBK (methyl isobutyl ketone) and IPA (Isopropyl alcohol) developer (1:3) for 30 s at room temperature followed by  $N_2$  drying. Subsequently metal deposition was carried out at a pressure of  $10^{-6}$  Torr and then lift off was done in acetone for 4 hours.

The second lithography step involves patterning the graphene interconnects with width (W) in the range of 300 nm to 1500 nm, length of 1  $\mu$ m and thickness of 0.335 nm. HSQ (Hydrogen Silsesquioxane) was used for patterning the graphene channels at 2000 rpm for 45 sec and exposing it to acceleration voltage of 18 kV and a dose of 190 s  $\mu$ C/Cm². The resist was developed in Microposit MIF319 developer and Tetra-methyl ammonium hydroxide (TMAH 2.3%) for 1 sec. While using HSQ an overlying dielectric layer is formed on the graphene interconnects. A low power oxygen plasma etch for 1 min 30 sec and at 50 Watt power was used, but still the fine line remained. After the plasma etch the HSQ resist pattern was etched into the graphene flake.

The Current-voltage (I-V) characteristics of the device were measured using Proxima (Fast IV Measurement/ B1500) and Keithley 4200 Semiconductor Characterization System with two-probe configuration. The (I-V) characterisation was done by sweeping voltage in steps of  $0-0.5\,\mathrm{V}$ ,  $0-1\,\mathrm{V}$  followed by 0 to breakdown voltage. Due to increasing current density in the graphene interconnects, there was a voltage at which the break down occurred in the graphene interconnect, resulting in a visible drop in current. The device testing was stopped at this point. This way of measurement helps in suppressing the effect of trapping centres due to resist residuals. Breakdown voltage for all cases was nearly found at 2 V. The temperature measurements were carried out at 298–473 K respectively. Temperature vs I-V characterisation results are discussed in the following section.

However, it has been reported in<sup>22</sup> that HSQ coating does not degrade the carrier mobility or rather they sometimes improve the mobility. Thus the reported two-step process of fabricating graphene interconnect not only reduces the rigour of fabrication but also reduces the residual trapping leading to higher current capacities of the graphene interconnects that is discussed in the subsequent section.

## **Results and Discussion**

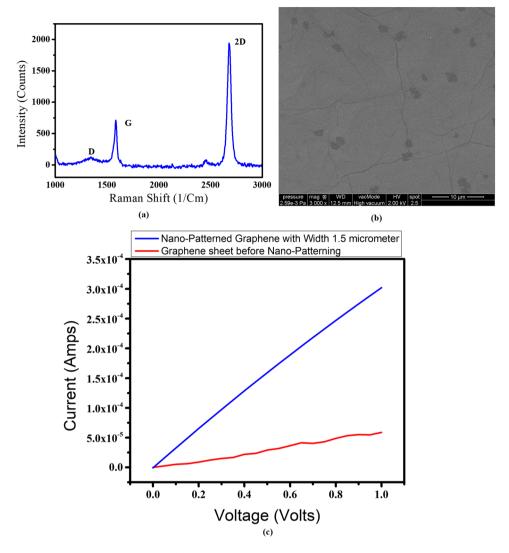

SEM and Raman spectrum studies were conducted at several locations in order to confirm the uniformity of the monolayer graphene film.

**Figure 1.** Fabrication process flow for patterning CVD graphene using a two-step approach - (**a-d**) shows the different stages of patterning the alignment marks and the contact pads and the insets shows the optical images of the same. (**e-g**) shows the patterning of the graphene interconnects and inset shows the SEM images of the patterned interconnect.

Figure 2(a) shows the Raman spectrum of the sample with an excitation wavelength of 532 nm (green, Ar laser), calibrated using quartz. The signature peaks, namely D, G and 2D bands, appeared around 1340, 1584 and  $2800 \, \text{cm}^{-1}$ , respectively. This ensures  $I_{(G)}/I_{(2D)} = 0.55$ , which indicates that it is a monolayer graphene sample<sup>28–33</sup>. Figure 2(b) gives the Scanning electron microscopy (SEM) image of graphene on top of SiO<sub>2</sub> (300 nm/Si substrate).

In spite of graphene devices that are produced from highly oriented pyrolytic graphite (HOPG), laser ablation, spin coating, CVD graphene is widely known method for device fabrication since it is by far the most popular way for producing graphene and also results in relatively high quality graphene, potentially on a large scale  $^{34-38}$ . Therefore we have used CVD Monolayer graphene film on SiO2/Si substrate procured from M/s. Graphenea Inc, USA, with a current density of  $10^2~\text{A/cm}^2$ , having width of  $1~\text{Cm} \times 1~\text{Cm} \times 0.35~\text{nm}$  as the starting material for patterning graphene interconnects.

Besides, study reported in  $^{19,20}$  have also used CVD graphene for electrical characterization of the patterned samples and the maximum current densities reported are up to  $4\times10^7$  A/cm<sup>2</sup> and  $1.2\times10^7$  A/cm<sup>2</sup> respectively

**Figure 2.** (a) Raman spectrum of the monolayer graphene sample (b) Scanning electron microscopy (SEM) image of graphene (c) Shows the I–V plot of the graphene sheet and graphene interconnect of width 1.5  $\mu$ m and length 1  $\mu$ m.

which is about an order lesser than that of our fabricated graphene interconnects with the maximum current density of  $1.18 \times 10^8$  A/cm<sup>2</sup>, which is attributed by the proposed simplistic two-step procedure.

The major bottleneck for graphene application is, while patterning due to multistep process - the electronic transport properties gets degraded due to the resist residual trapped in the grain boundaries and on the surface of the CVD graphene that acts as scattering sites, limiting the transport of charge carriers resulting in the reduction of the electron mobility and also increase in the sheet resistance of the CVD graphene sheet<sup>20</sup>.

Thus in this paper, a simple two-step lithography process has been reported for patterning graphene. As the number of lithography steps has been reduced, the effect of resist residuals and contaminants on the graphene surface also gets reduced resulting in one order higher current density as compared to other patterned CVD graphene current densities reported in <sup>19,20</sup>.

The results obtained has been divided into four main parts

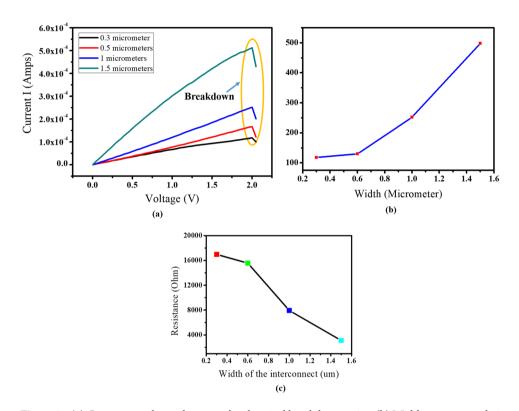

**Effect of Width on the graphene interconnect.** The variation of current with width (0.3 to 1.5  $\mu$ m) of monolayer graphene interconnect is given in Table 1 where the length has been fixed to 1  $\mu$ m. These widths were particularly studied for the application viewpoint of MQCA based nanoelectronic devices. Since, the nanomagnets used in MQCA based devices are in the range of 135  $\times$ 70  $\times$ 30 nm<sup>3 39</sup>, hence in order to place the easy axis of the nanomagnets on the graphene interconnect, the minimum width of the graphene interconnect was selected in the range of equal to or more than 300 nm and less than the copper interconnect, so as to maintain the keep-out zone (to have the proper placement of nanomagnets on the interconnect and also to avoid fringing field interactions between nanomagnets).

It was observed that with an increase in width of the graphene interconnects, the current also increased. It was found that the current (at breakdown voltage) increases at an increasing rate, though the breakdown current

| Sl.<br>No | Width of the Graphene interconnect in micrometres | Current in microamperes for<br>breakdown voltage-2V and test<br>temperature 300 K |

|-----------|---------------------------------------------------|-----------------------------------------------------------------------------------|

| 1.        | 0.3                                               | 117.89                                                                            |

| 2.        | 0.6                                               | 135                                                                               |

| 3.        | 1                                                 | 252.1                                                                             |

| 4.        | 1.5                                               | 512.4                                                                             |

**Table 1.** Variation of current with the width of Graphene interconnects at room temperature.

**Figure 3.** (a) Current vs voltage plot up to the electrical breakdown point, (b) Width vs current relation and (c) Resistance vs Width relation for Monolayer graphene interconnect of different width.

density decreases as shown in Fig. 3(b). It can be observed from Fig. 3(c) that, with the increase in width the resistance decreases due to the availability of higher number of free electrons on the surface of graphene and as a result the current values have increased.

The results obtained indicate that as the width increases the influence of the interconnect boundaries (rough area) decreases leading to lesser scattering and increased conductivity & current<sup>40</sup>.

Breakdown current densities for all the cases were calculated and a maximum current density of  $1.18\times10^8$  A/cm², was observed which is an order more than state-of-the-art²0, whereas the minimum was found to be 3.68  $\times10^7$  A/cm² for 1.5  $\mu$ m interconnect at room temperature.

This may be attributed by the reduction in the number of lithography steps as compared to the state of the patterning of CVD Graphene interconnects. Figure 3(a) shows the I-V characteristics of graphene interconnect which are covered by a thin layer of HSQ. It was found that an HSQ coating does not degrade the current carrying capacity of the graphene interconnect that is consistent with previous findings<sup>21</sup>. The voltage and current were found to follow ohm's law, i.e.  $V \propto I$ .

Patterning CVD monolayer graphene samples is quite an exhaustive, complicated and expensive process and thus we have formulated a mathematical expression for calculating the current from the width of the interconnects. The relationship between the current and width has been derived from Fig. 3(b) and is found to be typically valid when the graphene interconnects ranges between 300 to 1500 nm and is given as-

$$I = a + bw + cw^2 \tag{1}$$

The best fit for the obtained values of the intercept were found to be a = 143.93, b = -177.47 and c = 288.44.  $R^2$  for this fit was found to be 99.91%. I (microampere) and w (micrometer) represent here the current and width of the graphene interconnects and a, b and c are constants respectively. Thus from the above relation, we can calculate the current or width of the interconnects without doing fabrication every time.

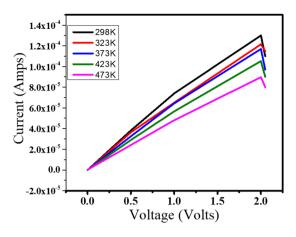

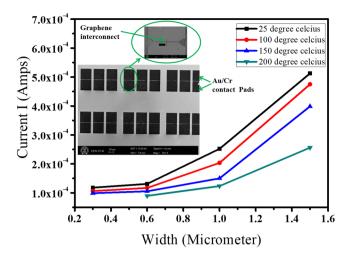

Figure 4. High-temperature current-voltage characteristics of graphene interconnect.

| Width | $\alpha(\text{at } K^{-1})$ |

|-------|-----------------------------|

| 0.3   | 0.00168                     |

| 0.5   | 0.0019                      |

| 0.6   | 0.00248                     |

| 1     | 0.0027                      |

Table 2. Width of graphene interconnects vs TCR.

Effect of temperature on the graphene interconnect. The graphene interconnects between the two metal electrodes on an insulating oxide layer was electrically characterised in the temperature range of  $T=298\,\mathrm{K}$  to 473 K. The typical I-V characteristics of the CVD monolayer graphene interconnect of a  $0.6\,\mu\mathrm{m}$  is given in Fig. 4.

It was observed that with the increase in temperature, the current decreased. The resistivity was found to follow the law  $\rho = \rho_0 + AT$  (A is a positive constant). Therefore, it can be observed from the above figure, that the resistance dependence of temperature can be modelled by the equation.

$$R = R_0(1 + \alpha(T - T_0)) \tag{2}$$

Where  $\alpha$  is the temperature coefficient of resistance. This increase in resistance occurs because of the increase of interaction between charge carriers and the phonons of the graphene nanoribbon.

The sensitivity to temperature was also calculated for this case by using the *Temperature Coefficient of Resistance* (TCR), defined as:

$$TCR = \frac{\partial R/R}{\partial T} \bigg| T = T^* \tag{3}$$

The temperature coefficient of resistance at 298 K for  $0.6 \,\mu m$  was found to be  $0.00248 \, K^{-1}$ . Thus it was found that TCR was positive and therefore with increase in temperature, the current decreased.

TCR for all other cases of the study was also calculated and is listed below:-

Size effects of TCR. From Table 2, it is evident that as the width of graphene interconnect reduces, the coefficient of  $\alpha$  decreases, *i.e.* the sensitivity of the resistivity to temperature variations decreases. The TCR for 1  $\mu$ m was found to be about 38% larger compared to 300 nm wide interconnects.

The variation of current as a function of a) width of graphene interconnects, and b) temperature ranging from 298 K to 473 K are shown in Fig. 5. The SEM image of the interconnect patterns between the metal pads has been shown in the inset of Fig. 5, where the length of interconnect is fixed in all the cases as l  $\mu$ m and width is varied from 0.3 to 1.5  $\mu$ m.

We observed that interconnect of width  $0.3~\mu m$  could not withstand the temperature of 473~K and rather failed after 423~K. The drop in current at 423~K for  $0.3~\mu m$  width as compared to room temperature was noted to be 17% whereas, for all other cases, the drop in current at 473~K as compared to room temperature was more than 30%. The maximum drop in current was observed for  $1.5~\mu m$  as 51%. Thus temperature was found to play a significant role in the current-carrying capacity of the graphene interconnect thus leading to decreased current densities.

**Effect of contact resistance on the graphene interconnect.** It has been reported in the literature by Withers *et al.*<sup>41</sup>, that Cr/Au forms a good Ohmic contact with graphene and hence the contact resistance (Rc) due to the Cr/Au pads were found to be negligible as compared with the sample resistance. Similarly, as reported by Wei *et al.*<sup>42</sup> the contact resistance versus contacts inter-spacing plot for CVD grown graphene with Cr/Au contact

**Figure 5.** Current vs width plot for monolayer graphene interconnect at different temperatures respectively. The inset shows the SEM image of the patterned graphene interconnects between the metal pads.

pads deposited on top of graphene channel was found to be 20 ohms for the contact inter-spacing of 1  $\mu$ m. The similar observation on the contact resistance was also reported by Cai *et al.*<sup>43</sup>, where Cr/Au metal contact pads were fabricated on Single-layer graphene yielding 33.5  $\Omega$  which was found to be compared favourably with the study reported in<sup>42</sup>. We have adopted the procedures followed in the previously reported studies<sup>41–43</sup>, with a similar kind of setup for planning our experiments. The results shown in<sup>41–43</sup> can also be correlated to the experimentally fabricated monolayer graphene interconnect used in our study.

Moreover from Fig. 3(a), it can also be seen that the I-V curve depicted is a linear curve that follows Ohmic behaviour and thus it can also be inferred from the refs.  $^{41-43}$ , the contact resistance is within the range of 20–34 ohm. The total resistance of the proposed fabricated graphene interconnects falls in the range of 3.5–18 K $\Omega$ , and thus the impact of the contact resistance (in the order of 20–34 ohm) on the total resistance can be considered as negligible which is also aligned with the findings reported in  $^{17}$  by Murali *et al*.

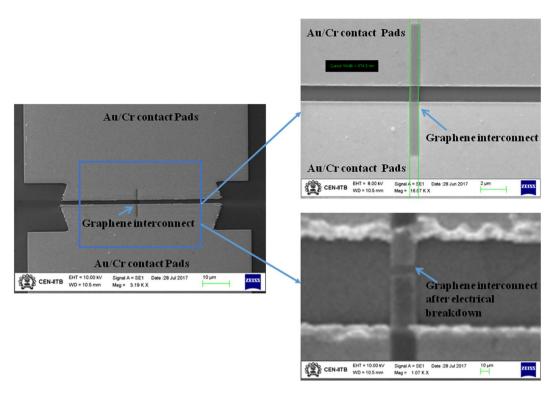

**Electrical breakdown of the graphene interconnects.** Figure 6 shows the SEM images of graphene interconnect covered by HSQ where Fig. 6(a) shows the conducting Graphene interconnect of 600 nm and (b) shows the graphene interconnect after the electrical breakdown. As the voltage was increased, the flow of current produces Joules heating leading to temperature rise across the graphene interconnect. After reaching breakdown voltage of 2 V the graphene interconnect failed at the mid-region, although incipient melting was also observed at the metal pads as heat dissipated equally through them as shown in Fig. 6(c). This may be due to better heat dissipation at the metal pads (Cr/Au) due to higher thermal conductivity of gold-chromium alloy as compared to SiO<sub>2</sub> substrate on which graphene interconnect is directly lying.

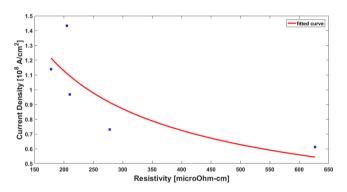

The effect of resistivity on the breakdown current density was analysed on the experimental data using Matlab. From the plot obtained (Fig. 7), it was found that the current density and the resistivity follows a power-law relationship given as-.

$$J_{BR} = C\rho^{-b} \tag{4}$$

Where J represents the current density in Ampere/Cm<sup>2</sup>, C and b are constants while  $\rho$  represents the resistivity respectively. The best fit was obtained for C = 32.9 ×10<sup>8</sup> and b = -0.64 with  $\rho$  having the units of  $\mu\Omega$ -cm.  $R^2$  for this fit was found to be 65%.

The exponent term of 0.64 represents the breakdown of the graphene interconnects with increasing resistivity, indicating that higher resistivity is responsible for the degradation of breakdown current density. This higher resistivity can be attributed to the defect morphologies such as the lattice imperfections, in-plane defects and voids, thus resulting in - jJoule's heating that finally results in the electrical breakdown.

The maximum temperature point of a suspended longitudinal dc biased graphene interconnect was found at the middle point. In steady-state conditions, the distribution of temperature  $\theta(x)$  along a conductor is governed by the heat equation –

$$\frac{d^2\theta(x)}{dx^2} - \frac{\theta(x)}{L_H^2} = -\frac{q}{k} \tag{5}$$

Where  $\mathbf{q} = J^2 \rho$ , is the volumetric heat generation due to heating, k is the thermal conductivity and  $L_H$  is the thermal heating length defined as

$$L_H = \sqrt{\frac{ka}{g}} \tag{6}$$

**Figure 6.** SEM image of (a) Monolayer graphene interconnect between metal pads (b) at intact condition and (c) after electrical breakdown.

Figure 7. Breakdown current density vs Resistivity plot.

g is the thermal conductance of the GNR, and a is the area of cross-section. Inserting the values of k, g from ref.  $^{17}$ , the maximum temperature was found to be 1073 K (800 °C) at x = l/2, where l is the length of the graphene interconnect.

Thus the mechanism of breakdown reported here is believed to be Joule's heating. Similar phenomenon has been reported by Collins *et al.* in <sup>44</sup> where, breakdown in Multi-walled carbon nanotube occurred midway between the two electrodes which was precisely due to the dissipative self-heating that produces a peak temperature of  $500-700\,^{\circ}$ C, a range that agrees well with the thermal oxidation of graphite studies as also reported by Yao *et al.* in <sup>45</sup>. Similarly, Murali *et al.* has studied the breakdown event of the graphene nanoribbon as reported in <sup>17</sup>, where the graphene nanoribbon breakdown occurred midway between the two electrodes producing a peak temperature of  $700-800\,^{\circ}$ C. A similar breakdown phenomenon of the graphene interconnect was also observed in our proposed study, where it was found that the graphene interconnects breakdown occurred midway between the two electrodes and that produces a peak temperature of  $700-800\,^{\circ}$ C, inferred from the above calculation that shows that the maximum temperature obtained at x = 1/2 was  $1073\,^{\circ}$ K ( $800\,^{\circ}$ C), where l is the length of the graphene interconnect resulting thermal oxidation of graphite <sup>45</sup> and maybe intimately connected with self-heating of the graphene interconnects.

Furthermore, in order to explain the constant breakdown voltage with the increment in width, the Power dissipation (Joule's heating) for all cases was calculated as shown below:-

| Sl. No | Width (W) of the sample, µm | I <sup>2</sup> R product value, 10 <sup>-4</sup> W at<br>Breakdown Voltage (2 V) |

|--------|-----------------------------|----------------------------------------------------------------------------------|

| 1.     | 0.3                         | 2.35                                                                             |

| 2.     | 0.6                         | 2.56                                                                             |

| 3.     | 1                           | 5.04                                                                             |

| 4.     | 1.5                         | 8.24                                                                             |

Table 3. Width of graphene interconnects Vs. Power relation.

It can be observed from Table 3 that, the power dissipation increased with the increase in width of the graphene sheet. Also it can be noticed from Fig. 3(b,c), that with the increase of width, the resistance decreases and the current increases.

Thus from the experimental observation, it can be found that:-

$$I_1R_1 = I_2R_2 = I_3R_3 = I_4R_4 = 2V$$

(7)

It can be noted that, although the product of I and R, i.e., breakdown voltage (V) remains the same, for various widths, the quadratic component I play the dominant role in contributing to the self-heating phenomenon which is referred here as the Joule's heating and the same can be represented using the inequality below and is also tabulated in Table 3.

$$I_1^2 R_1 < I_2^2 R_2 < I_3^2 R_3 < I_4^2 R_4$$

(8)

Thus, the quadratic component of the current I is not same throughout and therefore the Power dissipation,  $P = I^2R$  is causing the breakdown in the graphene interconnects which is the jJoule's heating. Also it can be noted that with the wider graphene patterns, both the heat dissipation and heat absorption capability increases due to increase in the surface area. Since the radiative heat transfer is directly proportional to the surface area, increase in Joule's heating due to the quadratic component of current ( $I^2$ ) is therefore compensated by the higher heat dissipation resulting in averaging out the effect of increase in the temperature of the patterned graphene sample and hence the breakdown voltage doesn't get lowered down even for the wider graphene patterns.

Hence from the experimental observations and the theoretical calculations, the authors intuitively conclude that the mechanism of breakdown is attributed primarily by the self-heating referred to as Joule's heating.

# Conclusion

The effect of width and temperature on the electrical properties of CVD monolayer graphene has been investigated experimentally. The outcomes of the study are summarised below:

- A simple two-step lithography for patterning CVD monolayer graphene has been used, thus resulting in lower complexity, cost-effective solution and higher current density as compared to the state-of-the-art fabrication methods for CVD graphene.

- The fabricated graphene interconnects were found to have a current density of  $1.18 \times 10^8 \, \text{A/cm}^2$  (for 0.3  $\, \mu \text{m}$  width) that is 100 times ( $10^6 \, \text{A/cm}^2$ ) more than the copper, resulting in outperforming copper-based interconnects.

- Based on our experimental observation, we formulated a generalised equation between the current and width

of the CVD monolayer graphene-based interconnect that enables to calculate the current or width values

without doing fabrication.

- The current at the breakdown point was found to decrease significantly with the increase in temperature, indicating a positive temperature coefficient of resistance. Further, as width of interconnects increases from 0.3 to 1.5 μm, the current at breakdown voltage was found to increase, at an increasing rate. This is due to decrease in scattering because of lesser contribution of boundaries, as the width of interconnects increases.

- It was observed that the graphene interconnects failed at the mid-segment of the interconnects due to incipient fusion at the breakdown voltage.

- The failure mechanism of the graphene interconnects was analysed. We found that the current density and the resistivity follows a power-law relationship signifying that higher resistivity of the interconnects were also responsible in the degradation of breakdown current density. This higher resistivity can be attributed to the defect morphologies such as the lattice imperfections, in-plane defects and voids, thus resulting in joule's heating that finally results in the electrical breakdown.

- Monolayer graphene interconnects on SiO<sub>2</sub> substrate obeyed Ohm's law.

- The drop in current at 473 K for nearly all other cases as compared to room temperature was more than 30%.

- The temperature was found to have a profound effect on the graphene interconnects. Results show that while

working with lower widths of the monolayer graphene interconnects at high temperatures pose challenges.

Thus with the maximum current density being  $1.18 \times 10^8$  A/cm² for  $0.3~\mu m$  graphene interconnect on SiO<sub>2</sub>/Si substrate, i.e. two orders higher than that of conventionally used copper interconnects, Graphene has an enormous potential in outperforming copper wires.

Received: 1 May 2019; Accepted: 12 November 2019;

Published online: 10 April 2020

### References

- 1. Porod, W. & Niemier, M. Better Computing With Magnets The simple bar magnet, shrunk down to the nanoscale, could be a powerful logic device, *IEEE Spectrum* (2015).

- Cowburn, R. P. & Welland, M. E. Room Temperature Magnetic Quantum Cellular Automata. Science 287, 1466, https://doi. org/10.1126/science.287.5457.1466 (2000).

- 3. Imre, A. et al. Majority logic gate for magnetic quantum-dot cellular automata. Science 311, 205-208 (2006).

- 4. Steinlesberger, G. et al. Electrical assessment of copper damascene interconnects down to sub-50 nm feature sizes. *Microelectronic Engineering* **64**(Issues 1–4), 409–416, https://doi.org/10.1016/S0167-9317(02)00815-8 (2002).

- Chang, C. W., et al, Joule heating-assisted electromigration failure mechanisms for dual damascene Cu/SiO/2/interconnects, Proceedings of the 10th International Symposium on the Physical and Failure Analysis of Integrated Circuits. IPFA, 69–74, 10.1109/ IPFA.2003.1222741 (2003).

- Das, J., Alam, S. M. and Bhanja, S., Ultra-Low Power Hybrid CMOS-Magnetic Logic Architecture, IEEE Transactions on Circuits and Systems I59 (9), DOI: 10.1109/TCSI.2012.2185311 (2012)

- 7. Alam M. T., et al, On-Chip Clocking for Nanomagnet Logic Devices, IEEE TRANSACTIONS ON NANOTECHNOLOGY, 9 (3),

- 8. Novoselov, K. S. et al. Electric field effect in atomically thin carbon films, Science 306, 666–669, https://doi.org/10.1126/science.1102896 (2004)

- 9. Carlo Gilardi et al. Graphene-Si CMOS oscillators. Nanoscale 11, 3619-3625, https://doi.org/10.1039/C8NR07862A (2019).

- 10. Ferrari, A. C. *et al.* Science and technology roadmap for graphene, related two-dimensional crystals, and hybrid systems. *Nanoscale* 7, 4598–4810, https://doi.org/10.1039/C4NR01600A (2015).

- 11. SanghamitraDebroy, V. P. K., Miriyala, K., VijayaSekhar, S. G. & Acharyya, A. Acharyya, Graphene heals thy cracks. Comput. Mater. Sci. 109, 84, https://doi.org/10.1016/j.commatsci.2015.05.025 (2015).

- 12. SanghamitraDebroy, V. P. K. Miriyala, K. VijayaSekhar, S. G. Acharyya, A. Acharyya, Synergistic effect of temperature and point defect on the mechanical properties of single layer and bi-layer graphene, Superlattices and Microstructures, (Accepted- in press), https://doi.org/10.1016/j.spmi.2017.08.040.

- 13. VijayaSekhar, K. et al. Self-healing phenomena of graphene: potential and applications. Open Phys. 14, 364, https://doi.org/10.1515/phys-2016-0040 (2016).

- 14. Sivasubramani, S., Debroy, S., Acharyya, S. G., Acharyya, A., Tunable intrinsic magnetic phase transition in pristine single-layer graphene nanoribbons, Nanotechnology, 29 (45), 455701, IOP Publishing, (2018).

- 15. Morozov, S. V. et al. Giant Intrinsic Carrier Mobilities in Graphene and Its Bilayer. Phys. Rev. Lett. 100, 016602, https://doi.org/10.1103/PhysRevLett.100.016602 (2008).

- 16. Du, X., Skachko, I., Barker, A. & Andrei, E. Y. Approaching ballistictransport in suspended graphene. *Nat. Nanotechnol.* 3(no. 8), 491–495, https://doi.org/10.1038/nnano.2008.199 (2008).

- Murali, R., Yang, Y., Brenner, K., Beck, T. & Meindl, J. D. Breakdown current density of graphene nanoribbons. Appl. Phys. Lett. 94, 243114, https://doi.org/10.1063/1.3147183 (2009).

- 18. Balandin, A. A. et al. Superior thermal conductor graphene. Nano Lett. 8, 902-907, https://doi.org/10.1021/nl0731872 (2008).

- 19. Lee, K. J., Chandrakasan, A. P. and Kong, J., Breakdown Current Density of CVD-Grown Multilayer Graphene Interconnects, IEEE ELECTRON DEVICE LETTERS, VOL. 32, NO. 4, APRIL 2011

- Prasad, N., Kumari, A., Bhatnagar, P. K., Mathur, P. C. & Bhatia, C. S. Current induced annealing and electrical characterization of single layer graphene grown by chemical vapor deposition for future interconnects in VLSI circuits. APPLIED PHYSICS LETTERS 105, 113513, https://doi.org/10.1063/1.4895802 (2014).

- 21. Murali, R., Brenner, K., Yang, Y., Beck, T. & Meindl, J. D. Resistivity of Graphene Nanoribbon Interconnects. *IEEE Electron Device Letters* 30, 611–613, https://doi.org/10.1109/LED.2009.2020182 (2009).

- Yang, Y. & Murali, R. Impact of Size Effect on Graphene Nanoribbon Transport. IEEE Electron Device Letters 31, 237–239, https://doi.org/10.1109/LED.2009.2039915 (2010).

- 23. Jain, N. *et al.* Extenuated interlayer scattering in double-layered graphene/hexagonal boron nitride heterostructure. *Carbon* 126, 17–22, https://doi.org/10.1016/j.carbon.2017.09.074 (2018).

- 24. Wang, L. et al. Negligible Environmental Sensitivity of Graphene in a Hexagonal Boron Nitride/Graphene/h-BN Sandwich Structure. ACS Nano 6(10), 9314–9319, https://doi.org/10.1021/nn304004s (2012).

- 25. Mehta, R., Chugh, S. & Chen, Z. Enhanced Electrical and Thermal Conduction in Graphene-Encapsulated Copper Nanowires. *Nano Lett.* 15(3), 2024–2030, https://doi.org/10.1021/nl504889t (2015).

- 26. Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nano 5, 722-726 (2010).

- 27. Jain, N., Durcan, C. A., Jacobs-Gedrim, R., Xu, Y. & Yu, B. Graphene interconnects fully encapsulated in layered insulator hexagonal boron nitride. *Nanotechnology* 24, 355202 (2013).

- 28. Hwang, E. H. & Sarma, S. D. Acoustic phonon scattering limited carrier mobility in two-dimensional extrinsic graphene. *Phys. Rev.* B 77, 115449, https://doi.org/10.1103/PhysRevB.77.115449 (2008).

- Romanenko, A. I. et al. Quasi-two-dimensional conductivity and magnetoconductivity of graphite-like nanosize crystallites. Solid State Commun. 137, 625, https://doi.org/10.1016/j.ssc.2006.01.003 (2006).

- 30. Nirmalraj, P. N., Lutz, T., Kumar, S., Duesberg, G. S. & Boland, J. J. Nanoscale Mapping of Electrical Resistivity and Connectivity in Graphene Strips and Networks. *Nano Lett.* 11, 16, https://doi.org/10.1021/nl101469d (2011).

- 31. Hwang, E. H. & Sarma, S. D. Screening-induced temperature-dependent transport in two-dimensional graphene. *Phys. Rev. B* **79**, 165404, https://doi.org/10.1103/PhysRevB.79.165404 (2009).

- 32. Liu, C., Ma, Y., Li, W. & Dai, L. The evolution of Raman spectrum of graphene with the thickness of SiO2 capping layer on Si substrate. *Appl. Phys. Lett.* 103, 213103, https://doi.org/10.1063/1.4832063 (2013).

- 33. Ni, Z., Wang, Y., Yu, T. & Shen, Z. Raman Spectroscopy and Imaging of Graphene. *Nano Res* 1, 273 291, https://doi.org/10.1007/s12274-008-8036-1 (2008).

- 34. Reina, A. et al. Large area few-layer graphene films on arbitrary substrates by chemical vapor deposition. Nano Lett. 9(no. 1), 30–35 (2009).

- 35. Kim, K. S. et al. Large-scale pattern growth of graphene films for stretchable transparent electrodes. Nature 457(no. 7230), 706–710 (2009).

- 36. Lee, Y. et al. Wafer-scale synthesis and transfer of graphene films. Nano Lett. 10(no. 2), 490-493 (2010).

- 37. Bae, S. et al. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotechnol. 5(no. 8), 574–578 (2010).

- 38. Chen, X., et al, High-speed graphene interconnects monolithically integrated with CMOS ring oscillators operating at 1.3 GHz, IEDM Tech. Dig., pp. 1-4, (2009).

- 39. Niemier, M., et al, Clockingstructures and power analysis for nanomagnet-based logic devices, in Proceedings of the 2007international symposium on Low power electronics and design (ISLPED 07),10.1145/1283780.1283787.

- 40. Chen, Z., Lin, Y. M., Rooks, M. J. & Avouris, P. Graphene nano-ribbon electronics. *Physica E: Low-dimensional Systems and Nanostructures* 40, 228, https://doi.org/10.1016/j.physe.2007.06.020 (2007).

- 41. Withers, F., Dubois, M. & Savchenko, A. K. Electron properties of fluorinated single-layer graphene transistors. *PHYSICAL REVIEW B* **82**, 073403, https://doi.org/10.1103/PhysRevB.82.073403 (2010).

- 42. Wei, W., et al, Graphene field effect transistors with optimized contact resistance for current gain, in Proc. 75th Annu. Device Res. Conf., Aug. 2017, pp. 1–2.

- 43. Cai, X. et al. Sensitive room-temperature terahertz detection via the photothermoelectric effect in graphene. Nature Nanotechnology ume 9, 814–819 (2014).

- 44. Collins, P. G., Hersam, M., Arnold, M. & Martel, R. and Ph. Avouris, Current Saturation and Electrical Breakdown in Multiwalled Carbon Nanotubes. *Phys. Rev. Lett.* **86**, 3128 (2001).

- 45. Yao, Z., Kane, C. L. & Dekker, C. High-Field Electrical Transport in Single-Wall Carbon Nanotubes. Phys. Rev. Lett. 84, 2941 (2000).

# Acknowledgements

The authors would like to thank Indian Nanoelectronics Users Program, IIT Bombay (IITB) for providing the facilities for fabrication and electrical characterisation of the device at Centre of Excellence in Nanoelectronics (CEN), IITB.

# **Author contributions**

S.D. and S.S. contributed equally to this work. S.D. and S.S. carried out the fabrication procedures and analysed the results. G.V., S.D. and S.S. did the EBL patterning. S.D. wrote the paper. S.S. and S.D. revised the paper. A.A. and S.G.A. supervised the study and revised the paper. All authors discussed the results, prepared the figures and commented on the manuscript.

# **Competing interests**

The authors declare no competing interests.

# Additional information

Correspondence and requests for materials should be addressed to A.A.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2020