#### University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

8-2022

# Constraint-Aware, Scalable, and Efficient Algorithms for Multi-Chip Power Module Layout Optimization

Imam Al Razi University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Computer-Aided Engineering and Design Commons, Power and Energy Commons, and the Software Engineering Commons

#### Citation

Al Razi, I. (2022). Constraint-Aware, Scalable, and Efficient Algorithms for Multi-Chip Power Module Layout Optimization. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/4602

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

# Constraint-Aware, Scalable, and Efficient Algorithms for Multi-Chip Power Module Layout Optimization

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering

by

# Imam Al Razi Bangladesh University of Engineering and Technology Bachelor of Science in Electrical and Electronic Engineering, 2016

### August 2022 University of Arkansas

| This dissertation is approved for reco  | ommendation to the Graduate Council.  |

|-----------------------------------------|---------------------------------------|

| Yarui Peng, Ph.D. Dissertation Director |                                       |

| Jia Di, Ph.D.<br>Committee Member       | David Andrews, Ph.D. Committee Member |

| Alan Mantooth, Ph.D. Committee Member   |                                       |

#### Abstract

Moving towards an electrified world requires ultra high-density power converters. Electric vehicles, electrified aerospace, data centers, etc. are just a few fields among wide application areas of power electronic systems, where high-density power converters are essential. As a critical part of these power converters, power semiconductor modules and their layout optimization has been identified as a crucial step in achieving the maximum performance and density for wide bandgap technologies (i.e., GaN and SiC). New packaging technologies are also introduced to produce reliable and efficient multichip power module (MCPM) designs to push the current limits. The complexity of the emerging MCPM layouts is surpassing the capability of a manual, iterative design process to produce an optimum design with agile development requirements. An electronic design automation tool called PowerSynth has been introduced with ongoing research toward enhanced capabilities to speed up the optimized MCPM layout design process. This dissertation presents the PowerSynth progression timeline with the methodology updates and corresponding critical results compared to v1.1. The first released version (v1.1) of PowerSynth demonstrated the benefits of layout abstraction, and reduced-order modeling techniques to perform rapid optimization of the MCPM module compared to the traditional, manual, and iterative design approach. However, that version is limited by several key factors: layout representation technique, layout generation algorithms, iterative design-rule-checking (DRC), optimization algorithm candidates, etc. To address these limitations, and enhance PowerSynth's capabilities, constraint-aware, scalable, and efficient algorithms have been developed and implemented. PowerSynth layout engine has evolved from v1.3 to v2.0 throughout the last five years to incorporate the algorithm updates and generate all 2D/2.5D/3D Manhattan layout solutions. These fundamental changes in the layout generation methodology have also called for updates in the performance modeling techniques and enabled exploring different optimization algorithms. The latest PowerSynth 2 architecture has been implemented to enable electro-thermo-mechanical and reliability optimization on 2D/2.5D/3D MCPM layouts, and set up a path toward cabinet-level optimization. PowerSynth v2.0 computer-aided design (CAD) flow

has been hardware-validated through manufacturing and testing of an optimized novel 3D MCPM layout. The flow has shown significant speedup compared to the manual design flow with a comparable optimization result.

#### Acknowledgements

First, thanks to the Almighty Creator who has showered blessings throughout my life and has enabled me to complete this dissertation. Then, I would like to express my heartiest gratitude to my dissertation director, mentor, research, and academic advisor, Dr. Yarui Peng for his continuous direction, support, and efforts over the last five years. I have learned a lot from his invaluable expertise and guidance. His constructive advice and critiques enabled me to improve my research from time to time. Without his supervision and encouragement, this dissertation would not have materialized. Thanking him would not be enough for the knowledge I have learned from him. I would like to thank Dr. Alan Mantooth for his guidance, and feedback throughout my research works. His expertise has always helped me towards shaping myself as a better researcher. Also, his strong network and popularity in the power electronics society have helped me to achieve attention in different places. Thanks to Dr. Jia Di and Dr. David Andrews for taking time out of their schedules to participate in the committee for this dissertation. Moreover, I have learned a lot from their courses, which helped me to lay the foundation for CAD research as well as a computer engineer. I am really grateful for all the help and cooperation I have received from them for the last five years. Also, I want to thank Dr. David Huitink for his suggestions and helps with my research progress. I want to extend my gratitude to Dr. Brajendra Panda, our graduate coordinator, who has directed me in every formal step towards graduation and also taught several courses, which helped me in earning my degree as well. Also, I would like to thank Tom Vrotsos for his suggestions during the early stage of this disseration work.

I would like to thank my parents, my wife, my sister, and other family members, who have supported me in every step to achieve this goal. It would not have been possible for me to finish this degree without all of them. I am grateful to have such a supporting family.

I would like to express my great appreciation to my colleagues, Quang Le, Tristan Evans, and Shilpi Mukherjee, who helped me from the beginning of my research. They have guided me with valuable resources to make the onboarding very smooth. Quang's support on the research and development works helped me a lot to improve my skills. Besides, Tristan's and Shilpi's

suggestions have helped me to improve my writing and presentation skills a lot. I would like to thank Joshua Mitchener for helping with the PowerSynth v2.0 GUI development. I would like to mention MD Arafat Kabir, who has been very helpful in both my academic and personal life. As a former lab-mate, he helped me on brainstorming, coding, and many other technical issues. His in-depth technical knowledge in engineering and technology encourages me a lot to be a better tech-enthusiast. Also, I would like to thank Dr. S M Nahian Al Sunny, and Dr. Md Rakib Shahriar for their help with my programming skills improvement. I want to thank students from the UA power group especially Dr. Md Hazzaz Mahmood, Md Bakhtiyar Nafis, Ange Iaradukunda, Dr. Mahsa Montazeri, Ahmed Rahouma Fares Rahouma, Yuheng Wu, Yuqi Wei, Andrea Wallace, David Gonzalez Castillo, Hao Chen, Md Jabed Hossain, Dr. Yuxiang Chen, Reece Whitt who helped me throughout the manufacturing and testing of the power modules. Also, I would like to thank Md Asif Imran Emon for helping me with his power module packaging and testing expertise.

I want to express my gratitude to the National Science Foundation (NSF) funded research center Power Optimization of Electro-Thermal Systems (POETS) and the Army Research Lab (ARL) for supporting the projects that led to this dissertation. POETS has been a great platform for me to develop and improve my communication, technical, and behavioral skills. POETS helped me to improve my research quality through the Annual meetings and Tech conferences in every year, where I interacted with a lot of experts from both academia and industry.

Finally, I would like to thank Bangladeshi students and community people who have made my life in Fayetteville, AR very happening and eventful. Dr. Samrat Nath is one of the kind-hearted persons I have ever seen, who helped me to settle down in Fayetteville, AR.

#### **Dedication**

To my mother, who always cares for me

To my father, who always believes in me

To my sister and brother-in-law, who always inspire me

To my beautiful wife, who has been by my side supporting me in every step of my career

This thesis and all of my achievements are the results of the care, support and sacrifices from you all. Without your continued belief in me and prayer to succeed, I would not be where I am today.

I LOVE YOU ALL

# **Table of Contents**

| 1 | Intr | oduction                                                         | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  | Design Automation in Power Electronics                           | 1  |

|   | 1.2  | Need for Design Automation in MCPM Layout Optimization           | 3  |

|   | 1.3  | MCPM Design Variations                                           | 5  |

|   | 1.4  | Dissertation Contributions                                       | 7  |

|   | 1.5  | Contributions from Other Team Members                            | 11 |

|   | 1.6  | Dissertation Outline                                             | 12 |

| 2 | Lite | rature Review                                                    | 14 |

|   | 2.1  | MCPM Physical Design Automation and Optimization Efforts         | 14 |

|   |      | 2.1.1 Existing Works Outside PowerSynth Scope                    | 14 |

|   |      | 2.1.2 Preliminary Research and Development Efforts on PowerSynth | 16 |

|   | 2.2  | Power Modules' Reliability Optimization Efforts                  | 18 |

|   |      | 2.2.1 Thermal Cycling Impact Minimization Efforts                | 20 |

|   |      | 2.2.2 Electromigration Impact Minimization Efforts               | 20 |

| 3 | Mot  | ivations and PowerSynth Progression Flow                         | 22 |

|   | 3.1  | Motivations                                                      | 22 |

|   | 3.2  | PowerSynth Progression Flow                                      | 23 |

|   | 3.3  | Preliminary Research                                             | 26 |

| 4 | Hier | carchical 2D/2.5D MCPM Layout Optimization                       | 35 |

|   | 4.1  | Methodology                                                      | 35 |

|   | 4.2  | Models and Optimization Algorithms                               | 42 |

|   |      | 4.2.1 Performance Evaluation Models                              | 42 |

|   |      | 4.2.2 Optimization Algorithms                                    | 44 |

|   | 4.3  | Results                                                          | 46 |

|   | 4.4  | Limitations                                                      | 52 |

| 5 | Pow   | erSynth   | 2: High-Density 3D MCPM Layout Optimization       | 53 |

|---|-------|-----------|---------------------------------------------------|----|

|   | 5.1   | Powers    | Synth 2 Architecture                              | 53 |

|   |       | 5.1.1     | User Interfaces and Design Input                  | 53 |

|   |       | 5.1.2     | Layout Generation and Evaluation                  | 55 |

|   |       | 5.1.3     | Design Optimization and Solution Export           | 57 |

|   | 5.2   | Physic    | al Design Automation Methodology                  | 57 |

|   |       | 5.2.1     | Layout Representation and Data Structures         | 58 |

|   |       | 5.2.2     | Constraint-Aware Layout Synthesis Algorithms      | 61 |

|   |       | 5.2.3     | Multi-Objective Modeling and Optimization         | 65 |

|   | 5.3   | Suppor    | rted High-Density Power Packaging                 | 67 |

|   | 5.4   | 3D La     | yout Optimization Case Study                      | 71 |

|   |       | 5.4.1     | Layout Optimization                               | 71 |

|   |       | 5.4.2     | Post-Layout Optimization                          | 73 |

|   | 5.5   | Experi    | mental Results                                    | 73 |

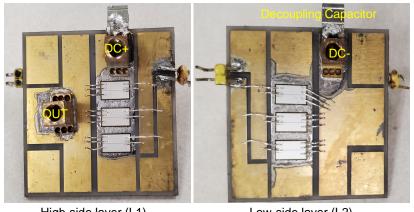

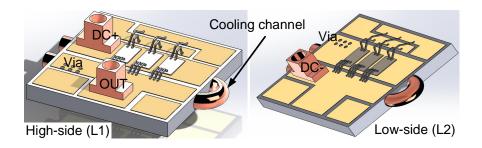

|   |       | 5.5.1     | 3D Power Module Fabrication                       | 73 |

|   |       | 5.5.2     | Functionality Verification                        | 75 |

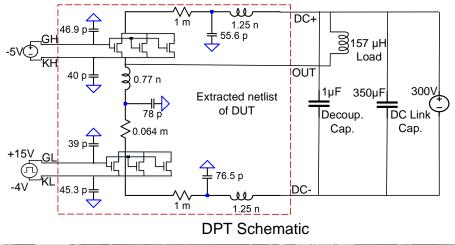

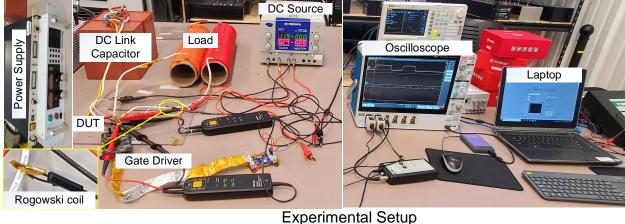

|   |       | 5.5.3     | Electrical Validation                             | 77 |

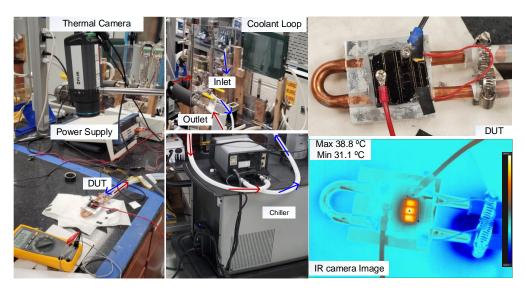

|   |       | 5.5.4     | Thermal Validation                                | 77 |

|   |       | 5.5.5     | Comparison with Other High-Density Designs        | 79 |

|   | 5.6   | Limita    | tions                                             | 80 |

| 6 | Relia | ability ( | Optimization Using PowerSynth                     | 82 |

|   | 6.1   | Optimi    | ization for Reducing Thermal Cycling Impact       | 82 |

|   |       | 6.1.1     | Methodology                                       | 82 |

|   |       | 6.1.2     | Thermal Model Validation                          | 88 |

|   |       | 6.1.3     | Optimization Results                              | 90 |

|   | 6.2   | Optimi    | ization for Reducing Electromigration (EM) Impact | 94 |

|   |       | 6.2.1     | Methodology and Design Tools                      | 95 |

|    |                | 6.2.2   | Expe  | erim | ental | Re  | sul | ts | <br>• |  | <br>• | • |  | <br>• | <br>• | <br>• | <br>• | <br> | . 101 |

|----|----------------|---------|-------|------|-------|-----|-----|----|-------|--|-------|---|--|-------|-------|-------|-------|------|-------|

| 7  | Con            | clusion | and F | utu  | re V  | ork | ζ.  |    |       |  |       |   |  |       |       |       |       |      | 106   |

|    | 7.1            | Conclu  | ısion |      |       |     |     |    |       |  |       |   |  |       |       |       |       | <br> | . 106 |

|    | 7.2            | Future  | Work  |      |       |     |     |    |       |  |       |   |  |       |       |       |       | <br> | . 107 |

| Re | References 110 |         |       |      |       | 110 |     |    |       |  |       |   |  |       |       |       |       |      |       |

| Aı | pend           | lix     |       |      |       |     |     |    |       |  |       |   |  |       |       |       |       |      | 119   |

# **List of Figures**

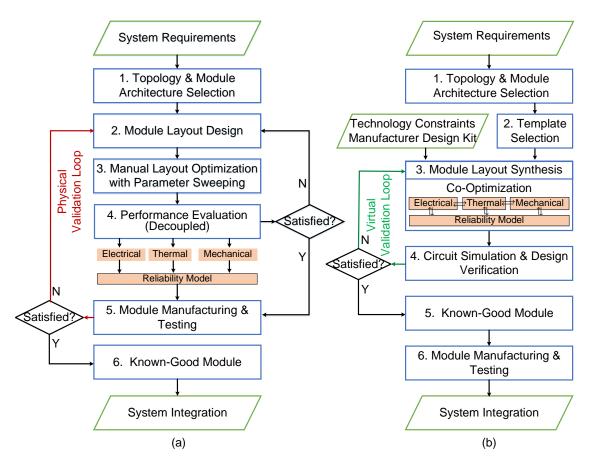

| 1  | Power module design flow: (a) traditional vs. (b) automated                            | ۷  |

|----|----------------------------------------------------------------------------------------|----|

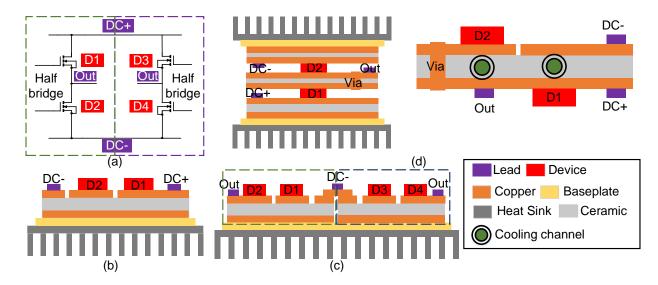

| 2  | (a) Full-bridge power module circuit, cross sections of three MCPM structures: (b)     |    |

|    | 2D half-bridge, (c) 2.5D full-bridge, (d) 3D half-bridge                               | 6  |

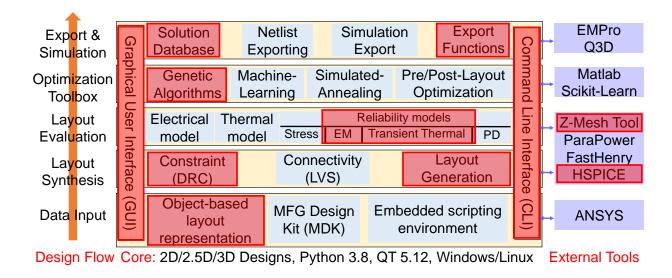

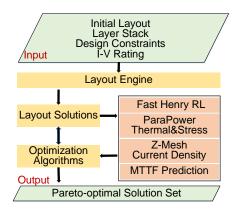

| 3  | PowerSynth 2 architecture                                                              | 7  |

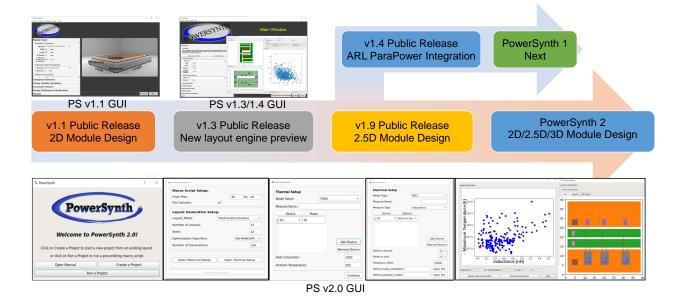

| 4  | PowerSynth package release flow with GUI                                               | 24 |

| 5  | Layer stack and design constraints illustration, corner-stitched planes (HCS/VCS)      |    |

|    | and corresponding constraint graphs (HCG/VCG)                                          | 28 |

| 6  | (a) Half bridge power module layout and (b) associated reliability constraints:        |    |

|    | G1 through G8 are voltage-dependent minimum spacing, and traces have current-          |    |

|    | dependent minimum width                                                                | 29 |

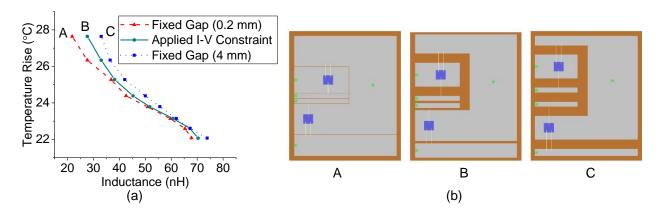

| 7  | (a) Three Pareto-fronts of layout solutions. Sample 45 mm $\times$ 55 mm layouts gen-  |    |

|    | erated with (b) 0.2 mm gaps, (c) I-V dependent constraints, (d) 4 mm gaps              | 31 |

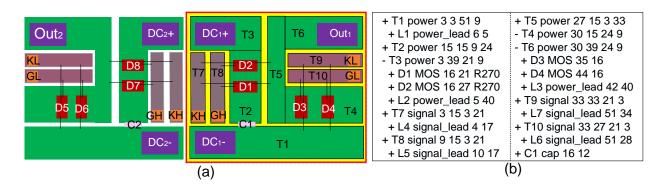

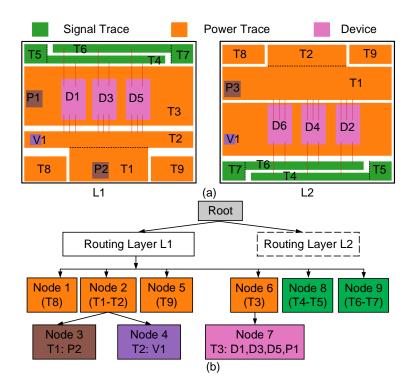

| 8  | (a) Two half-bridge modules of a 2.5D full-bridge power module, (b) input geom-        |    |

|    | etry script for the right half module                                                  | 36 |

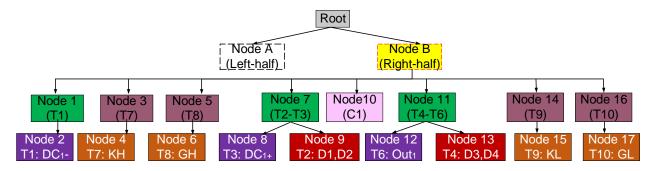

| 9  | (a) Tree structure of the full-bridge module from Figure 8(a)                          | 36 |

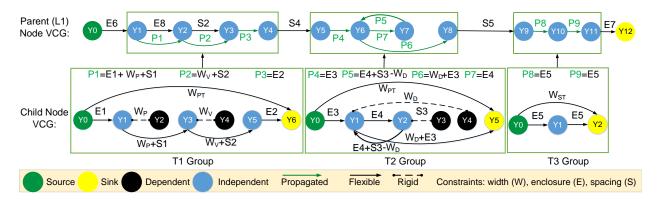

| 10 | Illustration of edges, vertices, and constraint propagation for a sample layout        | 37 |

| 11 | Five types of rigid wire bond connections                                              | 42 |

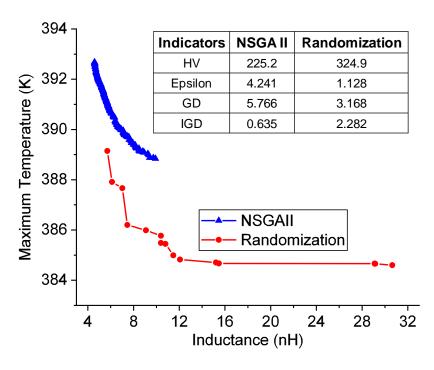

| 12 | Pareto-front solution set comparison and tabular representation of the performance     |    |

|    | indicator values. Here, HV reference point is (33,397)                                 | 46 |

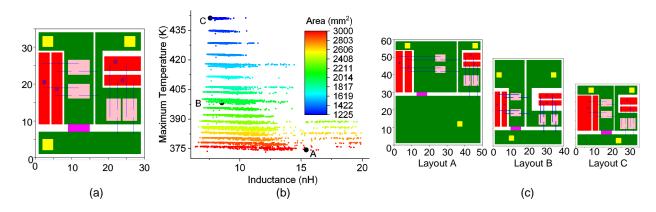

| 13 | (a) Minimum-sized solution $(30mm \times 35mm)$ , (b) complete solution space, (c) se- |    |

|    | lected three layouts                                                                   | 47 |

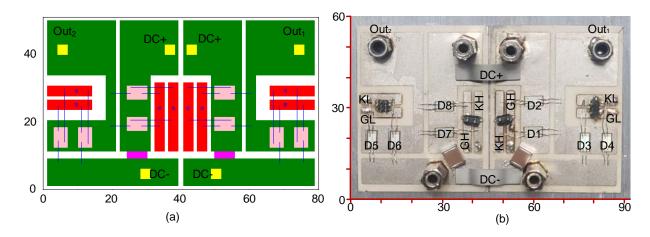

| 14 | (a) Balanced 2.5D solution layout from the tool, (b) fabricated 2.5D full-bridge       |    |

|    | power module (92 mm $\times$ 60 mm)                                                    | 48 |

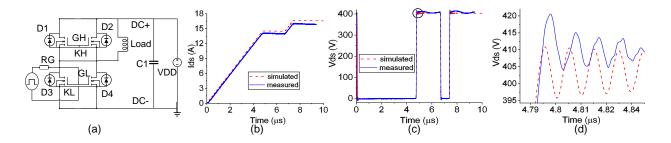

| 15 | (a) DPT schematic and measurement results for (b) Ids, (c) Vds, and (d) zoom-in        |    |

|    | shot of (c)                                                                            | 49 |

| 16 | (a) Thermal measurement experimental setup, (b) measurement results                | 50 |

|----|------------------------------------------------------------------------------------|----|

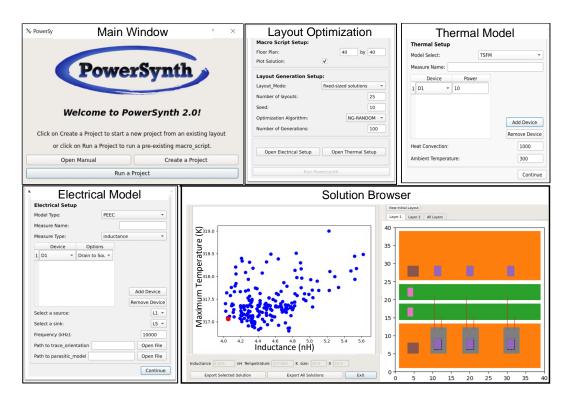

| 17 | PowerSynth 2 graphical user interface (GUI)                                        | 54 |

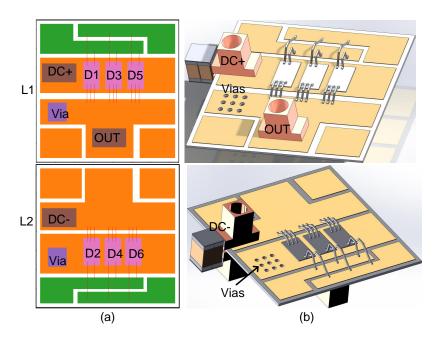

| 18 | Input layout structure of a 3D MCPM: (a) 2D view of each routing layer, (b) the    |    |

|    | L1 layer hierarchical tree                                                         | 55 |

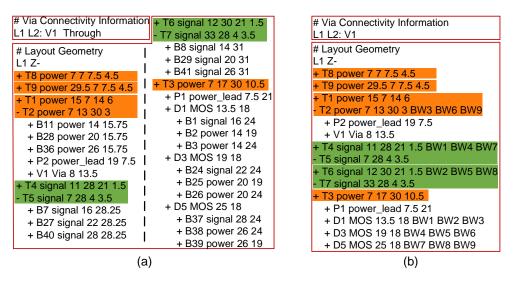

| 19 | Input geometry script of routing layer L1: (a) developer mode, (b) user mode       | 56 |

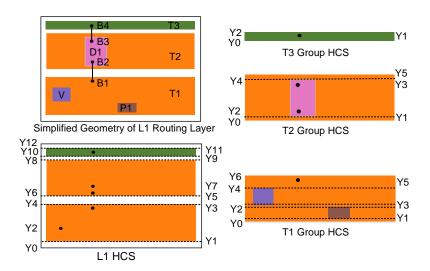

| 20 | Constraint propagation using a simplified example from Figure 18(a)                | 60 |

| 21 | Bottom-up constraint propagation illustration for HCS shown in Figure 20. Here,    |    |

|    | subscripts P, V, D, PT, ST represents power lead, via, device, power trace, signal |    |

|    | trace, respectively                                                                | 60 |

| 22 | Top-down location propagation illustration for T1 in Figure 20                     | 64 |

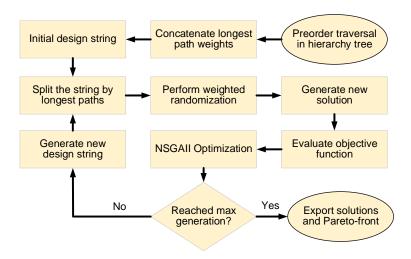

| 23 | NSGAII implementation workflow                                                     | 64 |

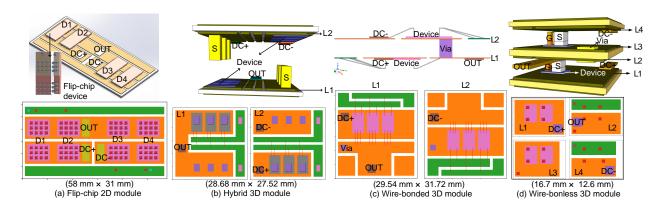

| 24 | 3D structure and minimum-sized solution of high-density packaging layouts          | 65 |

| 25 | Solution space generated by PowerSynth 2 using (a) Randomization, (b) NSGAII,      |    |

|    | (c) 2D view of the three selected solutions                                        | 67 |

| 26 | (a) Modified layout of solution B, (b) exported 3D structure                       | 68 |

| 27 | Fabricated 3D module                                                               | 69 |

| 28 | Double pulse test schematic and experimental setup                                 | 70 |

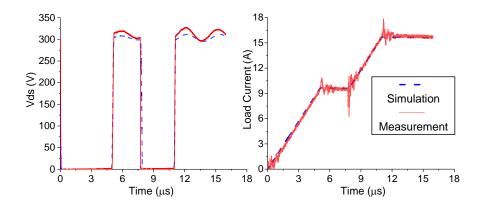

| 29 | Double pulse test comparison on Vds and load current                               | 73 |

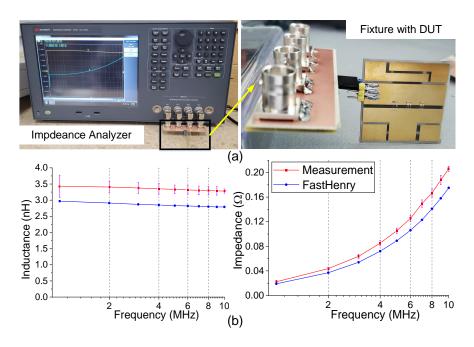

| 30 | (a) Impedance measurement setup and (b) result comparison for the power loop       | 74 |

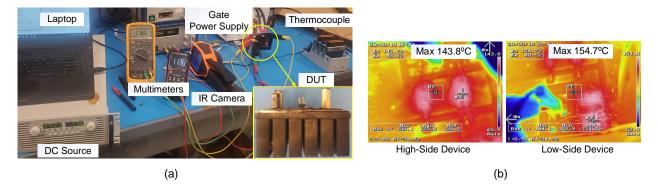

| 31 | Proposed embedded cooling structure                                                | 79 |

| 32 | Thermal test setup and temperature measurement result                              | 79 |

| 33 | Two-step optimization flow                                                         | 83 |

| 34 | Thermal model workflow                                                             | 83 |

| 35 | Cauer thermal network for the test structure (shown in Figure 38(a))               | 84 |

| 36 | Variation of (a) thermal resistance, (b) thermal capacitance for organic PCM (Ery- |    |

|    | thritol) against temperature                                                       | 85 |

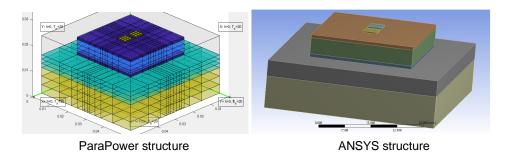

| 37 | Test structure in the state-of-the-art tools                                       | 85 |

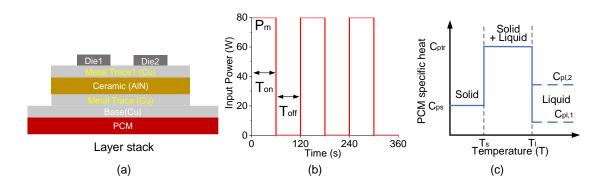

| 38 | (a) Layer stack of the test structure, (b) model validation result input power wave-         |

|----|----------------------------------------------------------------------------------------------|

|    | form, (c) specific heat variation of PCM against temperature                                 |

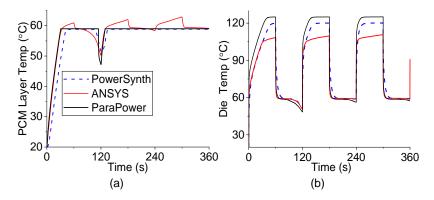

| 39 | Maximum temperature result comparison for the input waveform shown in Fig-                   |

|    | ure 38 (b): (a) PCM layer, and (b) die layer                                                 |

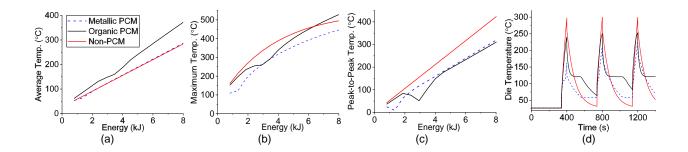

| 40 | Energy sweep result for three metrics: (a) average, (b) maximum, (c) peak-to-peak,           |

|    | and (d) maximum transient temperature waveform comparison for device layer 91                |

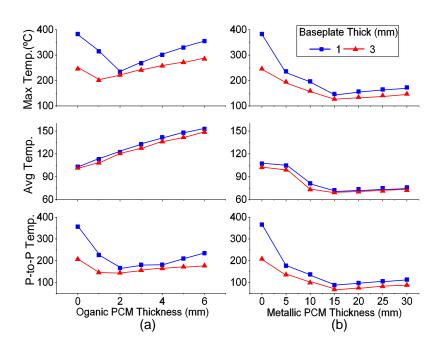

| 41 | Multiple temperature metrics vs. layer thickness: (a) organic PCM case, (b) metal-           |

|    | lic PCM case                                                                                 |

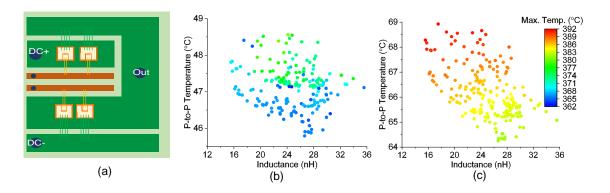

| 42 | (a) Layout of a half-bridge power module and fixed-floorplan size $(46mm \times 36mm)$       |

|    | solution space. (b) metallic PCM, and (c) Non-PCM case                                       |

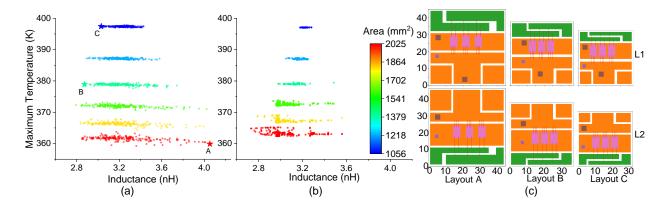

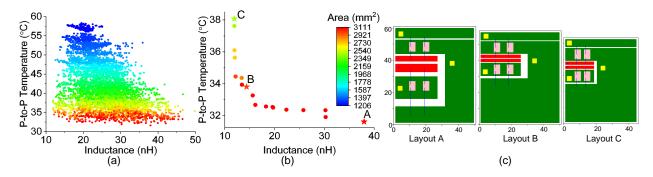

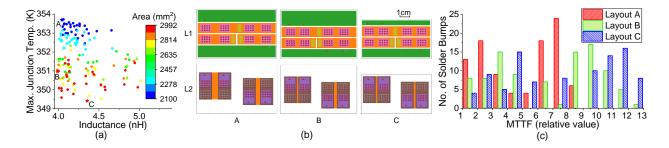

| 43 | (a) Complete solution space with variable floorplan sizes and (b) the Pareto-front           |

|    | with (c) three selected solutions: Layout A (51 mm $\times$ 61 mm), Layout B (51 mm $\times$ |

|    | 58.5 <i>mm</i> ), Layout C (46 <i>mm</i> × 53.5 <i>mm</i> )                                  |

| 44 | EM-aware optimization flow                                                                   |

| 45 | Sample mesh from our Z-Mesh tool                                                             |

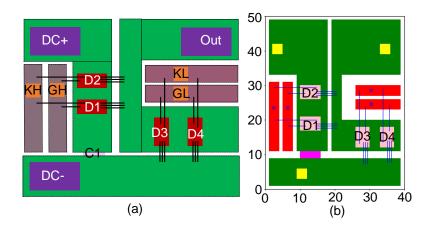

| 46 | Minimum-sized solution from PowerSynth                                                       |

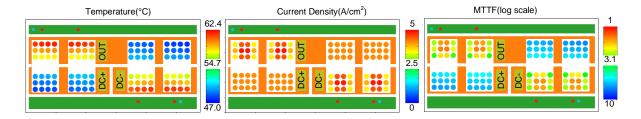

| 47 | Temperature, current density, and MTTF results at DC                                         |

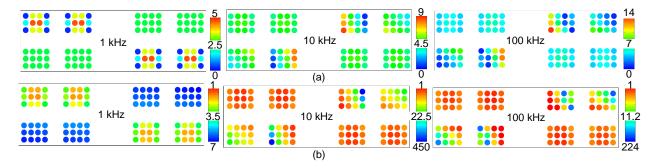

| 48 | AC results: (a) current density distribution (linear scale), (b) relative MTTF values        |

|    | (log scale)                                                                                  |

| 49 | (a) Optimization solution space, (b) three selected layouts, (c) MTTF distribution           |

|    | of three layouts                                                                             |

| 50 | Wire-bonded case: (a) initial layout, (b) balanced solution                                  |

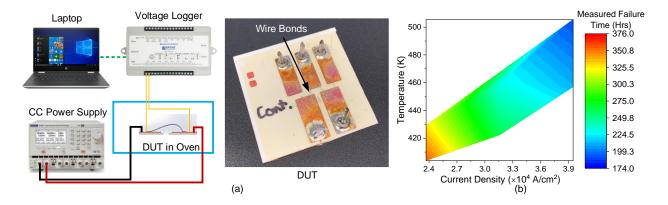

| 51 | (a) Test Vehicle for Establishing EM experimental failure risk in Al wire bonds,             |

|    | (b) Reliability data library based on the experimental results                               |

|    |                                                                                              |

# **List of Tables**

| 1  | Methodology and feature comparison with most recent MCPM layout design au-     |     |

|----|--------------------------------------------------------------------------------|-----|

|    | tomation works                                                                 | 19  |

| 2  | Summary of operating modes                                                     | 30  |

| 3  | Algorithm efficiency comparison between the old and new layout engines         | 33  |

| 4  | Runtime analysis of proposed algorithms, with 3015 layouts generated for opti- |     |

|    | mization                                                                       | 34  |

| 5  | Performance tradeoff of three selected solutions                               | 48  |

| 6  | Comparison between thermal measurement, ANSYS, and PowerSynth                  | 51  |

| 7  | Performance metrics for the three selected layouts                             | 71  |

| 8  | Comparison between thermal measurement, ANSYS, and ParaPower                   | 75  |

| 9  | Summary of high-density packaging designs                                      | 76  |

| 10 | Layer stack properties of the test structure in Figure 38(a)                   | 88  |

| 11 | Runtime and memory comparison between ANSYS, ParaPower, and PowerSynth         |     |

|    | model                                                                          | 89  |

| 12 | Efficiency comparison of current density extraction                            | 97  |

| 13 | MTTF optimization with various solder bump array sizes                         | 103 |

| 14 | Reliability Evaluation of Wire-Bonded 2D Module                                | 105 |

#### Chapter 1

#### Introduction

Power electronics systems and components are an inevitable part of the modern world. Recent advancements in electric automobiles, aircraft, smart grids, and consumer devices all require next-generation power conversion circuits and systems with extremely high density, efficiency, and reliability [1, 2, 3]. The demand for a more-electric world has initiated a call for high-density and reliable power conversion circuits and systems. Designing these converters is a sophisticated multi-physics problem, which requires joint efforts from the users, researchers, and manufacturers of energy conversion systems to solve. Continuous research and development are ongoing to address the challenges associated with the design process and improve the efficiency of the systems. Researchers from both academia and industries are working on the different hierarchies of these power electronic equipment to push the power density higher and higher. Therefore, power electronics designers are trying to cope with a higher complexity resulting from the shortening of product development cycles and increasing use of power electronics with the demand for more tailored solutions [4]. Design automation has been identified as the key to addressing these emerging challenges and adapted by researchers from all the branches such as devices, components, systems, grids, etc. Innovative, automated design tools and methodologies are emerging in all different areas of power electronics society.

#### 1.1 Design Automation in Power Electronics

To optimize different power electronic components and systems, researchers propose design automation methodologies. For example, for effective thermal management solutions, heat sink design and optimization is very crucial. A lot of heat sink design optimization works can be found in the literature [5, 6, 7, 8]. In [8], authors have developed a rapid design optimization tool for liquid-cooled heat sinks based on reduced-order models for the thermal-hydraulic behavior. Their tool-generated solution has reduced the SiC junction-to-coolant thermal resistance by 25% for the

same pressure drop compared to an aggressive state-of-the-art single-phase liquid cooling solution for commercial silicon carbide (SiC) power module. Another significant component of power electronic equipment is the electromagnetic interference (EMI) filter, which design needs to be optimized very carefully to increase the power density of the system. Among several efforts [9, 10, 11] in EMI filter design optimization methodologies, the authors from [11] have developed an automatic design method for EMI filters aiming at volume and weight reduction and satisfying the electromagnetic compatibility standards. They have obtained a reduction of 56%, 67% in weight, and about 46%, 62% in volume in two case studies, respectively. Design automation has been adopted by the power converter designers as well. New design and optimization methodologies can be studied [12, 13, 14, 15, 16] from the literature on different converter topologies. For example, a generic and automated RMS current-oriented optimal design tool is developed in [15] for the LLC resonant converters used in renewable energy applications. This tool-optimized converter has achieved a 2.14% efficiency improvement over the traditional design method.

Researchers have been applying machine learning (ML) and artificial intelligence (AI) algorithms to improve the efficiency of the design cycle in the power electronics domain. These efforts are computer-aided and can achieve significant speedup compared to the traditional design process, thus falling into the design automation track. ML/AI-based techniques are widely used in component-level [17, 18, 19], system-level [20, 21, 22], and grid-level [23, 24] design problems. In [17], three nonlinear machine learning-based models are constructed to automatically estimate the junction temperature of the IGBT module to predict the reliability of the module, which can be used in module layout design automation to accelerate the design cycle. ML-based estimators can be used to reduce the computational expense associated with dc-dc converter characterization in the design and optimization problem of power electronics systems [20]. The authors have shown that system optimization approaches using ML estimators can generate power electronics systems with efficiency and size within 15% of systems are designed using high fidelity but computationally expensive models using test cases. Authors from [23] identified the need for

AI/ML-based prediction techniques for a resilient and reliable power electronics-dominated grid. ML algorithms are widely used in load forecasting, fault detection, and cyber-physical security of the grids.

Based on the aforementioned literature, it is clear that design automation is an emerging area in power electronics that can speedup the design optimization process of the equipment.

Therefore, targeting designers, tool providers including simulation, physical design and design for reliability, manufacturers of test and characterization equipment for high power, high voltage systems, and researchers in universities and research labs working on power electronic design automation. Since MCPMs are the fundamental components of the power converters, design automation methodologies are obvious for optimizing them. This dissertation focus on such methodologies, and the rest of the content is centered around MCPM layout design and optimization.

#### 1.2 Need for Design Automation in MCPM Layout Optimization

The design and packaging evolution of MCPMs are happening by integrating wide bandgap (WBG) devices (e.g., SiC/GaN) and passive components [25, 26, 27]. WBG devices are beneficial for power modules because of their reduced switching time and correspondingly higher switching frequency and lower losses [28]. However, the advantages of SiC devices cannot be utilized fully due to the impact of the parasitic inductance of the module. The inductance in the power loop coupled with the high di/dt of the SiC devices introduces higher voltage overshoot, increased switching losses, and electromagnetic interference and compatibility issue [29]. The switching loss mismatches among different devices on the same switching position would cause the temperature distribution uneven, and ultimately derate the performance and lifetime of the module. Therefore, novel packaging and design techniques are introduced to minimize parasitics, improve cooling, increase power density, and reduce voltage overshoot [30, 31, 32]. These techniques include integrating multiple substrates into a single package, flip-chip wire bondless modules, and packaging heterogeneous components like gate drivers, heat sinks, thermal sensors

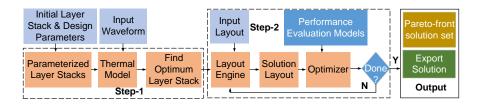

Figure 1: Power module design flow: (a) traditional vs. (b) automated

and switches, decoupling capacitors along with power devices. These advances in the power electronics industry have enabled power conversion design with enhanced efficiency, compact physical structure, and higher reliability [33]. Among different steps of the module design, layout design and optimization are very critical due to the high degree of design freedom and wide range of applications [4].

The current power module design process is a manual, repetitive, tedious task that requires expertise in several tools and software [34, 35]. To come up with a satisfactory solution, the designer requires several iterations of finite element analysis (FEA) to account for changes in the trace orientation, device spacing, etc. Due to the conflicting nature of electrical, thermal, and mechanical aspects of a power module, one trial to improve one aspect affects the other one. Therefore, it generally takes at least four to six iterations in the industry for an expert to come up with a satisfactory design ready for fabrication [4]. There is no standard Computer-Aided Design

(CAD) tool available to verify real-world performance before manufacture. Once the module is fabricated and if the module does not perform according to expectation, a costly redesign is required. This causes a limited solution space and a long development period that is hard to fulfill the cost and time-to-market requirements [36]. It is evident that with the ever-growing complexity of the MCPM layouts, this manual and iterative design process is not capable of generating high-performance designs that are both cost and time-effective. Also, the solution space is often restricted due to limitations in engineering time. Therefore, the traditional, iterative design approach is unable to satisfy the ever-growing demands for optimized power modules with high power density. To reduce engineering time and cost, the industry is looking for electronic design automation (EDA) tools. Though the very large-scale integrated circuit (VLSI) industry has adapted the design automation concept for quite a long time, this concept is relatively new in the power electronics society. Traditional, manual design flow vs. the EDA tool-aided design flow comparison is summarized in Figure 1. A significant speedup can be achieved in the automated design flow as the electro-thermo-mechanical and reliability co-optimization is possible. Moreover, the virtual validation loop ensures the round trip engineering before fabrication, which can save prototyping costs as well. Considering the technology constraints in the manufacturer design kit (MDK) guarantees the manufacturable solution generation. Such benefits can be achieved from an EDA tool that has a scalable, efficient, and generic layout synthesis engine and reduced-order, hardware-validated, accurate models to evaluate electro-thermo-mechanical and reliability performances.

#### 1.3 MCPM Design Variations

To categorize the existing MCPM designs, the number of routing and device layers present in a design is considered. Based on these criteria, the MCPM designs are classified into three types: 2D, 2.5D, and 3D. To clearly define these types of multi-chip power module layouts under this dissertation scope, an illustration is shown in Figure 2. A full-bridge MCPM circuit consisting of two half-bridge circuits is shown in Figure 2(a). A 2D layout refers to a single device layer, as

Figure 2: (a) Full-bridge power module circuit, cross sections of three MCPM structures: (b) 2D half-bridge, (c) 2.5D full-bridge, (d) 3D half-bridge

shown in Figure 2(b). Here, Figure 2(c) represents a 2.5D full-bridge layout, which is defined by multiple device-supporting substrates horizontally connected with additional routing resources. Finally, Figure 2(d) shows a 3D half-bridge module that consists of multiple devices and multiple routing layers stacked vertically. Vias are used for establishing vertical connections across different routing layers. Also, the device's gate and source connections can be performed through metallic posts, which can be treated as vias between two different layers. Due to the 3D stacking, the electrical performance has been improved, but thermal management has become a challenge. Double-sided cooling is one solution for face-to-face stacking of the devices as well as flip-chip devices. However, for face-to-back stacking (shown in Figure 2(d)), it requires at least four layers to form a half-bridge module with double-sided cooling, which increases the fabrication cost and complexity. To reduce fabrication complexity and cost, back-to-back stacking can be performed to create a half-bridge module with embedded heat sink/micro-cooler water channels between two DBCs [37]. Since different layout architectures are possible in 3D configurations, the design tool must handle all these variations.

Figure 3: PowerSynth 2 architecture

#### 1.4 Dissertation Contributions

The core contribution of this dissertation is a constraint-aware, scalable, and efficient layout engine for PowerSynth that can be used in multi-objective optimization for satisfying high power density requirements. There is no commercial tool available that can consider MCPM layout impact on performance optimization and intelligently search the solution space for satisfying the requirements for electro-thermo-mechanical and reliability aspects. Therefore, PowerSynth is the first tool offering all of these features in a complete package. This dissertation has not only addressed the limitations with PowerSynth v1.1 [38] but also introduced some new features in PowerSynth 2. PowerSynth 2 architecture (shown in Figure 3) is a modular and hierarchical one, which is laid out by Dr. Peng. This architecture is more flexible compared to previous versions that can interact with external tools through application programming interfaces (APIs). PowerSynth 2 architecture has a very generic and hierarchical design flow, which can be used for any power electronic component/system layout optimization. Therefore, this is the first proposed architecture in the power electronics design automation area, which design flow is generic enough to be easily applicable for any power electronic component or even system. In this dissertation, this architecture has been used for the MCPM layout optimization case and the contribution areas

have been highlighted in the architecture.

- Layout Representation Technique: An initial layout is required for any design automation tool to perform optimization. Some tools can generate the initial layout combining the circuit netlist and components template library [36], whereas some tools require the initial layout from the user in terms of some abstraction method or detailed description. PowerSynth v1.1 considered symbolic layout method as an abstraction technique, whereas PowerSynth 2 needs the detailed layout information through a text script. Each method has pros and cons. For example, the netlist with a template library can generate different initial layouts based on the templates and find an optimum layout for further optimization. However, this method is limited by the template library as these libraries are not editable by the user. Therefore, the methodology becomes very application-specific. The methodology cannot be extended easily across different component/system layout optimization. The symbolic layout is a user-friendly and simple method for taking the initial layout as input. However, the complex geometry and non-collinear components cannot be represented through this method. PowerSynth 2 requires a hierarchical text script with a layer stack and manufacturer design kit (MDK) to describe the initial layout geometry. This script introduces an object-based layout representation technique, which is generic and scalable enough to represent any component/system. However, the drawback with such script is it cannot overcome any connectivity error introduced by the user while declaring the script. If the script is not representing the circuit netlist, the layout engine cannot detect that, and hence can generate wrong solutions. To consider more generic layout description technique, an embedded scripting environment with power electronics hardware description language is required.

- Layout Generation Methodology: DRC-clean solution generation is a must for an MCPM layout optimization tool. The sequence pair method is used in [39] for layout generation, where the layout is mapped into a 1D binary string for introducing variations in the solution space. However, due to the simplified geometrical representation, lack of interconnection,

and constraint information, the method requires a tedious DRC process and is hence inefficient for handling complex geometries. In PowerSynth v1.1, the matrix-based layout generation methodology does not consider the design constraints in the layout generation phase, which leads to ignoring a lot of solutions due to DRC violation. PowerSynth v1.3 has first introduced the constraint-aware layout generation methodology, which considers the design constraints in the layout generation phase and eliminated the tedious DRC step. This constraint graph methodology has been adapted by [36] as the method has been proven to be efficient. However, their methodology is still limited to 2D layout solution generation only as they did not consider hierarchical evaluation methodology. PowerSynth v1.9 can handle all 2D/2.5D Manhattan geometries by considering hierarchical corner-stitching data structure with constraint graph evaluation technique. Corner-stitching data structure has been proven to be efficient to derive the design constraints easily. PowerSynth 2 layout engine can handle all 2D/2.5D/3D Manhattan layouts. The baseline algorithms from v1.9 have been updated to handle inter-layer connections (i.e., via). The fixed dimension handling algorithms have been generalized to consider all types of edges in a generic way. This methodology has a linear time complexity with the number of components in the layout that makes the methodology scalable. Also, PowerSynth 2 methodology can generate minimum-sized, variable-sized, and fixed-sized solutions, whereas most of the other methodologies are capable of generating only fixed-sized solutions, and [36] can also generate the minimum-sized solution as they are using constraint graph approach inspired by PowerSynth works.

• Improved User Experience: One of the outstanding features that PowerSynth 2 has the user interfaces. Both graphical user interface (GUI) and command-line interface (CLI) are available for the user's flexibility. The other methodologies in literature did not clearly disclose their user interfacing method. The initial layout geometry description script is updated to make it more user-friendly. With help from Joshua (a formar REU student), an interactive GUI has been developed for PowerSynth 2. The command line interface for

PowerSynth v1.9 and v2.0 has been developed with help from my colleague Quang Le.

- Reliability Modeling Efforts: Electrical and thermal performance optimization is necessary for safe operation of SiC MCPM modules at high switching frequency. So, all of the other research groups have tried to develop electrical and thermal models. However, no one considered layout impact on other reliability metrics like transient thermal performance, electromigration associated risk assessment, partial discharge, performance at high-voltage-current, etc. Besides electro-thermal performance models, reliability modeling efforts are initiated in PowerSynth 2. A transient thermal model has been developed for 2D layouts that can predict both static and transient thermal performance with about 3500 times speedup while keeping the accuracy within 10% compared to ANSYS Fluent. Also, an electromigration-aware reliability model is proposed in [40] to assess the risk of different interconnects and optimize accordingly. The new layout engine has been enabled PowerSynth 2 to handle both wire bonds and solder bumps, whereas the other tools can handle only wire-bonded layouts. Therefore, such reliability modeling study is possible with PowerSynth 2.

- Optimization Algorithms: Optimization algorithm is one of the key parts of the CAD flow. The other works from the literature have considered only genetic algorithm (NSGAII [41]) as the optimization algorithm candidate. Though NSGAII can converge faster, it has certain limitations: Many generations are required before convergence; the distribution of the weights to the objectives is complicated; generated solutions are not guaranteed to be globally optimum; solution space is not large enough. Therefore, PowerSynth 2 has an exhaustive search option (Randomization) for optimization alongside the NSGAII option. Though off the shelf NSGAII python package has been used, the design string formulation and modification algorithm has been developed and generalized for PowerSynth 2 layout engine to consider 2D/2.5D/3D MCPM layouts.

- Hardware-Validation of CAD Flows: The generic CAD flow for 2D/2.5D/3D MCPM

layout optimization has been validated with brand-new 2D/2.5D design and 3D design cases. For both cases, the initial module layout is optimized for electrical and thermal performance. An optimized solution for both cases has been fabricated and tested for result comparison. In 2D/2.5D case, PowerSynth prediction is within 10% for both electrical and thermal, whereas for 3D case, those are within 13%, and 10%, respectively. Though the other tools have also verified their optimized designs with hardware prototype, efficiency and capability wise PowerSynth 2 is way ahead of them. For example, the hardware-validated 2D module can be found within 1288 s by iterating for 100 generations of NSGAII in PowerSynth 2, whereas the the methodology in [36] took almost 5,400 s for 30 generations, and [42] took 266,343 s for 10 generations of NSGAII. Performance-wise all the solutions are comparable, as PowerSynth 2, [36], and [42] has achieved 8.33, 5.59, and 7.44 nH of power loop inductance. The layout from [36] has a lower loop inductance as that layout has two parallel power loops, whereas the others have a single loop.

#### 1.5 Contributions from Other Team Members

Apart from the highlighted parts in the PowerSynth 2 architecture, other components are required to complete the design flow. My colleagues are working on those parts. A brief summary of their efforts is summarized below.

• My colleague Quang Le has helped me with the electrical modeling efforts, user interfacing, external APIs development, and hardware-validation of the CAD-flows. He has built the interfaces for all of the electrical performance evaluations. In the case of 2.5D MCPM hardware validation, the PEEC model [43] is developed by Quang. Also, the netlist extraction methodology that is used in [44] is solely developed by Quang. Thanks to his enormous contribution to PowerSynth 2 code base that has made my layout engine results get validated. Besides, his contribution toward the solution export, database maintain features have played an important role in this dissertation. The electrical performance validation work for the 3D module would not be possible without him.

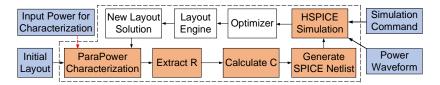

- Another colleague Tristan Evans has been working on ParaPower interfacing, EMI

modeling, electro-thermo-meachanical co-optimization study, and layout synthesis from

input netlist. Among his several contributions the ParaPower integration effort has made it

possible to evaluate the 3D MCPM design [45]. Also, he has helped in many ways to

validate the thermal performance of both 2.5D and 3D modules.

- Another team member, Shilpi Mukherjee has been working on partial discharge (PD) modeling and post-layout optimization feature like filleting the sharp corner to minimize the current crowding and field focusing. She has helped a lot to test the high-voltage-current dependent reliability constraints implementation as those constraints are obvious at high power operation and reduce partial discharge threats.

- Last but not the least, Joshua Mitchener (former REU student) has helped to put together the GUI for PowerSynth 2. His works are summarized in [46].

Therefore, it is clear that without the other team members' enormous support and contributions this dissertation would not be possible. Finally, combining all the team efforts, we have been able to release binary packages for different versions of PowerSynth. All of these packages can be found in [47].

#### 1.6 Dissertation Outline

Since this dissertation includes the updates after the PowerSynth v1.1 release, the goal of this dissertation is to present the background, methodology, and results starting from PowerSynth v1.3 to v2.0. The dissertation outline is as follows.

- Chapter 2 represents a detailed literature review of design automation efforts in MCPM layout synthesis and optimization area. PowerSynth v1.1 research and development history is also summarized in this chapter.

- Chapter 3 contains the motivations behind this dissertation. Also, the progression flow

from PowerSynth v1.1 to v2.0 is summarized in this section along with the preliminary research works that laid the foundation of PowerSynth 2.

- Chapter 4 describes the MCPM layout optimization flow and validation results for PowerSynth v1.9, which is released for handling 2D/2.5D MCPM layouts. The methodology, key results, and limitations of v1.9 are stated in this chapter.

- **Chapter 5** includes the PowerSynth 2 architecture description including the updated methodology, results, and limitations.

- **Chapter 6** represents the reliability optimization efforts using PowrSynth updates in layout generation and modeling efforts. Both thermal and electromigration-aware reliability optimization methodology and results are presented.

- **Chapter 7** concludes the dissertation with some potential future works.

#### Chapter 2

#### **Literature Review**

Realizing the importance of an EDA tool for MCPM design and optimization, several research groups have been working on this topic. Since both analog/mixed-signal and power electronics design processes are manual and iterative, researchers from both societies have been adapting the design automation methodologies from VLSI as the EDA tools for digital IC design are highly matured compared to the others [48]. The similarity between VLSI and analog CAD flow has led a large group of researchers towards developing different CAD tools for analog/mixed-signal layout design automation to address critical challenges like handling device parameterization, constraint generation, maintaining symmetrical placement and routing, etc. [48, 49, 50, 51]. Unlike analog and digital CAD flow, Power-CAD [52] requires simultaneous analysis of thermal, electrical, and mechanical parameters to design an optimal layout. As such, recently, design automation tools with multi-objective optimization have been investigated by the power electronics society to explore a large variety of designs, reduce cost and computational effort, and alleviate design complexity. A brief literature review on MCPM layout synthesis and co-optimization (Step 3 in Figure 1(b)) efforts are described below.

#### 2.1 MCPM Physical Design Automation and Optimization Efforts

#### 2.1.1 Existing Works Outside PowerSynth Scope

In [53], the authors proposed an automatic layout generation method to consider a legitimate trade-off between electromagnetic compatibility (EMC) and thermal constraints. A simplified EMC and a thermal model are applied individually to generate a "Thermal-EMC" plane with Pareto-front solutions. Though the proposed method may determine a theoretical optimum solution for a given technology, it is hindered by limited solution space and design rule violations.

In [54], a sequentially coupled approach is proposed for optimizing power module layouts by integrating a few FEA modeling tools (e.g., ANSYS). These tools are coupled in a

multidisciplinary design optimization (MDO) framework to interact with each other while generating solution layouts. Though the methodology has been proven superior to the traditional manual design flow, some limitations like the time-consuming finite element method (FEM) for electro-thermal evaluation, few design variables in the solutions, and a single variable in each iteration of the optimization make this methodology infeasible for 2.5D/3D layout optimization.

Another research also adapted the placement and routing concept from the VLSI design automation area and implemented it in power electronics design automation [39]. The components like die, wire bonds, and connected traces are merged into a single rectangle to simplify the problem. Relative position, component orientation, and the gap among components are translated into a binary string, which is manipulated in the optimization phase to generate new solutions. Two-folded optimization is performed by a genetic algorithm, where the outer loop aims at placement optimization via the sequence pair method [55], and the inner loop focuses on routing. The optimization cost function involves only footprint area and electrical parasitics, which arises concern about the thermal reliability of the solutions. Also, simplified representation saves computation time by sacrificing accuracy in calculating parasitics. Though the methodology has been extended to 3D layout optimization [56], no hardware validation has been presented even with a simplified technology.

In [42], researchers have developed a genetic algorithm-based multi-objective electro-thermal optimization framework, where only the device placement varies with a fixed routing of the traces. FEM tools are used for electro-thermal performance evaluation. Though the proposed methodology can optimize the device placement, the trace routing impact is not considered, resulting in a smaller solution space. Moreover, the time-consuming FEM solver is infeasible for rapid design space exploration of the high-density and heterogeneous layouts.

Authors from [36] developed an MCPM layout optimization method that uses a graph model to describe heterogeneous layouts with all interconnectivity and design constraints. Integer programming is introduced to generate layout templates with variable geometric topologies from the initial graph model. An in-house discrete extractor is used for evaluating loop and branch

inductance, and thermal resistance. This extractor is leveraged to achieve the Pareto-front from the genetic algorithm providing a tradeoff boundary for loop inductance and branch mismatch. This methodology does not require a complete initial input layout from the user as it generates the initial layout based on the user's choice from the template library. However, the methodology is very application-specific with a limited number of components handling capability. The integer programming method is not scalable as with the number of increasing components, the runtime exponentially increases and it may face convergence issues in some cases. Moreover, the proposed methodology is applied and verified through a 2D design. Any 2.5D/3D module is not optimized and verified with the methodology.

#### 2.1.2 Preliminary Research and Development Efforts on PowerSynth

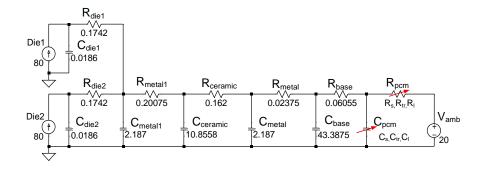

The initial work in [52] has introduced a simultaneous electro-thermal optimization methodology named "Power-CAD" for design, analysis, and optimization of a discrete power module. Power-CAD has been proven to be both cost and time-effective for the power module design industry by significantly reducing the number of design cycles. However, this methodology treats the maximum temperature in the module as a constraint without considering the trade-off between electrical parasitics and temperature. Realizing the significance of considering the balance between electrical and thermal performance, the foundation of PowerSynth is established in [57]. The very early version of the tool provides a flexible framework for synthesizing not only half-bridge MCPMs but any circuit topology, and able to generate a set of optimal trade-off MCPM designs considering any number of thermal or electrical performance criteria. The reduced-order electrical and thermal models used in this version are built based on the study from [58]. The models require an initial layout design and a layer stack to start with. Then, a thermal behavior extraction tool like ANSYS Workbench is used to create the lumped thermal model. An electrical parasitic extraction tool like Ansoft Q3D Extractor, is used to create a lumped electrical parasitic model. The limped thermal model is a Cauer thermal network, which allows 1D heat dissipation and requires characterization by FEM tool. The electrical model

considers the MCPM structure as a micro-strip structure and uses staight-forward micro-strip equations for parasitic modeling. However, the assumptions like infinite ground plane and very thin, large traces are not valid for accurate modeling effort and results in mismatches with FEM results. Including these efforts, an internal release of PowerSynth v1.0 is done in 2015. After a few more years of research and development effort, a complete EDA tool "PowerSynth" for MCPM layout optimization was presented in [38]. Since ANSYS tools require licensing, the characterization for thermal modeling is done by open source GMesh [59] and Elmer [60] tools in this version. To address the limitations with micro-strip method, a response surface-based method [29] is used for electrical parasitic modeling. Both of these models are hardware-validated in [38]. PowerSynth v1.1 release is performed in 2019 integrating these fast, accurate, hardware-validated electrical, and thermal models for MCPMs within a multi-objective optimization framework. PowerSynth v1.1 uses a symbolic layout for layout abstraction, which consists of lines and points representing traces, devices or lead connections with normalized coordinates. Then, each trace or component is stamped into a matrix representation to effectively update the trace dimension and component locations during the optimization process. It has a built-in technology library to account for a wide range of materials and design rules from the manufacturer. Another important capability is the back-annotation of layout-extracted parasitics to the original circuit schematic, which enables round-trip engineering before fabrication. Also, exporting 3D models to several commercial FEA tools are another must-have feature for detailed analysis. However, this layout generation method does not consider any design constraints during the layout generation phase. Therefore, once a layout is generated, it has to go through an iterative DRC checking process. In some complicated layout cases more than 90% layout solutions are discarded due to DRC failures. Also, this DRC step could be time-consuming on complicated 2D/2.5D/3D layouts with many heterogeneous components and limits geometric configurations due to many built-in assumptions. This dissertation is based on further research and development efforts of PowerSynth. Therefore, rest of the works are described in the following chapters.

A brief summary of comparison with this dissertation methodology and other most recent

MCPM layout optimization methodologies is provided in Table 1.

#### 2.2 Power Modules' Reliability Optimization Efforts

The most dominating challenges for high-density modules are from the reliability perspective due to their highly inhomogeneous structures. The prominent cause of the failures like solder joint fatigue, wire bond fatigue, and isolation substrate delamination is thermal cycling [61]. Another reason behind most of the interconnect failures, especially at high-current density is electromigration (EM) [62]. Since different materials with different coefficients of thermal expansion (CTE) are used in an MCPM, CTE mismatch of the components leads to induced thermal stresses within the module that causes mechanical failures [63]. To reduce the failure rate and increase the reliable operation period of the modules, reliability optimization before fabricating a module is obvious. From the literature, two types of reliability optimization approaches can be found: a) Optimization aiming at specific failures [61, 63, 64], b) Optimizing thermal management aiming at reducing thermal cycling effects [65, 66, 67].

In the first approach, researchers have focused on a part (i.e., wire bond, solder joints, substrate) of the module rather than the module as a whole. Since this approach has a limited scope, physics-based modeling and finite element analysis produced helpful results for predicting failure and lifetime. Among different failure mechanisms, EM is one of the prevalent ones, especially at high-current density. EM is a material migration based on the flow of current through it, which is a diffusion-controlled process. Though high current density drives the migration process, high temperature also plays an important role in increasing the diffusion rate. Therefore, the combination of high current density and high temperature in the interconnect/solder material can cause very severe EM-induced failures that can affect the long-term reliability of the component. In the second approach, researchers have focused on the reliability of the module as a whole and tried to reduce thermal cycling effects by changing materials in the layer stack. In this approach, thermal management using phase change materials (PCM) have been found as a prevalent solution for reliability enhancement. For both of these

In-house & External models Exhaustive (Randomization) Wire bond, solder bump, Evolution (NSGA II) & Placement & routing Corner stitching & Constraint graph PowerSynth 2 (Dissertation) Available [47] 2D/2.5D/3D Not required Considered Considered Actual Yes Table 1: Methodology and feature comparison with most recent MCPM layout design automation works Integer linear programming & Block graph model Placement & routing Evolution (NSGA II) Zhou et. al. (2022) In-house models Not considered Not considered Not Required Not available Not required Wire bond  $^{\circ}$ Evolution (NSGA II) Shuhei et. al. (2021) Die placement only Parameter sweep Not considered Not considered Not available Not required Wire bond Actual FEA No 2DPuqi Ning et. al. (2017) Placement & routing Evolution (GA) Not considered Not considered Discrete model Sequence pair Not available Wire bond Simplified Required Yes Interconnection technology Layout generation method Hierarchical optimization Reliability optimization Optimization algorithm Performance modeling Methodology Features Optimization goal Release packages DRC checking Layout types Initial layout Scalability

approaches, the existing researches are based on FEA-based modeling and optimization.

#### 2.2.1 Thermal Cycling Impact Minimization Efforts

In [63], authors have developed an optimization methodology that uses a mathematical function relating system response to design parameters. This process parameterizes the design variables within a permissible range that uses commercially available optimization packages to generate new solutions, simulated using the finite element method (FEM) tools. The design-for-reliability tool concept has been presented in [61] that has built-in reduced-order stress prediction models with numerical optimization. While optimizing a module, it can consider uncertainty data from material properties and manufacturing processes using a Monte Carlo method that provides a stochastic approach to reliability predictions.

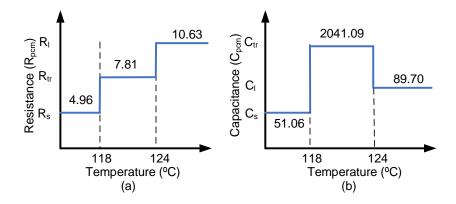

Authors from [68] have proposed a design automation and optimization methodology based on FEM simulation to optimize the layer stack of a double-sided cooling power module. Several research groups have identified PCMs as an effective ingredient of the power module layer stack that acts as buffers against the intermittent temperature spikes from thermal cycling. In [67], authors have used PCM to reduce the peak temperature of the module under thermal cycling. In [66], authors have shown that PCM can be modeled as a voltage-controlled variable RC-network and verified the benefits of using PCM over encapsulant using such a network model.

#### 2.2.2 Electromigration Impact Minimization Efforts

In [69], authors have studied the combined effect of high current and high temperature on Ag, Cu, and Au wire bonds through experiments. Authors of [70] performed an electrical-thermal-mechanical coupled analysis of electromigration in a bonding wire of a power module. A test method is developed for studying the current effect on the aging process of a wire-bonded Silicon Carbide (SiC) MOSFET module under a power cycling test in [71]. The experimental and analysis results showed that different current densities have different impacts on both the bond wire resistance and die-attach solder layer. This methodology is also an

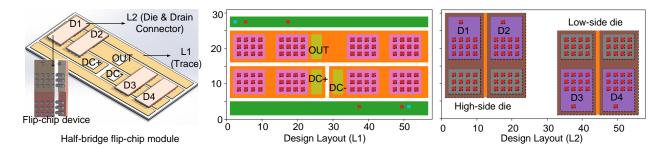

experimental case study whose results can be used in validating the modeling effort for EM risk assessment. In [72], authors have tried to optimize the packaging structure of a flip-chip device by studying a few variations in solder material, solder bump diameter as well as pitch, and the drain connector geometry. All these variations are manually designed by the authors, and the module layout variation impact has not been studied. Therefore, the solution space is limited. Authors have studied a few solder bump distribution orientations in [73] to optimize the electromigration reliability by applying a more balanced current distribution among solder bumps. This trial is also a manual one and is limited by the designer's choice.

From the literature review, it is clear that there is no software tool exists that is scalable, efficient, and generic enough to perform electro-thermo-mechanical and reliability optimization on 2D/2.5D/3D MCPM designs. Most of the layout optimization methodologies are limited to 2D modules and cannot perform any reliability optimization. Design for reliability optimization toolbox for power electronic system has been introduced in [30], which is suitable for system-level reliability assessment. Therefore, no existing tool can perform reliability optimization accounting for thermal cycling and electromigration on power modules.

#### Chapter 3

#### **Motivations and PowerSynth Progression Flow**

#### 3.1 Motivations

PowerSynth is the first tool that focuses on MCPM layout optimization. Though PowerSynth v1.1 has shown the complete optimization flow for simple 2D layouts as a proof of concept, there is room for improvements in the methodology associated with the layout optimization flow. The critical items include:

- Layout Representation Technique: Symbolic layout representation using lines and points is unable to represent the 2.5D/3D layouts, even some complex 2D layouts. The method restricts the wire bonding and trace routing orientation, and unable to handle multiple non-collinear components.

- Layout Generation Methodology: The matrix-based layout generation methodology has limited types of geometry handling capability. While generating solutions, it requires design rule checking (DRC) for each solution, which makes the methodology inefficient for a broader range of geometry handling.

- Layout Engine Efficiency: The layout engine generated solutions are not always DRC-clean, which shows a variable efficiency with a varying number of devices in the same layout. For example, in a half-bridge module, the number of parallel devices is varied from 4 to 12 with an increment of 2. For each case, total of 15,015 solutions are generated and among all cases, it generates a maximum of 20.47% DRC-clean solutions [74].

- Reliability Modeling: Since PowerSynth v1.1 cannot consider arbitrary layer stack and does not equipped with any transient thermal model, it cannot optimize layouts accounting for thermal cycling. The reduced-order, compact thermal model is not capable of capturing detailed temperature distribution that makes the tool incapable of assessing EM-associated

risk. Besides, the matrix-based layout generation methodology cannot handle user-defined/reliability constraints.

• Optimization Framework: A non-dominated sorting genetic algorithm (NSGA-II) [41] has been used for optimization since the matrix-based methodology is not compatible with some other optimization algorithms. Though NSGA-II can converge faster, it has certain limitations: Many generations are required before convergence; The distribution of the weights to the objectives is complicated; Generated solutions are not guaranteed to be globally optimum; Solution space is not large enough. These limitations initiated a study toward assessing the viability of other optimization algorithms. Also, for heterogeneous power module layouts, the layout complexity and number of design variables grow exponentially, which makes it difficult due to dependency between variables.

To address these limitations, a more generic, efficient, and scalable layout optimization methodology is required. Therefore, research and development have been carried out to improve PowerSynth from time to time. A brief description of the progression flow is described below.

## 3.2 PowerSynth Progression Flow

PowerSynth progression flow is shown in Figure 4. A brief feature comparison among different versions from v1.1 to PowerSynth 2 has been described in this section. Released packages of these versions can be found in the PowerSynth release webpage [47].

• PowerSynth v1.1: This version has the following key features: (1) Simple 2D layout geometry handling capability; (2) Symbolic layout representation; (3) Matrix-based layout engine; (4) Iterative DRC-checking; (5) A user-extensible technology library and manufacturer design kit (MDK); (6) Reduced-order electrical and thermal model validated against both FEA simulation and experimental measurements; (7) Back annotation of layout-extracted parasitics to the original circuit schematic; (8) Export of 3D structure of the 2D MCPM layouts to several commercial FEA tools for further analysis.

Figure 4: PowerSynth package release flow with GUI

• PowerSynth v1.3/1.4: A constraint-aware, flat-level layout engine has been introduced in v1.3. This new layout engine requires a text script-based input to represent the initial layout. Such input script enables to describe 2D layouts with complex geometry. With the updated layout representation technique, the layout engine can handle arbitrary types of components including heterogeneous passive elements. Besides, the new layout engine has enabled studying multiple optimization techniques like stochastic approach, gradient-based, and evolutionary approach. In v1.3, the new layout engine has been launched as an alternative option for the user to generate layout solutions and the optimizer is still dependent on the symbolic layout-based input, and the electrical and thermal models are also the same as in v1.1.

In v1.4, the Army Research Lab (ARL) developed ParaPower [75] tool has been interfaced with PowerSynth v1.3 for leveraging their thermal and stress evaluation capability.

Therefore, in this version, the user has an additional thermal model compared to v1.3. Since ParaPower uses a 3D matrix-based representation of the module structure, it has better accuracy and coverage of layout geometries compared to the built-in 1D thermal model with a small runtime overhead. PowerSynth has a very similar graphical user interface for

- v1.1 to v1.4 except the **Constraint-Aware Layout Engine** button.

- PowerSynth v1.9: The major updates on PowerSynth research and development have been released in this version. The flat-level constraint-aware layout engine has been updated to a hierarchical one to leverage the hierarchical optimization benefits. Hierarchy has been considered in the layout geometry description script as well to replicate the real-world scenario. With these major updates, this version is capable of handling all 2D/2.5D Manhattan geometries and can generate a larger solution space compared to the previous versions. This new flow has been hardware-validated with a real-world 2.5D full-bridge module. The electrical model has been updated from the response surface technique to the partial element equivalent circuit (PEEC) method. This version has a command-line interface to ensure linux compatibility. Since significant updates have been performed on the underlying algorithms, details have been described in Chapter 4.

- PowerSynth v2.0: A completely new modular architecture has been implemented in this version. The modular architecture allows the integration of modeling techniques from other research groups and external tools through application programming interfaces (APIs). The algorithms have been updated to consider both intra-layer and inter-layer interconnects (wire bonds and vias). This version can handle high-density 2D/2.5D/3D MCPM layouts and state-of-the-art (SOTA) packaging technologies. A completely new code base has been developed that has both command-line and graphical user interfaces. The latest version has enabled reliability optimization alongside the basic electro-thermal optimization.

PowerSynth 2 CAD flow has been hardware-validated with a novel 3D MCPM module design. Detail algorithms and modeling updates with the hardware-validation results for this version have been described in Chapter 5.

Before diving deep into the PowerSynth v1.9 and 2 updates, some preliminary concepts and topics are discussed in the following to better understand the algorithms and CAD flows. These concepts include the flat-level layout engine implementation and results, which are the backbone

of the hierarchical layout engine introduced in v1.9 and extended in v2.0.

## 3.3 Preliminary Research

Due to inefficiency and restrictions with the matrix-based methodology, to transform the layout engine into constraint-aware, the corner stitching data structure and constraint graph evaluation methodology have been considered.

**Data Structure:** The corner stitching data structure and the constraint graph evaluation technique have been adapted from VLSI and customized for power modules. A brief overview of the basic corner stitch and constraint graph is introduced here.

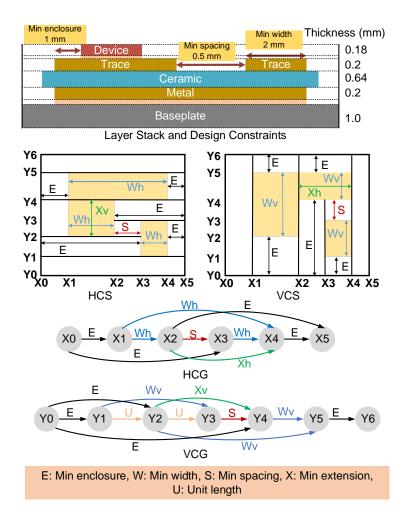

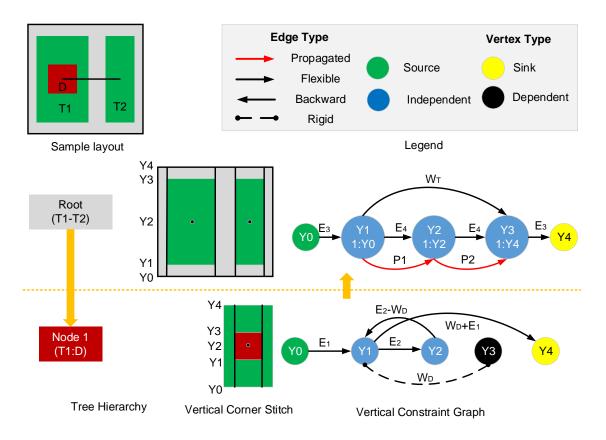

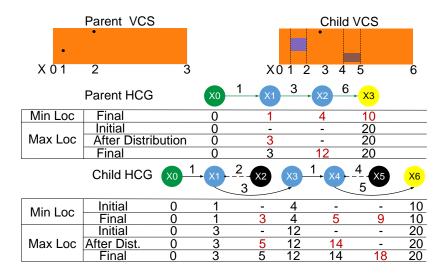

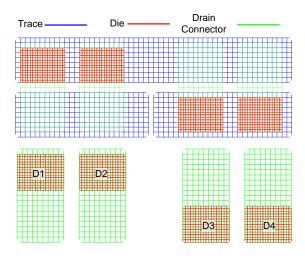

The basic corner stitch data structure was introduced by John Ousterhout [76] and widely used in VLSI CAD tools. In this data structure, there are two types of non-overlapping rectangular tiles: solid and empty. Four pointers are used in each tile to traverse the layout area efficiently. The planar corner stitch has two orientation types: horizontal corner stitch (HCS) and vertical corner stitch (VCS). The basic rules for creating HCS (and VCS) are: (1) Each tile must be as wide (tall) as possible; (2) After satisfying rule (1), each tile must be as tall (wide) as possible. Due to the linear time complexity of associated algorithms (e.g., insert, merge, search) to create corner stitch data structure and the convenience of obtaining necessary design constraints, this data structure has been extended to represent power module layouts in PowerSynth. Horizontal and vertical corner stitch planes of a sample layout are shown in Figure 5.

A constraint graph is a computation technique for a set of inequalities. In this graph, if a vertex A should always maintain a minimum distance of W from another vertex B, then the relationship between A and B can be expressed as:

$$B - A \ge W \tag{1}$$

Here, A is the source, and B is the sink. To maintain the minimum design constraints among all components, two types of constraint graphs (CGs) are created: horizontal (HCG) and vertical

(VCG). HCG maintains the relative location among components horizontally, and VCG vertically. For each corner-stitched plane, two constraint graphs are used to maintain the constraints, where coordinates are mapped into vertices, and the constraints are mapped into edges. Sample HCG and VCG are shown in Fig 5.

Customization for Power Modules: Though the basic corner stitch data structure has only two types of tile, in the case of the power module, each component is represented as a tile of an individual type. Therefore, heterogeneous components can be easily represented and the number of components is not bounded, which ensures the scalability of the methodology. Also, the basic version does not allow overlapping tiles. However, overlapping is a must for proper representation of the layout structure of the power module, because devices (such as power FETs and diodes) are normally placed on top of traces. Therefore, the basic tile insertion function has been modified to allow overlapping of tiles.

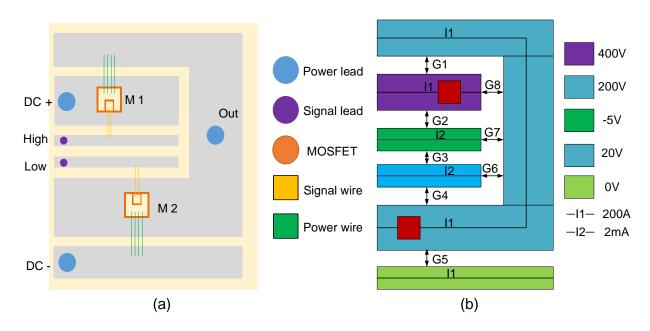

Incorporated Constraints: For power module design, two types of constraints are considered: design constraints and reliability constraints. Design constraints are minimum constraints imposed by the technology, to ensure the proper fabrication of the module. Reliability constraints are considered to address issues related to high voltage and current such as partial discharge and thermal.

- **i. Design Constraints:** The following design constraints are considered to have DRC-clean layouts. An illustration of the constraints is shown in Figure 5.

- Minimum Width: Minimum width is associated with each component in the power module. Some components can have a different minimum width along the x and y-axis. All horizontal widths are taken from horizontal corner stitch and vertical widths are taken from vertical corner stitch.

- Minimum Spacing: Minimum spacing value is considered between two components. When

there are multiple components in between the same vertices maximum value determines the

spacing to ensure DRC validity. All horizontal spacing and vertical spacing are taken from

horizontal corner stitch, and vertical corner stitch, respectively.

Figure 5: Layer stack and design constraints illustration, corner-stitched planes (HCS/VCS) and corresponding constraint graphs (HCG/VCG)

- Minimum Enclosure: To ensure proper connectivity, some components are required to be surrounded by some other components underneath, with a spacing known as minimum enclosure. For example, when a device is placed on top of a trace, there should be a minimum enclosure of the trace to the device.

- Minimum Extension: In some cases, there may be L-shaped or T-shaped components,

where one leg extends in the direction perpendicular to the components routing direction.

For those cases, the minimum extension rule appears. Horizontal extensions can be found

from the vertical corner stitch, whereas vertical extensions can be found from the horizontal