FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

## eduARM: Web platform to support the teaching and learning of the ARM architecture

Maria Inês Fernandes Alves

Mestrado em Engenharia Informática e Computação

Supervisor: António Duarte Araújo Second Supervisor: Bruno Lima

October 12, 2022

© Maria Inês Fernandes Alves, 2022

# eduARM: Web platform to support the teaching and learning of the ARM architecture

Maria Inês Fernandes Alves

Mestrado em Engenharia Informática e Computação

Approved in oral examination by the committee:

Chair: Prof. João Bispo External Examiner: Prof. Manuel Gericota Supervisor: Prof. António Duarte Araújo

October 12, 2022

## Abstract

Computer architecture is a prevalent topic of study in informatics and electrical engineering courses, though students' overall grasp of the concepts present in this subject is many times hampered, mainly due to the lack of educational tools that can intuitively represent the internal behaviour of a CPU. This already posed a problem in the teaching of the most commonly used processors in academic settings, and with the ever-growing evolution of the ARM architecture and its adoption in higher education institutions, the demand for this sort of tools has increased. Although a few works dedicated to this domain already exist, none dedicated to the ARM architecture and capable of effectively responding to this problem have been found. Nevertheless, certain tools contain valuable features which could present a good starting point for the platform to develop.

Taking this into account, this thesis aims to contribute towards solving this problem with the development of a practical and interactive web platform that simulates how a CPU functions, tailored specifically for the ARMv8 architecture. Since this tool's main purpose is to aid computer architecture students, contributing to an improvement in their learning experience, the platform must be modular and highly interactive, comprising varied concepts of computer architecture and organization in a simple and intuitive manner, such as showcasing the internal structure of a CPU, in both its unicycle and pipelined versions, and the effects of executing a set of instructions. This solution is thus a source of innovation, as educational tools for computer architecture, specifically the ARMv8 processor, are scarce and inadequate for what is necessary in an academic context.

Since this platform should encourage learning computer architecture through interactive experimentation, the developed solution is to be validated with a case study, along with the participation of students of the informatics and electrical engineering courses, which constitute the target group of this project.

Keywords: computer architecture teaching, ARM, simulation, learning resources

## Resumo

Arquitetura de computadores é um tópico de estudo predominante nos cursos de Engenharia Informática e Eletrotécnica, embora a compreensão global dos conceitos presentes nesta unidade curricular seja muitas vezes dificultada, principalmente devido à falta de ferramentas educativas que possam representar intuitivamente o comportamento interno de um CPU. Este problema já se verificava no ensino dos processadores mais utilizados em ambientes académicos, e com a rápida evolução da arquitetura ARM e a sua adoção em diversas instituições do Ensino Superior, a procura por este tipo de ferramentas tem aumentado. Embora existam alguns trabalhos dedicados a este domínio, nenhum foi encontrado que fosse dedicado à arquitetura ARM e capaz de responder de forma eficiente ao problema. Apesar disto, certas ferramentas contêm funcionalidades vantajosas que podem ser um bom ponto de partida para o desenvolvimento da plataforma.

Tendo isto em conta, esta dissertação visa contribuir para a resolução deste problema através do desenvolvimento de uma plataforma web prática e interativa capaz de simular o funcionamento de um CPU, adaptada especificamente para a arquitetura ARMv8. Uma vez que o principal objetivo desta ferramenta é ajudar os estudantes de arquitetura de computadores, contribuindo para uma melhor experiência de aprendizagem, a plataforma deve ser modular e interativa, abordando vários conceitos de arquitetura e organização de computadores de uma forma simples e intuitiva, tais como mostrar a estrutura interna de um CPU, tanto nas suas versões uniciclo e pipeline, como mostrar os efeitos da execução de um conjunto de instruções. Esta solução assume-se assim como uma fonte de inovação, uma vez que as ferramentas educacionais dedicadas a arquitetura de computadores, especificamente para o processador ARMv8, são escassas e inadequadas para o que é necessário num contexto académico.

Uma vez que esta plataforma deve encorajar a aprendizagem de arquitetura de computadores através de experimentação interativa, a solução desenvolvida deve ser validada com um caso de estudo, contando com a participação de estudantes dos cursos de Engenharia Informática e Eletrotécnica, que constituem o público-alvo deste projeto.

Palavras-chave: ensino de arquitetura de computadores, ARM, simulação, recursos de aprendizagem

## Acknowledgements

Gostaria de agradecer, antes de mais, ao meu orientador, o Professor António Duarte Araújo, e ao meu co-orientador, o Professor Bruno Lima, por me darem a oportunidade de desenvolver este trabalho, e por me terem acompanhado ao longo deste ano no desenvolvimento deste projeto, tendo sempre disponibilidade para me ajudar.

Queria agradecer, também, à minha família, especialmente aos meus pais, irmã e avó, por terem estado do meu lado ao longo destes anos, por sempre me motivarem e acreditarem nas minhas capacidades. Espero que me ver a concluir o curso vos traga um pouco de orgulho.

Daniela, obrigada especialmente a ti, por aturares os texugos que te mando constantemente como resposta, e pelas fotos dos (lindos!) gatos que foram a origem de grande parte da minha motivação. Obrigada também ao Miguel, rei do tech support.

Ao Francisco, com quem já é mais de uma década juntos, obrigada por todos estes anos, por me aturares desde a escola até aqui, e mal posso esperar para seres tu deste lado. Desculpa a minha ausência estes últimos meses, que mais pareceram anos.

João, juntos desde o primeiro dia, tenho muito orgulho do que conseguimos fazer. Adoro-te sempre.

Márcia, és um exemplo de esforço e dedicação, tenho imenso orgulho em ti, e quero que me tragas um bacalhau.

Henrique, sabes que sem ti isto não era possível. Já tinha ficado maluca. Adoro-te, e obrigada por tudo, mesmo.

A todos os restantes membros do SCTP, Bruno, Campos, Nunito, Pedrito, Vitor, obrigada por estes cinco anos, e que venham muitos mais.

Inês

"Have no fear of perfection - you'll never reach it."

Salvador Dalí

## Contents

| 1 | Intr | oduction 1                                                                                                |

|---|------|-----------------------------------------------------------------------------------------------------------|

|   | 1.1  | Context and Motivation                                                                                    |

|   | 1.2  | Goals 2                                                                                                   |

|   | 1.3  | Document Structure   2                                                                                    |

| 2 | Stat | e of the Art 3                                                                                            |

|   | 2.1  | Background                                                                                                |

|   |      | 2.1.1 Unicycle                                                                                            |

|   |      | 2.1.2 Pipeline                                                                                            |

|   | 2.2  | MIPS                                                                                                      |

|   |      | 2.2.1 SPIM                                                                                                |

|   |      | 2.2.2 WebMIPS                                                                                             |

|   |      | 2.2.3 MARS                                                                                                |

|   |      | 2.2.4 DrMIPS                                                                                              |

|   | 2.3  | RISC-V                                                                                                    |

|   |      | 2.3.1 RARS                                                                                                |

|   |      | 2.3.2 BRISC-V Simulator                                                                                   |

|   |      | 2.3.3 BRISC-V Explorer                                                                                    |

|   | 2.4  | ARM 13                                                                                                    |

|   |      | 2.4.1 VisUAL                                                                                              |

|   |      | 2.4.2 Graphical Micro-Architecture Simulator                                                              |

|   | 2.5  | Support for multiple architectures                                                                        |

|   |      | 2.5.1 WepSIM                                                                                              |

|   |      | 2.5.2 CREATOR                                                                                             |

|   | 2.6  | Discussion                                                                                                |

|   | 2.7  | Concluding Remarks                                                                                        |

| 3 | Met  | hodology 20                                                                                               |

| • | 3.1  | Requirements Specification                                                                                |

|   | 3.2  | Development Process                                                                                       |

|   | 5.2  | 3.2.1         Backend development         21                                                              |

|   |      | 3.2.2       Frontend development       21                                                                 |

|   |      | 3.2.2       Adding a pipeline CPU version       22                                                        |

|   |      | 3.2.4       Deployment and validation       22                                                            |

|   | 3.3  | Architecture and Technologies                                                                             |

|   | 5.5  | 3.3.1         System architecture         22                                                              |

|   |      | 3.3.1       System arcmeeture       22         3.3.2       Choosing the appropriate technologies       24 |

|   | 24   |                                                                                                           |

|   | 3.4  | Concluding Remarks                                                                                        |

| 4  | Bacl   | kend and Simulation Logic 2                         |

|----|--------|-----------------------------------------------------|

|    | 4.1    | Unicycle CPU Version                                |

|    |        | 4.1.1 Supported Instructions                        |

|    |        | 4.1.2 Understanding the execution flow              |

|    |        | 4.1.3 CPU Components                                |

|    |        | 4.1.4 Control Unit                                  |

|    |        | 4.1.5 Computing the CPU Datapath                    |

|    |        | 4.1.6 Assembler                                     |

|    |        | 4.1.7 Latencies and critical path                   |

|    | 4.2    | Pipeline CPU Version                                |

|    |        | 4.2.1 Pipeline Hazards                              |

|    | 4.3    | User Sessions                                       |

|    | 4.4    | Server Logic                                        |

|    | 4.5    | Concluding Remarks                                  |

| _  | TT     | - T                                                 |

| 5  |        | <b>Interface</b> 4<br>Interface Design and Features |

|    | 5.1    |                                                     |

|    | 5.2    | Implementation Details   5                          |

|    |        | 5.2.1 Datapath Visualization                        |

|    |        | 5.2.2 CPU States and Execution                      |

|    | 5.3    | Client-server communication                         |

|    | 5.4    | Concluding Remarks                                  |

| 6  | Vali   | dation 6                                            |

|    | 6.1    | User Testing                                        |

|    |        | 6.1.1 Survey                                        |

|    | 6.2    | Analysis of feedback                                |

|    |        | 6.2.1 CA Background                                 |

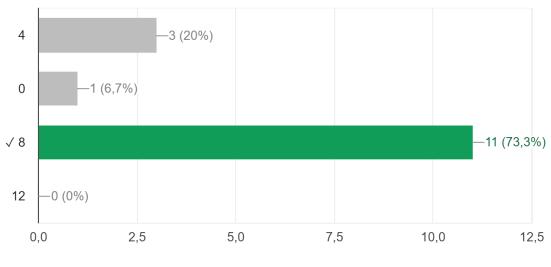

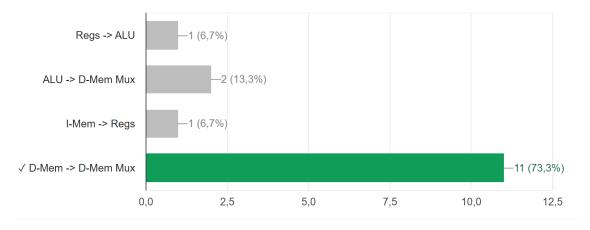

|    |        | 6.2.2 Platform testing with an exercise             |

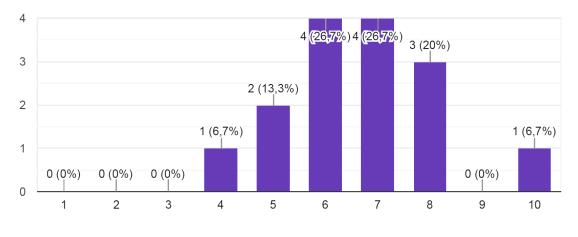

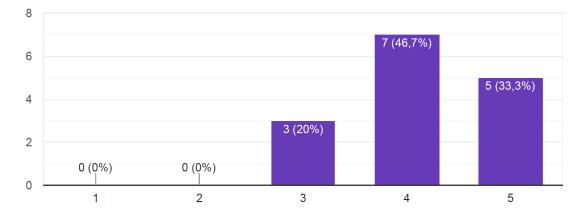

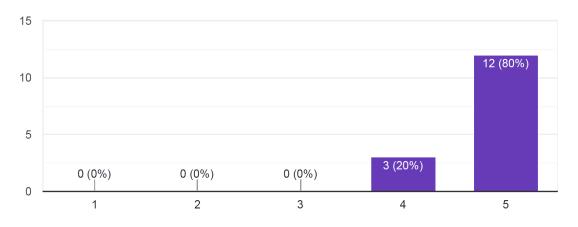

|    |        | 6.2.3 Quantitative feedback                         |

|    |        | 6.2.4 Qualitative feedback                          |

|    | 6.3    | Concluding Remarks                                  |

| _  | a      |                                                     |

| 7  |        | clusions       7         Future Work       7        |

|    | /.1    | Future Work                                         |

| Re | eferen | ces 7                                               |

| A  | Vali   | dation Material 7                                   |

| -  | A.1    | User Manual                                         |

|    |        | User Survey                                         |

|    |        |                                                     |

# **List of Figures**

| 2.1  | Unicycle CPU Datapath [17]                                      |

|------|-----------------------------------------------------------------|

| 2.2  | Pipeline CPU Datapath [17]         5                            |

| 2.3  | SPIM: A MIPS32 Simulator         7                              |

| 2.4  | WebMIPS - Web-Based MIPS Simulation Environment                 |

| 2.5  | MARS, the Mips Assembly and Runtime Simulator                   |

| 2.6  | DrMIPS - Educational MIPS simulator                             |

| 2.7  | RARS, the RISC-V Assembler and Runtime Simulator                |

| 2.8  | BRISC-V Assembly Simulator                                      |

| 2.9  | BRISC-V Explorer 13                                             |

| 2.10 | VisUAL - A highly visual ARM emulator                           |

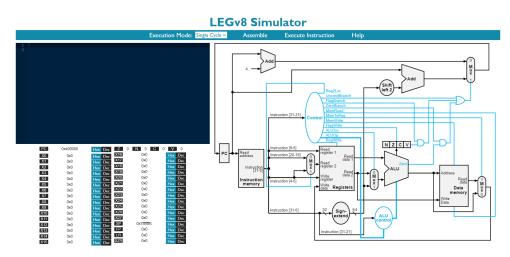

| 2.11 | Graphical Micro-Architecture Simulator - LEGv8 Visual Simulator |

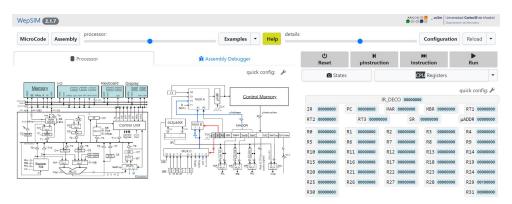

| 2.12 | WepSIM - The Web Elemental Processor SIMulator                  |

| 2.13 | CREATOR - Generic assembly programming simulator                |

|      |                                                                 |

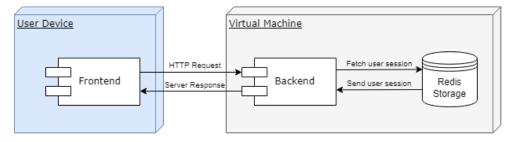

| 3.1  | eduARM Architecture Diagram 23                                  |

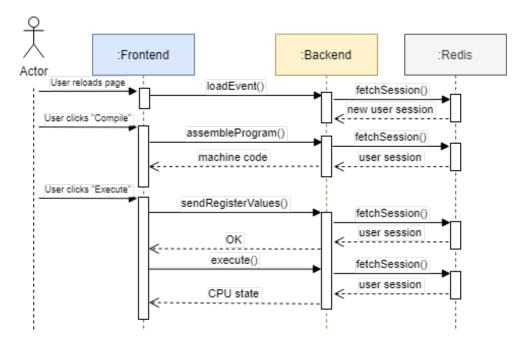

| 3.2  | Sequence Diagram of the execution of a program 23               |

| 4.1  | Types of instructions and their formats                         |

| 7.1  |                                                                 |

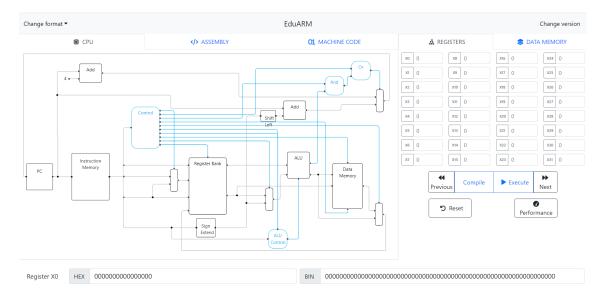

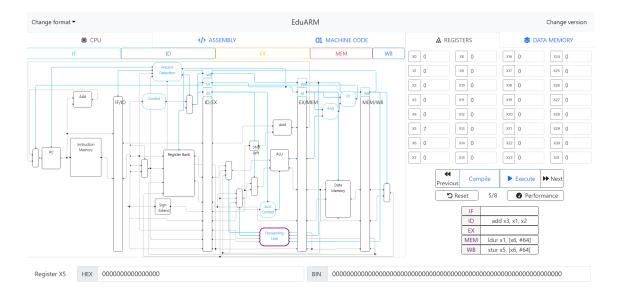

| 5.1  | Homepage of eduARM                                              |

| 5.2  | Area dedicated to assembly programming and the register file    |

| 5.3  | Machine code of the written assembly program                    |

| 5.4  | Alert received after writing an unknown instruction             |

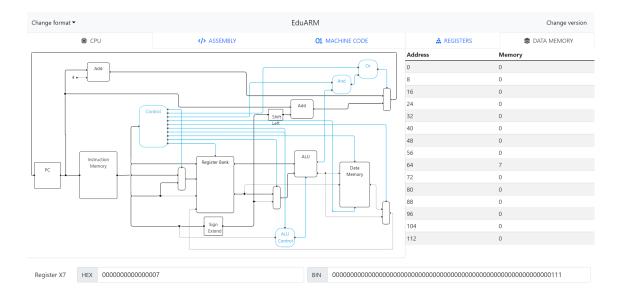

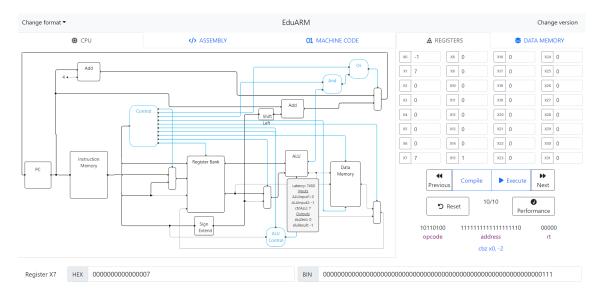

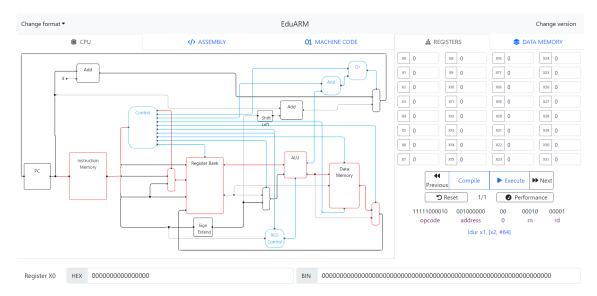

| 5.5  | Datapath and memory after execution                             |

| 5.6  | Interface after executing a program                             |

| 5.7  | Critical path of a load instruction                             |

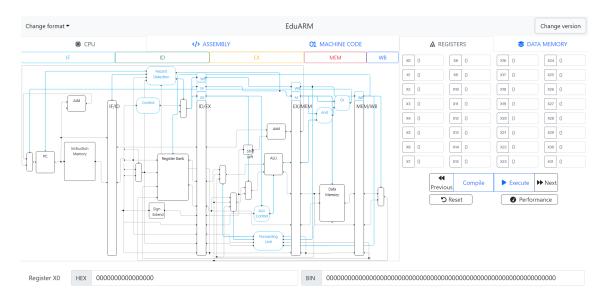

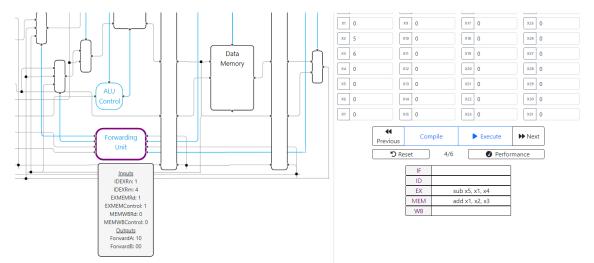

| 5.8  | Pipeline CPU version of the platform                            |

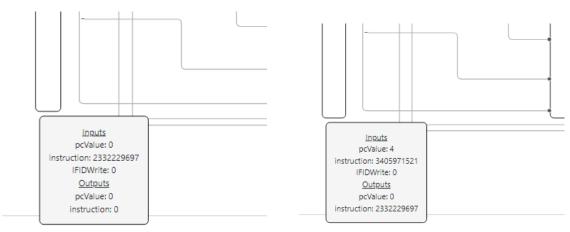

| 5.9  | Close-up of a pipeline register in between two stages           |

|      | (a) First clock cycle                                           |

|      | (b) Second clock cycle                                          |

| 5.10 | Forwarding in the pipeline to solve an instruction dependence   |

|      | Results of a hazard on the instruction flow                     |

|      |                                                                 |

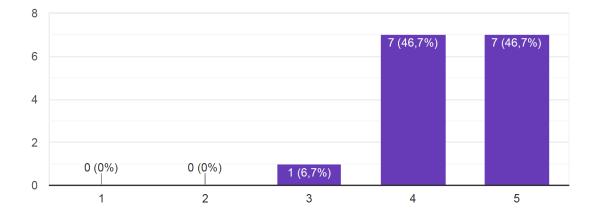

| 6.1  | Results of Question 1 (Q1)                                      |

| 6.2  | Results of Question 2 (Q2)         63                           |

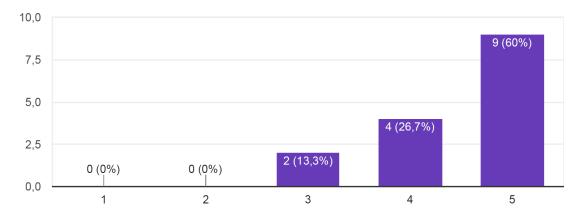

| 6.3  | Results of Question 4 (Q4)                                      |

| 6.4  | Results of Question 5 (Q5)         65                           |

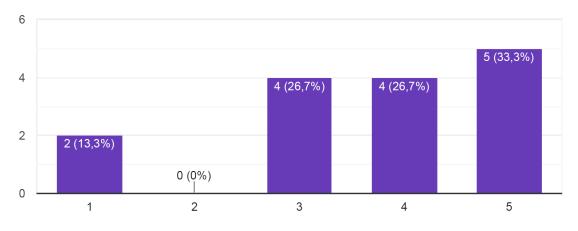

| 6.5  | Results of Question 6 (Q6)         65                           |

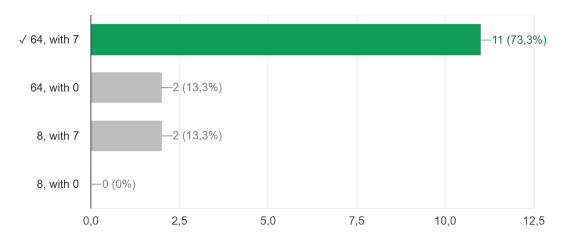

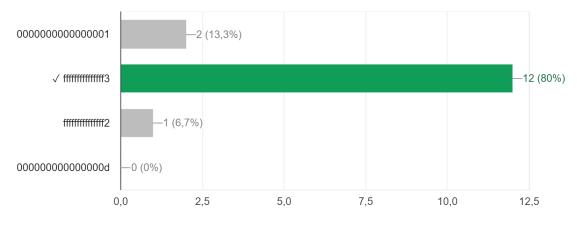

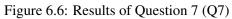

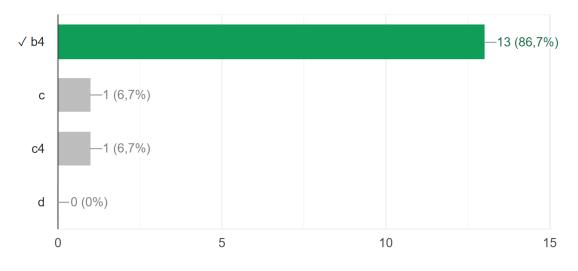

| 6.6  | Results of Question 7 (Q7)                                      |

| 6.7  | Results of Question 8 (Q8)   | 66 |

|------|------------------------------|----|

| 6.8  | Results of Question 9 (Q9)   | 66 |

| 6.9  | Results of Question 10 (Q10) | 67 |

| 6.10 | Results of Question 11 (Q11) | 67 |

| 6.11 | Results of Question 12 (Q12) | 68 |

| 6.12 | Results of Question 13 (Q13) | 68 |

| 6.13 | Results of Question 14 (Q14) | 69 |

| 6.14 | Results of Question 15 (Q15) | 69 |

| 6.15 | Results of Question 16 (Q16) | 70 |

## **List of Tables**

| 2.1 | Comparison of requirements met by the tools                                      | 18 |

|-----|----------------------------------------------------------------------------------|----|

| 4.1 | LEGv8 instruction set used in this project                                       | 27 |

| 4.2 | Table with the inputs, outputs, and execution behaviour of each component type . | 31 |

| 4.3 | Control signals' values according to their instruction type                      | 35 |

| 4.4 | How the ALUOp and opcode influence the ALU control bits                          | 35 |

| 4.5 | Table with the API's endpoints and their purpose                                 | 46 |

| 5.1 | Table with the key state variables of the App component and their contents       | 58 |

## Listings

| 4.1  | Example class for a component                                           | 29 |

|------|-------------------------------------------------------------------------|----|

| 4.2  | JSON object representing a CPU component                                | 32 |

| 4.3  | JSON object representing a CPU connection                               | 32 |

| 4.4  | JSON object defining control values                                     | 33 |

| 4.5  | Class representing a CPU                                                | 34 |

| 4.6  | Snippet of the "initializeCPU" method                                   | 36 |

| 4.7  | "connectComponents" method                                              | 37 |

| 4.8  | JSON object of a connection belonging to an instruction's critical path | 39 |

| 4.9  | "UserSession" contents                                                  | 43 |

| 4.10 | Endpoint for route "/execute" that handles a program's execution        | 44 |

| 5.1  | "RegBank" node created for representing the register bank               | 55 |

| 5.2  | Edge connecting one of RegBank's outputs with an ALU input              | 56 |

| 5.3  | Snippet of method "executeProgram"                                      | 57 |

| 5.4  | Axios HTTP "POST" request used in the assembly of instructions          | 59 |

|      |                                                                         |    |

## Abbreviations

API Application Programming Interface

- CA Computer Architecture

- CISC Complex Instruction Set Computer

- CPU Central Processing Unit

- CSS Cascading Style Sheets

- FEUP Faculty of Engineering of the University of Porto

- HTML HyperText Markup Language

- HTTP Hypertext Transfer Protocol

- ISA Instruction Set Architecture

- I/O Input/Output

- IDE Integrated Development Environment

- L.EIC Bachelor in Informatics and Computing Engineering

- MIPS Microprocessor without Interlocked Pipeline Stages

- PC Personal Computer

- RISC Reduced Instruction Set Computer

- VPN Virtual Private Network

## Chapter 1

## Introduction

In this chapter, the main context and motivation for this thesis are introduced, as well as the goals it strives to achieve, finishing with a general overview of the document's structure.

#### **1.1** Context and Motivation

Computer Architecture (CA) is a fundamental subject in higher education technology courses, namely Informatics and Electrical Engineering. Such is the case of the Bachelor in Informatics and Computing Engineering (L.EIC) on the Faculty of Engineering of the University of Porto (FEUP) and its CA course unit - among other topics, students can learn about the major internal subsystems of a computer, the general architecture of its platform, and assembly programming based on the ARMv8 64-bit architecture.

The Central Processing Unit (CPU) itself and its internal behaviour is a key study item, and one that students tend to exhibit difficulties in understanding. This problem is a result of the scarcity of intuitive educational tools that can graphically represent the CPU and the impact of executing a set of instructions [14].

Another problem is raised with the evolution and popularity of the ARM architecture, specifically ARMv8. This architecture is currently the most popular instruction set architecture (ISA) in the industry [17], that is widely used in smartphones, laptops, and other embedded systems. Consequently, this caused certain higher education institutions to adapt their syllabus to include the teaching of this architecture instead of the previously lectured MIPS or RISC-V architectures [16].

Similarly to what was already identified as a problem in the teaching of the most common processors [14], suitable platforms for teaching ARMv8 are scarce, which increases the need for developing an adequate software tool. Such a tool would encourage CA students to learn through

#### Introduction

interactive experimentation, allowing them, for example, to thoroughly consult the CPU's datapath, in both its unicycle and pipelined versions, for each instruction in a set written in assembly language.

To contribute towards solving this issue, this thesis aims to develop a practical and interactive web platform that simulates how a CPU works, built for ARMv8 education, that can thus be used in higher education with the objective of improving student comprehension and productivity.

#### 1.2 Goals

This project was created with the interest of CA students in mind, anticipating that they can take maximum advantage of the developed tool and thus better comprehend the topics approached in classes. Taking this motivation into account, a set of goals for this thesis were defined as follows:

- Deliver a practical and intuitive web platform suitable for teaching CA, specifically the ARMv8 ISA. This platform should be capable of replicating, in a simple manner, the behaviour of the CPU, in both its unicycle and pipelined versions, displaying its components and their states during the execution of a given assembly program.

- Validate the solution with former CA students of both the Informatics and Electrical Engineering courses at FEUP, as well as collect feedback for further improvements.

- Analyse and discuss the results obtained in order to understand the value of the developed solution and how much of an impact it can have on student comprehension of the topics lectured in CA.

- Document the work developed in paper format, with the objective of being submitted to a conference

In order to achieve these goals, a work plan for this project was devised and is documented throughout the following chapters.

#### **1.3 Document Structure**

Following the present chapter, this document includes a review and discussion of state of the art in Chapter 2, where related work is analysed in detail. In Chapter 3, the requirements set for the project and an overall summary of the development process are provided. An in-depth explanation of the platform's backend is provided in Chapter 4, followed by its correspondent frontend in Chapter 5. Following these chapters on methodology, Chapter 6 features the results obtained from validation with students and their analysis. To finalize, conclusions and proposals for future work are disclosed in Chapter 7.

### Chapter 2

### State of the Art

In this chapter, previous work on tools for CA education is presented and analysed. An overview of the ARM architecture, necessary for a better understanding of the project and its requirements, is provided. For each of the projects presented, their various features are discussed, as well as their positive and negative aspects. Finally, in the last section, a comparison is made between the presented tools, also highlighting which features are desirable in the platform this thesis aims to develop and what contribution it can give to the field.

#### 2.1 Background

In order to develop an adequate platform to teach the ARM architecture, educational tools already used in this domain should first be studied, as to better understand which features are most important to include, and how these tools' good practices can be adopted. This state of the art analysis, however, requires some prior contextualization on how an architecture such as ARMv8 works, which is provided in this section.

To understand how any computer architecture works, one must know what exactly an architecture is. An architecture is defined as an abstract model of a computer that defines the interface between the hardware and the lowest-level software. It encapsulates everything necessary to write a machine language program, including instructions, data types, registers, memory access and I/O.

Another important concept to understand is the CPU, or processor for short. As David A. Patterson and John L. Hennessy mentioned in their book Computer Organization and Design (Arm Edition) [17], the five standard components of a computer are input, output, memory, datapath, and control. The combination of the datapath and control units is commonly referred to as the processor, the active part of a computer capable of executing a set of instructions within a program.

A processor can have multiple possible implementations, and each of them entails different clock cycle times and number of clock cycles per instruction. These two variables, along with the number of program instructions, are what impact a computer's performance. Fundamentally, different CPU versions will perform in different ways, which is the case for the two approaches considered in this project: the unicycle and the pipeline.

#### 2.1.1 Unicycle

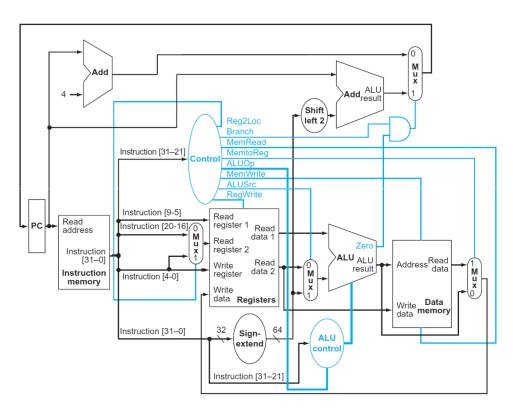

Figure 2.1: Unicycle CPU Datapath [17]

As seen in Figure 2.1, the CPU comprises various components connected by buses. Highlighted blue is the control unit, whose signals' values, depending on the instruction to execute, influence the datapath. Specifically, every component type has a different behaviour, sometimes changing according to the control values. Within the datapath, each connection carries important data from one component to another, and the sequential actions of each component make it possible to execute a given instruction.

In this CPU version, each instruction is executed in a single clock cycle. This means this implementation, albeit straightforward and easy to understand, is not very efficient for modern designs [17], which is why another technique, pipelining, was created to improve performance.

#### 2.1.2 Pipeline

Although its components remain mostly the same, the behaviour of a pipelined CPU differs from its unicycle version. In this case, the datapath is divided into five stages, with each taking one clock cycle:

- IF (Instruction Fetch): Fetch the instruction from memory

- ID (Instruction Decode): Read registers and decode instruction

- EX (Execute): Execute the operation or calculate an address

- MEM (Memory access): Access an operand in data memory

- WB (Write back): Write the result back into a register

Dividing an execution's tasks into five steps makes it so that an instruction can only be present at one stage at a given time. This means that, for example, while an instruction is in its decoding phase, the next instruction is already being fetched from memory.

This overlapping of multiple instructions in a program's execution is, indeed, the technique called pipelining, used universally and capable of, under ideal circumstances, making a five-stage pipeline nearly five times faster than its unicycle version [17]. The reason behind this increase in performance is that pipelining increases instruction throughput, instead of decreasing the execution time of just one instruction - and the former offers a significant advantage in terms of total execution time.

PCSe

The full pipeline CPU datapath is represented in Figure 2.2.

Figure 2.2: Pipeline CPU Datapath [17]

A CPU can also be classified as either CISC (Complex Instruction Set Computer) or RISC (Reduced Instruction Set Computer). RISC architectures, considering their simple instruction sets and fewer clock cycles, make up a much less complicated processor compared to CISC [10]. Taking this simplicity into account, CA courses such as FEUP's choose to adopt this ISA for

teaching the CPU [16], thus this chapter focuses solely on tools dedicated to RISC architectures, namely MIPS, RISC-V and ARM. All of the tools presented are open-source, which means their code base is free for developers to expand for innovation.

#### 2.2 MIPS

#### 2.2.1 SPIM

*SPIM* is an open-source, self-contained MIPS simulator that runs assembly language programs. Developed by James Larus, it is considered the most widely known and used MIPS simulator [22], both for education and the industry. This program has an updated version, called QtSpim, that unlike the previous versions, runs on Microsoft Windows, Mac OS X, and Linux, and is the one that is currently actively maintained [12].

This platform's interface, as seen in Figure 2.3, contains a panel dedicated to register visualization, accompanied by an area that displays the text and data segments, and a console window on the lower part of the screen. *SPIM* does not provide an integrated code editor, which means users must write code externally and then load it. Additionally, this tool allows users to modify register and memory values, set breakpoints and execute on single step or multi step mode.

Although *SPIM* can be used for debugging assembly programs, in order for the tool to thoroughly support the teaching of CA, CPU datapath visualization is missing. This functionality is essential for understanding the internal behaviour of the CPU, as well as support for the pipelined version of the CPU.

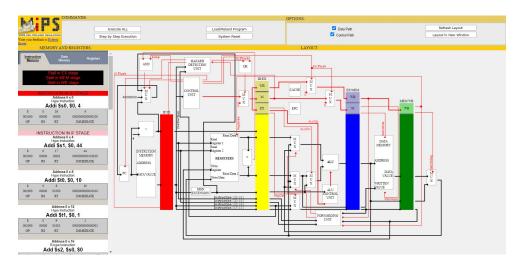

#### 2.2.2 WebMIPS

*WebMIPS* is an educational web-based MIPS simulation environment, developed by the University of Siena in Italy and written in the ASP language. This platform is designed for Web browsers, which means users can have access to the software regardless of their operating system.

More specifically, this tool is a five stage MIPS pipeline simulator (thus not including support for the unicycle version of the processor), conceived with the objective of teaching assembly programming and mastering pipeline, control and datapath design [6]. This means students can explore what type of hazards can occur in the system, and how the CPU detects and solves them in the pipeline, using data forwarding and stalls.

As seen in Figure 2.4, the interface includes an area for visualization of instructions, data memory and registers, accompanied by a display of which parts of the pipeline are stalled. The CPU datapath and its components are shown in the center of the screen, with the wires related to the data or control paths differentiated by color. The user can, in the commands panel, load any MIPS assembly file on a simple editor or use one of the built-in examples. Each program can then be executed all at once or step-by-step, where the student can explore what happens in each stage of the pipeline - by clicking on each component of the processor, along with a small description, data input and output data in each clock cycle is displayed.

| 🐌 🧾 🖬                             | Registers Text Segment |    |            |          |                        |                                                           |      |

|-----------------------------------|------------------------|----|------------|----------|------------------------|-----------------------------------------------------------|------|

| FP Regs                           | Int Regs [16]          |    | Data       | Tex      |                        |                                                           |      |

| nt Regs [16]                      | 6                      | 7× | Text       |          |                        |                                                           |      |

| PC = 0                            |                        | ^  |            |          | User Text S            | egment [00400000][00440000]                               |      |

| SPC = 0                           |                        |    | [00400000] | 8fa40000 | lw \$4, 0(\$29)        | ; 183: 1w \$a0 0(\$sp) # argc                             |      |

| Cause = 0                         |                        |    | [00400004] | 27a50004 | addiu \$5, \$29, 4     | ; 184: addiu \$a1 \$sp 4 # argv                           |      |

| adVAddr = 0                       |                        |    | [00400008] | 24a60004 | addiu \$6, \$5, 4      | ; 185: addiu \$a2 \$a1 4 # envp                           |      |

| Status = 3                        | 000ff10                |    | [0040000c] | 00041080 | s11 \$2, \$4, 2        | ; 186: sll \$v0 \$a0 2                                    |      |

|                                   |                        |    | [00400010] | 00c23021 | addu \$6, \$6, \$2     | ; 187: addu \$a2 \$a2 \$v0                                |      |

| II = 0                            |                        |    | 1004000141 | 0c000000 | jal 0x00000000 [main]  | ; 188; jal main                                           |      |

| LO = 0                            |                        |    | 1004000181 | 00000000 | nop                    | ; 189; nop                                                |      |

|                                   |                        |    | [0040001c] | 3402000a | ori \$2, \$0, 10       | ; 191: li \$v0 10                                         |      |

| R0 [r0] = 0                       |                        |    | 1004000201 |          |                        | ; 192; svscall # svscall 10 (exit)                        |      |

| <pre>R1 [at] = 0</pre>            |                        |    |            |          | -                      |                                                           |      |

| 2 [v0] = 0                        |                        |    |            |          | Kernel Text            | Segment [80000000][80010000]                              |      |

| $x_3 [v_1] = 0$<br>$x_4 [a0] = 0$ |                        |    | [80000180] | 0001d821 | addu \$27, \$0, \$1    | ; 90: move \$k1 \$at # Save \$at                          |      |

| (4 [a0] = 0<br>(5 [a1] = 0        |                        |    | 1800001841 | 3c019000 | lui \$1, -28672        | ; 92: sw \$v0 s1 # Not re-entrant and we can't trust \$sp |      |

| $R_{6} [a1] = 0$                  | FFFF9b4                |    | [80000188] | ac220200 | sw \$2, 512(\$1)       |                                                           |      |

| R7 [a3] = 0                       |                        |    | [8000018c] | 3c019000 | lui \$1, -28672        | ; 93: sw \$a0 s2 # But we need to use these registers     |      |

| (1 = 0)                           |                        |    | [80000190] | ac240204 | sw \$4, 516(\$1)       |                                                           |      |

| R9 [t1] = 0                       |                        |    | [80000194] | 401a6800 | mfc0 \$26, \$13        | ; 95: mfc0 \$k0 \$13 # Cause register                     |      |

| (10 [t2] = 0                      |                        |    | [80000198] | 001a2082 | srl \$4, \$26, 2       | ; 96: srl \$a0 \$k0 2 # Extract ExcCode Field             |      |

| (11 [t3] = 0                      |                        |    | [8000019c] | 3084001f | andi \$4, \$4, 31      | ; 97: andi \$a0 \$a0 0x1f                                 |      |

| R12 [t4] = 0                      |                        |    | [800001a01 | 34020004 | ori \$2, \$0, 4        | ; 101: li \$v0 4 # syscall 4 (print str)                  |      |

| R13 [t5] = 0                      |                        |    | [800001a4] | 3c049000 | lui \$4, -28672 [ m1 ] |                                                           |      |

| R14 [t6] = 0                      |                        |    | [800001a8] |          |                        | ; 103: syscall                                            |      |

| R15 [t7] = 0                      |                        |    |            |          |                        | ; 105: li \$v0 1 # syscall 1 (print int)                  |      |

| R16 [s0] = 0                      |                        |    |            |          |                        | : 106: srl SaO SkO 2 # Extract ExcCode Field              |      |

| R17 [s1] = 0                      |                        |    |            |          |                        | ; 107: andi \$a0 \$a0 0x1f                                |      |

| R18 [s2] = 0                      |                        |    | [800001b8] |          |                        | ; 108; svscall                                            |      |

| R19 [s3] = 0                      |                        |    |            |          |                        | ; 110: li \$v0 4 # syscall 4 (print str)                  |      |

| (s4] = 0                          |                        |    |            |          |                        | ; 111: andi \$a0 \$k0 0x3c                                |      |

| <b>R21 [s5] =</b> 0               |                        |    |            |          | lui \$128672           | ; 112: lw \$a0 excp(\$a0)                                 |      |

| <b>R22 [s6] =</b> 0               |                        |    |            |          | addu \$1, \$1, \$4     | , 112, 1, 40 chop(400)                                    |      |

| 23 [s7] = 0                       |                        |    |            |          | lw \$4, 384(\$1)       |                                                           |      |

| (124 [t8] = 0)                    |                        |    | [800001d0] |          |                        | ; 113: nop                                                |      |

| R25 [t9] = 0                      |                        |    |            |          |                        | ; 114: syscall                                            |      |

| $R_{26} [k0] = 0$                 |                        |    |            |          |                        | ; 116: bne \$k0 0x18 ok pc # Bad PC exception requires sp | ecia |

| (27 [k1] = 0)                     |                        |    |            |          | 011 (1) (0) 11         | , ite, bue the oute of but to encopered requires op       |      |

Figure 2.3: SPIM: A MIPS32 Simulator

Figure 2.4: WebMIPS - Web-Based MIPS Simulation Environment

Similarly to the simulator previously presented, *WebMIPS* solely supports the MIPS architecture and, in this case, only the pipeline version of the CPU, which poses a great disadvantage, compared with other tools that can support both unicycle and pipeline. The visualization is mostly static, as the datapath seemingly does not change with each instruction (the user must click on each component in order to see the differences) and there is a need to refresh the layout to enable or disable the data and control paths. The platform can, therefore, be seen as outdated and easily surpassed by other similar, more recent tools.

#### 2.2.3 MARS

*MARS*, the Mips Assembly and Runtime Simulator, was created by the Missouri State University, and its objective is to assemble and simulate the execution of MIPS assembly language programs. This tool can be used either from a command line or through its integrated development environment (IDE).

This platform is an extremely complete assembly debugger, used in various CA courses all around the world, containing, as of Release 4.0, "155 basic instructions of the MIPS-32 instruction set, approximately 370 pseudo-instructions or instruction variations, the 17 syscall functions mainly for console and file I/O defined by SPIM, and an additional 22 syscalls for other uses such as MIDI output, random number generation and more" [21].

As seen in Figure 2.5, *MARS* has a fairly simple and easy to use interface, which contains an integrated editor with multiple file-editing tabs and syntax highlighting dedicated to assembly programming, accompanied by a panel for showcasing register values, that can be either displayed in hexadecimal or decimal, and a console window on the lower part of the interface.

Each program can be executed all at once or step-by-step. During the execution, the user can see the compiled code and the data segment, as well as the resulting inputs and outputs. Users can also create and remove execution breakpoints and go back and forth through a set of instructions while viewing or editing register and memory values.

This assembly simulator was designed as an alternative to *SPIM*, tackling most of its shortcomings and greatly outperforming it.

Despite being a robust and useful tool for assembly debugging, *MARS* has no CPU datapath visualization, which, in order for students to thoroughly understand how the processor functions, is considered a crucial feature. Moreover, this tool executes the instructions according to the unicycle version of the CPU, with no support for pipelined architectures. Another disadvantage is the program not being available on the Web, as it must be downloaded and may not be available for every user's operating system.

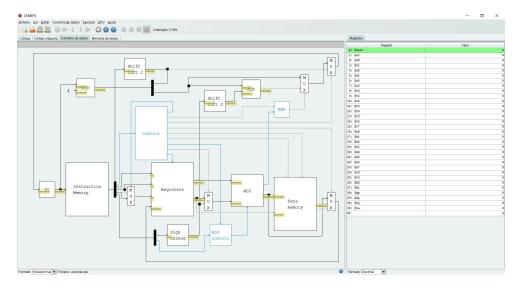

#### 2.2.4 DrMIPS

*DrMIPS* is an open-source graphical simulator of the MIPS processor, specifically designated for teaching and learning CA [14]. This project was developed in a Master's thesis at FEUP, having since been updated with various bug fixes and interface improvements.

| L¥           |                          |                                                    | 1 1 | 1 1 1     | - <b></b> |            |

|--------------|--------------------------|----------------------------------------------------|-----|-----------|-----------|------------|

| Edit E       | Execute                  |                                                    | 1   | Registers | Coproc 1  | Coproc 0   |

| # Comp       | pute first twelve Fibo   | nacci numbers and put in array, then print         |     | Name      | Number    | Value      |

|              | .data                    |                                                    |     | \$zero    | 0         | 0x00000000 |

| fibs:        | .word 0 : 12             | # "array" of 12 words to contain fib values        |     | \$at      | 1         | 0x0000000  |

| size:        | .word 12                 | # size of "array"                                  |     | \$v0      | 2         | 0x0000000  |

|              | .text                    |                                                    |     | \$v1      | 3         | 0x0000000  |

|              | la \$t0, fibs            | # load address of array                            |     | \$a0      | 4         | 0x0000000  |

|              | la \$t5. size            | # load address of size variable                    |     | \$a1      | 5         | 0x00000000 |

|              | 1w \$t5, 0(\$t5)         | ∉ load arrav size                                  |     | \$a2      | 6         | 0x0000000  |

|              | li \$t2, 1               | # 1 is first and second Fib. number                |     | \$a3      | 7         | 0x0000000  |

| 0            | add.d \$f0, \$f2, \$f4   |                                                    |     | \$t0      | 8         | 0x0000000  |

|              | sw \$t2, 0(\$t0)         | # F[0] = 1                                         |     | \$t1      | 9         | 0x0000000  |

| 2            | sw \$t2, 4(\$t0)         | # F[1] = F[0] = 1                                  |     | \$t2      | 10        | 0x0000000  |

| 3            | addi @tl, @t5, -2        | # Counter for loop, will execute (size-2) times    |     | \$t3      | 11        | 0x0000000  |

|              | lw \$t3, 0(\$t0)         | # Get value from array F[n]                        |     | \$t4      | 12        | 0x0000000  |

|              |                          | # Get value from array F[n+1]                      |     | \$t5      | 13        | 0x0000000  |

|              | 1w \$t4, 4(\$t0)         |                                                    |     | \$t6      | 14        | 0x0000000  |

| 6<br>7       | add \$t2, \$t3, \$t4     |                                                    |     | \$t7      | 15        | 0x0000000  |

|              | sw \$t2, 8(\$t0)         | <pre># Store F[n+2] = F[n] + F[n+1] in array</pre> |     | \$s0      | 16        | 0x0000000  |

|              | addi \$t0, \$t0, 4       | # increment address of Fib. number source          |     | \$s1      | 17        | 0x0000000  |

|              | addi \$tl, \$tl, -1      | # decrement loop counter                           |     | \$s2      | 18        | 0x0000000  |

|              | bgtz \$tl, loop          | # repeat if not finished yet.                      |     | \$s3      | 19        | 0x0000000  |

| 1            | la \$aO, fibs            | # first argument for print (array)                 |     | \$\$4     | 20        | 0x0000000  |

| 2            | add \$al, \$zero, \$t5   | # second argument for print (size)                 |     | \$s5      | 21        | 0x0000000  |

| 3            | jal print                | # call print routine.                              | -   | \$s6      | 22        | 0x0000000  |

| f            |                          |                                                    |     | \$s7      | 23        | 0x00000000 |

| ine: 1 Col   | lumn: 1 🔽 Show Line Numi | pers                                               |     | \$t8      | 24        | 0x0000000  |

| *            |                          |                                                    |     | \$t9      | 25        | 0x00000000 |

|              | essages Run I/O          |                                                    |     | \$k0      | 26        | 0x0000000  |

| INICI S INIC | caaugea munito           |                                                    |     | \$k1      | 27        | 0x0000000  |

|              |                          |                                                    |     | \$gp      | 28        | 0x1000800  |

|              |                          |                                                    |     | \$sp      | 29        | 0x7fffeff  |

|              |                          |                                                    |     | \$fp      | 30        | 0x0000000  |

| Clear        |                          |                                                    |     | \$ra      | 31        | 0x0000000  |

| Ciodi        |                          |                                                    |     | pc        |           | 0x0040000  |

|              |                          |                                                    |     | hi        |           | 0x0000000  |

|              |                          |                                                    |     | lo        |           | 0x0000000  |

Figure 2.5: MARS, the Mips Assembly and Runtime Simulator

*DrMIPS* provides students with a robust and highly intuitive tool that includes fundamental principles lectured in CA, such as the components and behaviour of the CPU, on both its unicycle and pipelined versions, latencies and critical path, and assembly programming. Its educational focus and various functionalities make *DrMIPS* a greatly valuable tool, having it been used at FEUP to support students in CA classes.

The platform is available for free on both PCs and Android devices, namely tablets, which allows students to use the application wherever they want. In terms of functionalities, it includes step-by-step assembly instruction execution, accompanied by CPU datapath visualization. Users can thus create (or import) their own assembly programs and explore what happens within the CPU and its components while executing certain instructions, encouraging learning through interactive experimentation. Moreover, the CPU datapath is highly configurable, as CPU components can be created externally and imported into the simulator, allowing users to customize it according to their needs.

DrMIPS only supports instruction sets that the datapath itself can support, which, in turn, makes up for a limited set of instructions (for example, floating point and shift operations, syscalls, *jal* and *jr* are not supported) - besides these exceptions, the instruction sets used by the CPU are highly configurable.

This tool displays the values of the registers in each step of execution, on the right side of the screen, so students can see, along with the CPU datapath, what influence certain instructions have on these registers. Besides this, DrMIPS also displays the assembled instructions in machine code

and the register values on the data memory, which are also important concepts approached in CA classes.

In regards to further visualization, the datapath shows, for each execution of a set of instructions, the current values at input or output of every CPU component and which wires are relevant to the current instruction. Students can thus, at each step, understand how the datapath and its values change with a specific instruction.

Support for both unicycle and pipeline versions of the processor is provided, which allows users to experiment with both versions and, in the case of the pipeline CPU, learn what types of hazards can arise while using a pipeline and how the system solves them.

Moreover, the platform includes a "performance mode" where latency is simulated, allowing for visualization of the CPU critical path, in order to better understand how latencies can have an effect on it, as well as showcasing performance metrics, such as time of execution and clock cycles, that can highlight the impact of each execution on the CPU's performance.

Regarding its user interface, *DrMIPS* is simple and intuitive, providing useful features such as tooltips for data visualization, which allows students to interact with components and check their current status and values, support for multiple representation formats (binary, decimal and hexadecimal), and an integrated code editor with auto-complete and syntax highlighting. *DrMIPS* also has support for multiple languages, dark mode, and different possibilities for window layout.

Figure 2.6: DrMIPS - Educational MIPS simulator

Although this intuitive and educational tool, with its various features described above, seems ideal for supporting CA students in their studies, the fact that it exclusively supports the MIPS architecture impedes its adoption in more recent higher education courses that currently work with the ARMv8 processor.

Another disadvantage arises considering that more recent simulators, as presented in the next section, can already be used on the Web with support for multiple browsers, making it even easier to have immediate access to these platforms, with no need to download them.

Nevertheless, its focus on education and multitude of functionalities and visualization, that help students learn the MIPS architecture, make DrMIPS an extremely valuable platform whose vision serves as a model for a new platform to develop, this time dedicated to the ARMv8 ISA.

#### 2.3 RISC-V

#### 2.3.1 RARS

*RARS*, or RISC-V Assembler and Runtime Simulator, is a direct port of the MIPS simulator *MARS*, described in subsection 2.2.3, for teaching the RISC-V architecture. This platform, created with the intent of delivering an intuitive development environment for those new to this architecture, uses *MARS*' source code and adapts it to RISC-V, maintaining its user interface, as seen in Figure 2.7.

| Europeed at max (no interaction)                                                                                                                                                                                                          |     |                    |                          |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|--------------------------|---------------|

| t Execute                                                                                                                                                                                                                                 |     | Registers Floating | Point Control and Status |               |

| ttles.s printf.s printnum.s printstr.s                                                                                                                                                                                                    |     | Name               | Number                   | Value<br>0x00 |

| alabi main                                                                                                                                                                                                                                | _   | zero               | 0                        | 0.0           |

|                                                                                                                                                                                                                                           |     | sp                 | 2                        | 8.0           |

| template:                                                                                                                                                                                                                                 |     | gp                 | 3                        | 0.4           |

| .string "Wd bottles of beer of the wall. Wd bottles of beer. Take one down pass it around. Wd bottles of beer on the wallun"                                                                                                              |     | tp<br>t0           | 4                        | Ox<br>Ox      |

| text                                                                                                                                                                                                                                      |     | t1                 | 6                        | 80            |

| mai n:                                                                                                                                                                                                                                    |     | t2                 | 7                        | 0.0           |

| # Save state to free up s0, s1, and ra for use<br>add1 sp, sp, -16                                                                                                                                                                        |     | 50                 | 8                        | 8.0           |

| sv sl.4(sp)                                                                                                                                                                                                                               |     | s1<br>a0           | 10                       | 0.0           |

| sv s0,8(sp)                                                                                                                                                                                                                               |     | al                 | 11                       | 0             |

| sv ra,12(sp)                                                                                                                                                                                                                              |     | a2                 | 12                       | 0.            |

|                                                                                                                                                                                                                                           |     | a3                 | 13                       | 0.            |

| # Call printf(template, x, x, $x \cdot 1$ ) for $\theta < x < 189$                                                                                                                                                                        |     | a4<br>a5           | 14                       | 0             |

| li 10,99                                                                                                                                                                                                                                  |     | a5<br>a6           | 15                       | 0             |

| oop                                                                                                                                                                                                                                       |     | 97                 | 17                       | 0             |

| a2, s0                                                                                                                                                                                                                                    |     | 92                 | 18                       | 0             |

| addi s0,s0, -1                                                                                                                                                                                                                            |     | 83                 | 19                       | 0             |

| ev a3.00<br>la a0.temlate                                                                                                                                                                                                                 |     | 84<br>55           | 20                       | 0             |

| call print                                                                                                                                                                                                                                |     | 55                 | 21                       | 0             |

| bnez s0,loop                                                                                                                                                                                                                              |     | 97                 | 23                       | 0             |

| # Load state                                                                                                                                                                                                                              |     | s8                 | 24                       | 0             |

| v (a.12(a))                                                                                                                                                                                                                               |     | s9<br>s10          | 25                       | 0             |

| le s0.8(sp)                                                                                                                                                                                                                               |     | \$10               | 27                       | 0             |

| lw s1.4(sp)<br>addi sp.sp.16                                                                                                                                                                                                              |     | t3                 | 28                       | 0             |

| wood sp.sp.ac                                                                                                                                                                                                                             |     | t4                 | 29                       | 0             |

| # Exit (93) with code 0                                                                                                                                                                                                                   |     | t5                 | 30                       | 0             |

| 11 e0. 0<br>11 a7. 93                                                                                                                                                                                                                     |     | t6<br>pc           | 31 32                    | 0             |

| tia, so                                                                                                                                                                                                                                   |     | pe                 |                          |               |

| ebreak                                                                                                                                                                                                                                    |     |                    |                          |               |

|                                                                                                                                                                                                                                           |     |                    |                          |               |

|                                                                                                                                                                                                                                           | _   |                    |                          |               |

|                                                                                                                                                                                                                                           | ×   |                    |                          |               |

| 1 Column: 1 🖓 Show Line Numbers                                                                                                                                                                                                           |     |                    |                          |               |

| I Column: 1 2 Show time numbers                                                                                                                                                                                                           |     |                    |                          |               |

| sages Run VO                                                                                                                                                                                                                              |     |                    |                          |               |

| 199 bottles of beer of the wall, 99 bottles of beer. Take one down pass it around, 98 bottles of beer on the wall                                                                                                                         | 1.1 |                    |                          |               |

| 98 bottles of beer of the wall, 98 bottles of beer. Take one down pass it around, 97 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| 97 bottles of beer of the wall. 97 bottles of beer. Take one down pass it around. 96 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| 96 bottles of beer of the wall. 96 bottles of beer. Take one down pass it around. 95 bottles of beer an the wall<br>95 bottles of beer of the wall. 95 bottles of beer. Take one down pass it around. 94 bottles of beer an the wall      |     |                    |                          |               |

| 94 bottles of beer of the wall, 94 bottles of beer. Take one down pass it around, 93 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| 93 bottles of beer of the wall. 93 bottles of beer. Take one down pass it around. 92 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| lear 52 bottles of baer of the wall. 92 bottles of baer. Take one down pass it around. 91 bottles of baer on the wall<br>95 bottles of baer of the wall. 91 bottles of baer. Take one down pass it around. 90 bottles of baer on the wall |     |                    |                          |               |

| 90 bottles of beer of the wall. 90 bottles of beer. Take one down pass it around. 89 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| 89 bottles of beer of the wall. 89 bottles of beer. Take one down pass it around. 88 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| 88 bottles of beer of the wall. 88 bottles of beer. Take one down pass it around. 87 bottles of beer on the wall<br>87 bottles of beer of the wall. 87 bottles of beer. Take one down pass it around. 88 bottles of beer on the wall      |     |                    |                          |               |

| 86 bottles of beer of the wall. 86 bottles of beer. Take one down pass it around. 85 bottles of beer on the wall                                                                                                                          |     |                    |                          |               |

| 85 bottles of beer of the wall. 85 bottles of beer. Take one down pass it around. 84 bottles of beer on the wall<br>82 bottles of beer of the wall 84 bottles of beer Take one down pass it around. 83 bottles of beer on the wall        | _   |                    |                          |               |

Figure 2.7: RARS, the RISC-V Assembler and Runtime Simulator

Besides the changes associated with switching from MIPS to RISC-V, this platform includes major internal restructuring and refactoring, such as removing small features present in *MARS* that were considered irrelevant or incompatible with RISC-V [11].

*RARS*, much like its MIPS counterpart, focuses intensively on assembly debugging, containing essentially the same features described in 2.2.3. As a consequence, this tool also lacks CPU datapath visualization and support for pipelined architectures, which are considered key features for teaching the CPU's structure and behaviour.

#### 2.3.2 BRISC-V Simulator

The *BRISC-V Simulator* is a browser-based assembly programming simulator developed by the Adaptive and Secure Computing Systems Laboratory at Boston University. Together with *BRISC-*

*V Explorer*, it makes up the *BRISC-V Platform* [1]. This simulator's main objective is to provide an educational environment for writing, compiling, assembling and executing RISC-V code.

Students can learn about several low level CA concepts, such as calling conventions, memory allocation and the flow of execution of a set of instructions. As it is available on the web, users can easily access the simulator and study the RISC-V architecture regardless of their platform.

|             | Home                              |                                                             | BRISC-V Simula | tor   |             |         |      |      |       |         |          |         |               |       | Manuz  | al & Exam |

|-------------|-----------------------------------|-------------------------------------------------------------|----------------|-------|-------------|---------|------|------|-------|---------|----------|---------|---------------|-------|--------|-----------|

| BR          |                                   | V Simulator                                                 |                |       |             |         |      |      |       |         |          |         |               |       |        |           |

| ISC-V       | Assembly                          |                                                             | Reg            | giste | s           |         |      |      |       |         | Memo     | ory     |               |       |        |           |

| <u> 1</u>   | ► H                               | H4                                                          | Re             | giste | r           | Value   | Regi | ster | Value | Ê.      | HEX (    |         | BINARY        |       |        |           |

| 0           |                                   | zero, zero, Ø                                               | zer            | n     | [0]         | 0       | ra   | [1]  | 0     |         |          | _       | STACK         |       | NT     |           |

|             | kernel:                           |                                                             |                |       |             |         |      |      |       |         | 0x00000  |         | FREE 5        |       |        |           |

| 1           |                                   | sp,zero,1536<br>main                                        | sp             |       | [2]         | 0       | gp   | [3]  | 0     |         | 8×88888  |         |               |       |        |           |

| 2           |                                   | zero,zero,Ø                                                 | tp             |       | [4]         | 0       | t0   | [5]  | 0     |         | 8×999996 |         |               |       |        |           |

| 4           |                                   | \$1,00                                                      | t1             |       | 61          | 0       | t2   | [7]  | 0     |         | 8x88886  | 95f0:   |               |       |        |           |

| 5           |                                   | zero,zero,0                                                 |                |       |             |         |      |      | -     |         | 0x00000  |         |               |       |        |           |

| 6           | addi zero,zero,0                  |                                                             | s0/            | /tp   | [8]         | 0       | s1   | [9]  |       | 12      | 0x00000  |         |               |       |        |           |

| 7<br>8<br>9 | auipc ra,0x0<br>jalr ra.0(ra)     | a0                                                          | [1             | 0]    | 0           | a1      | [11] |      |       | 0X00000 |          |         |               |       |        |           |

|             | jair ra,0(ra)<br>addi zero,zero,0 |                                                             | a2             | 1-    | 21          | 0       | a3   | [13] | 0     |         | 0x00000  |         |               |       |        |           |

| 0           |                                   | zero, zero, 0                                               |                |       |             |         |      |      |       |         | 8x88886  |         |               |       |        |           |

|             |                                   |                                                             | a4             | [1    | 4]          | 0       | a5   | [15] | 0     |         | 0x00000  |         |               |       |        |           |

|             | main:                             |                                                             | a6             | [1    | 6]          | 0       | a7   | [17] | 0     |         | 90000x8  |         |               |       |        |           |

|             |                                   | file will show you how to use #                             | s2             | P     | 81          | 0       | s3   | [19] | 0     |         | 8x000000 |         |               |       |        |           |

|             |                                   | m calls in the BRISC-V emulator! #                          |                |       |             |         |      |      |       |         | 8x00000  |         |               |       |        |           |

|             |                                   | *******                                                     | s4             | [2    | !0]         | 0       | s5   | [21] | 0     |         | 0x00000  |         |               |       |        |           |

|             |                                   |                                                             | s6             | [2    | 2]          | 0       | s7   | [23] | 0     |         | 0x00000  |         |               |       |        |           |

|             |                                   | start by loading an integer from the user                   | \$8            |       | 41          | 0       | s9   | [25] | 0     |         | 8x88886  |         |               |       |        |           |

| 1           |                                   | ng 4 in register t0 an calling ecall does that<br>, zero, 4 | 50             |       |             | 0       |      |      |       |         | 8×8888   |         |               |       |        |           |

|             |                                   | ecall is run, a box will pop up in the console              | \$10           | D [2  | [6]         | 0       | s11  | [27] | 0     |         | 8x88886  | Sac:    |               |       |        |           |

|             | # 1.ml+n                          | a /amall) number and reason enter to continue               |                |       | ~~          |         |      |      | ^     | *       | ax00000  | 95.a8 · | 66 69         | aa aa |        |           |

| nsol        |                                   | Output ##########                                           |                |       | on br       | eakdown |      |      |       |         |          |         |               |       |        |           |

|             | raisei                            | oucpuc                                                      | 31             | 31    |             |         | 20   | 19   | 19 15 | 14      | 1        | 2       | 11            | 7     | 6      | 0         |

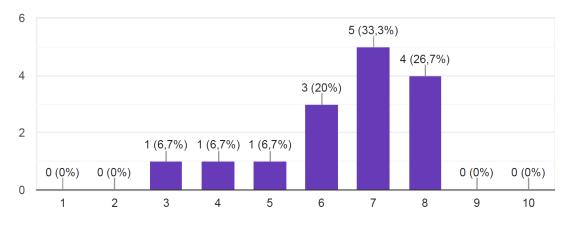

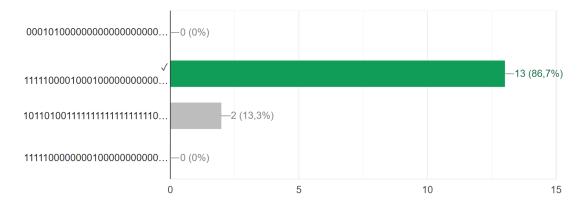

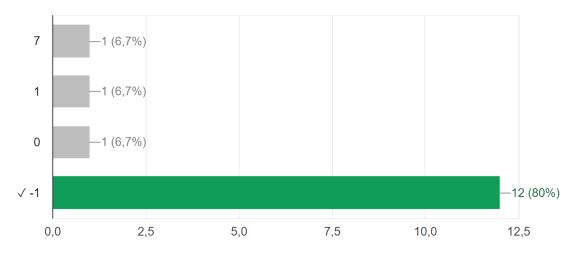

| sing        | g successfu                       | 111                                                         | im             | m     |             |         |      | rs1  |       | fun     | ct3      |         | rd            |       | opcode |           |