Technische Universität Dresden

## Electro-Photonic Transmitter Front-Ends for High-Speed Fiber-Optic Communication

### Dipl.-Ing. Alexandru Giuglea

von der Fakultät Elektrotechnik und Informationstechnik der Technischen Universität Dresden

zur Erlangung des akademischen Grades

#### Doktoringenieur

(Dr.-Ing.)

genehmigte Dissertation

| Vorsitzender:      | Prof. DrIng. Kambiz Jamshidi               |

|--------------------|--------------------------------------------|

| Gutachter:         | Prof. Dr. sc. techn. habil. Frank Ellinger |

| Gutachter:         | Prof. DrIng. habil. Viktor Krozer          |

| weiteres Mitglied: | Prof. DrIng. Dirk Plettemeier              |

|                    |                                            |

Tag der Einreichung:08.03.2022Tag der Verteidigung:16.09.2022

# Abstract

This thesis addresses basic scientific research in the field of transmitter frontend circuits for electro-optical data communication. First, the theoretical fundamentals are presented and analyzed. Based on the theoretical considerations, conceptual circuit designs are studied. Finally, in order to prove the described concepts, the circuits were experimentally characterized and subsequently compared to other works in the literature.

The analysis covers key theoretical aspects regarding transmitter front-end circuits. It starts from the basic physical effects inside a transistor and ends with the design of high-swing modulator drivers. Furthermore, it comprises the fundamentals of optical modulators as well as the integration of the electrical driver with the modulator.

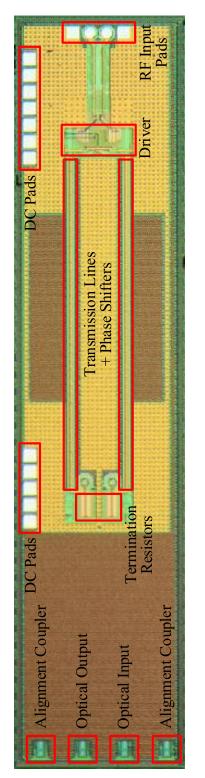

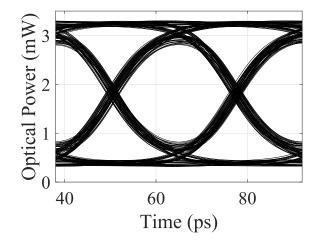

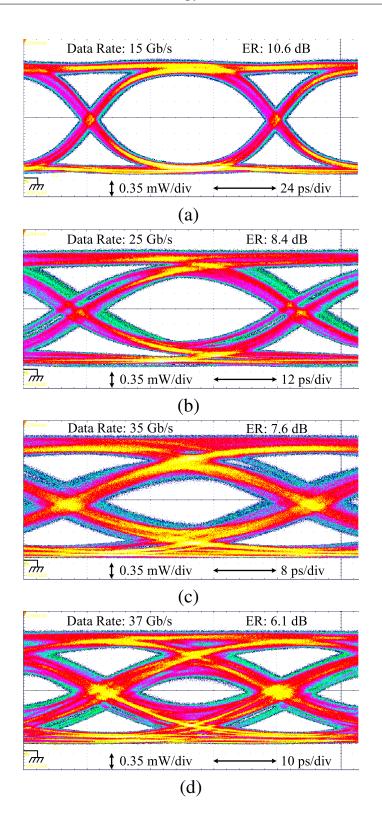

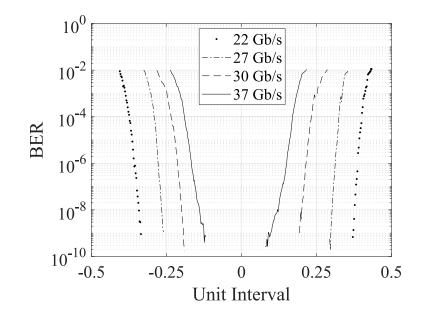

The concept of a basic monolithically integrated transmitter consisting of a Mach-Zehnder modulator (MZM) and an electrical driver is presented in Section 3.1. The circuit reaches a bit-error-free  $(10^{-10})$  data rate of 37 Gb/s, which is a record among other monolithically integrated transmitters reported in the literature. It was shown that by employing a high-swing driver, high extinction ratios (ER) can be achieved (namely 8.4 dB at 25 Gb/s and 7.6 dB at 35 Gb/s) while using short-length phase shifters (2 mm of length). It was therefore proved that one of the main drawbacks of the MZM-based transmitters, namely their large chip area, can be mitigated by using high-swing drivers, however without sacrificing the ER.

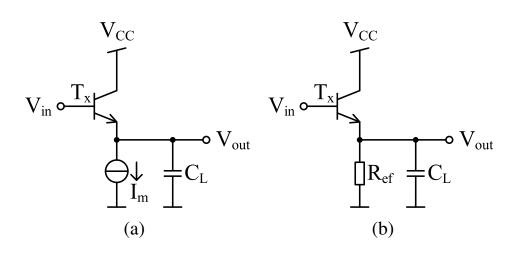

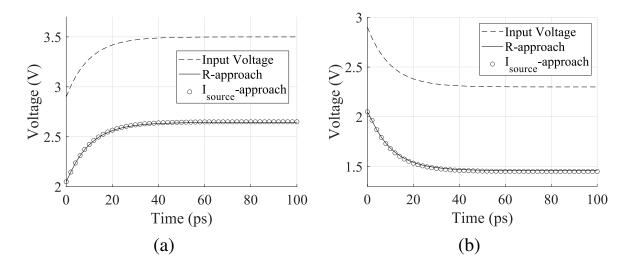

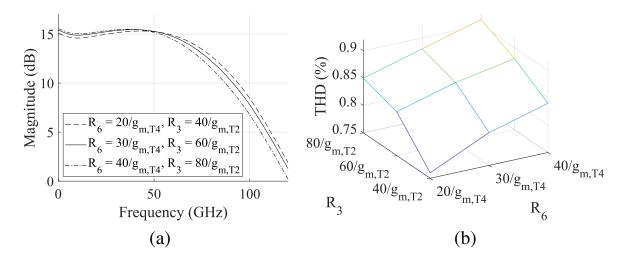

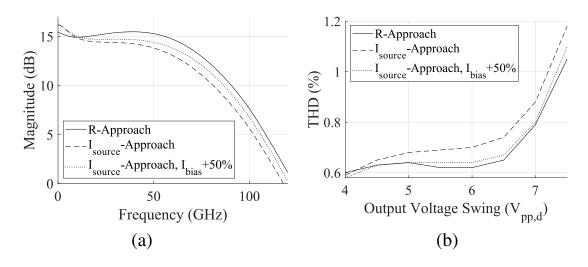

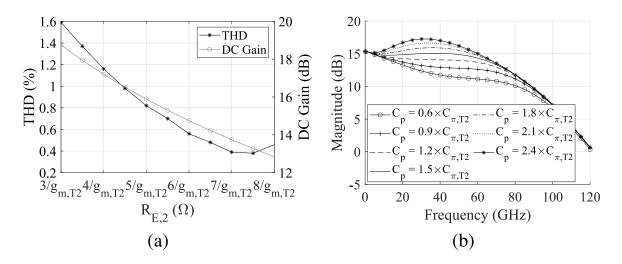

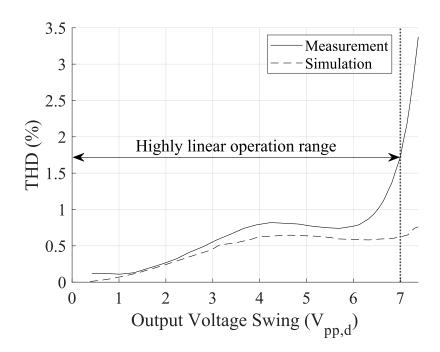

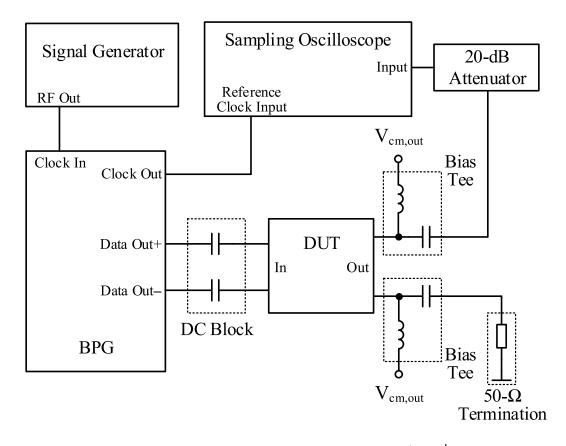

In Section 3.2, an improved modulator driver design was investigated, the focus of the study being the linearity. In addition to a high peak-to-peak differential output voltage swing of 7.2  $V_{pp,d}$ , the driver achieves record-low total harmonic distortion (THD) values of 1% (at 1 GHz, for the output swing of 6.5  $V_{pp,d}$ ) and 1.7% (at 1 GHz, for the output swing of 7  $V_{pp,d}$ ). Moreover, the driver reaches a bandwidth of 61.2 GHz and shows a high power efficiency

when relating its DC power consumption to its output voltage swing. The achievement of a high linearity and bandwidth without an increased power consumption is due to the fact that the bias currents of the emitter-follower (EF) stages are provided by means of resistors instead of the conventional current sources. The two approaches were first analyzed mathematically and subsequently compared by means of circuit simulations. It was shown that the proposed approach for the realization of the EFs – i.e. by means of resistors – allows a reduction of the DC power consumption by 19% compared to the current-source approach for an equivalent performance in terms of linearity and bandwidth.

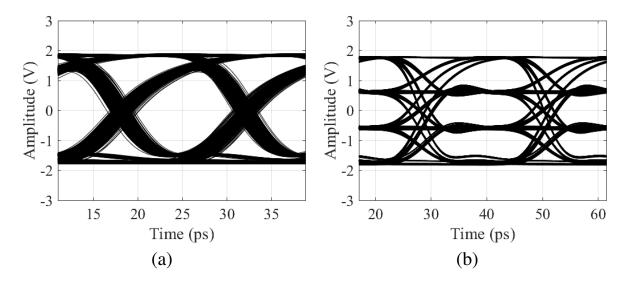

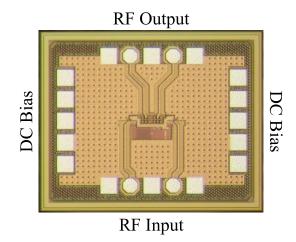

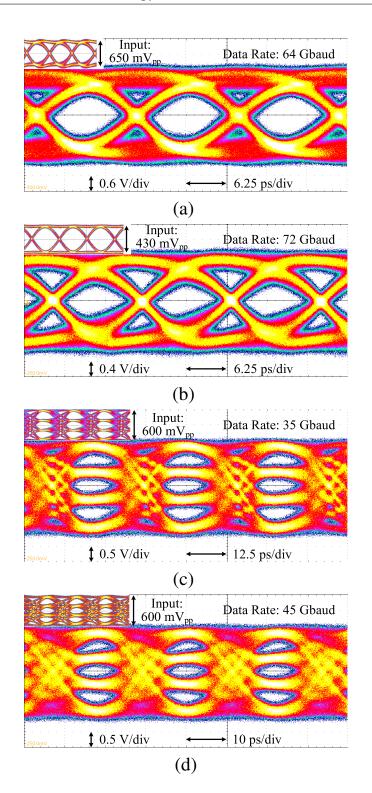

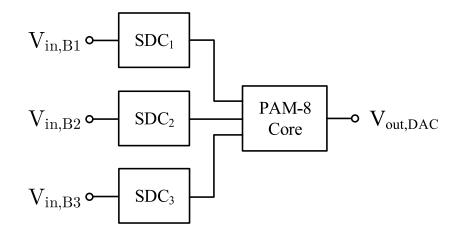

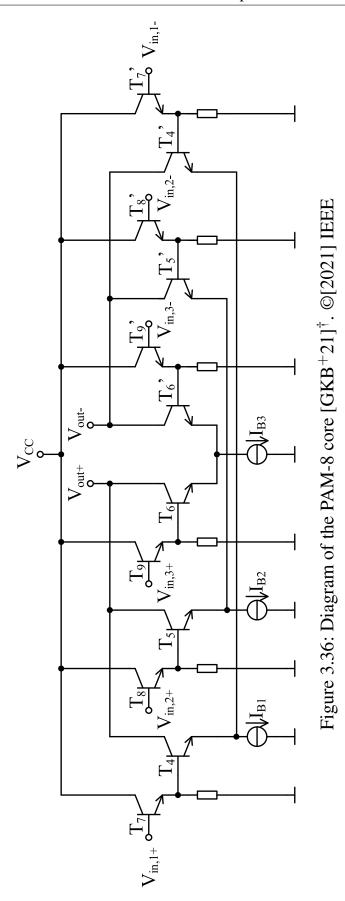

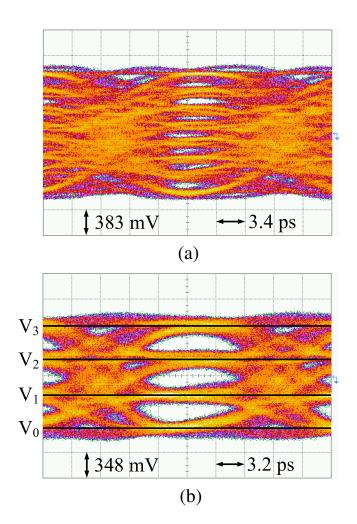

Finally, Section 3.3 studies a modulator driver concept suitable for higherorder modulation formats, namely the 8-level pulse amplitude modulation The circuit was realized as a 3-bit digital-to-analog converter (PAM-8). (DAC), thus being able to yield 8-level output signals. Moreover, the circuit is able to function as a PAM-4 driver as well, thanks to the tunable tail currents of the DAC core. It achieves a symbol rate of 50 Gbaud, which corresponds to a bit rate of 150 Gb/s for the PAM-8 modulation and 100 Gb/s for PAM-4. The study showed that a modulator driver can be realized that is able to switch between different modulation formats (namely PAM-8 and PAM-4), without requiring extra power or additional circuit parts. Moreover, the use of on-chip single-to-differential converters (SDCs) targets the relaxation of the requirements on the stages that precede the driver. Finally, relating its DC power consumption (590 mW, including the SDCs) to its output voltage swing (4  $V_{pp,d}$ ), the driver shows one of the highest power efficiencies among PAM modulator drivers in the literature.

# Zusammenfassung

Diese Arbeit umfasst Grundlagenforschung im Bereich von Transmitter-Front-End-Schaltungen für die elektro-optische Datenübertragung. Als Erstes werden die theoretischen Grundlagen dargestellt und analysiert. Darauf basierend werden konzeptionelle Schaltungsentwürfe untersucht. Um die beschriebenen Konzepte zu überprüfen, wurden die Schaltungen experimentell charakterisiert und anschließend mit anderen Arbeiten aus der Literatur verglichen.

Die Analyse beinhaltet theoretische Schlüsselaspekte bezüglich Transmitter-Front-End-Schaltungen. Sie umfasst die grundlegenden, physikalischen Effekte innerhalb eines Transistors bis hin zum Entwurf von Modulatortreibern mit hohen Spannungshüben am Ausgang. Sie beinhaltet zudem die Grundlagen von optischen Modulatoren sowie die Integration des elektrischen Treibers mit dem Modulator.

Das Konzept eines grundlegenden, monolithisch integrierten Transmitters bestehend aus einem Mach-Zehnder Modulator (MZM) und einem elektrischen Treiber ist im Abschnitt 3.1 vorgestellt. Die Schaltung erreicht eine bitfehlerfreie (10<sup>-10</sup>) Datenrate von 37 Gb/s, was ein Rekord unter den monolithisch integrierten Transmittern in der Literatur darstellt. Es wurde gezeigt, dass die Verwendung eines Treibers mit hohem Ausgangsspannungshub den Einsatz von kurzen Phasenschiebern (2 mm) ermöglicht, während hohe Extinktionsverhältnisse (ER) erreicht werden können (nämlich 8.4 dB bei 25 Gb/s und 7.6 dB bei 35 Gb/s). Es wurde demzufolge bewiesen, dass einer der Hauptnachteile von MZM-basierten Transmittern, nämlich ihre große Chipfläche, durch den Einsatz von Treibern mit hohen Ausgangsspannungshüben beachtlich verringert werden kann, ohne dabei das ER zu beeinträchtigen.

Im Abschnitt 3.2 wurde das Konzept eines verbesserten Modulatortreibers

untersucht, wobei der Schwerpunkt auf einer hohen Linearität lag. Zusätzlich zu einem hohen Spitze-Spitze-Wert der differentiellen Ausgangsspannung von 7.2 V<sub>pp,d</sub> zeigt der Treiber einen niedrigen Rekordwert für die gesamte harmonische Verzerrung (THD): 1% bei 1 GHz für den Ausgangshub von 6.5 V<sub>pp,d</sub> und 1.7% für 7 V<sub>pp,d</sub>. Außerdem erzielt der Treiber eine hohe Bandbreite von 61.2 GHz und weist eine hohe Effizienz auf, wenn der DC-Leistungsverbrauch auf den Ausgangsspannungshub bezogen wird. Die hohe Linearität und Bandbreite wurde erzielt, ohne dass ein erhöhter Leistungsverbrauch notwendig war. Das ist darauf zurückzuführen, dass die Biasströme für die Emitterfolger-Stufen der Schaltung anhand von Widerständen anstatt von Stromspiegeln bereitgestellt werden. Die zwei Ansätze wurden zuerst mathematisch analysiert und anschließnd durch Schaltungssimulationen verglichen. Es wurde gezeigt, dass der neue Ansatz zur Realisierung der Emitterfolger-Stufen - d.h. anhand von Widerständen - eine Verminderung des Leistungsverbrauchs um 19% im Vergleich zum herkömmlichen Ansatz mit Stromspiegeln ermöglicht. Diese Verringerung des Leistungsverbrauchs setzt keine Verschlechterung der Linearität oder Bandbreite voraus.

Letztlich wurde im Abschnitt 3.3 das Konzept eines Modulatortreibers erforscht, das für Modulationsverfahren höherer Ordnung geeignet ist, und zwar für die achtstufige Pulsamplitudenmodulation (PAM-8). Die Schaltung wurde als 3-Bit Digital-Analog-Umsetzer (DAC) realisiert und kann achtstufige Ausgangssignale ausgeben. Zudem kann die Schaltung aufgrund der einstellbaren Fußpunktströme des DAC-Kerns auch als ein PAM-4-Treiber fungieren. Es wurde eine Symbolrate von 50 Gbaud erreicht, was einer Bitrate von 150 Gb/s für die PAM-8-Modulation und 100 Gb/s für die PAM-4-Modulation entspricht. Die Untersuchung hat gezeigt, dass ein Modulatortreiber realisiert werden kann, der zwischen verschiedenen Modulationsverfahren (nämlich PAM-8 and PAM-4) umschalten kann, ohne dass mehr Leistungsverbrauch oder zusätzliche Schaltungsteile notwendig sind. Zudem erlaubt die Verwendung von on-chip Eintakt-Gegentakt-Umsetzern die Vereinfachung der Anforderungen für die Vorstufen. Letztlich zeigt das Verhältnis zwischen DC-Leistungsverbrauch (590 mW, einschließlich der Eintakt-Gegentakt-Umsetzer) und Ausgangsspannungshub (4 Vpp,d), dass die Schaltung zu den energieeffizientesten PAM-Modulatortreibern in der Literatur zählt.

#### Note on the Use of IEEE Material from Own Publications

The contents of section 1.2 of chapter 1, section 2.6 of chapter 2 as well as chapter 3 are largely based on published IEEE papers where I was the first author. The papers were published during my doctoral research work at Technische Universität Dresden. All these papers are referenced accordingly. A list of these publications is available at the end of the thesis, in the section called "Own Publications". When citing the figures and tables from the own publications, a special symbol (<sup>†</sup>) was used in order to distinguish them from other citations in the thesis. Finally, a footnote at the beginning of each chapter or section mentioned above was introduced, which specifies the own publication on which the respective chapter or section is based.

# Contents

| 1 | Intr | oductio                                      | n                                               | 1  |

|---|------|----------------------------------------------|-------------------------------------------------|----|

|   | 1.1  | Electro-Optical Communication                |                                                 |    |

|   | 1.2  | 2 Scientific Context and Open Challenges     |                                                 |    |

|   |      | 1.2.1                                        | MZM-Based Electro-Optical Transmitters          | 3  |

|   |      | 1.2.2                                        | MZM Drivers                                     | 5  |

|   | 1.3  | Object                                       | tives and Structure of the Thesis               | 6  |

| 2 | The  | ory and                                      | I Fundamentals of Electro-Optical Transmitters  | 9  |

|   | 2.1  | Electro                                      | o-Optical Communication Systems                 | 9  |

|   | 2.2  | Bipola                                       | ar Junction Transistor                          | 13 |

|   | 2.3  | Basic                                        | Amplifiers                                      | 18 |

|   |      | 2.3.1                                        | Common-Emitter Amplifier                        | 19 |

|   |      | 2.3.2                                        | Common-Base Amplifier                           | 22 |

|   |      | 2.3.3                                        | Common-Collector Stage                          | 24 |

|   |      | 2.3.4                                        | Comparison of the Basic Amplifier Topologies    | 27 |

|   |      | 2.3.5                                        | Common-Emitter with Current-Type Negative Feed- |    |

|   |      |                                              | back                                            | 28 |

|   |      | 2.3.6                                        | Cascode Amplifier                               | 30 |

|   |      | 2.3.7                                        | Differential Amplifier                          | 35 |

|   | 2.4  |                                              |                                                 |    |

|   |      | 2.4.1                                        | Physics of the Transistor Breakdown Process     | 39 |

|   |      | 2.4.2                                        | Circuit Concept                                 | 40 |

|   |      | 2.4.3                                        | Circuit Analysis                                | 42 |

|   | 2.5  | Mach-Zehnder Modulator                       |                                                 |    |

|   | 2.6  | Concepts of MZM-Based Transmitter Front-Ends |                                                 |    |

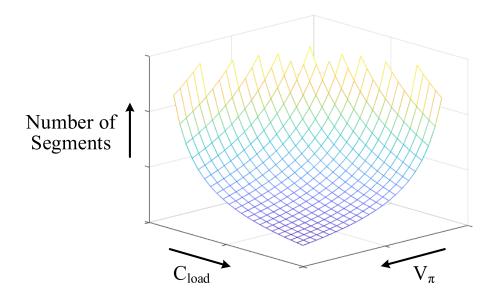

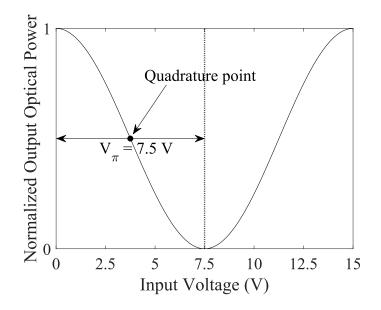

|   |      | 2.6.1                                        | Segmented Transmitter Front-End Topology        | 50 |

|   |      | 2.6.2                                        | Traveling-Wave Front-End Topology               | 52 |

|                  |                                                        | 2.6.3                                                  | Comparison Study between Segmented and Traveling-        |     |

|------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|-----|

|                  |                                                        |                                                        | Wave Topologies                                          | 53  |

| 3                | Con                                                    | ceptual                                                | Circuit Implementations                                  | 57  |

|                  | 3.1                                                    | A Mo                                                   | nolithically Integrated Electro-Optical Transmitter in a |     |

|                  |                                                        | Si Pho                                                 | otonics 250-nm BiCMOS Technology                         | 58  |

|                  |                                                        | 3.1.1                                                  | Introduction                                             | 58  |

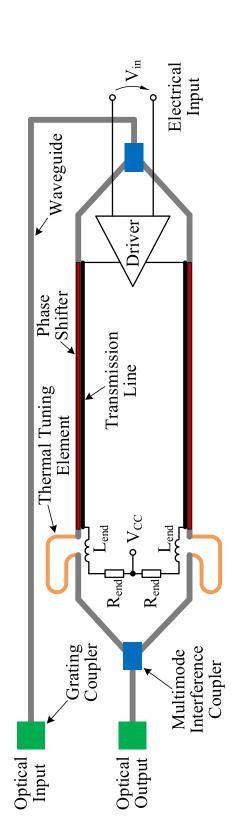

|                  |                                                        | 3.1.2                                                  | Circuit Design                                           | 59  |

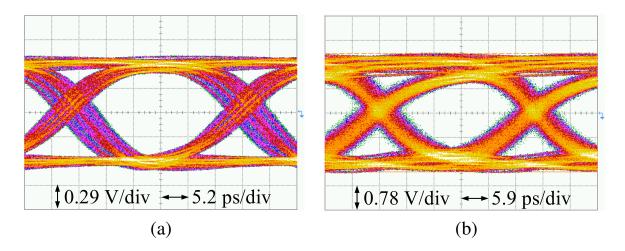

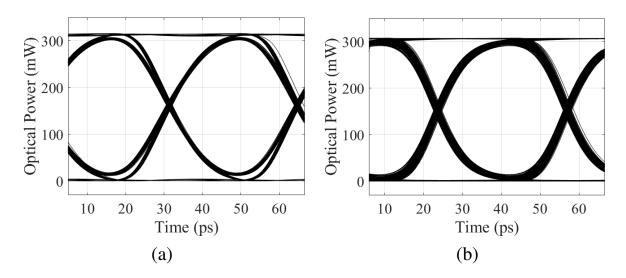

|                  |                                                        | 3.1.3                                                  | Experimental Characterization                            | 68  |

|                  |                                                        | 3.1.4                                                  | Achievements of the Basic Scientific Research            | 73  |

|                  | 3.2                                                    | 3.2 A Linear, High-Swing and Power-Efficient Modulator |                                                          |     |

|                  |                                                        | in a 13                                                | 30-nm SiGe BiCMOS Technology                             | 76  |

|                  |                                                        | 3.2.1                                                  | Introduction                                             | 76  |

|                  |                                                        | 3.2.2                                                  | Circuit Design                                           | 76  |

|                  |                                                        | 3.2.3                                                  | Experimental Characterization                            | 87  |

|                  |                                                        | 3.2.4                                                  | Achievements of the Basic Scientific Research            | 94  |

|                  | 3.3 A PAM-8 Modulator Driver Implemented as a Digital- |                                                        | A-8 Modulator Driver Implemented as a Digital-to-Analo   | g   |

|                  |                                                        | Conve                                                  | rter                                                     | 97  |

|                  |                                                        | 3.3.1                                                  | Introduction                                             | 97  |

|                  |                                                        | 3.3.2                                                  | Circuit Design                                           | 98  |

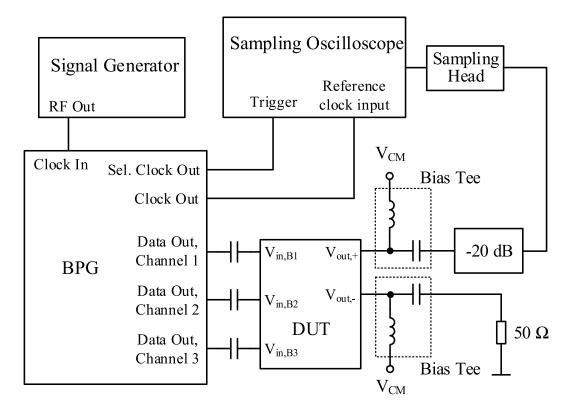

|                  |                                                        | 3.3.3                                                  | Experimental Characterization                            | 102 |

|                  |                                                        | 3.3.4                                                  | Achievements of the Basic Scientific Research            | 104 |

| 4                | Con                                                    | clusion                                                | and Further Research                                     | 107 |

| Own Publications |                                                        |                                                        |                                                          |     |

| Re               | References<br>List of Abbreviations                    |                                                        |                                                          |     |

| Li               |                                                        |                                                        |                                                          |     |

| Li               | st of S                                                | Symbol                                                 | S                                                        | 125 |

| Li               | st of ]                                                | Figures                                                |                                                          | 129 |

| Li               | st of '                                                | Tables                                                 |                                                          | 135 |

# **1** Introduction

### **1.1 Electro-Optical Communication**

In the last decades, the data volume in the worldwide networks has been growing sharply, and this trend is currently accelerating with the development of the Internet of Things and other big data applications. Therefore, there is a high motivation for research on faster, low-loss and high-reliable channels of communication.

Attempts to use light as a data carrier date back to the 19th century, however it is only in the 1970s that low-loss transmission through optical fibers has been achieved. Thus, in 1970, light transmission with a loss of less than 20 dB/km was demonstrated. In 1975, this figure was improved to 4 dB/km and in 1979 to 0.2 dB/km [Raz03], which allows reliable data transmission over an optical medium.

At the present day, the optical fibers, as communication medium, offer a series of advantages compared to the traditional copper cables. First, they show a higher bandwidth as well as lower losses, thus being suitable for high-speed data transmission over long distances [Raz03]. Second, they are not susceptible to electromagnetic interference. Third, they are lighter, thinner and have lower production costs. Finally, they provide a higher degree of security, since they cannot be intercepted by means of tapping.

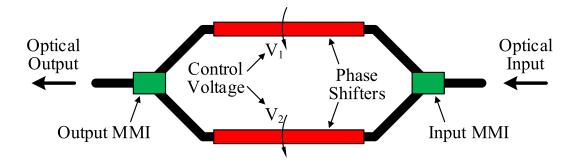

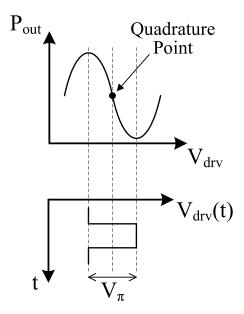

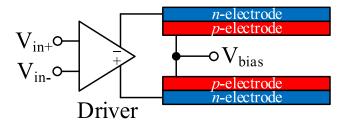

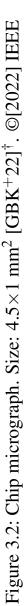

A key part in the realization of electro-optical transmission is the conversion of electrical data into optical data. This implies the modulation of an optical carrier signal by an electrical data signal. This can be done either directly, by modulating the laser source with an electrical signal, or indirectly, by means of optical modulators, which in turn modulate the laser. The Mach-Zehnder optical modulators (MZM) are one of the most popular modulator types used in electro-optical transmitters, since they provide high speed, wide optical spectra and low thermal sensitivity [XLX<sup>+</sup>14]. The input of these modulators is the light coming from a continuously emitting laser source. The modulation is realized by means of phase shifting of the light waves in the two modulator arms. This phase shift occurs as a result of the applied voltage provided by an electrical driver. Subsequently, the light waves are being recombined, thus realizing a logical "1" if the recombination is constructive, or a logical "0" if the recombination is destructive. A more detailed insight into the functioning of an MZM is provided in Section 2.5.

There are several integration methods for realizing electro-photonic communication systems. The most straightforward way is to fabricate all components separately (and in different materials) and subsequently assemble them. While no special manufacturing techniques are required, this method implies several fabrication processes as well as long interconnections between the electrical and optical components. Another method of integration is the hybrid one, which makes use of silicon (Si) photonic technologies, where the optical components are fabricated on a Si substrate. Such technologies (also known as photonic integrated circuit technologies, or PIC) offer advantages in terms of high-yield, volume and low-cost manufacturing, as well as higher integration capabilities. Nevertheless, the electrical and optical components are realized separately and their integration require additional fabrication steps as well as long interconnections. A particularly promising way of fabricating electro-photonic communication systems is the monolithic integration of electronic and photonic components on the same Si chip (with the exception of laser diodes, which up to this date could not be successfully integrated on a Si chip). Several such technologies have been presented in the literature [KLB<sup>+</sup>15] [ASG<sup>+</sup>12]. Also known as electro-photonic integrated circuit (EPIC) technologies, this way of integration shows two main advantages in comparison to the hybrid integration. First, the interconnections between the optical and the electrical components are reduced to a minimum length, thus enabling high-speed performance [PLL+16]. Second, it offers a good approach to decreasing manufacturing costs as well as to enable mass production [ASG+12], since the chips are produced in one single fabrication process.

For the purpose of increasing the data volume that can be transmitted via

the telecommunication networks, several modulation formats have been investigated. In recent times, coherent transmission techniques became particularly attractive [NWY<sup>+</sup>20], since they use both amplitude and phase modulation and thus multiply the number of bits that can be sent within one symbol. By means of such modulation schemes (called quadrature amplitude modulation, or QAM), systems with data rates as high as 400 Gb/s are being realized [Miy16]. However, such systems, as well as the modulation format itself, pose very high requirements on the integrated electric drivers of the electrooptical assemblies. The modulator drivers are therefore expected to have a high bandwidth for high-speed operation, a high linearity to avoid harmonic distortions, a high output voltage swing for an efficient driving of the optical modulator, and finally a low power consumption. Fulfilling all these requirements simultaneously represents a considerable challenge for the driver design.

## **1.2 Scientific Context and Open Challenges<sup>1</sup>**

This section presents an overview of the state of the art in the field of MZMbased electro-optical transmitters and of electrical modulator drivers in particular. We present the latest and most relevant designs reported in the literature, as well as their performance and trade-offs.

#### **1.2.1 MZM-Based Electro-Optical Transmitters**

Several designs of MZM-based electro-optical transmitters have been reported in the scientific literature, realized either by means of monolithic integration (excluding the laser) or by hybrid integration techniques (i.e. wire bonding or flip-chip). In [RLP<sup>+</sup>16] and [PRL<sup>+</sup>16], transmitters realized in a cointegrated electro-photonic technology were presented. The designs reached high extinction ratios (ER) of 13 dB and 11 dB, respectively, and symbol rates of 28 Gbaud and 32 Gbaud, respectively. Since the electrical drivers provided only a limited peak-to-peak differential output swing (4 V<sub>pp,d</sub> and

<sup>1</sup> **Copyright Note**: Section 1.2 of Chapter 1 is largely based on the descriptions of the state of the art from the IEEE publications  $[GBK^+22]^{\dagger}$  and  $[GKB^+22]^{\dagger}$ , in which I was the first author.

3.5  $V_{pp,d}$ , respectively), phase shifters with a length of 6.05 mm each had to be employed in order to ensure the high ERs. This led to a significant chip area. The power consumption was considerable as well (2 W and 1.8 W, respectively). Another transmitter making use of monolithic integration of the optical and electrical components was presented in [XGP<sup>+</sup>15]. The transmitter employed a CMOS driver and consumed a much less amount of DC power, namely 270 mW. The circuit was also more compact than the previously mentioned designs, since the MZM's phase shifters were only 3 mm long. Nevertheless, the short phase shifter length as well as the limited driver output swing  $(2.2 V_{pp,d})$  led to a lower ER (6.3 dB). The transmitter achieved a symbol rate of 28 Gbaud. In [YSM<sup>+</sup>18], a design using hybrid integration, namely the flip-chip technique, was shown. The circuit achieved a high symbol rate of 50 Gbaud and a good ER of 8 dB, while employing 4-mm long phase shifters and consuming 553 mW of DC power. Other transmitters using hybrid integration methods were presented in [TMR<sup>+</sup>16] (integration by means of flip-chip) and [BRG<sup>+</sup>20] (integration by means of wire bonding). These circuits achieved high symbol rates (56 Gbaud and 53 Gbaud, respectively) and featured a low power consumption (300 mW and 386 mW, respectively). However, due to the limited output voltage swing of the electrical drivers (1.6  $V_{pp,d}$  and 2  $V_{pp,d}$ , respectively) and because of the short phase shifter lengths (3.15 mm and 3.45 mm, respectively), the circuits achieved low ERs (2.5 dB and 4.5 dB, respectively). A design employing wire bonding was presented in [LQL<sup>+</sup>20]. The transmitter achieved a high ER of 9.6 dB with a compact MZM design featuring 3-mm long phase shifters. The circuit had nevertheless a limited symbol rate (25 Gbaud) and consumed a high amount of DC power (1.34 W).

An open research topic in the field of electro-optical transmitters that was not thoroughly investigated in the literature is the realization of compact monolithically integrated assemblies capable of reaching high symbol rates and high ERs. Nevertheless, the compactness and speed are one of the main advantages of the monolithic integration compared to its hybrid counterpart, since the assemblies are supposed to be realized on the same Si chip, without long interconnections between the electrical and optical components that limit the data rate and without extra bond wires or flip-chip bumps, which require additional floorplanning for the chip layout.

#### **1.2.2 MZM Drivers**

Next, an overview of the latest MZM driver designs reported in the literature is presented. The focus is on circuits with high output voltage swing, but also high bandwidth and high linearity, since these are the main requirements for future coherent electro-optical communication systems. For the purpose of maximizing the ER that can be achieved at the MZM output, a high-swing driver employing the breakdown voltage doubler topology was proposed in [AML<sup>+</sup>20]. The circuit reached a high output voltage swing of 6 V<sub>pp,d</sub>, however it had a limited bandwidth of only 40 GHz as well as a high power consumption of 1 W. Moreover, it showed an average linearity, with a total harmonic distortion (THD) of 3.6% measured at 1 GHz and for the full output swing. A high voltage swing was also achieved in [RJA+19], namely 4.9 V<sub>pp,d</sub>, by using the cascode topology in the output stage. The circuit also showed a high bandwidth of 86.8 GHz. However, this was achieved by means of inductive peaking, which considerably increases the circuit layout size. At 10 GHz and for 2.5  $V_{pp,d}$  output swing, the driver showed a THD of 5%, which indicates a low linearity. The power consumption of the circuit was 1.2 W, which is considerable. In [ZSV17], a driver with lower power consumption was presented, namely 820 mW, while reaching a comparable output voltage swing (4.8 V<sub>pp,d</sub>). However, the bandwidth was limited to 57.5 GHz. The driver employed a MOS-HBT cascode topology. Its THD at 10 GHz and for 2.5 V<sub>pp,d</sub> output swing was 2.5%. A driver using the distributed amplifier topology was shown in [BHSV17]. It achieved a high bandwidth of 70 GHz, a high linearity (THD was 2% at 4 GHz for 4.5 V<sub>pp,d</sub> output swing) as well as a high differential gain of 20 dB. Nevertheless, it showed a high power consumption of 1.1 W. The design shown in  $[RGA^+17]$  made use of the distributed amplifier topology as well and reached a high bandwidth of 90 GHz. The circuit had a limited output voltage swing, namely 4  $V_{pp,d}$ , as well as a low linearity (the THD was 5% at 1 GHz for 3  $V_{pp,d}$  output swing). A very high bandwidth of 110 GHz was achieved in [NWY<sup>+</sup>20] by means of a bandwidth doubler topology using a 2:1 analog multiplexer. However, the

design had a very low output voltage swing (1.5  $V_{pp,d}$ ), which makes the use of long-length phase shifters unavoidable in order to reach a high ER at the MZM output. Moreover, the circuit had an average linearity, with a THD of 3% at 1 GHz for the full output swing, while the power consumption was considerable (990 mW). In order to minimize the power consumption, the designs presented in [NNT<sup>+</sup>17] and [JNO<sup>+</sup>20] employed the stacked current mode architecture as well as an open-drain topology. Thus, the circuits showed a power consumption of only 180 mW and 225 mW, respectively. Nevertheless, the designs had limited output voltage swings (2  $V_{pp,d}$  and 1.5  $V_{pp,d}$ , respectively), bandwidths of 56 GHz and 48 GHz, respectively, and THD values of 3.8% and 2.2%, respectively, at 1 GHz and for the maximum output voltage swings. In [NBNM13] and [WNY<sup>+</sup>14], two highly linear drivers were presented with THDs as low as 1.2% and 1.1%, respectively, at 1 GHz and for the full output swing. Both circuits used a cascode topology with resistive emitter degeneration. Nevertheless, the designs showed very low bandwidths (37.8 GHz and 22 GHz, respectively) as well as low output voltage swings (3 V<sub>pp,d</sub> each).

As it can be seen, the modulator driver designs reported in the literature show either a high bandwidth, a high output voltage swing or a high linearity. An unresolved challenge is the optimization of the driver design with the purpose of maximizing all these parameters at the same time, while keeping the power consumption as low as possible. Moreover, the output voltage swing of the driver is of particular importance, since for MZM-based assemblies a high-swing driver allows the use of short-length phase shifters without sacrificing the modulator's ER, thus being an essential feature for compact electro-optical transmitters.

### **1.3 Objectives and Structure of the Thesis**

In this thesis, we address the basic scientific research in the field of circuits and systems for electro-optical communication networks, with focus on MZM-based electro-optical transmitters. We describe the underlying theory, we establish the concepts for our work, and finally we prove these concepts by means of chip implementations and their experimental verification. The first circuit concept that we propose is a monolithically integrated electro-optical transmitter front-end consisting of an MZM and an electrical driver. The design targets the realization in an EPIC-type technology of a compact and high-speed electro-photonic assembly by employing a short-length MZM, however without sacrificing the ER. This was achieved by co-integrating the MZM with a high-swing electrical driver, which uses the break-down voltage doubler topology [MH04] and thus overcomes the physical limitations of the output transistors regarding the maximum allowed output voltage swing.

Second, a similar driver architecture is investigated and subsequently enhanced. Thus, the concept of an MZM driver design is presented, which simultaneously achieves a high output voltage swing, a high linearity as well as a high bandwidth. Moreover, the driver has a low power consumption thanks to a new implementation approach for its emitter-follower stages, where the bias currents are provided by resistors instead of traditionally used current sources.

Finally, in order to increase the amount of data that can be sent for a given bandwidth, we study the concept of a non-linear DAC-based modulator driver design capable of yielding PAM-8 output signals. Furthermore, depending on the given requirements, the circuit can operate as a PAM-4 driver as well. This switching capability between two modulation formats does not come at the expense of additional power consumption or circuit complexity.

The thesis is structured as follows. Chapter 2 introduces the basic theoretical concepts of the electrical and optical design of MZM-based transmitters, with focus on the transmitter front-ends. Chapter 3 presents the proposed chip implementations, which are based on the theory described in Chapter 2. The successful experimental characterization of these circuits proves the concepts introduced in Chapter 2. Finally, Chapter 4 draws up the conclusion of the thesis and offers an outlook on the future research work.

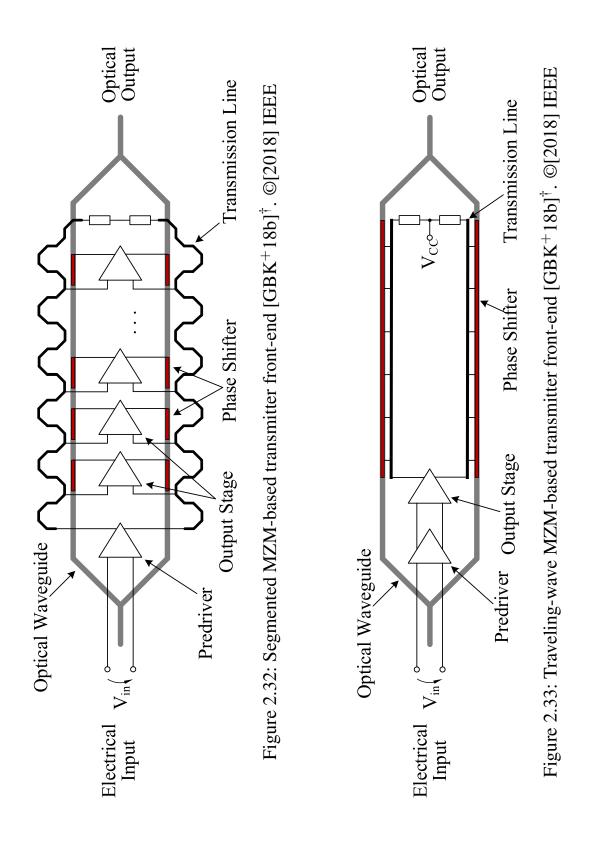

# 2 Theory and Fundamentals of Electro-Optical Transmitters

In this chapter, an overview of the basic theoretical concepts for the design of electro-photonic transmitters is outlined. First, a general view over the electro-optical communication systems is provided including a short presentation of the building blocks on the transmitter and the receiver side. Next, the design of electrical modulator drivers is addressed. We first describe the working principles of bipolar transistors, since they are the basic active components of all circuits that are going to be presented in this thesis. Afterwards, the common-emitter stage is described. Subsequently, the cascode amplifier is presented as an enhancement of the common-emitter stage. Next, the breakdown voltage doubler architecture is explained, since this topology was mainly preferred for the chip implementation of the modulator drivers presented in this thesis. Finally, the fundamentals of Mach-Zehnder optical modulators are presented and explained. The chapter is concluded by a description of two ways of implementing MZM-based electro-optical transmitters, namely the segmented and the traveling-wave topology.

## 2.1 Electro-Optical Communication Systems

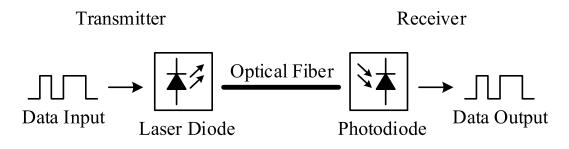

A basic electro-optical communication system consists of three elements: a transmitter, where electrical data is modulated and converted to optical data; an optical fiber, which serves as a medium for the transfer of data; and a receiver, where optical data is converted back to electrical data. The basic diagram of such a system is shown in Fig. 2.1. On the transmitter side, there are two approaches for converting electrical signals to optical signals. The first approach is the direct modulation, where a laser diode is used to convert the

Figure 2.1: Basic electro-optical communication system.

electrical pulses (in form of electric current) coming from a laser driver into optical pulses. Thus, the laser diode outputs a light signal with an intensity that depends on the current provided by the laser driver. The second approach is the indirect modulation. Here, a continuous emitting laser source is used in combination with an optical modulator. The continuous light wave coming from the laser diode is provided to the modulator, which outputs it with different intensities, depending on the voltage that is applied to the modulators' electrodes by an electrical driver. For both approaches, the signal transmitted over the optical fiber is a digital waveform with several amplitude levels and phase shifts, depending on the chosen modulation scheme.

When transmitting data over large distances, several challenges appear, mainly due to chromatic dispersion and non-linear effects within the optical fibers [Agr18]. Therefore, special circuitry is required both on the transmitter side as well as on the receiver side in order to ensure reliable data transfer.

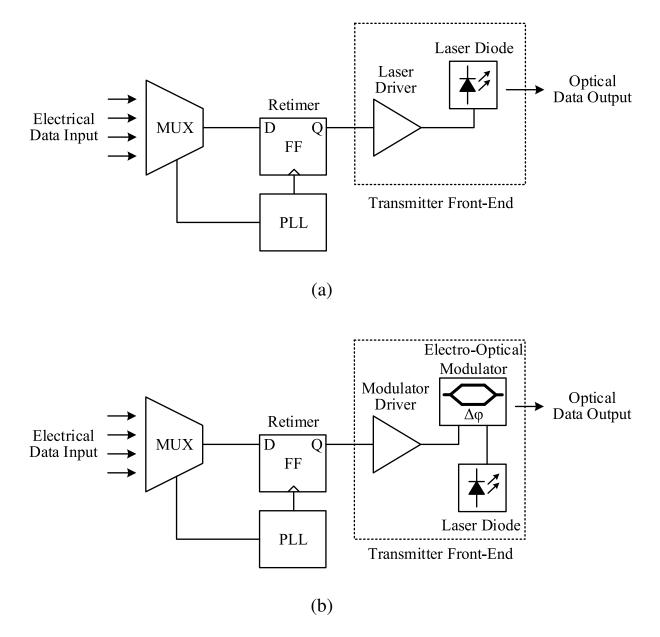

Fig. 2.2 depicts the basic block diagram of a transmitter of an optical communication system for direct (a) and indirect (b) modulation, respectively [Raz03]. First, the electrical data coming from multiple users via several parallel channels has to be converted into a single data stream. This process of parallel-to-serial conversion is done by means of a multiplexer (MUX). A MUX requires a certain number of clock frequencies with very precise phase alignment. A plain oscillator would not suffice to this task, since it is prone to process variations, jitter, temperature and aging. Therefore, a phase-locked loop (PLL) is employed, which offers a stable and synchronized output by means of a feedback loop. As the MUX usually shows jitter and intersymbol interference, a re-timer flip-flop (FF) is also employed which ensures a clean MUX output [Raz03].

Figure 2.2: Transmitter block diagram of an electro-optical communication system for (a) direct modulation and (b) indirect modulation.

The front-end of the transmitter is constituted either by a laser driver and a laser diode, in case of direct modulation (Fig. 2.2 (a)), or by a modulator driver, an optical modulator and a laser, in case of indirect modulation (Fig. 2.2 (b)). The purpose of the transmitter front-end is to amplify the electrical data coming from the MUX and to convert it into optical data with a sufficient output optical power in order to be transmitted over a certain dis-

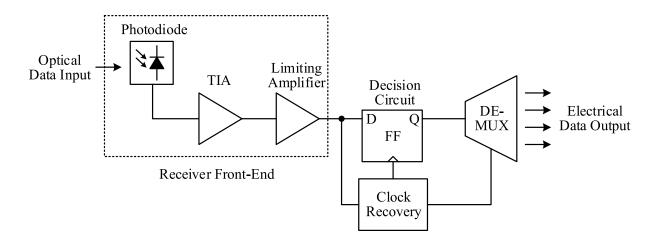

Figure 2.3: Receiver block diagram of an electro-optical communication system.

tance. In the case of direct modulation, the laser driver has to provide a certain amount of output current to the laser diode, depending on the current-voltage characteristics of the laser. This represents a challenge since the maximum collector current that a transistor is able to switch at high frequencies is related to its size. Thus, for high laser currents, large transistor sizes with high parasitic capacitances are required, which restrict the achievable bandwidth. On the other hand, if indirect modulation is used, a modulator driver has to provide a sufficiently high output voltage swing in order to efficiently drive the optical modulator. This poses a challenge to the driver design, since the maximum output voltage swing is restricted by the technology-given breakdown voltage of the transistors.

In Fig. 2.3, the block diagram of a receiver for optical communication systems is illustrated [Raz03]. The incoming optical signal from the transmitter is converted into electrical signal by means of a photodiode. The photodiode output current is then converted into voltage by means of a transimpedance amplifier (TIA). Since the light wave arriving at the receiver is considerably attenuated, the photodiode usually outputs a low current. Therefore, a high amplification and a high signal-to-noise ratio (SNR) are among the main requirements of the TIA. A limiting amplifier further amplifies the TIA's output. Next, a flip-flop cell is employed in order to cancel the noise in the signal and to ensure a clean waveform, where the digital levels are clearly distinguish-

able. For this reason, this flip-flop cell is called a decision circuit [Raz03]. In order to generate the clock for the components of the receiver, a clock recovery cell is employed. This circuit recovers the frequency of the transmitter's PLL based on the received bit stream. Finally, a demultiplexer (DEMUX) is used at the output of the receiver in order to restore the initial electrical channels that were merged by the transmitter's MUX.

### **2.2 Bipolar Junction Transistor**

The transistor is the basic active component of any amplifier circuit. A bipolar junction transistor (BJT) can be regarded as a voltage controlled current source, since it outputs a current depending on its input voltage. Usually, bipolar transistors are used for high-frequency applications and for circuits requiring a high-current-driving capability. In comparison, the field-effect transistors (FET) are preferred for low-power applications and for circuits that require a high input impedance [SS16].

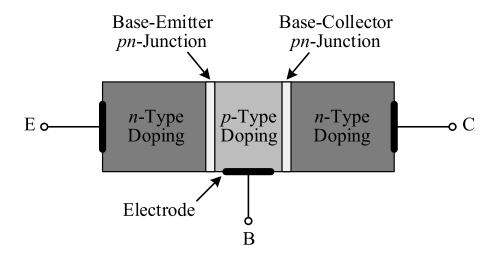

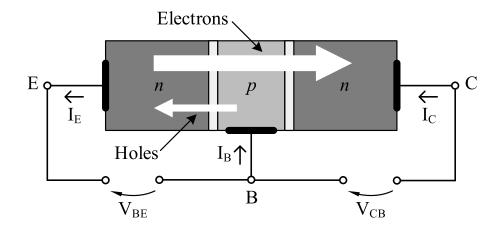

Fig. 2.4 shows the basic structure of an *npn*-type bipolar transistor [SS16]. It consists of three regions that are differently doped. The emitter and the collector region are doped with electrons (*n*-type doping), while the base region is doped with holes (*p*-type doping). The three regions correspond to the three terminals of a BJT: the base (B), the emitter (E) and the collector (C). When

Figure 2.4: Basic structure of an *npn* bipolar transistor.

Figure 2.5: Working principle of an *npn* bipolar transistor.

a voltage  $V_{BE}$  is applied over the base and the emitter of the BJT (Fig. 2.5), the base-emitter *pn*-junction becomes forward biased and starts conducting a current (the emitter current  $I_E$ ): the holes from the base region are injected into the emitter, while the electrons from the emitter region are injected into the base. We also assume a positive voltage  $V_{CB}$  applied over the collector and the base of the BJT. Since the emitter is much highly doped than the base, the electron current largely dominates the hole current [SS16]. Next, the electrons injected from the emitter into the base diffuse throughout the base in the direction of the collector due to the concentration gradient. Since the base is only lightly doped, only a few electrons are lost by recombination [SS16]. As the voltage potential at the collector of the transistor  $V_C$  is higher than the potential  $V_B$  at the transistor's base, the electrons injected into the base diffuse further into the collector region, thus forming the transistor's collector current  $I_C$ .

The collector current  $I_C$ , which constitutes the transistor's output current, can be expressed in terms of the base-emitter voltage  $V_{BE}$  (which can be seen as the transistor's input voltage) by means of the following equation [SS16]:

$$I_C = I_S e^{\frac{V_{BE}}{V_T}} \tag{2.1}$$

where  $I_S$  is the saturation current of the transistor and  $V_T$  the thermal voltage, defined as:

$$V_T = \frac{kT}{q} \tag{2.2}$$

where k is the Boltzmann constant, T the absolute temperature and q the elementary charge of an electron.

The base current  $I_B$  is proportional to  $e^{\frac{V_{BE}}{V_T}}$  as well [SS16] and can thus be expressed in terms of the collector current  $I_C$  by means of the following equation:

$$I_B = \frac{I_C}{B_i} \tag{2.3}$$

Therefore, the parameter  $B_i = I_C/I_B$  is considered to be the current gain of the bipolar transistor [SS16].

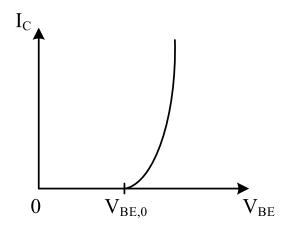

Based on equation (2.1), the  $I_C$ - $V_{BE}$  relation of a BJT can be represented graphically as in Fig. 2.6. As it can be seen, the collector current  $I_C$  starts rising exponentially after a certain threshold voltage  $V_{BE,0}$ . This behavior is similar to the current-voltage characteristic of a diode.

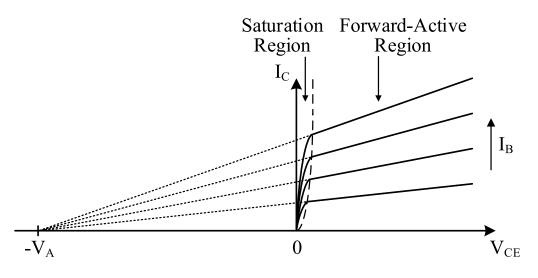

Ideally, the collector current  $I_C$  does not change with the collector-emitter voltage  $V_{CE}$ , since the transistor is supposed to be an ideal current source. Nevertheless, due to the Early effect,  $I_C$  does show a slight linear increase with  $V_{CE}$  for a certain base current  $V_B$ . Fig. 2.7 shows the dependence of  $I_C$  on  $V_{CE}$  for different  $I_B$  currents. The two main operating regions of the transistor,

Figure 2.6:  $I_C$  dependence on  $V_{BE}$  for an *npn*-type BJT.

Figure 2.7:  $I_C$  dependence on  $V_{CE}$  for different  $I_B$ . *npn*-type BJT.

namely the saturation and the forward-active region are also highlighted.

The linear increase of  $I_C$  with  $V_{CE}$  due to the Early effect can be expressed by inserting a factor  $(1 + \frac{V_{CE}}{V_A})$  in equation (2.1), where  $V_A$  is the Early voltage (as depicted in Fig. 2.7) [SS16]. Thus, equation (2.1) becomes:

$$I_C = I_S e^{\frac{V_{BE}}{V_T}} \left( 1 + \frac{V_{CE}}{V_A} \right) \tag{2.4}$$

Small-signal wise, the slope of the  $i_C$ - $v_{CE}$  function (in the forward-active region) can be regarded as the small-signal output resistance  $r_o$  of the bipolar transistor and is calculated using the following formula [SS16]:

$$r_o = \left(\frac{\delta i_C}{\delta v_{CE}}\Big|_{v_{BE}=constant}\right)^{-1}$$

(2.5)

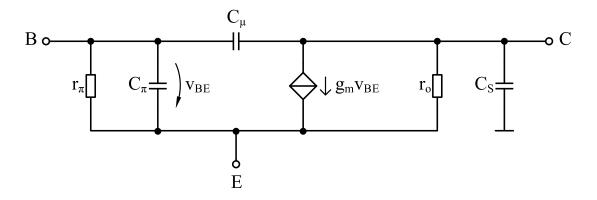

Based on the knowledge acquired so far and taking into account the main parasitic effects, the equivalent small-signal model of an *npn*-type bipolar transistor in the forward-active region can be drawn (Fig. 2.8). It consists of the input resistance  $r_{\pi}$  (between the base and the emitter), the capacitance  $C_{\pi}$  of the base-emitter *pn*-junction, the capacitance  $C_{\mu}$  of the base-collector *pn*-junction, the transconductance  $g_m$ , the output resistance  $r_o$  – expressed in equation (2.5) – and the substrate capacitance  $C_S$  (between collector and sub-

Figure 2.8: Small-signal equivalent circuit model of an *npn*-type BJT in forward-active region.

strate). All these parameters are small-signal parameters and are dependent on the chosen operating point (OP) of the transistor.

The input resistance  $r_{\pi}$  is defined as the ratio between the small-signal base-emitter voltage  $v_{BE}$  and emitter current  $i_B$  [SS16]:

$$r_{\pi} = \frac{v_{BE}}{i_B} \tag{2.6}$$

The transconductance  $g_m$  gives the relationship between the transistor's small-signal output current  $i_C$  and voltage  $v_{BE}$ , which can be regarded as the transistor's input voltage. The transconductance is calculated by the following equation [SS16]:

$$g_m = \frac{\delta i_C}{\delta v_{BE}}\Big|_{OP} \tag{2.7}$$

An important metric of the high-frequency performance of a transistor is the transit frequency  $f_T$ . This is the frequency where the current gain of the transistor equals 1. The transit frequency is given by the two dominant parasitic capacitances of the transistor's small-signal model, namely  $C_{\pi}$  and  $C_{\mu}$ . The formula for the calculation of  $f_T$  is [TS02]:

$$f_T = \frac{g_m}{2\pi (C_\pi + C_\mu)}$$

(2.8)

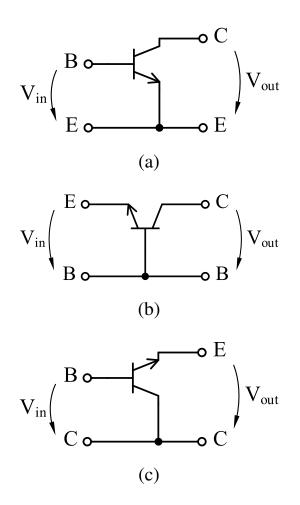

Figure 2.9: Basic amplifier topologies: (a) common emitter, (b) common base, (c) common collector.

### 2.3 Basic Amplifiers

There are three possibilities to realize an amplifier circuit by means of a transistor. Depending on which of the transistor terminals are connected to ground or supply voltage (or any other DC bias voltage), three basic amplifier topologies can be realized: the common-emitter, the common-base or the common-collector amplifier, as shown in Fig. 2.9 [Ell07]. Thus, the terminal connected to ground or supply voltage is common to both the input and output of the circuit. These amplifier topologies have different characteristics, therefore the choice which topology to use depends on the system requirements. In the following three subsections, an analysis of the basic amplifiers is done in order to investigate their characteristics.

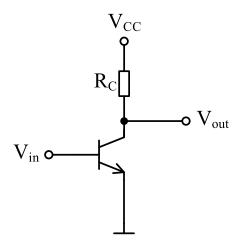

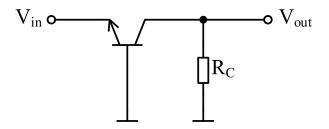

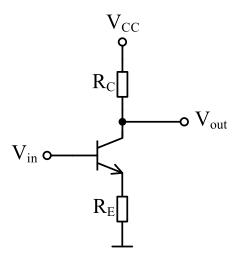

Figure 2.10: Common-emitter circuit.

#### 2.3.1 Common-Emitter Amplifier

The common-emitter circuit is shown in Fig. 2.10. The emitter terminal is connected to ground and is common to both the input and the output of the circuit. The collector resistance  $R_C$  is connected to the supply voltage  $V_{CC}$ . The transistor's collector terminal represents the output of the circuit.

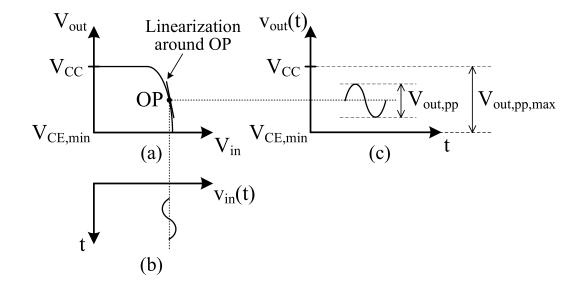

The large-signal behavior of a common-emitter amplifier is illustrated in Fig. 2.11 (a). The output voltage  $V_{out}$  remains constant and equals the supply voltage  $V_{CC}$  as long as no collector current  $I_C$  is flowing through the transistor. Once the threshold voltage  $V_{in} = V_{BE} = V_{BE,0}$  is reached, the transistor starts conducting and its output voltage becomes:

$$V_{out} = V_{CC} - R_C I_C \tag{2.9}$$

In order to characterize the small-signal behavior of the circuit, a linear operation is assumed around the chosen OP for very low input voltage amplitudes (Fig. 2.11 (a)). The resulting input and output voltages are shown in Fig. 2.11 (b) and (c), respectively.

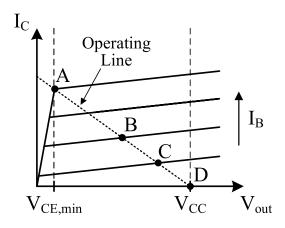

Next, the choice of the OP of the common-emitter amplifier is described [Ell07]. Fig. 2.12 illustrates several OPs based on the transistor's  $I_C$ - $V_{CE}$  diagram. Since  $V_{out} = V_{CE}$  and given the equation (2.9), the resistor  $R_C$  determines the slope of the operating line.  $V_{CE,min}$  represents the minimum collector-emitter voltage for which the transistor still operates in the forward-

Figure 2.11: Large-signal behavior of the common-emitter amplifier and the small-signal linearization around the operating point.

Figure 2.12: Choice of the operating point for the common-emitter amplifier.

active region (for the depicted operating line). The highest amplification is reached in point A, which yields the highest amount of collector current. Nevertheless, a symmetrical drive of the transistor is not possible, since the OP is close to  $V_{CE,min}$ . In order to guarantee a linear operation with a minimal amount of distortions, the transistor needs to be operated in point B. However, this OP implies a high dissipation of DC power. Point C is suitable for lownoise applications: the shot noise, which is dominant in bipolar transistors, increases with  $I_C$ ; however, for a too low  $I_C$  the BJT behaves as a passive RC network, showing a high thermal noise. Therefore, the choice of this OP represents an optimum  $I_C$  targeting the lowest amount of noise. Finally, point D is used for applications requiring a high power efficiency, since the collector current at this OP is close to 0.

Next, we shall analyze the small-signal behavior of the common-emitter amplifier. To this end, the inverse hybrid parameters of the circuit are used [TS02]:

$$i_{in} = g_{11}v_{in} + g_{12}i_{out}$$

$$v_{out} = g_{21}v_{in} + g_{22}i_{out}$$

(2.10)

Based on the inverse hybrid parameters, the following small-signal parameters of the circuit are defined:

$$g_{21} = a_v = \frac{v_{out}}{v_{in}}\Big|_{i_{out}=0}$$

(2.11)

as the small-signal voltage gain of the circuit,

$$g_{22} = r_{out} = \frac{v_{out}}{i_{out}} \Big|_{v_{in}=0}$$

(2.12)

as the small-signal output resistance of the circuit, and

$$g_{11} = r_{in}^{-1} = \frac{i_{in}}{v_{in}} \Big|_{i_{out}=0}$$

(2.13)

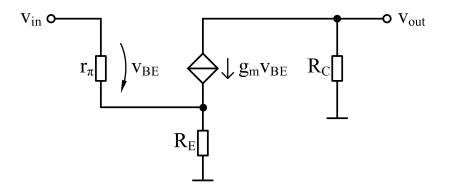

as the small-signal input conductance of the circuit. Next, we shall derive these parameters based on the small-signal equivalent circuit model depicted in Fig. 2.13. The Early effect is neglected, since it is assumed that the tran-

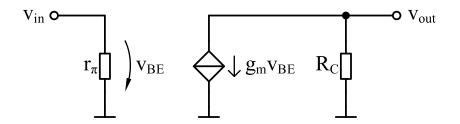

Figure 2.13: Small-signal equivalent circuit of the common-emitter amplifier.

sistor's output resistance described by equation (2.5) is much greater than the collector resistance  $R_C$ .

First, we shall calculate the small-signal voltage gain  $a_v$ , as defined in equation (2.11). To begin with, we express the output voltage  $v_{out}$  as:

$$v_{out} = -g_m v_{BE} R_C \tag{2.14}$$

With  $v_{in} = v_{BE}$  and by inserting equation (2.14) in equation (2.11), we obtain the following relation for the small-signal voltage gain:

$$a_{v} = \frac{-g_{m}v_{in}R_{C}}{v_{in}}$$

$$= -g_{m}R_{C}$$

(2.15)

Next, we investigate the small-signal output resistance of the commonemitter amplifier. Since the condition for calculating the output resistance is  $v_{in} = 0$  (as defined in equation (2.12)) and therefore  $v_{BE} = v_{in} = 0$ , the output resistance equals the collector resistance  $R_C$ .

Finally, the small-signal input resistance of the common-emitter amplifier equals the base-emitter small-signal resistance  $r_{\pi}$ , as it can be seen in Fig. 2.13.

#### 2.3.2 Common-Base Amplifier

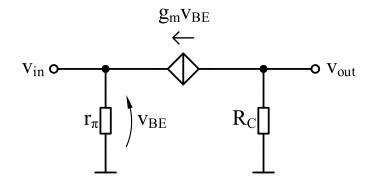

The common-base amplifier is shown in Fig. 2.14. For this amplifier topology, the base is shared between the input and output of the circuit and is connected to ground (or to a DC bias voltage). The equivalent small-signal circuit model is shown in Fig. 2.15.

Figure 2.14: Common-base circuit.

Figure 2.15: Small-signal equivalent circuit of the common-base amplifier.

We shall first calculate the small-signal voltage gain of the circuit. Similarly to the common-emitter amplifier, we express the output voltage as:

$$v_{out} = -g_m v_{BE} R_C \tag{2.16}$$

considering that  $v_{in} = -v_{BE}$ , we insert equation (2.16) in equation (2.11) and we obtain the following formula for the small-signal voltage gain of the common-base amplifier:

$$a_{v} = \frac{-g_{m}v_{BE}R_{C}}{-v_{BE}}$$

$$= g_{m}R_{C}$$

(2.17)

The calculated gain is similar to the gain of the common-emitter amplifier, except that it has a positive sign. This is of great importance for the bandwidth of the circuit, since the Miller effect is considerably reduced, as it will be explained in Subsection 2.3.6.

Next, we investigate the amplifier's small-signal output resistance. As for the common-emitter amplifier, the condition for calculating the output resistance is the shorted input ( $v_{in} = 0$ , equation (2.12)). With  $v_{BE} = -v_{in} = 0$  and therefore  $g_m v_{BE} = 0$ , the output resistance equals the collector resistance  $R_C$ .

Finally, we calculate the small-signal input resistance, as defined in equation (2.13). We first express the input current as:

$$i_{in} = -\frac{v_{BE}}{r_{\pi}} - g_m v_{BE}$$

$$= v_{in} \left( g_m + \frac{1}{r_{\pi}} \right)$$

$$= v_{in} \frac{1 + g_m r_{\pi}}{r_{\pi}}$$

(2.18)

assuming that  $g_m r_{\pi} \gg 1$  and inserting equation (2.18) in equation (2.13), we obtain the following small-signal input resistance:

$$r_{in} = \frac{1}{g_m} \tag{2.19}$$

Thus, contrary to the common-emitter amplifier, the small-signal input resistance of the common-base circuit is low-ohmic.

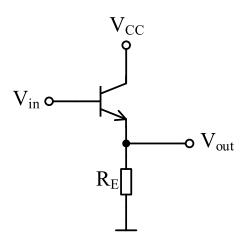

#### 2.3.3 Common-Collector Stage

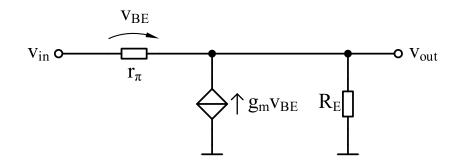

The schematic of the common-collector circuit is depicted in Fig. 2.16. Analogously to the common-emitter and common-base amplifiers, the collector terminal of the common-collector stage is connected to a constant supply voltage (or to any other DC bias voltage). The small-signal equivalent circuit model is illustrated in Fig. 2.17.

Figure 2.16: Common-collector circuit.

Figure 2.17: Small-signal equivalent circuit of the common-collector stage.

We begin our analysis by calculating the small-signal voltage gain of the circuit. First, we express the output voltage as:

$$v_{out} = R_E \left( g_m v_{BE} + \frac{v_{BE}}{r_\pi} \right)$$

$$= R_E v_{BE} \left( g_m + \frac{1}{r_\pi} \right)$$

$$= R_E v_{BE} \frac{1 + g_m r_\pi}{r_\pi}$$

(2.20)

assuming that  $g_m r_\pi \gg 1$ , equation (2.20) becomes:

$$v_{out} = g_m v_{BE} R_E \tag{2.21}$$

Next, we express the input voltage as:

$$v_{in} = v_{BE} + v_{out} \tag{2.22}$$

Inserting equation (2.21) in equation (2.22), we obtain:

$$v_{in} = v_{BE} + g_m v_{BE} R_E$$

=  $v_{BE} (1 + g_m R_E)$  (2.23)

Inserting equations (2.21) and (2.23) in equation (2.11), we obtain the following formula for the small-signal voltage gain:

$$a_{v} = \frac{g_{m}v_{BE}R_{E}}{v_{BE}(1+g_{m}R_{E})}$$

$$= \frac{g_{m}R_{E}}{1+g_{m}R_{E}}$$

(2.24)

Assuming that  $g_m R_E \gg 1$ , we conclude from equation (2.24) that the smallsignal voltage gain of the common-collector circuit is approximately 1, meaning that this topology has no voltage gain. Since the voltage at the emitter of the transistor (i.e. the output of the circuit) is almost equal to the voltage at the base (i.e. the input), the common-collector circuit is also known as emitter follower (EF).

Further, we calculate the small-signal output resistance. With the condition that  $v_{in} = 0$  (equation (2.12)), it results that  $v_{out} = -v_{BE}$ . Next, we define the output current as:

$$i_{out} = -g_m v_{BE} - \frac{v_{BE}}{r_\pi} + \frac{v_{out}}{R_E}$$

$$= g_m v_{out} + \frac{v_{out}}{r_\pi} + \frac{v_{out}}{R_E}$$

$$= v_{out} \left( g_m + \frac{1}{r_\pi} + \frac{1}{R_E} \right)$$

$$= g_m v_{out} \left( 1 + \frac{1}{g_m r_\pi} + \frac{1}{g_m R_E} \right)$$

(2.25)

Inserting equation (2.25) in equation (2.12) and assuming that  $g_m r_\pi \gg 1$  and  $g_m R_E \gg 1$ , we obtain the following small-signal output resistance of the common-collector stage:

$$r_{out} = \frac{v_{out}}{g_m v_{out}}$$

$$= \frac{1}{g_m}$$

(2.26)

which indicates a low-ohmic output.

Next, we calculate the small-signal input resistance of the common-collector

circuit. The input current can be expressed as:

$$i_{in} = \frac{v_{BE}}{r_{\pi}} \tag{2.27}$$

Inserting equations (2.27) and (2.23) in equation (2.13), we obtain the following expression for the small-signal input resistance:

$$r_{in} = v_{BE} (1 + g_m R_E) \frac{r_\pi}{v_{BE}}$$

=  $r_\pi (1 + g_m R_E)$

$\approx g_m r_\pi R_E$  (2.28)

which indicates a high-ohmic input.

#### 2.3.4 Comparison of the Basic Amplifier Topologies

All the above calculated parameters of the basic amplifier topologies are summarized in Table 2.1. For a comprehensive overview of the characteristics of the three topologies, a qualitative comparison is done in Table 2.2 [Ell07].

Table 2.1: Quantitative Comparison Between Basic Amplifier Topologies

|                      | Common-Emitter | Common-Base     | Common-Collector |

|----------------------|----------------|-----------------|------------------|

| Voltage<br>Gain      | $-g_m R_C$     | $g_m R_C$       | ≤ 1              |

| Output<br>Resistance | $R_C$          | R <sub>C</sub>  | $\frac{1}{g_m}$  |

| Input<br>Resistance  | $r_{\pi}$      | $\frac{1}{g_m}$ | $g_m r_\pi R_E$  |

| <u> </u>            | <b>L</b>       |             | 1 1 0            |

|---------------------|----------------|-------------|------------------|

|                     | Common-Emitter | Common-Base | Common-Collector |

| Voltage<br>Gain     | High           | High        | $\leq 1$         |

| Output<br>Impedance | High           | High        | Low              |

| Input<br>Impedance  | High           | Low         | High             |

| Current<br>Gain     | High           | $\leq 1$    | High             |

| Bandwidth           | Average        | High        | High             |

Table 2.2: Qualitative Comparison Between Basic Amplifier Topologies

## 2.3.5 Common-Emitter with Current-Type Negative Feedback

From all the basic amplifier topologies presented in the previous three subsections, the common-emitter stage is one of the most widely used in the realization of modulator or laser driver circuits, thanks to its high input and output impedance and its high voltage gain (Table 2.2). In this section, we shall focus on the enhancement of its performance.

As equation (2.15) shows, the voltage gain of the common-emitter amplifier depends on the transistor's transconductance  $g_m$ , which depends on the transistor's OP and is a source of non-linearity. In order to make the circuit linear, a resistor  $R_E$  can be added at the emitter of the transistor. This resistor is therefore called emitter-degeneration resistor and it realizes a currenttype negative feedback. The resulting common-emitter amplifier is shown in Fig. 2.18. Fig. 2.19 shows the equivalent small-signal circuit model.

In order to calculate the new voltage gain  $a_{v,e}$ , we start from the input voltage  $v_{in}$ :

Figure 2.18: Common-emitter amplifier with emitter-degeneration resistor.

Figure 2.19: Equivalent small-signal circuit model of the common-emitter with emitter-degeneration.

$$v_{in} = v_{BE} + v_{R_E}$$

=  $i_B r_{\pi} + (i_B + i_C) R_E$  (2.29)

With  $i_B = \frac{i_C}{b_i}$  and  $r_{\pi} = \frac{b_i}{g_m}$ , equation (2.29) becomes:

$$v_{in} = \frac{i_C}{b_i} \frac{b_i}{g_m} + \left(\frac{i_C}{b_i} + i_C\right) R_E$$

$$= \frac{i_C}{g_m} + i_C \left(\frac{b_i + 1}{b_i}\right) R_E$$

(2.30)

With  $\frac{b_i+1}{b_i} \approx 1$ , equation (2.30) becomes:

$$v_{in} = i_C \left(\frac{1}{g_m} + R_E\right) \tag{2.31}$$

With the output voltage

$$v_{out} = -i_C R_C \tag{2.32}$$

the voltage gain of the common-emitter amplifier with resistive emitter degeneration is calculated as:

$$a_{v,e} = \frac{v_{out}}{v_{in}}$$

$$= \frac{-i_C R_C}{i_C \left(\frac{1}{g_m} + R_E\right)}$$

$$= -\frac{g_m R_C}{1 + g_m R_E}$$

(2.33)

Compared to the small-signal voltage gain of the common-emitter amplifier in equation (2.15), the gain of the amplifier with emitter degeneration resistor is reduced by the factor  $(1 + g_m R_E)$ . However, as equation (2.33) shows, the gain  $a_{v,e}$  is less dependent on the transistor's parameter  $g_m$ . Thus, if a sufficiently large resistor  $R_E$  is chosen, the gain of the common-emitter amplifier with resistive emitter-degeneration is approximately  $a_{v,e} \approx -\frac{R_C}{R_E}$ , which is constant and therefore indicates a linear behavior of the amplifier.

Besides linearity, applying current-type negative feedback to the commonemitter amplifier further increases the input impedance of the circuit as well as its bandwidth [SS16]. Moreover, by minimizing the dependence of the voltage gain on the transistor's small-signal parameters, the circuit is less sensitive to temperature and process variations.

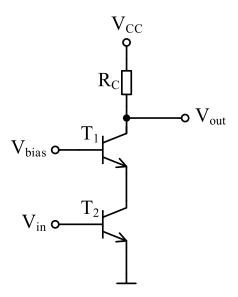

#### 2.3.6 Cascode Amplifier

In order to increase the small-signal output resistance, the voltage gain as well as the bandwidth of a common-emitter circuit, two basic amplifier stages can be cascaded, namely a common-emitter and a common-base stage. Such a

Figure 2.20: Cascode amplifier.

Figure 2.21: Equivalent small-signal circuit model of the cascode amplifier.

circuit is called cascode amplifier and is shown in Fig. 2.20. The equivalent small-signal circuit is shown in Fig. 2.21.

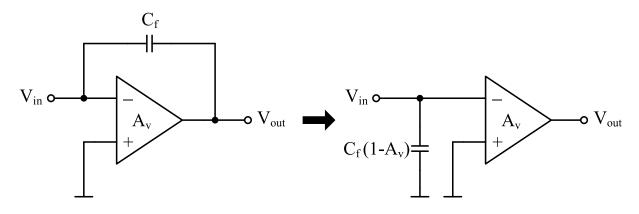

To begin with, we shall explain the Miller effect. This effect is illustrated in Fig. 2.22. It manifests itself when a capacitor  $C_f$  is fed back from the output to the input of an inverted amplifier. As a consequence of the Miller effect, the capacitor will be seen at the input of the amplifier magnified by the factor

Figure 2.22: The Miller effect.

$(1-A_v)$ , where  $A_v$  is the voltage gain of the amplifier. For the commonemitter stage, the capacitance which is fed back from the output to the input of the circuit is represented by the transistor's base-collector capacitance  $C_{\mu}$ (Fig. 2.8). As the small-signal voltage gain of the common-emitter stage is high and negative (equation (2.15)), the Miller capacitance that is created at the input is considerable, thus lowering the overall bandwidth of the circuit.

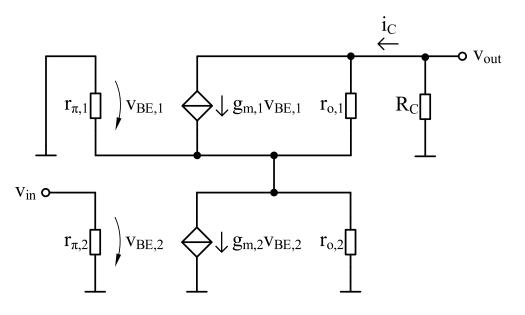

In a cascode amplifier, the common-emitter stage ( $T_2$  in Fig. 2.20) is followed by a common-base stage ( $T_1$ ) in order to neutralize the Miller-effect (since the latter stage shows a high, but positive voltage gain, thus having a low parasitic Miller capacitance). Since the common-base stage acts as a load for the common-emitter stage, the common-emitter's voltage gain  $a_{v,2}$  can be expressed as:

$$a_{\nu,2} = -g_{m,2}r_{\pi,1} \tag{2.34}$$

where  $r_{\pi,1}$  is the small-signal input resistance of the common-base stage. With  $r_{\pi,1} = \frac{b_{i,1}}{g_{m,1}}$  and considering the fact that the common-base circuit has a low current gain ( $b_i \le 1$ ), equation (2.34) becomes:

$$a_{\nu,2} = -g_{m,2} \frac{b_{i,1}}{g_{m,1}}$$

$$\approx -g_{m,2} \frac{1}{g_{m,1}}$$

(2.35)

Assuming that the two transistors  $T_1$  and  $T_2$  have equal geometries and are

biased under similar conditions, we consider that  $g_{m,1} = g_{m,2}$ . Thus, equation (2.35) yields that  $a_{\nu,2} \approx -1$ . Therefore, we conclude that the commonemitter stage of a cascode amplifier does not generate a considerable parasitic Miller capacitance at the input.

The small-signal voltage gain of the common-base stage is given by the following formula:

$$a_{v,1} = g_{m,1} r_{out,c} \tag{2.36}$$

where  $r_{out,c}$  is the small-signal output resistance of the cascode amplifier. Thus, in order to determine the overall voltage gain  $a_{v,c} = a_{v,1}a_{v,2}$  of the cascode stage, we first need to calculate its output resistance. To begin with, we omit the load resistor  $R_C$ . Based on the small-signal equivalent circuit in Fig. 2.21, we write:

$$r'_{out,c} = \frac{v_{out}}{i_C}\Big|_{v_{in}=0}$$

(2.37)

where  $i_C$  is the small-signal collector current of  $T_1$  and  $T_2$ . The output voltage  $v_{out}$  of the cascode amplifier can be expressed as:

$$v_{out} = v_{o,1} + v_{o,2} \tag{2.38}$$

where  $v_{o,1}$  and  $v_{o,2}$  are the voltages over the output resistances  $r_{o,1}$  and  $r_{o,2}$  of the common-base and common-emitter stages, respectively. Since  $v_{BE,2} = v_{in} = 0$  and subsequently the current  $g_{m,2}v_{BE,2} = 0$ , voltage  $v_{o,2}$  is calculated as follows:

$$v_{o,2} = i_C r_{o,2} \tag{2.39}$$

Voltage  $v_{o,1}$  is calculated as follows:

$$v_{o,1} = (i_C - g_{m,1} v_{BE,1}) r_{o,1} \tag{2.40}$$

With  $v_{BE,1} = -v_{o,2}$  and considering equation (2.39), equation (2.40) becomes:

$$v_{o,1} = (i_C + g_{m,1} i_C r_{o,2}) r_{o,1}$$

(2.41)

Thus, the output voltage of the cascode stage becomes:

$$v_{out} = v_{o,1} + v_{o,2}$$

=  $(i_C + g_{m,1}i_Cr_{o,2})r_{o,1} + i_Cr_{o,2}$  (2.42)

=  $i_C(r_{o,1} + r_{o,2} + g_{m,1}r_{o,1}r_{o,2})$

Inserting equation (2.42) in equation (2.37) we obtain the expression for the small-signal output resistance of the cascode amplifier (while omitting  $R_C$ ):

$$r'_{out,c} = r_{o,1} + r_{o,2} + g_{m,1}r_{o,1}r_{o,2}$$

(2.43)

Under the assumption of equal transistors  $T_1$  and  $T_2$  biased under equal conditions, equation (2.43) becomes:

$$r'_{out,c} = 2r_o + g_m r_o^2$$

$$\approx g_m r_o^2$$

(2.44)

Inserting the newly calculated  $r'_{out,c}$  in equation (2.36) and while still omitting  $R_C$ , we obtain:

$$a_{\nu,1}' = g_m^2 r_o^2 \tag{2.45}$$

which results in a total small-signal voltage gain of the cascode amplifier  $a'_{v,1}$  (without resistor  $R_C$ ) of:

$$a'_{v,c} = a_{v,1}a'_{v,2}$$

$$= -g_m^2 r_o^2$$

(2.46)

Both equations (2.44) and (2.46) indicate a very high small-signal output resistance and voltage gain of the cascode amplifier compared to the commonemitter stage. Nevertheless, the total output resistance of the cascode amplifier is also influenced by the load resistor  $R_C$ :

$$r_{out,c} = r'_{out,c} \parallel R_C \tag{2.47}$$

Therefore, in order to take full advantage of the cascode amplifier's high output resistance and voltage gain, it is reasonable to choose a high-impedance load.

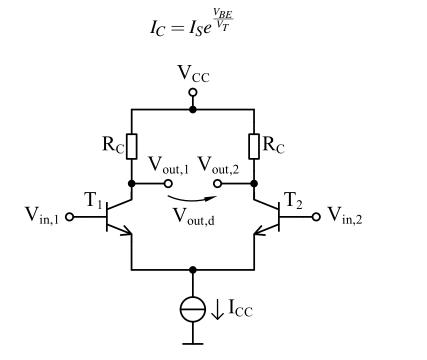

#### 2.3.7 Differential Amplifier

The amplifiers presented so far are single-ended, having one input and one output. Therefore, they amplify not only the main signal, but also unwanted spurious signals. By placing two amplifiers symmetrically, it is possible to drive them in a differential manner, thus amplifying only the difference between two input signals of opposite phases (differential signals), while suppressing the unwanted common-mode signals. Such a circuit is called differential amplifier and is illustrated in Fig. 2.23. It consists of two common-emitter stages sharing the emitter terminal, and a current source which yields the tail current  $I_{CC}$ . The purpose of the current source is to provide the bias current for transistors  $T_1$  and  $T_2$  and to keep the sum of the two collector currents  $I_{C,1}$  and  $I_{C,2}$  constant.

We begin the analysis of the circuit from equation (2.1):

Figure 2.23: Differential amplifier.

(2.48)

Assuming that  $I_C \gg I_B$ , the tail current  $I_{CC}$  is defined as:

$$I_{CC} = I_{C,1} + I_{C,2} \tag{2.49}$$

Next, we define the output differential current  $I_{out,d}$  as:

$$I_{out,d} = I_{C,1} - I_{C,2} \tag{2.50}$$

Finally, we define the input differential voltage  $V_{in,d}$  as:

$$V_{in,d} = V_{in,1} - V_{in,2}$$

$$= V_{BE,1} - V_{BE,2}$$

(2.51)

From the following two relations:

$$I_{C,1} - I_{C,2} = I_S \left( e^{\frac{V_{BE,1}}{V_T}} - e^{\frac{V_{BE,2}}{V_T}} \right)$$

(2.52)

and

$$I_{C,1} + I_{C,2} = I_S \left( e^{\frac{V_{BE,1}}{V_T}} + e^{\frac{V_{BE,2}}{V_T}} \right)$$

(2.53)

we get the ratio:

$$\frac{I_{C,1} - I_{C,2}}{I_{C,1} + I_{C,2}} = \frac{e^{\frac{V_{BE,1}}{V_T}} - e^{\frac{V_{BE,2}}{V_T}}}{e^{\frac{V_{BE,1}}{V_T}} + e^{\frac{V_{BE,2}}{V_T}}}$$

(2.54)

By applying the following definition of the hyperbolic tangent function:

$$\tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}}$$

(2.55)

and after several calculations, equation (2.54) becomes:

$$\frac{I_{C,1} - I_{C,2}}{I_{C,1} + I_{C,2}} = \tanh\left(\frac{V_{BE,1} - V_{BE,2}}{2V_T}\right) \Leftrightarrow$$

$$\Leftrightarrow I_{out,d} = I_{CC} \tanh\left(\frac{V_{in,d}}{2V_T}\right)$$

(2.56)

Considering equations (2.49), (2.50) and (2.56), the collector currents  $I_{C,1}$  and  $I_{C,2}$  can be expressed as:

$$I_{C,1} = \frac{I_{CC} + I_{out,d}}{2}$$

$$= \frac{I_{CC}}{2} \left(1 + \tanh \frac{V_{in,d}}{2V_T}\right)$$

(2.57)

and

$$I_{C,2} = \frac{I_{CC} - I_{out,d}}{2}$$

$$= \frac{I_{CC}}{2} \left(1 - \tanh \frac{V_{in,d}}{2V_T}\right)$$

(2.58)

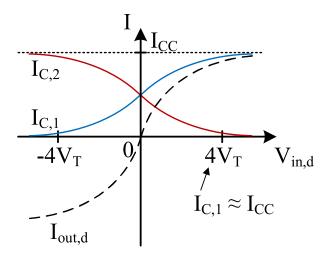

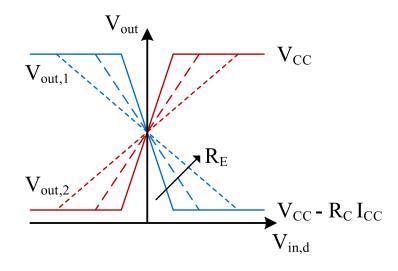

Based on equations (2.56), (2.57) and (2.58), diagram 2.24 can be drawn, which illustrates the dependence of the two collector currents  $I_{C,1}$  and  $I_{C,2}$  as well as of the output differential current  $I_{out,d}$  on the input differential voltage  $V_{in,d}$ . Thus, a differential amplifier switches almost all the tail current  $I_{CC}$  between the two transistors  $T_1$  and  $T_2$ , provided that the input differential voltage is sufficiently high. However, for small  $V_{in,d}$ , the differential amplifier shows a linear behavior, the transfer function being approximately:

Figure 2.24: Transfer characteristics of the differential amplifier.

Figure 2.25: Conceptual representation of the linearization of a differential amplifier by means of emitter-degeneration resistors  $R_E$ .

$$I_{out,d} = I_{CC} \left(\frac{V_{in,d}}{2V_T}\right) \tag{2.59}$$

In order to increase the linear operation range of the differential amplifier, the resistive emitter degeneration technique is employed, which was described in Section 2.3.5. Nevertheless, as for the common-emitter stage with current-type negative feedback, the voltage gain of the circuit is reduced. Fig. 2.25 shows the effect of the emitter-degeneration resistors  $R_E$  on the transfer characteristics of the differential amplifier. As it can be seen, a higher  $R_E$  means a higher linear operation range, however the gain of the differential amplifier is decreased. Therefore, in case that both a high output voltage swing and a high linearity are required, the tail current of the circuit has to be increased, which considerably increases the power consumption.

# 2.4 High-Swing Amplifier

Based on the basic amplifier topologies presented in the previous section, more complex circuit architectures can be realized, with enhanced functions and parameters. One very important parameter for amplifier circuits is the maximum achievable output voltage swing. Mach-Zehnder modulators are widely employed in the front-ends of electrooptical communication systems. Such modulators require high voltage swings in order to efficiently convert the electrical data into optical data. Nevertheless, the maximum output voltage swing that can be provided by an amplifier circuit is limited by the collector-emitter breakdown voltage ( $BV_{CE}$ ) of the output bipolar transistors, or the drain-source breakdown voltage ( $BV_{DS}$ ) of the field-effect transistors. This voltage is given by the technology specifications and represents a major design constraint. Therefore, special circuit topologies need to be investigated in order to overcome this limitation.

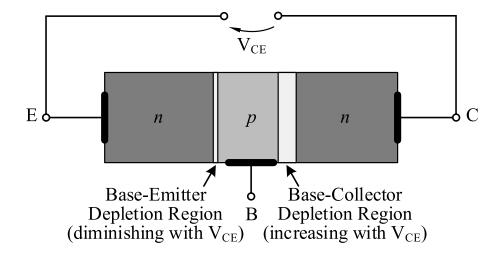

#### 2.4.1 Physics of the Transistor Breakdown Process

In this subsection, we provide a brief description of the breakdown process in a bipolar transistor. For a better visualization, this process is illustrated in Fig. 2.26. We assume a  $V_{CE}$  voltage applied over the collector and emitter of the transistor, where the collector potential  $V_C$  is higher than the emitter potential  $V_E$ . The base of the transistor is initially left open, the base current  $I_B$  being thus equal to 0.

The base-collector pn-junction is reversed biased and shows a reverse saturation current. This current is caused by the minority charge carriers in the n-doped collector and p-doped base region, respectively, which cross the pn-junction. Holes are therefore injected from the collector region into the

Figure 2.26: Physics of the breakdown process in the npn transistor.

base, and drift further towards the base-emitter *pn*-junction. In turn, electrons are injected from the emitter region into the base, and move further towards the base-collector junction. As the  $V_{CE}$  voltage increases, a chain reaction occurs: more holes arrive at the base-emitter junction, thus making it narrower [MH07]. A narrower base-emitter junction means a lower barrier for the electrons in the emitter, so that more electrons are injected into the base and afterwards into the base-collector junction, which keeps widening [MH07]. The increase of  $V_{CE}$  causes the increase of the electric field in the depletion region of the base-collector junction. Therefore, the drift velocity of the electrons in this region increases, and their collision with atoms produces more electron-hole pairs, which further speeds up the chain event. This phenomenon is called avalanche breakdown [SS16]. When  $V_{CE} = BV_{CE}$ , the current through the transistor rises exponentially and the transistor enters into breakdown.

So far, we have regarded the case where the base of the bipolar transistor is left open. If a certain impedance is available at the transistor's base, some of the holes injected from the base-collector junction into the base will be prevented from arriving at the base-emitter region, being absorbed by the base terminal instead. Therefore, the transistor breakdown will occur at a higher  $V_{CE}$ . The following relationship can be established between various  $BV_{CE}$ depending on the impedance seen at the base of the transistor [TS02]:

$$BV_{CE, open base} < BV_{CE, base impedance} < BV_{CE, shorted base}$$

(2.60)

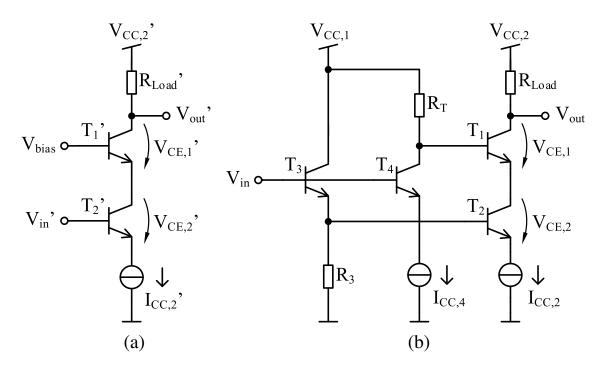

#### 2.4.2 Circuit Concept

A way to overcome the limitation imposed by the breakdown voltage of the transistors and increase the maximum achievable voltage swing at the output of a driver circuit is to use a cascaded transistor structure. Nevertheless, a basic cascode amplifier, as presented in Section 2.3.6, would not be sufficient to accomplish the task of increasing the output voltage swing. Fig. 2.27 (a) illustrates a basic cascode amplifier. The upper transistor  $T'_1$  is a common-base circuit and its base is connected to a constant DC bias voltage. Be-

Figure 2.27: (a) Basic cascode amplifier; (b) Breakdown Voltage Doubler [GBK<sup>+</sup>18a]<sup>†</sup>. ©[2018] IEEE

cause of this, and due to the fact that the transistor's base-emitter voltage  $V_{BE}$  varies logarithmically with the transistor's collector current  $I_C$  (as shown in Fig. 2.6), the voltage  $V'_{BE,1}$  of transistor  $T'_1$  and thus the voltage at the emitter of  $T'_1$  change only slightly. Therefore, the collector-emitter voltage  $V'_{CE,2}$  of transistor  $T'_2$  remains largely constant during the whole operation of the driver. This means that almost the whole output voltage swing of the driver falls over the upper transistor  $T'_1$ , which can go into breakdown in the case of a too large swing.

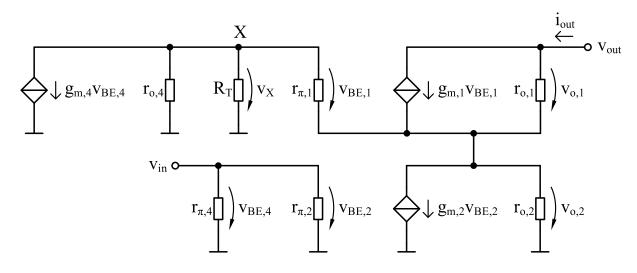

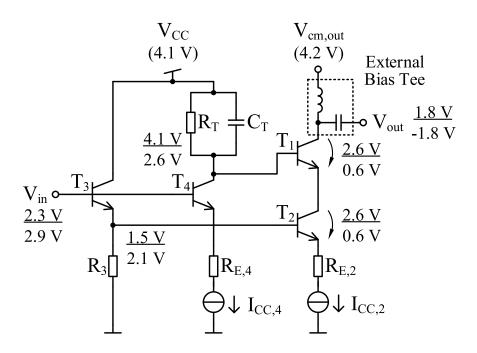

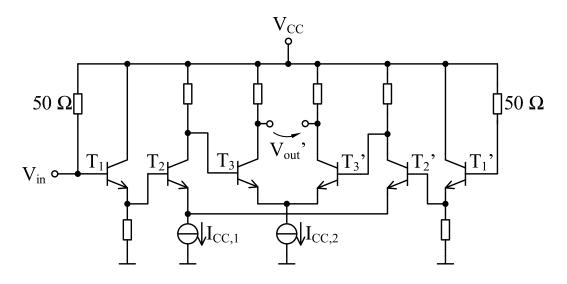

In order to distribute equally the output voltage swing between the two cascaded transistors, the base of  $T'_1$  should vary in a synchronized manner with the base of  $T'_2$ . This is done by adding a common-emitter circuit  $T_4$  (Fig. 2.27 (b)) with the load resistor  $R_T$  that drives the base of the upper transistor  $T_1$  [MH07]. Both the common-emitter circuit  $T_4$  and the base of transistor  $T_2$  are connected to the input  $V_{in}$  of the circuit (transistor  $T_2$  is connected via the common-collector stage  $T_3$ ). By this means, the bases of the two cascaded transistors  $T_1$  and  $T_2$  are driven in a synchronized manner and the output voltage swing is divided equally between them, with  $V_{CE,1} = V_{CE,2}$

Figure 2.28: Equivalent small-signal circuit model of the breakdown voltage doubler topology.

during the whole operation of the driver. This circuit topology is called breakdown voltage doubler [MH07], since it doubles the maximum achievable output voltage swing of the circuit by driving the two output transistors close to their  $BV_{CE}$ , however without exceeding it.

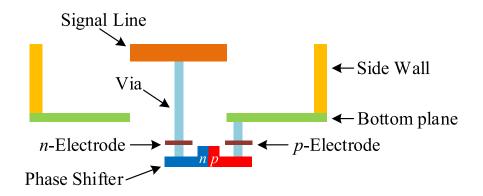

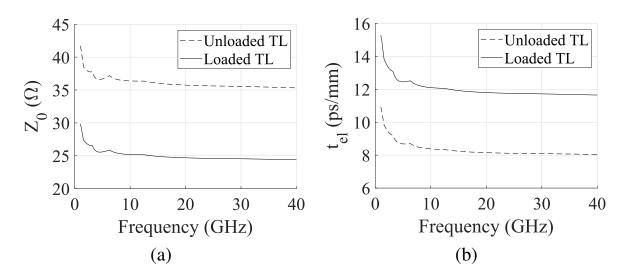

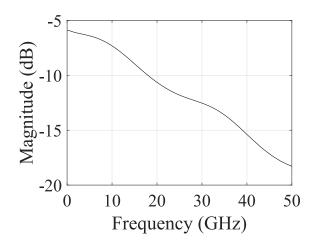

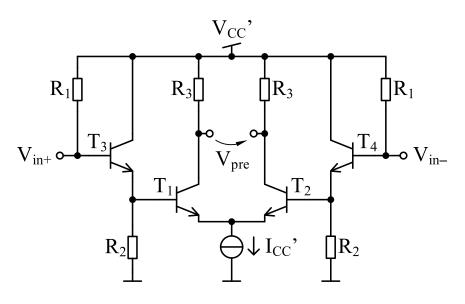

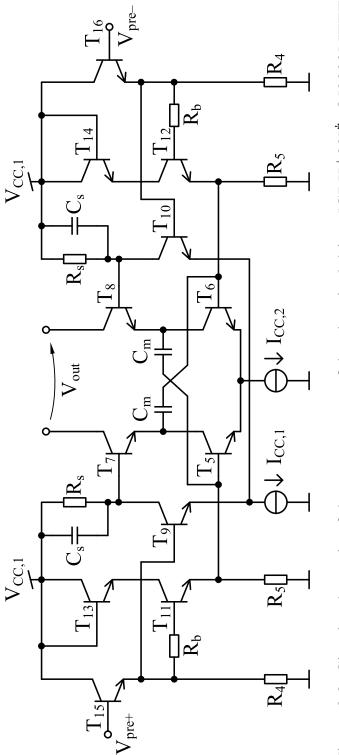

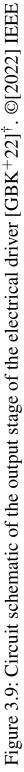

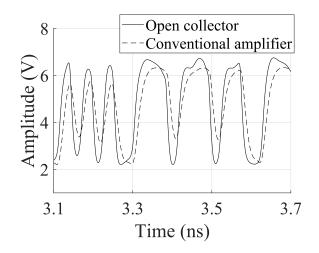

#### 2.4.3 Circuit Analysis