Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

10-26-2007

# **Ultra Reliable Computing Systems**

Chong Ho Lee Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons Let us know how access to this document benefits you.

### **Recommended Citation**

Lee, Chong Ho, "Ultra Reliable Computing Systems" (2007). *Dissertations and Theses*. Paper 6156.

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# ULTRA RELIABLE COMPUTING SYSTEMS

by

### CHONG HO LEE

A dissertation submitted in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY in ELECTRICAL AND COMPUTER ENGINEERING

Portland State University ©2007

### DISSERTATION APPROVAL

The abstract and dissertation of Chong Ho Lee for the Doctor of Philosophy in Electrical and Computer Engineering were presented October 26, 2007 and accepted by the dissertation committee and the doctoral program.

COMMITTEE APPROVALS:

| <i>(</i> )           |               | <u>_</u> |   |

|----------------------|---------------|----------|---|

|                      |               |          |   |

|                      | •             |          |   |

| Douglas V./Hall, Cha | air           |          |   |

| 1 1                  | 11 1          |          |   |

|                      |               |          |   |

| Marek A. Perkowski   |               |          |   |

| 1                    | Λ             |          |   |

|                      |               |          | / |

| Xiaoyu Song          |               | 1        |   |

|                      | $\mathcal{V}$ |          |   |

|                      |               |          |   |

| Dan Hammerstrom      |               |          |   |

Jong Sung Kim Representative of the Office of Graduate Studies

DOCTORAL PROGRAM APPROVAL:

Λ

Malgorzata Chrzanowska-Jeske, Director Electrical and Computer Engineering Ph.D. Program

#### ABSTRACT

An abstract of the dissertation of Chong Ho Lee for the Doctor of Philosophy in Electrical and Computer Engineering presented October 26, 2007.

Title: Ultra Reliable Computing Systems

For high security and safety applications as well as general purpose applications, it is necessary to have ultra reliable computing systems. This dissertation describes our system of self-testable and self-repairable digital devices, especially, EPLDs (Electrically Programmable Logic Devices). In addition to significantly improving the reliability of digital systems, our self-healing and re-configurable system design with added repair capability can also provide higher yields, lower testing costs, and faster time-to-market for the semiconductor industry.

The digital system in our approach is composed of blocks, which realize combinational and sequential circuits using GALs (Generic Array Logic Devices). We describe three techniques for fault-locating and fault-repairing in these devices. The methodology we used for evaluation of these methods and a comparison with devices that have no self-repair capability was simulation of the self-repair algorithms. Our simulations show that the lifetime for a GAL-based EPLD that uses our multiple self-repairing methods is longer than the lifetime of a GAL-based EPLD that uses a single self-repair method or no self-repair method. Specifically, our work demonstrates that the lifetime of a GAL can be increased by adding extra columns in the AND array of a GAL and extra output ORs in a GAL. It also gives information on how many extra columns and extra ORs a GAL needs and which self-repairing method should be used to guarantee a given lifetime. Thus, we can estimate an ideal point, where the maximum reliability can be reached with the minimum cost.

### **ACKNOWLEDGMENTS**

As I finish up the doctoral program, I realized that this program is more than just a process for becoming a doctor in engineering. I feel that the philosophy I have come to understand in this lengthy program is what is really important in life, as the word philosophy in Ph. D., may indicate.

I am truly grateful for this day where I have finally reached the point of writing this acknowledgment after countless hours of research, development, and verification, but this dissertation could not have been completed without the support of many people. My utmost gratitude goes to the ones mentioned here.

First of all, I would like to thank my parents whose endless support from near and far allowed me to be the best student and engineer that I could have been, and get here where all my hard effort is finally being printed. The first ones I want to share this moment with are my mother and late father, Dr. Min Jae Lee, who would have been the happiest and the proudest of my achievement. My family who patiently supported me through the long and arduous process. I regret not being able to spend more time with my little prince, Daniel H. Lee, who stayed strong and persevered with me, and even gave encouragements at times. There are no words that can express my appreciation for his support.

My advisor, Professor Douglas V. Hall, whose teachings gave me insights that are applicable to academic and practical world. He was a teacher in the class, an advisor in the program, and a father figure in life. He guided me with such integrity all the way to the end of the program. He taught me the true meaning of being an engineer, and was a great role model in life.

Professor Marek A. Perkowski who suggested the topic and provided many ideas and guidance. It truly was an honor and an unforgettable experience to learn from a professor of his stature and knowledge. He taught with much passion and strict rules, but always treated students warm-heartedly.

Professor Xiaoyu Song who did not hesitate to provide physical and mental support. He always helped me in difficult situations almost as a friend, and encouraged me to believe that I can complete the program. It was an honor to have Professor Dan Hammerstrom and Professor Jong Sung Kim as the approval committee members. The points they made in the process will be a tremendous help to completing the thesis.

I will always be grateful for the Assistant Director of International Affairs, Ms. Christina Luther, for her kindness and dedication to guide me through the complicated international student rules and forms.

I would like to share this accomplishment with everyone who supported and waited for this day by my side, especially Mr. Tae Kun Woo and Mr. Hank Lee for their help in the simulation process, which was an integral part of the study.

Finally, I had many difficulties in finding reference materials directly related to this study, but I hope that this paper can be a useful reference to any related studies in the future.

# Table of contents

| ACKNOWLEDGMENTSi                                               |

|----------------------------------------------------------------|

| List of Tablesix                                               |

| List of Figuresxi                                              |

| 1. Introduction1                                               |

| 1.1. MOTIVATIONS AND REAL PROBLEMS                             |

| 1.1.1. Two-level Regular-Structured Programmable Logic Devices |

| 1.1.2. Memories                                                |

| 1.2. Domain of the Work10                                      |

| 1.2.1. General Research Objectives11                           |

| 1.2.1.1. Purposes and Goals                                    |

| 1.2.1.2. Hypotheses                                            |

| 1.2.2. Contributions and Applications17                        |

| 1.3. Outline                                                   |

| 2. Prerequisites for the Self-Repair Technology21              |

| 2.1. INTRODUCTION TO PLDs                                      |

| 2.1.1.                                           | What is PLD?                                             |

|--------------------------------------------------|----------------------------------------------------------|

| 2.1.2.                                           | Types of PLDs                                            |

| 2.1.3.                                           | PAL                                                      |

| 2.1.4.                                           | GALs Structure                                           |

| 2.2. P                                           | ROGRAMMING TECHNOLOGY                                    |

| 2.2.1.                                           | Fusible Link                                             |

| 2.2.2.                                           | E <sup>2</sup> CMOS Programming Technology               |

| 2.2.3.                                           | PLDs' Programming Procedure                              |

| 3. Previo                                        | ous Work on Self-Test and Self-Repair                    |

|                                                  |                                                          |

| 3.1. S                                           | elf-Healing Memories                                     |

|                                                  | ELF-HEALING MEMORIES                                     |

| 3.1.1.                                           |                                                          |

| <i>3.1.1</i> .<br>3.1.                           | Introduction to Memories; SRAM, DRAM, and Flash Memory   |

| <i>3.1.1.</i><br>3.1.<br>3.1.                    | Introduction to Memories; SRAM, DRAM, and Flash Memory37 |

| <i>3.1.1.</i><br>3.1.<br>3.1.<br>3.1.            | Introduction to Memories; SRAM, DRAM, and Flash Memory   |

| 3.1.1.<br>3.1.<br>3.1.<br>3.1.<br>3.1.<br>3.1.2. | Introduction to Memories; SRAM, DRAM, and Flash Memory   |

| 3.1.2.3. Self-Testing and Self-Repairing Algorithms             | 47  |

|-----------------------------------------------------------------|-----|

| 3.1.2.4. The STAR (Self-Test and Repair) SRAM Embedded Memory   | 49  |

| 4. Self-Testing and Self-Repairing EPLDs                        | .51 |

| 4.1. DESIGN METHODOLOGY OF SELF-REPAIRABLE GALS                 | 52  |

| 4.1.1. Fault Model and Assumptions                              | 53  |

| 4.1.2. Design Architecture                                      | 57  |

| 4.1.3. Test Generation and Fault Diagnosis/Location             | 67  |

| 4.2. Self-Repairing Methodologies                               | .76 |

| 4.2.1. Column Replacement with Extra Columns                    | 76  |

| 4.2.2. Column Re-Use with Extra Columns                         | 80  |

| 4.2.2.1. Column-Column Re-Use with Extra Columns                | 81  |

| 4.2.2.2. Cell-Column Re-Use with Extra Columns                  | .86 |

| 4.2.3. Integration of the Column Repair Methods                 | 91  |

| 4.2.4. Replacement and Re-use with Extra OR-gates               | 93  |

| 5. Self-Testing and Self-Repairing Switching Circuit            | .95 |

| 5.1. HARDWARE DESIGN MECHANISM OF THE SELF-REPAIRABLE SWITCHING |     |

| Circuit                                                         | .98 |

| 5.1.1. Fault Model and Assumptions                                                     |             |

|----------------------------------------------------------------------------------------|-------------|

| 5.1.2. Design Architecture                                                             |             |

| 5.1.3. Test Generation and Fault Diagnosis/Location                                    | 112         |

| 5.2. Switching Circuit Self-Repairing Methodologies                                    | 121         |

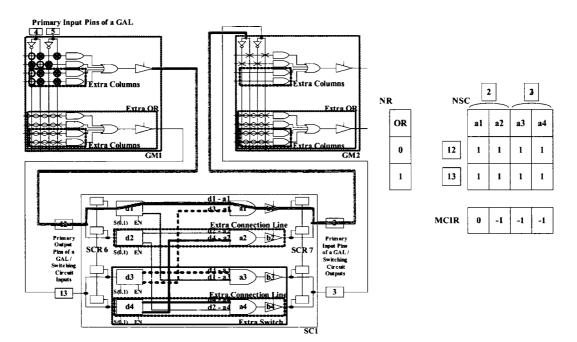

| 5.2.1. Line Replacement with Extra Lines                                               | 121         |

| 6. New Hardware Prototype and Simulator for the Ultra Reliabl<br>Systems               |             |

| 6.1. Analysis and Synthesis of the Hardwired Test and the                              | E DIAGNOSIS |

| Algorithm                                                                              | 127         |

| 6.2. INTRODUCTION TO THE COMPUTER-BASED SIMULATOR                                      | 140         |

| 7. Evaluation and Analysis of the Simulation Results for the Ultr<br>Computing Systems |             |

| 7.1. Assumptions and Failure Rates                                                     | 164         |

| 7.2. EVALUATION AND ANALYSIS OF THE SIMULATION RESULTS                                 | 167         |

| 7.3. HARDWARE OVERHEAD AND PERFORMANCE                                                 |             |

| 7.3.1. Extra OR-Gate                                                                   |             |

| 7.3.2. Extra Line on Switching Circuits                                                |             |

| 7.3.3. Performance by Available OR-Gate                                                |             |

|    | 7.3.4. FPGA and ASIC Design  | 199 |

|----|------------------------------|-----|

| 8. | Conclusions and Future Works | 206 |

| BI | BLIOGRAPHY                   | 213 |

# List of Tables

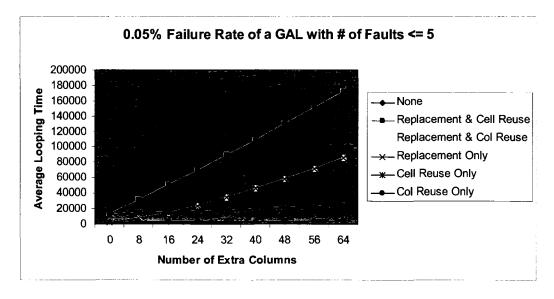

| Table 7.1 Average Looping Times of Simulating the Replacement Methodology168    |  |  |

|---------------------------------------------------------------------------------|--|--|

| Table 7.2 Average Looping Time of Simulating the Column-Column Re-Use Only. 170 |  |  |

| Table 7.3 Average Looping Time of Simulating the Cell-Column Re-Use Only 171    |  |  |

| Table 7.4 Average Looping Time of Simulating the Column-Column Re-Use and       |  |  |

| Replacement174                                                                  |  |  |

| Table 7.5 Average Looping Time of Simulating the Cell-Column Re-Use and         |  |  |

| Replacement175                                                                  |  |  |

| Table 7.6 Generic Components    181                                             |  |  |

| Table 7.7 GAL Components    182                                                 |  |  |

| Table 7.8 OLMC's OR-gate Combination Chart                                      |  |  |

| Table 7.9 Area Overhead and Ratio                                               |  |  |

| Table 7.10 Performance of a Self-Repairable GAL using Column Replacement        |  |  |

| Method                                                                          |  |  |

| Table 7.11 Performance of a Self-Repairable GAL using Cell-Column Re-Use Method |  |  |

| & Replacement Method186                                                         |  |  |

.

| Table 7.12 Average Looping Time of Simulating the Cell-Column Re-Use and     |

|------------------------------------------------------------------------------|

| Replacement188                                                               |

| Table 7.13 Performance Comparison of GALs with Extra OR-Gates and with Extra |

| Columns                                                                      |

| Table 7.14 Average Looping Time of SC with 1 and 2 Extra Lines               |

| Table 7.15 SC Components   193                                               |

| Table 7.16 SC Overhead Cell Count    194                                     |

| Table 7.17 Performance of SC using Extra Line    194                         |

| Table 7.18 GAL Overhead – Total Cell Count                                   |

| Table 7.19 GAL Overhead Ratio (Based on the Basic Prototype Proposed)        |

| Table 7.20 SC Looping Time Variance on Number of Unused OR-Gates on GAL198   |

| Table 7.21 GAL Overhead Ratio (against a Generic Chipset, GAL)               |

| Table 7.22 Comparing Data of FPGA and ASIC Simulation with Extra ORs         |

| Table 7.23 Prototype of FPGA and ASIC's Comparison to a Generic System       |

| Table 7.24 Unused Extra OR-Gate Efficiency    204                            |

# List of Figures

| Figure 2.1 Simplified Notation for Input Lines of an AND Gate                      |

|------------------------------------------------------------------------------------|

| Figure 2.2 Basic Structure of a PROM23                                             |

| Figure 2.3 Basic Structure of a PLA23                                              |

| Figure 2.4 Basic Structure of a PAL/GAL24                                          |

| Figure 2.5 Simplified Logic Diagram of a PAL26                                     |

| Figure 2.6 A Programmed Simple Logic Function in a GAL27                           |

| Figure 2.7 Structure of the GAL16V829                                              |

| Figure 2.8 (a) Non-Programmed State and (b) Programmed State in Basic Structure of |

| an OR-Array30                                                                      |

| Figure 2.9 (a) Non-Programmed State and (b) Programmed State in Basic Structure of |

| an AND-Array31                                                                     |

| Figure 2.10 E <sup>2</sup> CMOS Cell                                               |

| Figure 2.11 PLDs' Programming Procedure                                            |

| Figure 3.1 The BIST Augmented Architecture                                         |

| Figure 3.2. BIST Architecture with Column Repair                                   |

| Figure 3.3. STAR Memory System                                                        |

|---------------------------------------------------------------------------------------|

| Figure 4.1 Example of a Logic Diagram Notation                                        |

| Figure 4.2 Cellular Array of EPLDs/Memory in a System; controlled by a FLFRP          |

| (Fault-Locating/Fault-Repairing Processor) to repair faults in each                   |

| EPLD/memory58                                                                         |

| Figure 4.3 Design Architecture for Self-Repairable GAL60                              |

| Figure 4.4 Inner Structure of the Block                                               |

| Figure 4.5 Structure of MAP and SAP Arrays                                            |

| Figure 4.6 Structure of the NC Register                                               |

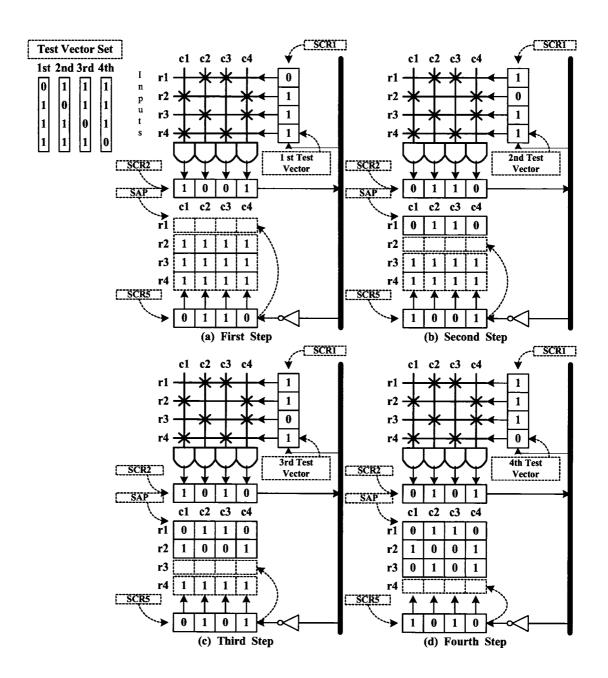

| Figure 4.7 Generation of the Test Vector Set/Storing Scanning Results into the SAP.70 |

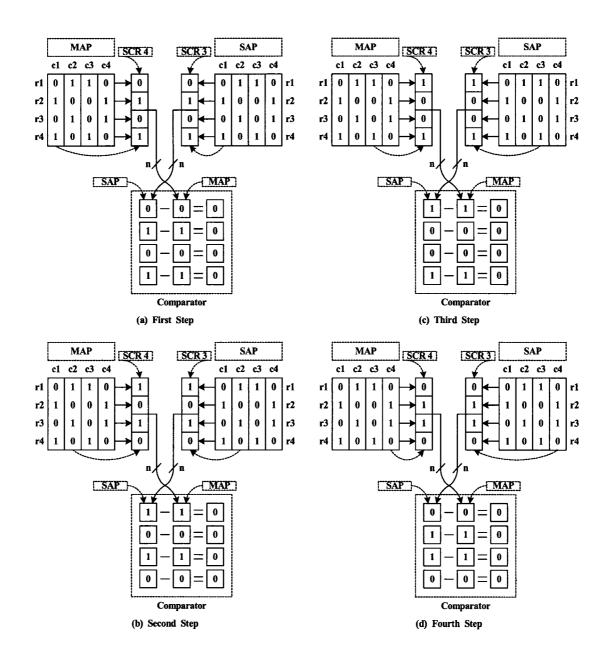

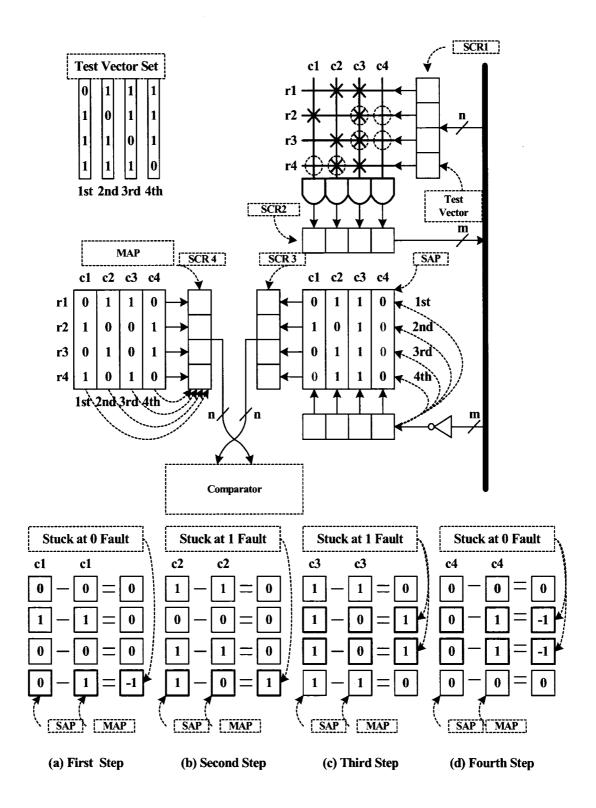

| Figure 4.8 Comparator Operation for Finding Faults on a Circuit without Faults73      |

| Figure 4.9 Fault Diagnosis/Location of an Example with Faults75                       |

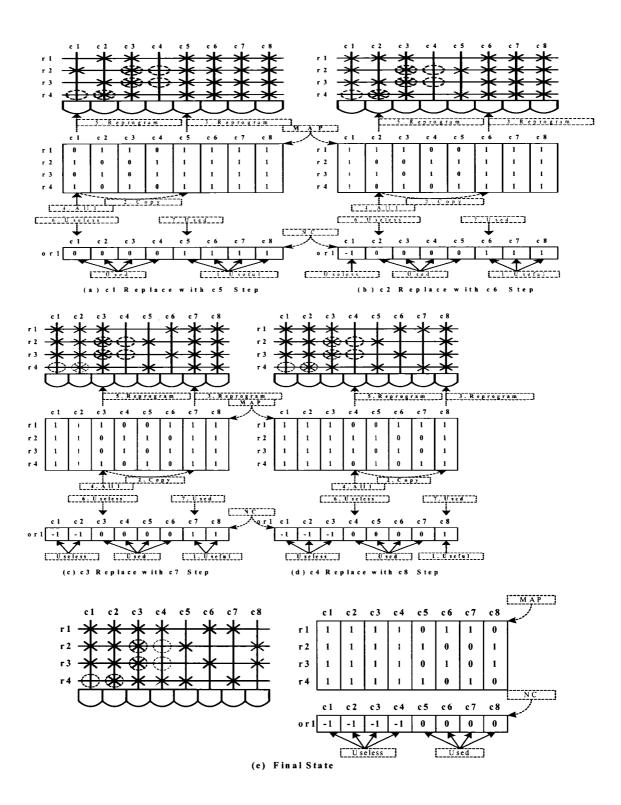

| Figure 4.10 A Column Replacement Method Example of Multiple Faults                    |

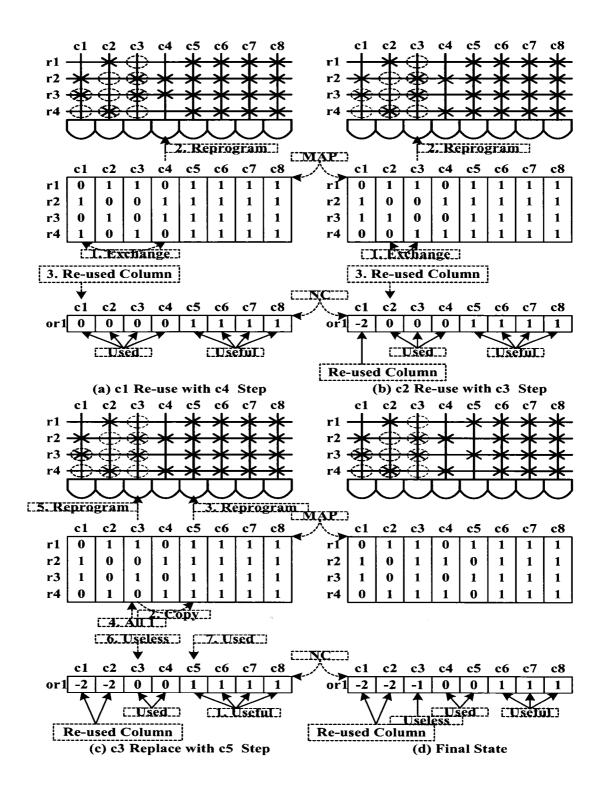

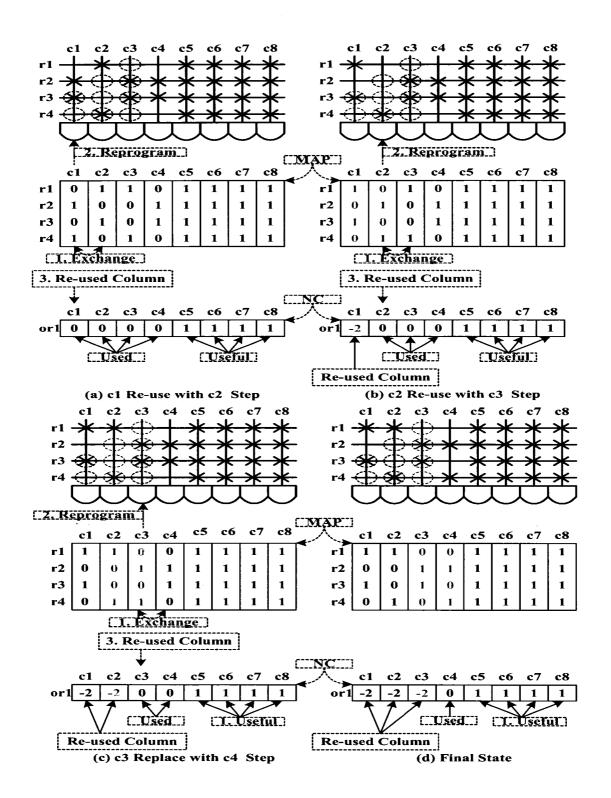

| Figure 4.11 An Example of the Column-Column Re-Use with Multiple Faults83             |

| Figure 4.12 An Example of the Cell-Column Re-Use with Multiple Faults                 |

| Figure 5.1 Design Architecture for the Ultra Reliable Computing System with Self-     |

| Repairable GAL Module and Self-Repairable Switching Circuit Block 103               |

|-------------------------------------------------------------------------------------|

| Figure 5.2 Inner Structure of the Switching Circuit Block                           |

| Figure 5.3 Structure of MSCI Array107                                               |

| Figure 5.4 Structure of the NSC Register108                                         |

| Figure 5.5 Structure of the NR Register                                             |

| Figure 5.6 Structure of the MCIR Register112                                        |

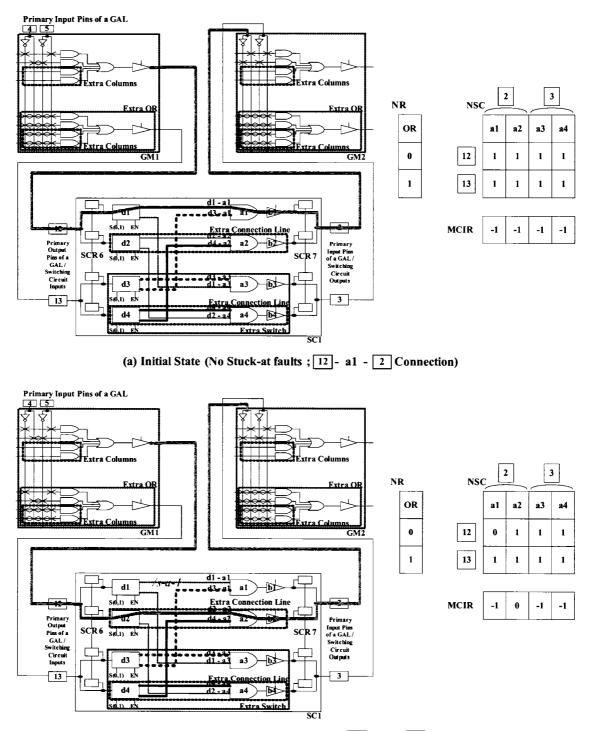

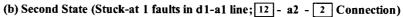

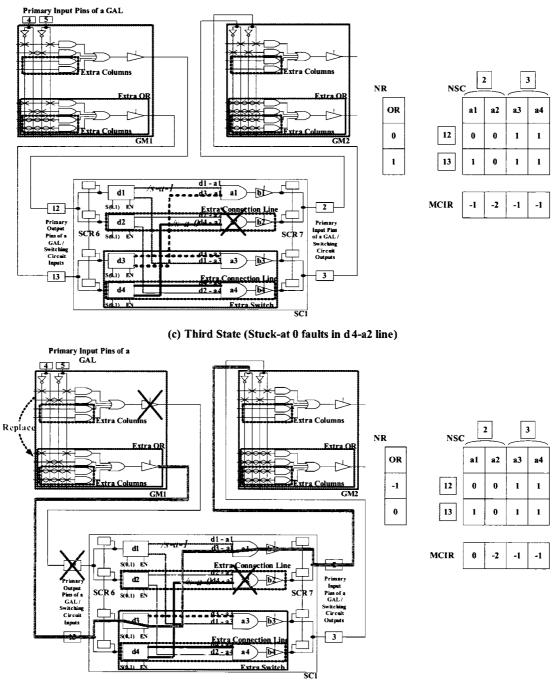

| Figure 5.7 General Concept of an Example without Faults                             |

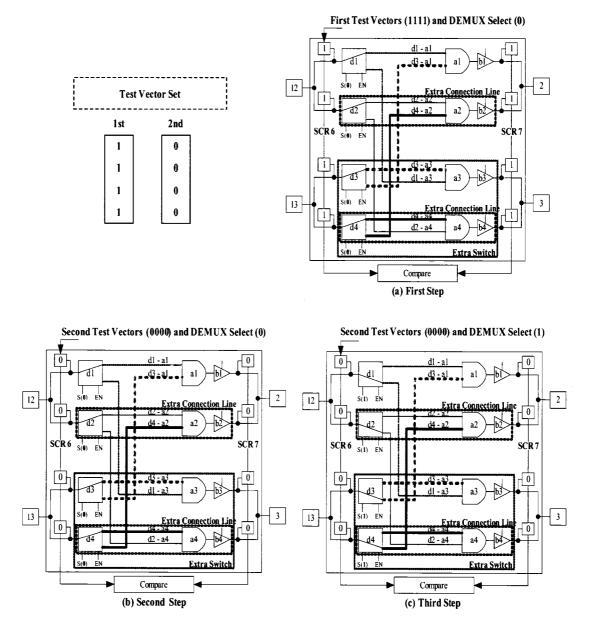

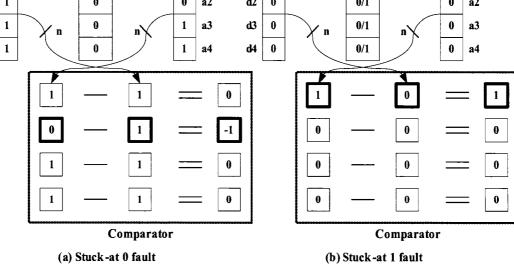

| Figure 5.8 Generation of the Test Vector Set/Storing Scanning Results into SCR7 116 |

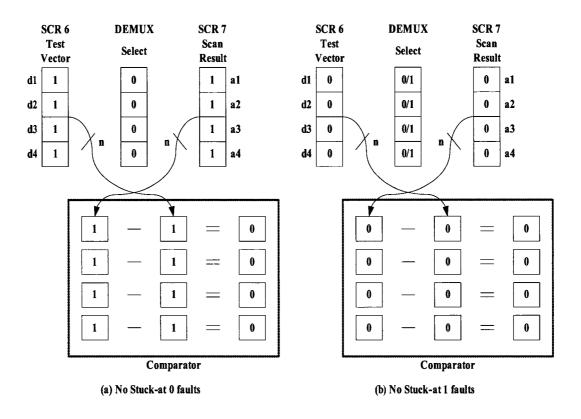

| Figure 5.9 Comparator Operation for Finding Faults on an SC without Faults 118      |

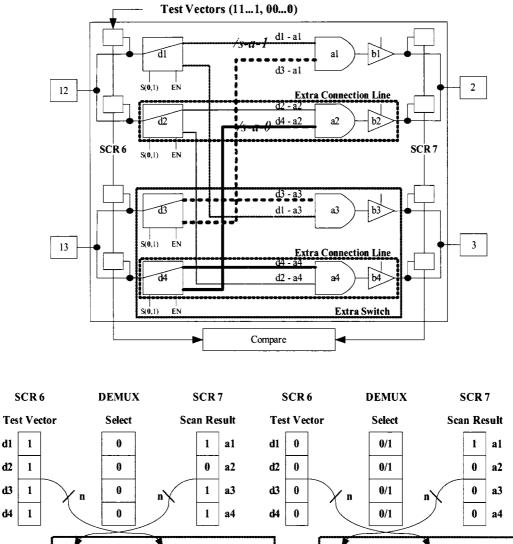

| Figure 5.10 Fault Diagnosis/Location of an Example with Faults                      |

| Figure 5.11 A Line Replacement Method Example of Multiple Faults without a Faulty   |

| OR                                                                                  |

| Figure 5.12 A Line Replacement Method Example with a Faulty OR126                   |

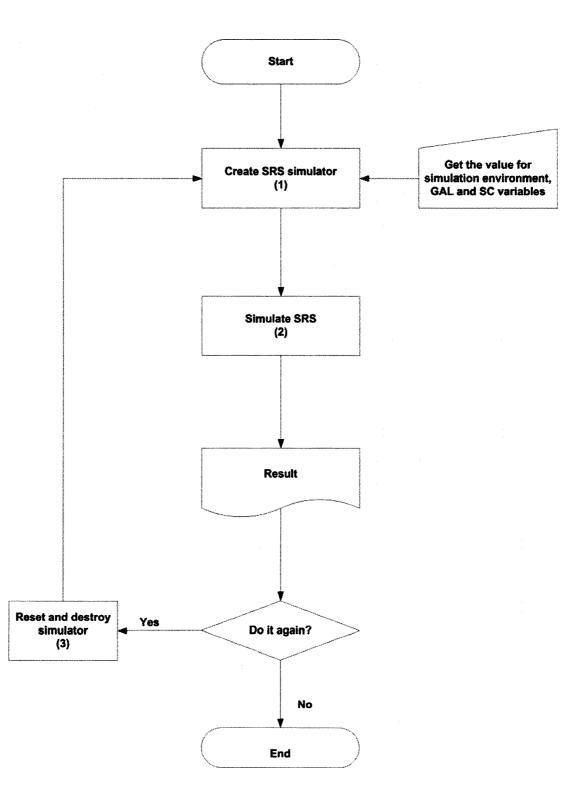

| Figure 6.1 Overall Process                                                          |

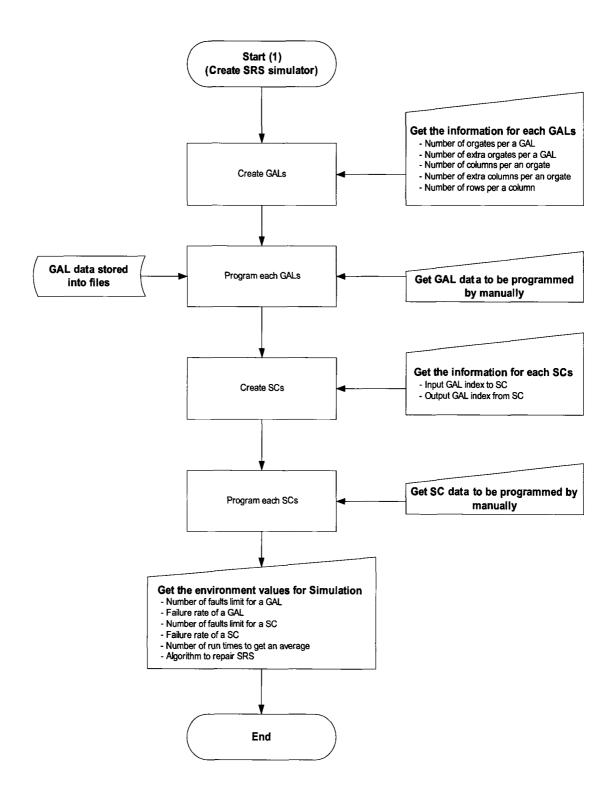

| Figure 6.2 GAL and SC Generation                                                    |

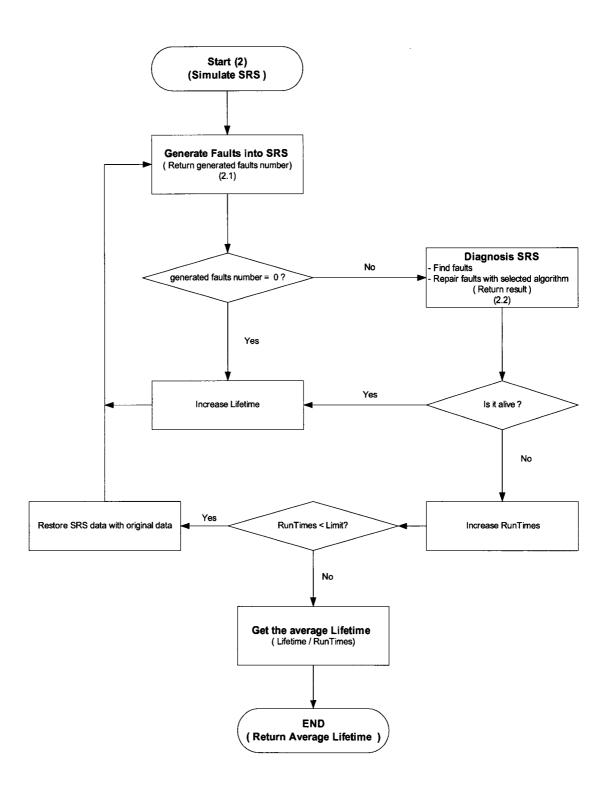

| Figure 6.3 System Lifetime Generation                                               |

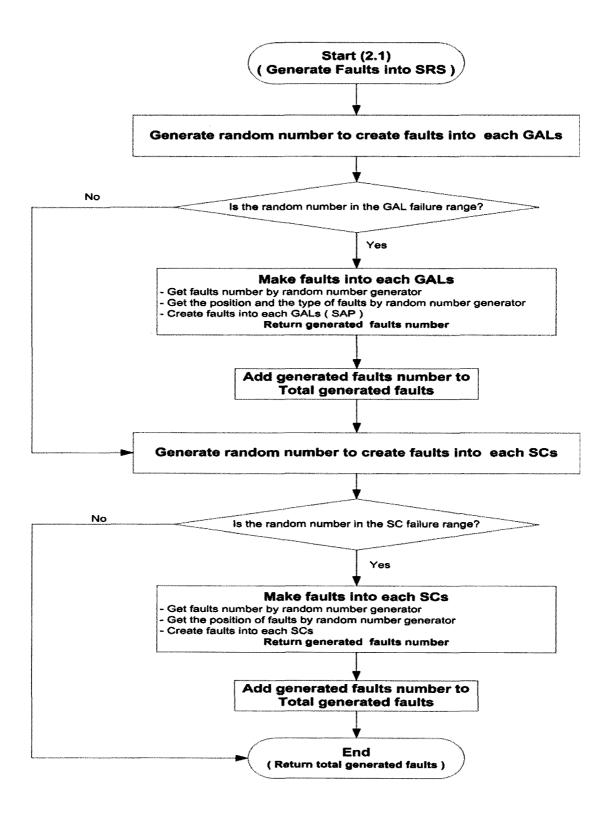

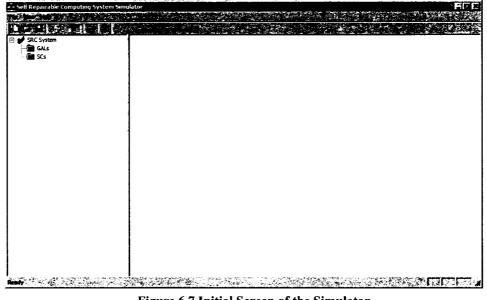

| Figure 6.4 Fault Generation Simulation                                | 135 |

|-----------------------------------------------------------------------|-----|

| Figure 6.5 System Diagnosis Process                                   |     |

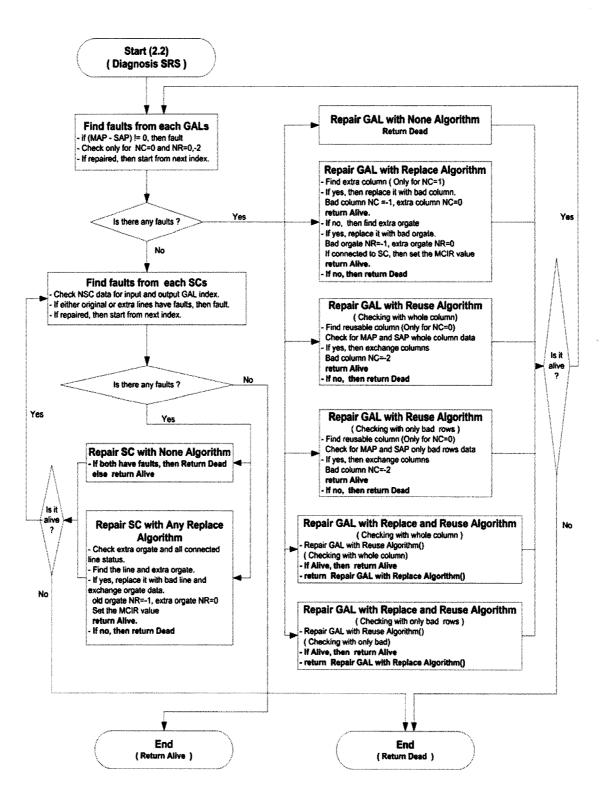

| Figure 6.6 Simulator Reset Process                                    | 139 |

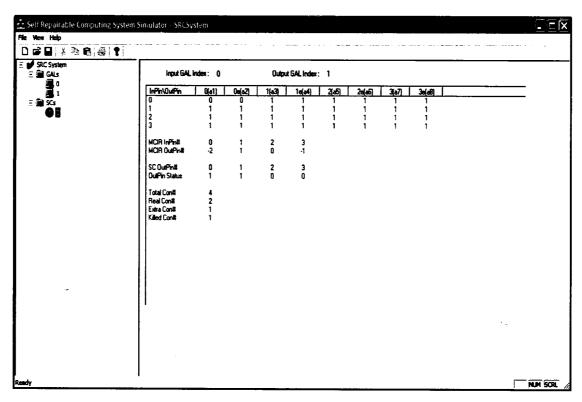

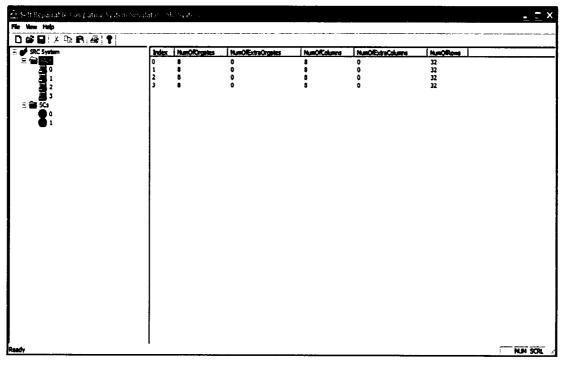

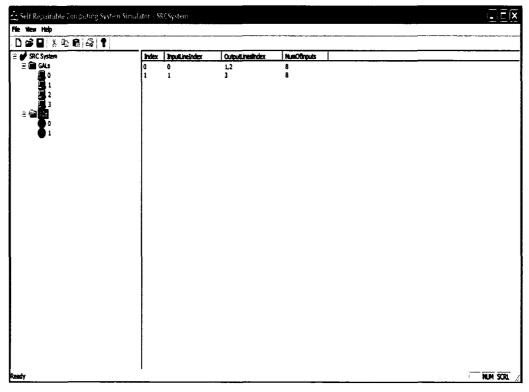

| Figure 6.7 Initial Screen of the Simulator                            | 141 |

| Figure 6.8 Creating GAL Options                                       | 141 |

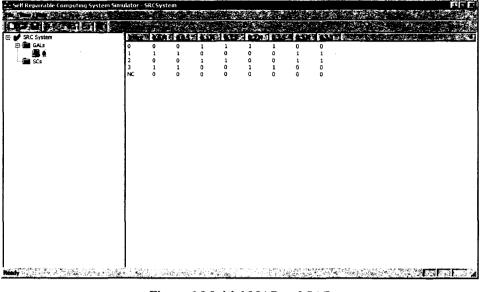

| Figure 6.9 Initial MAP and SAP                                        | 143 |

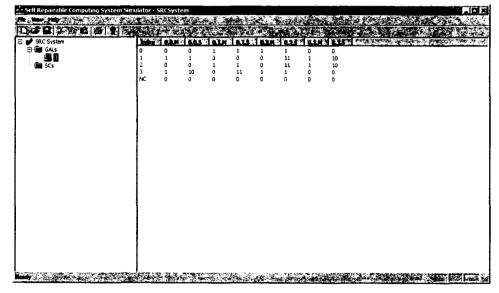

| Figure 6.10 Added Faults                                              |     |

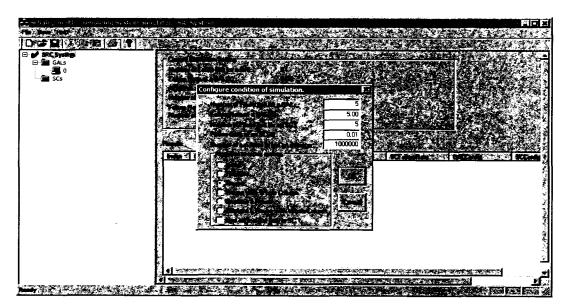

| Figure 6.11 Simulation Configuration                                  | 144 |

| Figure 6.12 Simulation Result                                         | 145 |

| Figure 6.13 Initial Screen of the Replacement Method                  | 146 |

| Figure 6.14 Replacement Method Result                                 | 147 |

| Figure 6.15 Initial Screen of Column Re-Use with Extra Columns Method | 148 |

| Figure 6.16 Column-Re-Use with Extra Columns Method Result            | 149 |

| Figure 6.17 Initial Screen of Cell Re-Use Method                      | 150 |

| Figure 6.18 Cell Re-Use Method Result                                 | 152 |

| Figure 6.19 Extra OR-gate Initial Screen                              | 153 |

| Figure 6.20 Extra OR-gate Result                                                   |

|------------------------------------------------------------------------------------|

| Figure 6.21 Switching Circuit Initial Screen                                       |

| Figure 6.22 SC 2                                                                   |

| Figure 6.23 SC 3                                                                   |

| Figure 6.24 SC Final158                                                            |

| Figure 6.25 ASIC Initial Screen                                                    |

| Figure 6.26 ASIC 2                                                                 |

| Figure 6.27 FPGA Initial161                                                        |

| Figure 6.28 FPGA 2162                                                              |

| Figure 6.29 Typical Simulation Result                                              |

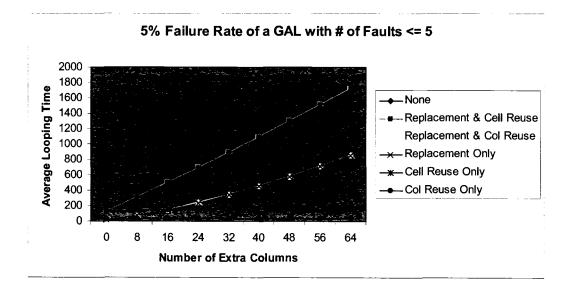

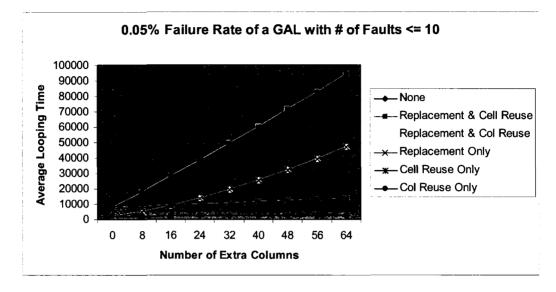

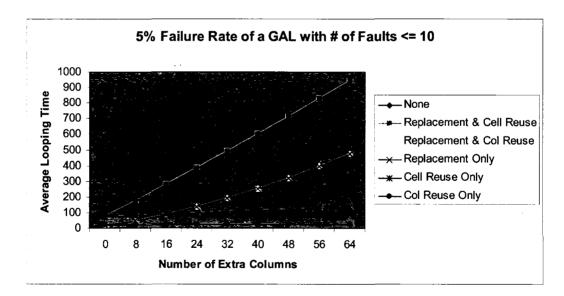

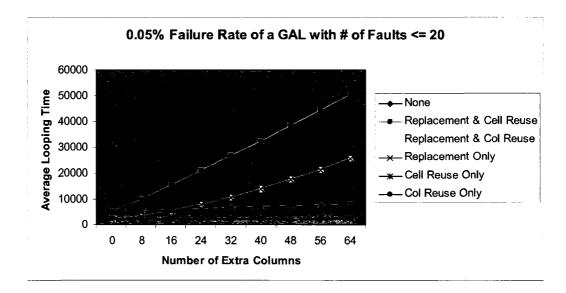

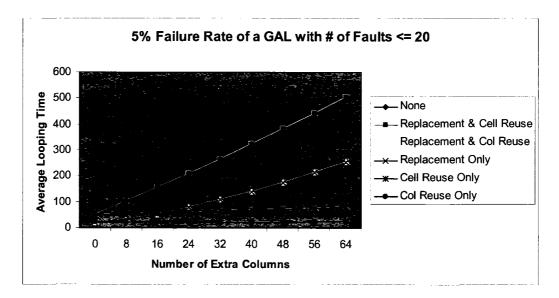

| Figure 7.1 Comparison of Average Looping Time for All Methodologies with the Fault |

| Limit less than or equal to 5 and 0.05% Failure Rate                               |

| Figure 7.2 Comparison of Average Looping Time for All Methodologies with the Fault |

| Limit less than or equal to 5 and 5.00% Failure Rate                               |

| Figure 7.3 Comparison of Average Looping Time for All Methodologies with the Fault |

| Limit less than or equal to 10 and 5.00% Failure Rate                              |

| Figure 7.4 Comparison of Average Looping Time for All Methodologies with the Fault |

|------------------------------------------------------------------------------------|

| Limit less than or equal to 10 and 5.00% Failure Rate                              |

| Figure 7.5 Comparison of Average Looping Time for All Methodologies with the Fault |

| Limit less than or equal to 20 and 5.00% Failure Rate                              |

| Figure 7.6 Comparison of Average Looping Time for All Methodologies with the Fault |

| Limit less than or equal to 20 and 5.00% Failure Rate                              |

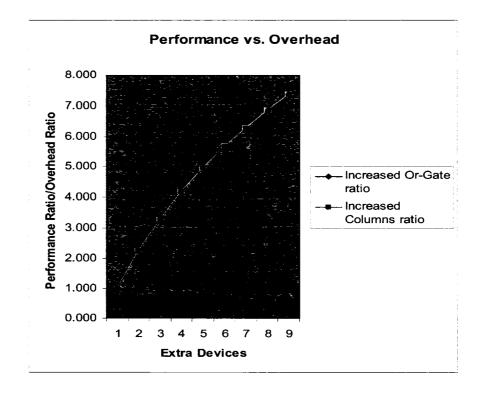

| Figure 7.7 Performance Ratio/Overhead Ratio of Increased OR-Gate vs. Columns. 190  |

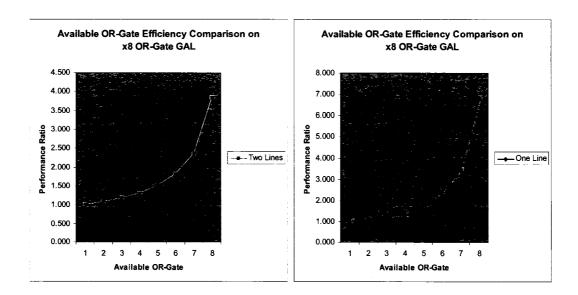

| Figure 7.8 Available OR-Gate and Performance Increase (One Line: No Extra Line &   |

| Two Lines: 1 Extra Line in each Pin-to-Pin Connection)                             |

# 1. Introduction

Post-fabrication self-repair of digital circuits that have to work in adverse conditions such as increased cosmic radiation is not a new idea. Refer to the research of the "Hundred Year Spacecraft" in NASA [1] for instance. However, such circuits have not been built in VLSI and so far not much has been published on the subject, except in the area of memories. Although the self-repair problem is already important to current technologies, it will become a necessity when the next scientific revolution of "molecular engineering" or "nanotechnology" creates molecular computers [2,3,4,5] that will be implanted in the human body. In high reliability applications such as these, a circuit should not only test itself but also repair itself as quickly as possible.

There has been a very little research on diagnosis-based self-repair at the logic level. There are a few existing publications presenting various ideas for PLA (Programmable Logic Array) and PLA-based circuits [6,7,8,9,10,11]. However, to our knowledge, the circuits analyzed by other authors were not designed nor even simulated for reliability analysis. We want to systematically develop designs for selfrepair methodologies on levels of systems, blocks, and logic/layout, with the minimum overhead.

### **1.1. Motivations and Real Problems**

This section describes the reasons why we need to research self-testable and selfrepairable digital devices according to regular-structured programmable logic device's realm as well as memories based on EEPROM (Electrically Erasable Programmable Read Only Memory) technology. Also introduced here are the realistic problems in today's world of technology.

# 1.1.1. Two-level Regular-Structured Programmable Logic Devices

### • GALs; AND-OR Based Arrays

PLDs (Programmable Logic Devices) have become extremely popular in modern systems since they can be reprogrammed simply and inexpensively without making time-consuming PCB (Printed Circuit Board) changes as was required by earlier designs that used random logic ICs [12,13,14]. The following citation evaluates the PLD market [25]:

Market for PLDs heats up: (from Semiconductor Business News, Nov. 1997)

- Industry revenue in PLDs was expected to grow 22.7percent in 1997 to \$2.26 billion, compared to \$1.84 billion in 1996.

- In new market forecast update, the research company predicted world wide sales of user programming logic devices will increase by a 23.2 percent compound annual growth rate, reaching \$5.24 billion in 2001.

PLDs use various programming technologies such as fusible link, E<sup>2</sup>CMOS, and others. PLDs allow easy implementation of a variety of logic circuits using EDA (Electronic Design Automation) tools. However, as the complexity of digital devices increases and the chips' geometry shrinks, the probability of developing faulty components (input/output lines, and product terms) also increases as components age [15].

Thus, in-circuit testing of PLDs, especially PLAs (Programmable Logic Array), has become of primary importance and has attracted the attention of large research community [6,7,8,9,10,11]. In high-reliability applications, the circuit should test itself in real-time and repair itself as early as possible. This requires special logic built into a chip to make it easily testable and diagnosable as well as self-repairable by means of hardware re-programmability. If the high-reliability and quick in-field repair of a digital system is of the primary importance, and a system with only selftesting is not sufficient, then the addition of a self-repairing system would be highly desirable. As far as we know, nothing has been previously published on self-repair of PLDs such as GALs or similar devices.

Computers and other digital systems are subject to any number of faults caused by inadequate quality control during manufacturing, the wear and tear of normal operation, and other. Failures occur in CMOS due to manufacturing defects and due to wear out mechanisms whose effects accumulate over time [22]. External disturbances such as heat, radiation, and electrical and mechanical stress also increase the failure rate [22].

The failure rate and yield calculation of digital ICs has been surveyed in order to understand better the real problem; actually how and which faults are likely to occur in the real world. Particularly, failure rate of EEPROM is concerned, since our first target model, GAL, uses EEPROM technology with E<sup>2</sup>CMOS cells in a programmable AND array. Memories are particularly sensitive to aging as a function of cycling.

Now, we refer to the Early Failure Rate (PPM; Parts Per Million devices or DPM; Defects Per Million devices from 0 year to 1 year) and the Long Term Failure Rate (FIT; Failures In Time from 0 year to 10 years) from data provided by National Semiconductor Corporation. Early failure rates were calculated at 60% confidence using the Chi-Square distribution. Long term failure rates were calculated at 60% confidence using the Arrhenious equation at 0.7eV activation energy and derating the stress temperature to an application temperature of 55°C [23,24]. The data used to calculate the failure rates were obtained from high temperature operating life tests (OPL) performed on product qualification and long term audit (LTA) programs during the period from May 4, 1998 to May 4, 1999 [23]:

0.35μm CMOS: Early Failure Rate = 194 PPM, FITs = 4.66 %

0.50μm CMOS: Early Failure Rate = 141 PPM, FITs = 14.34 %

EEPROM: Early Failure Rate = 489 PPM, FITs = 5.07 %

The values of the PPM and FIT of EEPROM shown above suggest that it is reasonable to invest in a repair mechanism. These data are used to simulate our repair algorithm of the first project in order to get practical and useful information in Chapter 6 and Chapter 7.

### 1.1.2. Memories

Memory is a big part of any system, and is critical for building a system, today. According to San Jose-based Gartner Dataquest, by 2005, 70 % of the chip's surface will be memory [34]. While the embedded microprocessor and DSP (Digital Signal Processing) cores are essential in defining the system architecture, embedded memory is key to ensure design manufacturability at cost-effective levels. However, we note that memory is a magnet for defects during IC manufacturing because it has twice the defect densities that logic design has [34]. With design productivity doubling only every 39 months, a "design gap" has opened [35]. Design reuse and the availability of semiconductor IP (Intellectual Property) is being cited as the only way to close this gap so that silicon is not underutilized and products are not late to market [35]. The inspection result from [37] shows a fairly high failure rate of DRAM with 0.35µm design rules; the ratio of electrical failures caused by detected defects is 57%, and the results obtained on DRAMs (Dynamic Random Access Memories) can be accurately extrapolated to ASIC (Application Specific Integrated Circuit) products. Gaitonde [38] describes a methodology to accurately predict the probability of fatal faults and yield in array-based ASICs using the DEFAM (DEtect to FAult Mapper); the yield is around 65% under 95% transistor utilization in both the traditional yield estimation and the circuit-based yield estimation, and in 50% transistor utilization, yield based on traditional estimates is 70% and circuit-based yield is 75%. The yield simulator VLASIC (VLSI LAyout Simulation for Integrated Circuits) has been developed for determining functional yield in [39].

Memories are particularly sensitive to aging as a function of cycling. Failure analysis is important in the case of high performance systems, such as air and space assets, where usage of EEPROM [40] is high. The aging process is difficult to study, as it requires observation times of the order of the lifetime of the systems. It has been common practice to rely on the thermal stress as a way to accelerate the aging process, thus enabling experimental measurements in a typical laboratory time scale. On average software changes in an F/A-18 type asset are implemented every 18-24 months, and during these changes, the EEPROM memory banks of the on-board computers are programmed without avionics removal through a nose wire harness.

During these changes when many memory failures are observed, the verification of performance of the on-board EEPROM devices is needed. The typical failure rates of the EEPROM with respect to the aging problem or wear out over time, under testing of large number of EEPROMs, are 4.35 errors per million device cycles with first error occurring after around 200,000 cycles. The problem of EEPROM in an abnormal condition such as a military temperature range is discussed in [41]. The gate oxide wear out failures and the difference between defect rates in predicted level and in actual level are discussed in [42] and [43], respectively.

When we consider only stand-alone memory, EEPROM, it is a useful device and stores nonvolatile data. However, it suffers from a serious deficiency that is absent in other nonvolatile storage devices. For instance, a magnetic disk has no limit on the number of erase/write cycles for a location, but the finite number of erase/write cycles

for any byte location in EEPROM often limits the disk's performance and utility. Today's technology limits the most commonly used EEPROMs to 100,000 to 1 million erase/write cycles because the erase function degrades the oxide barrier on the silicon and eventually leads to failure [36]. If one byte is erased and written per second in for example, a personal-safety monitor system or full date-and-time stamp system, the location exceeds its endurance rating in 100,000 to 1 million sec, or approximately 27.7 to 277 hours. Thus, the useful life of the equipment containing this device is to three and one half to 35 days at 8 hours per day of usage [36]. In other words, this device must have self-repairing capability so that the lifetime can be extended. This nonvolatile memory, especially Flash memory, is used in many real life applications; BIOS (Basic Input/Output System), digital cellular phones, digital cameras, LAN (Local Area Network), PC cards for notebook computers, digital set-top boxes, embedded controllers, and other devices.

Also, failure mode analysis of electronic devices is of utmost importance in the case of high performance systems, such as air and space systems that have a large amount of memories. It is therefore important to establish the expected lifetime and to understand the failure modes of these components for procurement and maintenance purposes. With the trend and demand to develop high temperature tolerant electronics, there is an increasing need for repair methodology not only to assure performance reliability, but also to qualify commercial off-the-shelf components for more critical use. This could result in a significant acquisition and maintenance cost saving. If the repair mechanism is used for testing either during the manufacturing process or on outgoing products, the test cost will be decreased and the reliability of the outgoing products will be increased. In other words, it will minimize defect levels at the production test and thereby promote both the cost efficiency and the confidence in the reliability of the outgoing products. Therefore, the second main research target is developing ultra reliable computing systems for high security and safety applications as well as general purpose applications

### **1.2. Domain of the Work**

This section states the objective of the study and describes the scope of the research.

## **1.2.1.** General Research Objectives

The purposes, hypotheses, contributions, and applications of the dissertation are described in this section.

## 1.2.1.1. Purposes and Goals

The purpose of this research is to introduce ultra reliable computing systems based on nonvolatile EEPROM technology; the EPLD (Electrically Programmable Logic Devices), specially a GAL (Generic Array Logic), and develop a design methodology including hardware architecture, and the fault-detecting, fault-diagnosing, fault-locating, and fault-repairing circuitry that allows us detect, diagnose, locate, and repair automatically of all multiple stuck-at faults in nonvolatile cells and a switching circuit in a system that we propose in this dissertation.

### Purpose of the first project

• Introduce the concept of the self-testable and self-repairable EPLDs for high security and safety applications.

- Prove that a self-repairable GAL will last longer in the field.

- Develop a design methodology (the fault-locating and fault-repairing architecture with electrically re-configurable GALs); that will allow us to detect, diagnose, and repair of all multiple stuck-at faults that might occur on  $E^2$ CMOS cells in programmable AND plane of a GAL.

- Develop a self-repairing methodology for EPLDs based on our 3 design architectures;

- Column Replacement with extra columns; the respective faulty elements (E<sup>2</sup>CMOS cells/cross-points) are replaced with the new ones (extra columns) by automatic reprogramming of the chip.

- Column Re-Use with extra columns; the respective faulty elements (E<sup>2</sup>CMOS cells/cross-points) are re-used for columns which have been already programmed if terms' personalities would fit the nature of the existing faults.

- OR Replacement with extra columns; the respective faulty ORs are replaced with the new ones (extra ORs) by automatic reprogramming of the chip.

#### Purpose of the second project

- Introduce the concept of the ultra reliable computing systems for high security and safety applications as well as general purpose applications.

- Prove that the self-healing and re-configurable system design with added repair capability will last longer in the field and can provide higher yields, lower testing costs, and faster time-to-market to the semiconductor industry.

- Introduce the concept of a self-testing and the self-repairing switching circuit based on Demultiplexer structure.

- Develop a design methodology (the fault-locating and fault-repairing architecture with electrically re-configurable GAL modules and self-testing and self-repairing switching circuits); that allows us to detect, diagnose, and repair of all multiple stuck-at faults that might occur on E<sup>2</sup>CMOS cells in

programmable AND plane of a GAL, faulty ORs in a GAL, and faulty lines of a switching circuit in a system.

- Develop a self-repairing methodology for switching circuits based on our design architecture; line Replacement with extra lines; the respective faulty interconnection lines are replaced with the new ones (extra lines) by automatic reprogramming of the chip.

- Develop an evaluation methodology; Evaluate and analyze all self-repairing methods and combinations of self-repairing algorithms, Prove that the lifetime for a GAL-based EPLD that uses our self-repairing methods is longer than the lifetime of a GAL-based EPLD that uses a single self-repair method or no self-repair method;

- Prove how many extra columns and extra ORs a GAL needs and which self-repairing method a GAL uses to guarantee a given lifetime.

- Prove that our most advanced self-repair algorithm, the cell-column reuse with extra column and column replacement method, gives the best results in all the comparisons with our other algorithms.

- Demonstrate that the lifetime of a device can be increased by self-repair capability.

- Estimate an ideal point, where the maximum reliability can be reached with the minimum cost.

- Develop a computer based simulator for implementing our self-testing and self-repairing hardwired algorithm; Self-repair with redundancy and Self-repair with no redundancy

- Develop a computer based simulator for implementing a microcontroller, FLFRP (Fault-Locating/Fault-Repairing Processor) that stores fault location and repair-related data.

- Demonstrate that the lifetime of a GAL can be increased by adding extra columns in an AND array.

- Demonstrate that the lifetime of a GAL can be increased by adding extra ORs in an AND array.

- Demonstrate that the lifetime of a switching circuit can be increased by adding extra lines in a switching circuit.

- Introduce the basic concepts of modeling repairable systems as introductory-level knowledge

- Find how many extra columns a GAL needs to reach a lifetime goal in terms of simulation looping time until a GAL is not useful any more.

# 1.2.1.2. Hypotheses

- The following research hypotheses have been formulated;

- There exists a appropriate built-in self-repair circuitry for reliability, availability, and maintainability

- There exists a efficient self-testing and self-repairing algorithm with no redundancy

- There exists a computer based simulator to represent a repairable device accurately and efficiently.

- There exists a general tool to estimate cost-effect factors for self-testing and self-repairing hardware architecture.

# **1.2.2.** Contributions and Applications

- The proposed research will have following contributions and applications;

- Contribute to high security and safety applications with self-repair capability such as aerospace systems, military systems, and medical instruments.

- Use the self-repairing technique in space, oceanic, and hazardous environments, where replacement of faulty devices cannot be done manually.

- Contribute to general purpose applications with self-repair capability in many real life applications; BIOS (Basic Input/Output System), digital cellular phones, digital cameras, LAN (Local Area Network), PC cards for notebook computers, digital set-top boxes, embedded controllers, and other devices.

- Contribute to the ultra reliable computing systems which will become a necessity for next scientific revolution such as nanotechnology.

- Close design gap, faster time-to-market, lower tests cost, and higher yields to the semiconductor industry.

- Contribute our simulator to simulate the self-repair hardware and to verify how self-repair hardwired algorithms improve the performance of a system in realistic environment.

- Apply the self-repairing method to a FPGA and be expandable for PLAs or EXOR PLAs for ESOP, GRM (General Reed-Muller), FPRM (Fixed Polarity Reed-Muller), and other AND/EXOR canonical forms and AND/EXOR multilevel circuits.

- Applicable to FPGA (Field Programmable Gate Array) design or ASIC (Application-Specific Integrated Circuit) design to shrink the design gap more quickly and affordably by adding redundancy.

- Generalize the stochastic reliable device model and apply it to estimation of cost-effect values.

#### 1.3. Outline

The general statements of the problems are described in Chapter 1. Next chapter introduces several types of PLDs and GALs structure as well as PLDs' programming technology as a prerequisite for our project in this dissertation.

In Chapter 3, the most advanced and related work on memory is described. The literature for memories is reviewed. Especially, BISTAR embedded memories are discussed in industrial point of view with a real product in the market. The BIST and BISR memories from current papers are also examined and evaluated for our project.

In Chapter 4, fault models in the literature are reviewed. Our first project, "self-repairable EPLDs", is explained in detail according to several purposes and contributions; what is the digital system in our approach, and how are the multiple stuck-at faults detected, diagnosed, located, and repaired using either redundancy or no redundancy in a GAL. Our fault model, cross-point stuck-at faults in an E<sup>2</sup>CMOS cell of a GAL, and assumptions also are in Chapter 4.

In Chapter 5, the main project is stated; the self-healing and re-configurable system design with added repair capability is described for the ultra reliable computing systems. For high security and safety applications as well as general purpose applications, a hardware prototype based on EEPROM (Electrically Erasable Programmable Read Only Memory) technology is also introduced. It is deployed to design the general fault-repair circuitry for EEPROM-based digital devices.

In Chapter 6, our computer based simulator is introduced, and our hardwired repairing algorithms are simulated.

In Chapter 7, we analyze and evaluate the simulation results; it demonstrates that the lifetime of a GAL can be increased by adding extra columns in an AND array of a GAL and extra ORs in a GAL, and also gives information on how many extra columns and extra ORs a GAL needs and which self-repairing method a GAL uses to guarantee a given lifetime. Hardware overhead and performance are also discussed in terms of the ratio of efficiency versus cost factor. Thus, we can estimate an ideal point, where the maximum reliability can be reached with the minimum cost.

In Chapter 8, we conclude all the works in this dissertation and discuss potential future work and trends of the semiconductor industry.

# 2. Prerequisites for the Self-Repair Technology

This chapter introduces PLDs, especially PAL and GAL, the E<sup>2</sup>CMOS programming technology, and the PLDs' programming procedure.

#### 2.1. Introduction to PLDs

The background of PLDs is briefly explained, and the PAL/GAL, which is our model of this first project, is described in more detail. The E<sup>2</sup>CMOS programming technology and PLDs' programming procedure are also shown concisely in this sub section.

#### 2.1.1. What is PLD?

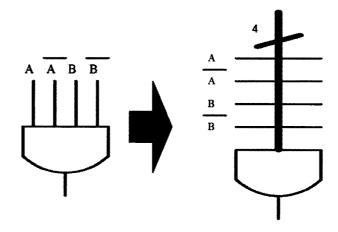

A PLD (Programmable Logic Device) is normally composed of a specific number of input lines connected through a fixed or programmable array to a set of AND gates, which are in turn connected to a fixed or programmable array of OR gates [14]. The OR gates provide the output signals from the logic array. Note that a simple array will be used to graphically describe complex PLD structures: we will use special notation shown below, because a typical PLD has many inputs, outputs, and product terms. The modified AND input lines, likewise OR input lines, are also shown to simplify many input lines of an AND gate as in Figure 2.1.

Figure 2.1 Simplified Notation for Input Lines of an AND Gate

#### 2.1.2. Types of PLDs

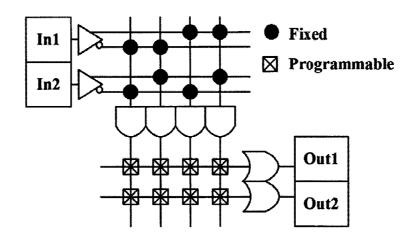

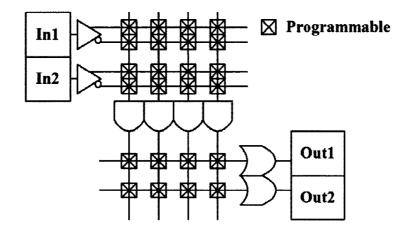

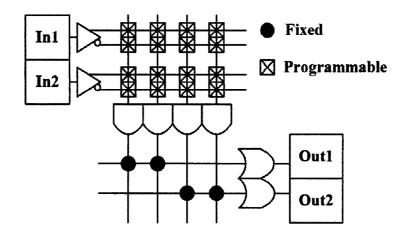

There are generally four types of PLDs; PROM (Programmable Read Only Memory), PLA (Programmable Logic Array), PAL (Programmable Array Logic), and GAL (Generic Array Logic) [14,44,45]. The PROM has a fixed AND array and a programmable OR array. It is usually used as memory, and a logic diagram of a PROM is shown in Figure 2.2.

Figure 2.2 Basic Structure of a PROM

Figure 2.3 Basic Structure of a PLA

Figure 2.3 shows the basic structure of a PLA. The PLA has a programmable AND array and a programmable OR array. It is invented to improve constraints of a fixed AND array in a PROM, and can be programmed by users rather than manufacturers. It is also called to FPLA (Field Programmable Logic Array).

The basic structure of a PAL and a GAL is shown in Figure 2.4.

Figure 2.4 Basic Structure of a PAL/GAL

#### 2.1.3. PAL

The Programmable Array Logic (PAL) device is a special case of the PLA. The PAL is one of today's most commonly used types of PLDs [12,14,16]. It has a fixed OR array and a programmable AND array, and is the registered trademark of

Advanced Micro Devices, Inc. (AMD) in the late 1970's. The key innovation of the PAL is the use of fixed OR array and bi-directional input/output pins. The PAL16L8 is probably the today's most commonly used combinational PLD structure.

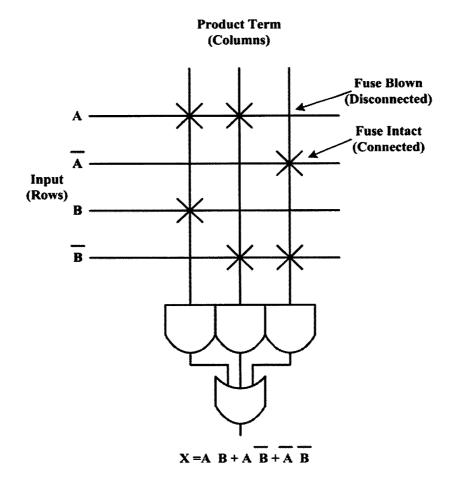

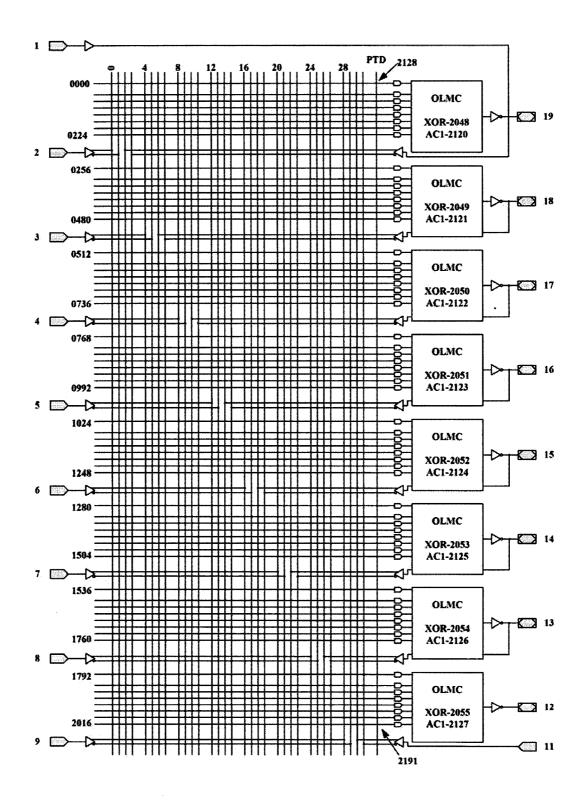

The PAL16L8 has 64 columns (product terms) and 32 rows (inputs), therefore there are 2048 (64x32) fusible links to be programmed in an AND array. Each of the 64 AND gates in the array has 32 inputs, accommodating 16 variables and their complements, and each of eight OR gates is associated with output pin in the PAL16L8. Each product term can be a function of any subset of the 16 inputs. A simplified logic diagram of a PAL is shown in Figure 2.5. The notation 'X' denotes that the cross-points between each input line and each AND gate is connected with a fusible link.

Figure 2.5 Simplified Logic Diagram of a PAL

#### 2.1.4. GALs Structure

Lattice Semiconductor company introduced GAL devices such as the GAL16V8 in the mid 1980's. A GAL16V8 has a fixed OR array and a programmable AND array. The re-programmable array is essentially a grid of conductors forming rows and columns with an electrically erasable CMOS ( $E^2$ CMOS) cell at each cross-point, rather than a fuse as in a PAL [16, 17, 18]. The programmed state of a simple logic function is schematically shown in Figure 2.6.

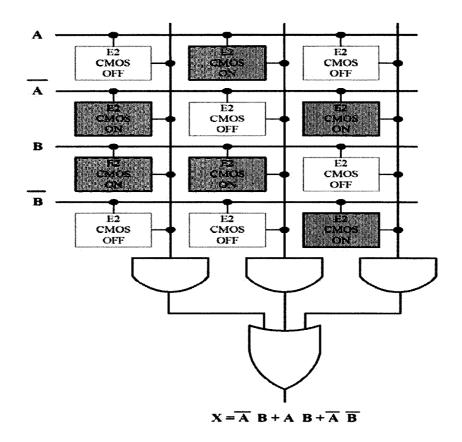

Figure 2.6 A Programmed Simple Logic Function in a GAL

The GAL16V8 provides 3.5ns maximum propagation delay, 250MHz clocking, full programmability, low power consumption, and 100 erase/write cycles [16]. Each column is connected to one input of an AND gate, and each row is connected to an input variable or its complement. Any combination of input variables or complements can be applied to an AND gate to form any desired product term by programming each  $E^2$ CMOS cell to be either 'ON' or 'OFF'. A cell that is ON effectively connects its corresponding row and column, and a cell that is OFF disconnects the row and column. The cells can be electrically erased and reprogrammed. A GAL has the programmable AND array and OLMCs (Output Logic Macro Cells) that contain OR gates and flipflops [18]. The  $E^2$ CMOS cell makes our self-repairing methodology possible. Thus, we choose as our model in this project the GAL16V8, which is a simple low density PLD.

For the more detailed description of pins and configurations the reader is referred to a GAL data book from Lattice Semiconductor, Inc. The sixteen primary inputs which include feedback paths from the OLMC are considered for this project, thus there are 32 input lines, which come with complements of each input variable, in the AND array. The eight primary outputs and eight product terms per an OLMC are considered in our model, thus there are 64 (8X8) product terms in this model. Therefore, the total number of  $E^2CMOS$  cells (cross-points) is 2048.

Figure 2.7 Structure of the GAL16V8

### 2.2. Programming Technology

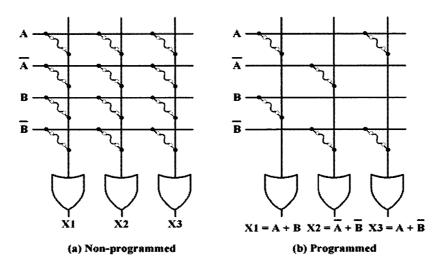

The PLD has a generalized structure as an array for data inputs and each gate to program PLDs. The OR arrays can implement logical sums and the AND array can implement logical products. These arrays use the fusible link or the E<sup>2</sup>CMOS cell to make connections between the data input lines and the gate input lines.

#### 2.2.1. Fusible Link

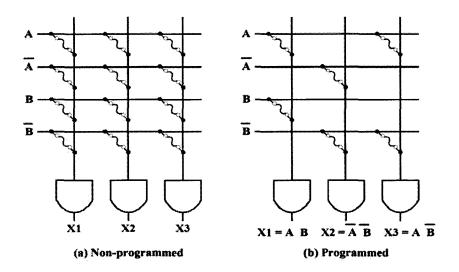

Figure 2.8 and Figure 2.9 schematically show the basic structure and nonprogrammed/programmed states of which the PLDs are programmed in an OR array and an AND array with fusible links.

Figure 2.8 (a) Non-Programmed State and (b) Programmed State in Basic Structure of an OR-

Array

Figure 2.9 (a) Non-Programmed State and (b) Programmed State in Basic Structure of an AND-Array

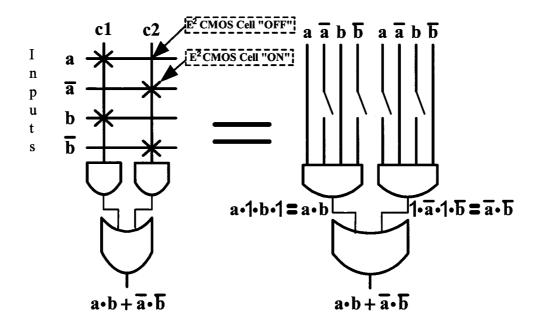

# 2.2.2. E<sup>2</sup>CMOS Programming Technology

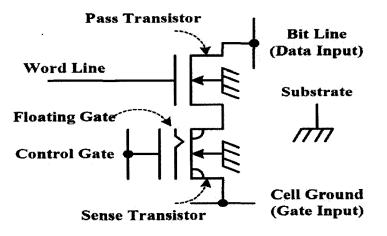

The  $E^2$ CMOS technology is based on a combination of CMOS and NMOS technologies and is used in GALs [45]. The following figure shows an  $E^2$ CMOS cell structure.

Figure 2.10 E<sup>2</sup>CMOS Cell

The cell is programmed by applying a programming pulse to either the control gate or bit line of a cell that has been selected by a voltage on the word line. During the programming cycle, applying a voltage to the control gate to make the floating gate negative first erases the cell. This leaves the sense transistor in the OFF (storing a 1). A write pulse is applied to the bit line of a cell in which a 0 is to be stored. This will charge the floating gate to a point where the sense transistor is ON (storing a 0). The bit stored in the cell is read by sensing presence or absence of a small cell current in the bit line. When a 1 is stored, there is no cell current because the sense transistor is ON.

Once a bit is stored in a cell, it will remain indefinitely unless the cell is erased or a new bit is written into the cell. If the  $E^2$ CMOS is ON, data input can be transmitted to the gate input (AND gate input of a GAL). If the  $E^2$ CMOS is OFF, data input cannot be transmitted to the gate input (AND gate input of a GAL). The bit line (data input) and the cell ground (gate input) of Figure 2.10 are corresponding to the horizontal line and vertical line of Figure 2.6, respectively. The word line and the control gate are not shown in Figure 2.6.

#### 2.2.3. PLDs' Programming Procedure

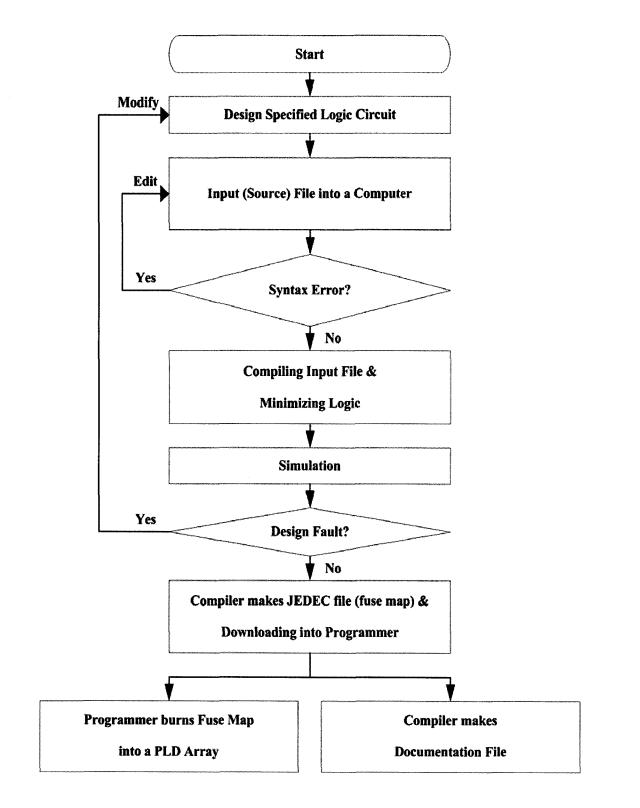

Generally, it needs a programming software (a logic compiler), a personal computer which mounts the software, and the software-driven programmer to program PLDs. A personal computer should satisfy requirements of software and programmer, like microprocessor type, memory amount, OS, and etc. ABEL, CUPL, OrCAD-PLD, LOGiC, PLDesigner, TANGO-PLD, and others can be used as the programming software. These software packages operate and synthesize the logic designs, transform these logic designs into intermediate files, produce JEDEC (Joint Electronic Device Engineering Council) files, and simulate and debug these logic designs. The JEDEC file which has cross-point's programming information is also called Cell Map or Fuse Map. Boolean equation, truth table, state machine, schematic, timing waveform, hardware description, and etc. are used as a method of presenting logic designs to the programming software. Finally, according to the Fuse Map of JEDEC file, softwaredriven programmer implements PLDs after a PLD is put on programmer socket, called ZIF (Zero Insertion Force) socket.

To implement logic designs on PLDs, designer has to specify them with Boolean equations or other specifications. The produced input or source file is put on programming software, and debugged by syntax error checking. These are compiled and the compiler minimizes the logic. The logic designs are simulated with a set of test vectors. The programming software provides JEDEC file, and this file is downloaded into a programmer. The Fuse Map has cross-point information, in a GAL case, it will tell whether E<sup>2</sup>CMOS cell is ON or OFF. The flowchart of this procedure is shown in Figure 10.

Figure 2.11 PLDs' Programming Procedure

# 3. Previous Work on Self-Test and Self-Repair

#### **3.1. Self-Healing Memories**

Most of the research activities on self-repair techniques were focused on FPGA [65,66,67,68,69]. BIST and BISR schemes have been proposed as potential solutions to the problem of repairing memories, mainly at the manufacturer level [70,71,72,73,74,75,76]. Recently, new techniques have been introduced to perform a memory repair through self-reconfiguration of the addressing space [77,78,79]. The paper [78] considers a column-only repair strategy to simplify the spare allocation procedure, and the paper [80] introduces on-line BIST RAM architecture based on cell-only redundant space allocation at the user level. In this section, several types of memories are described and the self-healing memories are reviewed from the literature. The self-testing and self-repairing algorithms are examined as well as the hardware architecture designs. The trend and product of the BISTAR embedded memories are introduced from the industry in this section.

# 3.1.1. Introduction to Memories; SRAM, DRAM, and Flash Memory

#### 3.1.1.1. SRAM

SRAM is random access memory that retains data bits in its memory as long as power is being supplied. Unlike dynamic RAM, which stores bits in cells consisting of a capacitor and a transistor, SRAM does not have to be periodically refreshed. Static RAM provides faster access to data but is more expensive than DRAM. SRAM is used for a computer's cache memory and as part of the RAM digital-to-analog converter on a video card.

#### 3.1.1.2. DRAM

Dynamic random access memory is the most common kind of RAM for personal computers and workstations. Memory is the network of electrically charged points in which a computer stores quickly accessible data in the form of 0s and 1s. Random access means that the PC processor can access any part of the memory or data storage space directly rather than having to proceed sequentially from some starting place. DRAM is dynamic in that, unlike SRAM, it needs to have its storage cells refreshed or given a new electronic charge every few milliseconds. Static RAM does not need refreshing because it operates on the principle of moving current that is switched in one of two directions rather than a storage cell that holds a charge in place. DRAM stores each bit in a storage cell consisting of a capacitor and a transistor. Capacitors tend to lose their charge rather quickly; thus, the need for recharging.

#### 3.1.1.3. Flash Memory

Flash memory (sometimes called "flash RAM") is a type of constantly powered nonvolatile memory that can be erased and reprogrammed in units of memory called blocks. It is a variation of EEPROM that, unlike flash memory, is erased and rewritten at the byte level, which is slower than flash memory updating. Flash memory is often used to hold control code such as the basic input/output system (BIOS) in a personal computer. When BIOS needs to be changed (rewritten), the flash memory can be written to in block (rather than byte) sizes, making it easy to update. Flash memory gets its name because the microchip is organized so that a section of memory cells are erased in a single action or "flash." The erasure is caused by Fowler-Nordheim tunneling in which electrons pierce through a thin dielectric material to remove an electronic charge from a floating gate associated with each memory cell. Intel offers a form of flash memory that holds two bits (rather than one) in each memory cell, thus doubling the capacity of memory without a corresponding increase in price.

# 3.1.2. Research on the BISTAR Embedded Memories: Trends and Products

Several parallel processors which have self-repair property based on processor/switch level reconfiguration have been presented in literature and some of them have been built [51,52,53]. The research on memory faults has been published in which the faults were localized and ICs were repaired in the production process by laser trimming or other techniques. However, laser repair is becoming increasingly expensive and is requires dedicated expertise. Now, the fuse based hard repair turns into soft repair, namely Built-In Self-Repair (BISR), which includes the storage of repair data and controls the soft reconfiguration mechanism. Yervant Zorian said the integrated BIST and self-repair on the chip is becoming more feasible in the growing numbers of ICs with embedded DRAM and system-level LSI integrated circuits [63]. Today's large embedded static/dynamic RAM and flash memories are cases in point [54]. A highly reconfigurable Built-In Self-Test, Diagnosis, and Repair (BISTDR) solution for embedded DRAMs has been deployed by Genesys Testware and is a part of Memory BIST core. Embedded memories are the most dense components within a system-on-chip, accounting for up to 90% of its real estate. Memories also the most sensitive to process defects [55]. The following two subsections are mainly described in [55,64].

#### 3.1.2.1. Why BIST

The complexity of today's ICs demands that embedded memory testing be taken further than traditional pass/fail testing. As the geometries of ICs become increasingly concentrated, new techniques such as diagnostic testing and built-in self-repair must be implemented into the devices. Many embedded memories are designed with builtin redundancy, which provides spare rows and columns that can replace failing locations. Redundancy enables the manufacturer to repair a number of otherwise defective devices to ensure maximum production yield [55].

These issues are being addressed by the use of built-in self-test (BIST). BIST is the methodology of choice for testing embedded memories within SoC. It offers a simple and low-cost means to test for failures of embedded memories without significantly impacting device performance.

While it has been used primarily for production pass/fail testing, BIST can be extended to provide the diagnostic data required for process monitoring and repair. Although the area overhead required by the BIST circuitry is increased, designing the diagnostic circuitry into the BIST provides many advantages in terms of time for both setup and test [55,56,57]. The overview of memory testing procedures and the BIST are found in [55,58,59,60,61,62,64].

#### • BIST advantages

- Lower cost of test

- Better fault coverage

- Possibly shorter test times

- Tests can be performed throughout the operational life of the chip

#### • BIST disadvantages

- Silicon area overhead

- Access time

- Requires the use of extra pins

- Correctness is not assured

#### • **BIST Circuitry**

In the basic BIST architecture, each memory is tested by a BIST block that supplies a series of patterns to the memory, usually march tests or checkerboard patterns, and then compares the outputs against a set of expected responses. Because the patterns are highly regular, the outputs from the memories can be compared directly to the reference data using a comparator. This ensures that an incorrect response from the memory will be immediately flagged as a test failure.

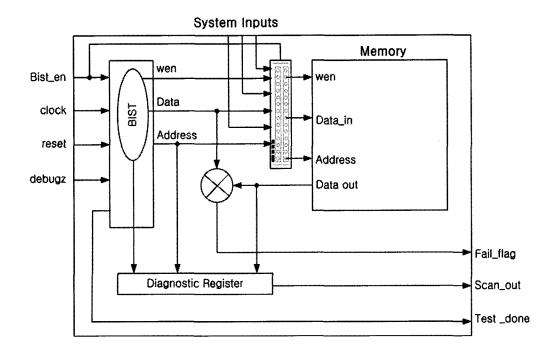

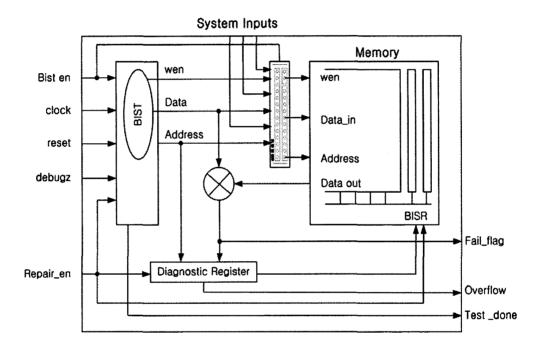

Two schemes have proven popular. The first uses the BIST circuitry to identify each failing location and then to serially scan out the fail data. Figure 3.1 illustrates how this process is added to the basic BIST architecture. The BIST controller is augmented with additional circuitry and has an additional debug enable input (debugz) and scan output (scan out).

Figure 3.1 The BIST Augmented Architecture

The BIST controller operates in two modes: production BIST and diagnostic BIST. In production BIST, the BIST controller performs the default test and quickly identifies a passing or failing device. The failing devices then are run off-line using the diagnostic BIST mode. In this mode, when the BIST controller detects a mismatch, it will suspend the application of the test, and the failing data will be serially scanned out of the controller through the scan\_out port. The failing data scanned out consists of the data output from the memory, the address at which the failure occurred, and if required, the actual operation within the test algorithm being applied. This scheme requires only two additional ports per BIST controller and an interrupt handling mechanism in the tester software to detect the failure and capture the fail data. And because only the failing data is extracted from the device, this method ensures that additional application time is minimized. The total testing time depends on the number of failures in the test and may not be identical from device to device. For devices with few defects such as those manufactured in mature processes, this method is an effective means of extracting fail data.

A second mechanism makes use of a small diagnostic data bus and repeats the BIST operation many times to view a different slice of the memory output for each run [57]. Because the entire memory bit map is captured, a large requirement is placed on ATE (Automatic Test Equipment) pattern memory, usually resulting in a longer test application time than the scan method. The application time, although longer, is uniform for each corresponding memory regardless of the defects present. A memory test option (MTO), if available on the ATE, can relieve the large memory requirements of the pattern memory [56]. The MTO generates patterns algorithmically and can be configured to create identical patterns to the BIST and be used as the reference source.

#### 3.1.2.2. Redundancy and Repair

The use of redundancy and repair is not uncommon today, but the process of repair is tedious because it traditionally has required the use of external lasers. Built-In Self-Repair goes hand in hand with BIST as it simply takes advantage of the on chip processor to route around bad memory bits rather than using expensive and slow lasers to burn out bad memory rows. Typically, only a log of the address locations for each failure is required. For self-repair, only defective address locations must be logged. These are decoded on-chip to identify the failing rows or columns.

Figure 3.2 shows architecture for the BIST required to interface with self-repair (column repair) [55]. On each mismatch, the fail flag latches the address value onto

the decoder which identifies the failing column. At the end of the test, the number of defective columns is compared to those available within the redundancy.

Figure 3.2. BIST Architecture with Column Repair

During the repair process, the repair circuitry is loaded with the values of the columns to be repaired. Once the repair is completed, the BIST is rerun to ensure that the repair produces a functional device.

#### 3.1.2.3. Self-Testing and Self-Repairing Algorithms

The deterministic test algorithms for DRAM chips and Dipilp Bhavsar's algorithm are examined in this sub section.

A truly random design will surely be much smaller than a deterministic one. It would be necessary to build a LFSR (Linear Feedback Shift Register) to produce pseudo-random patterns, but this is much smaller than the counters needed for a deterministic test. It is also important to note that this would not be a truly random test but a repeatable test based on the initial seed. The standard methods of data testing is either to operate in parallel on multiple memory blocks and then check if they concur on a read, or use a set of known seeds and have a compacted form of the output stored as reference output values [64,81,82].

Deterministic memory test algorithms fall into two main categories [64,81,82];

#### • March Tests:

- A March test is a finite sequence of tests to be preformed on every cell in the memory array before moving on to the next cell.

- All cells of the array are subjected to these same tests and traversed in order, either forwards or backwards.

- Runs in time ranging from 4n to 17n.

- Can cover all address faults, stuck-at faults, coupling faults (independent), inked coupling faults, transition faults, and transitions faults linked with coupling faults.

- Neighborhood Pattern Sensitive Tests (NPST):

- A NPSF tests every cell of the memory in relation to its set of 5 or 9 neighboring cells (including the base cell).

- Tests run as long as 195n.

- Test covers the class of active, passive, and static neighborhood pattern sensitive faults.

- These include stuck-at faults and all coupling and transitional faults between physically adjacent memory cells.

#### Bhavsar's algorithm [83];

- It generates and analyzes the required failure-bitmap information on the fly during self-test and then automatically repairs and verifies the repaired RAM arrays.

- It is concept of the condensed maximally repairable sparse failure array.

- It is divide-and-conquer strategy;

- First, partition a large RAM array into small, identical segments

- Second, repair each segment independently of the others.

- Next, provide a spare row and a spare column for each segment.

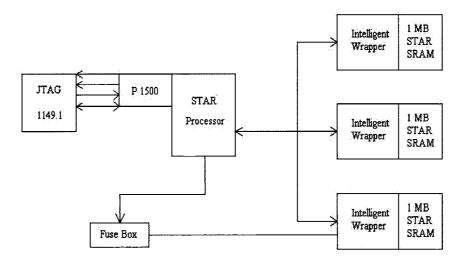

# 3.1.2.4. The STAR (Self-Test and Repair) SRAM Embedded Memory

Virage Logic Corp. claimed development of the industry's first on-chip self-test and repair memory solution for the system-on-chip design. This STAR memory system does not need a expensive ATE and larger-repair tools. Currently, there are three versions of the STAR SRAM (single port 4Mbit and 512Kbit, and dual port 256Kbit). Its test and repair algorithm comes in the form of hardwired logic gates and will fix as much as 99% of the bad bits in an SRAM [78,84]. The test and repair architecture takes advantage of redundant rows and columns of memory. There are 4 test and repair logic components; foundry-specific BIST algorithm, built-in self-diagnostics, repair and redundancy allocation logic, and reconfiguring algorithm for the row and columns to be topologically efficient. The STAR memory system architecture is shown in Figure 3.3.

Figure 3.3. STAR Memory System

# 4. Self-Testing and Self-Repairing EPLDs

The concept of the self-testable and the self-repairable EPLDs (GAL-based structure) for high security and safety applications is described as our first project in this chapter. We developed the fault-locating and fault-repairing architecture with electrically re-configurable GALs to allow detection, diagnosis, and repair of all multiple stuck-at faults that might occur on E<sup>2</sup>CMOS cells in a programmable AND plane of a GAL. Three self-repairing methods are presented based on our design architecture: a column replacement method with extra columns; and two column reuse methods with extra columns, one using the whole column's re-use (simply called column-column re-use) and the other using the only cell's (E<sup>2</sup>CMOS cell's) re-use (simply called cell-column re-use). In first case the respective faulty elements (E<sup>2</sup>CMOS cells, also called cross-points) are replaced with the new ones (extra columns) by automatic reprogramming of the chip. In the latter two respective faulty elements (E<sup>2</sup>CMOS cells/cross-points) are re-used for whole columns or only cells which have been already programmed, if a terms' personalities would fit the nature of the existing faults. All three self-repairing methods use a FLFRP (FaultLocating/Fault-Repairing Processor), diagnosis/repair bus and the memory that stores fault location and repair-related data. In Chapter 7, we propose an evaluation methodology for this project. Our methodology is based on simulating the self-repair algorithms. It shows that the lifetime for a GAL-based EPLD that uses our selfrepairing methods is longer than the lifetime of a GAL-based EPLD that uses a single self-repair method or no self-repair method. It demonstrates that the lifetime of a GAL can be increased by adding extra columns in an AND array of a GAL, and also gives information on how many extra columns a GAL needs to guarantee a given lifetime. Thus, we can estimate an ideal point, where the maximum reliability can be reached with the minimum cost.

## 4.1. Design Methodology of Self-Repairable GALs

In this section, we develop a design methodology for self-repairing an  $E^2$ CMOS cell in the programmable AND plane of a GAL, describe our fault model and assumptions, and develop universal test set for detecting and locating faults on each cross-point ( $E^2$ CMOS cell) [47, 48, 49].

### 4.1.1. Fault Model and Assumptions

Fault modeling is concerned with the systematic and precise representation of physical faults in a form suitable for simulation and test generation [19]. Such a representation usually involves the definition of abstract or logical faults that produce approximately the same erroneous behavior as the actual physical faults [19]. Good fault models should be straightforward, accurate, and easy to use. The most widely used fault model is the stuck-at fault model, which has been used for fault analysis and test generation in all types of logic circuits [19, 20]. While exact coverage figures are difficult to obtain, substantial empirical evidence shows that for general combinational or sequential logic circuits implemented with common MOS (Metal Oxide Semiconductor) or bipolar technologies, the stuck-at fault model provides good coverage of permanent physical faults [21, 46]. The most dominant failure modes in CMOS are shorts and opens [22]. In a switch-level representation of a CMOS circuit, MOS transistors are modeled as switches that conditionally transfer signals. The stuckopen fault model assumes that a faulty transistor never switches on (permanently disconnected), while a stuck-on fault model assumes that a faulty transistor never switches off (permanently connected) [22]. The fault model for the memory cell array is presented in [21] and [46]; one or more cells are stuck-at 0 or 1. The functional defect (functional level fault model), which is very useful for describing a wide variety of faults, is introduced in [46]. Functional defects are those that will cause a functional failure or degradation in functional performance either immediately or in the short term [43].

The cross-point stuck-at faults, which are located in  $E^2CMOS$  cells, are considered as our fault model because  $E^2CMOS$  cells of an AND array make up a large percentage of a GAL and the  $E^2CMOS$  cells' array has the same structure as an EEPROM (Electrically Erasable Programmable Read Only Memory). Each  $E^2CMOS$ cell (cross-point) of a programmable AND array of a GAL, which is located between a vertical line (row, input line) and a horizontal line (column, product term), may be ON or OFF permanently, caused by an aging problem or by other factors referred to in Chapter 1. It is called the cross-point stuck-at-1 (simply, s-a-1) if the  $E^2CMOS$  cell of a particular cross-point, which should be programmed as OFF, is ON. If the  $E^2CMOS$ cell of a particular cross-point, which should be programmed as ON, is OFF, it is called the cross-point stuck-at-0 (simply, s-a-0). Only these faults will be considered in this first project because we assume that there are no faults found in a GAL after the manufacturing process. Note that horizontal lines and vertical lines represent product terms and data inputs, respectively in a data book, but rows will be represented as data inputs and columns will be used as AND gates product terms in the rest of figures in the following sections.

The following assumptions will be used for the design, self-repair and evaluation methodologies. The GAL is initially fault free after manufacturing. The primary input/output fault does not exist in a GAL, and also every AND gate input line does not have faults. For GALs, the cross-point stuck-at faults are considered much more probable than the stuck-at faults in wires. The cross-point faults (s-a-0, s-a-1) as defined above are only taken into account in this first project. If the E<sup>2</sup>CMOS cell is ON, binary data '1' will be stored in memory, and if the E<sup>2</sup>CMOS cell is OFF, binary data '0' will be stored in memory.

In order to replace a faulty column, several extra columns are built into each OR gate (OLMC) in a GAL. There are at least two E<sup>2</sup>CMOS cells programmed as ON for

a pair of input variables, like A and complement of A. Thus, an AND gate product term (column) can be discarded safely from the OR gate without changing an OR function even though the faults are appeared in certain cross-points of that column. When a fault occurs in a certain column of a particular OLMC, this faulty column can be replaced with an extra column only in that OLMC. When an E<sup>2</sup>CMOS cell is OFF, it can be called 'programmed as OFF.' This cell disconnects a primary input from an AND gate input, and '1' will be on the AND gate input. It will be described with just an intersection between a row and a column in a logic diagram. When an E<sup>2</sup>CMOS cell is ON, it can be also called 'programmed as ON'. This cell connects a primary input to an AND gate input. It is denoted by 'X' between rows and columns in a logic diagram.

Figure 4.1 Example of a Logic Diagram Notation

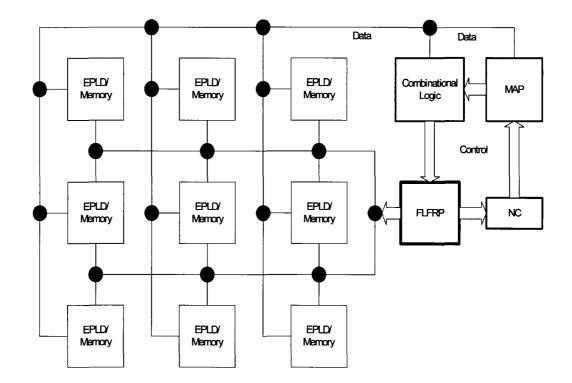

# 4.1.2. Design Architecture

The complete digital system in our first approach is shown in Figure 4.2, and it is a network of blocks realized as separate integrated circuits. Each block is a two-level realization of a Boolean function, and is realized with a GAL. FSMs (Finite State Machines) are composed of Boolean Logic and registers located in OLMCs. This seems to be reasonable since, as the EPLD/FPGA (Field Programmable Gate Array) technology advances, functions and machines of even greater sizes can be implemented in them. Reprogramming of a GAL serves to replace defective gates in

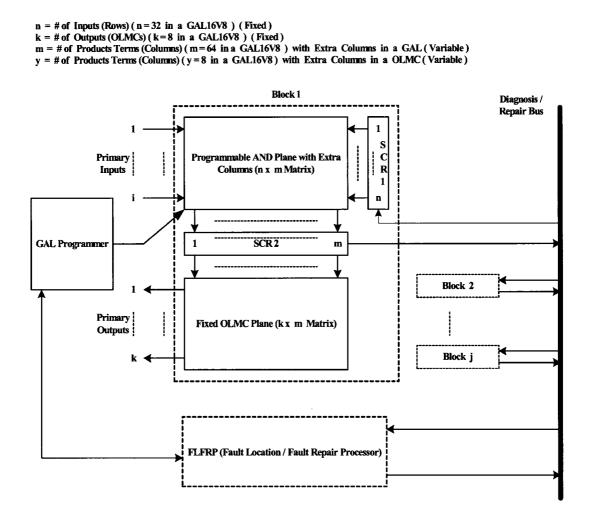

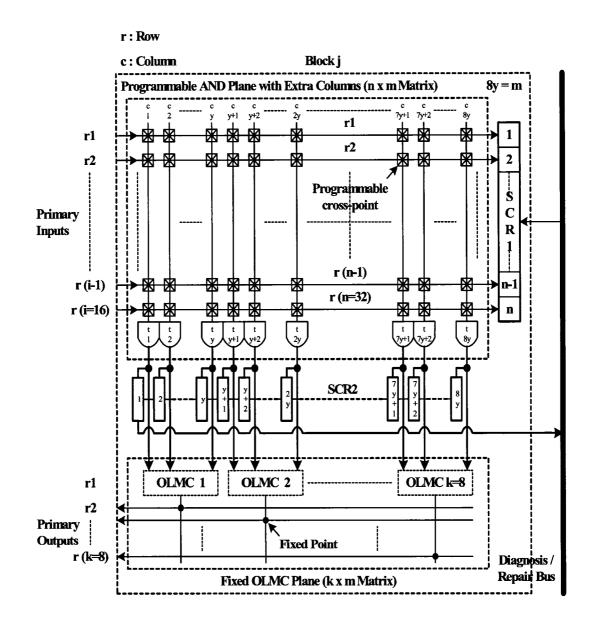

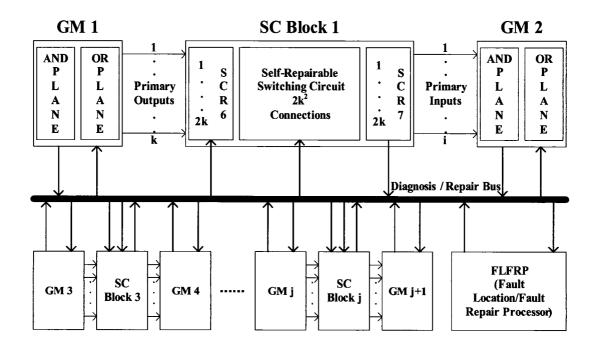

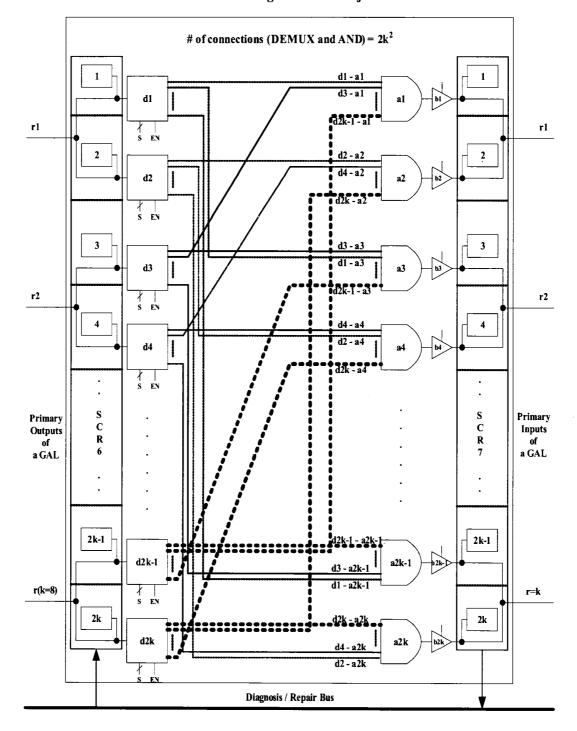

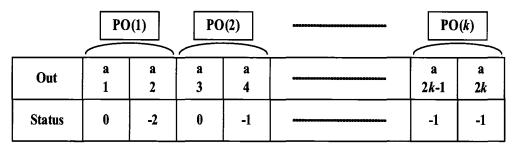

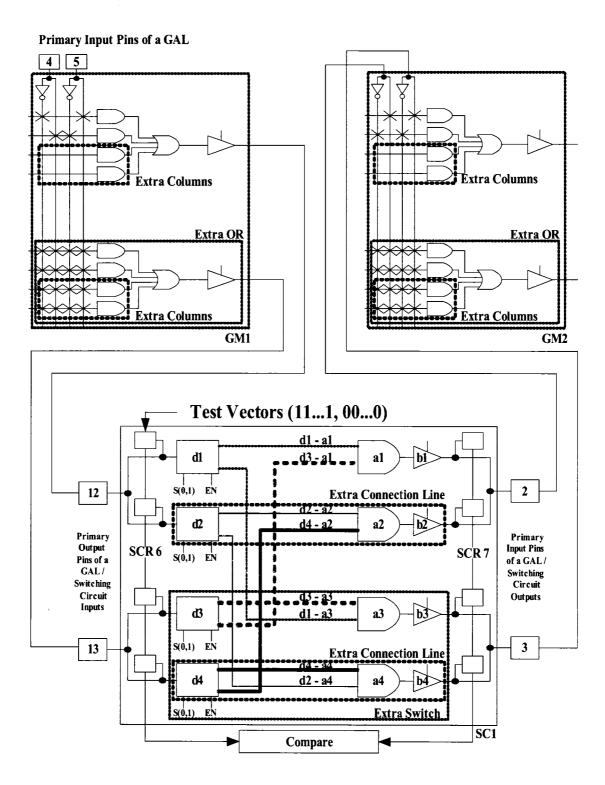

Figure 4.2 Cellular Array of EPLDs/Memory in a System; controlled by a FLFRP (Fault-Locating/Fault-Repairing Processor) to repair faults in each EPLD/memory

that GAL. The proposed method assumes that when the redundant area to create gates (i.e. the extra columns) in a block is exhausted and there are no more columns to replace a newly found defective gate, the controller will signal a global go/no-go signal. The block can be a single module (a chip, a board) or different modules. In the first case, the module should be replaced, and in the second case, the modules and their connections should be tested independently. We assume that each block includes just one self-repairable GAL. Thus, each block has a programmable AND array with several extra columns and fixed OR (OLMC) plane.

At this point, we consider the problem of getting the maximum usefulness from each block in a system at the lowest level, when the system degrades over time with new faults arising in a block that has already been tested in the manufacturing process.