#### **Portland State University**

#### **PDXScholar**

**Dissertations and Theses**

**Dissertations and Theses**

5-8-2008

# Advanced Algorithms for VLSI: Statistical Circuit Optimization and Cyclic Circuit Analysis

Osama Neiroukh

Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons

# Let us know how access to this document benefits you.

#### **Recommended Citation**

Neiroukh, Osama, "Advanced Algorithms for VLSI: Statistical Circuit Optimization and Cyclic Circuit Analysis" (2008). *Dissertations and Theses.* Paper 6150.

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# ADVANCED ALGORITHMS FOR VLSI: STATISTICAL CIRCUIT OPTIMIZATION AND CYCLIC CIRCUIT ANALYSIS

by

#### OSAMA NEIROUKH

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

ELECTRICAL AND COMPUTER ENGINEERING

Portland State University ©2008

#### DISSERTATION APPROVAL

The abstract and dissertation of Osama Neiroukh for the Doctor of Philosophy in Electrical and Computer Engineering were presented May 8, 2008, and accepted by the dissertation committee and the doctoral program.

| COMMITTEE APPROVALS                              |  |

|--------------------------------------------------|--|

| Xiaoyu Song, Chair                               |  |

| •                                                |  |

| Garrison W. Greenwood                            |  |

|                                                  |  |

| Douglas V Hall                                   |  |

| Marek A. Perkowski                               |  |

|                                                  |  |

| Jingke Li                                        |  |

| Representative of the Office of Graduate Studies |  |

Malgorzata Chizanowska-Jeske, Director

Electrical and Computer Engineering Ph.D. Program

#### **ABSTRACT**

An abstract of the dissertation of Osama Neiroukh for the Doctor of Philosophy in Electrical and Computer Engineering presented May 8, 2008.

Title: Advanced Algorithms for VLSI: Statistical Circuit Optimization and Cyclic Circuit Analysis

This work focuses on two emerging fields in VLSI. The first is use of statistical formulations to tackle one of the classical problems in VLSI design and analysis domains, namely gate sizing. The second is on analysis of non-traditional digital systems in the form of cyclic combinational circuits.

In the first part, a new approach for enhancing the process-variation tolerance of digital circuits is described. We extend recent advances in statistical timing analysis into an optimization framework. Our objective is to reduce the performance variance of a technology-mapped circuit where delays across elements are represented by random variables which capture the manufacturing variations. We introduce the notion of statistical critical paths, which account for both means and variances of performance variation. An optimization en-

gine is used to size gates with a goal of reducing the timing variance along the statistical critical paths. Circuit optimization is carried out using a gain-based gate sizing algorithm that terminates when constraints are satisfied or no further improvements can be made. We show optimization results that demonstrate an average of 72% reduction in performance variation at the expense of average 20% increase in design area.

In the second part, we tackle the problem of analyzing cyclic circuits. Compiling high-level hardware languages can produce circuits containing combinational cycles that can never be sensitized. Such circuits do have well-defined functional behavior, but wreak havoc with most tools, which assume acyclic combinational logic. As such, some sort of cycle-removal step is usually necessary. We present an algorithm able to quickly and exactly characterize all combinational behavior of a cyclic circuit. It used a combination of explicit and implicit methods to compute input patterns that make the circuit behave combinationally. This can be used to restructure the circuit into an acyclic equivalent, report errors, or as an optimization aid. Experiments show our algorithm runs several orders of magnitude faster than existing ones on real-life cyclic circuits, making it useful in practice.

Dedicated to my wife Sophia.

### **Acknowledgments**

I wish to thank my parents who saw to it that I get the best education possible without regard to the financial burdens imposed by such a pursuit. My wife and children have exhibited immeasurable patience as my doctoral degree spanned the better part of eight years while I juggled a multitude of responsibilities to God, family, work, and community in addition to a full time job. Several people at Portland State University influenced my education and inspired me in different ways. My advisor Dr Xiaoyu Song helped provided valuable input along the years that positively affected my research direction, my publications, and overall steps towards degree completion. The first course I took at PSU was with Dr Perkowski who is a great inspiration to anyone looking for research advice. He brings high passion to electrical engineering despite having spent decades in the field. The remainder of the faculty on my PhD committee have also provided useful inputs that shaped my output. Thanks are due to Intel Corporation who provide financial support for continuing education and foster a continuous improvement attitude.

# **Table of Contents**

| Acknov    | vledgm  | nents                                         | ii   |

|-----------|---------|-----------------------------------------------|------|

| List of   | Tables  |                                               | vii  |

| List of 1 | Figures | <b>S</b>                                      | viii |

| Chapte    | r 1. I  | ntroduction                                   | 1    |

| Chapte    | r 2. S  | Statistical Optimizations of Digital Circuits | 8    |

| 2.1       | Introd  | luction                                       | 8    |

| 2.2       | Litera  | ture Survey                                   | 9    |

|           | 2.2.1   | Statistical Yield Optimization                | 10   |

|           | 2.2.2   | Gate Sizing                                   | 11   |

|           | 2.2.3   | SSTA: Statistical Static Timing Analysis      | 14   |

| 2.3       | SSTA    | Overview                                      | 16   |

|       | 2.3.1     | Introduction to SSIA                                   | 10 |

|-------|-----------|--------------------------------------------------------|----|

|       | 2.3.2     | Challenges and Assumptions in SSTA                     | 19 |

| 2.4   | SSTA      | -based Circuit Optimization: Problem Overview          | 21 |

|       | 2.4.1     | Problem Formulation                                    | 21 |

|       | 2.4.2     | Overview of Research                                   | 26 |

| 2.5   | Statis    | tical Gate Sizing                                      | 28 |

|       | 2.5.1     | Overview of Algorithm                                  | 28 |

|       | 2.5.2     | FULLSSTA: Full Statistical Static Timing Analysis      | 29 |

|       | 2.5.3     | FASSTA: Fast Statistical Static Timing Analysis        | 34 |

|       |           | 2.5.3.1 Statistical Critical Path Identification       | 39 |

|       |           | 2.5.3.2 Subcircuit extraction and ranking              | 43 |

|       | 2.5.4     | Experimental results                                   | 44 |

|       | 2.5.5     | Concluding Remarks                                     | 49 |

|       | 2.5.6     | Benefits of Research                                   | 49 |

| 2.6   | Sumn      | nary                                                   | 50 |

| Chapt | er 3. 🛚 🕹 | An Efficient Algorithm for Analysis of Cyclic Circuits | 52 |

| -     |           |                                                        |    |

| 3.1   | Introd    | luction                                                | 52 |

| 3.2  | Notation and Definitions                                      | 55 |  |

|------|---------------------------------------------------------------|----|--|

| 3.3  | 3.3 Literature Survey                                         |    |  |

|      | 3.3.1 Origins of Cyclic Circuits                              | 57 |  |

|      | 3.3.2 Analysis of Cyclic Circuits                             | 58 |  |

|      | 3.3.3 Synthesis of Cyclic Circuits                            | 60 |  |

|      | 3.3.4 Most Recent Publications on Analysis of Cyclic Circuits | 61 |  |

| 3.4  | Types of Cycles                                               | 62 |  |

| 3.5  | Our Circuit Model                                             | 63 |  |

| 3.6  | Combinational Circuits                                        | 65 |  |

| 3.7  | Finding a Combinational Cover for a Cyclic Circuit            | 68 |  |

|      | 3.7.1 Theoretical Background                                  | 68 |  |

|      | 3.7.2 Searching for combinational behavior                    | 71 |  |

|      | 3.7.3 Merging partial assignments                             | 73 |  |

|      | 3.7.4 Another Example                                         | 79 |  |

| 3.8  | Experimental Results                                          | 83 |  |

| 3.9  | Benefits of Proposed Research                                 | 83 |  |

| 3.10 | Conclusions                                                   | 83 |  |

| 3.11 Summary                                               | 86 |

|------------------------------------------------------------|----|

| Chapter 4. Conclusions                                     | 90 |

| 4.1 Statistical Optimization of Digital Circuits           | 90 |

| 4.2 An Efficient Algorithm for Analysis of Cyclic Circuits | 92 |

| Bibliography                                               | 94 |

# **List of Tables**

| 2.1 | Experimental Results: $\lambda = 3$                       | 45 |

|-----|-----------------------------------------------------------|----|

| 2.2 | Experimental Results: $\lambda=9$ , runtime is in minutes | 46 |

| 3.1 | Comparison with Edwards [22]                              | 84 |

# **List of Figures**

| 2.1 | Mapping from circuit to timing graph for timing analysis       | 17 |

|-----|----------------------------------------------------------------|----|

| 2.2 | Examples of cumulative and probability distribution functions  |    |

|     | for a circuit's timing.                                        | 19 |

| 2.3 | Example of circuit output Delay PDFs                           | 25 |

| 2.4 | Example of circuit output Delay CDFs                           | 26 |

| 2.5 | Overview of Statistical Sizer Algorithm                        | 30 |

| 2.6 | Extracting Subcircuit Cost for Statistical Sizer               | 31 |

| 2.7 | Probabilistic event representing delay at a given edge in an   |    |

|     | SSTA timing graph                                              | 31 |

| 2.8 | Shift with scaling and grouping techniques to perform convolu- |    |

|     | tion of input and gate-delay PDFs to compute the output-delay  |    |

|     | PDF                                                            | 32 |

| 2.9  | Tracing worst negative statistical slack (WNSS) path. Num-                            |    |

|------|---------------------------------------------------------------------------------------|----|

|      | bers in parenthesis are $(\mu,\sigma)$ of arrival time. The shaded nodes              |    |

|      | indicate the WNSS using our method                                                    | 40 |

| 2.10 | Normalized Mean-Std Variation for C432 at different $\lambda$ . The                   |    |

|      | x-axis shows the mean while the y-axis has the standard variation.                    | 48 |

| 3.1  | A trivial cyclic circuit and its truth table                                          | 53 |

| 3.2  | Cyclic circuit for illustrating definitions                                           | 56 |

| 3.3  | Rivest's Circuit                                                                      | 58 |

| 3.4  | Cyclic circuit arising from resource sharing due to Stok [56] .                       | 59 |

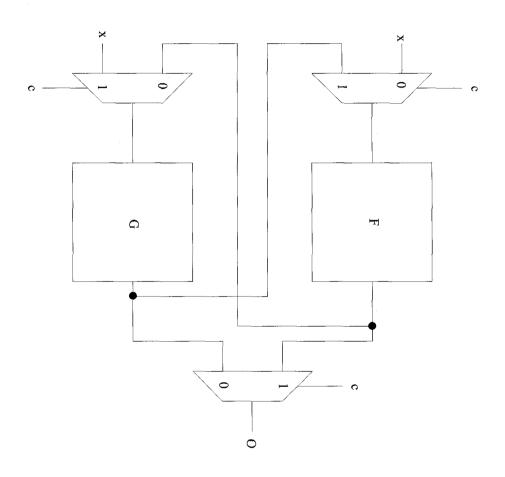

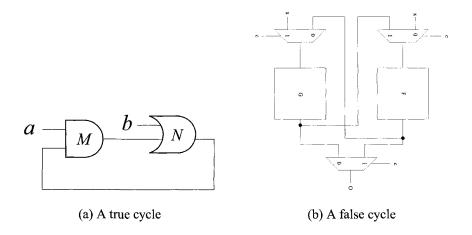

| 3.5  | Examples of true and false cycles                                                     | 63 |

| 3.6  | The three-valued simulation algorithm, which takes a circuit                          |    |

|      | $\langle G, I, W \rangle$ , an input function $x$ , and an infinite schedule of gates |    |

|      | s. It evaluates gates until it reaches a fixed point using EVAL,                      |    |

|      | which updates a single (NAND) gate                                                    | 66 |

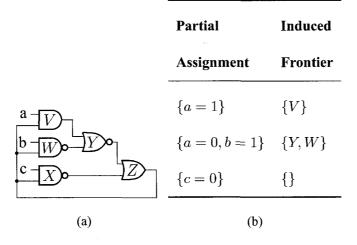

| 3.7  | (a) A cyclic circuit. (b) Partial assignments and their induced                       |    |

|      | frontiers—the boundary between defined and X-valued gates                             |    |

|      | after applying inputs.                                                                | 67 |

| 3.8  | Our algorithm for finding a minimal set of PAs for a circuit          |    |

|------|-----------------------------------------------------------------------|----|

|      | (SCC) that together cover all its combinational behavior              | 72 |

| 3.9  | Illustration of merging PAs at a gate                                 | 77 |

| 3.10 | Our PA merging algorithm: return a set of PAs that apply non-         |    |

|      | controlling values to every input of a gate                           | 80 |

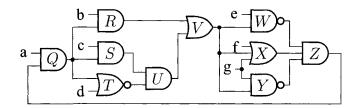

| 3.11 | Small cyclic circuit for illustrating partial assignment extraction   | 81 |

| 3.12 | PAs from applying controlling values to each input in isolation.      |    |

|      | All frontiers are either gate $V$ or gate $Z$                         | 88 |

| 3.13 | Partial assignment extraction on a small cyclic circuit (a) POS       |    |

|      | and final ISOP for frontier gate $V$ . (b) POS and ISOP for $Z$ . (c) |    |

|      | A minimal set of partial assignments that reproduce all combi-        |    |

|      | national hehavior                                                     | 89 |

## Chapter 1

#### Introduction

Advances in VLSI technology continue to present both challenging and exciting opportunities for advanced research in electrical and computer engineering. Moore's law has continued to motivate designers to keep fulfilling its prediction by continually shrinking down device geometries and packing more devices per square micron while meeting numerous challenges brought on by the most recent technologies. These challenges include several parameters such as power density and dissipation, supply voltage droop, and reliability under wide operating conditions. However, the most pressing difficulty facing designers today is the decreasing correlation between physical verification (PV) models used in pre-silicon design and optimization and behavior of manufactured circuits on silicon. Manufacturing variations and its adverse effect on predictability on silicon behavior have spurred designers to seek new tools and methodologies to deal with these variations in order to better predict

performance of circuits during design cycle.

This dissertation focuses on two emerging fields in VLSI. The first is use of statistical formulations to tackle one of the classical problems in VLSI design and analysis domains, namely gate sizing. The second is on analysis of non-traditional digital systems in the form of cyclic combinational circuits. Neither field is really new, early publications in both topics can be traced back to the 60's and 70's as our literature survey will show. However, both fields have received renewed interest recently, with statistical approaches in particular featured prominently at all major CAD conferences nowadays and getting increased coverage in journals.

Usage of statistical approaches has been well-known in parametric yield analysis for post-manufacturing die sorting and analysis, but had not made its foray yet into pre-silicon analysis or optimization areas. It began to receive increased focus around the turn of the 21st century when Physical Verification (PV) models of pre-silicon behavior started to diverge substantially from actual silicon measurements. The field has exploded in the past 5 years, with almost every analysis or optimization problem in VLSI revisited from a statistical perspective. It remains to be seen whether this is merely an academic curiosity or whether statistical analysis and optimization techniques will narrow the widening gap between pre-silicon models and post-silicon behavior.

As of this writing, IBM is the only company which has publicly claimed to deploy statistical static timing analysis in pre-silicon PV models of industrial circuits [32,33]. It is not clear to what extent does IBM use this methodology, and whether it merely augmented or completely replaced standard static timing tools as the golden timing verification model. At the same time, the field cannot be neglected. At least for the time being, it provides a rich field for research, though competition is stiff with numerous researchers both in academia and industry attacking a variety of CAD problems using statistical techniques very aggressively.

Cyclic circuits appear to have been a black sheep of digital circuits. Convincing examples of cyclic circuits that had provably less gates than any acyclic equivalents have been around for decades. Nevertheless, cyclic circuits have not received much attention in industry as candidates for deployment in real-life ASICs or custom designs. While circuits that have registers (flops or latches) that depend on current state for future state and output calculation are commonplace in state machine design, purely combinational cyclic circuits are not intuitive to reason about. Despite this, the lure of area savings and potential for other advantages has continued to spur researchers to study these circuits. More recently, a synthesis engine was proposed that produces cyclic implementations at an area saving compared to traditional synthesis. The re-

search was well-accepted, receiving best paper award at Design Automation Conference in 2003 [49].

An alternate motivation for tackling cyclic circuits arises during processing of high level hardware modeling languages such as ESTEREL [8]. Some of the literature on cyclic circuit analysis was contributed by researchers who were trying to grapple with ESTEREL and other synchronous programming languages such as LUSTRE [25] and ARGOS [36]. Synthesizing these languages into digital circuits often yields loops that are difficult for regular CAD tools to handle. Ability to handle cycles became imperative for compilation of these languages, forcing researchers to find ways to take out these cycles as a post-processing step before handing off these circuits to other tools.

This dissertation tackles both areas separately. The first part focuses on usage of statistical analysis in a digital circuit optimization setting. The main contribution is an adaptation of well-known gate sizing techniques to use a statistical timing model toward reducing the performance variation of a circuit at design time. The second part of this dissertation investigates more efficient methods for analysis of cyclic circuits. We note that the two topics are distinct with no overlap in our context.

At a high level, there are similarities in the two research areas we pro-

pose here. Both problems involve netlist level analysis and optimization at the gate-level granularity. Gate sizing is NP-complete while cyclic circuit analysis is considered to be co-NP-complete. There are also distinct differences between the two areas. Gate sizing belongs to the class of electronic design automation problems, while cyclic circuit analysis is an enumeration problem as we will show.

There are advantages to tackling such disparate problems as part of a single PhD research. The field of IC design is increasingly becoming more vertical, with design, analysis and verification becoming strongly coupled with an expectation that a designer can move between these area with ease. Another rationale here was that a practitioner in the field of VLSI design would do well to understand in depth both analysis and design optimization domains of CAD techniques from an algorithmic and practical perspective as they present uniquely different challenges. Our characterization below of the differences is rather subjective but reflects the author's combined industrial and academic experience with these fields.

Automated circuit optimization techniques are much more heuristics based, with many decisions and tunings that can work for one design but not other designs. In addition, there is a possibility of oscillations or other unexpected problems where the algorithm seems to go astray. Given that most of the

problems EDA tools attempt to solve are NP-complete, a thorough understanding of the challenges of overcoming local optima and explaining otherwise odd outputs is a daily struggle for any engineer attempting to use and steer EDA design tools. This has been a perennial component of this author's job at Intel as an automation design engineer covering automated synthesis, placement, sizing, and routing tools. The research that was done in this field has helped the author tremendously with understanding the difficult tradeoffs these tools are juggling especially as the given timing, area, and power constraints that are usually impossible to meet at once.

The chief challenge with analysis techniques in CAD is reducing runtime while keeping peak memory usage within reasonable bounds. Analysis algorithms have different requirements than optimization algorithms. A design optimization algorithm might be successful even if terminates due to exceeding acceptable runtime or runs out of memory and stops earlier than it would otherwise having achieved a satisfactory result. On the other hand, an analysis algorithm must complete its execution; a partial result is of no value in practice. This makes data representation and programming methodology used critical to a successful implementation. Usage of existing technologies such as SAT, BDD manipulation, and ATPG techniques should be considered as much as possible by mapping the given problem into one of these formulations. This

enables designers to reuse efficient solvers that are publicly available for each of these formulations and improving the state of the art by focusing on the unique problem at hand.

The rest of this dissertation is structured as follows. Chapter 2 starts with an overview of statistical analysis and optimization of digital circuits. It presents an extensive literature survey covering the topic and gives an introduction of the problem we addressed and motivation for it. It presents our proposed algorithm for statistical gate sizing and provides experimental results and detailed analysis of the algorithm's performance on tested circuits. Chapter 3 presents a literature survey on cyclic circuits and presents motivation for the problem we tackle. We provide theoretical underpinnings for our circuit model and present our original algorithm for cyclic circuit analysis as well in-depth step-by-step review of how it works in practice with aid of examples. Finally chapter 4 gives concluding remarks about our contributions and directions for future research.

# Chapter 2

# **Statistical Optimizations of Digital Circuits**

#### 2.1 Introduction

Recent advances in VLSI have continued to shrink device geometries at a steady rate in accordance with Moore's Law. However, this advancement has also been accompanied by increasing variations in the performance of fabricated circuits. Numerous factors have contributed to this trend including clock PLL jitter, noise, PV model inaccuracies, and manufacturing variations. Nevertheless, it is often desirable to manufacture ASICs on advanced technology nodes due to substantial increase in available device count, reduction in power consumption, higher yields and lower costs due to the larger 300mm wafers.

Researchers have recently focused on statistical analysis approaches in an attempt to grapple with these sources of performance variations. Statistical static timing analysis (SSTA) is a modification of static timing analysis (STA) for determining delay across a circuit. SSTA models delay arcs across gates as random variables rather than discrete values which are used in regular STA. SSTA propagate timing constraints across a circuit using probability distribution functions (pdfs). A virtual sink is often used for all the circuits' outputs producing a single pdf that represents delay across the circuit.

When this research was first conceived, a substantial focus had gone into the analysis aspect of this problem [1, 28]. However, research into statistical optimization of circuits had been surprisingly diminutive. Circuit optimization was done in [29] by using LANCELOT [17] but had severe limitation on circuit size and used unrealistically simple gate delay models. A concept of criticality of gates was used in [27] but did not address the variance of the timing path delays. A transistor level approach was presented in [4]. Several yield-specific techniques were presented in [21].

#### 2.2 Literature Survey

An extensive review of prior work on areas related to this research area was undertaken before research into this area was started. Below is a summary of contributions in this field. It should be noted that research into application of statistical techniques to mainstream EDA problems continues to advance

at a very rapid pace, with almost all major CAD conferences dedicating at least one or two sessions to statistical analysis and optimization approaches. For example, the entire 2004 ACM/IEEE TAU Workshop on Timing Issues in the Specification and Synthesis of Digital Systems was dedicated to statistical approaches to timing analysis. Many topics that had previously appeared to mature such as static timing analysis, power analysis, and gate-level design optimization are now being re-examined using statistical formulations. We survey publications in a number of research thrusts below. However, we stress that such a survey is only a sampling of what is rapidly becoming a vast body of literature covering all aspects of electronic design and analysis.

#### 2.2.1 Statistical Yield Optimization

A wide variety of methods for yield optimization has been developed over the last few decades. A comprehensive reference that covers an exposition of representative techniques is [21]. Traditional statistical optimization methods define the yield as the probability of a random variable that represents a performance metric belonging to an acceptability region. This acceptability region can be expressed as a multi-dimensional integral which is typically evaluated by Monte-Carlo based methods or by relying on analytical expressions for the circuit performance parameters of interest. Monte-Carlo techniques are

far too expensive to deploy for digital circuit design due to the dimensionality of the statistical space.

While Monte-Carlo techniques find many uses in analysis of circuits, they are rarely deployed in a circuit optimization context. Modeling of performance metrics such delay along with possible variations using analytical expressions is also intractable especially in deep submicron technologies. In light of this, we found that traditional yield optimization techniques while being highly useful in parametric yield contexts are not directly usable for the problem at hand.

#### 2.2.2 Gate Sizing

Gate sizing has been studied extensively in the literature. Gate sizing is typically performed after technology mapping during logic synthesis and repeated several times during the physical design process. The aim of gate sizing is to assign sizes to all gates in a circuit such that some objective function is satisfied, possibly under some constraints. Typical formulations include minimizing area or power subject to a maximum delay constraint. Various gate delay models have been proposed in the literature such as Load-Independent Delay Model (LIDM) and Load Dependent Delay Model (LDDM).

The choice of which gate delay model to use has a direct impact on choice and efficacy of the gate sizing algorithm to be deployed. Since the output load of a gate has a great impact on delay across it, LIDM is of little value in real optimization contexts. Gate sizing has been shown to be NP-complete under LDDM which rules out finding globally optimal solutions for real-life circuits which consist of tens to hundreds of thousands of gates.

Research in circuit sizing has been carried out both at the transistor as well as gate level. Transistor level sizing is more accurate but presumes ability to size and therefore adjust layout on a per transistor basis, which is becoming less common due to layout complexity of recent processes. It is also limited to smaller circuits compared to gate-level approaches. Gate sizing relies on standard cell libraries that can come from library vendors which are designed in discrete sizes, laid out, and pre-characterized for timing, area and power. A typical cell characterization produces lookup tables for every input-pin output-pin transition. Timing characterization tables represent input slope and output capacitance as inputs with output slopes and delay through gate as outputs.

Gate sizing algorithms can be classified into one of two categories: global approaches and local approaches. Global approaches solve gate sizing in the continuous domain by relying on optimization techniques such as convex programming with posynomials [23], linear programming [5], sequential

quadratic programming [37], or Lagrangian Relaxation [13]. While these approaches can claim a globally optimum solution, they have two drawbacks. The presumption of a convex problem where a single global optimum exists is not supported by practical evidence. More importantly, library gates tend to come in pre-determined discrete sizes and solving the problem in the continuous domain requires snapping back size assignments to closest available gate sizes. Since standard cell library gates tend to be sized in a geometric progression of drive strength, this discretization may assign drive strengths significantly different from the values obtained in the continuous domain. Advantages of global approaches include a global solution without oscillations and faster runtime compared to local approaches.

Local sizing approaches assign gate sizes using local gain-based or greedy heuristics. Examples of this approach are available in [14,19,40]. Most of these algorithms share several common elements. The critical path, sometimes referred to as the Worst Negative Slack (WNS) path, is usually targeted for optimization. We note that the WNS path can change as the optimization proceeds so the path being evaluated for resizing must be updated at specific intervals in the optimization iteration. The algorithms can be run in a constrained mode where delay for example is optimized first then area is recovered as far as possible without violating a delay constraint. Other constraints can be similarly

satisfied either during optimization by not violating some cost/benefit ratio or in a recovery mode after unconstrained optimization.

Coudert [19] argues that accurate delay models make gate sizing a non-linear, non-convex, constrained, discrete optimization problem. Our experience corroborates this assertion, especially for deep-submicron technologies which are the target domain for this research. Many of the commercial tools for logic and physical synthesis such as Design Compiler® and Physical Compiler® from Synopsys® also use local approaches for gate sizing as these approaches are more accurate despite being slower than global approaches.

#### 2.2.3 SSTA: Statistical Static Timing Analysis

The earliest paper that suggested a statistical approach to timing analysis known to the author is [41]. The author attempted to determine the distribution of delay from source to sink of an acyclic directed graph that had probability distributions associated with its elements. However, the focus on use of statistical approaches in timing analysis is relatively new. Pioneering works in this field appeared in [11,20,30].

While difficulties in deterministic timing analysis such as false path detection carry into statistical approaches, the latter also introduce their own set of challenges. In particular, deterministic timing analysis relies on two operations for propagating timing through a network, sum and max. The summing operation adds arrival times at inputs of gates to delays from those input pins to the output. The max operation decides which of these to propagate for max frequency analysis. Performing these calculations on pdfs is more expensive computationally than their counterparts in the deterministic case. Moreover, the degree of correlation between two pdfs arriving at a gate's inputs due to reconvergent fanouts needs be taken into account for accurate calculations.

In the past few years statistical techniques for timing analysis of digital circuits have received tremendous focus with representative works including [2, 12, 34, 47]. A recent paper [9] reviews many of the the recent developments in SSTA. It discusses its underlying models and assumptions, then surveys the major approaches, and closes by discussing its remaining key challenges. It also has a large number of references which constitute a compendium of recent publications on statistical techniques in timing analysis and optimization.

#### 2.3 SSTA Overview

This section provides an overview of statistical timing analysis based on [9]. For more in-depth treatments, the reader is referred to the recent overview paper [9] and the references that paper cites.

#### 2.3.1 Introduction to SSTA

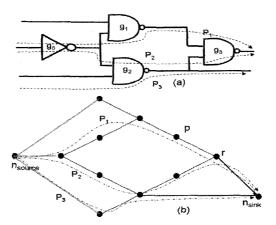

Traditional timing analysis abstracts a timing graph from a combinational circuit as follos. The nodes of the timing graph represent primary inputs/outputs of the circuit and gate input/ output pins. The edge of the timing graph represent the timing elements of the circuit, namely, the gate input-pinoutput-pin delay and wire delay from a driver to a receiver, as shown in Figure 2.1.

The weight on these edges represents the delay of the corresponding timing element. For a combinational circuit, it is convenient to connect all primary inputs to a virtual source node with virtual edges having weight equal to the input arrival times. Similarly, all the primary outputs are connected to a virtual sink node through virtual edges with weights representing the required arrival times. The resulting timing graph, therefore, has a single source and sink node.

Figure 2.1: Mapping from circuit to timing graph for timing analysis.

SSTA uses the same fundamental concept but uses random variables (RVs) to model gate delays. The random variables capture the uncertainty introduced by the manufacturing variations which are prevalent in deep submicron technologies. A formal definition of statistical timing analysis follows.

**Definition 1.** A timing graph  $G = N, E, n_s, n_f$  is a directed graph having exactly one source node ns and one sink node  $n_s$ , where N is a set of nodes, and E is a set of edges. The weight associated with an edge corresponds to either the gate delay or the interconnect delay. The timing graph is said to be a statistical timing graph if ith edge weight  $d_i$  is an RV.

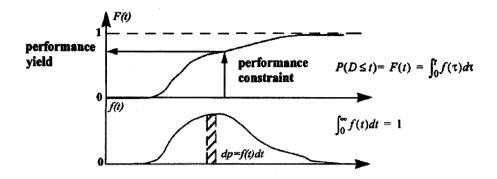

In traditional DSTA, the most basic goal of the analysis is to find the maximum delay between the source node and the sink node of a timing graph, which is the delay of the longest path in the circuit. When modeling process-induced delay variations, the sample space is the set of all manufactured dies. In this case, the device parameters will have different values across this sample space, hence the critical path and its delay will change from one die to the next. Therefore, the delay of the circuit is also an RV, and the first task of SSTA is to compute the characteristics of this RV. This is performed by computing its probability-distribution function (PDF) or cumulative-distribution function (CDF) (see Figure 2.2). Alternatively, only specific statistical characteristics of the distribution, such as its mean and standard deviation, can be computed.

Note that the CDF and the PDF can be derived from one another through differentiation and integration. Given the CDF of circuit delay of a design and the required performance constraint the anticipated yield can be determined from the CDF. Conversely, given the CDF of the circuit delay and the required yield, the maximum frequency at which the set of yielding chips can be operated at can be found.

Figure 2.2: Examples of cumulative and probability distribution functions for a circuit's timing.

#### 2.3.2 Challenges and Assumptions in SSTA

This section goes through various underlying assumptions and challenges pertaining to usage of SSTA in digital circuits

• Gates versus wires: Most literature to date presumes that gates are far more susceptible to variations than interconnects. There is some evidence for this in what little real silicon data has surfaced. As such, in this work, we will also stay with this assumption, modelling gate delays as random variables and ignoring wire delays as they do not impact our analysis or optimization

- Normal distributions: Again, we find that most literature assumes that gate delays can be represented by random variables. As [9] notes, normal or Gaussian distributions are found to be the most commonly observed distributions for RVs, and a number of elegant analytical results exist for them in the statistics literature. Hence, most of the research in SSTA assumed normal distributions for physical device parameters, electrical device parameters, gate delays, and arrival times. However, some physical device parameters may have significantly nonnormal distributions. Moreover, one of the two operations dominant in timing analysis, the max operator, is nonlinear and produces a nonnormal distribution when applied to two normal distributions. Nonnormal delay and arrival-time distributions introduce significant challenges for efficient SSTA.

- Correlation: Due to reconvergent fanouts from the same gate, inputs arriving at a given gate may have some common sources. This must be accounted for if we are to produce exact timing analysis. As per [9], the input arrival times at the reconvergent node become dependent on each other because of the shared edge delay. This dependence leads to so-called topological correlation between the arrival times and complicates the maximum operation at the reconvergent node. To perform accurate analysis, the SSTA algorithm must capture and propagate this correla-

tion so that it is correctly accounted for during the computation of the maximum function.

#### 2.4 SSTA-based Circuit Optimization: Problem Overview

This section will provide an overview of the problem we propose to solve and provide a mathematical formulation and motivation for this research direction.

#### 2.4.1 Problem Formulation

The starting point for our problem is a technology mapped digital circuit. Without loss of generality, this paper focuses on combinational circuits. We ignore interconnect delay though accounting for them can be readily accommodated. This is in line with other published literature and practical findings, as analysis of manufactured circuits indicates devices are much more susceptible to manufacturing variations than interconnect nets.

Our method uses discrete probability distribution functions (pdfs) throughout.

**Definition 2.** A discrete pdf for random variable X is defined as one or more

points where

$$f(x) = Pr(X = x) \tag{2.1}$$

The mean and variance of a discrete random variable are given by

$$\mu_X = \sum x_i f(x_i) \tag{2.2}$$

$$\sigma_X^2 = \sum (x_i - \mu_X)^2 f(x_i)$$

(2.3)

We shall also use the cumulative distribution function (cdf) to illustrate concepts and results. The cdf for a discrete random variable X is defined as

$$F(x) = Pr(X \le x) \tag{2.4}$$

We assume that every gate delay in the circuit is represented by a normally distributed random variable which is consistent with other published literature. In line with other researchers, we focus our work on gate delays and sizes and ignore second order factors such as slope propagation or capacitance variations. We shall have more to say about modeling of transistor variations in the conclusions chapter.

Both the mean and standard deviation of delay through a bigger gate are less than those of a smaller gate. Arrival times are propagated throughout the circuit as pdfs. We define the unconstrained timing variance minimization problem for a circuit as

Minimize

$$\sigma_Q^2$$

(2.5)

where

$$\mu_O = \text{Mean}(RV_O)$$

$$\sigma_X^2 = \text{Variance } (RV_O)$$

$RV_O = \underset{i \in OUT}{\operatorname{Max}}(RV_i)$  where the Max is the statistical Max operator on random variables

$RV_i =$ Random variable representing propagated arrival time of output  $o_i$

$$OUT = \{o_1, o_2, \cdots, o_N\}$$

are the circuits outputs

As we shall see later, due to the gain-based nature of the algorithm we propose, a constrained version is possible by terminating it once certain constraints are satisfied. From this point onwards, we shall focus on the unconstrained problem without loss of generality. However, in the course of making local optimization, we show how a user-defined weight multiplier can in fact steer the optimization towards different goals.

We note that the random variable  $RV_O$  characterizes the mean and variance of the entire circuit. It should be highlighted that a circuit may have multiple outputs with close mean delays but different variances. In this case, all such

outputs will contribute to the overall variance  $\sigma_X^2$  of the circuits performance. Alternatively, an output with the highest variance may have a much smaller mean than other outputs and reducing its variance will have minimal effect on overall variance of the circuits performance. Any algorithm that attempts to alter  $RV_O$  must account for both means and variances of delays simultaneously.

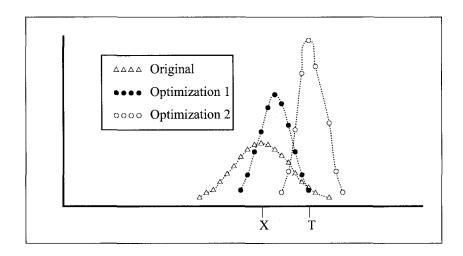

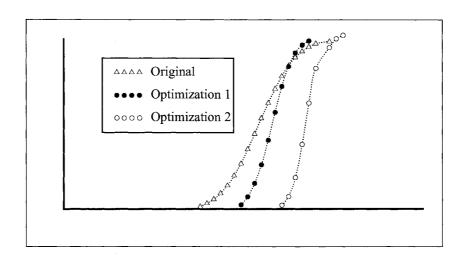

Figure 2.3 gives PDF plots of  $RV_O$  at different optimization points while Figure 2.4 provides the equivalent plots using CDFs instead of PDFs. The original line represents a pdf obtained by optimizing a circuit with a goal of minimizing the mean of the longest delay in the circuit. Such a circuit will typically exhibit the widest spread in performance due to high usage of smaller devices which exhibit more manufacturing variability. Depending on target application of circuit, such a performance variance around the center can represent undesirable uncertainty that should be minimized. In [48] reduction of uncertainty was shown to be a key strategy for designing leading edge industrial designs. Decreasing variance can increase the overall yield of a design. An example of this is *optimization 1* in Figure 2.3 which yields more functional units at period T relative to the original design. However, our technique is quite general and is not limited to yield optimization.

Decreasing performance variance is also desirable on several other accounts even if it means relaxing the original timing targets. For example, cir-

Figure 2.3: Example of circuit output Delay PDFs

cuits on the original curve to the left of X in Figure 2.3 below will exhibit undesirable variance in power consumption due to both dynamic and leakage power variations. These variations in turn contribute uncertainties in thermal dissipation and reliability verification. The effects of such performance variations can adversely product qualification and time-to-market. In such instances, the second optimization design criteria shown in Figure 2.3 labeled *optimization* 2 can be more desirable due to better tolerance to manufacturing variations. Our research is aimed at providing designers with a statistically aware gate sizing methodology that allows arbitrary tradeoffs between mean and variance of  $RV_O$ .

Figure 2.4: Example of circuit output Delay CDFs

#### 2.4.2 Overview of Research

We propose a gate sizing algorithm that uses statistical delay models for gates. We propose to extend local gate sizing approaches in such a way that they can be run in a statistical mode. Our choice of using a local gain-based sizing approach is based on our experience with real-life libraries that are almost exclusively characterized as lookup-tables which use input-slope/output-capacitance as inputs and produce output-slope/delay-across-gate. Such libraries do not lend themselves to accurate modeling with analytical formulae. Our specific objective with this sizing is to improve the reliability of the final circuit by reducing the spread of uncertainty in the timing model as produced

by statistical static timing analysis (SSTA).

The primary focus of our research is on reducing the variations of a digital circuit as measured by statistical static timing analysis (SSTA) before manufacturing. Our success criteria is reduction of  $\sigma$  of the SSTA distribution measured at a virtual sink of all the outputs of the circuits. An obvious way to reduce variations would be to prohibit usage of all devices smaller than a given dimension as smallest devices exhibit the most variation. However, this is not a very practical approach, since usage of these devices for non-critical paths saves both area and power. Instead, we show that variations in such devices can in fact be canceled out by appropriately sizing up subsequent gates with tolerable increases in circuit area.

Regular gain-based sizing algorithms operate on the worst negative slack (WNS) paths, continuously updating them as the algorithm proceeds. Our approach introduces concept of worst negative statistical slack paths (WNSS). These paths are the statistical counterpart of well known WNS paths, except that they track both mean and variance of delay. Our research enables a designer to chose appropriate tradeoffs between mean and variance of delay for a given circuit.

Optimization engines typically use different timing engines for opti-

mization versus final analysis. The core of an optimization algorithm requires a fast engine for evaluating sizing or other optimization choices. We expect that a side-product of our research will be a fast engine for performing statistical static timing analysis on small circuit segments. We use a more accurate but slower engine for analysis and tracking of WNSS paths which relies on the sampled PDF for propagation of timing edges while keeping the faster engine which uses point values for mean and standard variation for the core of the optimization engine.

## 2.5 Statistical Gate Sizing

Our research in this area combines statistical techniques as well as circuit optimization using gate sizing. This section will provide an overview of the proposed algorithm, develop the mathematical apparatus needed for algorithm implementation, present experimental results and analysis thereof. We also highlight benefits of research in context of design automation.

#### 2.5.1 Overview of Algorithm

We studied several deterministic sizing techniques to evaluate their fitness as a basis for statistical sizing. Our preference for accurate gate delay

models steered us away from methods [13, 37, 58], which require convex analytical expressions for gate delays. Such models not adequately capture the nonlinearities in current and foreseeable DSM technologies where manufacturing variations are prevalent. The main procedure of our approach is shown in Figure 2.5, with supporting function shown in Figure 2.6. This builds on the deterministic algorithms presented in [19,40] which are quite versatile and form basis of commercially available optimization tools. The next sections show how we deal with new challenges that arise when timing constraints are represented by random variables.

### 2.5.2 FULLSSTA: Full Statistical Static Timing Analysis

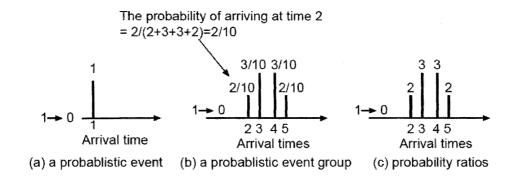

Our full statistical analysis engine is based on [34]. This approach discretizes pdfs at a user controlled sampling rate. We used 10-15 samples per pdf as a reasonable tradeoff between accuracy and speed. Note that the discrete PDFs are renormalized after sampling to ensure that the sum of the probabilities for the discrete events is equal to one. An example of a discrete pdf for delay is given in Figure 2.7

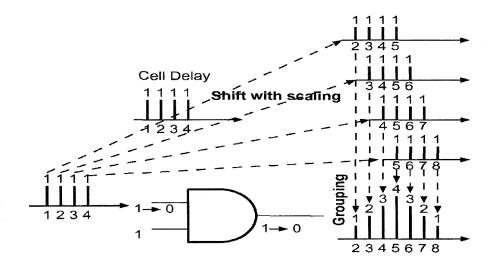

The operations sum and max are performed on discrete pdfs using shifting, scaling, and min/max reduction. An example of this process is shown

```

1: procedure STATISTICAL SIZER(Circuit C)

2:

repeat

Run FULLSSTA on C

3:

Trace critical path (WNSS) of C

4:

foreach g \in (gates \text{ on WNSS})

5:

extract subcircuit S around g

6:

SB = Cost(S)

7:

GC = CurrentSize(g)

8:

GB = GC

9:

foreach I \in (\text{sizes of g})

10:

g \text{ in } S \leftarrow I

11:

SN = Cost(S)

12:

if SN < SB then

13:

GB=I

14:

SB=SN

15:

if GB \neq GC then

16:

⊳ Schedule g for resizing

g.nextSize \leftarrow GB

17:

Resize scheduled gates

18:

until constraints met or no further improvement

19:

```

Figure 2.5: Overview of Statistical Sizer Algorithm

- 1: **function** COST(Subcircuit S)

- 2: Perform FASSTA on S

- 3: Return ObjectiveFunction(S)

Figure 2.6: Extracting Subcircuit Cost for Statistical Sizer

Figure 2.7: Probabilistic event representing delay at a given edge in an SSTA timing graph

Figure 2.8: Shift with scaling and grouping techniques to perform convolution of input and gate-delay PDFs to compute the output-delay PDF

## in Figure 2.8.

The approach utilizes discrete sum and maximum operations for arrivaltime propagation. In the case of a degenerate or deterministic input-delay distribution, the sum operation is simple, and the output-delay PDF is obtained by simply shifting the gate-delay distribution by the input delay. However, in the case where the input-delay PDF is nondegenerate, a set of shifted output-delay distributions is generated, as shown in [34]. Each of these shifted PDFs corresponds to a discrete event from the input-delay PDF. This set of shifted PDFs is then combined using Bayes theoremthe shifted PDFs are first scaled, where the scaling factor is the probability of the associated discrete input event. The scaled events are then grouped by summing the probability at each of the discrete time points. The actual probability of an event can be obtained by dividing the total value for each discrete point of the PDF by the sum of the numbers corresponding to all the events in each discrete PDF. The overall computation can be expressed as

$$f_s(t) = \sum_{i=-\infty}^{i=\infty} f_x(i) f_y(i-t) = f_x(t) \otimes f_y(t)$$

(2.6)

where s=x+y, and implies that the PDF of the sum of two RVs can be expressed as a convolution of their PDFs. The statistical maximum is computed using the relation

$$f_z(t) = F_x(t)f_x(t) + F_y(t)f_y(t)$$

(2.7)

where z = maximum(x, y), f and F represent the PDF and CDF of the RV, respectively, and x and y are assumed to be independent. The previous equation expresses mathematically that the probability that the maximum of two discrete RVs has a value  $t_0$  is equal to the probability that one of the RVs has a value equal to  $t_0$  and the other has a value less than or equal to  $t_0$ .

In addition to propagating pdfs, we also calculate the mean and variance at every node and store these values for use in the fast timing engine (FASSTA). This component in our algorithm can be updated as needed to track the latest emerging research in statistical timing analysis and represents the outer loop for our iterations.

## 2.5.3 FASSTA: Fast Statistical Static Timing Analysis

As we pointed out in 2.3, statistical analysis methods such as FULLSSTA are expensive and impractical for use alone in an optimization setting. This section presents new approximations for fast statistical static timing analysis (FASSTA). This allows us to quickly evaluate costs of subcircuits in the body of the optimization algorithm. The two operations needed in static timing analysis are sum and max. The FASSTA engine relies on the point values for means and delays calculated in FULLSSTA rather than the complete discrete pdf representations.

We start with two normally distributed independent random variables A and B with expected values  $\mu_A$  and  $\mu_B$  and with variances  $\sigma_A^2$  and  $\sigma_B^2$  respectively. Let random variable C be the sum of A and B. The mean and variance

of C are given by:

$$\mu_C = \mu_A + \mu_B \tag{2.8}$$

$$\sigma_C^2 = \sigma_A^2 + \sigma_B^2 \tag{2.9}$$

To calculate the max, we shall expand on the formulation in [15]. We use the following notation:

$$\varphi(x) = \frac{1}{\sqrt{2\pi}} e^{\frac{-x^2}{2}} \tag{2.10}$$

$$\Phi(x) = \int_{-\infty}^{x} \varphi(t)dt \tag{2.11}$$

$$a^2 = \sigma_A^2 + \sigma_B^2 \tag{2.12}$$

$$\alpha = \frac{\mu_A - \mu_B}{a} \tag{2.13}$$

The first two moments of max(A, B) are given by

$$v_1 = \mu_A \Phi(\alpha) + \mu_B \Phi(-\alpha) + a\varphi(\alpha) \tag{2.14}$$

$$v_2 = (\sigma_A^2 + \sigma_B^2)\Phi(\alpha) + (\sigma_A^2 + \sigma_B^2)\Phi(-\alpha) + (\mu_A + \mu_B)a\varphi(\alpha)$$

(2.15)

The variance of max(A, B) is given by

$$Var_{max(A,B)} = v_2 - v_1^2 (2.16)$$

These formulae cannot be evaluated directly because the integrals do not have analytical expressions. We found them to be expensive to compute numerically. Instead, we derive next an original approximation on how they can be avoided altogether and show bounds for the magnitude of approximation error. We reformulate the integral:

$$\Phi(x) = \int_{-\infty}^{x} \varphi(t)dt \tag{2.17}$$

$$\Phi(x) = \int_{-\infty}^{0} \varphi(t)dt + \int_{0}^{x} \varphi(t)dt$$

(2.18)

$$\Phi(x) = \frac{1}{2} + \frac{1}{2} erf(\frac{x}{\sqrt{2}})$$

(2.19)

where erf denotes the error function. To calculate the error function, we use the following quadratic approximation [59] which is accurate to two decimal places

$$\frac{1}{2}erf(\frac{x}{\sqrt{2}}) \approx \begin{cases}

0.1x(4.4-x) & 0 \le x \le 2.2 \\

0.49x & 2.2 < x < 2.6 \\

0.50x & \ge 2.6

\end{cases}$$

(2.20)

We also note that the error function is odd:

$$erf(-x) = -erf(x) \tag{2.21}$$

These formulae give us a quick method to approximate the error function for any value. We substitute this approximation in Eq 2.15. We note that if

$$\alpha = \frac{\mu_A - \mu_B}{a} \ge 2.6 \tag{2.22}$$

then

$$\Phi(\alpha) \approx 1 \tag{2.23}$$

$$\Phi(-\alpha) \approx 0 \tag{2.24}$$

$$\varphi(\alpha) \approx 0 \tag{2.25}$$

and we have

$$v_1 = \mu_A \tag{2.26}$$

$$v_2 = \mu_A^2 + \sigma_A^2 \tag{2.27}$$

which gives

$$Mean_{max(A,B)} \approx \mu_A$$

(2.28)

$$Var_{max(A,B)} \approx \sigma_A^2$$

(2.29)

Similarly, for

$$\alpha = \frac{\mu_A - \mu_B}{a} \le 2.6 \tag{2.30}$$

then

$$Mean_{max(A,B)} \approx \mu_B$$

(2.31)

$$Var_{max(A,B)} \approx \sigma_B^2$$

(2.32)

We observed that in the vast majority cases, one of Eq 2.22 or Eq 2.30 would apply obviating need for any calculation for max, while in other cases the approximations above provide quick estimates. These formulae assume independence of random variables which does not always hold. However, this approach emphasizes speed while retaining a reasonable degree of accuracy for small subcircuits. We stress that this approach is only used for the inner loop of the optimizations, while the outer loop relies on the more accurate discrete pdfs manipulation approach that can track correlations due to reconvergent paths using Principal Component Analysis [12] or other methods as long as runtime is managed appropriately.

#### 2.5.3.1 Statistical Critical Path Identification

As was pointed out in Section 2.2.2, circuit optimization engines typically focus their effort on the critical or WNS path to improve the performance

Figure 2.9: Tracing worst negative statistical slack (WNSS) path. Numbers in parenthesis are  $(\mu, \sigma)$  of arrival time. The shaded nodes indicate the WNSS using our method.

of the circuit. This section describes how we extend this concept to trace the Worst Negative Statistical Slack (WNSS) path in a circuit.

Consider a circuit consisting of 6 gates such as the one shown in Figure 2.9. The first number in the parenthesis represents the statistical mean of delay for that arc while the second one represents the standard variation. We wish to determine the critical path with the biggest contribution to the variance at the output of node X. We note that, unlike the deterministic case, one cannot simply pick the input with the higher mean or variance to determine which input is most responsible for the variance at the output. This is due to the non-linearity of the statistical max operation where all inputs contribute to

the output max. This is in contrast with deterministic max operation where only the maximum of the inputs contributes to the output.

We proceed to solve this problem by considering the sensitivity of the variance at the output of a node with respect to the inputs as follows. Starting from a given gate, we compare its inputs pair-wise. If either of Eq 2.22 or Eq 2.30 are satisfied, then we pick the input with the higher mean as clearly having the dominant influence on the output of this gate. If neither of these equations is satisfied, we compare

$$\frac{\partial Var_{max(A,B)}}{\partial \mu_A} \tag{2.33}$$

versus

$$\frac{\partial Var_{max(A,B)}}{\partial \mu_B} \tag{2.34}$$

Our justification for taking the partial derivatives with respect to the means of the delays is that the variances have a random component not under our direct control. On the other hand, using available gate sizes for a given circuit function gives us a direct ability to control means of delays.

One approach to obtaining these sensitivities is to differentiate Eq 2.33-Eq 2.34 directly. We found the resultant expressions to be complex requiring expensive floating-point computations not suited for the core of our optimization engine. Instead, we chose to use an approximation for differentiation as follows. Rewriting

$$Var_{max(A,B)} = f(\mu_A, \mu_B, \sigma_A, \sigma_B)$$

(2.35)

We use a forward finite-difference formula to approximate the partial derivative:

$$\frac{\partial Var_{max(A,B)}}{\partial \mu_A} \approx \frac{f(\mu_A + h, \mu_B, \sigma_A + g, \sigma_B) - f(\mu_A, \mu_B, \sigma_A, \sigma_B)}{h}$$

(2.36)

We used values for h of the order of 1% of the mean. It should be noted that  $\mu$  and  $\sigma$  along a given path are correlated and one cannot expect to change one value without the other being impacted. The change in  $\sigma_A$  that can result out of altering  $\mu_A$  is indicated by g. We also note that it is impossible in general to determine g accurately as the relationship between  $\mu$  and  $\sigma$  along a given path is governed by a combination of gate performance variations inversely proportional to their dimensions as well unsystematic random variations that are unpredictable. For purposes of ranking inputs, the following linear approximation linking these two was found to be adequate:

$$q \cong \Delta \sigma \cong c\Delta \mu \tag{2.37}$$

We used values for c equal to those assumed to relate mean delay through a gate to its variance.

## 2.5.3.2 Subcircuit extraction and ranking

For every gate being evaluated for resizing, our algorithm extracts a subcircuit around this gate based on a user-controlled depth. We have found that using two levels of transitive fanins and fanouts is sufficiently accurate without being too costly to evaluate. However, this is one of the many knobs that can be altered at will as a tradeoff between runtime and accuracy.

For every available size for this gate, we use FASSTA to calculate mean and variance of delay at the outputs of this subcircuit. We derive a cost function that allows us to rank the relative merits of gate sizing in this subcircuit quickly as follows. For all outputs of the subcircuit  $O_1 \dots O_n$ , we calculate a weighted sum of mean and standard variation:

$$Cost(O_i) = \mu_i + \lambda \sigma_i \tag{2.38}$$

where  $\lambda$  is a user-specified weight multiplier that ranks relative importance of minimizing standard variation against mean of delay. By choosing higher values for  $\lambda$ , the user can place more emphasis on variance reduction. We provide more analysis on effect of varying  $\lambda$  in the conclusions section at the end of the paper. The cost of the subcircuit is given by the maximum of  $Cost(O_i)$  across all outputs. We then pick the gate size that minimizes subcircuit cost across all gate sizes for candidate gate.

#### 2.5.4 Experimental results

The approach introduced above was implemented in Java and run on an Intel PC running at 2.53 GHz. We tested the algorithm on various circuits from the ISCAS benchmarks and various sized ALU circuits.

The circuits were first synthesized using Design Compiler [57] using an industrial 90nm lookup-table based standard cell library with 6-8 sizes per gate type. In line with other researchers, we added variations to the gate delays based on [16, 43]. Two variations components were added to the gate delays: one proportional to delay through gate and another random source corresponding to unsystematic manufacturing variations.

Table 2.1 shows the results of our optimization for two representative multiplier values,  $\lambda=3$  and  $\lambda=9$ . The ratio of  $\sigma$  to  $\mu$  obtained by optimizing for mean delay is shown in the first column entitled original. We then ran our algorithm at various values for multiplier  $\lambda(7)$ . Results are shown for optimization under two different values for  $\lambda$ , 3 and 9. We observed that increasing  $\lambda$  any further could not yield further reduction in variance in general though the highest value for  $\lambda$  was different for different circuits. This is due to the unsystematic variations whose effects cannot be totally eliminated regardless of gate sizes deployed.

Table 2.1: Experimental Results:  $\lambda=3$

| Circuit |       | Original     | $\lambda=3$ , runtime is in minutes |              |              |            |                |  |  |

|---------|-------|--------------|-------------------------------------|--------------|--------------|------------|----------------|--|--|

| Name    | Gates | $\sigma/\mu$ | $\Delta \sigma$                     | $\Delta \mu$ | $\sigma/\mu$ | $\Delta A$ | Runtime (mins) |  |  |

| alu1    | 234   | 0.124        | +4%                                 | -54%         | 0.055        | +16%       | 1.5            |  |  |

| alu2    | 161   | 0.147        | +3%                                 | -71%         | 0.041        | +14%       | 1.3            |  |  |

| alu3    | 215   | 0.127        | +7%                                 | -61%         | 0.046        | +16%       | 1.5            |  |  |

| c432    | 203   | 0.093        | +2%                                 | -58%         | 0.038        | +11%       | 1.6            |  |  |

| c499    | 381   | 0.077        | +5%                                 | -63%         | 0.027        | +13%       | 1.5            |  |  |

| c880    | 301   | 0.092        | +4%                                 | -57%         | 0.038        | +17%       | 1.5            |  |  |

| c1355   | 378   | 0.081        | +5%                                 | -63%         | 0.057        | +13%       | 1.7            |  |  |

| c1908   | 563   | 0.076        | +3%                                 | -44%         | 0.041        | +7%        | 3.7            |  |  |

| c2670   | 820   | 0.068        | +2%                                 | -42%         | 0.039        | +11%       | 9.8            |  |  |

| c3540   | 1245  | 0.062        | +4%                                 | -56%         | 0.026        | +12%       | 14.7           |  |  |

| c5315   | 2318  | 0.043        | +2%                                 | -36%         | 0.027        | +12%       | 36             |  |  |

| c6288   | 2980  | 0.021        | +1%                                 | -28%         | 0.015        | +5%        | 44             |  |  |

| c7552   | 2763  | 0.043        | +2%                                 | -50%         | 0.021        | +11%       | 31             |  |  |

Table 2.2: Experimental Results:  $\lambda = 9$ , runtime is in minutes

| Circuit |       | Original     | $\lambda = 9$   |              |              |            |                |  |  |  |

|---------|-------|--------------|-----------------|--------------|--------------|------------|----------------|--|--|--|

| Name    | Gates | $\sigma/\mu$ | $\Delta \sigma$ | $\Delta \mu$ | $\sigma/\mu$ | $\Delta A$ | Runtime (mins) |  |  |  |

| alu1    | 234   | 0.124        | +6%             | -80%         | 0.023        | +24%       | 1.6            |  |  |  |

| alu2    | 161   | 0.147        | +4%             | -86%         | 0.020        | +29%       | 1.4            |  |  |  |

| alu3    | 215   | 0.127        | +9%             | -75%         | 0.029        | +25%       | 1.7            |  |  |  |

| c432    | 203   | 0.093        | +4%             | -75%         | 0.022        | +21%       | 1.7            |  |  |  |

| c499    | 381   | 0.077        | +8%             | -76%         | 0.017        | +21%       | 1.8            |  |  |  |

| c880    | 301   | 0.092        | +5%             | -79%         | 0.018        | +23%       | 1.7            |  |  |  |

| c1355   | 378   | 0.081        | +7%             | -71%         | 0.022        | +19%       | 1.9            |  |  |  |

| c1908   | 563   | 0.076        | +4%             | -71%         | 0.021        | +16%       | 3.8            |  |  |  |

| c2670   | 820   | 0.068        | +7%             | -76%         | 0.015        | +18%       | 9.1            |  |  |  |

| c3540   | 1245  | 0.062        | +8%             | -70%         | 0.017        | +21%       | 13.1           |  |  |  |

| c5315   | 2318  | 0.043        | +7%             | -68%         | 0.013        | +15%       | 34             |  |  |  |

| c6288   | 2980  | 0.021        | +2%             | -47%         | 0.011        | +9%        | 41             |  |  |  |

| c7552   | 2763  | 0.043        | +4%             | -66%         | 0.014        | +17%       | 33             |  |  |  |

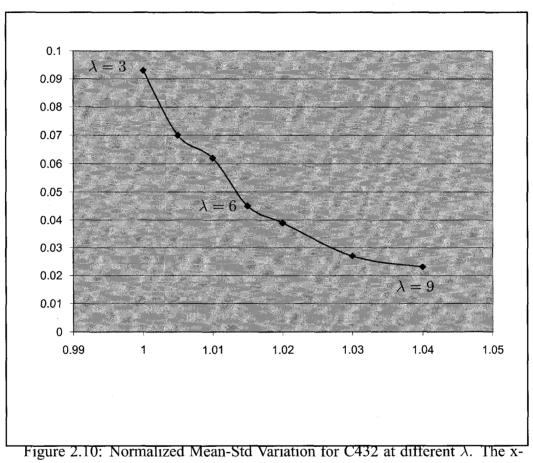

Figure 2.10 shows a plot of  $\mu$  against  $\sigma$  for various values of  $\lambda$  for circuit C432. As the multiplier  $\lambda$  is increased, the mean is increased in exchange for a gradual reduction in standard variation of delay across the circuit.

Several observations can be made from these results. Our algorithm consistently reduces the standard variation while increasing mean delay and area. This behavior is expected since our algorithm favors bigger gate sizes that reduce the variance of delay across them. The algorithms focus on minimizing variance also causes it to upsize gates near the outputs to reduce the overall variance at circuits output. This is done even if that path does not have the highest mean delay which is in contrast to a worst mean-delay optimizer which would not upsize such gates. This increases overall delay due to higher loading slowing down predecessor gates.

Another important observation is that the number of gates along a timing path is inversely proportional to the variance along that path and the ability to optimize it away. Paths with a shorter number of gates tend to be more susceptible to variations. The smaller ALU circuits exhibit significant variations as a percentage of their mean. Our algorithm can reduce this variation substantially but at a higher increase in area. On the other hand, circuit C6288 which is a 16x16 bit multiplier has the longest depth of any of the circuits in the table. We note that it has the lowest improvement due to its already low  $\sigma$  to  $\mu$  ratio.

axis shows the mean while the y-axis has the standard variation.

### 2.5.5 Concluding Remarks

We introduced a new concept of a worst negative statistical slack path and derived a procedure for tracing and optimizing such paths. In the process, we also derived a new approximation for the max operation on random variables for use in circuit optimization. Our approach allows us to steer the optimization process towards different mean-variance goals. The significance of this work is that it can be used during design cycle to increase tolerance for the effects of manufacturing variations by trading off circuit delay and area requirements for reduced timing variance with user controlled weights. We demonstrated efficacy of our approach on ISCAS benchmarks with consistent variance reduction in exchange for moderate increases in area and low increases in mean delays.

#### 2.5.6 Benefits of Research

As previously mentioned, our research can be deployed where predictability of performance of a manufactured circuit is of paramount importance. Manufacturing variations from pre-silicon PV models causes variance in power consumption due to both dynamic and leakage power variations. These variations in turn contribute uncertainties in thermal dissipation and reliability verification. The effects of such performance variations can adversely product qualification and time-to-market. In such instances, our proposed optimization becomes more desirable due to better tolerance to manufacturing variations. Our research is aimed at providing designers with a statistically aware gate sizing methodology that allows arbitrary tradeoffs between mean and variance of the delays across a circuit. It can be seen as adding a third tradeoff vector in addition to the well known area-timing tradeoffs designers work with.

## 2.6 Summary

Most recent deep submicron manufacturing technologies exhibit both inter- and intra-die variations, some of which are systematic and others which are random. The aggregate of these variations poses a significant challenge for circuit designers, who can either make worst case assumptions on all design axes such as delay, area, and power which severely limit the design space and may corner it into a wrong design point. Alternately, designers can use mean values of delays in the design phase with an expectation of widespread variations in silicon performance. Our proposed research is targeted to help designers navigate the available design space by using statistical models in the analysis and optimization of the circuit before it reaches silicon. We introduce

a new concept of a worst negative statistical slack path and plan to derive a procedure for tracing and optimizing such paths. In the process, we also derive a new approximation for the max operation on random variables for use in circuit optimization. Our approach allows us to steer the optimization process toward different mean-variance goals. The significance of this work is that it can be used during design cycle to increase tolerance for the effects of manufacturing variations by trading off circuit delay and area requirements for reduced timing variance with user controlled weights. We demonstrated fidelity of our approach on ISCAS benchmarks with variance reduction in exchange for increases in area and low increases in mean delays.

# Chapter 3

# An Efficient Algorithm for Analysis of Cyclic

# **Circuits**

## 3.1 Introduction

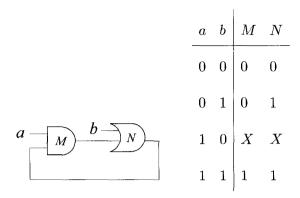

Cyclic circuits are those which contain loops or cycles within them. We will present a more formal definition later on in the chapter. An example of a cyclic circuit is shown in Figure 3.1. Cyclic circuits can be produced inadvertently during high-level synthesis from high level hardware languages such as ESTEREL [8]. They are also the most compact representation for certain circuits such as arbiters [50].

A key challenge for cyclic circuits is that correct operation is only guaranteed in specific cases. For certain input patterns, such circuits are well-behaved (functional), i.e., do not exhibit oscillations or state-holding behavior.

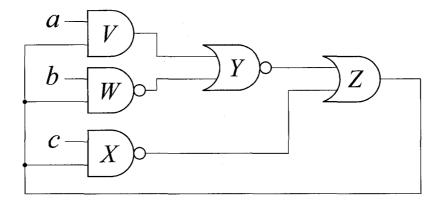

Figure 3.1: A trivial cyclic circuit and its truth table

Despite this, most circuit analysis tools forbid the presence of cycles. The central challenge of cyclic circuits is their data-dependent evaluation order, meaning their gates have no topological order. This causes difficulties for many tools such as static timing analyzers that rely on such a static order. Furthermore, applying regular logic simulation to these circuits is cumbersome.

Consider the small cyclic circuit in Figure 3.1. From its truth table, we see the circuit is well-behaved unless a=1 and b=0. It is impossible to predict with certainty how the circuit behaves when presented with this pattern. For all other input patterns, the circuit behaves combinationally because the feedback loop is broken by a controlling input on one of the gates.

We shall use the terminology of partial assignments for our exposi-

tion. A partial assignment is an assignment to one or more inputs to the loop;  $\{a=0\}$  is one such partial assignment. Our proposed algorithm will produce a set of partial assignments that provide a concise representation of the conditions under which a cyclic circuit is well-behaved. For example, the set of partial assignments  $\{\{a=0\}, \{b=1\}\}$  constitutes necessary and sufficient conditions for combinational operation of the circuit in Figure 3.1: at least one of these must hold in order for the circuit to operate functionally.

In this research, we propose a novel algorithm that can rapidly identify all possible combinational behavior of a cyclic circuit. The algorithm takes a circuit containing one or more loops and produces a set of partial assignments that represent every condition under which the circuit behaves combinationally. Our algorithm relies on the fact that gates such as ANDs and ORs have controlling inputs (0 and 1 respectively) that break feedback loops to aggressively prune the search space. The set of partial assignments our algorithm produces can be used to rule out non-constructive operation of circuits produced by high level compilers such as Esterel [6], or they can be used to create an equivalent acyclic circuit [22].

## 3.2 Notation and Definitions

This section defines the basic terminology needed for an exposition of material on cyclic circuits.

We represent circuits with a directed graph (digraph). A digraph G is a pair (V, E) where V is a set of vertices and E is a set of edges. An edge is an element of  $V \times V$  with distinct vertices. We represent a circuit as a digraph whose vertices correspond to gates and whose edges correspond to nets. A controlling value for a gate G is the value that applied to any input of G uniquely determines G's output independent of other inputs. To simplify our exposition, we only consider simple logic gates: NOT, AND/NAND, and OR/NOR. This is not a limitation as more complex gates can be represented as combinations of these gates. Loops or cycles are formally defined using graph theory in terms of strongly connected components.

**Definition 3.** A strongly connected component (SCC) of a digraph G = (V, E) is a maximal subset of vertices  $C \subseteq V$  such that any vertex in C is reachable from any other vertex in C. Inputs of an SCC are inputs of gates that are part of the SCC that are not driven by gates inside the SCC.

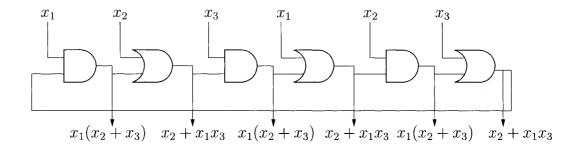

Figure 3.2 shows a circuit with a single SCC. Nets a, b, and c are inputs to the SCC. When analyzing an input circuit, we first decompose it into SCCs

Figure 3.2: Cyclic circuit for illustrating definitions

using a standard algorithm [18]. We note that finding SCCs in a circuit is linear in the size of the circuit. If the input circuit contains more than one SCC, we consider each SCC separately in a topological order.

Our analysis methodology and logic simulation use a ternary domain consisting of  $\{0, 1, X\}$  where X denotes an unknown digital value.

**Definition 4** (Malik [35]). A circuit is combinational for an input assignment if three-valued simulation starting with all internal nodes set to X resolves the output of every gate in the circuit to either 0 or 1 under the assignment.

Literature on cyclic circuits also refers to this behavior as "well-behaved" and "constructive" [51]. Combinational behavior is equivalent to stating that the circuit behaves as if it were acyclic with no X's and no oscillations.

## 3.3 Literature Survey

An extensive review of prior work on cyclic circuits was undertaken. Below is a summary of contributions in this field covering period from 1960 to late 2005.

### 3.3.1 Origins of Cyclic Circuits