## **Portland State University**

## **PDXScholar**

**Dissertations and Theses**

**Dissertations and Theses**

9-9-2009

## Simulation of INSB Devices using Drift-Diffusion Equations

Edin Sijercic

Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons

## Let us know how access to this document benefits you.

#### **Recommended Citation**

Sijercic, Edin, "Simulation of INSB Devices using Drift-Diffusion Equations" (2009). *Dissertations and Theses.* Paper 6135.

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

## **DISSERTATION APPROVAL**

The abstract and dissertation of Edin Sijercic for the Doctor of Philosophy in Electrical and Computer Engineering were presented September 9, 2009, and accepted by the dissertation committee and the doctoral program.

| COMMITTEE APPROVALS:   |                                                                                           |

|------------------------|-------------------------------------------------------------------------------------------|

| Bran                   | imir Pejcińovic, Chair                                                                    |

|                        |                                                                                           |

|                        |                                                                                           |

| Robo                   | ert Daasch                                                                                |

|                        |                                                                                           |

| <u> </u>               | *                                                                                         |

|                        |                                                                                           |

| Jame                   | es Morris                                                                                 |

|                        |                                                                                           |

|                        |                                                                                           |

|                        |                                                                                           |

|                        |                                                                                           |

| Chris                  | stof Teuscher                                                                             |

|                        |                                                                                           |

|                        |                                                                                           |

|                        |                                                                                           |

|                        |                                                                                           |

|                        | oenenkamb<br>sentative of the Office of Graduate Studies                                  |

| Kepie                  | sentative of the Office of Graduate Studies                                               |

|                        |                                                                                           |

|                        |                                                                                           |

| DOCTORAL PROGRAM APPRO |                                                                                           |

|                        | Malgorzata Chrzanowska Jesk <del>e, C</del> hair<br>Department of Electrical and Computer |

|                        | Engineering                                                                               |

**ABSTRACT**

An abstract of the dissertation of Edin Sijercic for the Doctor of Philosophy in Electrical and Computer Engineering presented September 9, 2009.

Title: Simulation of InSb Devices Using Drift-Diffusion Equations

Silicon technology has for several decades followed Moore's law.

Reduction of feature dimensions has resulted in constant increase in device density which has enabled increased functionality. Simultaneously, performance, such as circuit speed, has been improving. Recently, this trend is in jeopardy due to, for example, unsustainable increase in the processor power dissipation. In order to continue development trends, as outlined in ITRS roadmap, new approaches seem to be required once feature size reaches 10 – 20 nm range.

This research focuses on using III-V compounds, specifically indiumantimonide (InSb), to supplement silicon CMOS technology. Due to its low bandgap and high mobility, InSb shows promise as a material for extremely high frequency active devices operating at very low voltages. In this research electrical properties of InSb material are characterized and modeled with special emphasis on recombination-generation mechanisms. Device simulators based on drift-diffusion approach - DESSIS and nanoMOS – are

modified for InSb MOSFET design and analysis. To assess the quality of InSb MOSFET designs several figures of merit are utilized: Ion/Ioff ratio, I-V characteristics, threshold voltage, drain induced barrier lowering (DIBL) and unity current gain frequency for different configurations and gate lengths. It is shown that significant performance improvement can be achieved in InSb MOSFETs through proper scaling. For example, extrapolated cutoff frequencies reach into THz range. Semi-empirical scaling rules that remedy short channel effects are proposed. Finally, quantum mechanical (QM) effects in InSb MOSFET and their effect on device performance are examined using nanoMOS device simulation program. It is found that nonparabolicity has to be properly modeled and that QM effects have a large effect on threshold voltage and transconductance and should be included when analyzing and designing deca-nanometer size InSb MOSFETs.

# SIMULATION OF INSB DEVICES USING DRIFT-DIFFUSION EQUATIONS

by

## **EDIN SIJERCIC**

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY in ELECTRICAL AND COMPUTER ENGINEERING

Portland State University 2009

## Acknowledgment

I would like to express gratitude to my advisor, Dr. Branimir Pejcinovic, who provided me with constant guidance and valuable advice, Intel Corporation, for their financial support of this project, Dr. Robert Chau and my parents.

## **Table of contents**

| Acknowledgmenti                            |

|--------------------------------------------|

| List of Tablesv                            |

| List of Figuresvi                          |

| 1. Introduction and motivation 1           |

| 1.1 Problem Statement                      |

| 1.2 Current Solutions                      |

| 1.3. Potential Future Solutions            |

| 2. Research goals and contributions11      |

| 2.1 Research goals11                       |

| 2.2 Contributions12                        |

| 3. Material properties16                   |

| 3.1 Band structure and density of states   |

| 3.2 2D electron concentration              |

| 3.3 Degeneracy and intrinsic concentration |

| 3.4 Mobility and velocity saturation              | 28 |

|---------------------------------------------------|----|

| 3.5 Auger Recombination and Impact Ionization     | 30 |

| 3.6 Shockley-Reed-Hall (SRH) recombination        | 36 |

| 3.7 Band-to-Band tunneling                        | 37 |

| 4. DESSIS Implementation                          | 38 |

| 5. InSb diodes and Exclusion/extraction Mechanism | 43 |

| 5.1 Extraction Diode                              | 44 |

| 5.2 Exclusion/extraction Diode                    | 46 |

| 6. Diode simulations and results                  | 50 |

| 6.1 I-V characteristics                           | 50 |

| 6.2 Differential resistance                       | 51 |

| 7. Exclusion/extraction MOSFET                    | 56 |

| 7.1 Device description                            | 56 |

| 7.2. Short Channel effects                        | 58 |

| 7.3 Simple Scaling results                        | 60 |

| 7.4 Device scaling results                        | 62 |

| 8. Quantum Mechanical effects                      | 68 |

|----------------------------------------------------|----|

| 8.1 Non-parabolic quantum mechanical model         | 68 |

| 8.2 Impact of non-parabolicity on energy levels in |    |

| finite quantum wells                               | 71 |

| 8.3 Dual gate InSb MOSFET device                   | 74 |

| 8.4. Device Results                                | 76 |

| 9. Conclusions                                     | 85 |

| References                                         | 89 |

## **List of Tables**

| Table 1: Electrical properties of common semiconductors 6   |

|-------------------------------------------------------------|

| Table 2: Pros and Cons of the material properties of        |

| InSb for the transistor applications9                       |

| Table 3: Intrinsic concentration for different materials    |

| at 77K and 300K                                             |

| Table 4: Arora mobility model parameters                    |

| Table 5: Lombardi model parameters for InSb                 |

| Table 6: Threshold voltage [ $V_T$ ] vs. $V_{ds}$ and $L_g$ |

| Table 7: Channel doping vs. L <sub>g</sub>                  |

## **List of Figures**

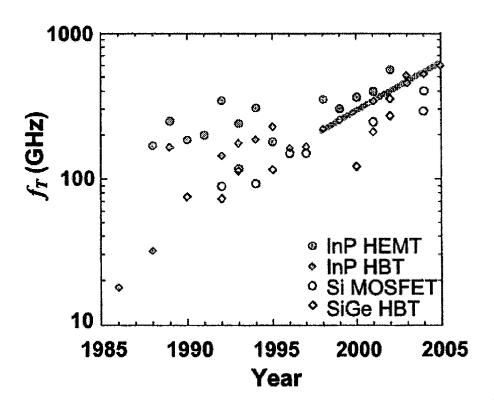

| Figure 1: Trends in the evolution of the high speed devices show exponential     |

|----------------------------------------------------------------------------------|

| increase in the unity gain frequency which can lead to the prohibitive increase  |

| in the power density [1] Copyright by World Scientific Publishing                |

| Company1                                                                         |

|                                                                                  |

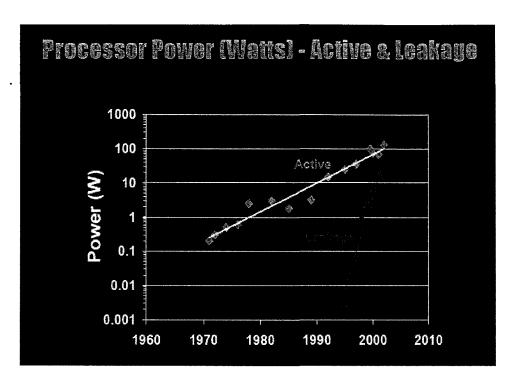

| Figure 2: Processor power trends show much faster increase of the leakage        |

| power over active power which may impede future generations of processors        |

| [3]. Copyright by Intel Corporation                                              |

|                                                                                  |

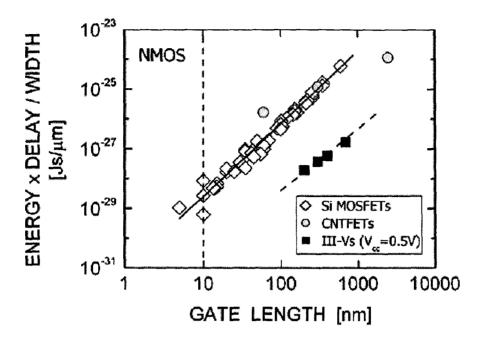

| Figure 3: Energy-delay product in Si MOSFETs, III-V QWFETs (or HEMTs)            |

| and carbon nanotube FETs; superior performance of the III-V devices [5].         |

| Copyright by IEEE7                                                               |

|                                                                                  |

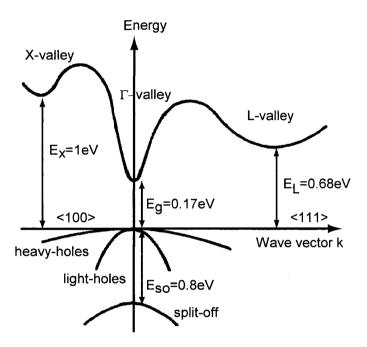

| Figure 4: InSb band structure [20]. Copyright by World Scientific                |

| rigare it mes sand structure (20). Copyright by Wend Coloniano                   |

|                                                                                  |

| Figure 5: Electron concentration vs. Fermi level for three different             |

| approximations for density of states and Fermi integrals (parabolic, eq. (13)    |

| truncated at Fermi integral of 3/2 order and full eq. (13)) show significance of |

| nonparabolicity21                                                                |

| Figure 6: Comparison of different models for 2D electron concentration in                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InSb                                                                                                                                                             |

| Figure 7: np product in equilibrium vs. Fermi level shows a large variation of two decades                                                                       |

| Figure 8: Impact ionization; electron-hole pair is generated contributing to the leakage current in the reverse bias                                             |

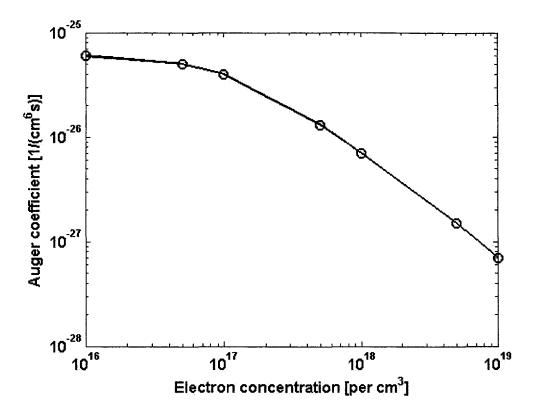

| Figure 9: Auger coefficient $C_n$ for electrons in InSb as a function of electron concentration. It is decreasing with increasing concentration due to effective |

| enlargement of the bandgap                                                                                                                                       |

| Figure 10: Equilibrium Auger recombination and electron lifetime vs Fermi                                                                                        |

| level: solid lines are from full band calculation, dashed from Beattie model in                                                                                  |

| eq. 22 and 24. It reaches a maximum slightly above the bottom of the                                                                                             |

| conduction band. Copyright by the American Institute of Physics 35                                                                                               |

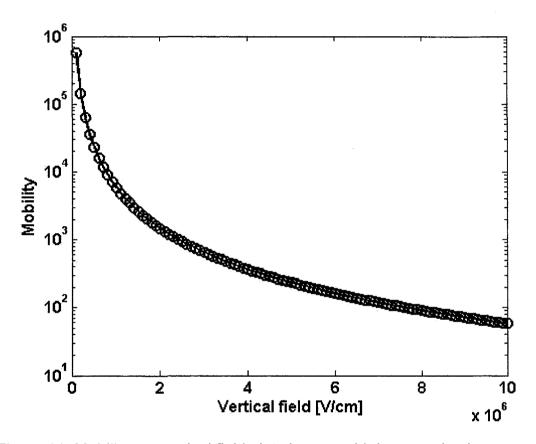

| Figure 11: Mobility vs. vertical field plot shows rapid decrease in electron                            |

|---------------------------------------------------------------------------------------------------------|

| mobility with the vertical field                                                                        |

|                                                                                                         |

| Figure 12: Extraction (top) and exclusion/extraction (bottom) diode cross                               |

| section                                                                                                 |

|                                                                                                         |

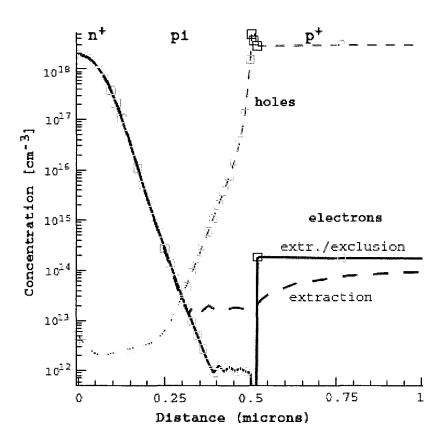

| Figure 13: Electron and hole concentrations for extraction and                                          |

| extraction/exclusion diodes under reverse bias V=-0.35 V                                                |

|                                                                                                         |

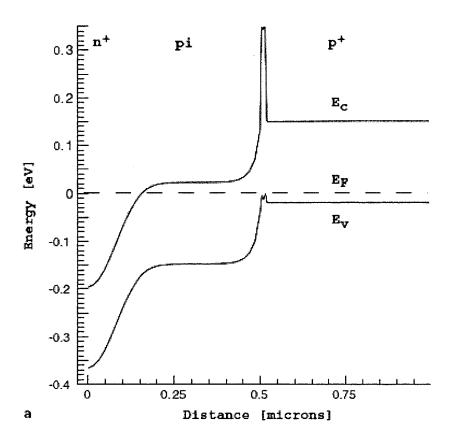

| Figure 14: Band diagrams for $n^+ - \pi - p^+ - p^+$ exclusion/extraction diode in                      |

| equilibrium47                                                                                           |

|                                                                                                         |

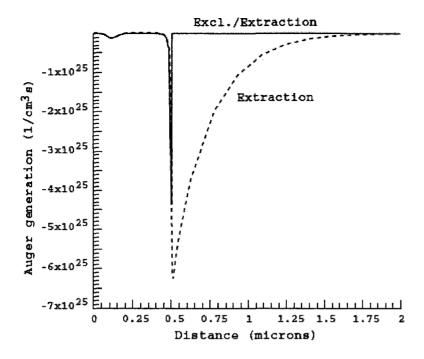

| Figure 15: Auger generation in $n^+-p-p^+$ and $n^+-\pi-p^+-p^+$ diodes under                           |

| reverse bias. Exclusion/extraction diode has reduced generation by more than                            |

| a decade in p <sup>+</sup> region close to p-n junction                                                 |

|                                                                                                         |

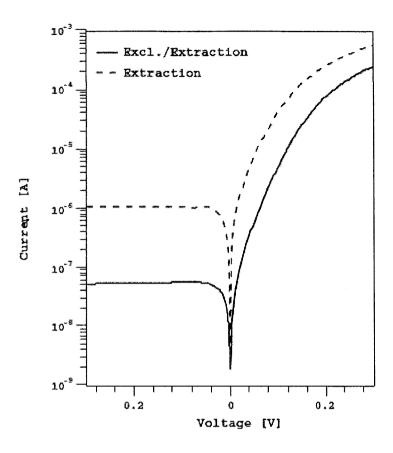

| Figure 16: Leakage currents in $n^+$ - $\pi$ - $p^+$ - $p^+$ (exclusion/extraction) and $n^+$ - $\pi$ - |

| p <sup>+</sup> (extraction) diodes show improvements in the reverse bias by addition of                 |

| thin InAlSb layer51                                                                                     |

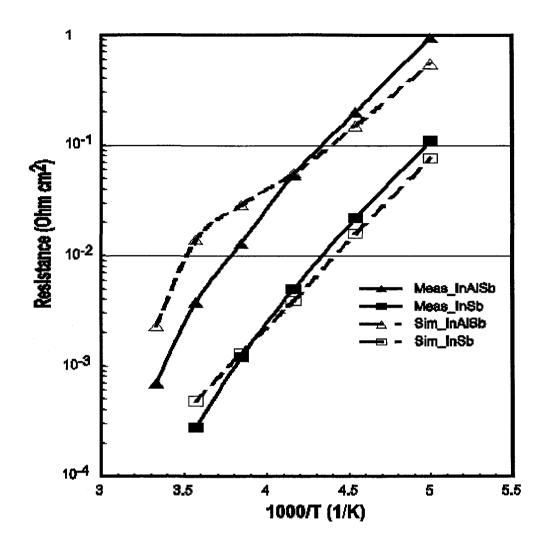

| Figure 17: Differential Resistance: simulation vs. measured data for extraction                                            |

|----------------------------------------------------------------------------------------------------------------------------|

| diode (labeled "InSb") and exclusion/extraction diode (labeled" InAlSb").                                                  |

| Extraction diode shows relatively good fit with the measured data 53                                                       |

|                                                                                                                            |

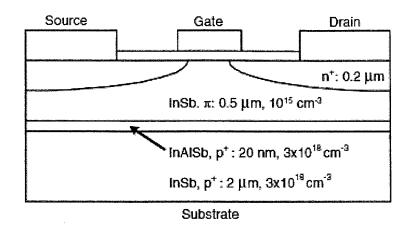

| Figure 18: Idealized cross section of the InSb MOSFET based on [6] 57                                                      |

| •                                                                                                                          |

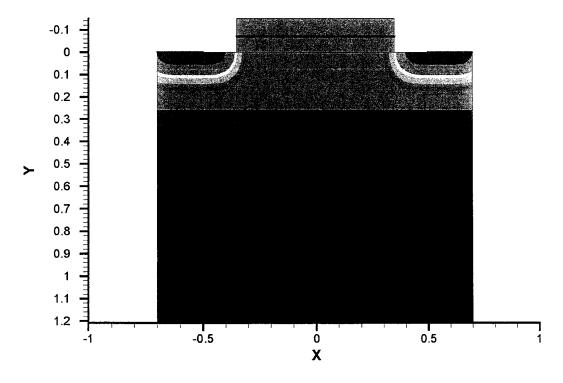

| Figure 19: InSb MOSFET cross section, as used in DESSIS all                                                                |

| units in µm                                                                                                                |

|                                                                                                                            |

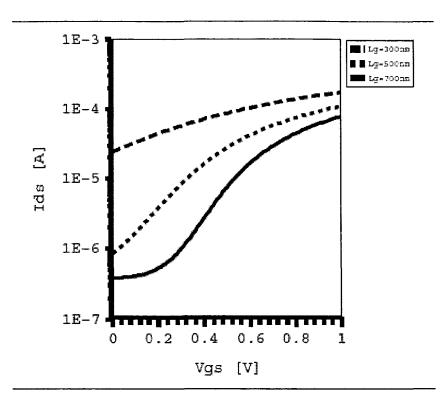

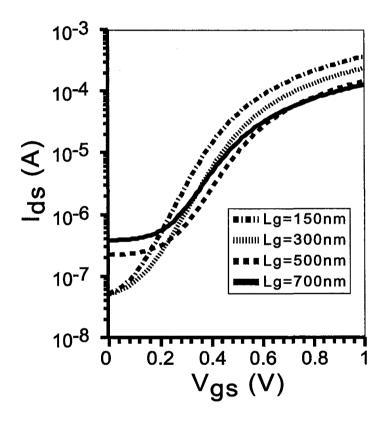

| Figure 20: $I_{ds}$ vs $V_{gs}$ for different gate lengths; short channel effects become                                   |

| dominant at 300nm device                                                                                                   |

|                                                                                                                            |

| Figure 21: I <sub>on</sub> /I <sub>off</sub> vs. gate length show more than 3 decades in I <sub>on</sub> /I <sub>off</sub> |

| separation, which is satisfactory performance; I <sub>off</sub> is I <sub>ds</sub> at zero volts,                          |

| I <sub>on</sub> at 1V                                                                                                      |

|                                                                                                                            |

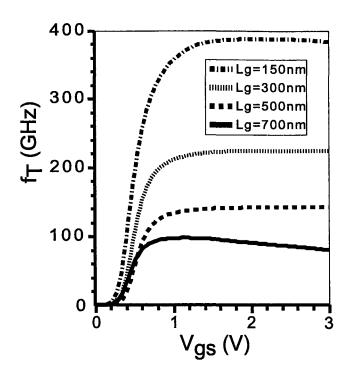

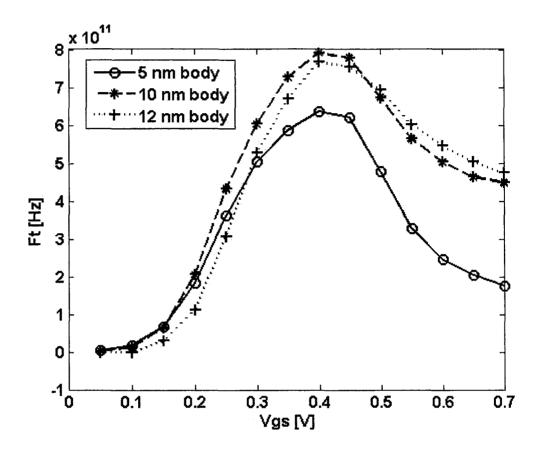

| Figure 22: $f_T$ vs. gate length and gate voltage $V_{gs}$ . inSb shows very high values                                   |

| for the unity gain frequency                                                                                               |

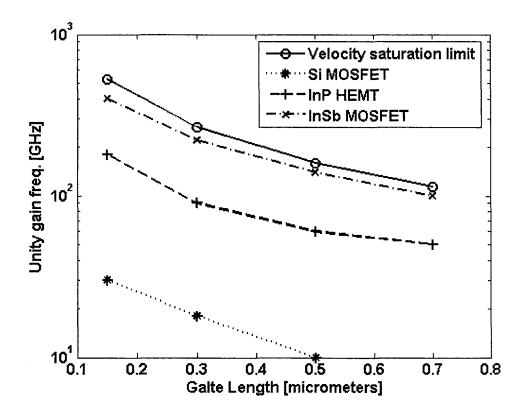

| Figure 23: Extrapolated f <sub>T</sub> demonstrates InSb is the most promising material           |

|---------------------------------------------------------------------------------------------------|

| for high speed applications. Numbers for Si and InP from [5] 67                                   |

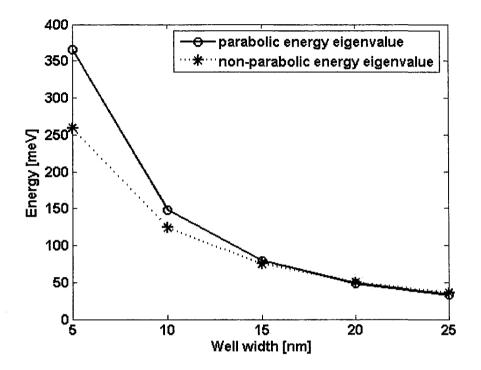

| Figure 24: 1eV rectangular quantum well ground states; Below 15nm                                 |

| nonparabolicity has to be taken into account                                                      |

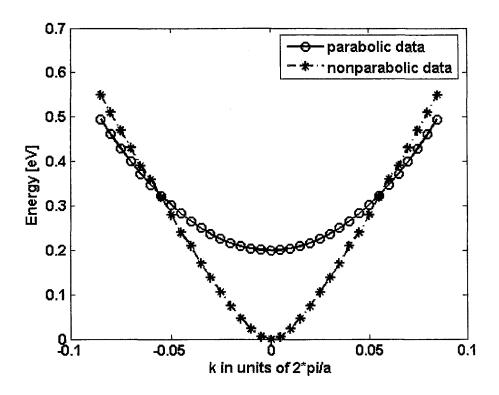

| Figure 25: Comparison of parabolic and nonparabolic E-k diagram.                                  |

| Assumption of parabolicity results in large errors in energy 74                                   |

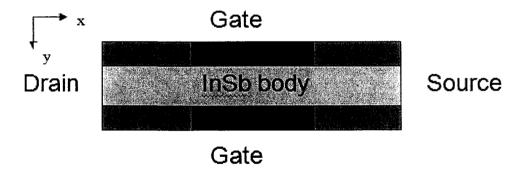

| Figure 26: Dual gate InSb MOSFET cross section                                                    |

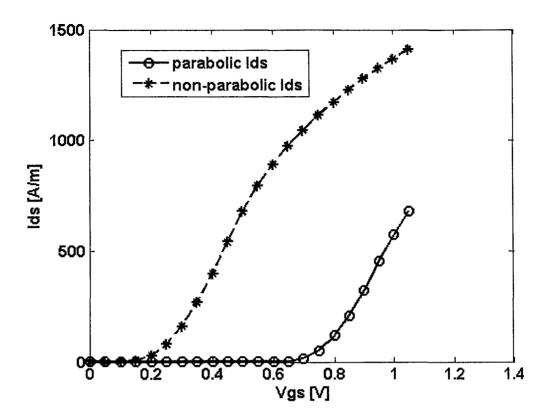

| Figure 27: $I_{ds}$ vs. $V_{gs}$ for $V_{ds}$ =0.5V show large shift in the threshold voltage due |

| to the nonparabolicity                                                                            |

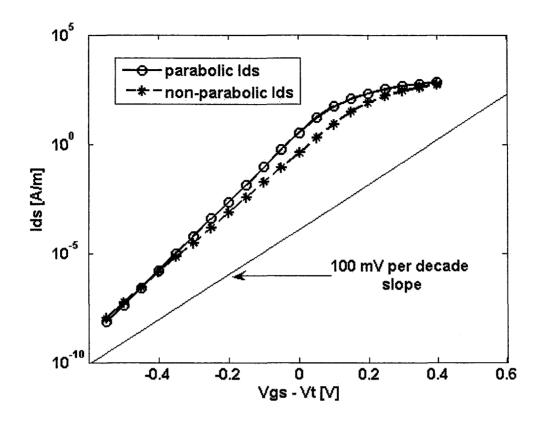

| Figure 28: Subthreshold I-V curves and subthreshold slope calculation;                            |

| nonparabolicity slightly increases subthreshold slope                                             |

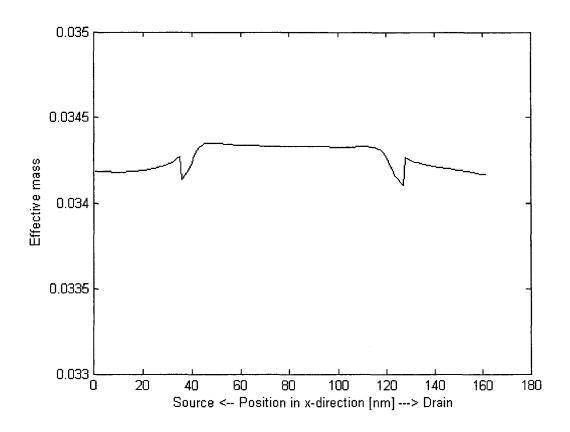

| Figure 29: Effective electron mass along the channel (in units of free electron                   |

| mass) is virtually constant, though different from the bottom of the $\Gamma$ valley              |

| value                                                                                             |

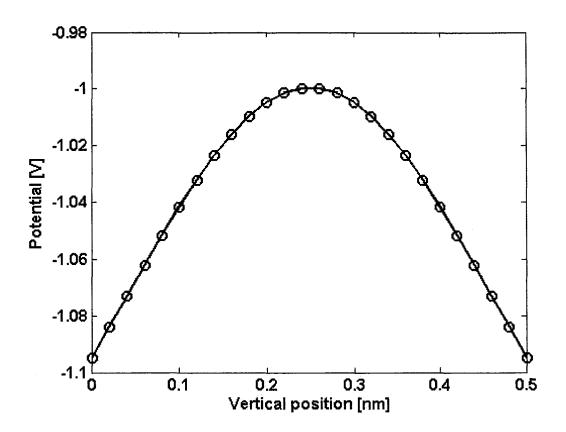

| Figure 30: Variation of the potential in the vertical direction is             |

|--------------------------------------------------------------------------------|

| within 10% 80                                                                  |

|                                                                                |

|                                                                                |

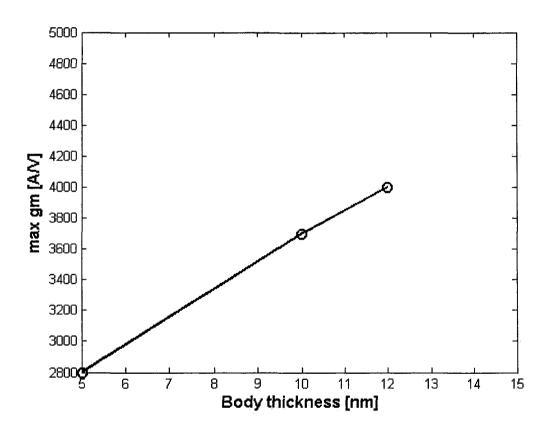

| Figure 31: Max. Transconductance vs. body thickness shows substantial          |

| decrease in the transconductance with the reduced body thickness due to the    |

| mixing of the inversion layers                                                 |

|                                                                                |

|                                                                                |

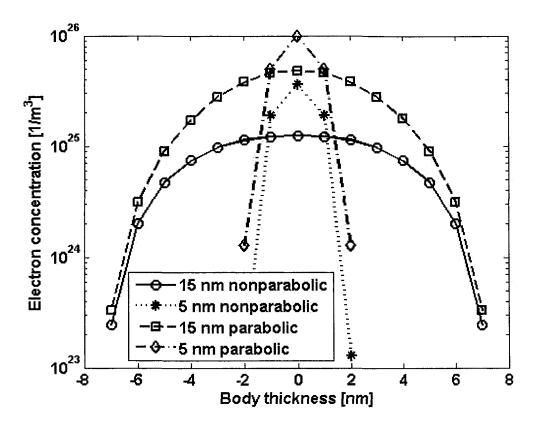

| Figure 32: Electron concentration vs. vertical position for 5 and 15 nm thick  |

| device; maximum concentration occurs in the middle of the device due to the    |

| QM effects82                                                                   |

|                                                                                |

|                                                                                |

| Figure 33: Unity gain frequency is directly proportional to the body thickness |

| due to the mixing of the inversion layers84                                    |

## 1. Introduction and motivation

#### 1.1 Problem statement

One of the most commonly used parameters to asses performance of the high-speed devices is the unity gain frequency. Trends in the recent years, for Silicon based MOSFETs, SiGe HBTs and InP HEMTs are shown in the Fig. 1 [1]

Figure 1: Trends in the evolution of the high speed devices show exponential increase in the unity gain frequency which can lead to the prohibitive increase in the power density [1] Copyright by World Scientific Publishing Company

In the past, increase in the unity gain frequency has led to the increase in the operation frequency. This increase, in turn, would lead to the increased power dissipation, for example through interconnect losses [2], increase in the leakage current and the nature of CMOS circuit operation. Also, reduction in the gate length, which is mainly responsible for the increase in the frequency shown in the graph, will enable larger device densities, leading to the larger power density. Currently, smallest commercial MOSFET gate length is 35 nm and HEMT 50 nm.

Increase in the processor power, active and leakage, is shown in the Fig. 2 [3]. Clearly, these figures illustrate that power is one of the main roadblocks to successfully maintaining Moore's law. In order to sustain product technology trends, as outlined in ITRS roadmap [4], new technologies will be required.

Figure 2: Processor power trends show much faster increase of the leakage power over active power which may impede future generations of processors [3]. Copyright by Intel Corporation

#### 1.2. Current solution

Further increases in the frequency of the execution of the single core processor would lead to the enormous power dissipation, which becomes prohibitive. One way to avoid this "wall", which microprocessor industry has already adopted, is to increase throughput, i.e. parallelize execution by using multiple cores. Trade-off in this approach is diminishing return with increased number of cores. At some point in the future, adding cores would not increase performance substantially, given the Amdahl's "Law":

Max.

$$speedup = \frac{1}{(1-P) + \frac{P}{N}}$$

(1)

Where P is the fraction of the software code that can be parallelized and N is the number of cores. If number of cores tends to infinity, benefit or speed up will saturate at  $\frac{1}{1-P}$ . In real world applications, this saturation will occur fairly quickly. Also, this approach presents challenge to the software developers to massively parallelize code, increasing the value of P.

#### 1.3 Potential future solutions

Alternative way would be to use materials other than silicon, which would enable higher current gain cut-off frequency f<sub>T</sub> for the same gate length and lower power consumption. This approach is already subject of intense research, e.g. in [5, 6, 7, 8]. However, some of the drawbacks of these new materials include the lack of the suitable process infrastructure, and the cost of setting one up, since the semiconductor industry is currently very heavily invested in silicon manufacturing infrastructure. Manufacturing of the devices based on these new materials or device designs can be substantially more expensive than silicon. Other potential issues are increased leakage at the room temperature, requiring cooling or some other expensive technique to enable device operation. Also, some materials may have a very different performance for PMOS and NMOS devices, making CMOS logic useless, i.e.

slower device reducing overall performance or requiring larger area, rendering this new technology impractical. Hence, new logic technologies may be required, potentially increasing area and the cost.

For example, carbon nanotubes have been investigated for transistor applications [9, 10]. Although they do show some promising results, there are problems with mass production and control of the nanotube conductivity. Surface features, which are hard to control, can condition nanotube to be either a conductor or semiconductor rendering its use in practical circuits somewhat dubious.

Use of alternative materials is the subject of the research presented here. We have focused on III-V compounds, in particular indium antimonide, as an alternative to silicon. Among bulk III-V compounds, InSb shows the highest mobility (7.8x10<sup>4</sup>cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and saturation velocity (5x10<sup>7</sup> cm/s) and has the smallest bandgap (0.17 eV). Hence, we expect InSb MOSFET devices to have much higher f<sub>T</sub> than silicon based, for the same gate length. Also, due to its high electron mobility, "knee" voltage on the I-V curve could be attained at much lower drain voltage, compared to the silicon, allowing for a low power operation. Comparison of some important physical parameters of Si, GaAs, InAs and InSb is shown in the Table 1. In practical MOSFET devices it is inversion layer mobility that matters and it is usually significantly smaller than the bulk value, as discussed later. One exception are HEMT devices that can have channel mobility close to intrinsic material values [11]. Mobility can also

be manipulated by judicious use of strain as is done in modern Si MOSFETs [12, 13].

|                                                                      | Sì              | InSb              | GaAs            | InAs                |

|----------------------------------------------------------------------|-----------------|-------------------|-----------------|---------------------|

| Bandgap [eV]                                                         | 1.1             | 0.175             | 1.43            | 0.354               |

| effective electron mass                                              | 0.19            | 0.013             | 0.072           | 0.023               |

| electron mobility [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | 1,500           | 78,000            | 8,500           | 40,000              |

| saturation velocity [cm s <sup>-1</sup> ]                            | 10 <sup>7</sup> | 5*10 <sup>7</sup> | 10 <sup>7</sup> | 3.5*10 <sup>7</sup> |

| Hole mobility                                                        | 450             | 850               | 400             | 500                 |

Table 1: Electrical properties of common semiconductors

In addition, Intel and QinetiQ have published work on quantum well transistors using indium antimonide [5]. This device shows promising trends as a substitute for silicon in the future MOSFETs. In particular, energy-delay product is substantially improved in InSb device over silicon based MOSFET, due to lower supply voltage and higher electron mobility, as shown in the Fig. 3 [5]. Energy-delay product is a useful metric for the efficiency of the devices, which represents energy required to run device at the particular speed.

Lowering energy-delay product enables operation at the higher speed with the same energy, or alternatively, same speed operation at the lower energy [14].

Figure 3: Energy-delay product in Si MOSFETs, III-V QWFETs (or HEMTs) and carbon nanotube FETs; superior performance of the III-V devices [5]. Copyright by IEEE

Exponential fits were generated for the graphs in the Fig. 3 and are given in eq. (2) - (4). In general, data points for the proposed solution should be below the silicon curve by at least factor of 2, in order to make it economically attractive.

If we choose 100 nm gate length, separation in energy-delay product between InSb and Si is more than a decade. This means that for the same gate length we can achieve better figure of merit, or alternatively, for the fixed energy delay product we can utilize larger gate length with InSb. Hence, Intel

researchers [5] conclude that InSb is the most promising material in this respect and that it could lead to significant reduction of dissipated power.

Si

$$MOSFET = 5.22 \cdot 10^{-32} \cdot e^{(\ln(L_g)2.586)}$$

(2)

$$CN \quad FET = 10^{-27} \cdot e^{\left(\ln\left(L_g\right)\right)} \tag{3}$$

$$InSbHEMT = 1.871 \cdot 10^{-32} \cdot e^{(\ln(L_g)_{1.58})}$$

(4)

However, due to very small bandgap, InSb devices may have high leakage current at room temperature. For this reason, InSb devices were used primarily as photo-diodes at low temperatures (77K) but not as transistors for digital logic. This problem needs to be solved if InSb is to be considered as a supplement to silicon. Also, InSb hole mobility is about 100 times smaller than electron mobility at the room temperature and intrinsic material. This makes ptype device much slower than n-type, making CMOS technology with InSb inefficient, as explained earlier. New logic operation using n-type devices only should be employed and investigated. Alternatively, p-channel devices could be improved through strain engineering or by employing heterojunction structures. In this dissertation, however, our primary interest is in investigating n-channel devices.

Additional challenge in making the case for and investigating InSb transistor operation, which is the ultimate objective of this research and dissertation, is adequate modeling. High nonparabolicity and degeneracy

necessitate modification of the carrier density equations, as well as Schrödinger equation. Based on our literature survey, only limited effort has been spent in this direction. Detailed overview of the current state of the art is given at the beginning of each subsection.

Summary of the pros and cons of InSb discussed in our work is given in Table 2.

| Pro                                           | Con                          |

|-----------------------------------------------|------------------------------|

| High mobility                                 | High electron intrinsic conc |

| High velocity Large disparity between n and p |                              |

| sat                                           | mobility                     |

Table 2: Pros and Cons of the material properties of InSb for the transistor applications

In the first part of the dissertation, we discuss research goals and metrics used to assess performance of the proposed device. In the second part we describe in detail important electrical properties of InSb which enable high performance MOSFET. In the third part DESSIS software implementation of this material is described. Since recombination-generation limits  $I_{on}/I_{off}$  ratio, in the fourth section we discuss these mechanisms in detail. Fifth part describes exclusion/extraction principle, which limits carrier generation in InSb device, enabling room temperature operation. Calibration and validation of this mechanism, through diode simulations, is described in the sixth section. Part seven discusses design of relatively large InSb MOSFETs and their performance and part eight deals with quantum mechanical effects in deca-

nanometer MOSFETs. Here we discuss necessary modification of the Schrödinger equation to account for the nonparabolicity and propose self-consistent methodology to calculate the effective mass and energy eigenvalues. This methodology is demonstrated on the dual-gate MOSFET device. Finally, we close with conclusions and make suggestions for future work.

## 2. Research goals and contributions

## 2.1 Research goals

The main research goals of this project are to develop appropriate material and device models and to examine feasibility and advantages of InSb MOSFET device over comparable silicon technology. To achieve that, following tasks have been completed:

- 1. characterize and model electrical properties of InSb,

- demonstrate applicability of device simulators based on drift-diffusion approach (DESSIS and nanoMOS) for InSb MOSFET design and analysis.

- assess the quality of the device, by analyzing I<sub>on</sub>/I<sub>off</sub> ratio, I-V

characteristics, threshold voltage, drain induced barrier lowering (DIBL)

and unity gain frequency for different configurations and gate lengths

using drift-diffusion simulation

- Study quantum mechanical effects in InSb MOSFET and their effect on transport properties and threshold voltage using drift-diffusion simulation in nanoMOS device simulation program.

- 5. Investigate scaling rules to remedy possible short channel effects.

Conclusions reached in accomplishing these tasks help us not only to identify areas of performance in which InSb MOSFET will show benefit over other types of transistors but also to point out areas of potential trouble.

#### 2.2 Contributions

Task: characterize electrical properties of InSb, which has been only partially done in the current literature

Conclusion and original contribution: developed appropriate and accurate physical models for InSb: electron concentration, density of states, recombination-generation, and mobility. We have developed novel mathematical models to describe 3D and 2D nonparabolic electron concentration which match measured data. These models were successfully implemented in DESSIS and nanoMOS (Matlab). Also, we have successfully implemented Auger model and resolved issues with numerical instability.

Status: Published in [15, 16]

2. Task: Demonstrate applicability of the drift-diffusion simulator (DESSIS) for InSb diodes and MOSFETs

Conclusion and original contribution: We have shown that the results obtained using models in the task 1 can be implemented in the currently available commercial simulators. We have characterized behavior of InSb diodes and MOSFETs, like differential resistance and I-V characteristics and showed that they match well measured data

**Status**: Published in [8] and [15]

3. Task: Assess quality of InSb MOSFET device, analyzing I<sub>on</sub>/I<sub>off</sub> ratio, DIBL, I-V characteristics, unity gain frequency for different configurations and gate lengths using drift-diffusion simulation

Conclusion and original contribution: Developed appropriate scaling rules for InSb MOSFET and demonstrated usefulness (as defined above) of the device down to 150nm gate length.

Status: Published in [8].

4. Task: Study quantum mechanical effects in InSb MOSFET on the transport properties and threshold voltage using drift-diffusion simulation

Conclusion and original contribution: Quantization effects in InSb MOSEFT have not been investigated in the literature and are critical for MOSFET operation. Using an analytic solution we have first demonstrated that nonparabolicity in InSb will have substantial impact on the energy states for narrow quantum wells and cannot be neglected. Therefore, we have developed mathematical model for self-consistent calculation of the effective mass and energy eigenvalues (Schrödinger equation). So far in literature, this was done separately.

**Status:** To be submitted for publication [17]

**5. Task:** Analyze performance of the dual gate MOSFET and assess impact of InSb nonparabolicity on the performance. Also, identify any

major roadblocks for the further scaling of InSb devices through nanoMOS drift-diffusion simulation.

Original contribution: We have demonstrated that dual gate MOSFET device can be successfully simulated in nanoMOS drift-difusion and quantum mechanical simulator. We show that nonparabolicity affects threshold voltage substantially and has to be taken into consideration. Impact of nonparabolicity on the subthreshold slope and the shape of the electron concentration profile in the channel is small. We have identified mixing of the inversion layers from two gates as a major factor in the reduction of the unity gain frequency, hence suitable scaling rules need to be developed.

**Status:** To be submitted for publication in [17]

To perform these tasks we used two different simulators: DESSIS and nanoMOS. DESSIS is a commercially available simulator [18], very accurate for silicon device simulation and widely used in industry. However, source code is not open and it has limited options for modification through so-called pmi interface (C-code interface). DESSIS is not designed for highly degenerate and non-parabolic materials like InSb, so creative ways are devised to implement transport properties of InSb. Lack of reliable electrical parameters and poor characterization of InSb makes this task even more difficult.

It has been determined that non-parabolic quantum mechanical treatment cannot be successfully implemented in DESSIS. While DESSIS is more accurate for the calculation of the leakage currents, this is not critical for the cases that require quantum mechanical treatment, due to small volume of the active region. Hence, we used nanoMOS [19, 48] which is an open-source Matlab code developed by Purdue University for simulation of dual gate MOSFET. Since it does not include any recombination-generation mechanisms and it has limited number of physical models for various parameters, such as mobility, it is less accurate then DESSIS, but it can be relatively easily modified to include nonparabolic effects for both transport and quantum mechanical equations. It is primarily used to investigate trends and indentify potential roadblocks in device design. Code is stored on the ICDT website at http://web.cecs.pdx.edu/~hfdmlab/Edin.

In the following section we describe most important electrical parameters of inSb.

## 3. Material properties

In our simulations we use so called drift-diffusion simulation mode. It is isothermal simulation, suitable for low power density devices which have long active regions. Reason we have chosen drift diffusion over some other alternatives, like hydrodynamic, ballistic or Monte Carlo simulation, is that for the purposes of the computation of the I<sub>on</sub> and I<sub>off</sub> it has better numerical stability. Also, size and accuracy of our simulated devices is large enough to make assumptions for drift diffusion to be valid. Basic equations solved are Poisson (eq. (5)), electron and hole continuity equations (6) and current density equations (7) [18]

$$\nabla \varepsilon \cdot \nabla \psi = -q \left( p - n + N_{D^{+}} - N_{A^{-}} \right)$$

$$\nabla \overrightarrow{J}_{n} = qR + q \frac{\partial n}{\partial t}$$

$$\nabla \overrightarrow{J}_{p} = -qR - q \frac{\partial p}{\partial t}$$

$$(6)$$

$$\overrightarrow{J}_{n} = -nq\mu_{n} \nabla \phi_{n}$$

$$\overrightarrow{J}_{p} = -pq\mu_{p} \nabla \phi_{p}$$

$$n = n_{i,eff} \cdot \exp\left( \frac{-q(\phi_{n} - \psi)}{kT} \right)$$

$$p = n_{i,eff} \cdot \exp\left( \frac{q(\phi_{p} - \psi)}{kT} \right)$$

Where  $\psi$  is electrostatic potential,  $\varepsilon$  is the electrical permittivity, q is the elementary electronic charge, n and p are the electron and hole densities, and  $N_D^+$  is the number of ionized donors, and  $N_A^-$  is the number of ionized acceptors,  $n_{i,eff}$  effective intrinsic concentration, R is the net electron—hole recombination rate,  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities and  $\phi_n$  and  $\phi_p$  are the electron and hole quasi-Fermi potentials, respectively [18]. These equations are discretized on a given geometry, and we need to know doping and the material properties at each point. Proper models for R and  $\mu_n$  and  $\mu_p$  have to be provided.

Implicit in the eq. (5) through (7) is Einstein's relationship between  $\mu$  and D,

i.e.

$$\frac{D}{\mu} = \frac{d\eta}{d(\ln(n))}$$

where D is diffusivity and  $\eta$  is Fermi level.

#### 3.1 Band structure and density of states

InSb is a direct bandgap material with the smallest bandgap of the III-V material family ( $E_g$ =0.17V). The band structure for this material is shown in Fig. 4 . InSb is direct bandgap material, i.e.  $\Gamma$  valley is directly above the peak of the valence band. Next valley is L-valley, 0.68 eV above valence band. This means that bottom of the  $\Gamma$  valley and the bottom of the L-valley are separated by about 0.5 eV at the room temperature. As we will see later, highly doped n-type

17

InSb ( $\sim 10^{20}$  cm<sup>-3</sup>) will have transfer of electrons from the  $\Gamma$  valley to the L-valley.

Valence band is doubly degenerate and split off band is separated by 0.8 eV from other two valence bands. Split off band will have impact on non parabolicity and cannot be neglected in the calculation of the effective mass, as will be shown later.

Figure 4: InSb band structure [20]. Copyright by World Scientific

In most commonly used semiconductor materials a standard parabolic band approximation can be used. For some of the III-V compounds this approximation begins to break down and the standard parabolic model is modified to include the non-parabolicity factors, so that the E-k relationship is given by:

$$E(1 + \alpha E + \beta E^2 + ...) = \frac{\hbar^2 k^2}{2m_e}$$

(8)

where  $m_e$  is the electron effective mass, E is energy, k is wave-vector and  $\alpha$ ,  $\beta$  are nonparabolicity factors. Usually eq. (8) is truncated to include only the lowest order of nonparabolicity, i.e. just the term containing  $\alpha$ .

InSb has a very large non-parabolicity factor of around 5 [1/eV] [20], compared with Si at 0.5 and GaAs at 0.64. Van Wood [21] developed equations to calculate electron concentration for non parabolic materials, but the result was not validated for InSb and final equation is not suitable to be implemented in DESSIS. Smith and Brennan propose dispersion equation but it does not fit experimental data for InSb well [22]. Here we develop independent approach.

To calculate density of states, we find number of states N at the certain wavevector k, contained within [k, k+dk].

$$g(E) = \frac{1}{L^3} \frac{dN}{dE}$$

$$N = \frac{k^3 L^3}{3\pi^2}$$

where L has units of real space.

Based on eq. (8) an exact 3D non-parabolic density of states can be derived:

$$g(E) = \frac{\sqrt{2}}{\hbar^2 \pi^2} \sqrt{E} m_e^{\frac{3}{2}} \sqrt{1 + \alpha E} (1 + 2\alpha E)$$

(9)

which for the limit of small  $\alpha$  results in the well known density of states function [23]. Eq. (9) needs to be put into a more suitable form for later integration in eq. (11). Two simplifications were used:

- 1. only the first term of Taylor's expansion of the  $\sqrt{1+\alpha E}$  is retained and it is assumed that  $F_{3/2} \approx F_{1/2}$ ,

- 2. more accurate approximation is obtained by retaining the first two terms of the Taylor's expansion of  $\sqrt{1+\alpha E}$  and neglecting higher terms, so that:

$$g(E) \approx const.\sqrt{E}\left(1 + \frac{5}{2}\alpha E - \frac{7}{8}\alpha^2 E^2\right) \tag{10}$$

Electron concentration is then calculated from:

$$n = \int g(E)f(E)dE \tag{11}$$

which for the two cases is evaluated to be:

1.

$$n = \overline{N_C} F_{1/2}(\eta)$$

,

$$\overline{N_C} = (1 + 15 \frac{\alpha m_e kT}{2\hbar^2}) N_C \tag{12}$$

2.

$$n = N_c \{ F_{1/2}(\eta) + \frac{15\alpha}{4} F_{3/2}(\eta) + \frac{105\alpha^2 (kT)^2}{32} F_{5/2}(\eta) \}$$

(13)

where  $N_C=2(\frac{m_ekT}{2\pi\hbar^2})^{\frac{3}{2}}$  and  $F_{1/2}$ ,  $F_{3/2}$ ,  $F_{5/2}$  are the Fermi integrals of order 1/2, 3/2 and 5/2, respectively, with  $\eta=(E_F-E_c)/kT$ . Using parabolic approximation

electron concentration has the same form as eq. (12) but  $\overline{N_c}$  is replaced by the familiar effective density of states  $N_c$ . Our results indicate that in the case of

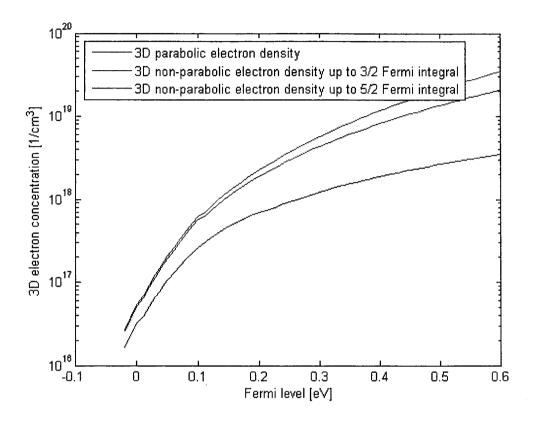

Figure 5: Electron concentration vs. Fermi level for three different approximations for density of states and Fermi integrals (parabolic, eq. (13) truncated at Fermi integral of 3/2 order and full eq. (13)) show significance of nonparabolicity.

eq. (13) integrals of order higher than 5/2 do not affect the results appreciably. Plot of different approximations is shown in Fig. 5. Standard parabolic formula (blue line in Fig. 5) substantially underestimates electron concentration, by about an order of magnitude for Fermi level 0.5 eV above E<sub>c</sub>. Error is significant

even for low doping. Since the highest n-type doping in our device is about 10<sup>19</sup>, parabolic expression for n would result in the Fermi level being higher that the work function, clearly a non-physical result.

Green plot represents eq. (13) truncated at Fermi integral 3/2, while red one is full eq. (13). Small glitch at about 0.1 eV is due to different algorithms used to compute higher order Fermi integrals, depending on whether Fermi level is high or low and it should be neglected. At low doping conditions (up to  $10^{18}$  cm<sup>-3</sup>), contribution of Fermi integral of the order 5/2 is negligible, but at the highest doping it can be as much as factor of 2. Since 3D electron concentration is used in DESSIS to compute Auger recombination, as will be shown in the section 3.5, accurate treatment is necessary. Therefore, full eq. (13) has to be implemented in the simulator.

### 3.2 2-D electron concentration

In this section we develop approximate 2D electron concentration formula for nonparabolic materials. 2D expression is needed because nanoMOS calculates 2D densities due to discretization of energy in one dimension. This formula is implemented in nanoMOS.

Two-dimensional electron concentration is in general given by:

$$n = \int D(E) \cdot f(E) dE \tag{14}$$

$$D(E)dE = \frac{k}{\pi}dk \tag{15}$$

$$k = \sqrt{\frac{2 \cdot m^*}{\hbar^2}} \sqrt{(E + \alpha E^2)} \Rightarrow dk = \sqrt{\frac{2 \cdot m^*}{\hbar^2}} \frac{1 + 2\alpha E}{2\sqrt{(E + \alpha E^2)}} dE \qquad (16)$$

Where D is energy dependent two dimensional density of states, f(E) is Fermi-Dirac probability function and  $\alpha$  is non-parabolicity parameter. Substituting k and dk into the expression for the density of states we get:

$$D(E)dE = \frac{1}{\pi} \sqrt{\frac{2 \cdot m^*}{\hbar^2}} \sqrt{\left(E + \alpha E^2\right)} \cdot \sqrt{\frac{2 \cdot m^*}{\hbar^2}} \frac{1 + 2\alpha E}{2\sqrt{\left(E + \alpha E^2\right)}} dE$$

$$D(E)dE = \frac{m^*}{\pi \cdot \hbar^2} (1 + 2\alpha E)dE \tag{17}$$

$$n = \int D(E) \cdot f(E) dE = \frac{m^*}{\pi \cdot \hbar^2} \int \frac{(1 + 2\alpha E)}{1 + e^{(E - Ef)/kT}} dE =$$

$$= \frac{m^*}{\pi \cdot \hbar^2} \left[ kT F_0(\eta) + 2 \cdot \alpha \cdot (kT)^2 F_1(\eta) \right] \tag{18}$$

Where  $F_0$  and  $F_1$  are Fermi-Dirac integrals of order zero and one, respectively. Eq. (18) is expression for two-dimensional non-parabolic electron concentration. Note that this expression is exact up to E-k expansion

in  $\alpha$ , i.e. up to accuracy of truncating eq. (8) after  $\alpha$ . Although eq. (18) is exact it is difficult to implement in a device simulator, due to two Fermi integrals, of order zero and order one. Additional difficulty in using this equation is in the derivation of the Einstein relationship for non-parabolic material, since it involves calculation of the derivative of electron concentration n with the respect to the Fermi level. Here we propose alternative expression. We introduce quantity  $N_c^*$  given by:

$$\overline{N}_c^* = \frac{m_e kT}{\pi \hbar^2} + \frac{m_e}{\pi \hbar^2} \cdot 2\alpha (kT)^2 \tag{19}$$

This is just a sum of prefactors to the Fermi integrals in the eq. (18). Then we claim that eq. (15) can be approximated by:

$$n = \overline{N}_c F_{1/2}(\eta) \tag{20}$$

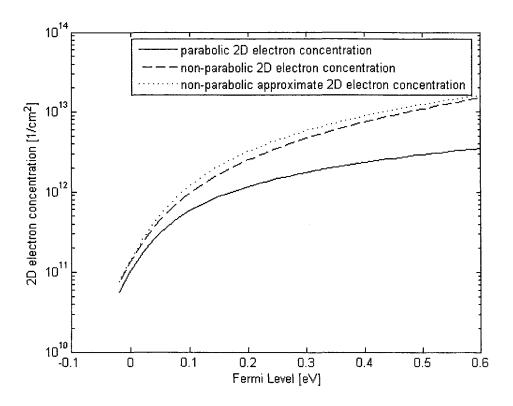

Eq. (18) and (20) are compared In Fig. 6, together with the parabolic expression. Parabolic expression would substantially underestimate electron concentration for a given Fermi level. As can be seen, eq. (20) approximates eq. (18) fairly well: in the worst case electron concentrations differ by 27 % for a given E<sub>F</sub>, with an average value around 19%. Since in nanoMOS, which uses these expressions, we do not compute any recombination/generation, this level error in electron concentration can be tolerated. We have implemented eq. (20) in nanoMOS for modeling of dual-gate InSb MOSFET transistors.

Figure 6: Comparison of different models for 2D electron concentration in InSb

## 3.3 Degeneracy and intrinsic concentration

Intrinsic concentration is a material parameter that often shows up in modeling of various material properties or processes in semiconductors. InSb, due to its very low bandgap and degeneracy, presents significant challenges in calculating and using this parameter. A material is considered to be degenerate if the Fermi level is less than 3kT (Boltzmann constant x temperature) below the conduction band or above the valence band. This is the point where the exponential Boltzmann approximation and the F<sub>1/2</sub> integral

start to significantly diverge. To get a rough estimate for the InSb case, we can use:

$$E_i = \frac{E_c + E_v}{2} + \frac{3}{4} kT \ln(\frac{m_h}{m_e}) \rightarrow E_i = 0.15 \text{eV for InSb}$$

(21)

This means  $E_i$  is only 0.02eV below the conduction band, well within the 3kT/q (=0.075eV) limit for degeneracy at 300K. Therefore, Fermi-Dirac statistics must be used for electrons in n-type InSb. Note, however, that  $E_i$  is far away from the valence band so that Maxwell-Boltzmann statistics can be used for holes in heavily n-doped regions. Fig. 5 illustrates the extreme degeneracy that occurs in n-type InSb, e.g., as doping concentration increases to  $10^{19}$  the Fermi level rises to  $\sim$ 0.45 eV above the conduction band.

Fermi-Dirac statistics will increase computational difficulty of some other models, like quantized energy or Auger recombination-generation. Some other models, like Einstein relationship between mobility and diffusivity, will have to be modified to accommodate Fermi-Dirac statistics [24]. Because of its very small bandgap (E<sub>g</sub> = 0.17eV), intrinsic concentration of InSb is very large, e.g. n≈2x10<sup>16</sup>cm<sup>-3</sup> at 300K, which has traditionally limited its usage to cooled infrared detectors. At 77K n<sub>i</sub> drops to ~10<sup>9</sup>cm<sup>-3</sup> which is comparable to Si [1.6x10<sup>10</sup>cm<sup>-3</sup>] and GaAs [1.1x10<sup>7</sup>cm<sup>-3</sup>] at 300K. Table 3 below shows intrinsic concentration for different semiconductors at 77K and 300K.

| intrinsic concentration<br>[cm <sup>-3</sup> ] | Si               | InSb               | InAs              |

|------------------------------------------------|------------------|--------------------|-------------------|

| T=300 K                                        | 10 <sup>10</sup> | 2x10 <sup>16</sup> | 10 <sup>15</sup>  |

| T= 77K                                         | <10 <sup>3</sup> | 8x10 <sup>9</sup>  | 5x10 <sup>6</sup> |

Table 3: Intrinsic concentration for different materials at 77K and 300K

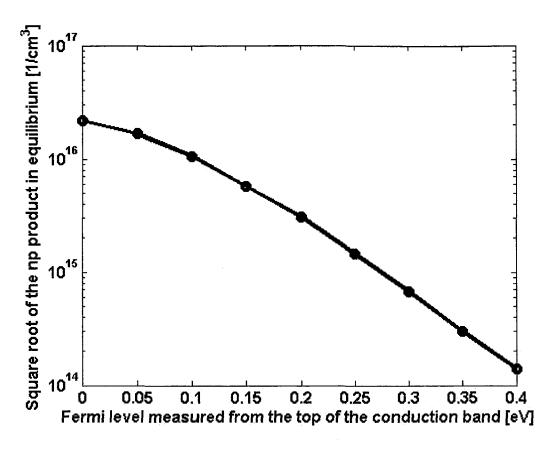

Such a high intrinsic concentration could potentially completely dominate any lowly doped InSb regions, thereby necessitating either expensive cooling techniques or carrier extraction-exclusion techniques, as described later in the section 5. Also, intrinsic concentration will appear explicitly in the computation of the Auger recombination-generation rate, so accurate treatment is necessary if the results for, e.g. leakage currents are to be accurate. Plot of the intrinsic concentration, or rather np product in equilibrium, is shown in the Fig. 7 below.

Figure 7: np product in equilibrium vs. Fermi level shows a large variation of two decades.

As can be seen, np product will vary over two decades for different Fermi levels. Doping varies from intrinsic on the left to about 10<sup>19</sup> cm<sup>-3</sup> on the right of the graph. Its accurate treatment in the Auger model is a must.

## 3.4 Mobility and velocity saturation

Intrinsic bulk mobility for InSb is reported to be around 7.8x10<sup>4</sup>cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [20], which is the largest value of all bulk semiconductors. As expected, the values are much reduced as doping is increased, but the value

does not fall below 4000 even at the highest doping. Intrinsic hole mobility is also relatively high at 800 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and falls to 150 for high doping.

In addition, InSb shows the highest electron saturation velocity, approaching  $5x10^7$  cm/s. Combined with very high mobility, it is expected that electron transport in InSb is extremely fast, enabling the design of very fast devices. Note that parasitic resistances in devices would benefit from very high mobilities, i.e. they would be much smaller than in other semiconductors. Parasitic resistances can dominate device performance in deeply scaled devices and this property is not always appreciated in discussions of MOSFET scaling in the literature.

Also, mobility in the channel will be reduced compared to its bulk value. This is due to the surface scattering, which is difficult to model even in silicon. Due to the lack of adequate measurements for InSb, we adjust mobility model for the vertical field dependence to achieve saturation velocity, as described later. However, in quantum mechanical regime, mobility will be increased since the peak of the electron concentration is moved away from the surface, which should reduce surface scattering [25].

In general, mobility data for InSb at 300K is lacking, especially universal mobility model which is widely used for silicon.

### 3.5 Auger recombination-generation and impact ionization

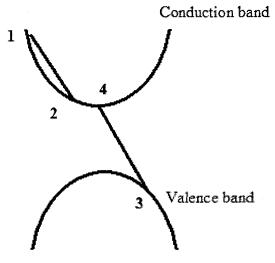

Leakage current in the InSb diodes is determined by Auger recombination/generation mechanism, in particular Auger-1 and Auger-7 processes [26]. It is a three particle process, where, for example, an electron recombines with a heavy hole releasing energy to another electron (recombination) or high-energy electron impact ionizes an electron-heavy hole pair (generation). Therefore, impact ionization is an inverse process of Auger recombination. Auger-1 is electron initiated process. Therefore it will be more pronounced in n-type material. Auger-7 process is initiated by a hole, making it dominant Auger process in p-type material. Auger processes are important for all low-bandgap materials where activation energy is low. For Auger-1 process, for example, activation energy is the energy required for an electron in valence band to jump to the available state in the conduction band. If the bandgap is small this energy will be small, so we expect leakage currents in these devices to be large. Illustration of the impact ionization is shown in the Fig 8. Electron in the position 1 will generate electron hole pair, denoted by transition from 3 to 4, and loose some energy going to the position 2.

Figure 8: Impact ionization; electron-hole pair is generated contributing to the leakage current in the reverse bias

There has been an effort in the literature to model impact ionization for III-V compounds. Cao and Lei developed formalism to calculate generation rate for GaN [27]. However, GaN has a large bandgap (3.5 eV). Wang and Lei investigated impact ionization for InSb within the framework of the balance equation [28]. These calculations were done at 77K and assuming parabolic bands. Non-parabolicity effects in the Auger generation have been only recently investigated [46, 47]. In our work, we adopt approach from Beattie and White [29]. They proposed following formula for the net recombination rate:

$$R = R_R \cdot \left(1 - e^{-\left(E_F + H_F + E_g\right)/kT}\right) \tag{22}$$

where  $R_R$  is recombination in the equilibrium, calculated as a function of the Fermi level  $E_F$  which is measured from the bottom of the conduction band and is positive upwards in E-k diagram and  $H_F$  is the hole Fermi level measured from the top of the valence band and is positive downwards. In equilibrium, electron and hole Fermi levels align, yielding zero net recombination, due to the exponential factor adding to zero. However, eq. (22) contains an exponential function which causes convergence problems. We were able to successfully implement it for diodes but full MOSFET simulation could not converge. Hence, we had to modify eq. (22) to enable application for InSb MOSFETs.

An alternative expression for Auger R-G is given by:

$$R = (C_n n + C_p p)(np - n_{ie}^2)$$

(23)

where  $C_n$  is Auger-1 coefficient and  $C_p$  is for Auger-7. While the value of  $C_p$  is constant with respect to doping and equal to  $5 \cdot 10^{-26} \text{cm}^{-6} \text{s}^{-1}$ ,  $C_n$  is strong function of electron concentration, due to high degeneracy and non-parabolicity. Plot of  $C_n$  dependence on doping is shown in the Fig. 9 below.

Figure 9: Auger coefficient  $C_n$  for electrons in InSb as a function of electron concentration. It is decreasing with increasing concentration due to effective enlargement of the bandgap

This behavior can be explained as follows: as Fermi level moves higher above the bottom of the conduction band there are more electrons available for Auger-1 process, but at the same time energy required to initiate it becomes larger. The latter effect dominates resulting in reduction of C<sub>n</sub> as shown in Fig. 9.

Total equilibrium recombination can be written as:

$$R_R = R_{A-1} + R_{A-7} + R_{SRH} (24)$$

Three terms indicate equilibrium recombination due to Auger-1, Auger-7 and Shockley–Reed–Hall process (SRH), respectively. Beattie and White evaluated equilibrium recombination for Auger-1 at four different temperatures: 294 K, 220 K, 150 K and 80 K. For temperatures between these points, we used linear interpolation. Auger recombination peaks at some value of E<sub>F</sub> above the bottom of the conduction band. It rapidly decreases as Fermi level increases above the peak value, due to strong degeneracy (increase in the activation energy). This is illustrated in the Fig. 10. As material becomes more p-type due to lack of electrons to initiate Auger-1, Auger process decreases.

Figure 10: Equilibrium Auger recombination and electron lifetime vs Fermi level: solid lines are from full band calculation, dashed from Beattie model in eq. 22 and 24. It reaches a maximum slightly above the bottom of the conduction band. Copyright by the American Institute of Physics

Equilibrium recombination rate for A-7 process is approximately 3 times smaller than for Auger-1 [30]. Therefore, in our implementation of the Auger-7 process we are simply using Auger-1 values divided by 3.

## 3.6 Shockley-Reed-Hall (SRH) recombination

Using the exclusion/extraction method described in the following section, Auger processes in the lowly doped  $\pi$  region are suppressed. Under such conditions SRH process becomes a comparable contributor to the overall generation-recombination at 300K. At lower temperatures SRH becomes the dominant process [29, 30, 31]. According to the measurements performed by Nott et al [31] on InSb/InAlSb diode, SRH coefficient in the  $\pi$  region is A=9.26x10<sup>6</sup> s<sup>-1</sup>. In our devices, this would result in the equilibrium recombination of R<sub>SRH</sub>=4.63x10<sup>22</sup> cm<sup>-3</sup>s<sup>-1</sup> according to  $R_{SRH} = N_T \cdot A$ , where N<sub>T</sub> is trap density. We assume N<sub>T</sub> to be equal to the doping i.e. N<sub>T</sub>≈10<sup>15</sup> cm<sup>-3</sup> Unfortunately, no measurements of the SRH coefficient for InSb for nonintrinsic conditions are available in the literature. However, it can be argued that they are not critcial since our MOSFET channel is close to intrinsic and in other regions of the device, Auger process dominates. Also, numbers presented for SRH recombination are somewhat arbitrary, since they depend on the processing and it is generally assumed to be related to how "clean" some process is. We have, therefore, decided to keep the SRH model simple and use a constant coefficient provided by Nott et al.

## 3.7 Band-to-Band tunneling

Due to narrow bandgap, even at the moderate doping of the p-n junction, one may expect substantial tunneling current. The band-to-band-tunneling (BTBT) is modeled as an R-G process, according to [32]:

$$R_{bbt} = -B|F|^{\sigma} D(F, E, E_{fn}, E_{fp}) \exp(-F_0/|F|)$$

(25)

where B and  $F_0$  are material dependent parameters, F is field,  $E_{fn}$  and  $E_{fp}$  are quasi-Fermi levels. Their values for InSb are determined according to Kane's model [33]. D is a function that accounts for the relative position of electron and hole Fermi levels in the neutral regions and the influence of perpendicular electron motion on tunneling probability. As will be shown below, BTBT has no influence on leakage current in InSb diodes.

All of the processes: Auger, SRH and BTBT are used in DESSIS but, as noted earlier, all recombination-generation mechanisms are turned off in nanoMOS. In the next section we discuss DESSIS implementation of the InSb electrical properties.

## 4. DESSIS Implementation

For simulation purposes, the DESSIS device simulator from ISE (now Synopsis) [18] was used. This software allows for custom material definition using at a minimum the following set of basic parameters (for drift-diffusion simulations):  $\varepsilon$  - the relative dielectric constant;  $E_g$  -the bandgap;  $\chi$  - the electron affinity, eDOS, - the electron density of states mass; hDOS - the hole density of states mass, and  $\mu$  - the carrier mobility. These parameters were obtained from [20].

$$E_g$$

= 0.17eV (at 300 K),

$\chi$  = 4.59 eV

hDOS = 0.43m<sub>0</sub>,

eDOS = 0.014m<sub>0</sub>

Calculation of density of states for electrons (DOS) in Dessis can be done in two ways:

- a) by defining a constant DOS, or

- b) by defining a density of states effective mass (mDOS), which is then used to calculate DOS.

Maxwell-Boltzmann (M-B) or Fermi-Dirac (F-D) statistics can be used in either case. If Fermi-Dirac statistics is used, only  $F_{1/2}$  integrals are calculated within DESSIS.

Given these options, the only way to implement eq. (13) is by utilizing approach b) and making the mDOS a function of doping, where its value is adjusted empirically to give the appropriate Fermi level for a given doping. This was implemented using C++ "pmi" subroutine. Results shown in Fig. 5 agree with those in [34].

Since heavy hole band is parabolic, no special treatment is needed in DESSIS, i.e. hole concentration is calculated through the standard Fermi-Dirac statistics formula.

Basic set of parameters for mobility model was obtained mostly from Levinshtein [20] and implemented as custom material. In DESSIS, we use Arora model [35, 36] for doping-dependent degradation:

$$\mu_{DOP} = \mu_{MIN} + \frac{\mu_{D}}{1 + \left(\frac{N_{i}}{N_{0}}\right)^{A^{*}}}$$

(26)

, where

$$\mu_{MIN} = A_{MIN} \cdot \left(\frac{T}{T_0}\right)^{\alpha_m} \qquad \mu_D = A_D \cdot \left(\frac{T}{T_0}\right)^{\alpha_D}$$

$$N_0 = A_N \cdot \left(\frac{T}{T_0}\right)^{\alpha_N} \qquad A^* = A_A \cdot \left(\frac{T}{T_0}\right)^{\alpha_a}$$

(27)

Individual parameters for InSb are given in the Table 4 and  $N_{\rm i}$  is doping concentration:

|          | N                    | р                  | Units                |

|----------|----------------------|--------------------|----------------------|

| Ar_mumin | 3x10 <sup>3</sup>    | 200                | cm <sup>2</sup> /V/s |

| Ar_alm   | 0                    | 0                  | 1                    |

| Ar_mud   | 7.4x10 <sup>4</sup>  | 500                | cm <sup>2</sup> /V/s |

| Ar_ald   | -1.538               | -2.108             | 1                    |

| Ar_N0    | 2.7x10 <sup>17</sup> | 7x10 <sup>17</sup> | cm <sup>-3</sup>     |

| Ar_alN   | 5                    | 3.45               | 1                    |

| Ar_a     | 0.9187               | 0.521              | 1                    |

| Ar_ala   | 1.1061               | 0.1077             | 1                    |

Table 4: Arora mobility model parameters

To model velocity saturation we turn on model 1 in DESSIS [18] which is based on the Canali model [36]:

$$\mu(F) = \frac{\mu_{low}}{\left[1 + \left(\frac{\mu_{low}F}{v_{sat}}\right)^{\beta}\right]^{\frac{1}{\beta}}}$$

(28)

where  $v_{sat} = 5 \times 10^7 cm$  /s is saturation velocity, mu\_low is low field mobility obtained from the Arora model described above,  $\beta=2$  and F is longitudinal electric field.

Due to the strong transverse electric field in the channel, there is an interaction between electrons and InSb-insulator boundary. In DESSIS, this effect is implemented using Lombardi model. Parameters are obtained by optimization to achieve proper velocity profile in the channel, i.e. most of the channel

achieves velocity saturation. Reduction of mobility was, in relative terms, the same as for Si . Furthermore, in our simulations of the reference device the maximum transconductance g<sub>m</sub> was around 125 mS/mm, which is very close to experimental data of 120 mS/mm [6], indicating a reasonable fit of our mobility model. Further model refinement and verification is not possible without more experimental data. Parameters for the Lombardi model are given in Table 5:

|                | n                     | р                     | Units                               |

|----------------|-----------------------|-----------------------|-------------------------------------|

| В              | 2.78x10 <sup>8</sup>  | 4.93x10 <sup>7</sup>  | cm/s                                |

| С              | 8.8x10 <sup>4</sup>   | 8.95x10 <sup>5</sup>  | cm <sup>5/3</sup> sV <sup>2/3</sup> |

| N <sub>0</sub> | 1                     | 1                     | cm <sup>-3</sup>                    |

| λ              | 0.125                 | 0.0317                | 1                                   |

| k              | 1                     | 1                     | 1                                   |

| δ              | 5.82x10 <sup>15</sup> | 2.05x10 <sup>15</sup> | V/s                                 |

| Α              | 2                     | 2                     | 1                                   |

| α              | 0                     | 0                     | 1                                   |

| N <sub>1</sub> | 1                     | 1                     | cm <sup>-3</sup>                    |

| V              | 1                     | 1                     | 1                                   |

| η              | 5.82x10 <sup>32</sup> | 2.05x10 <sup>32</sup> | V <sup>2</sup> /cm s                |

| I_crit         | 1x10 <sup>-6</sup>    | 1x10 <sup>-6</sup>    | cm/s                                |

Table 5: Lombardi model parameters for InSb

Dependence on the vertical field is given in the Fig. 11, to illustrate that mobility can be dramatically reduced by vertical field. In our device, fields can be in excess of  $10^6$  V/cm.

Figure 11: Mobility vs. vertical field plot shows rapid decrease in electron mobility with the vertical field

### 5. InSb diodes and exclusion/extraction mechanism

Exclusion/extraction principle is a design approach to overcome the high intrinsic concentration of InSb at room temperature and the corresponding leakage currents. High leakage current would reduce I<sub>on</sub>/I<sub>off</sub> ratio, rendering the device useless since the off state power would be prohibitively high. In a MOSFET design this approach is utilized to reduce the leakage coming from source-body and drain-body junctions.

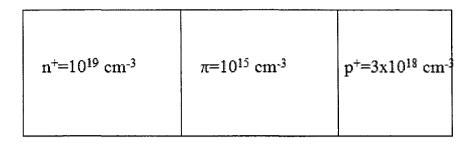

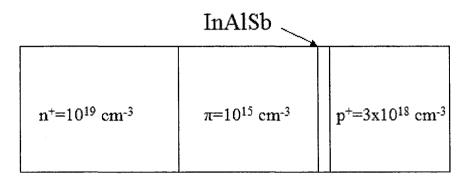

The drift diffusion models described here were used to examine the possibilities of InSb p-i-n diodes operating at room temperature. The devices were first published by Ashley, et. al. [37]. The extraction  $(n^+-\pi-p^+)$  and exclusion/extraction  $(n^+-\pi-p^+-p^+)$  diodes are two different strategies to overcome the high intrinsic concentration of InSb at room temperature and the corresponding leakage currents. Cross sections of both diodes are given in the Fig. 12. Following is a brief description of how these devices operate.

Figure 12: Extraction (top) and exclusion/extraction (bottom) diode cross section

### 5.1 Extraction Diode

The extraction diode is the simpler of the two and it consists of a heavily doped  $n^+$  layer, followed by a very lowly doped p layer (the  $\pi$  region) and a heavily doped  $p^+$  region yielding an  $n^+$ - $\pi$ - $p^+$  structure. Due to the extreme degeneracy in heavily doped n-type InSb, the Fermi level moves high into the conduction band so that  $E_F$ - $E_V$  =( $E_F$  –  $E_c$ ) +  $E_F$  is 2-3 times larger than the bandgap (see Fig. 5). This large difference drives the concentration of minority holes to very low levels in the  $n^+$  region. As a result, intrinsic concentration  $n_{ie}$

(or, more accurately, np product in equilibrium) is much reduced in highly doped  $n^+$  region. For reverse bias, generation in  $n^+$  region which happens close to the depletion layer depends on  $n_{ie}^2$  (see eq. (23)) and is thus reduced by several orders of magnitude.

Figure 13: Electron and hole concentrations for extraction and extraction/exclusion diodes under reverse bias V=-0.35 V

Degeneracy exists in  $p^+$  InSb material too, but to a much lesser extent than in n-type material. Due to the high density of states in the heavy hole band, degeneracy is not capable of reducing  $n_i$  below its "normal" value for intrinsic material because  $E_F$ - $E_v \approx E_g$ . In reverse bias there still exists a significant electron concentration that normally diffuses into the  $\pi$  region contributing to the leakage current (see Fig. 13). The minority concentration has an exponential "tail" (long diode case) that extends into neutral  $p^+$  layer and eventually reaches the equilibrium value inside it, some distance away from the depletion layer. Inside this transition layer np- $n_{ie}^-$ 2 term goes from being dominated by  $n_{ie}^-$ 2 (large generation) to zero (i.e. recombination = generation). Therefore, the total current has contributions from diffusion of electrons as well as from generation inside the  $p^+$  region resulting in large leakage currents. Overall effect of the extraction mechanism on the leakage current will be presented in section 6.

# 5.2 Exclusion/extraction Diode

In order to prevent electrons from entering the  $\pi$  region, a thin region of a wide bandgap material,  $p^+$ , is placed between the  $p^+$  and  $\pi$  regions resulting in a n+- $\pi$ -p+-p+ diode. It needs to be thick enough to prevent tunneling through the barrier and high enough to prevent injection over the barrier, but it cannot be too thick because of the lattice-mismatch strain. A layer of InAlSb with ~10 nanometers thickness was used in [37] and in our simulations. The

bandgap offset is assumed to show up almost entirely in the conduction band.

The p<sup>+</sup> region now acts as an "exclusion" layer (or contact), so the diode is called "exclusion/extraction" diode.

Figure 14: Band diagrams for  $n^+ - \pi - p^+ - p^+$  exclusion/extraction diode in equilibrium

Fig. 14 show equilibrium band diagrams for  $n^+-\pi-p^+-p^+$  diode. Notice the spike in the conduction band corresponding to the insertion of the InAlSb material.

$n^+$ - $\pi$ - $p^+$  diode diagrams look very similar, except for the absence of the spike. This spike effectively prevents any injection of minority electrons into  $p^+$  region. Also note the high degeneracy in the  $n^+$  region on the left.

Final illustration of our explanation of operation of these two diodes, is shown in Fig. 15 where the net generation rate is shown. In extraction diode there is a long tail of generation extending into  $p^+$  region, while exclusion/extraction diode has a very narrow region where generation occurs. This peak occurs precisely at the  $\pi$ - $p^+$  interface and it is bigger for the extraction diode since there is no wide gap layer to prevent injection of the electrons from  $p^+$  region. Clearly, Auger generation has a very large effect on leakage current of extraction diode, but much smaller one on exclusion/extraction diode.

Figure 15: Auger generation in  $n^+$ –p– $p^+$  and  $n^+$ - $\pi$ - $p^+$ - $p^+$  diodes under reverse bias. Exclusion/extraction diode has reduced generation by more than a decade in  $p^+$  region close to p-n junction.

#### 6. Diode simulations and results

In order to validate our models and verify exclusion/extraction mechanism, we first constructed and simulated two InSb diodes, as described above. Simulation results for electron and hole densities in each region of these devices are shown in Fig. 13 and we observed the following:

- a) the difference in electron concentrations inside the  $\pi$  region and

- b) sharp, step-like, increase of n for  $n^+$   $\pi$ - $\underline{p}^+$ - $p^+$  diode vs. exponential increase for  $n^+$ - $\pi$ - $p^+$  diode inside the  $p^+$  region.

In the following sections we discuss how this affects terminal behavior of diodes.

### 6.1 I-V characteristics

Additional diode I-V simulations were performed to determine the effectiveness of suppression of diffusion current and Auger generation in InSb exclusion/extraction and extraction diodes. One can see in Fig. 16 that the leakage current in the exclusion/extraction diode is more than an order of magnitude smaller than the simpler extraction diode. This is the region on the left of the plot, and since in our MOSFET device body will always be reversely biased, forward bias results can be ignored, but are shown for completeness.

Figure 16: Leakage currents in  $n^+$  -  $\pi$  -  $p^+$  -  $p^+$  (exclusion/extraction) and  $n^+$ - $\pi$ -  $p^+$  (extraction) diodes show improvements in the reverse bias by addition of thin InAISb layer

### 6.2 Differential resistance

Another commonly used method that allows us to evaluate the effectiveness of carrier extraction/exclusion is to calculate the zero bias differential resistance  $R_0$ . To accomplish this, a diode voltage is swept from negative to positive and the slope of the curve at 0 V bias is measured. This

measurement is commonly used in photodiodes to compare sensitivity.

Higher resistivity results in higher detector sensitivities, *i.e.*, for a given number of electron hole pairs, more voltage is generated in the detector.

An analytical expression for  $R_0A$ , where A is cross sectional area of the diode, can be obtained starting with the diode current equation

$$I=I_0(\exp(V/V_T)-1) \tag{29}$$

If the derivative of the above expression is taken with respect to V one finds:

$$\frac{dI}{dV} = \frac{I_0}{V_T} \exp(\frac{V}{V_T}) = \frac{I_0}{V_T} [\exp(\frac{V}{V_T}) - 1] + \frac{I_0}{V_T} = \frac{I}{V_T} + \frac{I_0}{V_T}$$

(30)

When V=0, I=0, and the expression for differential conductance reduces to:

$$\frac{dI}{dV} = \frac{I_0}{V_T} = \frac{I_0}{kT/q} \tag{31}$$

The inverse of differential conductance is the differential resistance,  $R_0$  . so that

$$R_0 A = \frac{kT/q}{I_0} A \tag{32}$$

Figure 17: Differential Resistance: simulation vs. measured data for extraction diode (labeled "InSb") and exclusion/extraction diode (labeled "InAlSb"). Extraction diode shows relatively good fit with the measured data.

From eq. (32) it is clear that  $R_0A$  is temperature dependent: explicitly thorough T and implicitly through  $I_0$ . Since main contributor to the leakage current is Auger generation, which is strongly dependent on temperature,  $R_0A$  will depend on T through it. If we plot  $R_0A$  as a function of inverse temperature, we

can see the difference in resistivities of the different types of diodes. We note that this difference is fundamentally due to the difference in leakage currents of these diodes, which in turn is related to the differing levels of effectiveness of the extraction/exclusion mechanisms. By measuring the slope of the  $I_d$  vs.  $V_d$  curve at the 0V Fig. 17 is obtained that matches well with published data [37].