#### **Utah State University**

### DigitalCommons@USU

All Graduate Theses and Dissertations

**Graduate Studies**

12-2022

### Modeling and Control of Battery Management Systems with High-Frequency AC Link Coupled Multiport Series Resonant Converters for 2nd Life Battery Applications

Brooks Jace Maughan Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Maughan, Brooks Jace, "Modeling and Control of Battery Management Systems with High-Frequency AC Link Coupled Multiport Series Resonant Converters for 2nd Life Battery Applications" (2022). All Graduate Theses and Dissertations. 8644.

https://digitalcommons.usu.edu/etd/8644

This Thesis is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

# MODELING AND CONTROL OF BATTERY MANAGEMENT SYSTEMS WITH HIGH-FREQUENCY AC LINK COUPLED MULTIPORT SERIES RESONANT CONVERTERS FOR 2ND LIFE BATTERY APPLICATIONS

by

Brooks Jace Maughan

A thesis submitted in partial fulfillment of the requirements for the degree

of

MASTER OF SCIENCE

in

Electrical Engineering

| Approved:                             |                                                           |  |

|---------------------------------------|-----------------------------------------------------------|--|

| Hongjie Wang, Ph.D.                   | Regan Zane, Ph.D.                                         |  |

| Major Professor                       | Committee Member                                          |  |

| Donald Cripps, Ph.D. Committee Member | D. Richard Cutler, Ph.D. Vice Provost of Graduate Studies |  |

$\begin{array}{c} \text{UTAH STATE UNIVERSITY} \\ \text{Logan, Utah} \end{array}$

Copyright  $\bigcirc$  Brooks Jace Maughan 2022

All Rights Reserved

#### ABSTRACT

MODELING AND CONTROL OF BATTERY MANAGEMENT SYSTEMS WITH HIGH-FREQUENCY AC LINK COUPLED MULTIPORT SERIES RESONANT CONVERTERS FOR 2ND LIFE BATTERY APPLICATIONS

by

Brooks Jace Maughan, Master of Science Utah State University, 2022

Major Professor: Hongjie Wang, Ph.D.

Department: Electrical and Computer Engineering

With the emerging solutions of Active Cell Balancing to enable second life use for Battery Management Systems, there is a need for large systems that can recycle large amounts of batteries. At Utah State University, a system has been designed and tested to enable up to 8 cells to be recycled using active cell balancing but has not been tested with larger amounts of battery cells. This project entails the design, production, and testing of a larger system up to 96 cells that would all be balanced to similar State of Health (SOH). This is done efficiently using calculated ratings and safety limits and permits the hot swapping, replacement, of a battery cell including disconnection preceding the replacement of a particular cell while the system is still running, of any module in the system.

(151 pages)

#### PUBLIC ABSTRACT

## MODELING AND CONTROL OF BATTERY MANAGEMENT SYSTEMS WITH HIGH-FREQUENCY AC LINK COUPLED MULTIPORT SERIES RESONANT CONVERTERS FOR 2ND LIFE BATTERY APPLICATIONS

#### Brooks Jace Maughan

While the use and production of Electric Vehicles becomes more prevalent, it is also important to make this economical and ensure the reduction of a carbon footprint. Second-life batteries can satisfy both problems as batteries can be used in a second-life application for lower power purposes such as supplementing the grid so the infrastructure needed to charge the expanding fleet of Electric Vehicles can be easily supplied. This thesis goes through the process of Active Cell Balancing which will produce equal capacities, or similar batteries, that can be more efficiently used in these and other types of second-life applications. The process is expanded through series connection of the converters and modules of batteries so the process can be used for up to 96 Nissan Cells at a time. This project at Utah State University will also entail the removal and replacement of these Nissan battery cells while running to ensure quick but smooth balancing of hundreds of batteries.

To my wife and family.

#### ACKNOWLEDGMENTS

I would like to express my appreciation to the professors and coworkers at ASPIRE that have helped me throughout my thesis work and contributed to my learning. The experience and accumulation of knowledge throughout my time at ASPIRE has gotten me to the point where I am now and I am a better engineer because of it.

Brooks J. Maughan

#### CONTENTS

|     | I                                                                                                                                                                                                                                                                                                                                     | Page                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| AE  | BSTRACT                                                                                                                                                                                                                                                                                                                               | . iii                                  |

| PU  | JBLIC ABSTRACT                                                                                                                                                                                                                                                                                                                        | . iv                                   |

| AC  | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                        | . vi                                   |

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                                                         | . ix                                   |

| AC  | CRONYMS                                                                                                                                                                                                                                                                                                                               | . xiii                                 |

| 1   | INTRODUCTION                                                                                                                                                                                                                                                                                                                          |                                        |

| 2   | BACKGROUND AND LITERATURE REVIEW  2.1 Battery Management Systems  2.2 Second-Life Applications of Battery Cells  2.3 Active Cell Balancing of Battery Management Systems  2.4 Phasor Transformation of Series Resonant Converters  2.5 Voltage Sharing of Output Series Connected Converters  2.6 Hot Swapping  2.7 Proposed Approach | . 3<br>3<br>4<br>5<br>7<br>7<br>10     |

| 3   | BATTERY CELL RECYCLING FOR SECOND LIFE APPLICATION                                                                                                                                                                                                                                                                                    | . 12<br>12<br>21<br>26<br>30           |

| 4   | MATHEMATICAL ANALYSIS AND DESIGN  4.1 Series Resonant Converters  4.2 Control Board Design  4.3 Boards Layout  4.4 Control Loop Analysis  4.4.1 SOC Estimation  4.4.2 Differential Current  4.4.3 Droop Control for Voltage Sharing                                                                                                   | 31<br>32<br>35<br>40<br>41<br>42<br>42 |

| 5   | TESTING AND RESULTS                                                                                                                                                                                                                                                                                                                   | 45<br>45<br>45<br>46                   |

|    |      |                                                        | viii |

|----|------|--------------------------------------------------------|------|

|    | 5.2  | Converter Unit Testing                                 | 49   |

|    |      | 5.2.1 Open Loop Control                                | 49   |

|    |      | 5.2.2 Closed Loop Control                              | 50   |

|    |      | 5.2.3 Differential Current Control Loop                | 53   |

|    | 5.3  | Module Testing                                         | 55   |

|    | 5.4  | String Testing                                         | 58   |

| 6  | НОТ  | Γ SWAPPING PROCESS AND ANALYSIS                        | 61   |

|    | 6.1  | Introduction                                           | 62   |

|    | 6.2  | Theoretical Approach, Simulation, and Hardware Results | 63   |

|    | 6.3  | Conclusion                                             | 69   |

| 7  |      | NCLUSION                                               | 70   |

|    | 7.1  | Completed Work                                         | 70   |

| RI | EFER | ENCES                                                  | 71   |

| AI | PPEN | DICES                                                  | 74   |

|    | A    | MicroController Module Control Code                    | 75   |

#### LIST OF FIGURES

| Fig | ure  |                                                                                        | Page |

|-----|------|----------------------------------------------------------------------------------------|------|

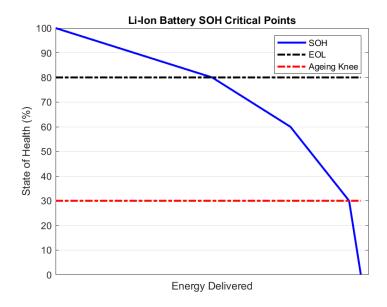

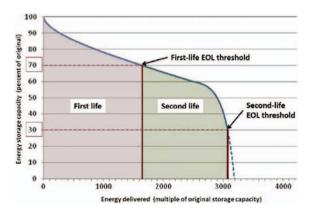

|     | 1.1  | State of Health curve over a period of time and energy provided                        | 2    |

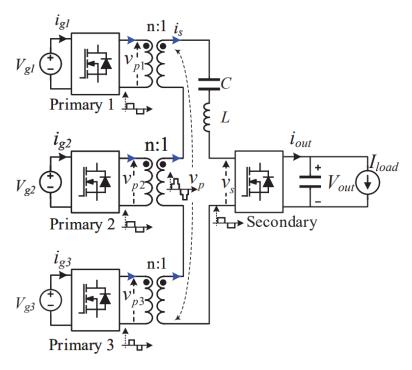

|     | 2.1  | Three-port power transfer using one series-connected secondary transformer             | 4    |

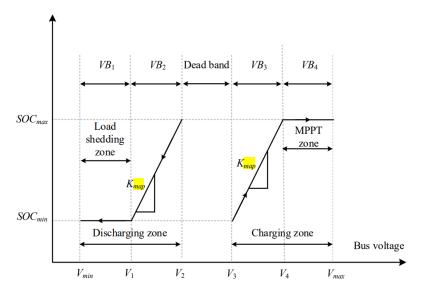

|     | 2.2  | Voltage mapping for active cell balancing                                              | 6    |

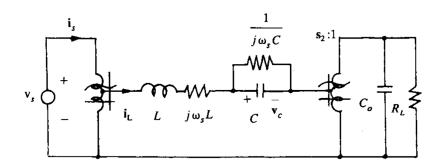

|     | 2.3  | Series Resonant Converter equivalent circuit input-output                              | 7    |

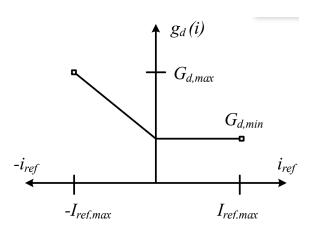

|     | 2.4  | Droop slope needed for voltage sharing                                                 | 8    |

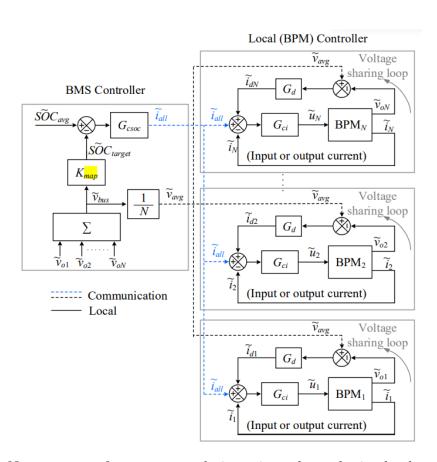

|     | 2.5  | N-port system for current regulation using voltage sharing by droop control            | 9    |

|     | 3.1  | Lithium-Ion battery recycled life-cycles for power smoothing of power plants           | 13   |

|     | 3.2  | Lithium-Ion battery SOH curve                                                          | 14   |

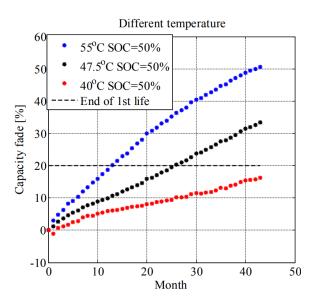

|     | 3.3  | SOH and capacity fade depending on temperature                                         | 14   |

|     | 3.4  | Resistive and capacitive fade of Li-Ion batteries throughout second life $ . $ .       | 15   |

|     | 3.5  | Equivalent circuit of a Li-Ion battery                                                 | 15   |

|     | 3.6  | Open Circuit Voltage curve at varying SOH                                              | 16   |

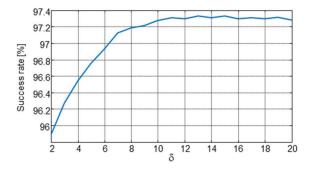

|     | 3.7  | RUL Estimation success rate                                                            | 16   |

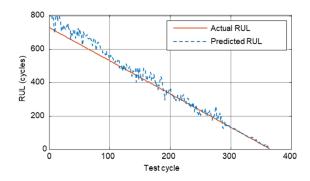

|     | 3.8  | RUL Estimation compare to actual RUL                                                   | 17   |

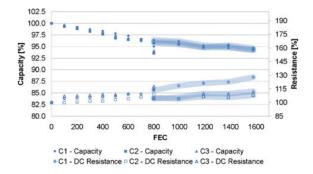

|     | 3.9  | Degradation of a homogeneous collection of Li-Ion cells                                | 17   |

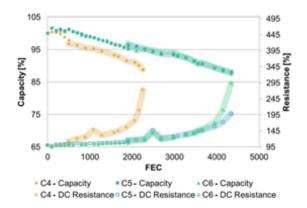

|     | 3.10 | Degradation of a heterogeneous collection of Li-Ion cells                              | 18   |

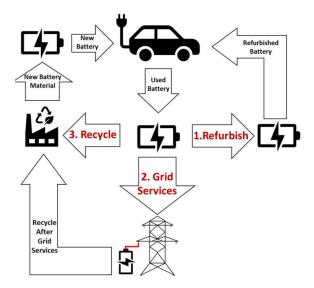

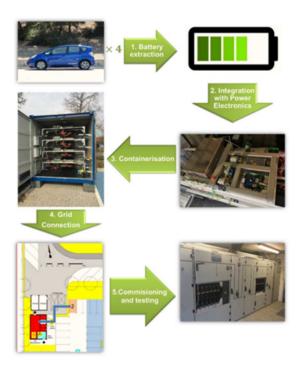

|     | 3.11 | Lifecycle of EV battery to grid supplemental battery                                   | 19   |

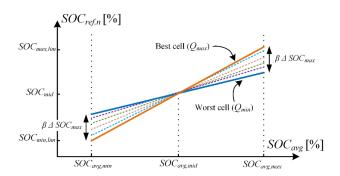

|     | 3.12 | Active Cell Balancing charge and discharge cycles depending on best/worst cells of BMS | 20   |

|     | 3.13 | Nissan Cell Characteristics from Datasheet                                             | 21   |

|     | 3 14 | Arbin Cycler Instrument for Battery Cycling                                            | 24   |

| 3.15 | Lithium-Ion Full Order Cell Model                                                                                                                         | 24 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

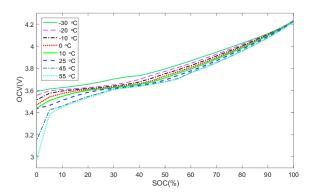

| 3.16 | OCV Curve developed through various temperatures [1]                                                                                                      | 25 |

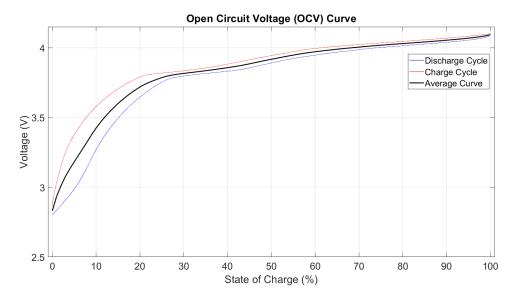

| 3.17 | OCV Curve developed through various capacities [2]                                                                                                        | 25 |

| 3.18 | Open Circuit Voltage Curve of a 2nd-life Nissan Cell developed by Arbin Cycler                                                                            | 25 |

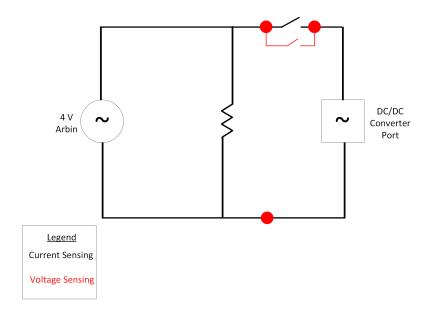

| 3.19 | Circuit design for isolation from Arbin to system at startup                                                                                              | 26 |

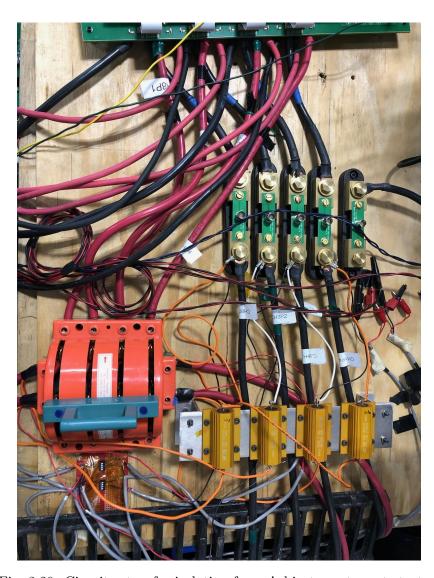

| 3.20 | Circuit setup for isolation from Arbin to system at startup                                                                                               | 27 |

| 3.21 | Lithium-Ion Battery Reconditioning Objective Map                                                                                                          | 29 |

| 3.22 | Active Cell balancing charge and discharge waveforms using POC concept .                                                                                  | 29 |

| 3.23 | Objective Map calibration for Nissan Cell chemistry                                                                                                       | 30 |

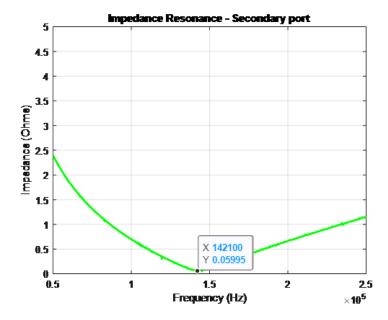

| 4.1  | Frequency plot of the impedance frequency sweep portraying the resonant frequency peak of the system                                                      | 32 |

| 4.2  | LCR meter readings of a frequency sweep indicating the inductance of the secondary                                                                        | 33 |

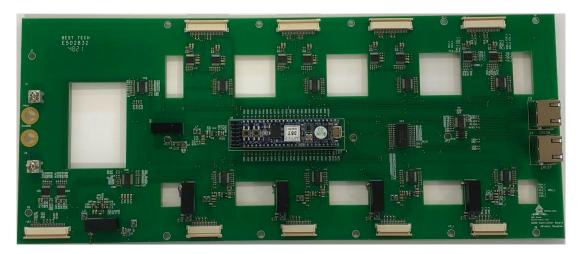

| 4.3  | Final design of control board for FPGA communication                                                                                                      | 34 |

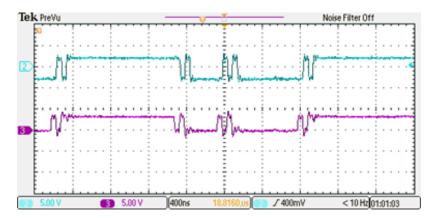

| 4.4  | ADC signals being delayed by one clock cycle with the new ADCs                                                                                            | 34 |

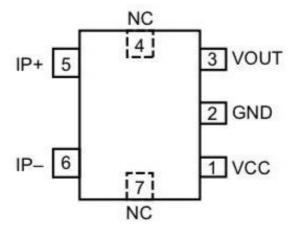

| 4.5  | Pin-out of the previous and new current sensor's provided by manufacturer                                                                                 | 35 |

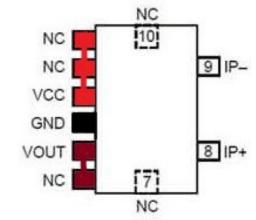

| 4.6  | Pin-out and workaround of the new current sensors sent by mistake                                                                                         | 35 |

| 4.7  | Simple Block Diagram portraying the Boards layout                                                                                                         | 36 |

| 4.8  | Signals being communicated between each of the four boards. (Signals from the String Controller are coming from a Site Controller controlled by the user) | 37 |

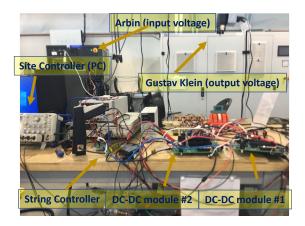

| 4.9  | POC setup for verification of string to module to converter unit communication                                                                            | 39 |

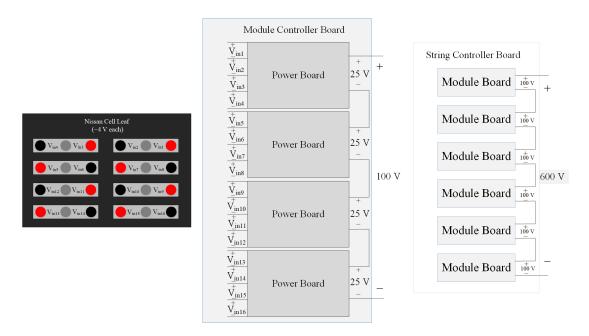

| 4.10 | Block Diagram portraying voltage ratings of the system for each unit                                                                                      | 39 |

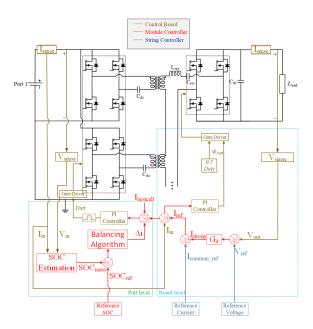

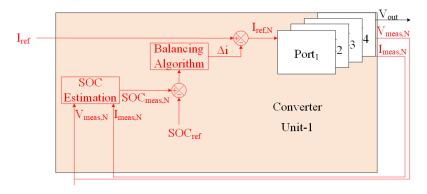

| 4.11 | Software diagram for the control of the Series Resonant Converter's of the system through String, Module, and FPGA Controllers                            | 40 |

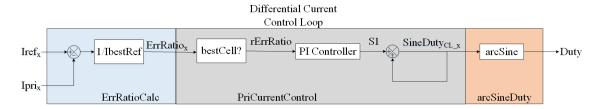

| 4.12 | Differential Current Control Loop based on Active Cell Balancing Algorithm                                                                                | 41 |

| 4.13 | Software diagram for the differential control of ports within FPGA                                                                                        | 42 |

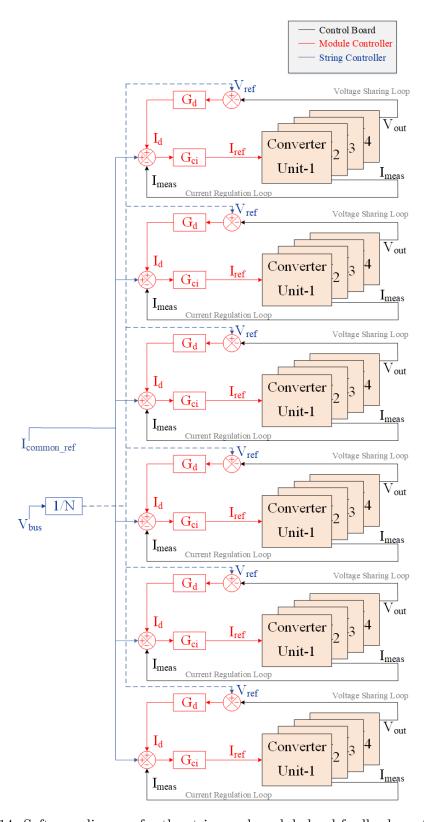

| 4.14 | Software diagram for the string and module level feedback controllers               | 44 |

|------|-------------------------------------------------------------------------------------|----|

| 5.1  | Test supplies and setup for board calibration                                       | 45 |

| 5.2  | Small level diagram of an H-bridge for DC/AC voltage conversion $\ \ldots \ \ldots$ | 46 |

| 5.3  | Analog to Digital Conversion tables for each current sensor - one board only        | 47 |

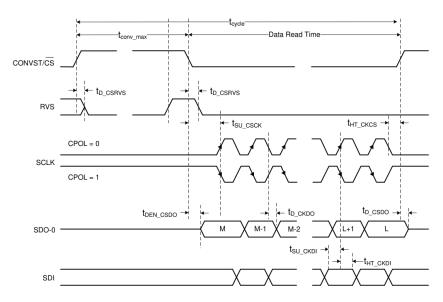

| 5.4  | Timing Diagram of the SDI line used for Range Selection of the ADC $$               | 48 |

| 5.5  | SDI message being sent from FPGA to ADC                                             | 48 |

| 5.6  | Test Setup for Converter Unit functionality verification                            | 49 |

| 5.7  | Software Diagram of Open Loop Control Testing (Phase Shift only)                    | 50 |

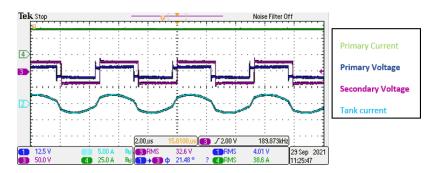

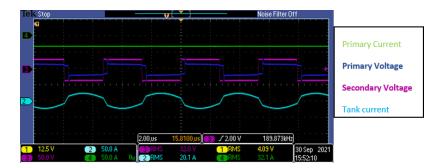

| 5.8  | Open Loop Control Waveform of 0 degree phase shift                                  | 51 |

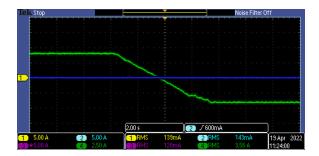

| 5.9  | Open Loop Control Waveform of -4 degree phase shift                                 | 51 |

| 5.10 | Software Diagram of Closed Loop Control Testing (Reference Current command only)    | 51 |

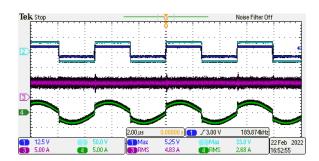

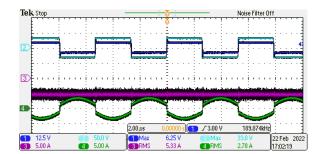

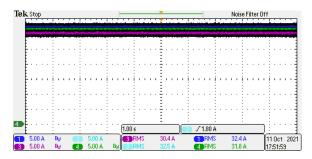

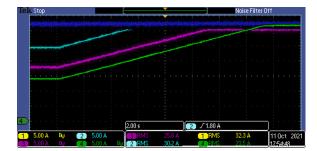

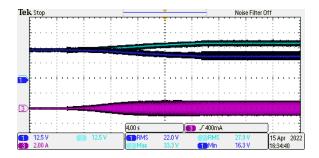

| 5.11 | Current Regulated Control Waveform. $I_{ref}$ =40A, $P_{out}$ =612W                 | 52 |

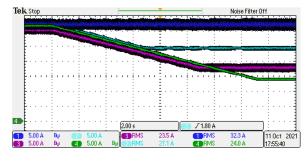

| 5.12 | Current Regulated Control Waveform. $I_{ref}$ =-32A, $P_{out}$ =-509W               | 52 |

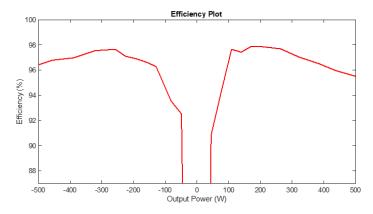

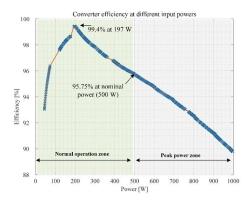

| 5.13 | Closed-loop operation efficiency curve of 100 kW system                             | 53 |

| 5.14 | Closed-loop operation efficiency curve of POC system                                | 53 |

| 5.15 | Software Diagram of Differential Current Testing                                    | 54 |

| 5.16 | Differential Current Operation using same Iref                                      | 54 |

| 5.17 | Differential Current ramping using differential current                             | 54 |

| 5.18 | Differential Current Operation using differential current                           | 54 |

| 5.19 | Differential Current ramping to same Iref                                           | 54 |

| 5.20 | Differential Control ramping from peak currents of -20 A to 20 A to -20 A .         | 55 |

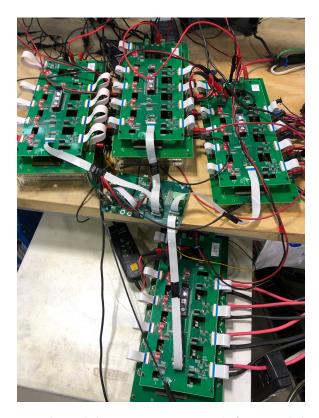

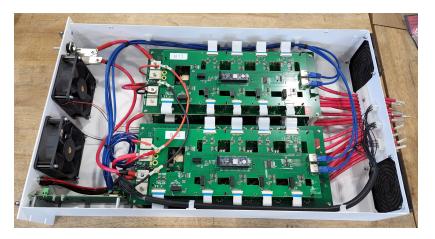

| 5.21 | Initial Module Testing setup with four modules in series                            | 56 |

| 5.22 | LED waveform indicating synchronous startup of two of the converters                | 57 |

| 5.23 | 2 SRC Converters starting up with no resistive load                                 | 57 |

| 5.24 | 2 SRC Converters in series with a 50 V resistive load ramping to open loop (no current feedback) performance | 57 |

|------|--------------------------------------------------------------------------------------------------------------|----|

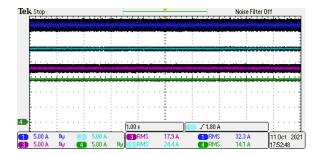

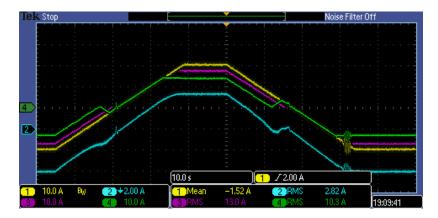

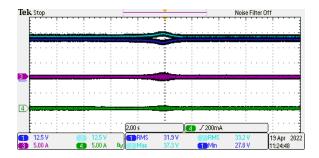

| 5.25 | Reference Current regulated with Droop Control for Voltage Sharing                                           | 58 |

| 5.26 | Droop Control from positive to negative current                                                              | 59 |

| 5.27 | Droop control stability transitioning from positive to negative current                                      | 59 |

| 5.28 | Module Enclosure for testing of 4 SRC converters in series                                                   | 59 |

| 5.29 | Module Connection to Nissan Cells                                                                            | 59 |

| 5.30 | Full string consisting of 6 modules and 6 Nissan Cell tubs                                                   | 60 |

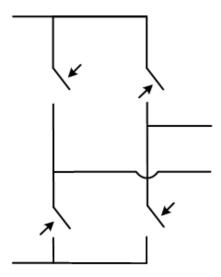

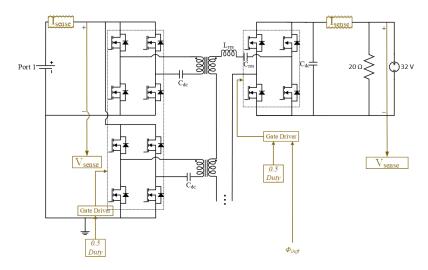

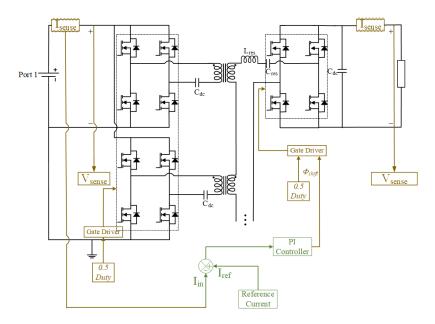

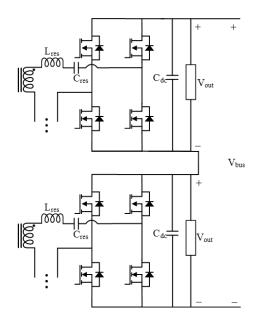

| 6.1  | Series-connected output in a module                                                                          | 63 |

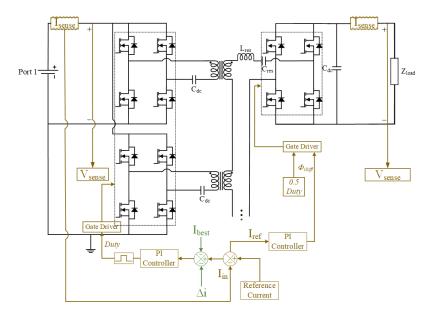

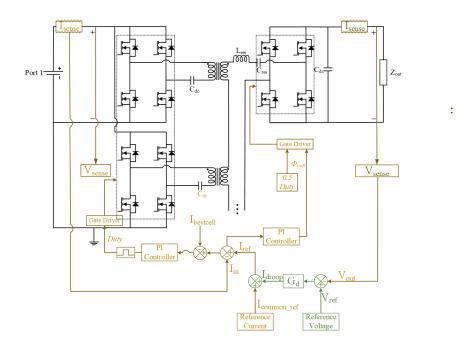

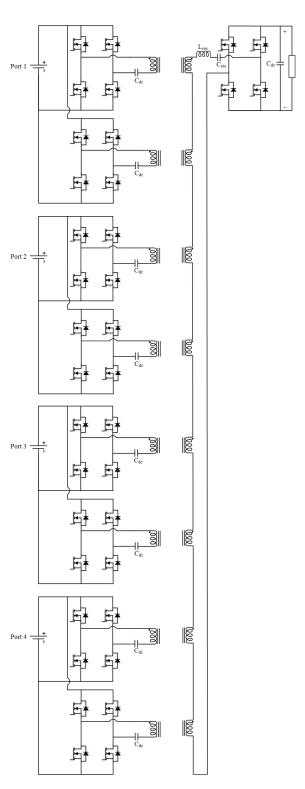

| 6.2  | Power converter architecture for 4-port Series Resonant Converter                                            | 65 |

| 6.3  | Power converter architecture for 4-port Series Resonant Converter                                            | 66 |

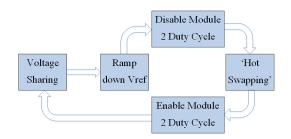

| 6.4  | Block Diagram modelling the process needed to perform Hot Swapping during full operation successfully        | 66 |

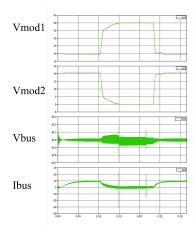

| 6.5  | Simulation waveform of Module and Bus voltage during hot-swapping                                            | 67 |

| 6.6  | Simulation waveform of Output and Tank current during hot-swapping                                           | 67 |

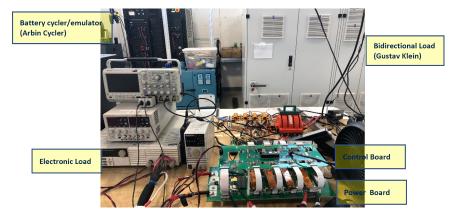

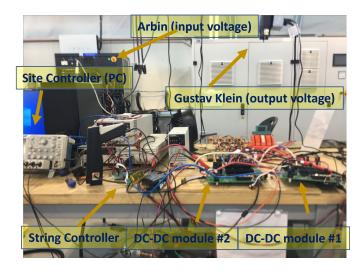

| 6.7  | Test Setup used for Hot Swapping of Scaled-down Prototype                                                    | 68 |

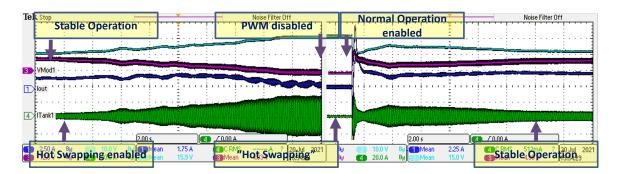

| 6.8  | Hardware Test of Scaled-down Prototype validating Hot Swapping Strategy                                      | 68 |

#### ACRONYMS

SRC Series Resonant Converters

BMS Battery Management Systems

SOH State of Health (in regard to BMS)

HF High Frequency

SOC State of Charge (in regard to BMS)

ACB Active Cell Balancing

AC Alternating Current

DC/DC Direct Current (in reference to Power Converters)

CV Constant Voltage

PCB Printed Circuit Boards

EOL End of Life

BESS Battery Energy Storage System

SPI Serial Peripheral Interface

MISO Master In Slave Out

EV Electric Vehicle

POC Proof of Concept

OCV Open Circuit Voltage

ZVS Zero Voltage Switching

IC Integrated Circuit

PI Proportional-Integrated (in reference to feedback controllers)

ADC Analog-to-Digital

CAN Controller Area Network

PWM Pulse Width Modulation

FPGA Field Programmable Gate Array

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Second Life Battery Applications of Lithium-Ion Batteries

Lithium Ion batteries are becoming more prevalent due to the expansion in vehicle electrification across all fronts. These batteries are extremely efficient and can maintain charge for years without degradation of the battery State of Health (SOH) or State of Charge (SOC). Electric Vehicles (EV) commonly use these types of batteries for their efficient characteristics and impressive chemistry. The degradation of a battery is an important question that has been analyzed and discussed in literature aplenty [3]. Electric Vehicles however only use the first 20% of the battery life-cycle which is then discarded for later use.

This thesis focuses on preparation of Li-Ion Batteries for Second Life Applications. This second life can best be defined by the State of Health after First-Life EV use, also known as the End-of-Life (EOL) stage, and before the battery degrades rapidly around 30% SOH, also known as the ageing knee. An example of a Lithium-Ion battery SOH curve with these critical points is represented in Figure 1.1. Second-Life Applications are typically much lower power density needs with lower C-rates (Current-rates), especially when compared to First-life. Many of these applications have to do with series connections of these Battery Systems used for grid supplement and protection, or for storage directly from the grid or an alternative power source. These series connections are best suited and last longer when the battery pack is homogeneous in State of Heath with the other batteries connected in the system. Thus the need for balanced batteries which can be best prepared using Active Cell Balancing techniques discussed in this thesis.

Fig. 1.1: State of Health curve over a period of time and energy provided

#### 1.2 Active Cell Balancing with a High Frequency Link Transformer

Cell balancing techniques can be done either passively or actively. Passive Cell balancing consists of various types of algorithms which use bleeder resistors to gradually degrade the capacity of cells with higher SOH than other batteries in the system [4]. This can be a long, arduous process and the system can not be scaled to balance n amount of cells at a time. To contrast this type of balancing, there exists Active Cell Balancing which uses power converters to cycle through discharging and charging of batteries until the capacity of each cell in the power converter has become equal.

Active Cell Balancing will be demonstrated in this thesis using a Series Resonant Converter system with series output connection of various converters. This type of converter and connection will allow for a large amount of batteries to be balanced at a time, limited to the number of converters in the system multiplied by the number of battery input ports per converter. These series resonant converters are designed using a novel High Frequency Link transformer to limit the resistance of the series connection of output transformers by using one transformer as the secondary for each of the primaries. This topology and converter will be discussed in the following chapters along with the design and control of the system.

#### CHAPTER 2

#### BACKGROUND AND LITERATURE REVIEW

In modern technology, Battery Management Systems (BMS) are used to operate all types of technology. As cells degrade in State of Health (SOH) and nominal capacity, active cell balancing is required if these cells are to be used again in a fully assembled battery pack. Magnetically coupled isolated topologies to perform this active balancing are usually limited to three ports due to challenges in controlling the hardware and the plenitude of switches and components needed to couple more than three ports [5] [6].

#### 2.1 Battery Management Systems

In a topology similar to the one proposed in this proposal, a High-Frequency (HF) transformer based isolated DC/DC converter is introduced that provides sufficient speed (1 kHz) for voltage matching. The secondary winding is common among each of the transformers, meaning that the secondary side transformer for each of the primary ports could be either connected in series, or have a magnetic field that would be scalable enough to handle the power transfer for each of the primary ports with just the one secondary side transformer [7]. This behavior is shown below in Figure 2.1. With this output regulation on three ports, the cells connected to each primary port can be continuously balanced through active or passive cell balancing, and the amount of input ports can be scaled to aggregate three or more primary input ports. Active cell balancing distributes energy among each of the cells to balance State of Charge (SOC), while passive balancing is less efficient due to dissipation of energy across balancing resistors [8].

In comparison with other three port power converters, this HF link uses a resonant LC tank to transfer the energy in a stable, more efficient manner than other topologies such as the non-resonant dual active bridge. This topology would account for many advantageous approaches, such as: 1) Where m is the number of input primary side ports the reduced

Fig. 2.1: Three-port power transfer using one series-connected secondary transformer

component count of switches and other components needed per secondary side transformer would only amount to m + 1 rather than 2\*m. 2) Efficiency goes up due to the winding length being much shorter because the windings are either coupled into one winding or are wound in series, reducing length opposed to separate secondary side transformers for each input. 3) Each of the cells would have a common ground reference as well as a common bus bar which would negate the need for isolation of each bus.

#### 2.2 Second-Life Applications of Battery Cells

Battery Management Systems typically produce high voltage systems due to the series connection between batteries that are nominally under a lower voltage. These systems typically take on the State of Health (SOH) of the battery with the lowest SOH. Because of variances in their nominal capacities and SOH, these systems degrade rapidly and need replacing of the cells with more similar cells [9]. For this reason, it has become an emphasis of research to enable these batteries for second-life applications to reduce electric vehicle costs and to make the process of using these BMS more economical [10]. As cells are

recycled in preparation for their second-life, it enables them to be used in future BMS under similar SOH and nominal capacities that the cells are recycled with. To do so, it requires to balance the cells in a common system using either Passive or Active Cell Balancing described hereafter.

#### 2.3 Active Cell Balancing of Battery Management Systems

Throughout literature there have been various methods of control for the active cell balancing, as well as the varying load types that have been applied to the systems. The output can be loaded with a fixed output, fixed voltage, or fixed resistance where each comes with their own limitations. Fixed current requires input voltage to be regulated, which is a much more tedious, and long process as opposed to regulating input current in a system [11]. Regulation of input current requires a fixed voltage system, which is a common approach used in much of literature but a downside being the need to share output voltage. This is known as droop current and is further researched and explained in this proposal so it may be implemented in the project. Previous authors have also regulated output voltages to achieve SOC balancing [12] which would require constant input current at each of the ports. Overall, the limitations seem to favor using droop current and more research on the subject would affirm that fact.

To generate a full duty cycle (50 percent) a four-switch H-Bridge is commonly applied to the input ports to generate square waves through gate drivers that will result in AC input voltage. This AC input voltage will be applied to the SRC where it will go through another four-switch H-Bridge on the secondary side to produce DC voltage, thus affirming the DC analysis of the phasor transformation. Referring to the Active Cell Balancing methods, the duty of each of the ports will vary depending on the SOC and SOH of each cell [7]. By changing the duty cycle between ports, it allows for the input current of each of the cells to differ while only controlling one "base" current, defined as the current of the best cell. The "best cell" is found using a voltage map [13], as shown below in Figure 2.2 which takes both SOH and SOC into account to map out which cell has the highest (best) order of magnitude according to the gain provided by the voltage map labelled as  $K_{map}$ . This

base current is a central part to controlling the SRC converter for this project but is also referred to as the "reference current" because it is the controlled current value that each input primary port will refer to. The results from these author's tests show the control of the input current effects the output current, but does not directly control the output current unless attached to a constant voltage (CV) load.

Fig. 2.2: Voltage mapping for active cell balancing

To alter the common reference current, the phase between the primary and secondary windings is altered to account for the change in current across each primary winding. This current regulation is important because it allows the outputs of the converters to be connected in series or parallel [13]. With the input cells providing a somewhat constant voltage, this reference current can be used to calculate the input power, using the equation shown below, which is then transferred over the converter to the output. By measuring the output current and considering the CV load on the output, the efficiency can be analyzed by calculating the secondary power using the same equation.

$$P = VI (2.1)$$

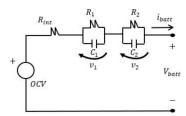

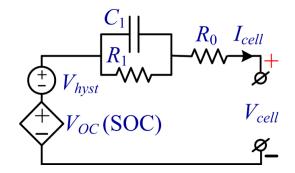

#### 2.4 Phasor Transformation of Series Resonant Converters

To regulate the input current, knowledge of the phasor currents and its input variables are required. Phasor transformations have been done for all types of converters including Buck, Boost, Buck-Boost, as well as SRC. Authors have analyzed the behaviors of SRC converters and have found it is difficult to analyze Alternating Current (AC) signals, but Direct Current (DC) signals can be simplified to give an approximate signal [14]. The math of this approximation can be difficult, but by using DC analysis and unity gains (1:1 conversion ratio of input to output) between input to output, it is proposed and discovered that input current can be controlled by the phase shift between input and output as well as the duty cycle of the bridges on each primary port. The equivalent circuit of an SRC used for this DC analysis is shown below in Figure 2.3.

Fig. 2.3: Series Resonant Converter equivalent circuit input-output

#### 2.5 Voltage Sharing of Output Series Connected Converters

Power sharing and regulation has been implemented through many of these power converters. Due to the limitations of just three primary ports in previous models, the series connection of output was the only method of balancing and controlling more than three battery cells at a time. This power sharing has come by way of both series and parallel connection, but parallel capabilities are degraded when implementing the input current regulation as researched. The major problem of output series connections of these type of converters is when connected in series the output voltage is extremely hard to control due

to the resonant capacitance on the output terminals [13].

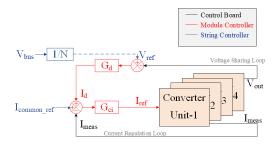

In [15]. the author noted that when a couple of SRC outputs were connected in series while in current regulation mode, the output voltage became mismatched and at times applied only to a single converter in an uncontrollable manner. Voltage sharing is a necessity among output series connected SRC and this author developed a Multi-Mode control that would implement a digital slope  $R_i$  which would determine the maximum voltage a converter could take according to the current of the output using equation 2.2. The author of [13] approached the problem in a similar manner and implemented a "droop" method that would achieve natural voltage sharing in the same manner. The performance of this droop slope is to be calculated, but an equivalent plot is shown in Figure 2.4. as well as the implementation of droop within the full system is shown in Figure 2.5. This droop accounts for any differences and maintain a similar voltage across each of the outputs (slightly offset due to uncontrollable discrepancies such as voltage loss, measuring errors, etc.).

$$V = IR (2.2)$$

Fig. 2.4: Droop slope needed for voltage sharing

This droop control allows for voltage sharing across N modules as shown above. This figure also shows the signals (namely  $I_{all}$ ) being sent from one controller to each of the converters. It is vital that the communication between each of these controllers be syn-

Fig. 2.5: N-port system for current regulation using voltage sharing by droop control

chronous. For this reason, the signals needed to start conversion and control parameters such as reference current and duty cycle are sent through a string controller to ensure timely communication [9]. Research has been done using String Controllers using various types of communication including SPI, I2C, and CAN. In [9]. the String Controller used CAN communication which made the system scalable to N modules and ensured that each module could control reference current at the same frequency.

#### 2.6 Hot Swapping

When using series or parallel connected converter, it is viable to disconnect one of the N batteries while the system is running and connect a new battery in the place of that primary port. This is called hot swapping [16]. Hot swapping has mostly been done for parallel-connected Battery packs, but the idea remains the same. There are various problems with hot swapping so it must be done with care, otherwise the battery may be damaged due to the peak current exceeding the nominal current of the system when disconnecting or replacing the battery [13]. Thus, the system must be able to ramp down the input current of one module while still processing the active cell balancing of the other N-1 systems. This method is an ongoing research discussion.

#### 2.7 Proposed Approach

With the emerging solutions of Active Cell Balancing to enable second life use for BMS, there is a need for large systems that can recycle large amounts of batteries. At Utah State University, a system has been designed and tested to enable up to 8 cells to be recycled using active cell balancing but has not been tested with larger amounts of battery cells. This project would entail the design, production, and testing of a larger system up to 96 cells that would all be balanced to similar SOH. This is to be done efficiently using calculated ratings and safety limits and will allow for hot swapping, replacement of a battery cell including disconnection preceding the replacement of a particular cell while the system is still running, of any module in the system.

Design and testing of this battery system used for series control of a SRC will include

but not be limited to these procedures. The SRC will need both inductors and a system control board to be designed and the efficiency will be analyzed and idealized. This board will need to be tested and controlled for active cell balancing of Nissan Cells to enable second life applications for battery cells. The secondary side of each of the boards will be connected in series to output up to 750 V using said Nissan Cells. For this series connection to function accurately, a PI droop compensator will need to be designed so each converter can share voltage nearly equivalent across each of the output ports. Modules containing these converters will be connected in series on the secondary side and communication between each of these modules will need to be synchronous at a frequency of nearly 1 kHz. This system will also require being able to disconnect and reconnect battery cells to fulfill the term "hot swapping."

#### CHAPTER 3

#### BATTERY CELL RECYCLING FOR SECOND LIFE APPLICATION

#### 3.1 Second Life Applications

Lithium-Ion batteries are commonly used in the EV sector, but prices of these batteries keep rising due to the limit that these batteries hit within the first 20% of their lifetime as their capacities degrade. This capacity limit of 70-80% is known as the 'ageing knee' and is typically when a battery is discarded from EV operation and deemed at its End of Life (EOL) for Electric Vehicle purposes [17]. As prices keep rising in the Lithium-Ion industry due to demand in the EV sector, optimization of these batteries is required for longer lifetimes of these batteries. The term 'second-life' refers to the batteries that have reached their EOL stage and are no longer applicable for Electric Vehicle use and are typically discarded, creating a carbon footprint that will be discussed later in this report. Instead of discarding these batteries, they can be used in applications that are less demanding when it comes to performance, volume, and weight limitations.

These applications for Lithium-Ion batteries can enable longer life of these batteries which will have environmental benefits as well as economical benefits. Studies have shown that Second-Life applications could drop the price of Lithium-Ion batteries by nearly 50% over the next 5 years as the production of batteries gets larger to accommodate for more Electric Vehicles and the use of these batteries are prolonged [18]. Bloomberg New Energy Finance estimates that the market for second-life batteries could account for 26 GWh by 2025 and will continue growing as the EV sector continues to grow. As the EV sector continues to grow, the grid will need to provide up to 30% more power in peak power times and these second-life batteries could be used to supplement the grid and be used in a power smoothing application for grid-scale power plants as shown in Figure 3.1.

So what happens to batteries during their first life that causes the End of Life stage

Fig. 3.1: Lithium-Ion battery recycled life-cycles for power smoothing of power plants

that limits these batteries from being able to provide power to Electric Vehicles? As shown in Figure 3.2 below, a Lithium Battery has three significant instances in its lifetime from 0-100%. The First-life EOL threshold is due to a change in slope of the capacity that usually occurs at around the 70% mark due to higher internal resistance and lower nominal capacitance. This State of Health (SOH) is no longer capable of powering a high-voltage application such as an Electric Vehicle, so Li-Ion batteries are removed from first-life application at the 80% mark, or close to it, to avoid that initial drop in slope of SOH. The next drop in slope occurs at about that 60% mark, but varies according to cell chemistry and capacity degradation that the cell has seen earlier in its lifetime, including during first-life. The final instance is the 30% threshold that signifies the Second-life EOL threshold. As seen in the below figure, the slope drastically drops to a point where the cell is no longer usable, even for second-life applications.

Second-Life applications are required to be less-demanding than applications such as Electric Vehicles. Performance, volume, and weight must not be critical to the function of the system, and the system must operate with low energy density to avoid high charge/discharge of the battery with high currents. The Figure 3.3 below shows a study done in [18] that indicates a fade in SOH at higher temperatures, which is fine for first-life, but to op-

Fig. 3.2: Lithium-Ion battery SOH curve

timize the capacity and SOH curve for second-life applications, this must be used at lower temperatures, as indicated by the small slope in capacity fade from the red data.

Fig. 3.3: SOH and capacity fade depending on temperature

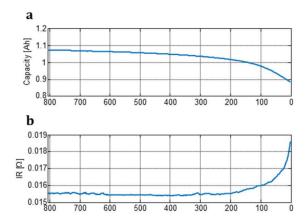

Another reason for second-life applications requiring lower energy density can be seen in Figure 3.4 from [19] which indicates the resistance and capacity fades becoming more rapid in latter stages of life, and that slope should continue to degrade as Li-Ion cells are used in second-life applications. Higher internal resistance promotes more resistive losses in the connection between the internal battery in the battery pack, and the application to

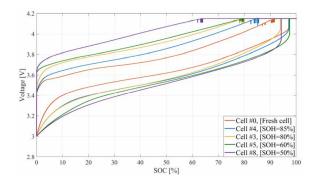

which it is connected. Another study in [20] models a Li-ion battery with the circuit shown in Figure 3.5. This circuit is used to demonstrate Open Circuit Voltage curve development and tests were run to find the OCV curve of a Li-Ion cell at varying rates of SOH. The data shown in Figure 3.6 demonstrates the OCV curves developed through charge (the top waveforms) and discharge (the bottom waveforms) cycles that indicate lower capacity and degraded OCV curves as a battery is degraded in SOH. The study also found confirmed that lower C-rates of these EOL batteries resulted in higher efficiency of each Battery Management System as a whole with slower degradation rates.

Fig. 3.4: Resistive and capacitive fade of Li-Ion batteries throughout second life

Fig. 3.5: Equivalent circuit of a Li-Ion battery

To optimize second-life performance for lower density applications, a study was done in [21] to detail the Useful life of a Li-Ion battery in its second-life. These Remaining-Useful-Life (RUL) Tests were typically used on batteries that were monitored their whole life, which is not the case with battery packs in electric vehicles, but the technique remained

Fig. 3.6: Open Circuit Voltage curve at varying SOH

the same to for the estimation algorithm of RUL for second-life batteries. The estimation requires large amounts of tests which take away from the RUL, so a healthy medium is established in this paper and the success rate is shown in Figure 3.7. Figure 3.8 shows the results of the RUL estimation techniques used on second-life Li-Ion batteries after only 150 cycles were performed for the algorithm.

Fig. 3.7: RUL Estimation success rate

Optimization of Li-Ion batteries in second-life can also result from how the Battery Management Systems makeup of batteries is decided. A study in [22] represents the internal resistance and capacity of cells in a pack and the degradation through a number of cycles that they call FEC (Full Equivalent Cycles:  $(Ah_{CHARGE} + Ah_{DISCHARGE})/Q_{NOM}$ . As shown in Figure 3.9, the degradation of both internal resistance and of capacitance, or SOH, is much more rapid in Figure 3.10 than Figure 3.10. This is due to the homogeneity of the cells in the pack. The cells that are heterogeneous differ in SOH and capacity and

Fig. 3.8: RUL Estimation compare to actual RUL

result in much faster degradation than those cells that have been balanced. After first-life use in Electric Vehicle application, cells have degraded in both resistance and capacitance in different manners. Even battery cells in the same battery pack during first-life become heterogeneous in cell chemistry. For homogeneity in cells to be used in a second-life BMS, cell balancing is required which can balance a number of cells through either active or passive cell balancing [23]. The makeup of the homogeneous cells result in a much better chemistry in the battery pack which would be well utilized in second-life applications.

Fig. 3.9: Degradation of a homogeneous collection of Li-Ion cells

As stated before, second-life battery applications require low energy density and relatively low C-rates compared to their use in first life. These applications include but are not limited to: Battery storage Systems that can increase household energy self-consumption and can power a small building or a home with the energy stored; Low-voltage grid reinforcements that can provide small amounts of voltage to account for any instability provided

Fig. 3.10: Degradation of a heterogeneous collection of Li-Ion cells

from applications being connected to the grid spontaneously; Grid reinforcements that can improve energy efficiency in the grid and can also match peak power generation consumption through storage systems. An application with an emphasis on being explored for second-life applications are grid reinforcements so EV batteries can be used to supplement the power grid increasing through these EV applications. The study in [24] explains the 30% additional power rating that the grid will require over the next two centuries, and they propose and test infrastructure of Battery Energy Storage Supplements for the grid. This process is shown below in Figure 3.11 and was validated through testing this process. These grid supplements would enable a better market and economy of Li-Ion batteries with prolonged use and would be able to stabilize grid problems that could arise from full electrification of transportation.

Research continues to be furthered in the area of Second Life Battery Technology. Second-Life batteries in general are becoming a bigger topic due to the nature of Lithium-Ion batteries and the need to find a more sustainable way of using them both environmentally and economically. With the expansion of the electrified transportation market, there grows a bigger need to determine how these batteries will be used once they have been deemed at their End-of-Life (EOL). Efforts are being made to maximize the life of the Second-Life batteries by balancing cells that will be accumulated into a battery pack to prolong the life of their next use.

Balancing of the cells can be taxing on the battery due to the charge/discharge of the

Fig. 3.11: Lifecycle of EV battery to grid supplemental battery

battery taking away from future cycles they could have with their second-life application. Active Cell Balancing, however, provides a longer lifetime for the batteries in their battery pack due to homogeneity of the capacities and State of Health of the batteries that would otherwise be heterogeneous. This homogeneity in cells will prolong each of these cells' lifetime considerably and thus is an ongoing area of interest to maximize lifetime of Li-Ion batteries. Active Cell Balancing entails the balancing of cell capacities using SOC Estimation algorithms and balancing techniques depending on which is the best cell and worst cell, as shown below in the Figure 3.12. Passive Cell Balancing is also a topic of interest for the same reason but has not shown quite the same progression in research as Active Cell Balancing.

There are various other techniques being used to maximize cell lifetime and efficiency by monitoring the cells during their first-life, or determining their Remaining Useful Life (RUL) using similar algorithms but without the information of the first-life [21]. Applications for battery packs with non-taxing needs continue to be researched and discovered giving more meaning for second-life application and cell balancing for their new applications.

Fig. 3.12: Active Cell Balancing charge and discharge cycles depending on best/worst cells of BMS

Secondary batteries in EVs are also being considered to help cell life. By having a secondary battery to extend range the cells in the primary battery can be operated at healthier states of charge (SOCs). These techniques are especially effective in long range applications despite the increased complexity [25]. Dual battery systems could be an effective use to improve battery usage.

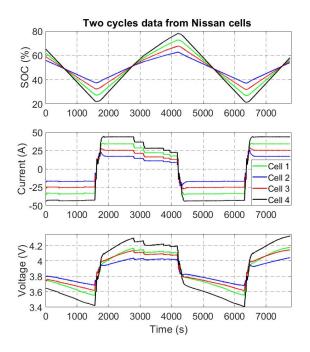

#### 3.2 Arbin Cyler

Batteries, such as the Nissan Cells being used for active cell balancing and second life applications, have various characteristics such as capacities (nominal and actual), State of Charge (SOC), and State of Health (SOH) which can denote the overall performance of a specified battery as well as determine what uses and limitations it may have for certain applications. For First-life applications, such as the Electric Vehicle (EV), the cells are carefully assembled with specified characteristics and chemistries that are designated beforehand and some values are provided by the manufacturer's of the battery. Below in Figure 3.13, some specifications are shown detailing the nominal voltage and current range of the battery. These are the specifications for the Nissan Cells used in this project when they were initially created and put into production for EV use. The modern limits and nominal values will be described later in this section, as well as characterized capacities.

| Nominal module voltage               | 7.5 V              |

|--------------------------------------|--------------------|

| Maximum charge module voltage        | 8.2 V (4.1V /cell) |

| End of discharge module voltage      | 5.6 V (2.8V /cell) |

| Maximum continuous charge current    | 40A                |

| Maximum continuous discharge current | 40 A               |

| Operation temperature                | 10 to 45°C         |

| Storage temperature                  | -10 to 45°C        |

| Storage humidity                     | Non-condensing     |

| Storage time limit                   | 200 days           |

| Mass                                 | MAX 3.85kg         |

| Dimension                            | 303 x 223 x 35 mm  |

| Insulation resistance                | >100 MΩ            |

Fig. 3.13: Nissan Cell Characteristics from Datasheet

The capacity and SOC of a battery can be determined using Coulomb counting to develop an Open Circuit Voltage (OCV) curve. This process uses current to charge/discharge a battery at various temperatures to produce an average waveform while measuring

Capacity, in Amp-hours (Ah), on the x-axis, and the voltage, in Volts (V), on the y-axis. OCV curves can be derived by charging and discharging the battery between 0% and 100%.. The nominal capacity is derived from the amount of Ah it takes to drop the voltage from it's highest voltage, also known as the full State of Charge, to it's drop-off point to 0 V, which in this case begins at about 2.5 V. Using this OCV curve, the State of Charge can be determined by replacing the x-axis from capacity to SOC with 100% as the peak voltage and 0% SOC as the drop-off point. It is important to know the State of Charge of a battery so as to not overcharge or over-discharge a battery beyond it's limits. Typically a battery is not used past the 80% or 20% SOC due to a rapid decline/incline of the slope at these points.

The State of Health of a battery is also important, especially when contemplating second-life applications and the limitations a battery may have. Upon conception for first-life use, a battery is deemed to be at 100% State of Health and degrades the more it is used. The cutoff between first-life and second-life is typically around 80% and the Nissan Cells are taken away from their Electric Vehicles and discarded. This project maintains the ability to use these cells in second-life applications depending on the density and SOH curve of the cell. Although not explored in this thesis, research has shown that rapidly degraded first-life cells also degrade more rapidly during their second life, which can be predicted using these SOH curves during first-life (Technical Liability, Martinez-Maserna). These second-life applications are deemed successful for these recycled batteries until about the 30% SOH mark where the battery is discarded due to the rapid decline in SOH seen in aforementioned battery life usefulness tests, also known as the ageing knee. The same paper mentioned the performance enhancements of second-life cells used with homogeneous cells in regards to their SOH and internal resistance.

The Arbin Cycler is a useful tool that can determine these characteristics of batteries using coulomb counting and other processes. The Arbin was used heavily in this project as a means of a power source and to find the capacities needed for coulomb counting for the individual Nissan cells. Due to the Nissan cells' first-life degradation, the cells being

used needed to be re-characterized to determine the proper OCV curve and find the actual capacity of the cell as opposed to the nominal capacity shown in the first OCV curve. The capacities of the cells were a necessity for this project to enable the coulomb counting and best/worst cell selection for the active cell balancing which will be discussed hereafter.

The Arbin is shown below in Figure 3.14 and is a battery life-cycle emulator that has various capabilities, all pertaining to batteries. It can be used to power a battery and charge it up, or as a load to discharge a battery and send power to the grid. The software developed uses switches to safely connect the 12 Arbin channels to 12 battery cells and has limits that can be set to ensure safe use of the batteries being characterized. It is capable of characterizing most battery cells, but does have limitations as it cannot exceed  $\pm 5$  V and has a limit of  $\pm 300$  A. Its high current capability helps to be able to run these characterization tests such as life-cycle tests, Open Circuit Voltage tests, dynamic and static characterization tests to develop an equivalent model of the battery, and many others. Tests that were not run on this project but could have been useful include the life-cycle test which charges and discharges a battery from 100% SOC to 0% SOC, or any other predetermined level of charge, to find it's first-life ageing knee where the SOH drops below 80% SOH, as well as full testing of equivalent circuit models for the Nissan Cells. The static and dynamic characterizations of the cells were performed in prelude to the equivalent circuit model analysis but were never realized fully. The results of these tests result in proper parameters for the full order cell model shown in Figure 3.15 as described in [26].

Open Circuit Voltage tests were performed on the Nissan Cells to determine new OCV curves and find the actual capacities of each cell in a pack. A detailed Open Circuit Voltage test requires a thermal chamber and Arbin to develop curves at different temperatures until an average waveform is found. The equipment needed for this varying temperature test was not available for this time of characterization. A characterization of a Lithium-Ion cells OCV curve is shown below in Figures 3.16 and 3.17 to demonstrate the small margin of difference between the test performed at room temperature, to the actual OCV curve of the cell, and of the cell characterizations at different capacities. For this reason, the Nissan

Fig. 3.14: Arbin Cycler Instrument for Battery Cycling

Fig. 3.15: Lithium-Ion Full Order Cell Model

Cells were tested purely at room temperature to determine the OCV curve and capacity of these second-life cells. This OCV Curve of a Nissan Cell is portrayed in Figure 3.18.

4.2

4.3.8

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.3.6

2.

Fig. 3.16: OCV Curve developed through various temperatures [1]

Fig. 3.17: OCV Curve developed through various capacities [2]

Fig. 3.18: Open Circuit Voltage Curve of a 2nd-life Nissan Cell developed by Arbin Cycler

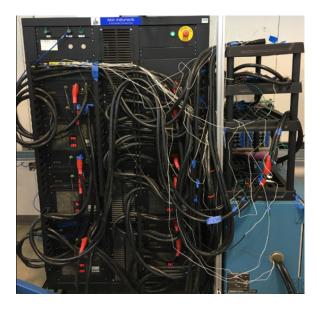

Before running testing of the converters and circuits with the Nissan Cells, preliminary testing was done to validate the design of the circuitry to ensure connection to the Nissan Cells could be done without damage and that the software worked correctly. For this reason, the project required 4 voltage sources with high current capability, namely  $\pm 40$  A, which

could be provided from the Arbin Cycler. However, when the Arbin made connection to a system it would begin in discharge mode to verify the connection to a battery. This could prove harmful to the system and fuses, so circuitry was developed as shown below in Figure 3.19 to discharge two resistors in series before closing switches that would connect the converter boards to the Arbin Cycler. This ensures that the Arbin Cycler would work as a voltage source to the system without causing any of that initial harm. The attachments and components assembled for this circuitry is shown in Figure 3.20.

Fig. 3.19: Circuit design for isolation from Arbin to system at startup

# 3.3 Active Cell Balancing

Series connection of battery cells require similar chemistry and capacity of cells to reduce the imbalance between cells and possibility for instability of the full system. Even without instability, series connected battery systems with heterogeneous cells pose threats to the longevity of the battery pack and the possibility of extending the life of the battery pack during second life would be diminished. Chemistry of battery cells are inevitably different thus the batteries will degrade differently and have different capacities and State of Health. Homogeneity is a condition of the batteries that will have to be imposed on each

Fig. 3.20: Circuit setup for isolation from Arbin to system at startup

cell through cell balancing.

There are two types of cell balancing, one being passive cell balancing and the other active cell balancing. Passive cell balancing are slower in process and less efficient than active cell balancing. It consists of various algorithms that have been studied [27] but the concept remains the same of using bleeding resistors for batteries with higher capacities in order to discharge the battery more rapidly and to degrade the capacity until it can become similar to other batteries. This process tends to be complex and slow unlike the active cell balancing techniques that require DC/DC converters to cycle the battery cells through various charge and discharge cycles [7] until the batteries achieve homogeneity in SOH.

Active cell balancing consists of DC/DC converters that can cycle various cells through charge/discharge cycles depending on the State of Charge of the cells connected to the converter. This thesis work consists of the Series Resonant Converter connected to a High Frequency (HF) link which is a novel idea introduced in [7] and requires galvanic isolation which is provided by the HF transformer that is common for each of the primaries. Most of the DC/DC converters used for active cell balancing consist of 3 or less ports, while this thesis work will enable cell reconditioning of 4 channels per converter with various converters connected in series for a modular connection which can be connected in series with other similar modules.

Active Cell reconditioning will achieve homogeneity of the cells by discharging/charging the cells with the highest capacity (the best cell) at the highest C-rate while the cell with the lowest capacity (the worst cell) will be charged at the lowest C-rate, as shown in Figure 3.21 [28]. This will enable little to no degradation of the SOH of the worst cell while the best cell will have rapid and major degradation in SOH and nominal capacity. This method was used in [29] and validation of the algorithms are shown below in Figure 3.22 while the next section will provide some insight into the algorithm used for the cell balancing. The figure provides the necessary waveform for SOC to be charged and discharged each cell proportional to its capacity. This was done using the Proof-of-Concept (POC) prototype to validate its use for the full scale system.

Fig. 3.21: Lithium-Ion Battery Reconditioning Objective Map

Fig. 3.22: Active Cell balancing charge and discharge waveforms using POC concept

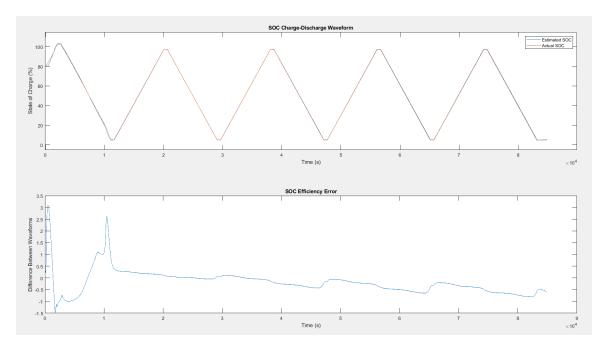

# 3.4 SOC Estimation and Objective Map Calculations

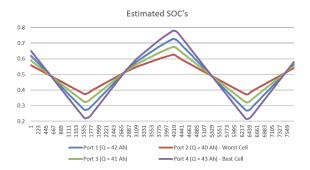

SOC Estimation requires initially the data showing the actual capacity of each of the cells and the OCV curve to denote State of Charge from the voltage at the terminals, as described previously on OCV curves. While the OCV curve is helpful for SOC calculations when there is negligible current coursing through the battery cells, when current is applied the voltage needs to settle before using this again. This does not bode well for measuring SOC during cell balancing, so an algorithm was developed that can estimate SOC based on the C-rate and nominal capacity of the batteries, called objective mapping. This algorithm is known as the Sigma-point Kalman filter (SPKF) derived in [30] and the gains were calibrated to the Nissan Cells being connected to the system. This calibration and validation can be seen in Figure 3.23 where the SOC is estimated in MATLAB over various intervals. This initially has a margin of error that gets corrected over time and through more cycles, which serves well for the cell balancing for SOC estimation.

Fig. 3.23: Objective Map calibration for Nissan Cell chemistry

#### CHAPTER 4

#### MATHEMATICAL ANALYSIS AND DESIGN

#### 4.1 Series Resonant Converters

Active Cell balancing requires a DC/DC Converter to cycle through charge and discharge cycles of batteries in a coordinated manner as described in the previous chapter. This is to be done continuously and efficiently which was an important factor in the decision to use a LCC Series Resonant Converter (SRC) for maximum power transfer and minimal resistive and conductive losses in the system which could cause the temperature of the system to exceed safety bounds needed for the cycling and use of battery cells, especially Nissan Cells.

A SRC is highly efficient due to the resonant frequency between reactive and resistive components in the system. Upon resonance, the reactive components of both primary and secondary impedances cancel each other out. This results in minimal electrical energy losses resulting in heat because the switching, resistive, and inductive losses are negligible during the resonant frequency and the system can perform more efficiently.

The switching frequency of the system was chosen to be 190 kHz, meaning that the switches would alternate in the H-Bridge every 5 us. The resonant frequency then could either be chosen to be above or below switching frequency depending on the desired switching characteristics of the system. Any resonant frequency above 200 kHz would result in Zero Current Switching and would result in the tank current increasing as the output current of the system after the rectifier decreased. With the system operating at currents up to 40 A, but also ramping current from 40 A to 0 A to -40 A, this was not desirable.

Instead, the resonant frequency was chosen to be below switching frequency, anywhere around 160 kHz for each converter unit. This resulted in Zero Voltage Switching (ZVS) and would result in the tank current decreasing as the output current of the system of

the rectifier decreased. This ZVS would also result in more efficient performance of the switches and higher efficiency of the system. Resonant Frequency can also be measured as  $f_r = 1/(2*pi*sqrt(L*C))$  where C is the DC blocking capacitor in the secondary and L is the secondary transformer inductance. The Power Converter design will be discussed in the upcoming sections, but have a DC blocking capacitance value of 1uF which would require an inductance of nearly 1uH for the resonant frequency to be met. The following Figures 4.1- 4.2 show the calibrated values for the secondary of one of the converter units. These values were obtained using a frequency sweep of the LCR meter to view the resonant frequency plot and the inductance value at the switching frequency of the system.

Fig. 4.1: Frequency plot of the impedance frequency sweep portraying the resonant frequency peak of the system

#### 4.2 Control Board Design

Printed Circuit Board's were designed for the needed controller boards and power boards. The boards involved in this project include the following: Power Board, Control Board, Module Controller Board, and the String Controller Board. While the Power Board, Module Board, and String Board were previously designed, the Control Board was needed

| 4   | А         | В         | С         | D        | Е        | F        |

|-----|-----------|-----------|-----------|----------|----------|----------|

| 1   | Frequency | AC Status | Cs        | Rs       | Z        | Ls       |

| 357 | 183740    | 0         | -8.62E-07 | 7.87E-02 | 1.01E+00 | 8.70E-07 |

| 358 | 184370    | 0         | -8.48E-07 | 7.36E-02 | 1.02E+00 | 8.79E-07 |

| 359 | 185000    | 0         | -8.41E-07 | 7.68E-02 | 1.03E+00 | 8.80E-07 |

| 360 | 185630    | 0         | -8.40E-07 | 7.93E-02 | 1.02E+00 | 8.75E-07 |

| 361 | 186260    | 0         | -8.23E-07 | 8.14E-02 | 1.04E+00 | 8.87E-07 |

| 362 | 186890    | 0         | -8.29E-07 | 1.15E-01 | 1.03E+00 | 8.75E-07 |

| 363 | 187530    | 0         | -8.40E-07 | 7.07E-02 | 1.01E+00 | 8.57E-07 |

| 364 | 188170    | 0         | -8.11E-07 | 6.29E-02 | 1.04E+00 | 8.82E-07 |

| 365 | 188810    | 0         | -8.07E-07 | 8.01E-02 | 1.05E+00 | 8.81E-07 |

| 366 | 189460    | 0         | -8.00E-07 | 6.97E-02 | 1.05E+00 | 8.83E-07 |

| 367 | 190100    | 0         | -7.76E-07 | 7.41E-02 | 1.08E+00 | 9.04E-07 |

| 368 | 190750    | 0         | -7.82E-07 | 7.18E-02 | 1.07E+00 | 8.90E-07 |

| 369 | 191400    | 0         | -7.90E-07 | 8.50E-02 | 1.06E+00 | 8.75E-07 |

| 370 | 192050    | 0         | -7.71E-07 | 8.16E-02 | 1.08E+00 | 8.91E-07 |

| 371 | 192710    | 0         | -7.70E-07 | 8.73E-02 | 1.08E+00 | 8.86E-07 |

| 372 | 193370    | 0         | -7.64E-07 | 8.30E-02 | 1.08E+00 | 8.87E-07 |

| 373 | 194030    | 0         | -7.55E-07 | 7.69E-02 | 1.09E+00 | 8.91E-07 |

| 374 | 194690    | 0         | -7.50E-07 | 7.87E-02 | 1.09E+00 | 8.91E-07 |

| 375 | 195350    | 0         | -7.45E-07 | 8.11E-02 | 1.10E+00 | 8.91E-07 |

| 376 | 196020    | 0         | -7.39E-07 | 8.24E-02 | 1.10E+00 | 8.92E-07 |

| 377 | 196690    | 0         | -7.35E-07 | 7.99E-02 | 1.10E+00 | 8.90E-07 |

| 378 | 197360    | 0         | -7.26E-07 | 7.98E-02 | 1.11E+00 | 8.96E-07 |

| 379 | 198030    | 0         | -7.23E-07 | 7.83E-02 | 1.11E+00 | 8.93E-07 |

Fig. 4.2: LCR meter readings of a frequency sweep indicating the inductance of the secondary

for communication between the Module Controller's microcontroller and the Power Converter Board. The Controller Board would be overlaid on top of the Power Converter Board to allow gate drive signals and ADC readings to be transferred between boards through Molex connector's. Other connections necessary included the auxiliary power supply, for the 12 V power needed for powering some of the Integrated Circuits (IC's) of the Power Board and Control Board, and the RJ-45 ethernet connector's allowing communication between the Microcontroller on the Module Controller Board to the FPGA on the Control Board. Shown below is an image of the final version of the Control Board in Figure 4.3.

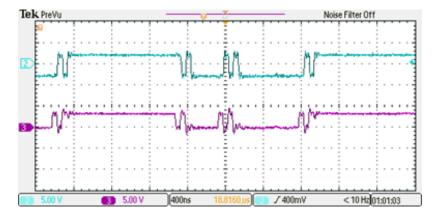

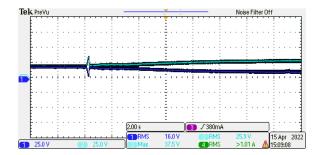

A difficulty in this project was component selection due to the shortage of components created from the COVID-19 pandemic. The DC/DC Converter's were replaced between the conceptual version for testing of functionality, and the actual version for full system testing as well as the ADC's and digital isolator's. The only real problem caused by these adjustments were the timing of the digital isolator's as the signal was delayed by one clock

Fig. 4.3: Final design of control board for FPGA communication

signal, as seen in the oscilloscope waveform from Figure 4.4, which was easily corrected in the FPGA code. The ADC's had no problem with the new implementation, but the signal's being sent from the current sensor had a problem. Both Current Sensor's had the same pin-out, shown below in Figure 4.5. Due to a mistake in product delivery and storage, the manufacturer provided a current sensor with a different pin-out so a small workaround was made in the soldering of the component to correctly connect the pins to the corresponding pads. The workaround on the new pin-out is shown in Figure 4.6. Other than the shorting of pins with NC pins, the IC had to be shifted slightly upward to account for the GND pin being misplaced slightly.

Fig. 4.4: ADC signals being delayed by one clock cycle with the new ADCs

Fig. 4.5: Pin-out of the previous and new current sensor's provided by manufacturer

Fig. 4.6: Pin-out and workaround of the new current sensors sent by mistake

The board was designed using Altium Designer where a circuit schematic and a PCB layout was configured. Grounds were configured to allow for the 600 V operation on the secondary. Other ground and signal interference was negligible due to the use of digital isolation between each ground signal. The FPGA was powered by the 12 V auxiliary after processing the voltage through a 12 V to 5 V DC/DC converter and a 3.3 V linear regulator. A multiplexer was also needed for cycling through the thermistor's needed for the Module Control Board which also held isolation on the Control Board along with an op-amp for cycling through using Chip Select. This communication was done through Serial Peripheral Interface (SPI) with a MISO (Master In Slave Out) line for communication from the Module Controller's Microcontroller to the FPGA and SIMO for the communication from the FPGA to the Microcontroller. Digital isolation was also provided between the ground of the Microcontroller and the ground of the FPGA. More of this communication will be discussed in the Module testing of the Results section.

## 4.3 Boards Layout

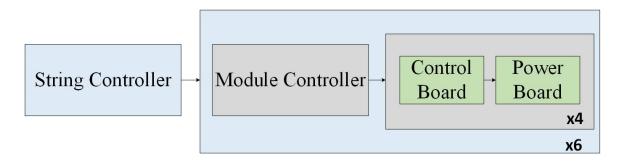

Each Power Board has a Control Board with an FPGA to communicate signals and process data between controllers and Power Converter. The combination of these two boards interlaced together will be known hereafter as a Converter Unit. The layout is shown below

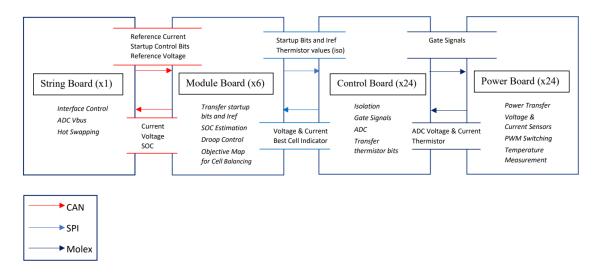

in Figure 4.7 where there will be four converter units for each Module Controller Board and there will be six Module Controller Boards for every String Controller Board. This will enable the main communication to come from a String Controller to simultaneously send signals to 6 Module Boards, each of which will be communicating with 4 Converter Units. The communication needs to be synchronous so each converter unit can power up at the same time as well as regulate input current and output voltage simultaneously with the other boards.

Fig. 4.7: Simple Block Diagram portraying the Boards layout

Timing between each board is set so every 1 ms the signals will be communicated between boards to operate as a 1 kHz frequency. The signals between each controller are clearly spelled out in Figure 4.8 and the method of communication each board will be using to send data from one board to the next. The main methods of communication are over a CAN bus between the String Controller and Module Controller (also the Site Controller, or the PC in this case) as well as through SPI communication using SIMO and MISO between Module Controller and Control Boards. Any analog signals, namely between control board and power board, will be traced together using Molex connectors that will allow the signal to go from one board to the next without any delay. The signals being communicated through these two boards include the gate signals, thermistor values, and the ADC readings of the input and output current and voltage. These ADC readings allow for limits and regulation of the Power Board from the FPGA. The Gate Signals are sent from the Control Board to control the switches on the Power Board which will enable power transfer from the Primary

to the Secondary side of the Series Resonant Converter transformer.

Fig. 4.8: Signals being communicated between each of the four boards. (Signals from the String Controller are coming from a Site Controller controlled by the user)