# Analysis and Design of Methods for Condition Monitoring of Capacitors in Multilevel Converters

Ronak Vivek Nemade

A Thesis

In the Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada.

March 2021

© Ronak Vivek Nemade, 2021

#### CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Ronak Vivek Nemade

Entitled: Analysis and Design of Methods for Condition Monitoring of Capacitors in Multilevel Converters

and submitted in partial fulfillment of the requirements for the degree of

### Master of Applied Science (Electrical and Computer Engineering)

Complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

Image: ChairChairDr. Glenn CowanExaminer, External to<br/>the programDr. Anjali Awasthi (CIISE)ExaminerDr. Glenn CowanExaminerSupervisorSupervisor

Dr. Akshay Kumar Rathore

Approved by:

Dr. Yousef R. Shayan, Chair Department of Electrical and Computer Engineering

March 18<sup>th</sup>, 2021 Date of Defence

Dr. Mourad Debbabi, Interim Dean Gina Cody School of Engineering and Computer Science

### ABSTRACT

#### Analysis and Design of Methods for Condition Monitoring of Capacitors in Multilevel Converters

Ronak Nemade.

Concordia University, 2021

Multi-level converters are an important class of power electronics based systems that enable seamless conversion of electrical power from one form to another. Due to its distinct merits, it finds a vast scope of application in the fields such as renewable energy, electrical power transmission, adjustable speed drives, uninterrupted power supplies and custom power devices. These merits often come at a cost of increased complexity, higher number of power semiconductor devices and higher number of energy storage elements. Multi-level converters generates staircase waveform by use of high density capacitor banks. These capacitor banks are often subject to failure due to vaporization of electrolyte forming weakest link in reliability context. This thesis addresses reliability issue by proposing an online condition monitoring method for a three-level neutral point clamped multi-level converter which can be easily integrated with existing control methods. The proposed method provides an online estimate of existing capacitance in DC-link and helps increase in reliability in terms of preventive maintenance. The validity of proposed technique is obtained by verification of the method on a 3KVA laboratory developed experimental prototype. It also addresses reliability by developing tool in terms of analytical expressions which can be used as a ready reckoner for proper design of capacitor bank employed in five-level active neutral point clamped multi-level converter. Results from this developed tool are quantitatively verified with the results obtained from converter models developed over MATLAB Simulink environment confirming their accuracy.

## Acknowledgement

I would like to express my sincerest gratitude, special appreciation and many thanks to my supervisor, Dr. *Akshay Kumar Rathore* for his guidance, supervision and his patience with me. I am thankful for his valued and timely suggestions not only for academics, and research work but also on personal life fronts. My success in learnings and completion of this thesis is based on his scientific knowledge, critical thinking and his continuous support.

The completion of this thesis also includes technical inputs and help from my colleagues in the Power Electronics and Energy Research (PEER) group. I would like to express thanks to *Dr. Sivanagaraju, Dr. Venkat, Swati, Dwaipayan, Karan* and *Abhinandandan* for their friendship and support. I would like to thank *Amit Chandra* my friend and my guide who helped me during the periods of depression and anxiety.

I would like to thank my parents (*Mr. Vivek Nemade* and *Mrs. Nilima Nemade*) and my brother *Hardik* for their continuous love and support.

In the end, I would like to acknowledge almighty God who kept me going during the hard times and helped me gain moral strength to complete this degree.

# **Table of Contents**

| LIST C | F TABLES                                                                                                                                  | VIII     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

| LIST C | F FIGURES                                                                                                                                 | IX       |

| LIST O | F ABBREVATIONS                                                                                                                            | XI       |

| LIST O | F SYMBOLS                                                                                                                                 | XII      |

| CHAP   | TER 1: INTRODUCTION                                                                                                                       | 1        |

| 1.1    | Introduction                                                                                                                              | 1        |

| 1.2    | Literature Review                                                                                                                         |          |

| 1.3    | Research Objectives                                                                                                                       | 6        |

| 1.4    | Thesis Outline.                                                                                                                           | 7        |

| CHAP   | TER 2: CONTROL METHODS FOR MULTILEVEL CONVERTERS                                                                                          |          |

| 2.1    | Introduction                                                                                                                              | 8        |

| 2.2    | Hysteresis Current Control                                                                                                                | 8        |

| 2.3    | Linear Control Method                                                                                                                     |          |

| 2.3    | .1 Carrier based Pulse Width Modulation                                                                                                   |          |

| 2.3    | .2 Linear control method using Space Vector based Modulation                                                                              |          |

| 2.4    | Predictive Control Method.                                                                                                                | 14       |

| 2.4    | .1 Finite Control Set Model Predictive Control                                                                                            |          |

| 2.5    | Synchronous Optimal Control                                                                                                               |          |

| 2.5    | .1 Synchronous Optimal Pulse Width Modulation                                                                                             |          |

| 2.6    | Potential Control Methods for Online Condition Monitoring                                                                                 | 17       |

| 2.7    | Conclusion                                                                                                                                | 17       |

| OF 3-I | TER 3: A FINITE CONTROL SET MODEL PREDICTIVE CURRENT (<br>LEVEL NEUTRAL POINT CLAMPED CONVERTER WITH COND<br>FORING OF DC-LINK CAPACITORS | ITIONING |

| 3.1 | Intr         | oduction                                                                                          | . 19 |

|-----|--------------|---------------------------------------------------------------------------------------------------|------|

| 3.2 | Ma           | thematical Modeling                                                                               | . 19 |

| 3.2 | 2.1          | Power Converter Model                                                                             | . 19 |

| 3.2 | 2.2          | Load Model                                                                                        | .23  |

| 3.2 | 2.3          | Discrete-Time Model for Prediction                                                                | .23  |

| 3.3 | Co           | ntrol Design                                                                                      | . 24 |

| 3.3 | 3.1          | Conventional FCS-MPCC Scheme                                                                      | . 24 |

|     | 3.2<br>onver | Dynamic Neutral-Point Model and its Impedance Predictability in a Three-Le                        |      |

| 3.3 | 3.3          | FCS-MPCC with Condition Monitoring                                                                | . 27 |

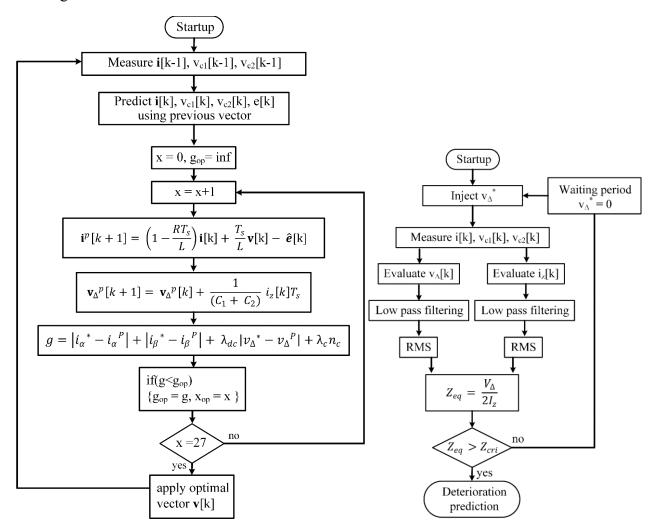

| 3.4 | Alg          | gorithm Implementation                                                                            | . 28 |

| 3.5 | Cho          | bice of difference voltage injection frequency                                                    | 30   |

| 3.6 | Sin          | nulation results                                                                                  | 30   |

| 3.7 | Haı          | dware Implementation and Results                                                                  | . 34 |

| 3.7 | 7.1          | Hardware Implementation                                                                           | 35   |

| 3.7 | 7.2          | Experimental Results                                                                              | 37   |

| 3.8 | Co           | nclusion                                                                                          | 41   |

|     |              | 4: ANALYTICAL EVALUATION OF CAPACITOR CURRENT STRESS<br>EL ACTIVE NEUTRAL POINT CLAMPED CONVERTER |      |

| 4.1 | Intr         | oduction                                                                                          | 42   |

| 4.2 | Pri          | ncipal of Operation                                                                               | 42   |

| 4.3 | Def          | fining mathematical expressions for conduction intervals.                                         | 43   |

| 4.3 | 3.1          | Conduction function - Low frequency switch                                                        | . 43 |

| 4.3 | 3.2          | Conduction function - High frequency switch                                                       | . 44 |

| 4.4 | An           | alytical expressions for capacitor current stresses                                               | 45   |

| 4.4.1 Flying capacitor current stress                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4.2 DC-Link Capacitor current stress                                                                                                         |

| 4.5 Comparison of results with simulation                                                                                                      |

| 4.6 Conclusion                                                                                                                                 |

| CHAPTER 5: CONCLUSIONS AND FUTURE WORK                                                                                                         |

| 5.1 Contributions of Thesis                                                                                                                    |

| • Finite control set MPCC of three-level NPC converter with conditioning monitoring o DC-link capacitors                                       |

| • Analytical evaluation of capacitor current stress in five-level active neutral point clamper converter. 54                                   |

| 5.2 Scope of Future Work                                                                                                                       |

| 5.2.1 Switching State Grouped Finite Control Set MPCC of multi-level converters with<br>Condition Monitoring of DC-link Capacitors             |

| 5.2.2 Control of Nested Neutral Point Clamped Converter with Condition Monitoring o<br>DC-link Capacitors                                      |

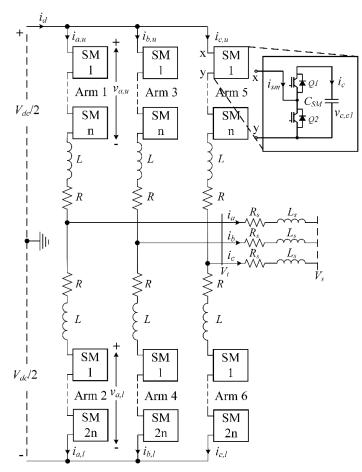

| 5.2.3 Finite Control Set Model Predictive Current Control of Modular Multileve<br>Converter with Condition Monitoring of Sub-Module Capacitors |

| REFERENCES                                                                                                                                     |

| LIST OF PUBLICATIONS                                                                                                                           |

# List of Tables

| Table 1.1 | Different condition monitoring schemes for different converters | 5  |

|-----------|-----------------------------------------------------------------|----|

| Table 2.1 | Switching state and voltage vectors 1                           | 2  |

| Table 3.1 | Switching states of inverter leg                                | 20 |

| Table 3.2 | Voltage vectors and switching states                            | 21 |

| Table 3.3 | Hardware specifications of prototype                            | 34 |

| Table 4.1 | Switching states for 5L-ANPC leg                                | 13 |

| Table 4.2 | Conduction function for low frequency operated switches         | 14 |

| Table 4.3 | Conduction function for flying capacitor                        | 15 |

| Table 4.4 | Peak stresses in capacitors at operating conditions             | 19 |

# **List of Figures**

| Figure 1.1 Single leg of basic MLI topologies for 5-level configuration                             | . 2 |

|-----------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 Division of multi-level inverter classes [3].                                            | . 3 |

| Figure 1.3 Classification of research efforts in direction of improving reliability                 | . 4 |

| Figure 2.1 Power electronics based system                                                           | . 8 |

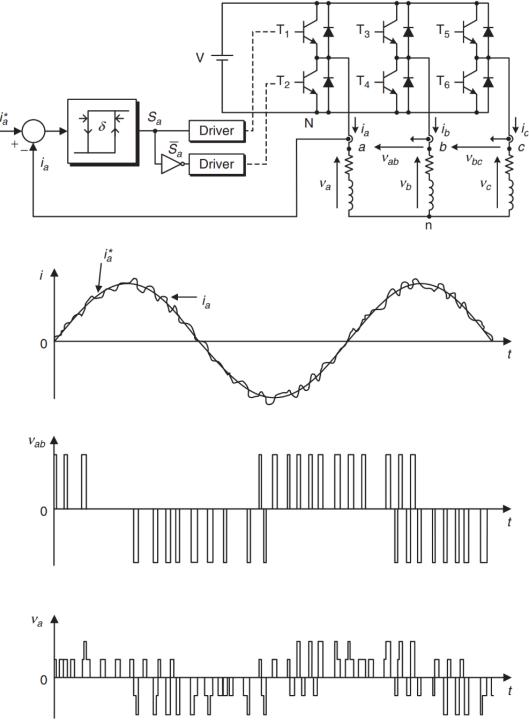

| Figure 2.2 Hysteresis current control of three-phase inverter [29].                                 | . 9 |

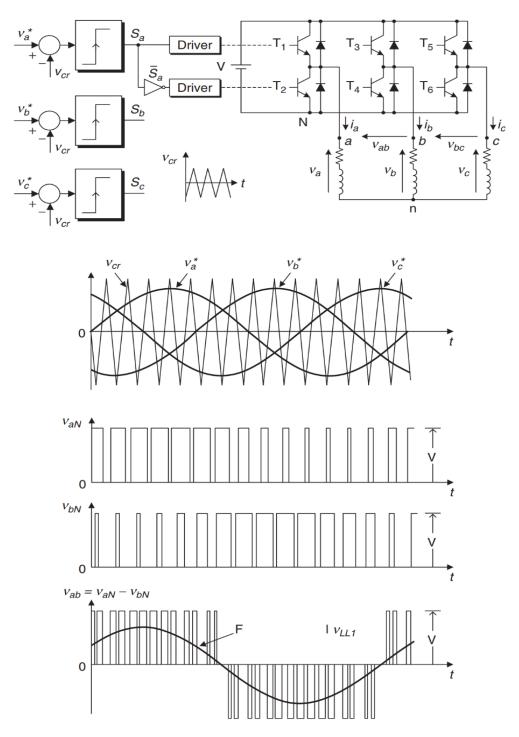

| Figure 2.3 Carrier based Pulse width modulator for a three-phase inverter [29].                     | 11  |

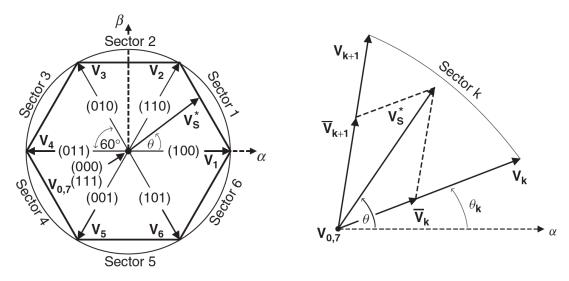

| Figure 2.4 Principles of space vector based modulation (a) Voltage vectors and sect definition.[29] |     |

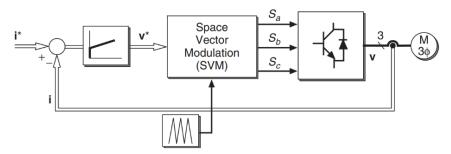

| Figure 2.5 Control scheme using Space Vector based Modulation [29].                                 | 13  |

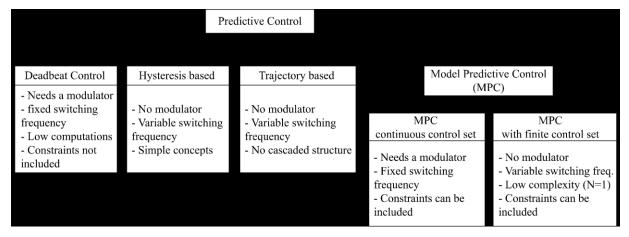

| Figure 2.6 Classification of predictive control techniques [32]                                     | 14  |

| Figure 2.7 Synchronous optimal modulation [38].                                                     | 16  |

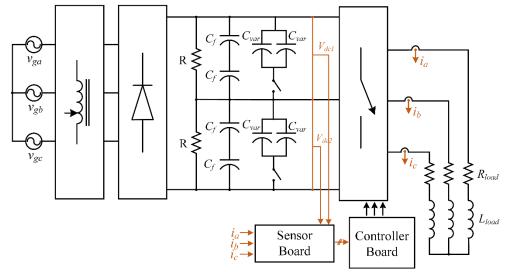

| Figure 3.1 Three-phase three-level neutral point clamped inverter power circuit                     | 20  |

| Figure 3.2 Circuit with phase - B connected to neutral point.                                       | 22  |

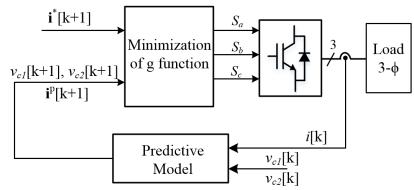

| Figure 3.3 Conventional Predictive Current Control for NPC Inverter                                 | 25  |

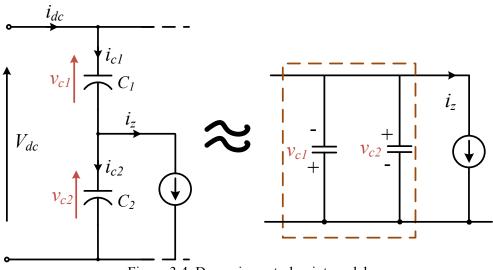

| Figure 3.4 Dynamic neutral point model                                                              | 26  |

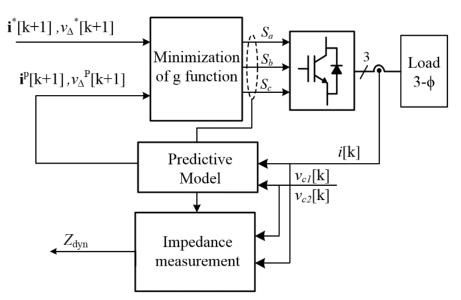

| Figure 3.5 FCS-MPCC of NPC inverter with Condition Monitoring                                       | 27  |

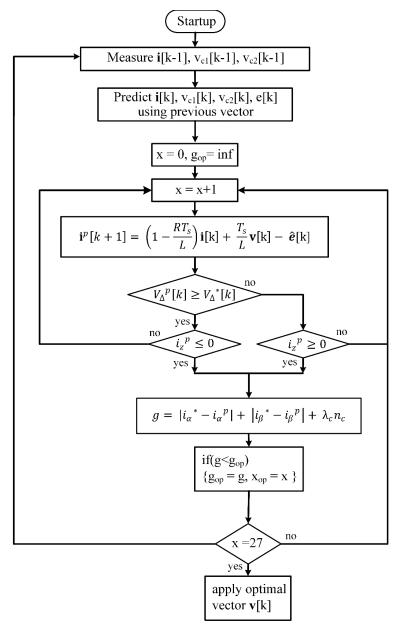

| Figure 3.6 Flow chart of predictive control algorithm with condition monitoring                     | 29  |

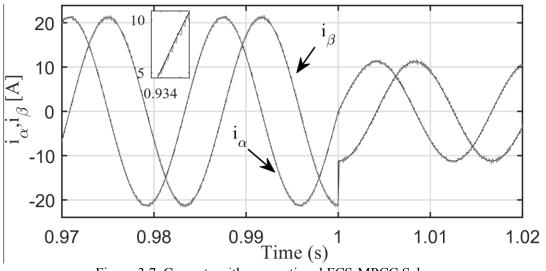

| Figure 3.7 Currents with conventional FCS-MPCC Scheme                                               | 31  |

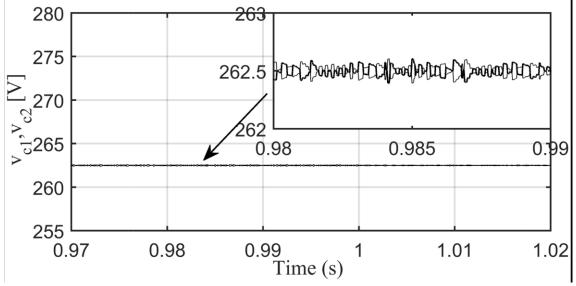

| Figure 3.8 Capacitor voltage control with FCS-MPCC                                                  | 31  |

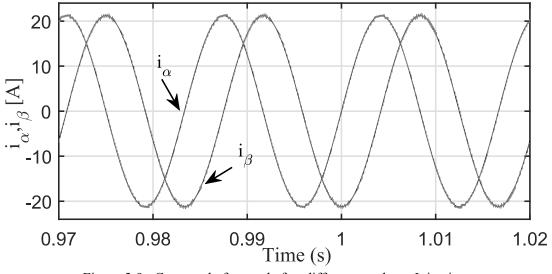

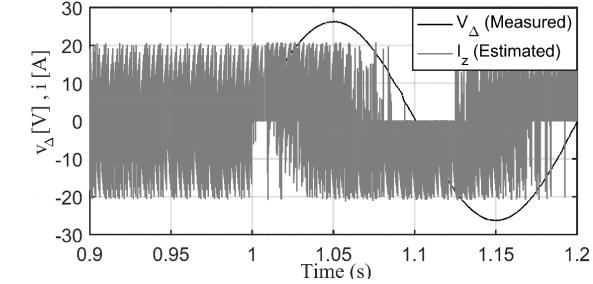

| Figure 3.9 Currents before and after difference voltage Injection                                   | 32  |

| Figure 3.10 Injected difference voltage and estimated neutral point current                         | 32  |

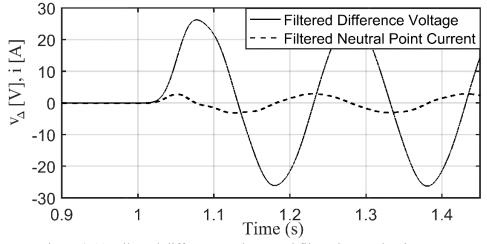

| Figure 3.11 Filtered difference voltage and filtered neutral point current                          | 33  |

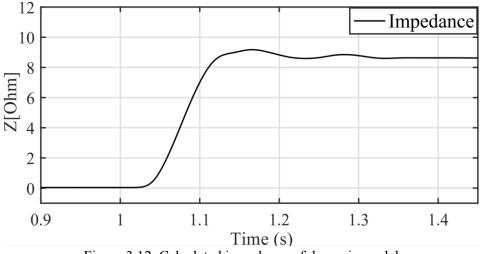

| Figure 3.12 Calculated impedance of dynamic model                                                   | 34  |

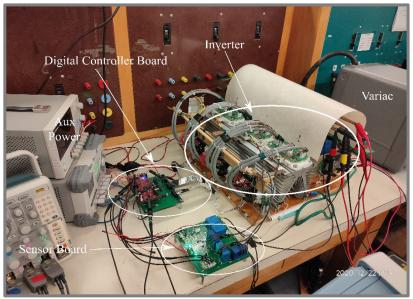

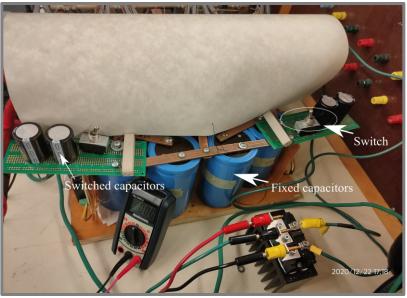

| Figure 3.13 3 kVA, three-level NPC inverter hardware prototype                                                                                                              | 35 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.14 Switched DC-link capacitor in hardware prototype                                                                                                                | 35 |

| Figure 3.15 Block diagram of hardware implementation with feedbacks                                                                                                         | 36 |

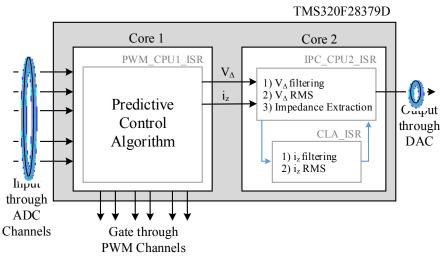

| Figure 3.16 Algorithm implemented in Digital Signal Processor                                                                                                               | 37 |

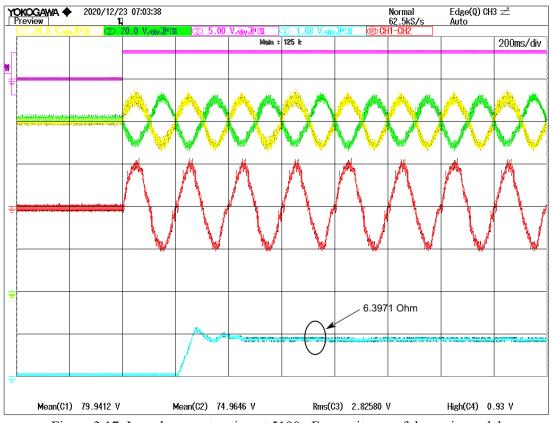

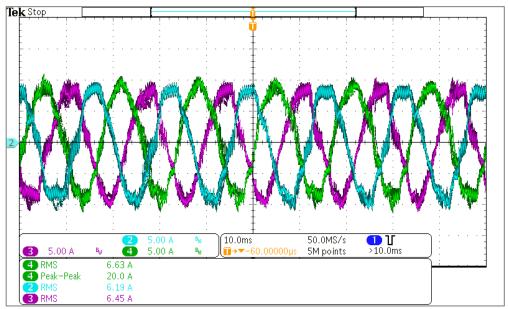

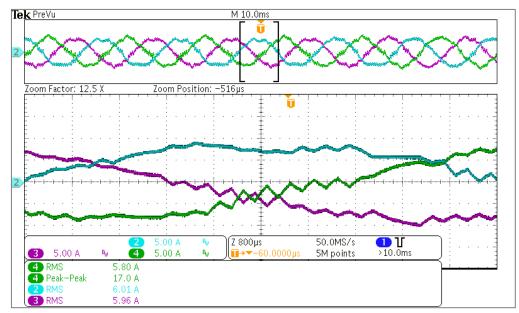

| Figure 3.17 Impedance extraction at 5100 uF capacitance of dynamic model                                                                                                    | 38 |

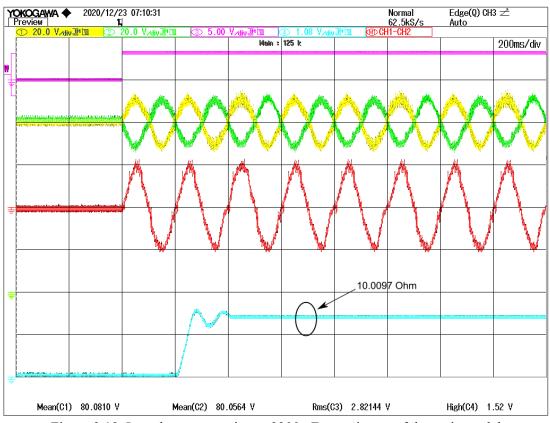

| Figure 3.18 Impedance extraction at 3300 uF capacitance of dynamic model                                                                                                    | 39 |

| Figure 3.19 Load Current during condition monitoring                                                                                                                        | 40 |

| Figure 3.20 Extensive control action leading to increased switching                                                                                                         | 40 |

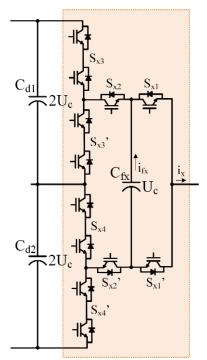

| Figure 4.1 Five level Active Neutral Point Clamped Converter leg                                                                                                            | 42 |

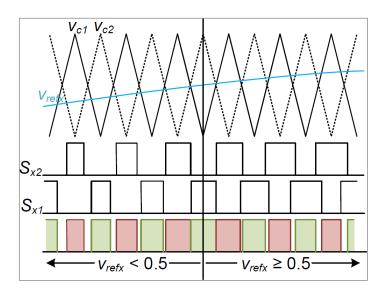

| Figure 4.2 Relation of flying capacitor conduction function with switching function                                                                                         | 44 |

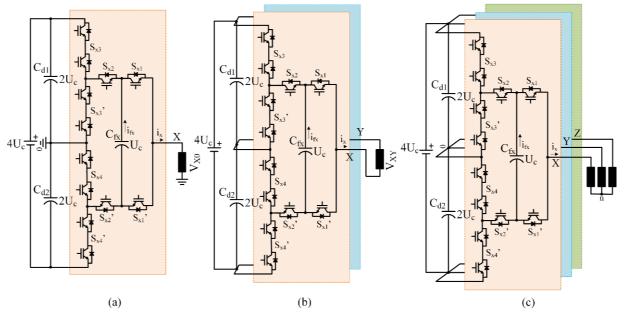

| Figure 4.3 5L-ANPC converter configurations                                                                                                                                 | 45 |

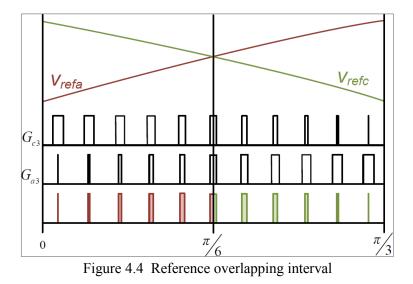

| Figure 4.4 Reference overlapping interval                                                                                                                                   | 48 |

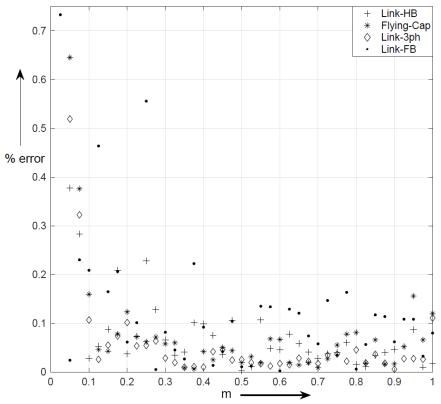

| Figure 4.5 Error in analytical expressions (modulation sweep)                                                                                                               | 50 |

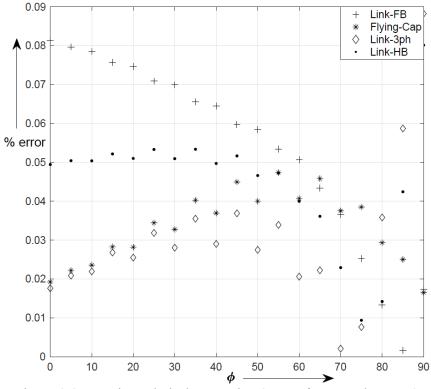

| Figure 4.6 Error in analytical expression (power factor angle sweep)                                                                                                        | 51 |

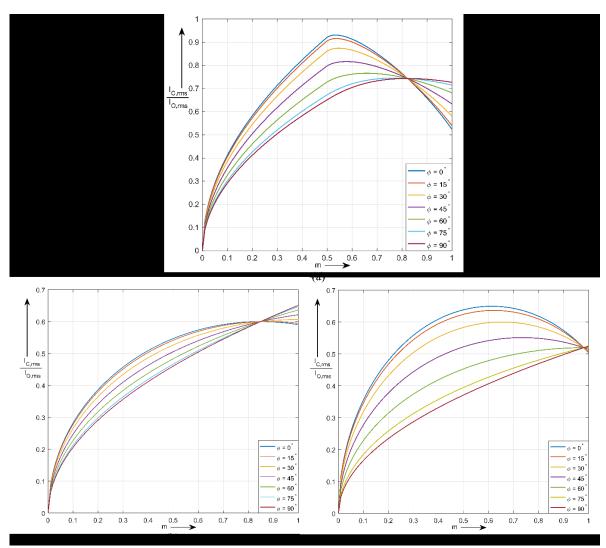

| Figure 4.7 Locus of capacitor current stress (a) flying-capacitor (b) DC-link capacitor in 1-p full-bridge configuration and (c) DC-link capacitor in 3-phase configuration |    |

| Figure 5.1 Flow chart of switching state grouped FCS-MPCC with condition monitoring                                                                                         | 55 |

| Figure 5.2 Nested neutral point clamped multilevel converter                                                                                                                | 56 |

| Figure 5.3 Modular multilevel converter topology                                                                                                                            | 57 |

# List of Abbreviations

| MLC      | Multi-Level Converters                              |

|----------|-----------------------------------------------------|

| HVDC     | High Voltage Direct Transmission                    |

| FACTS    | Flexible Alternating Current Transmission System    |

| ASD      | Adjustable Speed Drives                             |

| AFC      | Active Front-end Converters                         |

| CPD      | Custom Power Devices                                |

| REG      | Renewable Energy Generation                         |

| BESS     | Battery Energy Storage System                       |

| EV       | Electric Vehicles                                   |

| AEC      | Aluminum Electrolytic Capacitors                    |

| ESR      | Equivalent Series Resistance                        |

| MMCs     | Modular Multilevel Converters                       |

| SM       | Sub Module                                          |

| PWM      | Pulse Width Modulated                               |

| RLS      | Recursive Least Squared                             |

| FCS-MPCC | Finite Control Set Model Predictive Current Control |

| SVM      | Space Vector Modulation                             |

| MPC      | Model Predictive Control                            |

| NPC      | Neutral Point Clamped                               |

| MATLAB   | Matrix Lab                                          |

| IGBT     | Insulated Gate Bipolar Junction Transistors         |

| RMS      | Root Mean Square                                    |

| FIR      | Finite Impulse Response                             |

| ADC      | Analogue to Digital                                 |

| DAC      | Digital to Analogue                                 |

| ISR      | Interrupt Service Routine                           |

| CLA      | Control Logic Accelerator                           |

| IPC      | Inter Processor Communication                       |

| 5L-ANPC  | Five Level Active Neural Point Clamped              |

# List of Symbols

| S <sub>x</sub>                                  | Switch x / Switching state           |

|-------------------------------------------------|--------------------------------------|

| $v_a{}^*$ , $v_b{}^*$ , $v_c{}^*$               | Reference modulating voltage signals |

| v <sub>cr</sub>                                 | Carrier voltage signal               |

| $v_{ab}$                                        | Line-to-line inverter voltage        |

| $v_{aN}$                                        | Inverter phase voltage               |

| <b>v</b> *                                      | Reference voltage vector             |

| V                                               | Voltage vector                       |

| $T_c$                                           | Carrier period                       |

| heta                                            | Reference vector angle               |

| Ν                                               | Number of switching states           |

| D <sub>x</sub>                                  | Diode x                              |

| Z                                               | Neutral Point                        |

| $v_{c1}$ , $v_{c2}$                             | Capacitor voltages                   |

| $v_{\Delta}$                                    | Difference voltage                   |

| $i_a, i_b, i_c$                                 | Load Currents                        |

| i <sub>z</sub>                                  | Neutral point current                |

| L                                               | Load Inductance                      |

| R                                               | Load Resistance                      |

| i                                               | Load current vector                  |

| e                                               | Back emf vector                      |

| <i>i</i> <sub>c1</sub> , <i>i</i> <sub>c2</sub> | Capacitor currents                   |

| g                                               | Cost function                        |

| $\lambda_{dc}$ , $\lambda_n$                    | Weights                              |

| Z <sub>dyn</sub>                                | Dynamic model Impedance              |

| f <sub>inj</sub>                                | Injected Frequency                   |

| n <sub>c</sub>                                  | Number of commutations               |

| $v_{\Delta}^{*}$                                | Difference voltage reference         |

| V <sub>dc</sub> , U <sub>c</sub>                | DC-link voltage                      |

| VA                       | Volt amperes                                   |

|--------------------------|------------------------------------------------|

| $C_1, C_2$               | DC-link capacitors                             |

| kVA                      | Kilo volt amperes                              |

| $C_{\mathrm{fx}}$        | Flying-capacitor                               |

| G                        | Conduction function                            |

| m                        | Modulation index                               |

| ф                        | Load power factor angle                        |

| cosø                     | Load power factor                              |

| i <sub>cfx</sub>         | Instantaneous flying capacitor current         |

| Im                       | Maximum load current                           |

| Icfx                     | RMS flying capacitor current                   |

| i <sub>i-hb</sub>        | Instantaneous half-bridge capacitor current    |

| Ic-hb                    | RMS half-bridge capacitor current              |

| Iavg-hb                  | Average half bridge current                    |

| I <sub>c-fb</sub>        | RMS full-bridge capacitor current              |

| I <sub>avg-fb</sub>      | Average full bridge current                    |

| $I_{c-3\phi}$            | RMS three-phase DC-link capacitor current      |

| % error                  | Relative error                                 |

| I <sub>c,rms,1,sim</sub> | RMS capacitor current in Simulation            |

| I <sub>c,rms,1,eqn</sub> | RMS capacitor current by analytical expression |

## **CHAPTER 1: INTRODUCTION**

### **1.1 Introduction**

Electrical power available through the source is often different than the one desired by loads. This difference in form of electrical power is addressed by power electronics based power processing circuits. As the power handled by power processing circuits vary from few watts to mega-watts, the size of circuit and the semiconductor technology employed in them varies. A point of load power supply handling few watts of power are available in the form of integrated circuits which can be easily mounted on a printed circuit boards while a high voltage direct current (HVDC) based power transmission product handling mega-watts of power are available as an integrated system occupying large space. Though the integration size and power semiconductor device technology changes, the circuit configuration (electrical network) used to process electrical power more or less stays the same. These power processing circuits can be segregated into various classes based on the power converted from AC to DC, DC to DC, DC to AC or AC to AC. Multi-level converters is an important class of DC to AC conversion system generating AC voltage waveforms in form of a staircase. Multi-level converters (MLC) were developed to serve medium/high-power medium/high-voltage applications, by using low-voltage devices, because of limitation on the power semiconductor technology. Development of these converters led to the power electronic systems that have additional merits like better output voltage waveform quality, lower harmonic distortion of output and input currents, less dv/dt stress, reduced filter size, lower common-mode voltages and reduced electromagnetic interference [1, 2]. With advancement of semiconductor technology, analysis and integrating techniques multi-level structures are not only used for megawatt scale power electronic products like drives and HVDC, but are also used for low power ultracompact chip level class D-audio amplifier applications.

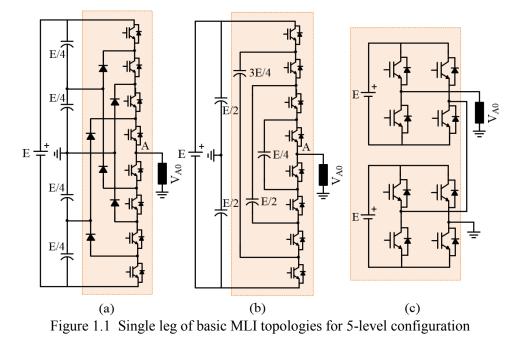

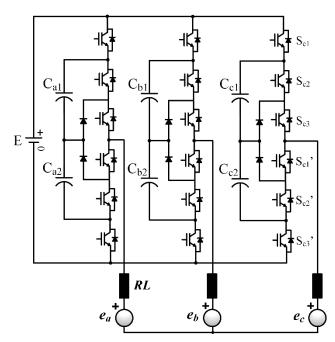

Basic configurations used to build MLC topologies include diode-clamped structure, flyingcapacitor and cascaded H-bridge configurations as shown in Figure 1.1. Now, these basic MLC configurations have evolved as a mature technology and are used for various commercial and customized products for a wide power range (1kW to several MW) of applications such as highvoltage direct-current (HVDC) transmission, flexible ac transmission systems (FACTS), adjustable speed drives (ASD), active front-end converters (AFC), custom power devices (CPD), battery energy storage systems

(BESS), electric vehicles (EV), renewable energy generation (REG), and more electric aircrafts [4-8]. Increased complexity of MLCs because of higher number of switching devices, which include complex control, uneven power distribution, reliability etc. These demerits have motivated researchers to find solutions based on basic MLC topologies. Various motivational factors that have contributed to research associated to the MLCs which can be listed as:

- **Converter Control:** Several control techniques of operating MLCs depending on application requirement.

- Fault tolerant ability: Fault tolerant ability enables the inverter to operate with abnormal working conditions such as faults on switching devices or dc sources, ensuring reliability with balanced operation.

- **Device Count:** To develop topology with appreciable reduction in device (switches/diodes/capacitors/dc-sources) count.

- **Requirement and Utilization of dc-sources:** Equal utilization of dc sources to contribute to the natural balancing of the DC-link voltages in closed loop applications. Reduction in dc source requirement increased the role of capacitors and thus, emerged self-balancing and voltage boosting topologies with and without galvanic isolation.

- **Device rating/ blocking voltages:** To develop the topology, involving identical device ratings and producing minimum device blocking voltages.

- Modularity: Topologies having modular configuration can easily be extended to higher levels.

- Even power distribution: Ability of the inverter to obtain required phase-voltage levels by distributing uniform power across all switches/units. This feature contributes to charge balance among the DC-link voltages.

- Application area: A critical analysis is carried out among the newly developed topologies in finding out its best application in the areas such as FACTS, HVDC, CPD, BESS, ASD, IPQC, EV and consumer electronics.

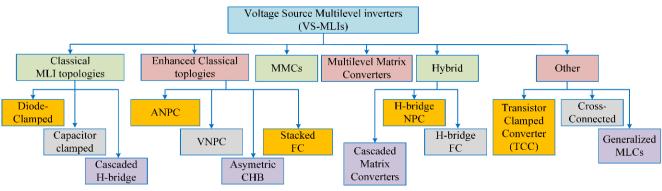

Extensive research activity enabled by stated motivational factors has resulted in proposal of numerous multilevel topologies and the methods to control them. Each of these topologies and its associated control having its own merits and demerits addresses specific application requirements. Thus, the classification of multilevel topologies available in literature is more or less based on the application requirements that mainly include number of phases, input to output isolation, voltage level boost, and availability of sources, power semiconductor switches connections and the symmetry of available voltage levels. Classification of MLC structures based on various circuit configurations is shown in Figure 1.2. [3]

Figure 1.2 Division of multi-level inverter classes [3].

## **1.2 Literature Review**

Basic and advanced MLC topologies essentially use multiple capacitors and power semiconductor switches connected in different configurations as basic building blocks. Due to the high capacitance per volume requirement and in order to reduce capacitor voltage ripple in the MLCs, aluminum electrolytic capacitors (AECs) are usually employed. Aluminum electrolytic capacitors

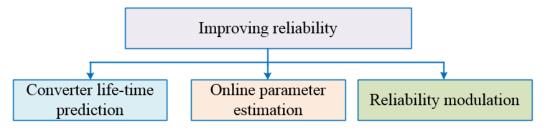

are subjected to wear-out failure due to vaporization of electrolyte and its loss over operational life [9]. According to load life test of capacitor manufacturers, a capacitor reaches end of its life-span when electrolyte is reduced by 40% or more. This 40% reduction in electrolyte can be translated into 20% reduction of capacitance from its initial value and 100% increase in equivalent series resistance (ESR). It is reported in literature that reduction in capacitance due to loss of electrolyte is responsible for the failure of power electronics system in 60% cases [10] forming weakest link in reliability context. A simple approach to improve system reliability would be to consider replacement of these capacitors when either of their electrical parameters bypass stated threshold levels of failure. Additionally, open-switch fault due to the lifting of bonding wire caused by the thermal cycling is a very common phenomenon [11]. Considering the reliability factors stated above, research efforts carried out to improve reliability of power electronic converters based systems can be segregated into three core areas as shown in Figure 1.3. Various techniques for the detection of open-switch fault are proposed, which involves sensing output voltages or load currents of converter. Open-switch fault ride through essentially involves bypassing the faulty path to operate the converter and hence, achieve desired voltage levels [12-14]. Offline methods have been proposed in [15, 16, 17] to evaluate the reliability of the converter in context to the life of capacitors. These methods involve the use of mission profile data along with probability theories to determine possible life time of capacitors. Online methods involve extraction of parameters by the sensing voltage and current components and thus predict health deterioration. Health deterioration is imperative to detect future system failure and replace failing devices before failure occurs.

Figure 1.3 Classification of research efforts in direction of improving reliability

During past years, research on monitoring health of AECs used in power converters has been conducted and reported in [18-28]. In [18], an analogue circuit is used to capture voltage ripples across the output capacitor of a fly-back converter. This information is fed to the mathematical model in a digital signal processor to evaluate capacitance C and Equivalent Series Resistance

(ESR). In [19], inductor current is used to evaluate ESR of capacitor connected between solar panel and a boost converter. In [20], health of output capacitor in a boost converter operating as a PFC rectifier is evaluated using C and the ESR calculation models. In [21], the ESR of DC-link capacitor employed in a three-phase two-level converter is evaluated by injecting controlled ac current components. In [22], voltage injection method with support vector regression technique is used to evaluate DC-link capacitance in three-phase AC/DC/AC converter system. A non-invasive technique, which uses information on charge stored in DC-link capacitor of H-bridge is proposed to evaluate health of a DC-AC grid connected converter system in [23]. A quasi online technique using least mean squared approach is proposed in [24] to evaluate capacitance of DC-link capacitor of single-phase solar inverter. A hardware based life-cycle monitoring and voltage-managing device for DC-link electrolytic capacitors in pulse-width modulation converters is presented in [25]. A condition monitoring scheme of the DC-link capacitors in Pulse Width Modulated (PWM) inverter-fed induction machine drives with front-end diode rectifiers using forced current injection and Recursive Least Squared (RLS) method is proposed in [26]. A failure prediction scheme for Sub-Module (SM) capacitors in the Modular Multilevel Converters (MMCs) by monitoring the SM capacitor voltage oscillations and hence, evaluating its impedance at twice the fundamental frequency is proposed in [27]. In [28], naturally circulating low frequency currents along with RLS algorithm is used to evaluate SM capacitance of MMCs. The summary of above referred capacitor health monitoring techniques proposed for different power converter configurations is listed in Table 1.1. Research work in context to the online condition monitoring of the capacitors is limited to the basic converter topologies or two-level bridge legs. Though efforts in the same direction are made for the MLCs, it is limited to MMC topologies only.

| Reference | Power Converter                  | Estimated<br>Parameter | Approach                                 |

|-----------|----------------------------------|------------------------|------------------------------------------|

| [18]      | Fly-back converter               | C and ESR              | Output voltage ripple                    |

| [19]      | DC/DC boost converter            | ESR                    | Inductor current ripple                  |

| [20]      | AC/DC boost converter            | C and ESR              | C and ESR calculation<br>model           |

| [21]      | $3-\phi$ 2-level AC/DC converter | ESR                    | Current injection with<br>RLS            |

| [22]      | 3-φ 2-level AC/DC/AC converter   | С                      | Voltage injection with<br>SVM regression |

Table 1.1 Different condition monitoring schemes for different converters

| [23] | 1-φ H-bridge 2-level<br>converter   | С         | Net charge calculation                                |

|------|-------------------------------------|-----------|-------------------------------------------------------|

| [24] | $1-\phi$ H-bridge 2-level converter | C and ESR | Voltage ripple with least mean square algorithm       |

| [25] | $3-\phi$ 2-level DC/AC converter    | ESR       | Ratio of average power<br>loss to capacitor current   |

| [26] | $3-\phi$ 2-level DC/AC converter    | С         | Current injection with<br>RLS method                  |

| [27] | [27] Modular Multilevel converter   |           | Low-frequency current<br>injection<br>with RLS method |

| [28] | Modular Multilevel converter        | С         | Second harmonic impedance extraction                  |

Out of the basic MLC topologies, three-level neutral-point clamped topology has found a noteworthy place as a basic building block in several commercial applications like adjustable speed drives, renewable energy grid integration, FACTS, solid state transformers, etc [1,2]. Therefore, possibility and a method of online health prediction of DC-link capacitors employed in a three-level converter as a basic block should be explored into. Sizing of DC-link capacitors is also an important aspect in system design for a specified application. Analytical expressions for the sizing of the capacitors aid as an important tool in initial design process.

## **1.3 Research Objectives**

The objective of this thesis is to investigate the possibility and development of a technique that can be directly integrated in power converter control method and use it for the online health monitoring of DC-link capacitors in a three-level neutral point clamped converter system. Proper design of the capacitor bank employed in a multi-level converter is an important aspect that ensures reliable converter operation over its expected life cycle. An extended objective also includes development of analytical equations which can be readily used for sizing capacitor banks.

The objectives of this thesis are to:

1) Investigate possibility of development of a model, which enables use of methods for evaluating health of DC-link capacitors in three-level neutral point clamped converter.

- 2) Develop online method for evaluating health of DC-link capacitors in three-level neutral point clamped converter.

- 3) Validate the method with a high performance control scheme in hardware.

- 4) Develop analytical tools that enables preliminary design of capacitor bank in multilevel converter topology.

An attempt to achieve these objectives is explained briefly in the next section and in detail in the subsequent Chapters.

## 1.4 Thesis Outline.

In Chapter 2, control methods for multi-level converters are explored and explained. Potential existing control methods which can be integrated with the condition monitoring technique are then identified. High performance multilevel converter control method for drives application is justified.

In Chapter 3, conventional Finite Control Set Model Predictive Current Control (FCS-MPCC) scheme for three-level diode clamped converter is explained. Then based on the developed dynamic neutral point model of split capacitor bank, an indirect method to inject controlled neutral point voltage deviation between two capacitors is embedded. This embedded scheme is simulated in MATLAB Simulink environment. Proposed concept is validated on a three-level neutral point clamped converter prototype.

In Chapter 4, mathematical expressions specifying conduction intervals of the capacitors in fivelevel active neutral point clamped converter considering sine-triangle PWM are defined. Analytical expressions for the current stress in capacitors based on the conduction intervals are derived. Analytical expressions are validated for the several operating points of converter in MATLAB Simulink environment.

In Chapter 5, recommendation for future work associated with the condition monitoring of DClink capacitors in three-level neutral point clamped converter system, a nested neutral point clamped converter system and MMC system is stated along with the conclusions of the thesis.

# CHAPTER 2: CONTROL METHODS FOR MULTILEVEL CONVERTERS

### 2.1 Introduction

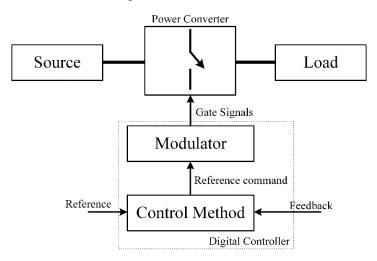

In a power electronic system, control of power flow is achieved by using a switching control logic implemented on a digital platform. A functional block diagram of a power electronic system is shown in Figure 2.1. A power converter control system encompasses a control method and its selection of which depends on the system constraints and technical specifications of the power converter. This Chapter reviews several control methods in their simplest forms that can be adopted in a multi-level converter. Classical hysteresis based current control, linear control that uses a carrier-based pulse width modulator (PWM) or space vector modulation (SVM), model predictive control (MPC), and an offline synchronous optimal control are studied. Finally, potential control methods to predict health of DC-link capacitors in three-level neutral point clamped converter are identified and explored in last section.

Figure 2.1 Power electronics based system

## 2.2 Hysteresis Current Control

The elementary concept of a hysteresis current control is to keep load current within the hysteresis limits by changing switching states of the switching devices of the converter whenever the load current moves out of the boundary [29, 30]. Figure 2.2 shows hysteresis control scheme for a three-phase two-level inverter. Sensed load current of each phase are compared with the references using

hysteresis comparator, which accepts current error as the input. Each comparator decides the switching states of the respective inverter leg devices ( $S_a$ ,  $S_b$ ,  $S_c$ ) in such a way that the load currents are forced to stay within the limits of the hysteresis band.

Figure 2.2 Hysteresis current control of three-phase inverter [29].

This control method is conceptually very simple, effective and its implementation avoids the use of complex circuits or digital processors. As far as dynamic performance is concerned, hysteresis controller is stable. The major drawback of hysteresis current control is that the switching frequency varies with the variation in the hysteresis width, load current, and the operating voltage conditions. Variable switching frequency can cause resonance problems. If this scheme is implemented in a digital controller, sampling frequency is required to be very high in order to keep the controlled variables within hysteresis band all the times.

### 2.3 Linear Control Method

If generation of gate control signals for the power semiconductor switches is considered using a pulse width modulator stage, one can linearize inherently nonlinear power converter. This enables control method to use a proportional – integral (PI) compensator for error compensation [31].

#### 2.3.1 Carrier based Pulse Width Modulation

In a carrier based PWM, the reference voltage signal is compared with a carrier signal (triangular or saw-tooth waveform) and the output of the comparator is used to modulate the switching state of the power semiconductor switches. For a three-phase inverter, the reference voltage of each corresponding phase is compared with the carrier voltage, thus generating the switching states for the corresponding inverter leg. Figure 2.3 shows the comparison process where  $v_a^*$ ,  $v_b^*$  and  $v_c^*$ are the sinusoidal three-phase reference voltages and  $v_{cr}$  is triangular carrier voltage. At any instant of time, when reference voltage is greater than carrier voltage gating signal for top switch  $S_x$  (x = a, b, c) is turned-on and turned-off when reference voltage is smaller than carrier voltage. Bottom switches for each leg operate in complement with the top switches along an appropriate dead-band. Operation of switches produces pole voltages, and line-to-line voltages  $v_{ab}$  which are shown in Figure 2.3.

#### 2.3.2 Linear control method using Space Vector based Modulation

SVM is a type of PWM scheme, which is based on the vectorial representation of the three-phase voltages. Each voltage vector duration is calculated from the reference vector generated as command from the linear regulator. Inverter output voltages represented as vector is defined by

$$\mathbf{v} = \frac{2}{3}(v_{aN} + av_{bN} + a^2 v_{cN})$$

(2.1)

Where  $\mathbf{a} = e^{j2\pi/3}$  and  $v_{aN}$ ,  $v_{bN}$  and  $v_{cN}$  are phase-to-neutral voltages of the inverter. The output voltage of each inverter leg depends on its switching state and the voltage available on DC-link.

Figure 2.3 Carrier based Pulse width modulator for a three-phase inverter [29].

On accounting the switching states combination for the three-phase system, a three-phase twolevel inverter generates the voltage vectors listed in Table 2.1and presented in Figure 2.4(a).

| Sa | Sb | Sc | Voltage vector V                                       |

|----|----|----|--------------------------------------------------------|

| 0  | 0  | 0  | $V_0 = 0$                                              |

| 1  | 0  | 0  | $V_1 = \frac{2}{3}V_{dc}$                              |

| 1  | 1  | 0  | $V_2 = \frac{1}{3}V_{dc} + j\frac{\sqrt{3}}{3}V_{dc}$  |

| 0  | 1  | 0  | $V_3 = -\frac{1}{3}V_{dc} + j\frac{\sqrt{3}}{3}V_{dc}$ |

| 0  | 1  | 1  | $V_4 = -\frac{2}{3}V_{dc}$                             |

| 0  | 0  | 1  | $V_5 = -\frac{1}{3}V_{dc} - j\frac{\sqrt{3}}{3}V_{dc}$ |

| 1  | 0  | 1  | $V_6 = \frac{1}{3}V_{dc} + j\frac{\sqrt{3}}{3}V_{dc}$  |

| 1  | 1  | 1  | $V_7 = 0$                                              |

Table 2.1 Switching state and voltage vectors

Figure 2.4 Principles of space vector based modulation (a) Voltage vectors and sector definition.[29]

Regions between each voltage vector can be considered as a sector. Hence,  $\alpha - \beta$  plane can be divided into six sectors as shown in Figure 2.4(a). Based on the concept of voltage time balance, a given reference voltage vector generated by linear controller v\*, located in a particular sector k,

can be synthesized using adjacent vectors  $V_k$ ,  $V_{k+1}$ , and  $V_0$  which are applied for durations  $t_k$ ,  $t_{k+1}$ , and  $t_0$ , respectively. This can be presented in the form of an equation as:

$$\mathbf{v}^* = \frac{1}{T_c} (\mathbf{V}_k t_k + \mathbf{V}_{k+1} t_{k+1} + \mathbf{V}_0 t_0)$$

(2.2)

$$T_c = t_k + t_{k+1} + t_0 \tag{2.3}$$

where  $T_c$  represents carrier duration and  $t_k/T_c$ ,  $t_{k+1}/T_c$  and  $t_0/T_c$  are the duty cycles of their respective vectors. Using vector co-relation, the application time for each vector can be calculated as:

$$t_k = \frac{3T_c |\mathbf{v}^*|}{2V_{dc}} \left( \cos(\theta - \theta_k) - \frac{\sin(\theta - \theta_k)}{\sqrt{3}} \right)$$

(2.4)

$$t_{k+1} = \frac{3T_c |\mathbf{v}^*|}{V_{dc}} \frac{\sin(\theta - \theta_k)}{\sqrt{3}}$$

(2.5)

$$t_0 = T_c - t_k - t_{k+1} \tag{2.6}$$

Where  $\theta$  corresponds the angle of reference vector  $\mathbf{v}^*$  and  $\theta_k$  is the angle of vector  $\mathbf{V}_k$ .

A conventional current control scheme using space vector based PWM scheme is shown in Figure 2.5. A PI controller processes the error between the load current vector and the reference current vector to generate a reference load voltage vector.

Figure 2.5 Control scheme using Space Vector based Modulation [29].

Linear control method obtains constant switching frequency by a fixed carrier waveform. The steady-state and dynamic performance of this control scheme depends on the controller parameters and on frequency of the reference current. A PI controller assures zero steady-state error for continuous reference frames. However, it presents a notable error for sinusoidal reference quantities. To overcome the problem of a PI controller compensation with sinusoidal references, a common solution is to use the present scheme after transferring coordinates from stationary to rotating reference frame in which the reference currents are converted into constant values.

## 2.4 Predictive Control Method.

Predictive control method encompasses a wide variety of controllers that find applications in power electronics based systems. Classification of various predictive control methods shown in Figure 2.6 is reported in [32]. Predictive control uses model of the system to predict future values of controlled variables. Predicted values of the controlled variables are used as the inputs to the controller, produce optimal actuation signals depending on the optimization criterion. In a trajectory based control, the variables are forced to follow a defined trajectory [33] while in a hysteresis based predictive control, optimization criteria is to keep the controlled variable in the limits of hysteresis band [34]. Optimal actuation in a deadbeat control makes error equal to zero in the next sampling interval [35,36]. Model predictive control (MPC) uses a flexible criterion, which is expressed as a cost function to be minimized [37]. Out of classified predictive control methods, deadbeat control and MPC with continuous control set uses a modulator while other controllers directly generate switching signals for the semiconductor switching devices. Controllers using the modulators will have constant switching frequency while controllers directly generating switching signals will have a variable switching frequency. Recently, medium/high power electronic systems are subjected to several system constraints and technical requirements like total harmonic distortion (THD), maximum current, maximum switching frequency, etc. All these constraints cannot be employed in modulator-based control schemes [38]. A simplified variant of MPC called finite control set MPC uses discrete nature of power electronic converters that simplifies the optimization problem, does not need a modulator and can be implemented online easily.

Figure 2.6 Classification of predictive control techniques [32].

#### 2.4.1 Finite Control Set Model Predictive Control

Design stage of finite control set MPC for the control of power electronics based system involves several steps which are listed as follows:

- Modeling the power converter in terms of all possible switching states and its co-relation to the voltages and currents.

- Defining control cost function, which presents system behavior.

- Obtain discrete-time equivalent models that allow the prediction of controlled variables.

Modeling power converter involves considering power semiconductor switches operating in two discrete states, ON and OFF state. Therefore, the total number of possible switching states for a power electronic converter depends upon the number of different combinations of switching states for each semiconductor switch. Combinations that lead to the short circuit of DC-link are excluded. A general rule stating number of possible switching states N can be stated as

$$N = x^{\mathcal{Y}} \tag{2.7}$$

where, x represents possible states of each converter leg, and y is number of phases (or legs). Every application defines its own control requirements such as current control, voltage control, torque control, switching frequency constraints, etc. These requirements are expressed in the form of a cost function. A digital controller calculates optimal switching states, which minimizes this cost function. Though the elementary cost function to be defined is a measure of error between reference and predicted variables, it is possible to control different types of variables by including restrictions in the cost function. Discrete-time equivalents of a system model for prediction are obtained by using forward Euler method. System constraints such as low harmonic distortion, low device switching frequency and fast dynamic responses are achieved simultaneously using this method. A control technique, which achieves these constraints simultaneously using an offline modulation is worth noting and explained briefly in the next section.

## 2.5 Synchronous Optimal Control

Synchronous optimal control technique is developed specifically for motor drives applications. Similar to linear control methods, synchronous optimal control method uses linear regulators to achieve control of load variables.

### 2.5.1 Synchronous Optimal Pulse Width Modulation

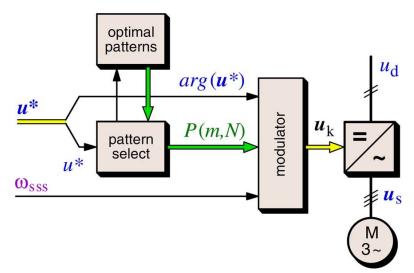

To implement synchronous optimal PWM, sequences of switching state vector and their dwell time duration are pre-calculated for the entire range of the modulation index m. It is to be noted that this sequence forms a pulse pattern, which is repeated every fundamental cycle. Calculations are usually done offline, assuming steady-state operation and satisfying specified optimization criterion [39]. Optimization criterions include current distortion, switching losses and switch utilization. Block diagram of a synchronous optimal PWM is shown in Figure 2.7. Pre-calculated pulse patterns for all the operating conditions are saved in a form of a look-up table. Depending upon the modulation command coming from the control system, a pulse pattern is loaded and pulses are generated with specified dwell times in a sequence.

Figure 2.7 Synchronous optimal modulation [38].

This modulation technique inherently satisfies simultaneous requirements of lower harmonic distortion, and the device switching losses. One disadvantage of this modulation technique in its simplest form is in terms of dynamic performance as it is not able to maintain optimal pulse pattern during dynamic conditions. However, this disadvantage is overcome with advanced control methods [38].

## 2.6 Potential Control Methods for Online Condition Monitoring

Considering the objective of online health monitoring of DC-link capacitors in a three-phase threelevel neutral point clamped converter operated as an inverter using dynamic neutral point model, the following advanced control methods listed below have potential application.

- Linear control method based on carrier PWM proposed in [40]. In this method, two DClink capacitor voltages are balanced by use of a proportional regulator, which introduces an offset voltage proportional to degree of unbalance in the modulating signal used as a reference in carrier based PWM method. To ensure balanced capacitor voltages, reference to this regulator is zero. If the reference to the regulator is non-zero ie. A sinusoidal low frequency low amplitude quantity, the difference between two capacitor voltages will follow the same reference and hence provide ability to monitor health in terms of capacitance of dynamic neutral point model.

- Linear control method based on SVM proposed in [41]. In this control method, a space

vector based modulation method is proposed where simultaneous voltage control, neutral

point voltage control and switching loss reduction is achieved. Like carrier based control

method, this modulation method has a potential for injecting sinusoidal DC-link capacitor

voltage difference and hence ability of online condition monitoring.

- Finite control set model predictive control proposed in [42]. It uses model of a three-phase three-level neutral-point clamped converter. The cost function g is designed to include terms dedicated to achieve reference tracking, voltage balance in the DC-link, and reduction of device switching frequency. Importance of control variables in cost function is adjusted using respective weights. Inclusion of neutral point voltage control in the cost function and the ability to adjust its relative importance using weights makes this method a potential candidate to be used for online condition monitoring technique.

## 2.7 Conclusion

In this Chapter, various control methods, which have been used for the multi-level converters in their simplest form are reviewed. Out of these methods, and based on the condition monitoring requirement, potential control methods, which can readily utilize the dynamic neutral point model

are listed. Linear control method based on SVM provides high dynamic performance compared to the methods based on the carrier PWM. But ongoing continuous requirement on the reduction in harmonic distortion and reduction of device switching frequency with high dynamic performance in applications such as electric drives, linear control method with SVM is not sufficient enough. Synchronous optimal PWM method satisfies all the requirements of low harmonic distortion in load current and reduced device switching frequency while maintaining attribute of high dynamic performance. It achieves these desirable merits due to utility of linear regulators in control stage and utility of look-up table stored highly optimized pulse patterns. Reliability of multi-level converters depends on reliability of switches, gate driving circuitry and the energy storage elements viz. Aluminum electrolytic capacitors. Since bond wire failure of semiconductors in switches is addressed by reliability modulation and gate driving circuitry is robust due to use of advanced electronics circuitry, capacitors form the weakest link in reliability context. Online condition monitoring techniques requires timely injection of sinusoidal current/ voltage components. Use of offline look-up table limits integration of online condition monitoring in synchronous optimal control method. Finite control set model predictive control is simple, online and retains all desirable qualities like synchronous optimal PWM control. Due to high dynamic performance while retaining implementation simplicity this control technique is often found in Industrial applications. The concept of online health monitoring of DC-link capacitors used in three-phase three-level neutral point clamped converter is explored using finite control set model predictive control scheme.

The next Chapter introduces the concept of finite control set model predictive current control (MPCC) for three-level neutral point clamped converter operated as an inverter and explains the online condition monitoring concept embedded with this control method.

# CHAPTER 3: A FINITE CONTROL SET MODEL PREDICTIVE CURRENT CONTROL OF 3-LEVEL NEUTRAL POINT CLAMPED CONVERTER WITH CONDITIONING MONITORING OF DC-LINK CAPACITORS.

## 3.1 Introduction

This chapter presents a Finite Control Set (FCS) Model Predictive Current Control (MPCC) scheme for a 3-level neutral point clamped (NPC) converter with condition monitoring of DC-link capacitors by evaluating impedance of dynamic neutral point model. First section describes mathematical modeling of three-level neutral point clamped inverter and connected load. Control design process of FCS-MPCC is presented in second section. Third section presents embedding of proposed condition monitoring method with FCS-MPCC. Proposed method is validated using MATLAB Simulink simulation environment in fourth section. Implementation and validation of the concept with laboratory developed hardware prototype is presented in the last section.

## 3.2 Mathematical Modeling

One of the elementary steps in designing FCS-MPCC for a power electronic system involves deriving model equations that represents behavior of the system. Since power electronic converter system is non-linear due to power semiconductors operating in ON-OFF states (saturated - cutoff regions), a power converter model can be derived using possible switching state combinations. Differential equations presenting a generic load model can be developed considering that the converter is connected to a three-phase balanced series connected resistive inductive and ac voltage source (RLE) load configuration.

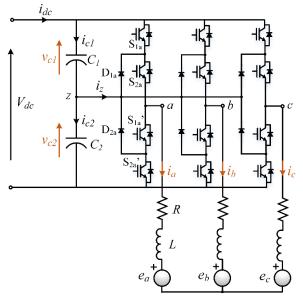

### 3.2.1 Power Converter Model

Figure 3.1 shows a three-phase three-level NPC inverter circuit that converts electrical power from DC to AC form through power semiconductor switching devices (IGBTs). Each inverter leg consists of four active switches (IGBTs) and two clamping diodes where inner switches ( $S_{2x}, S_{1x}'$ )

and clamping diodes  $(D_{1x}, D_{2x})$  enable the converter output terminal to be connected to the neutral point (z) of the DC-link.

Figure 3.1 Three-phase three-level neutral point clamped inverter power circuit

Neutral point is obtained through midpoint of two series connected DC-link capacitors. Operation of each switch is represented by its switching function as,

$$S_{xy} = \begin{cases} 1, & \text{when switch is conducting} \\ 0, & \text{when switch is blocking} \end{cases}$$

(3.1)

The switching state variable  $S_x$  represents the switching state of phase x, with  $x = \{a, b, c\}$ . Considering switching states as stated in Table 3.1, switching state variable can take three values denoted by P, O and N that represent the switching combinations. This circuit configuration allows generation of three voltage levels at the output terminal with respect to neutral point (z). To account for the variation in neutral-point voltage and its effects, inverter leg voltages are represented in terms of voltage across capacitors instead of absolute values of DC link voltages. Forced variation of neutral-point voltage is essential for the requirements of condition monitoring aspect of the scheme which will be explained in the chapter later.

| S <sub>x</sub> | $S_{x1}$ | S <sub>x2</sub> | $S_{x1}$ ' | S <sub>x2</sub> ' | V <sub>XZ</sub>  |

|----------------|----------|-----------------|------------|-------------------|------------------|

| Р              | 1        | 1               | 0          | 0                 | V <sub>c1</sub>  |

| 0              | 0        | 1               | 1          | 0                 | 0                |

| N              | 0        | 0               | 1          | 1                 | -V <sub>c2</sub> |

Table 3.1 Switching states of inverter leg

The pole voltage defined as voltage between the load terminal and the neutral point of DC-link for each inverter leg can be written by (3.2), (3.3) and (3.4) as,

$$v_{az} = S_{a1}v_{c1} + (S_{a2} - 1)v_{c2} \tag{3.2}$$

$$v_{bz} = S_{b1}v_{c1} + (S_{b2} - 1)v_{c2} \tag{3.3}$$

$$v_{cz} = S_{c1}v_{c1} + (S_{c2} - 1)v_{c2} \tag{3.4}$$

where,  $v_{c1}$ ,  $v_{c2}$  are the voltages across the two capacitors. Operation of each inverter leg is phase-shifted by 120°, therefore, using an unitary vector,  $\mathbf{a} = e^{j2\pi/3}$  inverter output voltage can be written in vector form as,

$$\mathbf{v} = \frac{2}{3}(v_{az} + \mathbf{a}v_{bz} + \mathbf{a}^2 v_{cz})$$

(3.5)

Three phases and three possible switching states for each converter leg results in 27 unique switching state combinations. Let us consider a switching state combination  $(S_a, S_b, S_c) = (P, N, O)$ , the output voltage vector corresponding to specified switching state combination can be derived as,

$$\mathbf{V}_{PNO} = \frac{2}{3} \left( V_{c1} e^{j0} - V_{c2} e^{\frac{j2\pi}{3}} + 0 e^{\frac{j4\pi}{3}} \right) \\ = \left( \frac{2V_{c1}}{3} + \frac{V_{c2}}{3} \right) - j \frac{1}{\sqrt{3}} (V_{c2})$$

(3.6)

Likewise, voltage vector for every possible switching state combination can be evaluated. The voltage vector for all switching state combinations are stated in Table 3.2. Each voltage vector can be represented by a distinct location in a two-dimensional complex plane.

| Space<br>Vector       | Switching<br>State     | Vector Definition                  | Vector Definition<br>$(V_{c1} = V_{c2} = V_{dc}/2)$ |

|-----------------------|------------------------|------------------------------------|-----------------------------------------------------|

| $\mathbf{V}_0$        | [PPP], [OOO],<br>[NNN] | 0 + j 0                            | 0 + <i>j</i> 0                                      |

| $\mathbf{V}_1$        | [PPO]                  | $2V_{cl}/3 + j 0$                  | $V_{dc}/3 + j 0$                                    |

| $\mathbf{V}_2$        | [ONN]                  | $2V_{c2}/3 + j 0$                  | $V_{dc}/3 + j 0$                                    |

| <b>V</b> <sub>3</sub> | [PPO]                  | $V_{cl}/3 + j(1/\sqrt{3})V_{cl}$   | $V_{dc}/6 + j (1/2\sqrt{3})V_{dc}$                  |

| $V_4$                 | [OON]                  | $V_{c2}/3 + j (1/\sqrt{3})V_{c2}$  | $V_{dc}/6 + j (1/2\sqrt{3})V_{dc}$                  |

| $V_5$                 | [OPO]                  | $-V_{cl}/3 + j (1/\sqrt{3})V_{cl}$ | $-V_{dc}/6 + j (1/2\sqrt{3})V_{dc}$                 |

| $V_6$                 | [NON]                  | $-V_{c2}/3 + j (1/\sqrt{3})V_{c2}$ | $-V_{dc}/6 + j (1/2\sqrt{3})V_{dc}$                 |

| $\mathbf{V}_7$        | [OPP]                  | $-2V_{cl}/3 + j 0$                 | $-V_{dc}/3 + j 0$                                   |

| $V_8$                 | [NOO]                  | $-2V_{c2}/3 + j 0$                 | $-V_{dc}/3 + j 0$                                   |

Table 3.2 Voltage vectors and switching states

| V <sub>9</sub>         | [OOP]          | $-V_{cl}/3 - j (1/\sqrt{3})V_{cl}$                   | $-V_{dc}/6 - j (1/2\sqrt{3})V_{dc}$  |

|------------------------|----------------|------------------------------------------------------|--------------------------------------|

| $\mathbf{V}_{10}$      | [001]<br>[NNO] | $-V_{c2}/3 - j(1/\sqrt{3})V_{c2}$                    | $-V_{dc}/6 - j(1/2\sqrt{3})V_{dc}$   |

| -                      | L 3            |                                                      |                                      |

| <b>V</b> <sub>11</sub> | [POP]          | $V_{cl}/3 - j(1/\sqrt{3})V_{cl}$                     | $V_{dc}/6$ - $j (1/2\sqrt{3})V_{dc}$ |

| <b>V</b> <sub>12</sub> | [ONO]          | $V_{c2}/3 - j(1/\sqrt{3})V_{c2}$                     | $V_{dc}/6$ - $j (1/2\sqrt{3})V_{dc}$ |

| <b>V</b> <sub>13</sub> | [PON]          | $(2V_{c1}+V_{c2})/3+j(1/\sqrt{3})V_{c2}$             | $V_{dc}/2 + j (1/2\sqrt{3})V_{dc}$   |

| $V_{14}$               | [OPN]          | $(-V_{c1}+V_{c2})/3+j(1/\sqrt{3})(V_{c1}+V_{c2})$    | $0 + j (1/\sqrt{3}) V_{dc}$          |

| $V_{15}$               | [NPO]          | $(-V_{c1} - 2V_{c2})/3 + j (1/\sqrt{3})V_{c1}$       | $-V_{dc}/2 + j (1/2\sqrt{3})V_{dc}$  |

| $V_{16}$               | [NOP]          | $(-V_{c1} - 2V_{c2})/3 - j(1/\sqrt{3})V_{c1}$        | $-V_{dc}/2 - j (1/2\sqrt{3})V_{dc}$  |

| $V_{17}$               | [ONP]          | $(-V_{c1}+V_{c2})/3 - j (1/\sqrt{3})(V_{c1}+V_{c2})$ | $0 - j (1/\sqrt{3}) V_{dc}$          |

| $V_{18}$               | [PNO]          | $(2V_{c1}+V_{c2})/3 - j(1/\sqrt{3})V_{c2}$           | $V_{dc}/2 - j (1/2\sqrt{3})V_{dc}$   |

| <b>V</b> 19            | [PNN]          | $(2V_{c1}+2V_{c2})/3+j 0$                            | $2V_{dc}/3 + j 0$                    |

| $V_{20}$               | [PPN]          | $(V_{cl}+V_{c2})/3+j(1/\sqrt{3})(V_{cl}+V_{c2})$     | $V_{dc}/3 + j (1/\sqrt{3})V_{dc}$    |

| $V_{21}$               | [NPN]          | $-(V_{c1}+V_{c2})/3+j(1/\sqrt{3})(V_{c1}+V_{c2})$    | $-V_{dc}/3 + j (1/\sqrt{3})V_{dc}$   |

| <b>V</b> <sub>22</sub> | [NPP]          | $-(2V_{c1}+2V_{c2})/3+j 0$                           | $-2V_{dc}/3 + j 0$                   |

| <b>V</b> <sub>23</sub> | [NNP]          | $-(V_{c1}+V_{c2})/3 - j(1/\sqrt{3})(V_{c1}+V_{c2})$  | $-V_{dc}/3 - j (1/\sqrt{3})V_{dc}$   |

| <b>V</b> <sub>24</sub> | [PNP]          | $(V_{c1}+V_{c2})/3 - j(1/\sqrt{3})(V_{c1}+V_{c2})$   | $V_{dc}/3 - j (1/\sqrt{3}) V_{dc}$   |

Use of additional voltage level generated from series connected DC-link capacitor causes deviation in the voltages across the two capacitors. One such case when phase - B is connected to the neutral point (z) is shown in Figure 3.2. Upper and lower capacitors may charge or discharge depending on neutral point current direction.

Figure 3.2 Circuit with phase - B connected to neutral point.

The equation governing the neutral point current and the voltage difference between two capacitors is given by (3.7) and (3.8) respectively,

$$i_{Z} = (1 - S_{a1})S_{a2}i_{a} + (1 - S_{b1})S_{b2}i_{b} + (1 - S_{c1})S_{c2}i_{c}$$

(3.7)

$$\frac{dv_{\Delta}}{dt} = \frac{1}{C_1 + C_2} \, i_Z \tag{3.8}$$

where,  $v_{\Delta} = v_{C1} - v_{C2}$ .

#### 3.2.2 Load Model

Accounting a generalized load model connected to inverter circuit as shown in Figure 3.1, differential equation that presents correlation of inverter phase voltage and dynamics of load current can be stated by,

$$v_{aZ} = L\frac{di_a}{dt} + Ri_a + e_a + v_{nZ}$$

(3.9)

$$v_{bZ} = L \frac{di_b}{dt} + Ri_b + e_b + v_{nZ}$$

(3.10)

$$v_{aZ} = L\frac{di_c}{dt} + Ri_c + e_c + v_{nZ}$$

(3.11)

By substituting (3.9)-(3.11) into (3.5) a vector representation of (3.9)-(3.11) can be written as

$$\mathbf{v} = L \frac{d}{dt} \left( \frac{2}{3} (i_a + \mathbf{a} i_b + \mathbf{a}^2 i_c) \right) + R \left( \frac{2}{3} (i_a + \mathbf{a} i_b + \mathbf{a}^2 i_c) \right) + \frac{2}{3} (e_a + \mathbf{a} e_b + \mathbf{a}^2 e_c) + \frac{2}{3} (v_{nz} + \mathbf{a} v_{nz} + \mathbf{a}^2 v_{nz})$$

(3.12)

Thus inverter voltage vector v, load current vector i and emf vector e can be correlated as

$$\mathbf{v} = R\mathbf{i} + L\frac{d\mathbf{i}}{dt} + \mathbf{e} \tag{3.13}$$

#### 3.2.3 Discrete-Time Model for Prediction

Prediction of variables to be controlled require discretization of continuous system variables over a specified sampling time  $T_s$ . Considering that the load can be modeled as a first order system, discretization process is a simple approximation of derivative. The derivative is approximated by replacing derivative quantity by a forward Euler approximation which can be stated by (3.14) as,

$$\frac{dx}{dt} \approx \frac{x[k+1] - x[k]}{T_s} \tag{3.14}$$

Equation (3.14) when substituted in (3.13) derives an expression that allows prediction of future load current vector at time k + 1, for each possible voltage vector  $\mathbf{v}[k]$  generated by the converter. The expression can be stated as

$$\mathbf{i}^{\mathbf{p}}[k+1] = \left(1 - \frac{RT_s}{L}\right)\mathbf{i}[k] + \frac{T_s}{L}(\mathbf{v}[k] - \hat{\mathbf{e}}[k+1])$$

(3.15)

where,  $\hat{\mathbf{e}}[k]$  denotes estimated emf. The subscript **p** denotes the predicted variables.

The emf vector can be calculated from (3.13) considering measurements of the inverter voltage vector and current vector with the expression;

$$\hat{\boldsymbol{e}}[k] = \hat{\boldsymbol{e}}[k-1] = \boldsymbol{v}[k-1] - \frac{L}{T_s}\boldsymbol{i}[k] - \left(R - \frac{L}{T_s}\right)\boldsymbol{i}[k-1]$$

(3.16)

Similarly, the expression that allows prediction of difference voltage obtained by substituting (3.14) in (3.8) and can be stated by

$$v_{\Delta}^{p}[k+1] = v_{\Delta}[k] + \frac{1}{C_{1} + C_{2}} i_{z}[k]$$

(3.17)

where,  $i_{z}[k]$  is every possible neutral point current for respective switching state combinations which is obtained using (3.7).

#### 3.3 Control Design

For the sake of understanding, conventional FCS-MPCC for a three-phase three-level inverter will be explained first. Then the possibility of condition monitoring will be elaborated and finally FCS-MPCC scheme with condition monitoring will be discussed thoroughly.

#### 3.3.1 Conventional FCS-MPCC Scheme

Block diagram of FCS-MPCC scheme for a three-phase three level inverter based system is shown in Figure 3.3. Future values of the load currents and capacitor voltages are predicted for 27 possible switching state combinations of inverter using (3.15), (3.18) and (3.19).

$$v_{c1}^{p}[k+1] = v_{c1}[k] + \frac{1}{C_{1}}i_{c1}[k]T_{s}$$

(3.18)

$$v_{c2}^{p}[k+1] = v_{c2}[k] + \frac{1}{C_2}i_{c2}[k]T_s$$

(3.19)

24

After obtaining predictions, a cost function g is evaluated for each switching state combination. The switching state combination that minimizes the cost function is selected and applied during the next switching period.

Figure 3.3 Conventional Predictive Current Control for NPC Inverter

The control requirements of three-level NPC Inverter are defined by:

- Load current reference tracking.

- Balancing voltages of DC link capacitors.

- Device switching frequency reduction.

The control requirements are formulated in the form of a cost function which is required to be minimized. The cost function to control three-phase three-level inverter is composed of

$$g = |i_{\alpha}^{*} - i_{\alpha}^{P}| + |i_{\beta}^{*} - i_{\beta}^{P}| + \lambda_{dc}|v_{c1}^{P} - v_{c2}^{P}| + \lambda_{n}n_{c}$$

(3.20)

The first two terms constitute load current errors obtained as the difference of reference and predicted quantities in orthogonal trajectories. The third term in (3.20) measures the difference in predicted values of DC link capacitor voltages. These predicted voltages are calculated using (3.18) and (3.19). The last term accounts for the number of commutations required to switch from the present switching state combination to the switching state combination under evaluation. The weighting factors  $\lambda_{dc}$  and  $\lambda_n$  adjusts the relation between terms associated with reference tracking, voltage balance, and reduction of switching frequency within the function g.

# 3.3.2 Dynamic Neutral-Point Model and its Impedance Predictability in a Three-Level Converter.

As shown in Figure 3.4, when neutral point is accessed by the converter to obtain additional voltage level, a current flows through the neutral point (z). This current depends on the load phases connected to the neutral point and the load current flowing through each of these phases. Let us assume a condition in which neutral point current is in the positive direction. This current is composed of two parts, the first will charge the upper capacitor and the second will discharge the lower capacitor. Change in each capacitor voltage is due to these charging and discharging currents. This change in voltage is identical to the change in voltage of a configuration with two capacitors connected in parallel when fed by the same amount of current. Due to identical variation in the capacitor voltages, series connected neutral point configuration during dynamic condition can be modeled as two capacitors connected in parallel.

Figure 3.4 Dynamic neutral point model

Since neutral point current is a function of the switching state combination and load currents stated in (3.7). A controlled co-sinusoidal neutral point current can cause sinusoidal variation in voltage across dynamic model. Similarly, forcing sinusoidal variation of voltage difference between two DC-link capacitors will cause indirect injection of co-sinusoidal neutral point current  $i_z$ . This forced sinusoidal variation can be achieved appropriately by formulating cost function in a FCS-MPCC scheme. Root Mean Square (RMS) quantities of this injected current and the voltage variation can be used to estimate Impedance of the dynamic model. Impedance of this equivalent configuration can be stated by,

$$Z_{dyn} = \frac{1}{2\pi f_{inj}(C_1 + C_2)}$$

(3.21)

Estimated impedance of dynamic neutral-point model can be used to monitor the condition of the capacitors to an extent. This concept can be exploited to obtain FCS-MPCC for a three-level NPC inverter with condition monitoring which is explained in the next section.

#### 3.3.3 FCS-MPCC with Condition Monitoring