University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Masters Theses**

**Dissertations and Theses**

October 2022

## Formally Verifiable Synthesis Flow In FPGAs

Anurag V. Muttur University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/masters\_theses\_2

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Muttur, Anurag V., "Formally Verifiable Synthesis Flow In FPGAs" (2022). *Masters Theses*. 1237. https://doi.org/10.7275/31043432 https://scholarworks.umass.edu/masters\_theses\_2/1237

This Open Access Thesis is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

## FORMALLY VERIFIABLE SYNTHESIS FLOW IN FPGAs

A Thesis Presented by ANURAG MUTTUR

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2022

© Copyright by Anurag Muttur 2022 All Rights Reserved

## FORMALLY VERIFIABLE SYNTHESIS FLOW IN FPGAs

A Thesis Presented by ANURAG MUTTUR

Approved as to style and content by:

Russell Tessier, Chair

Wayne Burleson, Member

Neal Anderson, Member

Christopher V. Hollot, Department Head Electrical and Computer Engineering

#### ACKNOWLEDGMENTS

I want to express my gratitude to my advisor Professor Russell Tessier, for his support, guidance, and mentorship throughout my thesis work. It was a great honor and privilege to work under his guidance. I am extremely grateful for what he has offered me.

I would also like to thank my colleagues and good friends Andrew Hartnett, Tien Li Shen, Dhruv Kansagara, and Shayan Moini for guiding me throughout my work. Their endless support throughout the research has been immense and I am thankful for that.

Finally, I would like to express my profound gratitude to my parents and brother for encouraging me along the way.

#### ABSTRACT

#### FORMALLY VERIFIABLE SYNTHESIS FLOW IN FPGAs

SEPTEMBER 2022

## ANURAG MUTTUR B.Tech., PES UNIVERSITY, BANGALORE M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Russell Tessier

FPGAs are used in a wide variety of digital systems. Due to their ability to support parallelism and specialization, these devices are becoming more commonplace in fields such as machine learning. One of the biggest benefits of FPGAs, logic specialization, can lead to security risks. Prior research has shown that a large variety of malicious circuits can snoop on sensitive user data, induce circuit faults, or physically damage the FPGA. These Trojan circuits can easily be crafted and embedded in FPGA designs. Often, these Trojans are small, consume little power in comparison to the target circuit, and are hard to detect via simulation or physical inspection.

Computer-aided design (CAD) software in FPGAs has been the subject of extensive research and development of FPGAs for the past thirty-five years. The current FPGA software landscape includes vendors that provide widely used software flows to convert behavioral and register-transfer level (RTL) descriptions to bitstreams needed to program an FPGA device. Given the complexity of the algorithms needed to perform this translation, these CAD tool flows are generally structured as black boxes with limited transparency regarding design conversion steps or the logical equivalence of the generated design and initial design specification.

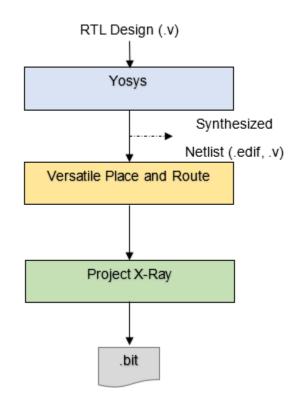

This work explores the enhancement of open-source FPGA software, SymbiFlow, that focuses on FPGA RTL synthesis, place and route and bitstream generation. SymbiFlow uses Yosys for synthesis, VPR for place and route, and Project X-Ray for bitstream generation. We focus on synthesis using Yosys and formal verification using the Cadence Conformal Logic Equivalence Checker (LEC) for Xilinx Artix-7 FPGAs. Yosys is used to synthesize 160 benchmarks written in Verilog. We implement required code modifications to Yosys for designs to pass the equivalence checker. For Conformal, this work involves processing 160 benchmark designs with the equivalence checker. Parameters can be toggled on or off to obtain results that indicates if a design has passed formal verification when comparing RTL and synthesized netlists.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                               | iv     |

|-----------------------------------------------|--------|

| ABSTRACT                                      | V      |

| CHAPTER 1                                     | 1      |

| INTRODUCTION                                  | 1      |

| 1.1 Yosys                                     | 2      |

| 1.2 Conformal Equivalence Checker (LEC)       | 2      |

| 1.3 Xilinx Vivado                             | 3      |

| 1.4 The Setup                                 | 3      |

| 1.5 Thesis Outline                            | 4      |

| CHAPTER 2                                     | 5      |

| SYNTHESIS WITH YOSYS                          | 5      |

| 2.1 Internal Yosys Operation                  | 5      |

| 2.2 Synthesis Flow                            | 6      |

| 2.3 Source Code Changes in Yosys              | 9      |

| 2.3.1 Turning off Optimizations               | 9      |

| 2.3.2 Addition of Hint Files for FSM recoding | 11     |

| 2.3.3 Hint Files for Flip Flop Merging        | 12     |

| 2.3.4 Renaming Registers                      | 12     |

| 2.3.5 ABC Script File                         |        |

| CHAPTER 3                                     | 14     |

| FORMAL VERIFICATION USING CADENCE CONFORMAL   | LEC 14 |

| 3.1 Conformal System Modes                    | 15     |

| 3.2 Key Points and Mapping                    | 16     |

| 3.3 Comparing and Diagnosing Key Points       | 16     |

| 3.4 Commands Used by Conformal                | 17     |

| CHAPTER 4                                     |        |

| BENCHMARKS USED IN SYNTHESIS AND FORMAL                   |    |

|-----------------------------------------------------------|----|

| VERIFICATION                                              |    |

| 4.1 Work in Design Verification For 8 Additional Designs  |    |

| CHAPTER 5                                                 |    |

| FORMAL VERIFICATION IN YOSYS                              | 26 |

| 5.1 An Open-Source Formal Verification Tool               |    |

| 5.2 Verifying Designs in Yosys-SMTBMC                     |    |

| 5.2.1 Files used by Yosys-SMTBMC                          |    |

| 5.3 Verifying Designs Using the Yosys Equivalence Checker |    |

| CHAPTER 6                                                 |    |

| BUGS AND BUG FIXES IN YOSYS                               |    |

| 6.1 Bug Fixes in Yosys                                    |    |

| 6.1.1 Preset-Clear Swapping Bug                           |    |

| 6.1.2 Synthesis Bug in boundtop                           |    |

| 6.2 Modifying the VPR Library                             |    |

| 6.2.1 Syntax Errors in VPR Library                        |    |

| 7.2.2 Addition of Cells to VPR Library                    |    |

| 7.2.3 Formally Verifiable Block RAMs                      |    |

| CHAPTER 7                                                 | 51 |

| RESULTS                                                   | 51 |

| CHAPTER 8                                                 | 55 |

| CONCLUSION                                                | 55 |

| 9.1 Future Work                                           |    |

| 9.1.1 Additional Benchmarks                               |    |

| 9.1.2 Protection of Hints Files                           |    |

| 9.1.3 Robust Yosys Equivalence Checker                    |    |

| APPENDIX                                                  | 57 |

| BIBLIOGRAPHY                                              |    |

# LIST OF TABLES

| Table                                                                           | Page |

|---------------------------------------------------------------------------------|------|

| 2. 1 Yosys Commands, Passes and Their Functions                                 | 7    |

| 2. 2. Optimizations Toggled in Yosys                                            | 10   |

| 3. 1. Commands in Conformal                                                     | 17   |

| 4. 1. Additional designs tested                                                 | 21   |

| 5. 1. Design tested in Yosys-SMTBMC                                             | 27   |

| 5. 2. Yosys Equivalence Check commands                                          | 33   |

| 5. 3. Yosys Equivalence Checker Statistics                                      | 35   |

| 7. 1. Logic Design Area Comparison (LUTs and Flip Flops)                        | 51   |

| 7. 2. Logic Design Area Comparison (BRAMs and DSP Blocks)                       | 53   |

| 7. 3. Design Performance Comparison                                             | 53   |

| 7. 4. Arithmetic and Geometric Means of Designs Synthesized in Yosys and Vivado | 54   |

| A. 1. All Verilog Benchmarks                                                    | 57   |

| A. 2. Initial 160 Designs Tested                                                | 63   |

| A. 3. Benchmarks Used In Results Generation                                     | 69   |

| A. 4. Benchmarks That Pass Equivalence Checking Through Yosys in                |      |

| SymbiFlow                                                                       | 71   |

| A. 5. Designs that generate bitstreams in SymbiFlow                             | 75   |

# LIST OF FIGURES

| Figure                                                                      | Page |

|-----------------------------------------------------------------------------|------|

| <b>1. 1</b> . The Formal Verification Environment                           | 4    |

| 2. 1. Data Flow of Yosys                                                    | 6    |

| 3. 1. Conformal LEC Flow                                                    |      |

| 3. 2. Design Fails Conformal                                                |      |

| 3. 3. Design Passes Conformal                                               | 17   |

| <b>5. 1.</b> The fiedler-cooley design                                      |      |

| <b>5. 2.</b> Condition to check reachability of count_out                   |      |

| <b>5. 3.</b> The fc.sby file used by fiedler-cooley                         |      |

| 5. 4. The fielder-cooley design passes SymbiYosys analysis                  |      |

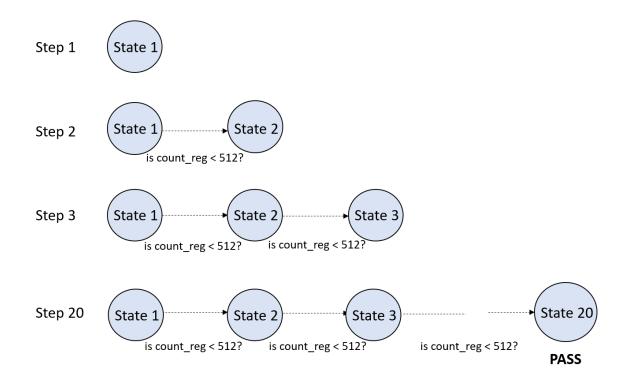

| <b>5. 5.</b> Visualization of BMC for fiedler-cooley                        |      |

| <b>5. 6.</b> Bash script used to execute the Yosys equivalence checker      |      |

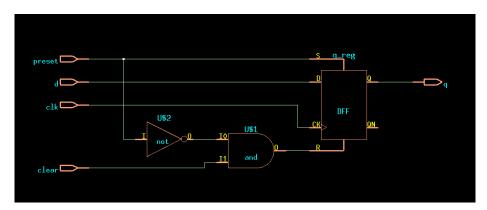

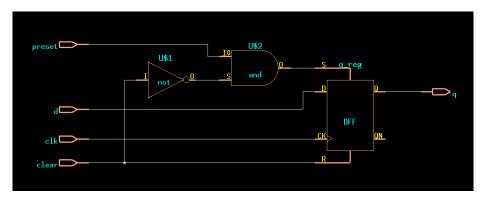

| 6. 1. Design dffsr2_sub synthesized by Yosys                                |      |

| 6. 2. Design dffsr2_sub synthesized by Conformal                            |      |

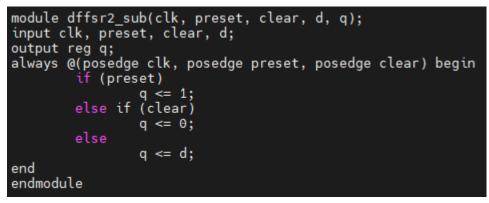

| <b>6. 3.</b> dffsr2_sub module in Verilog                                   |      |

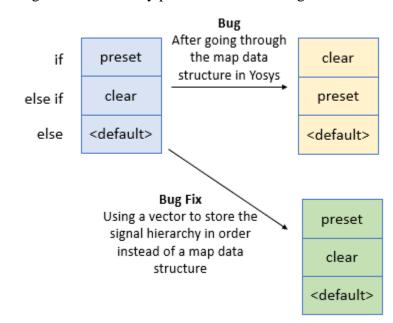

| 6. 4. Hierarchy of the <i>if</i> and <i>else</i> statements                 |      |

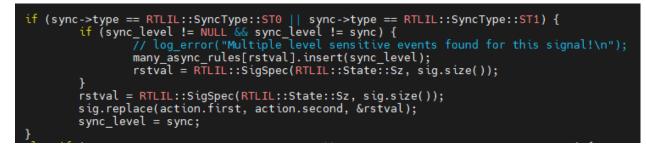

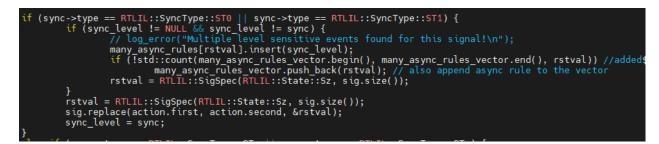

| 6. 5. <i>Many_async_rules_vector</i> created to keep track of the hierarchy |      |

| 6. 6. Before bug fix in <i>proc_dff.cc</i>                                  |      |

| 6.7. After bug fix in <i>proc_dff.cc</i>                                    | 39   |

| 6. 8. Synthesized dffsr2_sub with the bug                                   | 40   |

| 6. 9. Synthesized dffsr2_sub without the bug after bug fix                  | 40   |

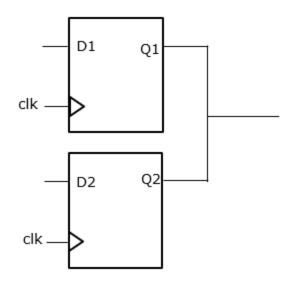

| 6. 10. Outputs of two flip flops drive the same wire                        |      |

| 6. 11. Added default statement to Boundtop                                  | 41   |

| 6. 12. FPGA flow from RTL to bitstream generation in SymbiFlow              |      |

| 6. 13. Before the Verilog syntax change                                     |      |

| 6. 14. After the Verilog syntax change                                      |      |

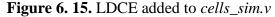

| 6. 15. LDCE added to <i>cells_sim.v</i>                                     |      |

| 6. 16. LDCE added to <i>cells_map.v</i>                      | . 46 |

|--------------------------------------------------------------|------|

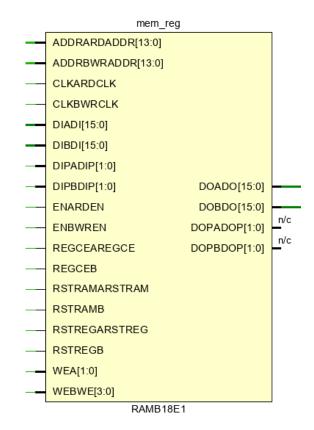

| 6. 17. RAMB18E1 Xilinx primitiveT                            | . 47 |

| 6. 18. BRAM36 module                                         | . 48 |

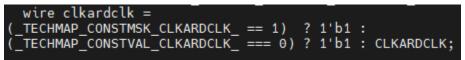

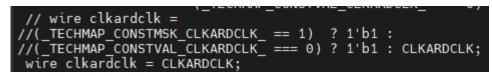

| 6. 19. clkardclk wire depends on parameter values            | . 49 |

| 6. 20. Direct connection of clkardclk wire to CLKARDCLK port | . 50 |

# CHAPTER 1 INTRODUCTION

The verification of digital hardware correctness is becoming increasingly important due to the growing use of custom accelerators using FPGAs. A register transfer level (RTL) hardware design is generally written in a hardware description language (HDL). An HDL, such as Verilog or VHDL, is used to describe the structure and behavior of a circuit. A synthesis tool is a program that takes the specified HDL file and converts it into a netlist that implements the circuit. Several circuit synthesis tools are available, but most of them are commercial tools, such as Cadence Genus [30] and Mentor Precision [31]. These proprietary tools limit the transparency of design conversion steps.

Yosys [1][2][21] is a free and open-source synthesis tool that uses ABC [10] as a backend for optimizations and technology mapping. The open-source tool allows the user to make code modifications for extra functionality. This work aims to improve the quality of synthesis tools and verify the correctness of the design through formal verification. The synthesis of an RTL design constructs a gate-level netlist by mapping it to a technology library. Conformal LEC [3], a tool developed by Cadence Design Systems [4][5], is a formal verification tool that can check whether a design written in RTL (the golden netlist) and a synthesized circuit (the revised netlist) have equivalent functionality. For this work, 160 benchmarks have been synthesized by Yosys and used by Cadence Conformal to perform formal verification. These designs of varying complexity are from the Yosys-simple [14], Yosys-bigsim [15], and VTR-benchmarks [16] benchmark suites. The designs vary from a simple full-adder to complex designs such as microprocessors and circuits used in ray tracing. The main goal for our work is to verify that synthesized designs pass equivalence checking [20]. A failed verification can lead to Trojan detection [48].

Rathmair et al. [48] apply formal methods to circuits to detect hardware Trojans. Equivalence checking, property checking, and reachability analysis are used to detect Trojans. Designs are converted into Reduced Ordinary Binary Decision Diagrams (ROBDDs) in a canonical form, a unique representation of digital logic. During equivalence checking, the functions are compared at different abstraction levels. Negative equivalence checking indicates that the abstraction level has changed by the insertion of malicious hardware in the design.

Previous synthesis work on RTL designs [17] examined Yosys, Xilinx Vivado [7][8], and Intel Quartus Prime [38]. An open-source tool named Verismith [32] generates pseudorandom, valid, deterministic Verilog designs and feeds each design to a synthesis tool. For formal verification, Verismith uses an SMT solver or the ABC circuit verification tool to check that the output is logically equivalent to the input. Bugs were found in multiple synthesis tools, except Quartus Prime [38]. Our work focuses on Yosys and performs formal verification using a commercial equivalence checker. The designs tested in this thesis were created for real-world deployment and were not randomly generated.

Shah et al. [19] showed how Yosys can be used for design synthesis and nextpnr can be used for place-and-route. This flow targets iCE40 and ECP5 FPGAs from Lattice [33]. In contrast, our work targets Xilinx Artix-7 FPGAs [34]. Our modified Yosys synthesis tool does not aim to be competitive with commercial synthesis flows in terms of area or performance. Our focus is formal verification of synthesized designs.

#### 1.1 Yosys

Yosys is a free and open-source tool that performs logic synthesis. Commands in Yosys are used to perform RTL and logic synthesis. In this work, Yosys generates a synthesized structural netlist that has Verilog syntax and contains FPGA cells. These designs can be mapped to a commercial FPGA board [7][8] including an Artix-7 series FPGA [34]. Logic cells include look up tables (LUTs), flip flops, block RAMs, and digital signal processing (DSP) blocks [12].

## **1.2 Conformal Equivalence Checker (LEC)**

Simulation can be used to verify a synthesized design's functionality. However, this solution may not be feasible for large designs as it requires sizable sets of input vectors to

be used with the design, and simulation may be time-consuming [18]. A potentially faster and more thorough verification approach is formal verification [22][23]. This approach establishes the functional equivalence of two designs generally represented as models without performing simulation. Cadence Conformal LEC is a logic equivalence tool that verifies if the RTL design is equivalent to the synthesized design. A '.dofile' command script contains the parameters required to direct Cadence Conformal LEC operation.

#### **1.3 Xilinx Vivado**

Vivado is a comprehensive FPGA design suite that includes synthesis, place-and-route, and bitstream generation. Vivado can read a post-synthesis netlist (e.g., one created by Yosys) for subsequent physical design. The tool includes a simulator that can be used to verify an RTL or post-synthesis netlist [8]. In this thesis, we contrast results generated with Vivado for an Artix-7 FPGA against those generated by Yosys. Designs from both flows are mapped to an Arty-35 board [11].

#### 1.4 The Setup

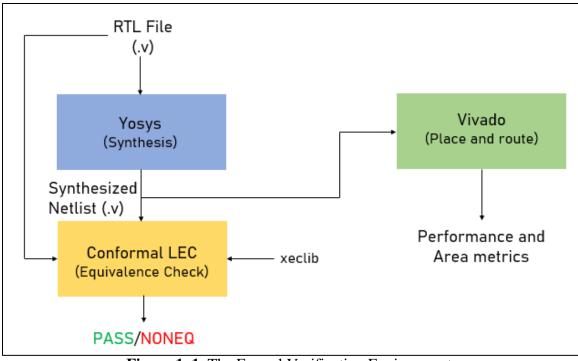

Figure 1.1 demonstrates the setup of the formal verification environment used in this work. Synthesis quality can be evaluated in lookup table (LUT) and flip flop count, number of block RAMs (BRAMs) and number of DSP blocks. Vivado performs place-and-route without optimizations using the Yosys-synthesized netlist. Post place-and-route performance and area can be determined by iteratively changing the clock period for each design until no timing violations are detected. During formal verification, the equivalence checker (e.g., LEC) should produce a 'PASS'. Incomplete or non-equivalent results can be considered a failure [5]. The input library, xeclib [27], is used to support verification.

Figure 1. 1. The Formal Verification Environment

### **1.5 Thesis Outline**

This thesis document is divided into the following chapters. Chapter 2 discusses how Yosys is used and includes changes made to the tool to allow optimization shut off and the generation of equivalence checking hints. This chapter also discusses Vivado place and route usage. Chapter 3 discusses Cadence Conformal LEC, and the various switches supported by the tool. Chapter 4 describes the 160 benchmarks used, of which 144 passed, and details why some designs may not have passed. Chapter 5 describes the results obtained when these designs are synthesized with Yosys and placed-and-routed by Vivado. Chapter 7 discusses formal verification with Yosys-SMTBMC [43] and the Yosys equivalence checker [2]. Chapter 8 discusses bug fixes made in Yosys and support for SymbiFlow. Chapter 9 concludes the thesis document and offers directions for future work.

# CHAPTER 2 SYNTHESIS WITH YOSYS

Logic synthesis converts a design specified in an HDL, such as Verilog or VHDL, into a gate-level netlist. Optimizations can be used by the synthesis tool to simplify a netlist. Our benchmarks are synthesized by Yosys using a synthesis library provided by Xilinx referred to as xeclib [27]. Our work uses a modified copy of Yosys version 0.9+4249 and 160 RTL benchmarks. Commands are used to read the design written in RTL, synthesize and technology map the design to the Xilinx library, and write out the synthesized netlist. This chapter provides information on how Yosys works and our modifications.

### 2.1 Internal Yosys Operation

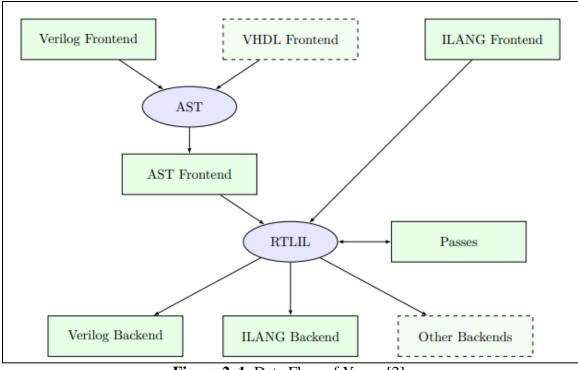

Yosys synthesis steps [24] include the use of a lexer and a parser. The input design is converted into an Abstract Syntax Tree (AST) [25] and then into Register-to-Transfer Level Intermediate Language (RTLIL) format. The lexer parses the input Verilog files, identifies Verilog keywords and tokenizes them. These tokens are used as nodes in an AST. The Verilog parser then generates an AST data structure using the information about nodes provided by the lexer. The data structure is then passed directly to the AST frontend where it is simplified and converted into an RTLIL netlist - an internal format used by Yosys. This conversion from AST to RTLIL can be done in two steps: simplification and RTLIL generation. During simplification, keywords present in the AST data structure are converted to simpler tokens. Once simplified, RTLIL generation is performed by a recursive process that generates equivalent RTLIL data for the AST data. Finally, the RTLIL representation is technology mapped using a library. The synthesized netlist is then written in the file format specified by the user.

Figure 2. 1. Data Flow of Yosys [2]

Figure 2.1 shows the simplified data flow in Yosys. The rectangles in the diagram are program modules and the ellipses are data structures generated by the program modules. Optimizations and technology mapping are examples of passes used in the Passes module. The ILANG representation shown in Figure 2.1 is a text representation of the RTLIL format that can directly be converted into RTLIL without conversion to AST. The 'other backends' module includes netlist output into different formats, such as edif or blif. The conversion of RTLIL to Verilog is performed when the netlist is written out.

#### 2.2 Synthesis Flow

Our Yosys synthesis flow includes the following commands:

1. read\_verilog <design\_file.v>

This command parses and reads the Verilog file. The lexer and parser are used to read the input RTL file provided and converts it into an AST representation.

2. synth\_xilinx

This command synthesizes the design and performs technology mapping to the Xilinx library input into Yosys. Synthesis uses the steps noted in Table 2.1.

| 1 | Command<br>under<br>'synth_xilinx'<br>begin | <ul> <li>Sub-commands/Passes</li> <li>read_verilog -lib +/xilinx/cells_sim.v</li> <li>read_verilog -lib +/xilinx/cells_xtra.v</li> </ul>                                                                                          | Function         Read the Xilinx libraries in         Yosys, checks the hierarchy of |

|---|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|   |                                             | <ul> <li>read_verilog -lib +/xilinx/brams_bb.v</li> <li>read_verilog -lib +/xilinx/drams_bb.v</li> <li>hierarchy -check -top <top></top></li> </ul>                                                                               | the design and sets the top<br>module accordingly                                    |

| 2 | synth -run<br>coarse                        | <ul> <li>proc</li> <li>opt_expr</li> <li>opt_clean</li> <li>check</li> <li>opt</li> <li>wreduce</li> <li>alumacc</li> <li>share</li> <li>opt</li> <li>fsm</li> <li>opt -fast</li> <li>memory -nomap</li> <li>opt_clean</li> </ul> | Run coarse optimizations                                                             |

| 3 | bram                                        | <ul> <li>memory_bram -rules +/xilinx/brams.txt</li> <li>techmap -map +/xilinx/brams_map.v</li> </ul>                                                                                                                              | Technology mapping for block<br>RAMs.                                                |

Table 2. 1 Yosys Commands, Passes and Their Functions

| 4 | dram      | • memory_bram -rules +/xilinx/drams.txt       | Technology mapping for         |

|---|-----------|-----------------------------------------------|--------------------------------|

|   |           | • techmap -map +/xilinx/drams_map.v           | memory (DRAMs).                |

| 5 | fine      | • opt -fast -full                             | Perform fine grain             |

|   |           | • memory_map                                  | optimizations.                 |

|   |           | • dffsr2dff                                   |                                |

|   |           | • dff2dffe                                    |                                |

|   |           | • opt -full                                   |                                |

|   |           | • techmap -map +/techmap.v -map               |                                |

|   |           | +/xilinx/arith_map.v                          |                                |

|   |           | • opt -fast                                   |                                |

| 6 | map_luts  | • abc -luts 2:2,3,6:5,10,20 [-dff]            | Map LUTs to design.            |

|   |           | • clean                                       |                                |

| 7 | map_cells | • techmap -map +/xilinx/cells_map.v           | Map cells to design.           |

|   |           | • dffinit -ff FDRE Q INIT -ff FDCE Q INIT -ff |                                |

|   |           | FDPE Q INIT                                   |                                |

|   |           | • clean                                       |                                |

| 8 | check     | • hierarchy -check                            | Check and display hierarchy of |

|   |           | • stat                                        | the design.                    |

|   |           | • check -noinit                               |                                |

The commands shown in Table 2.1 are used on the design RTLIL representation.

3. write\_verilog <design\_file\_synth.v>

The synthesized netlist is written to the current Yosys execution directory unless the directory of the synthesized file is specified. The synthesized file is usually appended with a 'synth' suffix at the end of the file name, before the '.v' extension. These steps can be automated by creating a text file with the commands and making a single call to Yosys to call the script. This call will run all steps in one command. For example, if the commands are stored in a text file named *yosys\_run.txt*, this file can be executed by calling Yosys along with the switch *-s* that makes use of the specified script. The command used would be *yosys -s yosys\_run.txt* to run all the steps.

#### 2.3 Source Code Changes in Yosys

Initially, over 100 of the 160 designs synthesized by Yosys for a Xilinx Artix-7 FPGA did not pass LEC equivalence checking with default Yosys optimizations. In some cases, the optimizations obscured the design function (e.g., removed registers, renamed registers, recoded state machines) making it impossible for the verification tool to work properly. Initially, to allow designs with these optimizations to pass equivalence checking, the optimizations had to be turned off. Yosys provide some switches to disable optimizations, such as *-nobram* which forbids the use of block RAMs [36]. However, there were optimizations (e.g. register removal) that could not be deactivated using standard Yosys switches. Yosys source code modifications allowed us to add command line switches and functionality to suppress these optimizations. These additions are noted below.

#### 2.3.1 Turning off Optimizations

The switches used to suppress optimizations are detailed in Table 2.2. These switches are used during the *synth\_xilinx* step.

| Sl. No. | Switch that turns off the | Function                                      |  |

|---------|---------------------------|-----------------------------------------------|--|

|         | optimization              |                                               |  |

| 1       | -nofsm                    | Do not extract and optimize finite state      |  |

|         |                           | machines in input code                        |  |

| 2       | -nowreduce                | Do not attempt word size reduction of         |  |

|         |                           | arithmetic operations. For example, if both   |  |

|         |                           | input values are 32 bits but only an 8-bit    |  |

|         |                           | output is needed, the adder size can be       |  |

|         |                           | reduced to 8 bits.                            |  |

| 3       | -noopt                    | Prevent simple logic optimizations that may   |  |

|         |                           | result in the elimination of flip flops.      |  |

| 4       | -noopt_dff                | Do not perform DFF optimization. This         |  |

|         |                           | includes the removal of D flip flops that are |  |

|         |                           | driven by constant values and the merging of  |  |

|         |                           | flip flops that are logically equivalent.     |  |

| 5       | -noopt_muxtree            | Do not eliminate dead branches in             |  |

|         |                           | multiplexer trees.                            |  |

| 6       | -noopt_reduce             | Do not simplify large MUXes and AND/OR        |  |

|         |                           | gates.                                        |  |

| 7       | -noopt_merge              | Do not merge logically identical cells,       |  |

|         |                           | including flip flops. This optimization is    |  |

|         |                           | separate from the optimizations affected by - |  |

|         |                           | noopt_dff                                     |  |

| 8       | -noopt_clean              | Do not remove unused cells and wires          |  |

| 9       | -noopt_expr               | Do not perform const folding and simple       |  |

|         |                           | expression rewriting                          |  |

| 10      | -noopt_mem                | Do not perform various optimizations on       |  |

|         |                           | memories in the design                        |  |

Table 2. 2. Optimizations Toggled in Yosys

| 11 | -keepff                   | Keep flip-flop output wires even if the wires  |

|----|---------------------------|------------------------------------------------|

|    |                           | do not affect primary output values.           |

| 12 | -abc_script <file></file> | Use the specified ABC script file instead of   |

|    |                           | the default script for logic optimization with |

|    |                           | ABC. More information on this optimization     |

|    |                           | is detailed in Section 2.3.5.                  |

#### 2.3.2 Addition of Hint Files for FSM recoding

During Yosys execution, state machines can be automatically recoded [26]. For example, binary coded state may be recorded to a one-hot encoding (e.g., a three-bit code representing states 0....7 would be converted to an 8-bit code with only one bit active at a time). By default, Conformal expects binary state machine encoding, so Yosys recoding leads to design mismatches and formal verification failure. To address this issue, Yosys was modified to write out FSM recoding information in a "hint" file that could be used by Conformal. For example, the following FSM that uses state registers of 32-bits is converted to one-hot encoding of 5-bits. The contents of the file is shown below.

.fromstates state\_reg[31] state\_reg[30] state\_reg[29] state\_reg[28] state\_reg[27] state\_reg[26] state\_reg[25] state\_reg[24] state\_reg[23] state\_reg[22] state\_reg[21] state\_reg[20] state\_reg[19] state\_reg[18] state\_reg[17] state\_reg[16] state\_reg[15] state\_reg[14] state\_reg[13] state\_reg[12] state\_reg[11] state\_reg[10] state\_reg[9] state\_reg[8] state\_reg[7] state\_reg[6] state\_reg[5] state\_reg[4] state\_reg[3] state\_reg[2] state\_reg[1] state\_reg[0]

.tostates state\_reg[4] state\_reg[3] state\_reg[2] state\_reg[1] state\_reg[0] .begin

The switch *-fm\_set\_fsm\_file fsm-file-conformal* is set during the *synth\_xilinx* step in Yosys to dump out recoding information into the fsm-file-conformal file. The line *read fsm encoding fsm-file-conformal -Golden* is added to the LEC "dofile" command file so that the file produced by Yosys is read by LEC and used during formal verification.

#### 2.3.3 Hint Files for Flip Flop Merging

During Yosys execution, design flip flops that are logically equivalent (e.g., same input signals) are identified. Redundant flip flops can be removed. If flip flops named FF1 and FF2 have the same functionality, the line *add instance equivalence FF1 FF2* is written to a hints file and FF2 is removed from the design. Yosys outputs a file *FF\_renaming.log* during this optimization which lists the name of the remaining flip flop for removed flip flops. This hints file can be used by Conformal to aid in formal verification. The line *dofile FF\_renaming.log* is added to the Conformal LEC "dofile".

#### **2.3.4 Renaming Registers**

The Yosys source code was modified to rename registers so that the names in the synthesized output file would be consistent with those expected by Conformal. By default, Conformal expects registers to have a '\_reg' suffix to the name of the flip flop or latch output signal. For example, a DFF with an output signal *outputval* is renamed to *outputval\_reg*. Output signals with an index append the suffix before the index. For example, *outputval[0]* becomes *outputval\_reg[0]*. This naming convention matches the flip flop and latch naming used by LEC.

#### **2.3.5 ABC Script File**

The addition of an ABC script to perform logic optimization provides more options for synthesis improvement in Yosys. ABC performs standard optimizations by default. A command file *abc.script* that optimizes the design for binary decision diagrams (BDDs) and performs structural hashing (strash) has been added. BDD optimization identifies XOR gates for more efficient implementation of arithmetic operations (for example, wide addition). Structural hashing is performed to minimize logic across RTL logic structures

such as chained multiplexers.

# CHAPTER 3 FORMAL VERIFICATION USING CADENCE CONFORMAL LEC

Formal verification uses mathematics to prove that two representations of a design possess the same behavior [28]. Equivalence checking is a type of formal verification that takes two designs that may be at the same or different levels of abstraction and determines if they are logically equivalent. Equivalence checking (e.g., Conformal LEC) can verify that a synthesized design's function is the same as an original RTL version [28]. Conformal uses combinational equivalence to determine if a design matches an original RTL or gatelevel description [29] (e.g. the golden netlist). Verified logic includes complex arithmetic circuits, datapath circuits, memories, and custom logic. A Conformal 'PASS' result indicates that the synthesized design has passed the equivalence check [5]. Other results ('NONEQ', 'INCOMPLETE' or 'ABORT') indicate that the design did not pass the equivalence check successfully. For a design that fails, Conformal provides the number of non-equivalence points (input or output pins and-flip flops or latches). An INCOMPLETE status indicates that there are some points in the synthesized netlist that do not exist in the golden file. An ABORT occurs when some portions of the design are too complex to verify. In some cases, this issue can be overcome by setting the netlist compare effort to a higher setting [4]. Designs that do not pass the equivalence check can be assessed by observing the circuit schematic and noting differences between the RTL and synthesized netlists.

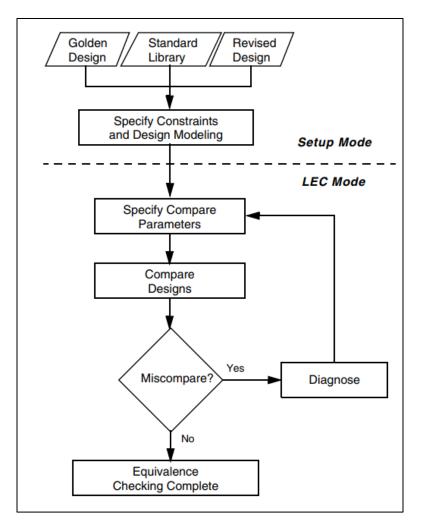

Figure 3. 1. Conformal LEC Flow [5]

#### **3.1 Conformal System Modes**

Conformal LEC operates in two modes – Setup and LEC [5]. In Setup mode, the RTL design, the synthesized design and libraries are read into Conformal LEC. The designs are set as golden and revised respectively. Generally, the revised design is the synthesized design. Constraints are set in Setup mode, such as whether the design should be flattened. Once constraints are set, Conformal switches to LEC mode. This mode uses options to perform equivalence comparison and can be used to report non-equivalent points. A variety of comparison effort settings can be used. The equivalence result is displayed at the end of LEC mode. Figure 3.1 gives an overview of the operations that occur in Setup and LEC modes.

#### **3.2 Key Points and Mapping**

In Conformal, multiple key points in the golden and revised netlists are compared. Key points include primary input and primary output pins, D flip flops, D latches, blackboxes, TIE-Z gates (high impedance signals), TIE-E gates (gates created when a don't care x-assignment exists in the revised design) and cut gates (artificial gates that break combinational loops) [5].

By default, Conformal maps key points by matching names once Setup mode exits. Name-based mapping is most useful when small changes are made to the logic [4]. A noname mapping method for mapping key points is used when designs have completely different names. Any key point that is not mapped by Conformal is an unmapped point.

Unmapped points are divided into three categories: extra, unreachable and not-mapped [5]. Extra points in Conformal include the key points that are present in only one of the designs – either the golden or revised. Unreachable points are key points that do not have an observable point, such as a primary input. These points can usually be ignored during debugging of unmapped points. Not-mapped points are key points that are reachable but do not have a corresponding point in the logic of the corresponding design.

### **3.3 Comparing and Diagnosing Key Points**

Once Conformal has finished executing, it will display a 'PASS' or 'NONEQ' result. A 'PASS' indicates that a design has passed Conformal LEC equivalence checking successfully. A 'NONEQ' indicates that in a design, there exists a cell or cells in the synthesized netlist that does not correspond to the golden netlist. Examples are shown in Figures 3.1 and 3.2.

| // command: add cd<br>// 2 compared poir<br>// Command: compar | nts addeo |     |       |  |

|----------------------------------------------------------------|-----------|-----|-------|--|

| Compared points                                                | P0        | DFF | Total |  |

| Equivalent                                                     | 1         | Θ   | 1     |  |

| Non-equivalent                                                 | Θ         | 1   | 1     |  |

Figure 3. 2. Design Fails Conformal

| Undriven key points<br>Unmapped                                                                           |     | 0<br>0     | 176<br>176 |

|-----------------------------------------------------------------------------------------------------------|-----|------------|------------|

| Unreachable                                                                                               |     | 0          | 176        |

| Primary outputs<br>Mapped                                                                                 | 120 | 128<br>128 | 128<br>128 |

| Equivalent                                                                                                | 128 |            |            |

| State key points<br>Mapped<br>Equivalent                                                                  | 128 | 896<br>128 | 896<br>128 |

| Unmapped<br>Unreachable                                                                                   | 120 | 768<br>768 | 768<br>768 |

| // Command: usage<br>CPU time : 4084.24 seco<br>Memory usage : 332.07 M by<br>// Command: report verifica | tes |            |            |

| // Command: set log file<br>// Command: set log file                                                      |     | acc        | PASS       |

Figure 3. 3. Design Passes Conformal

## 3.4 Commands Used by Conformal

A 'dofile' with the extension '.do' includes the commands executed by Conformal LEC to perform equivalence checking. Representative commands used by the dofile are summarized in Table 3.1.

| <b>Table 3.1</b> | Commands | in Conformal |

|------------------|----------|--------------|

|------------------|----------|--------------|

| Command in Conformal                              | Function of command               |

|---------------------------------------------------|-----------------------------------|

| read library -Both -Replace -sensitive -Verilog2k | Reads in the verification library |

| ~/FVSF-Benchmark/xeclib/*.v –nooptimize           | files for Xilinx 7-series FPGAs   |

|                                                   | named xeclib [27]. The files are  |

|                                                   | provided by Xilinx with the       |

| formal verification.read design <design.v> - Verilog2k -Golden -Replace<br/>-sensitive -continuousassignment Bidirectional -<br/>nokeep_unreach -nosupplyReads in the golden RTL and<br/>synthesized design files based on<br/>"-Golden" and "-Revised"<br/>switches, respectivelyread design <design_synth.v> - Verilog2k -Revised -<br/>Replace -sensitive -continuousassignment<br/>Bidirectional -nokeep_unreach -nosupplySets the root module name of the<br/>synthesized Verilog design for<br/>analysisset root module <top_module> -revisedSets the root module name of the<br/>synthesized Verilog design for<br/>analysisset analyze option -autoAllows LEC to automatically<br/>perform advanced equivalence<br/>checking operations automatically<br/>set flatten model -seq_constantset flatten model -seq_merge -goldenOptional line. Merges flip flops<br/>that have the same D and clock<br/>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br/>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br/>mapping with flip flops replaced<br/>by constantsadd compared points -allIncludes all compared points in the<br/>analysis</top_module></design_synth.v></design.v>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     | Vivado software distribution for    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------|

| -sensitive -continuousassignment Bidirectional -<br>nokeep_unreach -nosupplysynthesized design files based on<br>"-Golden" and "-Revised"<br>switches, respectivelyread design <design_synth.v> -Verilog2k -Revised -<br/>Replace -sensitive -continuousassignment<br/>Bidirectional -nokeep_unreach -nosupplysets the root module name of the<br/>synthesized Verilog design for<br/>analysisset root module <top_module> -revisedSets the root module name of the<br/>synthesized Verilog design for<br/>analysisset analyze option -autoAllows LEC to automatically<br/>perform advanced equivalence<br/>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br/>constant data input to a constant<br/>value, eliminating the flip flopsset system mode lecSwitches LEC from Setup to logic<br/>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br/>mapping with flip flops replaced<br/>by constantsadd compared points -allIncludes all compared points in the</top_module></design_synth.v>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     | formal verification.                |

| nokeep_unreach -nosupply"-Golden" and "-Revised"<br>switches, respectivelyread design <design_synth.v> -Verilog2k -Revised -<br/>Replace -sensitive -continuousassignment-Bidirectional -nokeep_unreach -nosupplySets the root module name of the<br/>synthesized Verilog design for<br/>analysisset root module <top_module> -revisedSets the root module name of the<br/>synthesized Verilog design for<br/>analysisset analyze option -autoAllows LEC to automatically<br/>perform advanced equivalence<br/>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br/>constant data input to a constant<br/>value, eliminating the flip flopsset system mode lecSwitches LEC from Setup to logic<br/>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br/>mapping with flip flops replaced<br/>by constantsadd compared points -allIncludes all compared points in the</top_module></design_synth.v>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | read design <design.v> -Verilog2k -Golden -Replace</design.v>       | Reads in the golden RTL and         |

| read design <design_synth.v> -Verilog2k -Revised -       switches, respectively         Replace -sensitive -continuousassignment       sidirectional -nokeep_unreach -nosupply         set root module <top_module> -revised       Sets the root module name of the synthesized Verilog design for analysis         set analyze option -auto       Allows LEC to automatically perform advanced equivalence checking operations automatically         set flatten model -seq_constant       Converts flip flops driven by a constant data input to a constant value, eliminating the flip flops         set system mode lec       Switches LEC from Setup to logic equivalence (LEC) mode         remodel -seq_constant       "Try harder" mode for LEC design mapping with flip flops replaced by constants         add compared points -all       Includes all compared points in the</top_module></design_synth.v>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -sensitive -continuousassignment Bidirectional -                    | synthesized design files based on   |

| read design <design_synth.v> -Verilog2k -Revised -<br/>Replace -sensitive -continuousassignment<br/>Bidirectional -nokeep_unreach —nosupplyset root module <top_module> -revisedSets the root module name of the<br/>synthesized Verilog design for<br/>analysisset root module <top_module> -revisedAllows LEC to automatically<br/>perform advanced equivalence<br/>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br/>constant data input to a constant<br/>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br/>that have the same D and clock<br/>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br/>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br/>mapping with flip flops replaced<br/>by constantsadd compared points -allIncludes all compared points in the</top_module></top_module></design_synth.v>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nokeep_unreach –nosupply                                            | "-Golden" and "-Revised"            |

| Replace -sensitive -continuousassignment         Bidirectional -nokeep_unreach -nosupply         set root module <top_module> -revised         Sets the root module name of the synthesized Verilog design for analysis         set analyze option -auto       Allows LEC to automatically perform advanced equivalence checking operations automatically         set flatten model -seq_constant       Converts flip flops driven by a constant data input to a constant value, eliminating the flip flops         set flatten model -all_seq_merge -golden       Optional line. Merges flip flops that have the same D and clock inputs into one flip flop         set system mode lec       Switches LEC from Setup to logic equivalence (LEC) mode         remodel -seq_constant       "Try harder" mode for LEC design mapping with flip flops replaced by constants         add compared points -all       Includes all compared points in the</top_module>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     | switches, respectively              |

| Bidirectional -nokeep_unreach -nosupply       Sets the root module name of the synthesized Verilog design for analysis         set root module <top_module> -revised       Sets the root module name of the synthesized Verilog design for analysis         set analyze option -auto       Allows LEC to automatically perform advanced equivalence checking operations automatically         set flatten model -seq_constant       Converts flip flops driven by a constant data input to a constant value, eliminating the flip flops         set flatten model -all_seq_merge -golden       Optional line. Merges flip flops that have the same D and clock inputs into one flip flop         set system mode lec       Switches LEC from Setup to logic equivalence (LEC) mode         remodel -seq_constant       "Try harder" mode for LEC design mapping with flip flops replaced by constants         add compared points -all       Includes all compared points in the</top_module>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | read design <design_synth.v> -Verilog2k -Revised -</design_synth.v> |                                     |

| set root module <top_module> -revised       Sets the root module name of the synthesized Verilog design for analysis         set analyze option -auto       Allows LEC to automatically perform advanced equivalence checking operations automatically         set flatten model -seq_constant       Converts flip flops driven by a constant data input to a constant value, eliminating the flip flops         set flatten model -all_seq_merge -golden       Optional line. Merges flip flops that have the same D and clock inputs into one flip flop         set system mode lec       Switches LEC from Setup to logic equivalence (LEC) mode         remodel -seq_constant       "Try harder" mode for LEC design mapping with flip flops replaced by constants         add compared points -all       Includes all compared points in the</top_module>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Replace -sensitive -continuousassignment                            |                                     |

| Instructionsynthesized Verilog design for<br>analysisset analyze option - autoAllows LEC to automatically<br>perform advanced equivalence<br>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br>constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bidirectional -nokeep_unreach -nosupply                             |                                     |

| analysisset analyze option -autoAllows LEC to automatically<br>perform advanced equivalence<br>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br>constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | set root module <top_module> -revised</top_module>                  | Sets the root module name of the    |

| set analyze option -autoAllows LEC to automatically<br>perform advanced equivalence<br>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br>constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     | synthesized Verilog design for      |

| perform advanced equivalence<br>checking operations automaticallyset flatten model -seq_constantConverts flip flops driven by a<br>constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     | analysis                            |

| set flatten model -seq_constantConverts flip flops driven by a<br>constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | set analyze option -auto                                            | Allows LEC to automatically         |

| set flatten model -seq_constantConverts flip flops driven by a<br>constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     | perform advanced equivalence        |

| constant data input to a constant<br>value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     | checking operations automatically   |

| value, eliminating the flip flopsset flatten model -all_seq_merge -goldenOptional line. Merges flip flops<br>that have the same D and clock<br>inputs into one flip flopset system mode lecSwitches LEC from Setup to logic<br>equivalence (LEC) moderemodel -seq_constant"Try harder" mode for LEC design<br>mapping with flip flops replaced<br>by constantsadd compared points -allIncludes all compared points in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | set flatten model -seq_constant                                     | Converts flip flops driven by a     |