University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Masters Theses**

**Dissertations and Theses**

October 2022

# Integration of Digital Signal Processing Block in SymbiFlow FPGA Toolchain for Artix-7 Devices

Andrew T. Hartnett University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/masters\_theses\_2

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Hartnett, Andrew T., "Integration of Digital Signal Processing Block in SymbiFlow FPGA Toolchain for Artix-7 Devices" (2022). *Masters Theses*. 1226. https://doi.org/10.7275/31161105 https://scholarworks.umass.edu/masters\_theses\_2/1226

This Open Access Thesis is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# INTEGRATION OF DIGITAL SIGNAL PROCESSING BLOCK IN SYMBIFLOW FPGA TOOLCHAIN FOR ARTIX-7 DEVICES

A Thesis Presented by ANDREW HARTNETT

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2022

Electrical and Computer Engineering

© Copyright by Andrew Hartnett 2022

All Rights Reserved

# INTEGRATION OF DIGITAL SIGNAL PROCESSING BLOCK IN SYMBIFLOW FPGA TOOLCHAIN FOR ARTIX-7 DEVICES

A Thesis Presented

by

ANDREW HARTNETT

Approved as to style and content by:

Russell Tessier, Chair

Wayne Burleson, Member

Daniel Holcomb, Member

Christopher V. Hollot, Department Head Electrical and Computer Engineering

### ACKNOWLEDGEMENTS

I would like to thank my advisor Professor Russell Tessier for providing me the opportunity to continue my academic growth. Through learning from him, I believe I have been impacted for the better in understanding the resolve and determination needed to see a project through, and for that I am grateful. My appreciation extends to colleagues and friends Anurag Muttur, Tien Li Shen, and Shayan Moini as well.

Lastly, I am profoundly grateful for the endless support from my family. Without them and my partner Kelly, this work would not have seen its completion. Thank you.

#### ABSTRACT

## INTEGRATION OF DIGITAL SIGNAL PROCESSING BLOCKS IN SYMBIFLOW FPGA TOOLCHAIN FOR ARTIX-7 DEVICES

#### SEPTEMBER 2022

# ANDREW HARTNETT B.S., UNIVERSITY OF MASSACHUSETTS AMHERST M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

#### Directed by: Professor Russell Tessier

The open-source community is a valuable resource for many hobbyists and researchers interested in collaborating and contributing towards publicly available tools. In the area of field programmable gate arrays (FPGAs) this is no exception. Contributors seek to reverse-engineer the functions of large proprietary FPGA devices. An interesting challenge for open-source FPGA engineers has been reverse-engineering the operation and bitstreams of digital signal processing (DSP) blocks located in FPGAs. SymbiFlow is an open-source FPGA toolchain designed as a free alternative to proprietary computer-aided design tools like Xilinx's Vivado. For SymbiFlow, mapping logical multipliers to DSP blocks and generating DSP block bitstreams has been left unimplemented for the Artix-7 family of FPGAs. This research seeks to rectify this shortcoming by introducing DSP information for the place and route functions into SymbiFlow. By delving into the SymbiFlow architecture definitions and creating functioning FPGA assembly code (FASM) files for Project X-Ray, a bitstream generator for Artix-7, we have been able to determine the desired output of the open-source Versatile Place & Route tool that will generate a working DSP bitstream. We diagnose and implement changes needed throughout the SymbiFlow toolchain, allowing for DSP design bitstreams to be successfully generated with open-source tools.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSiv                                        |

|-----------------------------------------------------------|

| ABSTRACTv                                                 |

| TABLE OF CONTENTS vi                                      |

| LIST OF TABLESviii                                        |

| LIST OF FIGURESix                                         |

| CHAPTER 1 - INTRODUCTION1                                 |

| 1.1 Xilinx Vivado                                         |

| 1.2 SymbiFlow Toolchain                                   |

| 1.3 DSP Blocks4                                           |

| 1.4 Thesis Outline7                                       |

| CHAPTER 2 - SYMBIFLOW                                     |

| 2.1 Yosys                                                 |

| 2.2 VPR / Genfasm9                                        |

| 2.3 Project X-Ray10                                       |

| 2.4 Using SymbiFlow11                                     |

| 2.5 State of DSP Block Usage in SymbiFlow13               |

| CHAPTER 3 - ARCHITECTURE DEFINITIONS AND GENFASM15        |

| 3.1 SymbiFlow Architecture Definitions15                  |

| 3.1.1 Architecture Primitives15                           |

| 3.1.2 Generating Routing Graph and Architecture File17    |

| 3.1.3 Developing A Basic DSP48E1 Primitive17              |

| 3.2 2x2 bit Multiplier Design Under Test (DUT)19          |

| 3.2.1 Symmetric Flow through SymbiFlow and Vivado19       |

| 3.2.2 Differences between SymbiFlow and Vivado FASM files |

| CHAPTER 4 – COMPLETE SYMBIFLOW DSP BITSTREAM              |

| 4.1 Diagnosing DSP Support Points24                       |

| 4.2 Investigating the Vivado Routing Resources GUI24      |

| 4.3 Yosys DSP Information into VPR                        |

| 4.4 Developing DSP48E1 Primitive                          |

| 4.5 Changes to Genfasm                          |    |

|-------------------------------------------------|----|

| 4.6 Summary of Modifications                    | 35 |

| CHAPTER 5 – EXPANDING DSP FUNCTIONALITY         |    |

| 5.1 Full 25x18 bit Multiplier                   |    |

| 5.2 Partial Pre-adder                           |    |

| 5.3 Pipelined Multiplier                        |    |

| CHAPTER 6 – CONCLUSION                          | 46 |

| 6.1 Future Work                                 | 46 |

| 6.1.1 Incorporating C Port for DSP48E1          | 46 |

| 6.1.2 Investigating the D Port Congestion Issue | 47 |

| 6.1.3 Allowing Behavioral Modeling of DSP48E1   | 47 |

| BIBLIOGRAPHY                                    | 48 |

#### LIST OF TABLES

# TablePage1 - STEPS CALLED AND TOOLS USED WITHIN SYMBIFLOW132 - DSP48E1 PORTS TIED TO GND NEEDED FOR WORKING 2X2 MULTIPLIER273 - MODE AND INVERTED SIGNALS FOR A\*B PORT MULTIPLIER294 - PORTS REMOVED FROM VPR LIBRARIES BASED ON VIVADO GUI315 - MODE AND INVERTED SIGNALS FOR 25X18 BIT MULTIPLIER376 - LED OUTPUT COMBINATIONS OF 25X18 BIT DSP MULTIPLIER387 - MODE AND INVERTED SIGNALS FOR MULTIPLIER WITH PRE-ADDER40

# LIST OF FIGURES

# Figure

| <b>1</b> - SUPPORTED ARCHITECTURE FOR VARIOUS POPULAR FPGAS                |

|----------------------------------------------------------------------------|

| <b>2</b> - VISUALIZATION OF TOOLS INVOLVED IN SYMBIFLOW TOOLCHAIN          |

| <b>3</b> - INTERNAL ARCHITECTURE OF 7 SERIES DSP48E1 SLICE                 |

| <b>4</b> - DSP48 MACRO PROVIDED BY VIVADO FOR DSP BLOCK CREATION           |

| 5 - DETAILED SYMBIFLOW TOOLCHAIN WITH ARCHITECTURE DEFINITIONS AND         |

| INTERMEDIATE FILES                                                         |

| 6 - COUNTER_TEST.V, PART OF SYMBIFLOW-EXAMPLES                             |

| 7 - COMMON.MK MAKEFILE USED TO CALL STEPS WITH SYMBIFLOW12                 |

| 8 - SNAPSHOT OF RAMB18E1.MODEL.XM 16                                       |

| 9 - SNAPSHOT OF BRAM.PB_TYPE.XML SHOWING RAMB18E1 INTERCONNECTS 16         |

| <b>10</b> - PRELIMINARY DSP48E1 PRIMITIVE USED FOR PLACE AND ROUTE         |

| 11 - CUSTOM 2X2 BIT UNSIGNED MULTIPLIER USING DSP48E1                      |

| 12 - SYMMETRIC FLOW BETWEEN SYMBIFLOW AND VIVADO                           |

| <b>13 -</b> FASM FILE INFORMATION COMPARISON                               |

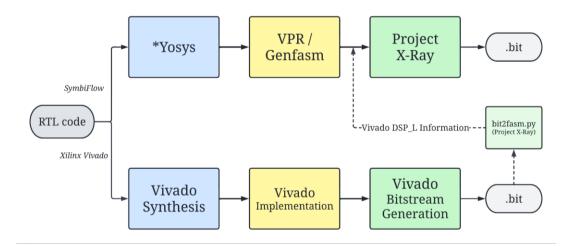

| 14 - ASSISTED WORKING 2X2 BIT MULTIPLIER FLOW THROUGH SYMBIFLOW $\dots 24$ |

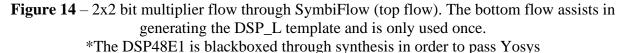

| <b>15</b> - VIVADO ROUTED FLOORPLAN FOR 2X2 MULTIPLIER                     |

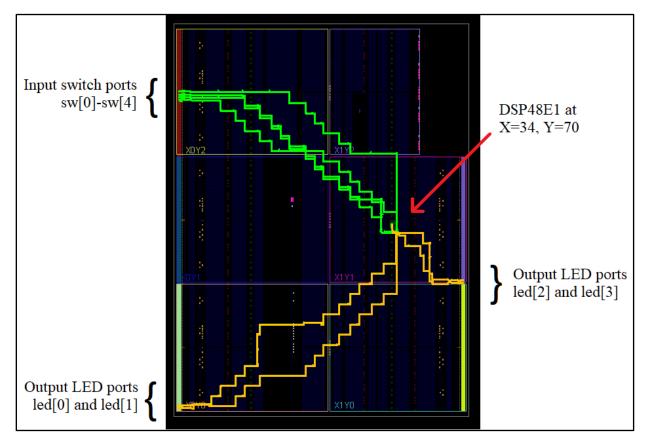

| <b>16 - SWITCHBOX INTERCONNECT FASM FILE WITH GUI</b>                      |

| 17 - ROUTING RESOURCE GUI VIEW OF DSP BLOCK                                |

| <b>18</b> - 2X2 BIT MULTIPLIER RTL CODE WITH PARAMETERS                    |

| <b>19 -</b> PART OF CELLS_MAP.V DEFINITION OF A DSP48E1_VPR CELL           |

| <b>20</b> - "FASM_PARAMS" SECTION OF DSP48E1 PRIMITIVE                     |

| 21 - RTL ASSIGNMENT OF INPUT SWITCHES ONTO A AND B INPUT SIGNALS 38        |

| 22 - DSP48E1 INTERNALS WITH PRE-ADDER INTO 25X18 BIT MULTIPLIER 39         |

| 23 - RTL ASSIGNMENT OF INPUT SWITCHES ONTO A, B, AND D INPUT SIGNALS 41    |

| 24 - PIPELINED REGISTER FLOW WITHIN THE DSP48E1                            |

| <b>25</b> - RTL INSTANTIATION OF A PIPELINED 25X18 BIT MULTIPLIER DSP48E1  |

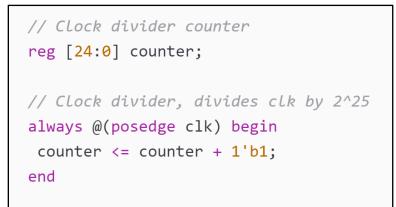

| <b>26</b> - CLOCK DIVIDER USED TO DRIVE DSP48E1                            |

#### **CHAPTER 1 - INTRODUCTION**

While Application Specific Integrated Circuits (ASICs) have been used as the primary hardware for digital logic implementation over the past few decades, the recent growth in popularity of Field Programmable Gate Arrays (FPGAs) now provides them with competition. FPGAs offer the reconfigurability of hardware post-manufacturing, which leads to more inexpensive implementation of digital circuitry. This flexibility is provided at the cost of optimality and efficiency towards a specific task which is a strong benefit of ASICs. Nevertheless, work has continued with FPGAs to leverage their reprogrammable digital hardware. Creative new applications for the FPGA include implementing the devices in data centers [1] and in hybrid-form with CPUs [2]. For data centers, work has been done to demonstrate the feasibility of allowing users to access portions of the device through the cloud and dividing the same chip amongst multiple tenants [1]. Further research has been conducted in combining the FPGA architecture with that of the existing CPU in modern computers. Doing so would allow for data transfer between the two devices, where FPGA reconfigurability and CPU efficiency can both be utilized [2].

Currently, popular FPGA vendors include Xilinx (AMD) [3], Altera (Intel) [4], and Lattice [5], among others. This work focuses on the Xilinx Artix-7 family of FPGAs and its Vivado Design Suite [6], [7] due to the popularity of the vendor and tools. Vivado offers the ability to generate bitstreams for their FPGAs from code written in a hardware description language (HDL). A commonly used HDL for this task is called Verilog. Using Verilog, one can describe the desired hardware configuration needed at register-transfer level (RTL), and then use Vivado to conduct the full flow of synthesis, place & route, and bitstream generation. As an alternative to proprietary tools like Vivado, the open-source synthesis toolchain SymbiFlow [8] seeks to emulate the same functions of synthesis, place & route, and bitstream generation for a variety of FPGA families. An important feature present in Vivado yet missing in SymbiFlow at the time of this writing is the processing of designs that use digital signal processing (DSP) blocks. These blocks are commonly used for bit multiplication and pattern detection in digital circuitry meant to emulate analog processes. One example of their use is in applications needing double-precision floating-point operations, presenting a large step forward in reducing necessary

1

hardware resources [9]. With DSP block support missing in the SymbiFlow toolchain, designs which could use DSP blocks are not able to successfully generate bitstreams for Artix-7 devices. The SymbiFlow authors demonstrate this in a table of implemented architectural features, copied here as Figure 1 [8]. The figure includes information for four different bitstream generation tools, each focused on FPGAs from a unique vendor. Project Icestorm [10] and Project Trellis [11] provide bitstream documentation for the Lattice iCE40 and Lattice ECP5 [5] architectures, respectively. Project X-Ray [12] documents the architecture of Xilinx 7-Series devices and is used in this work. Lastly, the QuickLogic [13] database documents bitstreams of the EOS-S3 and QLF-K4N8 FPGAs [14].

|                 | Project<br>Icestorm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Project<br>Trellis    | Project<br>X-Ray | QuickLogic<br>Database                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic Tiles:    | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~                     | ~                | <ul> <li>Image: A set of the set of the</li></ul> |

| - Logic         | <ul> <li>Image: A set of the set of the</li></ul> | <b>~</b>              | ✓                | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - Block RAM     | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~                     | *                | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advanced Tiles: | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~                     | <b>~</b> _       | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - DSP           | <ul> <li>Image: A set of the set of the</li></ul> | <b>~</b>              | ×                | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - Hard Blocks   | <ul> <li>Image: A set of the set of the</li></ul> | <b>~</b>              | ×                | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - Clock Tiles   | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>✓</li> </ul> | ✓                | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - IO Tiles      | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~                     | ~                | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Routing:        | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~                     | ~                | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - Logic         | <b>~</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ~                     | ✓                | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - Clock         | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~                     | ~                | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

**Figure 1** - Supported architecture for various popular FPGAs. Project X-Ray is the bitstream generation tool for the Xilinx Artix-7 family of boards (from [8])

Through this work, we diagnose points within the SymbiFlow toolchain that need modification to offer DSP block support. Completing these changes allows us to generate the first DSP design bitstream in SymbiFlow for Artix-7 FPGAs, enhancing the abilities of the opensource toolchain. From here, we broaden the functionality of the block to include support for the full 25x18 bit multiplier, a partial pre-adder, and pipelined multiplier support. The continuation of this introduction will provide a comparison of the Vivado Design Suite and the current state of the SymbiFlow toolchain. Then, an overview of the Artix-7 digital signal processing (DSP) block, referred to as the DSP48E1, will be provided.

#### **1.1 Xilinx Vivado**

Xilinx Vivado [7] is a proprietary computer-aided design tool used in FPGA development to create bitstreams. Its steps can be broken down into synthesis, implementation, and bitstream generation. Following synthesis, the user is provided with a gate-level netlist of the input RTL design along with resource utilization statistics, including the percentage of I/O ports and other logic gates used by the FPGA. Warnings and errors are shown if design rule checks fail during this step. The physical design step performs place and route of cells onto the target FPGA architecture. A visual representation of the routing network is made available via a graphical user interface (GUI). All mapped cells and the routed logic between them can be seen via this user interface. Finally, the bitstream generation step creates an FPGA-specific bitstream file that can be loaded onto an FPGA. Each of these functions provides information to the user in the form of log files and customization options. However, the proprietary nature of Vivado prevents sourcecode-level configurability and access to algorithms used in each step.

#### **1.2 SymbiFlow Toolchain**

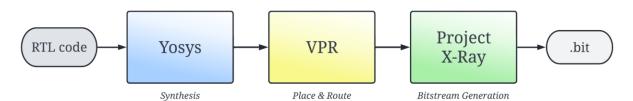

The purpose of the SymbiFlow toolchain [8] is to provide a free and open-source alternative to proprietary tools like Vivado for creating FPGA designs and bitstreams. In combining tools for synthesis, place & route, and bitstream generation, SymbiFlow allows users to take an RTL design and generate bitstreams functioning on FPGAs from several vendors. These FPGA vendors include Xilinx, Lattice, and QuickLogic as well as limited support for others. The Xilinx 7-series FPGAs are the focus of this study, with particular focus on the Artix-7 35TCSG324-1 FPGA. For the Artix-7 chip, SymbiFlow presents a flow using the following tools: Yosys [15] for synthesis, Versatile Place & Route (VPR) [16] for place and route, and Project X-Ray [12] for bitstream generation. A simplified visual representation of these tools within the toolchain can be seen in Figure 2. A version of each tool comes provided with installation of SymbiFlow.

3

### SymbiFlow Toolchain

Figure 2 - Visualization of tools involved in SymbiFlow toolchain

#### **1.3 DSP Blocks**

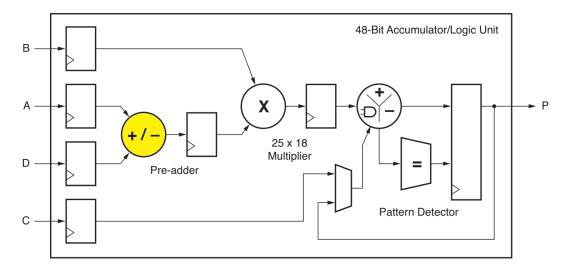

In FPGAs, DSP blocks are circuits used to implement multiplication, multiplyaccumulate, and similar arithmetic operations. The Arty 35T FPGA used in this work offers 90 of these DSP blocks spread across two columns, while the number available DSPs on larger Artix-7 chips can rise above 2,500 [7], [17]. The DSP block (also called a slice) native to Xilinx 7 series FPGAs is referred to as a DSP48E1. These cells can be used for a variety of tasks based on their architecture. Some of the functions provided by Xilinx for the DSP48E1 are multiply, multiply-accumulate, multiply add, three-input add, barrel shift, wide-bus multiplexing, magnitude comparator, bitwise logic functions, pattern detect, and wide counter [17].

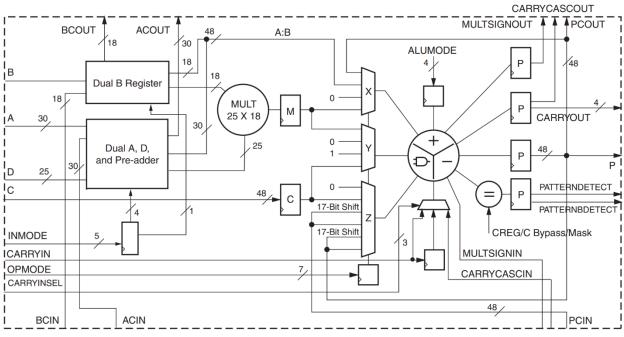

Figure 3 shows the internal architecture of the DSP48E1 block from the Xilinx 7 Series DSP48E1 Slice User Guide [17]. Data can enter the slice through input ports A, B, C, and D, each of which is wired internally through different logic functions. For instance, to implement the 25x18 bit multiplier, data can enter through the A and B ports. Alternatively, setting the "USE\_DPORT" parameter to "TRUE" in the RTL design, the multiplier could be configured to output the function B×D instead. The pre-adder can be included in a similar fashion to produce the function B×(A+D). The output of the DSP block is directed through the P port. In addition to the ports shown, reset and clock enable signals exist for the A through D inputs to allow for pipelining.

Figure 3 - Internal architecture of 7 Series DSP48E1 slice (from [17])

To determine the internal routing of signals and function implementation, there are three important inputs: INMODE, OPMODE, and ALUMODE. These signals are connected to multiplexers X, Y, and Z found between the logic units in the DSP48E1. INMODE is responsible for setting the output of the pre-adder, optionally choosing between inputs A and D as the output to be fed into the 25x18 multiplier. OPMODE controls the signals provided to the secondary logic unit. Finally, ALUMODE sets the function to be conducted within the secondary logic unit, taking in the outputs of multiplexers X, Y, and Z. An incorrect initialization of any of these values will result in unintended behavior of the DSP48E1 slice and are critical towards proper configuration of the block.

DSP blocks can be processed by Vivado using an intellectual property (IP) module called the DSP48 Macro [18]. Using the GUI, a user can instantiate the DSP48 Macro with their desired logic function and I/O signal bit widths. This approach simplifies needing to understand values for signals INMODE, OPMODE, and ALUMODE, as they are automatically set to implement the given logic function. A snapshot of the DSP48 Macro is shown in Figure 4. The user's defined DSP slice is in a simplified form on the left side of the window. In this example, a B×D multiplier was selected in the "Instructions" tab and the bit widths for these inputs are being set to three bits wide. This implements a 3x3 bit signed multiplier. Alternatively, if the MSB of each input is set to 0, a 2x2 bit unsigned multiplier can be implemented.

| P Symbol Instruction summary               | Component Name     | (bip_dsp48_mac    | ro_0          |                        |          |

|--------------------------------------------|--------------------|-------------------|---------------|------------------------|----------|

| Show disabled ports                        | Instructions Pip   | eline Options     | Implementatio | n                      |          |

|                                            | Input Port Propert | ies               |               |                        |          |

|                                            | D 3                |                   | 🛞 [2 - 25] A  | 3                      | [2 - 25] |

|                                            | В 3                |                   | 🛞 [2 - 18] C  | 48                     | [2 - 48] |

|                                            | CONCAT 48          |                   | [2 - 48]      |                        |          |

|                                            | Output Port Prope  | rties             |               |                        |          |

| <ul> <li>B[2:0]</li> <li>P[5:0]</li> </ul> | Output Proper      | ies Full Precisio | on v F        | Full Precision Width 6 |          |

| - D[2:0]                                   | Width              | 6                 | [             | 2 - 48]                |          |

|                                            | Additional ports   |                   |               |                        |          |

|                                            | Use ACOL           | JT Use            | BCOUT         | Use PCOUT              |          |

|                                            |                    |                   |               |                        |          |

Figure 4 - DSP48 Macro provided by Vivado for DSP block creation (from [7])

An important note about IP cores in Vivado is that unlike HDL written by the user, synthesized IP module information is encrypted post-synthesis. This approach denies the user access to configurability outside of the DSP48 Macro GUI and in the synthesized netlist. The need for encryption likely arises due to Xilinx's ownership of these IP cores; it is meant to prevent other individuals or companies from stealing their work and becoming a competitor. In all, Vivado provides support for the DSP48E1 slice with a detailed wizard allowing implementation of a user's exact needs.

At time of this writing, DSP block processing leading to bitstream generation has remained unimplemented for the Artix-7 SymbiFlow toolchain. The inclusion of DSP functionality is considered valuable due to the popularity of Artix-7 devices. Proprietary tools are often inaccessible for open-source contributors and individual researchers, lending to the need for further contributions towards open-source initiatives such as SymbiFlow. Addressing DSP implementation for the Artix-7 FPGA family offers insight into similar efforts for other FPGA families in the future.

#### **1.4 Thesis Outline**

This document is divided into five chapters, with this introduction serving as the first. An in-depth view into the tools that make up SymbiFlow, how it is used and its status for DSP block support for the Artix-7 family of FPGAs is presented in Chapter 2. Chapter 3 details the SymbiFlow FPGA architecture definitions and FPGA assembly (FASM) file formats used to generate bitstreams. A method of reverse engineering proper DSP FASM information from Vivado is presented as well. Chapter 4 breaks down all modifications made within SymbiFlow to support a basic use of the DSP48E1 block. Finally, Chapter 5 describes how this basic implementation has been expanded to include functions such as the 25x18 bit multiplier, partial pre-adder, and pipelining support.

#### **CHAPTER 2 - SYMBIFLOW**

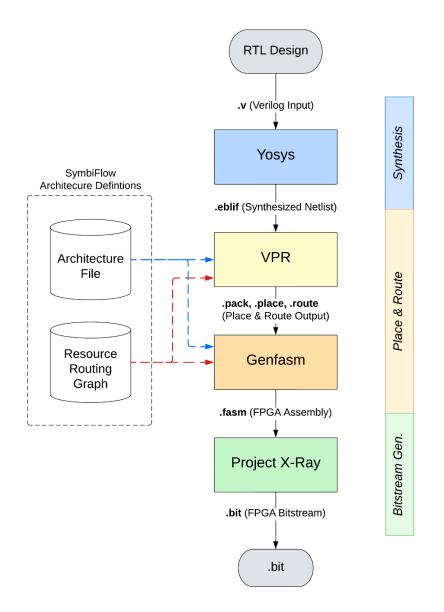

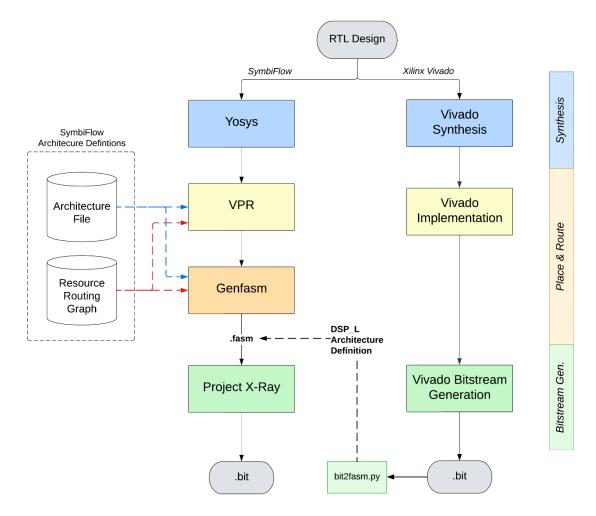

The SymbiFlow toolchain can be divided into its three main steps: synthesis, place & route, and bitstream generation. Figure 5 provides a detailed view of how the tools accomplishing these tasks are able to communicate with one another by displaying their intermediate files. Further, it introduces the notion of the architecture file and routing resource graph. These two files and their importance for the addition of DSP blocks will be the focus of Chapter 3. In the following sections, each of these tools will be viewed in detail.

Figure 5 - Detailed SymbiFlow toolchain with architecture definitions and intermediate files

#### 2.1 Yosys

Yosys [15], [19], is an open-source synthesis tool developed by Claire Wolf. It is built as a framework around the University of California Berkeley's ABC [20] sequential synthesis and verification tool, providing several additional features which support mapping to a variety of popular FPGA families. For the purposes of this work, we use Yosys to take in Verilog-2005 register-transfer level (RTL) code and produce a synthesized netlist in lookup tables (LUTs), memory-based truth tables. Yosys is the first of three tools making up the SymbiFlow toolchain [8]. In SymbiFlow, Yosys synthesis is conducted in two passes to generate an extended BLIF file (EBLIF), which is subsequently passed into the place and route tool VPR.

Synthesis in Yosys is conducted over several passes, some of which include optimization of flip-flops or limiting the design to use LUTs in place of block random access memory (BRAM) modules. It is the subsequent technology mapping and optimizations that lead to the generation of a synthesized netlist from RTL input. When executing Yosys, there are three main commands that are commonly used. They are tailored towards the FPGA architecture that is used within this work. These commands are the following:

- read\_verilog

- synth\_xilinx

- write\_verilog

The "read\_verilog" command accepts as input one or more Verilog-2005 RTL files to be synthesized. The "synth\_xilinx" command is the Xilinx family specific synthesis command, utilizing Xilinx FPGA cell libraries to create a netlist from the RTL input. Lastly, "write\_verilog" instructs Yosys to print out its synthesized netlist for the design.

#### 2.2 VPR / Genfasm

During the second stage of the SymbiFlow toolchain, VPR receives the EBLIF netlist output of Yosys to conduct three steps: packing, placement, and routing [21], [22]. The packing step of VPR will use technology mapping to turn the EBLIF netlist into VPR's own form of netlist [16]. It makes use of the chip's architecture file to understand the ports and interconnects going into and from each tile of the FPGA. The next two steps, placement and routing, are equivalent to the steps in Vivado. The defined logic blocks are then assigned to locations within the chosen FPGA architecture through the placement step. Locations for instantiation can be chosen based on factors such as area or power efficiency. Once placed, VPR makes use of its routing graph to determine the path which signals between logic blocks will take across the FPGA. These paths are directly written as FASM feature statements at the end of VPR through a script called Genfasm. Information involving locations of switchboxes being used and which programmable interconnect points (PIPs) are being activated to route signals are printed to this file. During its runtime, VPR also outputs intermediary files such as .pack. .place, and .route files, which describe logic location and routing assignments, and the execution output log from each VPR step.

VPR generates a FASM file by the end of its execution. Each line of a FASM file is called a feature, and it specifies either a routing connection or other attribute of a specific tile at a specific location on the chip.

Two of the supplemental files needed to run VPR, the routing graph and architecture file for the FPGA, can be generated separately from the SymbiFlow toolchain. The SymbiFlow authors provide a repository through GitHub titled SymbiFlow Architecture Definitions, through which it is possible to contribute information for new families of FPGAs and generate new sets of these files [14], [23]. These files are necessary resources for incorporating DSP blocks into the Artix-7 architecture definitions and subsequent toolchain. The SymbiFlow architecture definitions will be explored further in Chapter 3.

#### 2.3 Project X-Ray

Project X-Ray serves as the final step in the SymbiFlow toolchain [12], [24]. It is responsible for taking in the FASM file provided by VPR and Genfasm, producing a bitstream that can be loaded onto the given FPGA. Most of Project X-Ray is a database repository, containing information on possible connections for all supported FPGA families. The Artix-7 portion of this database contains pin maps for many variations of the chip, including the Xilinx Artix-7 xc7a35tcsg324-1 that is used for our testing purposes. To generate a bitstream from the

10

FASM file, Project X-Ray will consult its list of segbits files [25]. These are a set of databases provided by Project X-Ray containing all possible FASM features for a given tile. The segbits files are necessary to translate FASM features to their appropriate bits in the bitstream. Each connection combination is associated with a bit in the bitstream that will either be toggled on or off depending on whether its feature is present in the FASM file. The fixed length bitstream can then be written by translating the features given to their respective bits from the segbits file before being uploaded to the FPGA.

#### 2.4 Using SymbiFlow

Along with the Yosys, VPR, and Project X-Ray tools, an example directory titled "symbiflow-examples" is provided with SymbiFlow [26]. This includes several designs showcasing how new users can gain familiarity with using the toolchain. One such example is "counter\_test", the code for which can be found in Figure 6.

```

# counter test

1

2

3

module top (

4

input clk,

5

output [3:0] led

6

);

7

8

localparam BITS = 4;

9

localparam LOG2DELAY = 22;

10

11

wire bufg;

12

BUFG bufgctrl (

13

.I(clk),

14

.0(bufg)

15

);

16

17

reg [BITS+LOG2DELAY-1:0] counter = 0;

18

19

always @(posedge bufg) begin

20

counter <= counter + 1;</pre>

21

end

22

23

assign led[3:0] = counter >> LOG2DELAY;

24

endmodule

```

Figure 6 - counter\_test.v, part of symbiflow-examples (from [26])

The counter\_test.v design consists of a clock and buffer with outputs connected to four LEDs. The design is written to count in binary and display the result on the LEDs every clock cycle. It is a simple design, but helpful for understanding how SymbiFlow can take a Verilog RTL file such as counter\_test.v and generate a working bitstream for the Artix-7 FPGA.

```

46 # Build design

47 all: ${BOARD_BUILDDIR}/${TOP}.bit

49 ${BOARD_BUILDDIR}:

mkdir -p ${BOARD_BUILDDIR}

52 ${BOARD BUILDDIR}/${TOP}.eblif: | ${BOARD BUILDDIR}

cd ${BOARD_BUILDDIR} && symbiflow_synth -t ${TOP} -v ${SOURCES} -d ${BITSTREAM_DEVICE} -p ${PARTNAME} ${XDC_CMD} 2>&1 >

55 ${BOARD_BUILDDIR}/${TOP}.net: ${BOARD_BUILDDIR}/${TOP}.eblif

cd ${BOARD_BUILDDIR} && symbiflow_pack -e ${TOP}.eblif -d ${DEVICE} ${SDC_CMD} 2>&1 > /dev/null

58 ${BOARD_BUILDDIR}/${TOP}.place: ${BOARD_BUILDDIR}/${TOP}.net

cd ${BOARD_BUILDDIR} && symbiflow_place -e ${TOP}.eblif -d ${DEVICE} ${PCF_CMD} -n ${TOP}.net -P ${PARTNAME} ${SDC_CMD}

61 ${BOARD_BUILDDIR}/${TOP}.route: ${BOARD_BUILDDIR}/${TOP}.place

cd ${BOARD_BUILDDIR} && symbiflow_route -e ${TOP}.eblif -d ${DEVICE} ${SDC_CMD} 2>&1 > /dev/null

64 ${BOARD_BUILDDIR}/${TOP}.fasm: ${BOARD_BUILDDIR}/${TOP}.route

cd ${BOARD_BUILDDIR} && symbiflow_write_fasm -e ${TOP}.eblif -d ${DEVICE} 2>&1 > /dev/null

67 ${BOARD_BUILDDIR}/${TOP}.bit: ${BOARD_BUILDDIR}/${TOP}.fasm

cd ${BOARD_BUILDDIR} && symbiflow_write_bitstream -d ${BITSTREAM_DEVICE} -f ${TOP}.fasm -p ${PARTNAME} -b ${TOP}.bit

```

Figure 7 - common.mk Makefile used to call steps with SymbiFlow (from [26])

SymbiFlow operates from a Makefile which references the tools in the toolchain with their respective commands. A snapshot of the call steps within the *common.mk* Makefile can be seen in Figure 7. The final target "\${BOARD\_BUILDIR}/\${TOP}.bit" to generate a bitstream from the FASM file is called first. This step, as well as all others, has a dependency on the previous step in the flow being completed first. For the ".bit" step, it requires that the ".fasm" step was run to confirm that there is a FASM file to generate a bitstream from. These dependencies cascade down the toolchain until Yosys can be executed to create the synthesized netlist EBLIF file. Table 1 below shows each command found within the file common.mk. In order, they will take in an RTL input to Yosys and put the synthesized netlist through place and route in VPR, while ending with bitstream generation with Project X-Ray. While Project X-Ray has many functions, one of its main tasks is in housing a database of hundreds of FPGA

architectures. This tool is used to translate each line of a FASM file to exact bits within a bitstream, determining which features should be set ON or OFF based on entries in its database.

| Command                   | Description                                                                                                                                              |

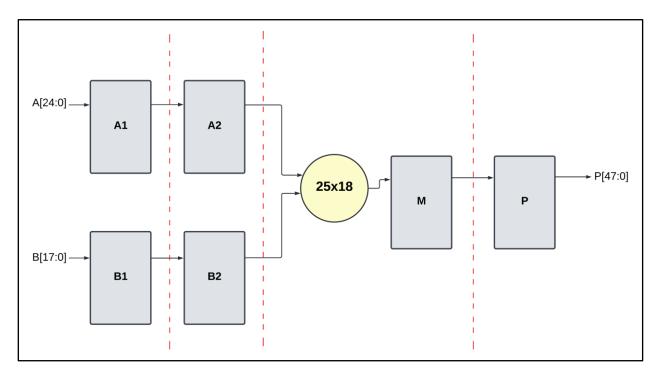

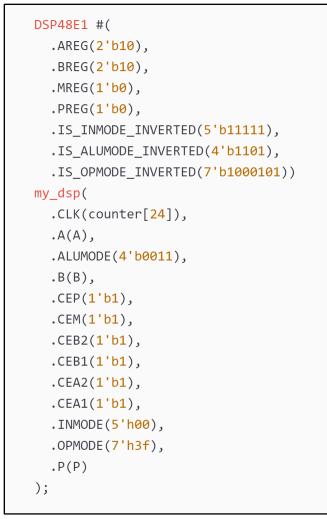

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|