Simpson, Kyle Andrew (2022) *Online learning on the programmable dataplane*. PhD thesis.

### https://theses.gla.ac.uk/83235/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

# Online Learning on the Programmable Dataplane

### Kyle Andrew Simpson

Submitted in fulfilment of the requirements for the degree of  $Doctor\ of\ Philosophy$

SCHOOL OF COMPUTING SCIENCE

College of Science and Engineering University of Glasgow

OCTOBER 2022

© Kyle Andrew Simpson

### **Abstract**

This thesis makes the case for managing computer networks with datadriven methods—automated statistical inference and control based on measurement data and runtime observations-and argues for their tight integration with programmable dataplane hardware to make management decisions faster and from more precise data. Optimisation, defence, and measurement of networked infrastructure are each challenging tasks in their own right, which are currently dominated by the use of hand-crafted heuristic methods. These become harder to reason about and deploy as networks scale in rates and number of forwarding elements, but their design requires expert knowledge and care around unexpected protocol interactions. This makes tailored, per-deployment or -workload solutions infeasible to develop. Recent advances in machine learning offer capable function approximation and closed-loop control which suit many of these tasks. New, programmable dataplane hardware enables more agility in the networkruntime reprogrammability, precise traffic measurement, and low latency on-path processing. The synthesis of these two developments allows complex decisions to be made on previously unusable state, and made quicker by offloading inference to the network.

To justify this argument, I advance the state of the art in data-driven defence of networks, novel dataplane-friendly online reinforcement learning algorithms, and in-network data reduction to allow classification of switchscale data. Each requires co-design aware of the network, and of the failure modes of systems and carried traffic. To make online learning possible in the dataplane, I use fixed-point arithmetic and modify classical (non-neural) approaches to take advantage of the SmartNIC compute model and make use of rich device-local state. I show that data-driven solutions still require great care to correctly design, but with the right domain expertise they can improve on pathological cases in DDoS defence, such as protecting legitimate UDP traffic. In-network aggregation to histograms is shown to enable accurate classification from fine temporal effects, and allows hosts to scale such classification to far larger flow counts and traffic volume. Moving reinforcement learning to the dataplane is shown to offer substantial benefits to stateaction latency and online learning throughput versus host machines; allowing policies to react faster to fine-grained network events. The dataplane environment is key in making reactive online learning feasible—to port further algorithms and learnt functions, I collate and analyse the strengths of current and future hardware designs, as well as individual algorithms.

I'm astounded whenever I finish something. Astounded and distressed. My perfectionist instinct should inhibit me from finishing; it should inhibit me from even beginning. But I get distracted and start doing something. What I achieve is not the product of an act of will but of my will's surrender. I begin because I don't have the strength to think; I finish because I don't have the courage to quit. This book is my cowardice.

-Fernando Pessoa, The Book of Disquiet (p. 156)

### **Acknowledgements**

First of all, I'd like to thank my wife and best friend Vanessa, for her tireless support and persistence in hearing my a) writing woes, b) angry tirades about software in general, and c) despair over experiment fixes running long into the night—most often in the run up to conference deadlines. I couldn't have made it this far without you. I also owe my family an inestimable debt for their their lifelong help and guidance: to my parents Elaine and Ronnie for always being there and always looking our for me (including making a mid-pandemic move-in possible), my brother Rhys for being there to bounce ideas off of (and hold many technically-involved emulator discussions), and my sister Brooklyn for her constant support. You've all always believed in me and in what I could achieve, and I can't ever pay that back. Lastly, Charlie¹, the best cat, for providing many loud, quizzical meows and for ¹ bestowing upon me the highest honour as Chief Feeder.

<sup>1</sup> Unabbreviated: Beloved Sir Charles of House Cattington, Esq., first of his name.

From Netlab, I'd like to thank Prof. Dimitrios Pezaros for his guidance, trust, and advice over the years, as well as the rest of my supervisory team—Simon Rogers and Angelos Marnerides—for their input. To the other Netlab PhD students in particular, Mircea Iordache-Şică, Stefanos Sagkriotis, and Haruna Umar Adoga: our daily meetings have been an essential wellspring of emotional support for me all through the pandemic. It's been great to look out for one another, in terms of morale and to keep engaged and challenged on what we're each working on. Not to mention the many proof-readings of various lumps of text, lovingly provided free-of-charge!

For many a fine lunch at *The Wee Curry Shop* and vibrant discussion (albeit on algorithmics and academic politics!), I have to thank Patrick Prosser, Ciaran McCreesh, James Trimble, Craig Reilly, Blair Archibald, and Ruth Hoffmann. To Patrick in particular, thank you for showing me that research was somewhere I could be and succeed in, and for helping put me down this path.

I'd like to thank all of the co-residents of F101 through the years; Yousef Alhaizaey, Dhahi Alshammari, Dejice Jacob, Thomas Koehler, Lito Michala, Sangkyu Park, Adrian Ramsingh, and Cris Urlea. The discussions, feedback on ideas and GLASS talks, technical help, and an occasionally borrowed poster tube have all been greatly appreciated.

I've met and known so many amazing people through the department via

lunches, cryptic crosswords, puzzles, and Friday coffees that are but a distant memory now. A lot of us started around the same time-or at least met constantly through boardgames, D&D, and mutual friends: Benjamin Bumpus, Marco Cook, Frances Cooper, Patrizia Di Campli San Vito, Natascha Harth, Ellen & William Kavanagh, Charlie Rutherford, Jess Ryan, Gözel Shakeri, Lovisa Sundin, and Tom Wallis. Studying was that much livelier for having you around, and you made Lilybank Gardens somewhere worth going for 5 years. To Andrew Doctor, Sami Kelly, Shaun Lithgow, Callum Milne, Jen Patrick, and Simon Tait: thank you for being lifelong friends (and keeping me sane and socialised!). There are so many other folks I've met through the department, Waterdeep, tea society, and teaching that have been great all around: Vivian Band, Simon Fowler, Katie Heeps, George Holt, Shaun Macdonald, David Maxwell, Michael McKay, Murray McKinstray, Flora McNulty, Stephen McQuistin, Alex Pancheva, Iulia Paun, Will Pettersson, Rebecca Rae, Jenny Savage, Michel Steuwer, Ritchie Walker, and Mihail Yanev.

To Derek 'Del' Hamilton, Douglas MacFarlane, Stewart MacNeill, Robert Nugent and the SoCS support staff, thanks for putting up with our unceasing demands around keeping G131 setup with whatever shiny toys we happened to acquire. To Helen Border and Gail Reat, thanks for keeping teaching and demonstrating as such a tightly run ship.

I met some fantastic people at ESnet, whom I must thank for an incredible 3 month stint in Berkeley, exciting work, and great hills to run on. Crucially, you helped reshape my research direction and introduced me to the joys of programmable dataplane hardware. Richard Czivá, Chin Guok, Yatish Kumar, Bruce Mah, Inder Monga; I hope to work with you again one day soon.

Between various online pastimes—namely, FFXIV and all manner of tabletop shenanigans—I've known and sometimes drifted away from a great number of folk who've offered distant support in their own way. Thank you Bernhard, Cam, Cameron, Carlos, Charles, Fred, Ian, James, Katie, Kyle, Lily, Mal, Olivia, Sasha, Sphenio, and Ves. For routinely keeping me up 'til 2AM—and later—but making it all worthwhile in exchange.

Additional thanks go to Dimitrios Pezaros, Jeremy Singer, Haruna Umar Adoga, Ian Salvagio, my father Ronnie Simpson, and Mircea Iordache-Şică for proof-reading part or all of this thesis. I would like to also thank Colin Perkins, Gianni Antichi, and Jonathan Grizou for the technical, challenging, and fun viva—and by extension for also reading this (very long!) thesis.

And at last, a begrudging 'thanks' to my anonymous reviewers over the years, who have been ever as much my mentors as they have my torturers and gaolers. For the *constructive* advice, I can only thank you.

### **Original Publications**

This thesis is based on the following publications:

- SIMPSON, K. A., ROGERS, S., & PEZAROS, D. P. (2020). Per-Host DDoS Mitigation by Direct-Control Reinforcement Learning. *IEEE Trans. Network and Service Management*, 17(1), 103–117. https://doi.org/10.1109/TNSM.2019.2960202

- SIMPSON, K. A., CZIVA, R., & PEZAROS, D. P. (2020). Seiðr: Dataplane Assisted Flow Classification Using ML. IEEE Global Communications Conference, GLOBECOM 2020, Virtual Event, Taiwan, December 7-11, 2020, 1-6. https://doi.org/10.1109/GLOBECOM42002.2020.9348063

- SIMPSON, K. A., & PEZAROS, D. P. (2021). Online RL in the programmable dataplane with OPaL. In G. Carle & J. Ott (Eds.), CoNEXT '21: The 17th International Conference on emerging Networking Experiments and Technologies, Virtual Event, Munich, Germany, December 7-10, 2021 (pp. 471-472). ACM. https://doi.org/10.1145/3485983.3493345

- SIMPSON, K. A., & PEZAROS, D. P. (2022). Revisiting the Classics: Online RL in the Programmable Dataplane [SICSA PhD Conference Best Paper '22]. 2022 IEEE/IFIP Network Operations and Management Symposium, NOMS 2022, Budapest, Hungary, April 25-29, 2022, 1–10. https://doi.org/10.1109/NOMS54207.2022.9789930

Code, data, and past writings for chapters 4 and 5 are publicly available in:

- https://github.com/FelixMcFelix/rln-dc-ddos-paper,

- https://github.com/FelixMcFelix/pdp-rl-paper.

Code and data used to analyse protocol distributions in *Center for Applied Internet Data Analysis* (CAIDA) traces (appendix A) are publicly available in https://github.com/FelixMcFelix/caida-stats, and code for the microbenchmark used to generate fig. 2.5 is available in https://github.com/FelixMcFelix/dp-perf-tester. Opus traffic generation code and traces are available at https://github.com/FelixMcFelix/opus-voip-traffic, and capture code is part of https://github.com/FelixMcFelix/felyne-bot (appendix B).

## **Notes on Typesetting**

Body text is set in 11 pt *Libertinus Serif*, a free, libre, and more visually pleasing Times New Roman alternative widely used in ACM publications. Headings, the table of contents, and some text elements (such as complexity classes) are set in sans-serif using the free, humanist *Alegreya Sans* typeface. Numerals, outside of certain mathematical contexts, are set in old-style figures.

This thesis is typeset, first and foremost, around readability. As such, the main body width is set to 11.75 cm, which provides a comfortable 60–65 characters per line. The remaining page width up to the University specification (15.5 cm) is used to provide lengthier asides in the margins<sup>1</sup>, which I find considerably less disruptive than footnotes. Line-spacing is set to 136.8 % to compensate, which achieves similar words per page to the University standard (490–520 without paragraph breaks, excluding sidenotes). *Practical Typography* by Matthew Butterick has been an excellent guide in shaping these design choices.

<sup>1</sup> Much like this one. This allows for more interesting comments and/or explanations without disrupting the main flow of the document.

Some colour coding is used for links and markers of various classes:

- Citations to other referenced works,

- Section and Acronym references, which are all functioning links,

- URLs, particularly in the bibliography,

- and Markers indicating key claims in the thesis statement (e.g., \$1) or key elements of other works' design which benefit from glance value (e.g., \$\mathcal{S}\$, \$\mathcal{A}\$).

# **Contents**

| ΑŁ  | ostrac   | t         |                                       | i    |

|-----|----------|-----------|---------------------------------------|------|

| Ac  | know     | ledgem    | ents                                  | iii  |

| Or  | iginal   | l Publica | itions                                | ν    |

| No  | otes o   | n Typese  | etting                                | vi   |

| Lis | st of Ta | ables     |                                       | xii  |

| Lis | st of Fi | gures     |                                       | xiii |

| Ac  | ronyn    | ns        |                                       | xvii |

| 1   | Intro    | oduction  | 1                                     | 1    |

|     | 1.1      | Thesis    | statement                             | 5    |

|     | 1.2      | Contri    | butions                               | 6    |

|     | 1.3      | Thesis    | outline and structure                 | 7    |

| 2   | Prog     | gramma    | ble Computer Networks                 | 11   |

|     | 2.1      | From f    | ixed-function to software-defined     | 13   |

|     |          | 2.1.1     | Active networking                     | 13   |

|     |          | 2.1.2     | Software-defined networking           | 17   |

|     | 2.2      | Moder     | n programmable dataplanes             | 21   |

|     |          | 2.2.1     | Virtualisation and commodity machines | 23   |

|     |          | 2.2.2     | Specialised hardware                  | 25   |

|     |          | 2.2.3     | The return of active networking?      | 29   |

|     |          | 2.2.4     | Frontiers in programmable networks    | 31   |

|     | 2.3      | Offloa    | ding and in-network compute           | 36   |

|     |          | 2.3.1     | Host offloading technologies          | 39   |

|     |          | 2.3.2     | Frameworks for automatic offloading   | 45   |

|     | 2.4      | In-net    | work compute use cases                | 49   |

|     |          | 2 / 1     | Network monitoring                    | 10   |

|   |      | 2.4.2    | Service acceleration and offloading                           | 51  |

|---|------|----------|---------------------------------------------------------------|-----|

|   |      | 2.4.3    | Transports, protocols, and routing                            | 52  |

|   |      | 2.4.4    | Machine learning                                              | 54  |

|   | 2.5  | Summ     | ary                                                           | 56  |

| 3 | Data | ı-driven | Networking                                                    | 59  |

|   | 3.1  | Use cas  | ses                                                           | 60  |

|   |      | 3.1.1    | Network management                                            | 61  |

|   |      | 3.1.2    | Protocol optimisation and design                              | 65  |

|   |      | 3.1.3    | Security, defence, and verification                           | 67  |

|   |      | 3.1.4    | Multimedia                                                    | 69  |

|   |      | 3.1.5    | Resource placement and management                             | 71  |

|   |      | 3.1.6    | Takeaways for effective data-driven networking                | 74  |

|   | 3.2  | Functio  | on approximation                                              | 77  |

|   |      | 3.2.1    | Linear Tile Coding                                            | 78  |

|   |      | 3.2.2    | Neural Networks                                               | 80  |

|   | 3.3  | Learnir  | ng an approximation                                           | 82  |

|   |      | 3.3.1    | Gradient descent                                              | 83  |

|   |      | 3.3.2    | Reinforcement learning                                        | 84  |

|   |      | 3.3.3    | Demonstrating RL: Sarsa                                       | 86  |

|   |      | 3.3.4    | The RL algorithm design space                                 | 86  |

|   |      | 3.3.5    | RL use considerations                                         | 89  |

|   | 3.4  | Numer    | rical representations for embedded ML                         | 90  |

|   |      | 3.4.1    | Floating-point                                                | 92  |

|   |      | 3.4.2    | Fixed-point and binary                                        | 93  |

|   | 3.5  | Challer  | nges                                                          | 94  |

|   |      | 3.5.1    | Input data and simulation                                     | 94  |

|   |      | 3.5.2    | Generality                                                    | 95  |

|   |      | 3.5.3    | Interpretability and verification                             | 96  |

|   | 3.6  | Securit  | у                                                             | 98  |

|   |      | 3.6.1    | Evasion attacks and adversarial examples                      | 98  |

|   |      | 3.6.2    | Poisoning attacks                                             | 102 |

|   |      | 3.6.3    | Data extraction and privacy                                   | 104 |

|   | 3.7  | Summ     | ary                                                           | 106 |

| 4 | DDo  | S Prever | ntion by Multi-agent Reinforcement Learning                   | 109 |

|   | 4.1  | Distrib  | uted denial of service                                        | 111 |

|   |      | 4.1.1    | Volumetric attacks                                            | 112 |

|   |      | 4.1.2    | Contributing factors in the detection problem $\ldots \ldots$ | 114 |

|   |      | 4.1.3    | Defences                                                      | 115 |

|   |      |          |                                                               |     |

|   | 4.2  | Motivation                          | 7 |  |  |

|---|------|-------------------------------------|---|--|--|

|   | 4.3  | Threat model                        |   |  |  |

|   | 4.4  | Per-flow RL agent designs           | 9 |  |  |

|   |      | 4.4.1 System design and assumptions | 9 |  |  |

|   |      | 4.4.2 Algorithm                     | ) |  |  |

|   |      | 4.4.3 Feature space                 | 1 |  |  |

|   |      | 4.4.4 Reward function               | 2 |  |  |

|   |      | 4.4.5 Action space                  | 3 |  |  |

|   |      | 4.4.6 Systems considerations        | 5 |  |  |

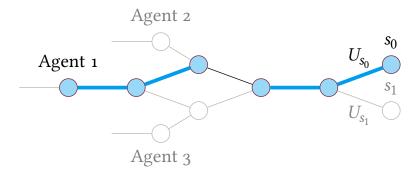

|   | 4.5  | System architecture                 | 5 |  |  |

|   |      | 4.5.1 Core and RL executor          | 5 |  |  |

|   |      | 4.5.2 Stats API and collectors      | 3 |  |  |

|   |      | 4.5.3 Flowstate database            | 3 |  |  |

|   |      | 4.5.4 Agent switches                | 9 |  |  |

|   | 4.6  | Rethinking the state space          | 9 |  |  |

|   | 4.7  | Traffic modelling                   | 3 |  |  |

|   |      | 4.7.1 Network design                | 3 |  |  |

|   |      | 4.7.2 TCP (HTTP) traffic model      | 4 |  |  |

|   |      | 4.7.3 UDP (Opus/VoIP) traffic model | 4 |  |  |

|   |      | 4.7.4 Attack traffic model          | 5 |  |  |

|   | 4.8  | Evaluation                          | 5 |  |  |

|   |      | 4.8.1 Single destination            | 5 |  |  |

|   |      | 4.8.2 Multiple destinations         | 5 |  |  |

|   |      | 4.8.3 Parameters                    | 7 |  |  |

|   | 4.9  | Results                             | 3 |  |  |

|   |      | 4.9.1 Congestion-unaware traffic    | 3 |  |  |

|   |      | 4.9.2 Congestion-aware traffic      | 9 |  |  |

|   |      | 4.9.3 Increased attack volume       | 1 |  |  |

|   |      | 4.9.4 Computational cost            | 1 |  |  |

|   | 4.10 | Discussion                          | 1 |  |  |

|   | 4.11 | Summary                             | 4 |  |  |

|   |      |                                     |   |  |  |

| 5 |      | etwork Reinforcement Learning 147   |   |  |  |

|   | 5.1  | Design                              |   |  |  |

|   |      | 5.1.1 Interaction and system model  |   |  |  |

|   |      | 5.1.2 Data format                   | - |  |  |

|   |      | 5.1.3 Algorithm                     |   |  |  |

|   | 5.2  | Implementation                      |   |  |  |

|   |      | 5.2.1 Policy storage                | 1 |  |  |

|   |       | 5.2.2    | Action and update computation                        | 162 |

|---|-------|----------|------------------------------------------------------|-----|

|   |       | 5.2.3    | Agent-environment communication                      | 165 |

|   |       | 5.2.4    | Intra-agent communication                            | 166 |

|   |       | 5.2.5    | Reconfigurability                                    | 169 |

|   |       | 5.2.6    | Work allocation                                      | 169 |

|   | 5.3   | Evalua   | tion                                                 | 171 |

|   |       | 5.3.1    | Experimental setup                                   | 171 |

|   |       | 5.3.2    | Experiments                                          | 172 |

|   | 5.4   | Result   | s and discussion                                     | 175 |

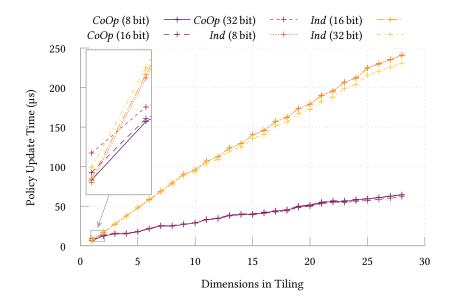

|   |       | 5.4.1    | Raw inference and learning performance               | 175 |

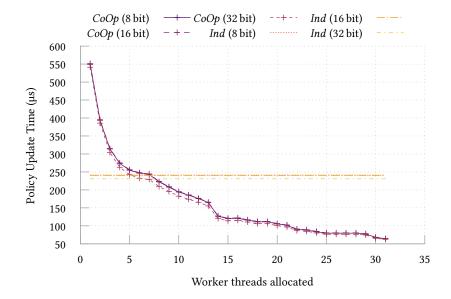

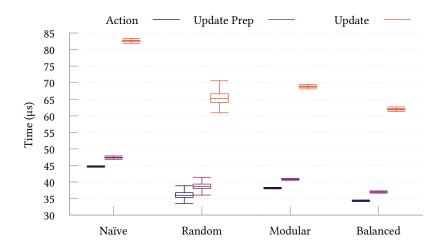

|   |       | 5.4.2    | Work allocation                                      | 181 |

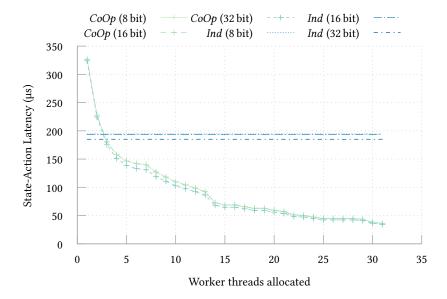

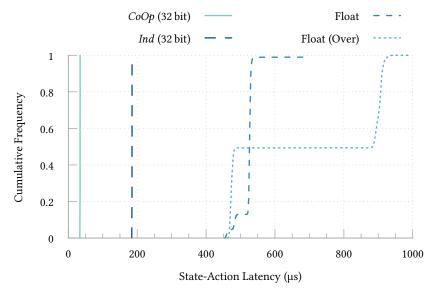

|   |       | 5.4.3    | End-to-end RL latency                                | 181 |

|   |       | 5.4.4    | Co-existence with the dataplane                      | 184 |

|   |       | 5.4.5    | Resource requirements                                | 184 |

|   |       | 5.4.6    | Deployability                                        | 186 |

|   |       | 5.4.7    | Magnitude comparisons against PDP ML                 | 187 |

|   | 5.5   | Potent   | ial integrations                                     | 187 |

|   |       | 5.5.1    | In-network DDoS defence                              | 187 |

|   |       | 5.5.2    | Network deployment considerations                    | 189 |

|   | 5.6   | Summ     | ary                                                  | 189 |

| 6 | Scala | able Flo | w Classification                                     | 191 |

|   | 6.1   | Telem    | etry aggregation in the dataplane                    | 193 |

|   |       | 6.1.1    | Histogram generation                                 | 193 |

|   |       | 6.1.2    | Histogram transmission                               | 196 |

|   |       | 6.1.3    | Accurate, precise and high-resolution timestamping . | 199 |

|   | 6.2   | TCP co   | ngestion control classification                      | 199 |

|   | 6.3   | Evalua   | tion                                                 | 201 |

|   |       | 6.3.1    | Datasets                                             | 201 |

|   |       | 6.3.2    | Experimental setup                                   | 202 |

|   |       | 6.3.3    | Classification performance                           | 202 |

|   |       | 6.3.4    | Training and inference costs                         | 206 |

|   |       | 6.3.5    | Switch resource usage                                | 206 |

|   |       | 6.3.6    | Quantifying in-network data aggregation              | 206 |

|   | 6.4   | Summ     | ary                                                  | 207 |

| 7 | Cond  | lusion   |                                                      | 209 |

| • | 7.1   |          | ed for co-design                                     | 210 |

|   | 7.2   |          | enging security context                              | 211 |

|   | 7.2   |          | directions                                           | 212 |

| Α  | Prot  | ocol Trends in CAIDA Traces           | 215 |

|----|-------|---------------------------------------|-----|

|    | A.1   | Dataset description                   | 215 |

|    | A.2   | Data processing methodology           | 216 |

|    | A.3   | Results                               | 217 |

| В  | Opu   | s VoIP Traffic Capture and Generation | 223 |

|    | B.1   | Voice session behaviour               | 224 |

|    | B.2   | Capture and storage                   | 225 |

|    | B.3   | Traffic generation                    | 226 |

| C  | Netr  | onome NFP Architectural Details       | 227 |

|    | C.1   | Execution model                       | 227 |

|    | C.2   | Memory                                | 228 |

| D  | OPa   | L Control Protocol                    | 231 |

| Re | feren | ces                                   | 235 |

# **List of Tables**

| 4.1 | Tile coding windows for traffic features                                                            |

|-----|-----------------------------------------------------------------------------------------------------|

| 4.2 | Average reward for combinations of model, host density and traffic class with a single destination  |

| 4.3 | Average reward for combinations of model, host density and traffic class with multiple destinations |

| 4.4 | Average reward versus attack volume                                                                 |

| 5.1 | IPC messaging costs on NFP hardware 166                                                             |

| 5.2 | Latencies and computation times for OPaL versus commodity hardware hosts                            |

| 5.3 | Action and update throughputs for OPaL versus commodity hardware hosts                              |

| 5.4 | NFP memory cost incurred by OPaL when built to use 1 and 4 MEs (32 bit)                             |

| 6.1 | Seiðr register map and required sizes using an an <i>h</i> -bit hash. 196                           |

| 6.2 | CNN architecture for 100-entry histograms 201                                                       |

| 6.3 | Training, inference, and runtime memory costs of CNN and $k$ NN models                              |

| C.1 | NFP memory hierarchy, locations, and sizes                                                          |

# **List of Figures**

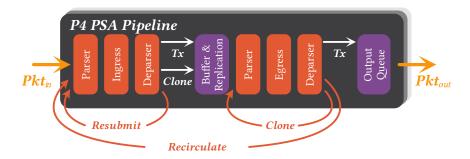

| 2.1 | Pipeline stages and forwarding paths of the P4 PSA                                                                                   | 28  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|-----|

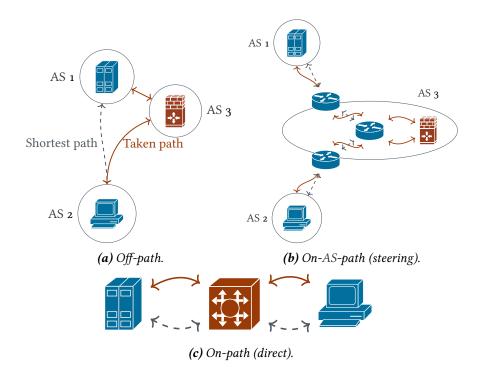

| 2.2 | The spectrum of on-path traffic processing                                                                                           | 37  |

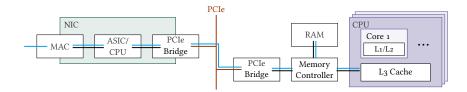

| 2.3 | A simplified view of the physical packet path on host machines                                                                       | 40  |

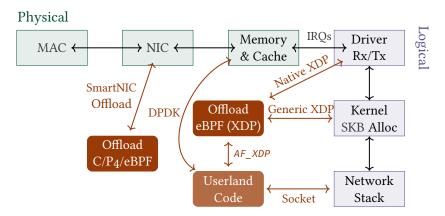

| 2.4 | The logical packet processing stack on host machines, and how the DPDK and XDP frameworks interface with it and user code            | 41  |

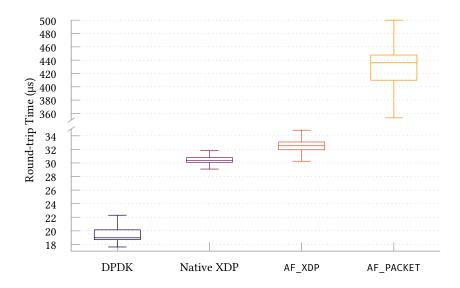

| 2.5 | A microbenchmark of bypass/offload frameworks' effects on packet RTTs                                                                | 45  |

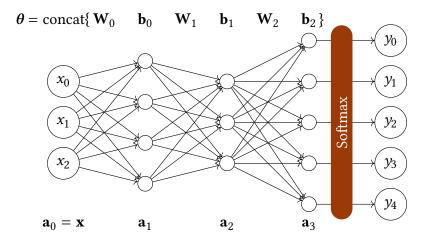

| 3.2 | An example fully-connected neural network                                                                                            | 81  |

| 3.1 | Operation of a single neuron                                                                                                         | 81  |

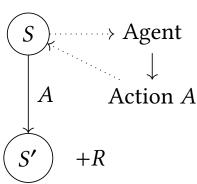

| 3.3 | A motivating example for MDPs in handling delayed rewards.                                                                           | 84  |

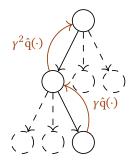

| 3.4 | An illustration of how value adjustments in single-step RL propagate backwards through a state trajectory                            | 86  |

| 3.5 | An end-to-end example of Sarsa selecting an action using a tile-coded policy                                                         | 87  |

| 3.6 | An end-to-end example of Sarsa updating the values for a chosen action using a tile-coded policy                                     | 87  |

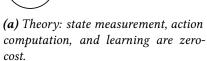

| 3.7 | Illustrating state slippage in an asynchronous RL agent                                                                              | 91  |

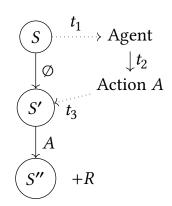

| 4.1 | Global state selection for a flow across a monitored AS                                                                              | 121 |

| 4.2 | VNF and OpenFlow-based system architecture for an RL-driven DDoS mitigation system                                                   | 127 |

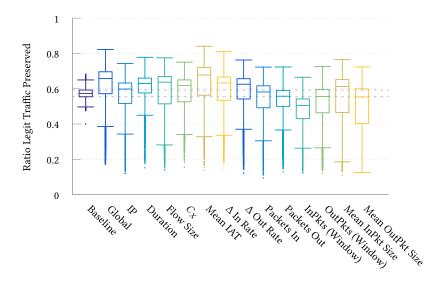

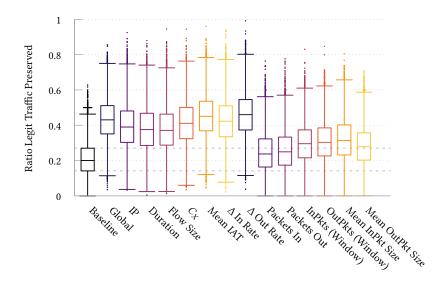

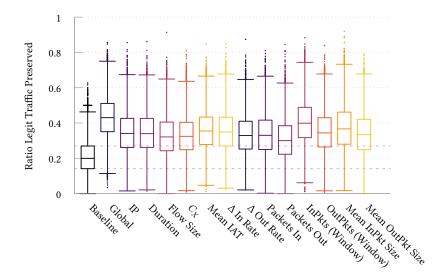

| 4.3 | Learnt performance of <i>Instant</i> agents when benign traffic is UDP-like, using only a single feature as a basis for decisions.   | 129 |

| 4.4 | Learnt performance of <i>Instant</i> agents when benign traffic is UDP-like, jointly tiling each feature with the last action taken. | 130 |

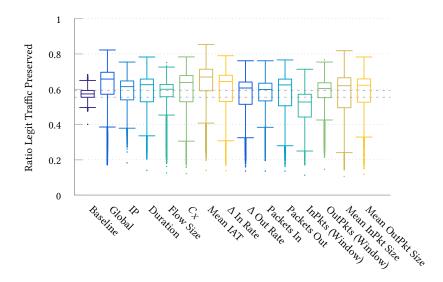

| 4.5  | Learnt performance of <i>Instant</i> agents when benign traffic is TCP-like, using only a single feature as a basis for decisions. 130   |

|------|------------------------------------------------------------------------------------------------------------------------------------------|

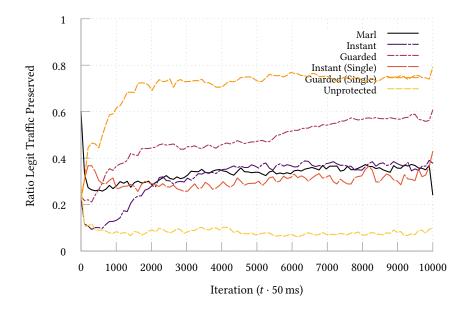

| 4.6  | Learnt performance of <i>Instant</i> agents when benign traffic is TCP-like, jointly tiling each feature with the last action taken. 131 |

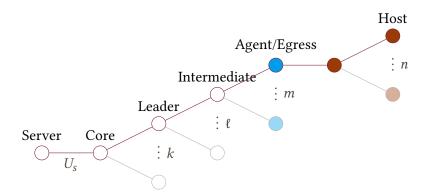

| 4.7  | Tree-structured network topology diagram for evaluating a single-destination network                                                     |

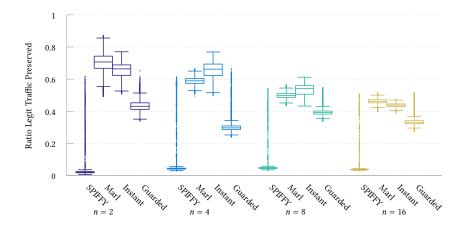

| 4.8  | Online performance for Opus benign traffic in a single-destination network, multi-agent mode                                             |

| 4.9  | Online performance for HTTP benign traffic in a single-destination network, single-agent mode                                            |

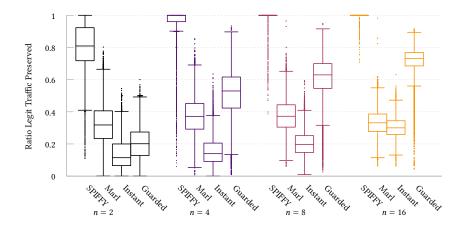

| 4.10 | Online performance of standard and single-agent models in a single-destination network with $n=16$ hosts per egress point, HTTP traffic  |

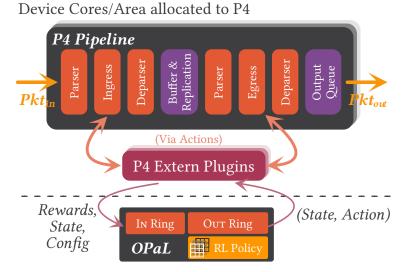

| 5.1  | OPaL's off-path interaction model with respect to a co-hosted P4 dataplane                                                               |

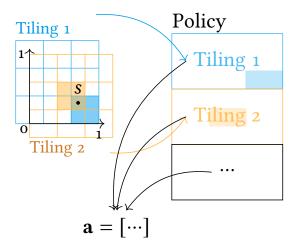

| 5.2  | A visualisation of how tile-coding can be split into subtasks as a map-reduce problem                                                    |

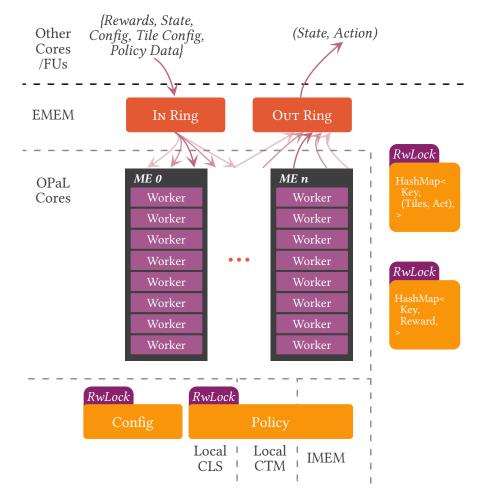

| 5.3  | Architectural diagram for OPaL's <i>Ind</i> firmware design 163                                                                          |

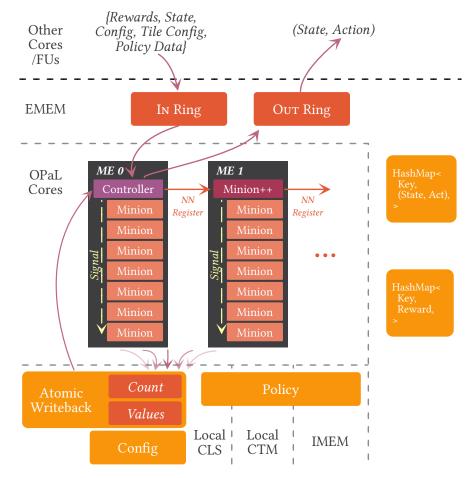

| 5.4  | Architectural diagram for OPaL's ${\it CoOp}$ firmware design 164                                                                        |

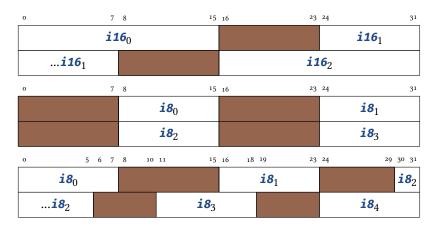

| 5.5  | Bit-packing layouts for emulated SIMD addition using atomics. 168                                                                        |

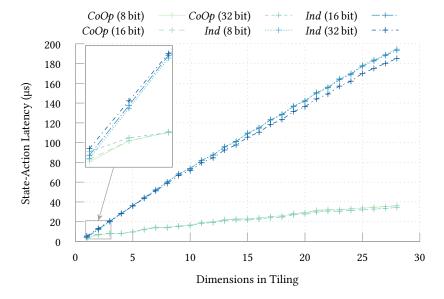

| 5.6  | OPaL's combined update and inference time as the degree of parallelism is varied                                                         |

| 5.7  | OPaL's state-action latency as the degree of parallelism is varied                                                                       |

| 5.8  | OPaL's combined update and inference time as the number of tiling dimensions is varied                                                   |

| 5.9  | OPaL's state-action latency as the number of tiling dimensions is varied                                                                 |

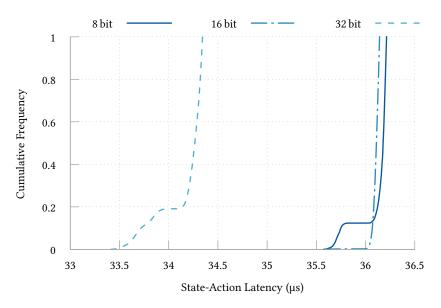

| 5.10 | Cumulative state-action latency plots for OPaL and host-based execution                                                                  |

| 5.11 | Action and update compute times in a 32 bit <i>CoOp</i> agent under different work schedulers                                            |

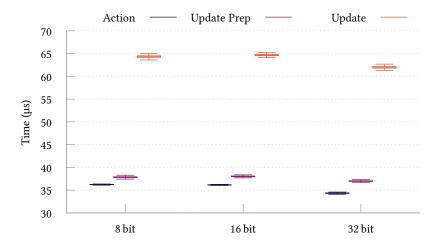

| 5.12 | Stage times of OPaL's <i>Balanced</i> allocator at 8 bit, 16 bit and 32 bit depths                                                       |

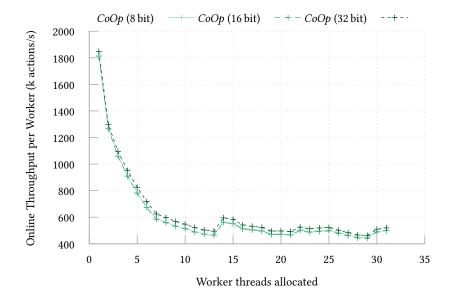

| 5.13 | OPaL- <i>CoOp</i> 's online throughput per core as the number of worker threads is varied                                                |

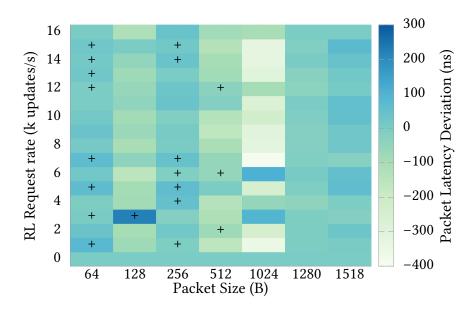

| 5.14 | Deviations in 99 $^{th}$ percentile cross-traffic RTTs for an OPaL agent processing 0–16k updates/s                                                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

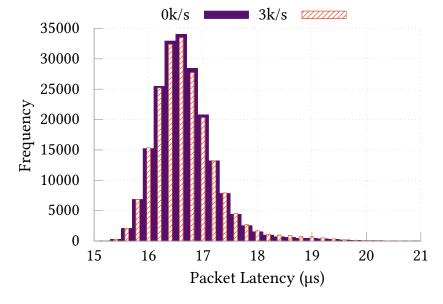

| 5.15 | Distribution of RTTs for 128 B packets for 0 and 3000 full RL updates/s                                                                                                                                     |

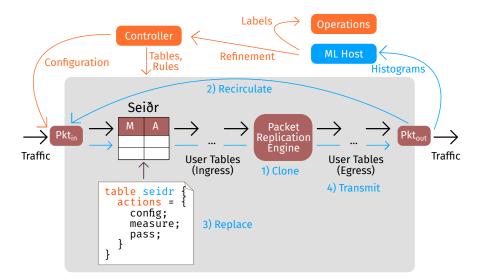

| 6.1  | Seiðr's integration with a PSA-compatible dataplane 193                                                                                                                                                     |

| 6.2  | P <sub>4</sub> headers for Seiðr configuration and histograms 194                                                                                                                                           |

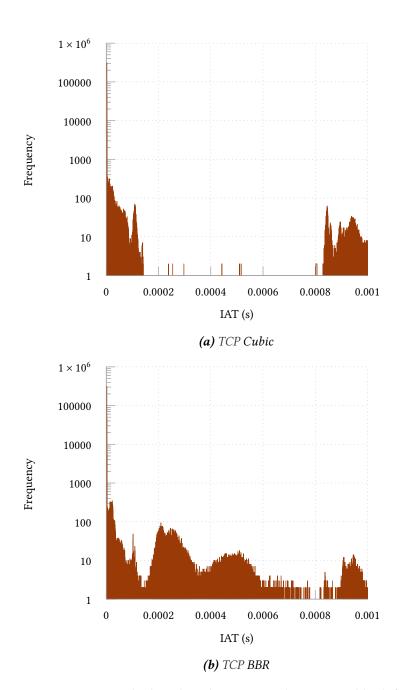

| 6.3  | Example dataplane histograms showing visible differences in inter-arrival times of selected TCP flavours 197                                                                                                |

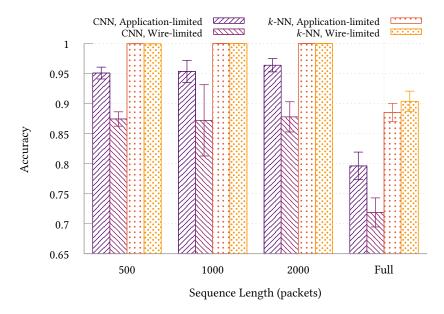

| 6.4  | Accuracy of $k$ NN and CNN classifiers when classifying $BBR$ and $Cubic$ TCP traffic from IAT histograms, trained over various sequence lengths                                                            |

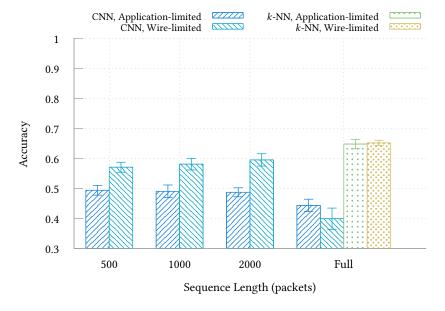

| 6.5  | Accuracy of <i>k</i> NN and CNN classifiers when classifying <i>BBR</i> , <i>Cubic</i> , <i>Reno</i> , and <i>Vegas</i> TCP traffic from IAT histograms, trained and tested on various sequence lengths 203 |

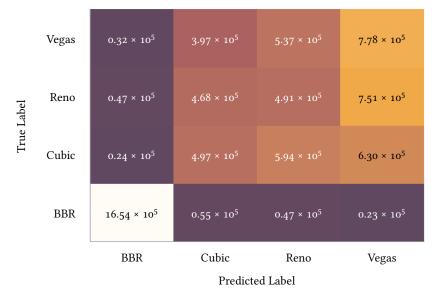

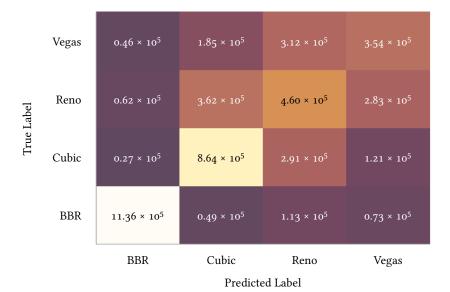

| 6.6  | Confusion matrices for a CNN on the <i>4-class</i> problem, 2000-packet length sequences                                                                                                                    |

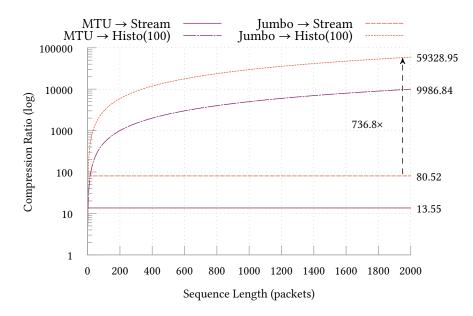

| 6.7  | Compression ratio of 100-bucket histograms and timestamp streams from raw packets on an IPv6 network 207                                                                                                    |

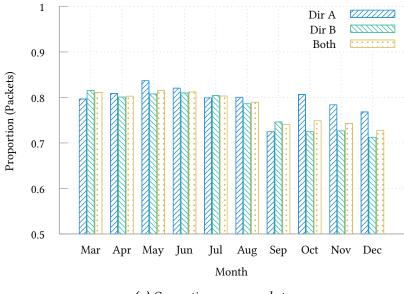

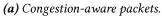

| A.1  | Proportional counts and byte volume of congestion-aware traffic                                                                                                                                             |

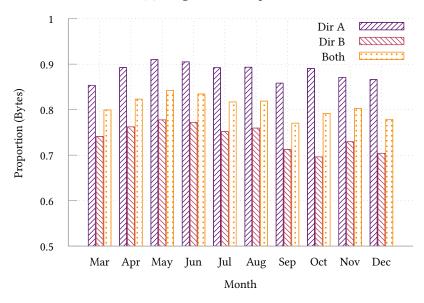

| A.2  | Proportional counts and byte volume of TCP traffic 219                                                                                                                                                      |

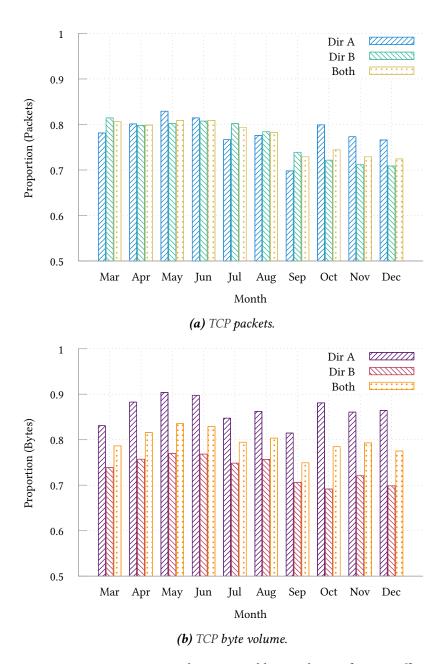

| A.3  | Proportional counts and byte volume of UDP traffic 220                                                                                                                                                      |

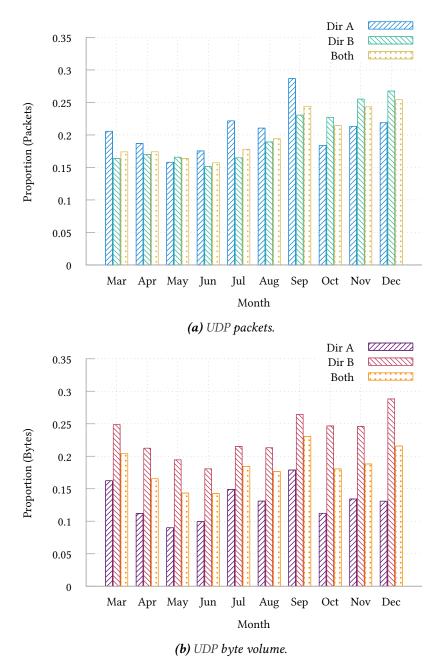

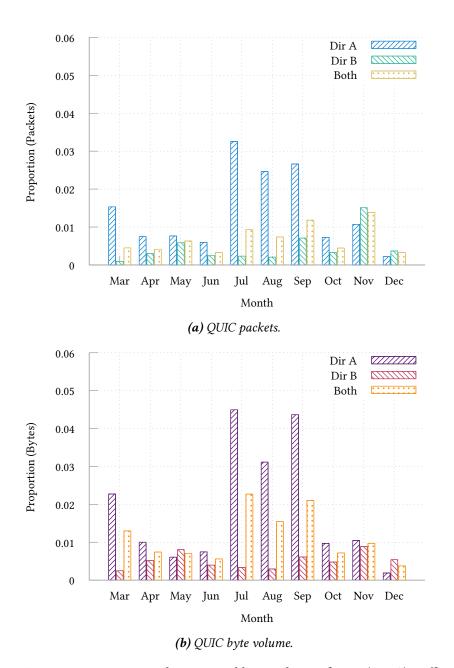

| A.4  | Proportional counts and byte volume of UDP (QUIC) traffic. 221                                                                                                                                              |

| D.1  | OPaL configuration (setup) packet                                                                                                                                                                           |

| D.2  | OPaL lookup key source layout                                                                                                                                                                               |

| D.3  | OPaL configuration (tiling) packet                                                                                                                                                                          |

| D.4  | OPaL tiling instance layout                                                                                                                                                                                 |

| D.5  | OPaL policy insertion header                                                                                                                                                                                |

| D.6  | OPaL state vector packet                                                                                                                                                                                    |

| D 7  | OPaL reward header 234                                                                                                                                                                                      |

# **List of Algorithms**

| 1 | Tile coding, for a single uniform grid tiling | 80  |

|---|-----------------------------------------------|-----|

| 2 | ParSa—Parallel Sarsa                          | 158 |

| 3 | Task scheduling for ParSa                     | 170 |

| 4 | Seiðr histogram update and transmission       | 195 |

### **Acronyms**

**ABR** Adaptive Bitrate 70, 94, 97

**ALU** Arithmetic Logic Unit 34, 54, 93, 154, 167, 168, 178

**API** Application Programming Interface 18, 28, 43, 134, 166, 196, 224

**APT** Advanced Persistent Threat 118, 119

**AQM** Active Queue Management 53, 92, 174

**AS** Autonomous System 14, 16, 17, 19, 22, 31, 36, 37, 59–61, 63, 64, 67, 112–117, 119, 122, 123, 134, 152, 174, 188, 189, 199, 212

**ASIC** Application-Specific Integrated Circuit 1, 12, 13, 15, 16, 22, 25, 26, 31, 34, 37, 39, 40, 48, 91, 129, 175, 198

**ATM** Asynchronous Transfer Mode 18

**BGP** Border Gateway Protocol 19, 21, 63, 115–117

**BNN** Binarised Neural Network 55, 69, 75, 93, 148, 175, 187, 213

CAIDA Center for Applied Internet Data Analysis v, 9, 115, 124, 215, 216

**CAM** Content-Addressable Memory 229

**CBR** Constant Bitrate 68, 114–116, 139, 223

CCA Congestion Control Algorithm 2, 3, 7, 8, 30, 40, 50, 52–54, 59, 61, 64–66, 94, 95, 97, 114, 115, 192, 199–201, 203–205, 208, 213

**CDN** Content Delivery Network 14, 29, 36, 72

**CGRA** Coarse-Grained Reconfigurable Array 35, 187

**CISC** Complex Instruction Set Computer 16

**CNN** Convolutional Neural Network 62–64, 70, 81, 96, 102, 104, 192,

200-206, 208

**CPP** Command Push-Pull 184, 227

**CPU** Central Processing Unit 2, 3, 14–16, 23, 25, 26, 31, 34, 35, 38, 40–42, 46, 47, 54, 55, 65, 66, 71, 72, 76, 77, 92, 105, 112, 147, 171, 174, 177, 178, 180, 196, 202, 214

**CSP** Constraint Satisfaction Problem 63, 76

**DAG** Directed Acyclic Graph 71, 72

**DASH** Dynamic Adaptive Streaming over HTTP 70, 215

**DDN** Data-Driven Networking 3-7, 21, 49, 54-56, 59-62, 67, 76-78, 82, 89, 90, 94-98, 106, 109, 111, 116, 145, 147-149, 191, 209-212

**DDoS** Distributed Denial of Service 2, 5–8, 22, 36, 51, 61, 65, 67, 68, 98, 109–112, 114, 116–119, 127, 134, 135, 142, 144, 145, 149, 152, 162, 174, 177, 187, 188, 190, 209, 210, 212

**DMA** Direct Memory Access 40, 54, 148

**DNN** Deep Neural Network 4, 55, 63, 65, 70, 72, 74–78, 82–84, 93, 97, 98, 100, 103, 148, 150, 211, 212

**DNS** Domain Name System 111, 113–116

**DoS** Denial of Service 98, 102, 111, 112

**DOTS** DDoS Open Threat Signalling 117, 123, 127

**DPDK** Data Plane Development Kit 24, 25, 28, 40–42, 44–46, 48, 183, 199

**DPI** Deep Packet Inspection 38, 52, 64

**DRAM** Dynamic Random-Access Memory 162

**DRL** Deep Reinforcement Learning 62, 63, 65, 66, 69–73, 77, 82, 97, 100, 147, 183

**DSCP** Differentiated Services Code Point 56, 169, 231

**DSL** Domain-Specific Language 46, 69

**eBPF** Extended Berkeley Packet Filter 16, 28, 34, 41–45, 47, 48, 214

**ECMP** Equal-Cost Multi-Path routing 52, 62, 122

**ES** Evolution Strategies 63, 88, 213

FCT Flow-Completion Time 53, 62, 65, 85, 115

FL Federated Learning 60, 68, 69, 102, 103

**FPGA** Field-Programmable Gate Array 26, 32, 33, 35, 47, 48, 54–56, 92, 148, 150, 151, 154, 162, 168, 175, 184, 187, 190, 213, 214

**FPU** Floating-Point Unit 39, 91–93, 126, 148, 149, 154, 190, 193, 211

**FSM** Finite State Machine 27, 34, 35, 123, 124, 225

**FU** Functional Unit 4, 25, 26, 38, 41, 73, 91, 92, 151, 169, 210, 211, 213

**GNN** Graph Neural Network 63, 69, 71–74, 76, 81, 82, 103

**GPU** Graphics Processing Unit 3, 35, 54, 55, 64, 66, 76, 81, 105, 147, 157

**GRU** Gated Recurrent Unit 64, 82

**HLS** HTTP Live Streaming 70

**HTTP** Hypertext Transfer Protocol 24, 71, 110, 113, 117, 122, 132–134, 137, 140, 141, 215, 217

IAT Inter-Arrival Time 7, 129, 130, 132, 133, 172, 192, 194, 196, 197, 200–204, 206–208

**IDS** Intrusion Detection System 22, 24, 25, 30, 64, 69

**IETF** Internet Engineering Task Force 13, 14, 22

**IID** independent and identically distributed 105, 109

**ILP** Integer Linear Programming 24, 49, 62, 63, 73

INT In-band Network Telemetry 29, 50, 51, 53, 191

**IoT** Internet of Things 93

IP Internet Protocol 51, 73, 112, 113, 116, 120, 123, 131, 132, 134, 153, 196, 216, 226, 231

**IPC** Inter-Process Communication 151, 159, 160, 165–167

IR Intermediate Representation 32, 46, 48

IRQ Interrupt Request 40, 41, 43, 44

**ISA** Instruction Set Architecture 16, 26, 47

ISP Internet Service Provider 9, 16, 22, 51, 62, 69, 71, 110, 114–118, 189, 214–217

**IXP** Internet eXchange Point 16, 19, 36, 217

**JCT** Job Completion Time 72

**JIT** Just-in-Time 43, 47, 48

kNN k-Nearest Neighbours 64, 118, 200, 202–204, 206, 208

**LFA** Link-Flooding Attack 6, 51, 114–118, 123

**LSTM** Long Short-Term Memory 35, 64, 65, 71, 76, 82, 96, 187, 192, 196, 202, 210

LUT Look-up Table 48, 162

MAC Medium Access Control 26, 36, 40, 41, 44, 183, 184, 199, 227

**MAT** Match-Action Table 4, 12, 20, 27, 28, 31, 33–35, 38, 47, 48, 51–53, 55, 64, 80, 94, 148, 151, 154, 175, 211, 213

**MDP** Markov Decision Process 61, 74, 85, 86, 88, 90, 91, 95, 106, 152

ME Microengine 33, 160, 161, 164, 167–172, 174, 175, 184, 186, 227–229

MIB Management Information Base 15, 16

ML Machine Learning 3–8, 30, 35, 38, 39, 49, 54–56, 59, 60, 63, 64, 67, 68, 70–72, 74, 76–78, 83–85, 90–100, 104–106, 109, 110, 143, 148, 149, 175, 187, 190–192, 196, 200, 206–209, 211, 214

MPLS Multiprotocol Label Switching 19, 69

MPMC Multi-Producer/Multi-Consumer 162, 165, 168

**MPTCP** Multipath TCP 65, 70

**MTU** Maximum Transmission Unit 38, 50, 135, 165, 207

NAT Network Address Translation 22, 117, 224

**NF** Network Function 23, 24, 36, 38, 39, 46, 188

**NFP** Netronome Flow Processor 8, 9, 36, 47, 52, 55, 151, 154, 160, 161, 165–167, 172, 174, 175, 178, 184, 186, 187, 198, 201, 213, 227–229

**NFV** Network Functions Virtualisation 23, 119, 144

NIC Network Interface Card 2, 7, 12, 26, 30, 35, 36, 38, 40–44, 46–48, 54, 55, 69, 75, 78, 90, 93, 94, 147–152, 155, 165, 173–175, 177, 178, 180, 181, 183, 186, 187, 190, 210, 214, 227

NN Neural Network 35, 55, 62–68, 70, 72, 75, 78, 80–82, 89, 93, 96, 97, 100–102, 104, 147, 187, 189, 213

**NPU** Network Processing Unit 2, 12, 15, 16, 25, 26, 31, 48, 52, 55, 75, 92, 151, 213

NTP Network Time Protocol 113, 135, 224, 226

NUMA Non-Uniform Memory Access 40

OS Operating System 15, 16, 20, 24, 26, 29, 36, 40–43, 68, 111, 113, 214

**OSPF** Open Shortest Path First 18, 19

**OVS** Open vSwitch 21, 28, 43, 64, 119, 120, 129, 143

PCIe PCI Express 35, 40, 41, 54, 104, 105, 147–149, 152, 169, 172, 174, 183, 210, 227

**PDP** Programmable Dataplane 2, 4–8, 12, 13, 22, 29–31, 33, 35–39, 46, 48–56, 75, 76, 78, 80, 82, 83, 88, 90–93, 129, 148–151, 154, 155, 157, 165, 171, 175, 189–193, 196, 207, 209–211, 213, 214, 228

**PIFO** Push-In First-Out 34, 53

**PISA** Protocol Independent Switch Architecture 27, 28

**PS** Parameter Server 56

**PSA** Portable Switch Architecture 7, 28, 32–36, 46, 55, 150, 152, 192, 193, 196, 198, 208

**QoE** Quality of Experience 53, 63, 69–71, 75, 123, 223

**QoS** Quality of Service 3, 4, 24, 34, 35, 53, 54, 61, 63, 75, 122, 191, 194, 212

**RAM** Random Access Memory 40, 44, 46, 72, 77, 83, 112, 136, 162, 171, 202, 203

**RIP** Routing Information Protocol 18

RISC Reduced Instruction Set Computer 15, 16, 26, 42

RL Reinforcement Learning 3, 4, 6–8, 56, 59–63, 65–70, 72–74, 76–79, 81–86, 89–91, 94, 95, 97, 100, 102, 106, 107, 109, 110, 116, 117, 119, 120, 124, 126, 127, 135, 138, 139, 142, 144, 145, 147–152, 154–157, 162–166, 172–175, 177, 178, 183–190, 209, 210, 212, 213, 231

**RMT** Reconfigurable Match Tables 2, 27, 28, 31, 33–36, 55, 56, 80, 82, 198, 213, 214

**RNN** Recurrent Neural Network 82, 192

**RPC** Remote Procedure Call 35, 39, 114

RTCP RTP Control Protocol 224-226

RTP Real-time Transport Protocol 134, 223–226

**RTT** Round-Trip Time 36, 39, 44, 45, 53, 62, 65, 66, 70, 71, 73, 166, 183, 185, 189

**SCTP** Stream Control Transmission Protocol 22, 114

**SDN** Software-Defined Networking 1, 2, 6, 12, 13, 18–21, 23, 24, 29, 30, 38, 53, 60, 68, 110, 119, 133, 143–145

**SGD** Stochastic Gradient Descent 83, 84, 104

**SIMD** Single Instruction Multiple Data 35, 55, 91, 167–169, 181

**SKB** Socket Buffer 40–43

**SLA** Service-Level Agreement 94, 199

**SMT** Satisfiability Modulo Theories 33, 63, 97

**SoC** System on a Chip 15, 25, 148, 151, 160, 168, 187, 214, 227

**SRAM** Static Random-Access Memory 67, 162

**SSRC** Synchronisation Source 224–226

**SVM** Support Vector Machine 35, 55, 96, 101, 187

**TCAM** Ternary Content-Addressable Memory 26, 27, 38, 64, 75, 94, 144, 150, 211

TCP Transmission Control Protocol 7, 17, 24, 40, 49, 53, 65, 66, 68, 110, 112–114, 117, 124, 130–134, 136, 137, 139, 140, 142, 188, 192, 196, 197, 199, 201–204, 208, 215–217, 219

**TD** Temporal-Difference 86, 87, 89, 157, 159

**TE** Traffic Engineering 1, 12, 17–19, 21, 22, 52–54, 61, 62, 97

TEE Trusted Execution Environment 25, 105

TLS Transport Layer Security 71, 116

TO Traffic Optimisation 19, 61, 62, 97

**TPU** Tensor Processing Unit 54, 81, 92, 105

**TRS** Timed Random Sequential 125, 126, 145, 188, 189

**TURN** Traversal Using Relays around NAT 135, 223–225

**UDP** User Datagram Protocol 14, 22, 68, 112–114, 116, 117, 122, 124, 129, 130, 132, 133, 135, 137, 142, 169, 183, 198, 216, 217, 220, 221, 223, 224, 226, 231, 232

**VLIW** Very Long Instruction Word 25, 27, 47

**VM** Virtual Machine 15–17, 23, 24, 42

**VNF** Virtual Network Function 6, 8, 12, 23–25, 36–39, 48, 97, 120, 126–129, 145, 149, 173, 174, 178, 183

**VoIP** Voice over Internet Protocol 6, 9, 110, 115, 116, 123, 134, 142, 223,

224

**VPN** Virtual Private Network 64

**VRAM** Video RAM 202

**WAN** Wide Area Network 21, 22, 191, 199

**XDP** eXpress Data Path 39, 41, 43–45, 47, 51, 183, 214

### Chapter 1

### Introduction

Computer networks are complex, yet critical infrastructure. The Internet of today is a prime example. From its birth as *ARPANET* (Heart *et al.*, 1970), interlinking the computer networks of self-governing research institutions, it has scaled to connect together billions of devices over chains of smaller networks owned by totally separate entities. This growth has come at a cost; large-scale networks are beset with layers upon layers of interlocking and overlaid systems divided amongst endpoint hosts and operators of the network fabric. The isolated, resilient design of all these layers is a strength in itself as these layers can, in theory, be replaced. Yet owing to this complexity, keeping the 'Internet machinery' well-oiled and performant is a difficult task.

As these networks have grown larger and faster over the last half-century, they have become more flexible to do just this. Early design choices such as routing algorithms had been bonded to fixed-function hardware. To escape these shackles, the community sought through the early 2000s to separate the high-level forwarding behaviour of network packets (the control plane) from the hardware dataplane, giving rise to Software-Defined Networking (SDN). This is a research success that has meaningfully impacted the design, adaptability, performance, and fault-tolerance of production networks. For instance, the ability to make routing decisions per-flow has enabled Traffic Engineering (TE) that formerly required complex workarounds. What this did not solve was inflexible dataplane behaviour; switches still supported a fixed set of actions applied to a fixed set of protocols known ahead-of-time, with limited shared state for measurement purposes. Many packet actions security functions and the like—were and are implemented as Application-Specific Integrated Circuits (ASICs) inside middleboxes to process traffic at line rate. Infamously, these add yet more inflexibility by relying on (possibly incorrect) handling of known protocols. Making up for this shortfall in malleability by implementing these tasks in host machines causes significant, orders-of-magnitude reductions in packet throughput and added latency. Between fixed-function dataplanes and commodity hosts, there is

no way to balance performance and arbitrary programmability. While it is one thing to argue around performance and ossification, what of new functionality? To observe incorrect (yet transient) paths followed by packets, or to inspect and aggregate queue state and nanosecond-level timestamps to detect recent issues such as *microbursts* both require packet modification and access to state which past switches simply do not allow.

Many other aspects of networks are run by heuristic methods: each complex, hand-tuned, and operating on limited information. Their responses must be both approximately correct and computationally cheap to scale reasonably. To make the point clear, consider Congestion Control Algorithms (CCAs). CCAs underpin the majority of Internet traffic's ability to dynamically scale send rates up or down-in the absence of actual network state, they must in effect reverse-engineer optimal actions by following a proxy metric such as delay or packet losses. While this is impressive, one can't help but ask if better information about the network itself could allow more useful decision making. What also happens, then, as networks change? Experience has shown that we simply iterate, from NewReno (Gurtov et al., 2012) to Cubic (Rhee et al., 2018) to BBR (Cardwell et al., 2016)<sup>1</sup> in long-fat networks. But even after years of design and tuning, these are easy to get subtly or fatally wrong; initial actively-deployed BBR versions were notably unfair to other flows (Ware et al., 2019). The takeaway is that it's infeasible to develop and hand-tune strategies per workload, per topology, and per protocol distribution. Should we not be able to automatically infer tailored mechanisms or parameters, robust to changes and evolution, from local performance and global management data-a data-driven solution? CCAs are but one case where we should ask ourselves these questions. Consider general optimisation of network protocols and infrastructure, or protection against the abuse of network resources such as Distributed Denial of Service (DDoS) attacks, or even the above dataplane measurement-equally strong candidates to consider whether data-driven logic and network cooperation can lead to meaningful improvement.

<sup>1</sup> Deployed circa 1999, 2006, and 2016 respectively.

While these aims are lofty, the last decade has seen surprising and rapid kinds of change, first of all in the design and introduction of *programmable* switching hardware and *Network Interface Cards* (NICs). *Programmable Dataplane* (PDP) switch hardware was originally designed to evolve past the fixed action sets of SDN at line rate, using a limited compute model rather than aiming for full programmability on par with host *Central Processing Units* (CPUs). Indeed, the turnaround from the original *Reconfigurable Match Tables* (RMT) proposal (Bosshart *et al.*, 2013) to full-scale switches based on Intel's *Tofino 2* (Intel, 2022) and Nokia's *FP5* (Nokia, 2021), aggregating 12.8–14.4 Tbit/s, in a scant few years is remarkable. Diversifying the field further, the legacy of older *Network Processing Units* (NPUs) has led to *SmartNICs*, offering more expressive and capable compute at a smaller scale such as via Intel's *infrastructure processing units* (Intel, 2021b). As it happens, these tools have not only enabled greater control and adaptability of networks

but also powerful schemes to measure them, a new environment to execute program logic, and tighter cooperation with end hosts. What's fascinating is that *these* ideas and use cases are not entirely novel, reflecting an undercurrent present since the *active networking* movement (Tennenhouse & Wetherall, 1996). Instead, both classes of efficient hardware have revealed the value of *offloading* and *in-network compute*—moving all or part of an application's logic to the network fabric to accelerate it further, in spite of its different compute capabilities versus a typical CPU. Moreover, these new classes of hardware are fully reprogrammable at runtime, allowing line-rate services to be easily installed, upgraded, and replaced.

The second substantial change of the last decade is the meteoric rise of Machine Learning (ML) and Reinforcement Learning (RL) through high-profile, breakaway successes in difficult domains such as classification (K. He et al., 2016) and game playing (Berner et al., 2019; Silver et al., 2017). These approaches learn a function to map input data (like the statistics of a monitored flow) to output labels or actions, repeatedly transforming it according to complex learnt statistical properties, with the aim that a learnt function extends well from seen to unseen data. This, too, is the revival of an older line of research-statistical and connectionist ideas which have been extended and empowered by powerful, specialised compute resources like commodity Graphics Processing Units (GPUs). What this offers us is the necessary toolkit for Data-Driven Networking (DDN)-the automatic tuning that networks cry out for—allowing the development of better generalised solutions to network problems, or even policies specifically tailored to the needs of a deployment environment. RL methods in particular have a unique affinity for closed-loop control tasks. These policies are iteratively learnt by taking an action—deliberately exploring supposedly suboptimal choices from time to time-before observing the controlled system's state some time later and using a measured reward score to improve the policy itself in its own feedback loop. We have, at last, the tools to learn complex decision boundaries and effective control in spite of the very non-trivial (and often surprisingly involved) system dynamics of computer networks. The beauty is that, even as our networks evolve, we should be able to learn adjustments and corrections to account for new protocols, behaviours, and topology changes by learning from (always-available) performance and Quality of Service (QoS) metrics.

Handling this evolution—particularly at local scales—requires also that we can learn these properties *online*. Pre-trained models to solve a task or implement some control mechanism such as a CCA are likely to be trained in a 'one size fits all' manner from a vast amount of data. This works well in the general case, of course; functions are often trained to handle the most common scenarios and behave well in response. In reality, a characteristic of our deployment environment might not have been included in training; either a useful property like a network's structure, or a problem dynamic like the local protocol distribution. In the event of either this scenario or

some gradual change in the underlying problem, it is reasonable to tailor an existing policy to suit our current needs. Alternatively, we might aim to prevent performance degradation arising from complex dynamics we don't yet know how to model but can see in live networks, needing us to train from scratch. Online learning techniques, such as RL and federated versions of unsupervised and semi-supervised algorithms, allow us to adaptively train policies to consider local tailoring and global evolution. Standard supervised ML approaches, on the other hand, require significant caveats to achieve similar tailoring; labelling data is expensive (either by hand or by constructing and running relevant simulations), datasets are too large to transport, and training datasets may have privacy or ownership concerns attached. RL in particular avoids this by using incremental performance metrics which should be easily observable at runtime. However, online learning adds concrete difficulties beyond simple ML inference. Even complex functions like Deep Neural Networks (DNNs) can be made efficient on weaker hardware using specialised representations or data formats, but their training relies on holding high volumes of data in memory, alongside costly procedures for computing the gradient estimates needed to update them.

While these developments enable (online) DDN and network programmability, it is at their intersection that the field of networking is truly on the cusp of something promising. For instance, PDP hardware and the integrated network measurement it enables expose new sources of data and state, such as port and queue occupancies, or precise and accurate flow telemetry. In the case of flows, DDN processes can then act based on such data rather than sampled metrics, potentially offering more accurate classification for uses like OoS assignment. In the network at large, they may act on a networkwide picture of device state which would have otherwise been unavailable. Although this data is evidently too much for any one host machine to process particularly per-packet events at a switch's aggregate @(Tbit/s)-the enhanced programmability allows PDP devices to pick up the slack by acting on it in situ. The first way we could achieve this is by aggregating and reducing data in PDP hardware to make it feasible to export (at lower volumes and rates), or to apply early statistical processing to ease the workload on process machines. The second is by moving ML and RL logic directly into PDP hardware. DDN decisions may then be instantly factored into the routing and processing of typical dataplane *Match-Action Tables* (MATs), at minimal latency cost. In concert with online learning techniques such as RL, we may also tailor this behaviour to suit the deployment device or location—either by tweaking a known-good base policy, or learning from scratch. However, programming in-network services has its own challenges: the hardware offers restricted instruction sets, program lengths, data types, Functional Units (FUs) for capabilities like floating-point support, and memory. Each limits the kinds of processing we aim to perform, but nowhere is this felt more keenly than the mismatch between the needs of ML algorithms and capabilities of network hardware. This grows greater still with our desire for

1.1. Thesis statement 5

online learning in the PDP context, which requires us to compute and represent incremental and optimal changes to a learned policy. While this logic could also be pushed to host machines, there are significant drawbacks in decision latency and throughput. This thesis explores and chronicles how these approaches benefit the network and one another, as well as the challenges introduced by the limited capabilities of a PDP environment. To that end, I show through the community's advances and my own additions to the state of the art how these approaches can offer meaningful benefit to network operators, as well as how we might enable both online and offline learning in the PDP networks of tomorrow.

#### 1.1 Thesis statement

This thesis asserts that:

Data-driven networking—enhancing networks with ML—and dataplane programmability are key tools in aiding the control and measurement of future networks (so). Data-driven methods such as reinforcement learning can lead to improved performance in network optimisation and control problems, such as DDoS prevention (s1). In-network compute can make data-driven networking more efficient, effective, and responsive—enabling online learning to tailor policies to their deployment environment (s2). Finally, dataplane programmability will allow the precise measurement and data aggregation that can enable fine-grained data-driven analyses to scale to high flow rates or large networks (s3). Applied together, programmable data-driven networks can improve computer network operation beyond the sum of these parts.

While claims \$50-1\$ fall in line with expected uses of these new technologies, the others require some extra explanation to unpack. Claim \$2\$ may be somewhat surprising, if we think only of the massive \$\mathcal{O}\$ (MiB-GiB) models which dominate classification, control, and language tasks. By considering changes to algorithms and numerical formats, smaller models can be executed in the limited resources of PDP hardware. The architecture of these devices is specialised around processing high rates of packet events—by parallelism or pipelining—which can allow line-rate operation of models transformed as above. If such decisions can be made at the same time and location as input data arrive, then the network can (re-)act faster. This also affords us more time to compute gradients and the like without impacting per-packet behaviour, making online learning feasible. Claim \$3\$ arises due to the scale and volume of data which PDP hardware can produce. Consider a single 100 Gbit/s port on a switch, operating at line rate with a mean packet size of 500 B, from which we want to make some DDN decision based on PDP-only

state such as ns-level timestamps and queue occupancies. On average, this produces 25 Mpps events *per-port*, which is difficult for a single machine to handle—let alone when it must perform per-packet inference. PDP hardware thus has an important role to play in digesting and summarising its newly available metrics for host machines.

#### 1.2 Contributions

Grouped according to the claims (so-3) in the thesis statement:

- A thorough summary of the literature on modern, programmable computer networks (including recent hardware trends) (chapter 2), and of machine learning techniques suitable for their control (chapter 3). This includes the history of a spectrum of tools developed to optimise dataplane processing—both automatically and by bespoke design. Not just how ML benefits networks, but how creative PDP-enhanced networking can benefit ML use cases (\$0,2\$).

- A novel synthesis of best practices, design decisions, and environmental tradeoffs to consider in the design of ML-led system control (section 3.1.6, S1).

- An improved RL-based DDoS prevention scheme (chapter 4, \$1). This builds on two protocol-agnostic, flow-granularity RL agent designs (Instant and Guarded action models), alongside algorithmic modifications to Sarsa to enable better concurrent learning from many inprogress RL trajectories, and reward functions tailored to detecting the negative impacts of amplification DDoS and Link-Flooding Attacks (LFAs). This is supported by a quantitative investigation of suitable flow features for attack traffic detection via RL, deadline-aware action planning and state fusion to shield agents from being overloaded, and a concrete architecture and design of a Virtual Network Function (VNF)- and SDN-based installation of this anti-DDoS solution. To assess this work, I introduce procedures and trace data for modelling and generating traffic similar to modern Opus-based Voice over Internet Protocol (VoIP) flows. This is then used in an empirical evaluation of these models against the prior state-of-the-art in RL-based DDoS mitigation and a non-ML algorithm tailored towards LFAs.

- OPaL—the first implementation of in-network, online RL (chapter 5, \$2). This includes an analysis of why RL in PDP hardware is needed and best-placed to interact with the network, made feasible by classical RL methods and quantisation. In support, I design an RL interaction model based on path-adjacent compute to protect carried traffic, offer an analysis of suitable data formats for online DDN in resource-constrained hardware. A new proof is given that 1-step temporal-difference RL algorithms admit a parallelisable, map-reduce form with

tile-coded policies, culminating in *ParSa*—a wait-free, parallel, online RL algorithm to accelerate tile-coded policy inference and updates. This allows a design space exploration of parallel RL strategies tailored to provide either maximum offline throughput, or optimal state-action latencies and online throughput, as well as work allocation algorithms and communication tailored to SmartNIC devices with an explicitly tiered memory model. OPaL is evaluated in-depth—how it affects carried dataplane traffic, performs in latency and throughput under different policy sizes (simple and complex state), and improves on host machines. Finally, I describe how OPaL would integrate with state-of-the-art PDP applications to perform fully in-NIC, fast, automated DDoS mitigation.

• Seiðr histograms for aggregation of precise flow telemetry (chapter 6, s3). This is a flexible dataplane-assisted architecture and algorithm compatible with the Portable Switch Architecture (PSA) that allows data aggregation in the form of histograms. The use of histograms is supported by a measurement study of Inter-Arrival Time (IAT) microstructure between Transmission Control Protocol (TCP) CCA variants, and analysis which establishes the algorithmic cause for these differences. Using ML methods, I present a high-accuracy method for using the Seiðr procedure to track IATs with nanosecond-accurate timing to tell apart timer-based (e.g., BBR) and cwnd-based TCP CCAs using host machines. Its effectiveness is shown by an extensive evaluation of TCP congestion control classification using IAT histograms in different ML models, as well as analysis of Seiðr's scalability compression ratio relative to input sequence length.

A contribution I can't claim to offer, but hope sincerely to have done, is to collect together enough of the literature and intuition on DDN and PDPs to serve as a comfortable introduction to a newer researcher in the field. The topic of DDN in particular has blossomed during the course of my PhD education—and scarcely existed at the scale it does today when this work was first undertaken in 2017. Making the case for its relevance and best practices has become much easier over the last few years alone in light of this. I'm fortunate that the work of many others tackles the same problems as I do, which I think lends credence to the thesis statement (*so* in particular)—in a sense, this work contributes one set of case studies among many. I hope that this thesis can be the book I would have wanted to read (and use) as a starting point when I was setting out on this research venture.

#### 1.3 Thesis outline and structure

Broadly speaking, this thesis is presented in two halves. The first offers in-depth background on both the fields of DDN and PDP:

**Chapter 2** describes the evolution of computer networks from fixed-function devices towards increased programmability in both the control plane and dataplane—critically examining early research directions in contrast with modern successes. It then describes how modern dataplanes improve or allow new networked applications—namely, off-loading and in-network compute.

**Chapter 3** provides an introduction to the new field of data-driven networking by critically reviewing the design of many recent ML solutions to network problems and relevant function approximation and learning methods. This includes data formats needed to run ML techniques in resource-constrained environments, and concludes with some discussion on the limitations and security context of ML.

The second half presents novel, concrete use cases which each demonstrate a part of the thesis statement (as discussed above):

Chapter 4 investigates using multi-agent RL to automatically learn the features of attack traffic online. I explore agent designs informed by past RL approaches (and their failures) relative to the realities of Internet traffic, while discussing the threat landscape of volumetric DDoS attacks. State spaces in particular are experimentally justified to find 'per-feature' value. A system architecture as part of a larger VNF system is shown, followed by evaluation of efficacy on different traffic classes and scenarios.

Chapter 5 takes to task the goal of enabling in-network, online RL for the first-time. I present an exploration of the design space around the interaction mechanisms, compute models, algorithm modifications, and data structures needed for PDP devices. This high-level design is named OPaL. It then presents significant implementation detail for OPaL on Netronome Flow Processor (NFP) SmartNIC hardware, followed by performance evaluation to show its improvements in stateaction latency and to assert that its impact on traffic is minimal.

**Chapter 6** examines how in-network data reduction to histograms can make complex, non-latency-sensitive ML decisions on host machines scalable. I motivate their use with a measurement study on CCA detection from per-flow ns-level timestamps, before evaluating their general scalability and effectiveness in the target use case.

The thesis then concludes by summarising its main takeaways, offering closing thoughts on these fields, and outlines future work specific to the above use cases (chapter 7).

Additional, supplementary details follow:

- **Appendix A** describes the methodology and results of a small-scale study on the distribution of protocols in CAIDA trace data, to establish a rough estimate of congestion-unaware traffic's presence in *Internet Service Provider* (ISP) networks.

- **Appendix B** provides additional detail on the measurement process used to collect trace data for simulating VoIP-like traffic, as well as the software architecture for packet generation.

- **Appendix C** expands on architectural details for the NFP family of SmartNICs to offer some additional context for OPaL's design constraints.

- **Appendix D** contains packet header and protocol descriptions for OPaL's inband control protocol.

## Chapter 2

# Programmable Computer Networks

Computer networks serve the important function of allowing any two machines to communicate with one another, typically via individual messages known as packets (i.e., a packet-switched network). Naturally, reality is much more complex than this broad statement would otherwise let on; the local routing fabric in a modern network comprises specialised (though commonplace) hardware for correctly routing these packets through arbitrary topologies of links and switches at ever-increasing data rates. This grows more complicated still when we consider the task of *inter*networking between such networks, where we must route packets on higher-level logically structured addresses between different domains of control according to fairly complex policies and relationships. At the inception of these technologies, computer scientists of the day wisely decided that the sole duty of the network itself should be the correct routing of individual packets. Their view was that application-level logic should be executed solely at endpoint machines; their definition extended, of course, to even include desirable (and some would say indispensable) transport-level properties such as error checking and stream reliability. This is known as the end-to-end principle (Saltzer et al., 1984). This position arose partly due to the logical complexity of all the tasks pushed onto the network at this time, as well as the need to ensure optimal forwarding performance while microprocessors were still relatively nascent, but was instrumental in ensuring that the network itself remained *extensible*. A consistent, pared down feature set was ensured while offering a good degree of freedom for the development and deployment of higher-level protocols.

Decades have passed since then, and to a large extent the zeitgeist has shifted on just how capable our networks should be—in both the research community and operators of large-scale networks. Consider the case where an operator has a fully converged network built entirely on fixed-function hardware, but wishes to use some program to inspect the behaviour, state,

and characteristics of some flow between two local machines. The problem is that these devices offer no means of modifying or influencing routing state, being highly-optimised switching devices that understand a selection of routing algorithms built into their internal circuitry. For the longest time, altering the network's routing behaviour in this instance—even for a single override—required not only physically altering and rewiring the network, but also would require additional hardware. SDN was a key development in enabling this fine-grained routing over traffic at various layers in the protocol stack, allowing operators to offer per-flow or per-class routing for improved performance—TE—or even application-aware load balancers at the switch level. Initial forays into SDN were built on exploiting a separate control plane to install MATs and rules on target switches-mapping fields of predefined protocols to predefined actions—leaving truly complex decisions to one or more controller machines. These developments have been pushed even further as the runtime capabilities of supporting devices have evolved into what we might now consider truly Programmable Dataplanes (PDPs). A wide variety of ASIC-based switches, SmartNICs, and other accelerators now offer an environment for expressing and executing truly arbitrary network logic, protocol parsers, and action definitions.

Despite all this, our general-purpose Internet remains much the same from an endpoint perspective—performance and reliability improvements aside. Yet this increase in capabilities has revealed new strands of research in more specialised networks such as data centres, where in-controller processing would have allowed the network fabric to cooperate with its hosted applications but presented an obvious computational bottleneck. *In-network compute* is enabled by such bespoke routing environments when combined with the above advances in programmability, and is founded on the growing idea that in-path network elements such as switches, NICs, and middleboxes can (and should) host complex logic to accelerate applications, participate in flow control, or to aid in network management.

This chapter begins by motivating and describing initial attempts at dataplane programmability in the '90s (primarily *active networking*), how controlplane programmability and SDN arose in their wake, and the reasons behind these movements' respective failures and successes (section 2.1). Section 2.2 introduces modern, programmable dataplanes by tracing efforts parallel to the development of SDN for improving the performance of host-based packet processing, such as VNFs, before leading into the emergence of specialised PDP hardware from legacy SDN and NPUs. This is followed by commentary on the ways that the original active networking movement differs from modern PDPs (and context behind the latter's successful adoption), as well as a selection of open challenges and proposals in PDP programming languages and hardware designs. Section 2.3 then explains the rationale behind *offloading* service logic to PDP hardware and into host network stacks, while describing recent research on using these capabilities to automatically accelerate existing dataplane programs. Finally, to further

motivate in-network compute I describe point solutions which take advantage of the execution environment and more granular view of network data to improve measurement and operation (section 2.4).

#### From fixed-function to software-defined 2.1

For historical value, and to provide some context on the design and architectural decisions of modern programmable network stacks (section 2.2), it is important to consider early developments and advances which laid the groundwork for the PDP ecosystem as we know it. This includes the illfated active networking movement, leading into the development of control plane programmability via SDN.