## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## PEDRO FILIPE LEITE CORREIA DE TOLEDO

# Digital-Based Analog Processing in Nanoscale CMOS ICs for IoT Applications

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microeletronics

Advisor: Prof. Dr. Hamilton Duarte Klimach Coadvisor: Prof. Dr. Paolo Stefano Crovetti

Porto Alegre September 2022 Leite Correia de Toledo, Pedro Filipe

Digital-Based Analog Processing in Nanoscale CMOS ICs for IoT Applications / Pedro Filipe Leite Correia de Toledo. – Porto Alegre: PGMICRO da UFRGS, 2022.

124 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2022. Advisor: Hamilton Duarte Klimach; Coadvisor: Paolo Stefano Crovetti.

1. CMOS. 2. VLSI. 3. Ultra Low Power. 4. Ultra Low Voltage. 5. Internet of Things. 6. IoT. 7. Digital-Based OTA. 8. Digital OTA. 9. DigOTA. 10. Operational Transconductance Amplifier. I. Klimach, Hamilton Duarte. II. Crovetti, Paolo Stefano. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"I am not here to take part, I am here to take over." — CONOR MCGREGOR

### ACKNOWLEDGEMENTS

I would like especially to acknowledge my wife, **Claudia Camerini Correa da Silva de Toledo** for all the motivation, support, and patience during my whole Ph.D. studies. She mainly had to take care of our kids alone during pandemic times while I was measuring the chips related to this thesis. During these three years of my Ph.D., I lost my loving father-in-law, who I considered a father. I want to dedicate this thesis to his memory. Rest in peace, Dear Sr. Prof. **Claudio Osma Crochi da Silva**. Hugs and kisses to my sons, **Pietro** and **Filippo**, who contributed to keeping this work in hard mode.

I would like to thank my parents, **Bernardino Marques Toledo** and **Sineide Leite da Silva**, and my beautiful sisters **Thais Toledo** e **Adriana Toledo**, for all the financial support given to my Ph.D.'s studies and life in Turin.

Thanks to my advisors, Prof. **Paolo Crovetti** and Prof. **Hamilton Klimach** for the excellent discussions that helped me to mature and learn so much in the field of microelectronics. In detail, I would like to especially thank Prof. **Paolo Crovetti** who has believed, received, and supported me while I was in Turin, giving personal pieces of advice, besides the technical ones. The same remarks apply to Prof. **Sergio Bampi**, Dr. **Orazio Aiello** and Prof **Massimo Alioto**. My friends from lab in Italy, **Roberto Rubino, Chen** and **Osama Bin Tariq**. Special remarks to **Maksudjon Usmonov** for his valuable support during the measurements. My friends of old NSCAD group, Prof. Eric Fabris, Everton Ghignatti, Renê Timbo, Diogo Santana, German Fierro, Helga Dornelas, Alonso Schmidt, Jhon Caicedo, and David Cordova. My old friends of lab 110 Analog/RF group, Arthur Liraneto, Filipe Baumgratz, Renato Campana , Sandro Binsfeld, Oscar Mattia, Márlon Lorenzetti, Rafael Schultz, Luís Rodovalho, Bruno Canal, Moacir Monteiro, Arthur Oliveira, Roger Zamparette, Gabriel Guimarães, Fernando Carrion, Marcelo Pedrini, Thales Ribeiro and Yi Chen Wu for the discussions in the lab and meetings.

Thanks to all administrative people, who have been working hard to keep all the infrastructure available to me, from both institutes: Graduate Program in Microelectronics from the Federal University of Rio Grande do Sul - Brazil and Department of Electronics and Telecommunications from Politecnico di Torino - Italy. MOSIS for the MOSIS Educational Program (MEP) allowed fabricating one of the circuits presented here.

### ABSTRACT

The Internet-of-Things (IoT) concept has been opening up a variety of applications, such as urban and environmental monitoring, smart health, surveillance, and home automation. Most of these IoT applications require more and more power/area efficient Complementary Metal–Oxide–Semiconductor (CMOS) systems and faster prototypes (lower time-to-market), demanding special modifications in the current IoT design system bottleneck: the analog/RF interfaces.

Specially after the 2000s, it is evident that there have been significant improvements in CMOS digital circuits when compared to analog building blocks. Digital circuits have been taking advantage of CMOS technology scaling in terms of speed, power consumption, and cost, while the techniques running behind the analog signal processing are still lagging. To decrease this historical gap, there has been an increasing trend in finding alternative IC design strategies to implement typical analog functions exploiting Digital-in-Concept Design Methodologies (DCDM). This idea of re-thinking analog functions in digital terms has shown that Analog ICs blocks can also avail of the feature-size shrinking and energy efficiency of new technologies.

This thesis deals with the development of DCDM, demonstrating its compatibility for Ultra-Low-Voltage (ULV) and Power (ULP) IoT applications. This work proves this statement through the proposing of new digital-based analog blocks, such as an Operational Transconductance Amplifiers (OTAs) and an ac-coupled Bio-signal Amplifier (BioAmp). As an initial contribution, for the first time, a silicon demonstration of an embryonic Digital-Based OTA (DB-OTA) published in 2013 is exhibited. The fabricated DB-OTA test chip occupies a compact area of 1,426  $\mu m^2$ , operating at supply voltages ( $V_{DD}$ ) down to 300 mV, consuming only 590 pW while driving a capacitive load of 80pF. With a Total Harmonic Distortion (THD) lower than 5% for a 100mV input signal swing, its measured small-signal figure of merit (FOM<sub>S</sub>) and large-signal figure of merit (FOM<sub>L</sub>) are 2,101  $V^{-1}$  and 1,070, respectively. To the best of this thesis author's knowledge, this measured power is the lowest reported to date in OTA literature, and its figures of merit are the best in sub-500mV OTAs reported to date.

As the second step, mainly due to the robustness limitation of previous DB-OTA, a novel calibration-free digital-based topology is proposed, named here as Digital OTA (DIG-OTA). A 180-nm DIGOTA test chip is also developed exhibiting an area below the 1000  $\mu m^2$  wall, 2.4nW power under 150pF load, and a minimum  $V_{DD}$  of 0.25 V. The proposed

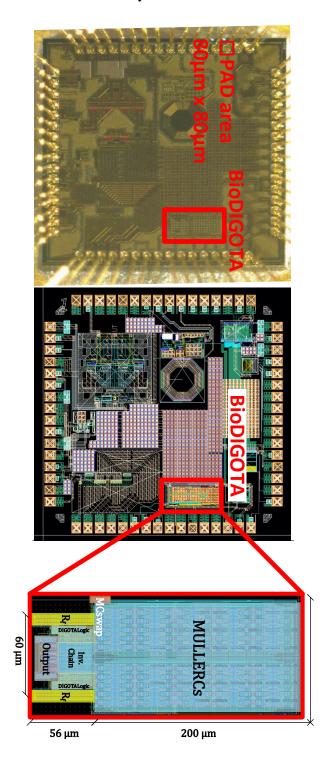

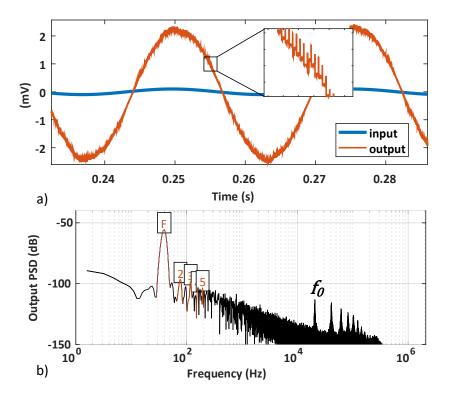

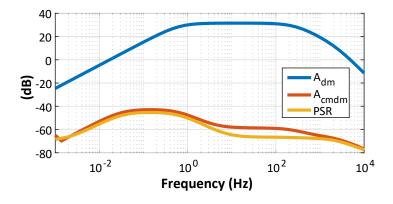

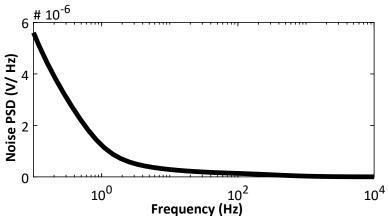

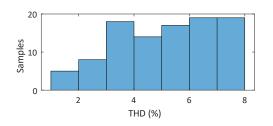

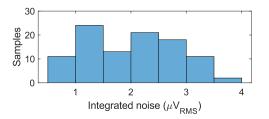

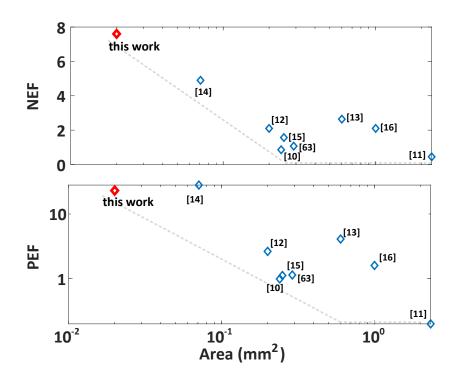

DIGOTA is more digital-like compared with DB-OTA since no pseudo-resistor is needed. As the last contribution, the previously proposed DIGOTA is then used as a building block to demonstrate the operation principle of power-efficient ULV and ultra-low area (ULA) fully-differential, digital-based Operational Transconductance Amplifier (OTA), suitable for microscale biosensing applications (BioDIGOTA) such as extreme low area *Body Dust*. Measured results in 180nm CMOS confirm that the proposed BioDIGOTA can work with a supply voltage down to 400 mV, consuming only 95 nW. The BioDIGOTA layout occupies only 0.022 mm<sup>2</sup> of total silicon area, lowering the area by 3.22X times compared to the current state of the art while keeping reasonable system performance, such as 7.6 Noise Efficiency Factor (NEF) with 1.25  $\mu V_{RMS}$  input-referred noise over a 10 Hz bandwidth, 1.8% of THD, 62 dB of the common-mode rejection ratio (CMRR) and 55 dB of power supply rejection ratio (PSRR).

After reviewing the current DCDM trend and all proposed silicon demonstrations, the thesis concludes that, despite the current analog design strategies involved during the analog block development has been indispensable to unfold several cutting edge applications over the last decades, the DCDM design strategy presented here seems to be very attractive for new technologies and continuing advance analog interface performance, especially for IoT applications. These circuits could take advantage of better awareness of the discrete nature of information and the steadily increasing timing resolution of more advanced CMOS nodes.

**Keywords:** CMOS. VLSI. Ultra Low Power. Ultra Low Voltage. Internet of Things. IoT. Digital-Based OTA. Digital OTA. DigOTA. Operational Transconductance Amplifier.

## LIST OF ABBREVIATIONS AND ACRONYMS

- IoT Internet-of-Things

- CMOS Complementary Metal–Oxide–Semiconductor

- VLSI Very Large Scale Integration

- RF Radio Frequency

- DCDM Digital in-Concept Design Methodologies

- ULV Ultra-Low-Voltage

- ULP Ultra-Low-Power

- OTAs Operational Transconductance Amplifiers

- BioAmp Bio-signal Amplifier

DB-OTA Digital-Based OTA

- THD Total Harmonic Distortion

- FOM<sub>S</sub> Small-Signal Figure Of Merit

- $FOM_L$  Large-signal Figure Of Merit

## **DIGOTADigital OTA**

- ULA Ultra-Low-Area

- NEF Noise Efficiency Factor

- CMRR Common-Mode Rejection Ratio

- PSRR Power Supply Rejection Ratio

- ICs Integrated Circuits

- FTP File Transfer Protocol

- ITU International Telecommunication Union

- IEEE Institute of Electrical and Electronics Engineers

- MCU microprocessors

- SOCs System on Chip

- FPGA Field-Programmable Gate Array

- SOA Service-Oriented Architecture

- TCP/IP Transmission Control Protocol/Internet Protocol

- NFC Near Field Communication

- IrDA Infrared Data Association

- UWB/IR Ultra-Wideband

- DASH7 Alliance Protocol

- RPL Routing Protocol for Low-Power and Lossy Networks

- BTLE Bluetooth

- 6LowPANPv6 over Low-Power Wireless Personal Area Networks

- EDA Electronic Design Automation

- PDK Process Design Kit

- PCB Printed Circuit Board

- ADC Analog to Digital Converter

- ENOB Effective Number of Bits

- SPIs Serial Peripheral Interfaces

- I2Cs Inter-Integrated Circuits

- USBs Universal Serial Buses

- UARTs Universal Asynchronous Receiver-Transmitters

- ISM Industrial Scientific Medical Band

- TSMC Taiwan Semiconductor Manufacturing Company

- IMF International Monetary Fund

- GDP Gross Domestic Product

- TFB thin-film battery

- DVS Dynamic Voltage Scaling

- DLS Dynamic Leakage-Suppression

- SDLC Scalable Dynamic Leakage-Suppression

- CMFB Common Mode Feedback

- CMFF Common Mode Feed Forward

- RSCE Reverse-Short-Channel Effect

- ALS Automate Analog Layout Synthesis

- CAS Circuit and System

- PLLs Phase-Locked Loops

- SARs Successive Approximation Registers

- VCO Voltage Controlled Oscillator

- DACs Digital to Analog converters

- LDOs Low-Dropout Regulators

- FO4 Fan-Out-of-4

- CMIR Common-Mode Input Range

- CM Common-Mode

- DM Differential-Mode

- PM phase margin

- MEP Minimum Energy Point

- SDC Static Digital Calibration

- DDC Dynamic Digital Calibration

- DPWM Digital Pulse Width Modulation

- DDPM Dyadic Digital Pulse Modulation

- FFT Fast Fourier Transform

- MC Montecarlo

- GBW Gain Bandwidth Product

- UCCM Unified Charge-Control Model

- DIBL Drain Induced Barrier Lowering

- ECG Electrocardiogram

- FD Fully Differential

- MiM Metal-insulator-Metal

- PSD Power Spectral Density

- CT Composite Transistors

- STA Static Time Analysis

# LIST OF FIGURES

| Figure 1.1 Vertical markets: smart things with their supposed functions constitute domain specific applications. <i>Horizontal markets</i> : application domain independent services with ubiquitous computing and analytical services (AL-FUQAHA et al., 2015)                                                                                                                                                                         | 19 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 a) McKinsey shows in 2013 its prediction of market share by 2025 (JAMES; MICHAEL; JACQUES, 2013) b) Significant opportunities along the IoT technology layers, highlighting a healthy market growth for edge devices (FREDRIK et al., 2019)                                                                                                                                                                                  | 21 |

| Figure 1.3 The IoT architecture. (a) Three-layer. (b) Middle-ware based. (c) service-oriented architecture (SOA) based. (d) Five-layer (AL-FUQAHA et al., 2015).                                                                                                                                                                                                                                                                        | 22 |

| Figure 1.4 Modern edge device with embedded intelligence before connecting to the cloud. Analytics can be applied to pre-process the raw data coming from the sensors before sending it upwards for deeper data mining analysis (BEAVERS, 2018).                                                                                                                                                                                        | 24 |

| Figure 1.5 The role of the cloud and fog resources in the delivery of IoT services (AL-FUQAHA et al., 2015)                                                                                                                                                                                                                                                                                                                             | 25 |

| Figure 1.6 Simplified IC Digial and Analog Design Flow (MAROLT; SCHEIBLE; JERKE, 2013).                                                                                                                                                                                                                                                                                                                                                 | 26 |

| Figure 1.7 A histogram of commercial IoT devices embedding each type of sensor (ALIOTO; SHAHGHASEMI, 2018). This survey of commercial IoT devices was done on a worldwide scale, using platforms such as Digi-Key to collect the data                                                                                                                                                                                                   | 27 |

| Figure 1.8 A histogram of maximum microcontroller clock frequency and of RAM memory capacity in commercial IoT nodes (ALIOTO; SHAHGHASEMI, 2018).2                                                                                                                                                                                                                                                                                      | 28 |

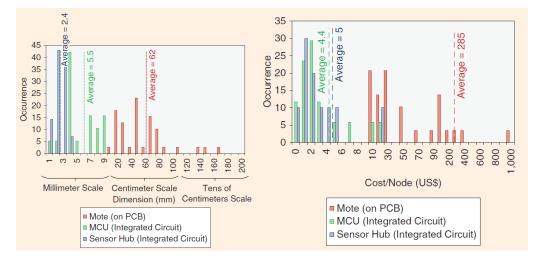

| Figure 1.9 The commercial devices size and cost for distributed sensing (ALIOTO;<br>SHAHGHASEMI, 2018).                                                                                                                                                                                                                                                                                                                                 | 29 |

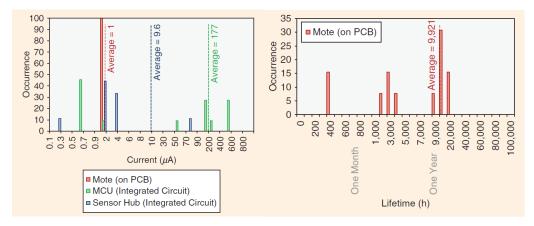

| Figure 1.10 A histogram of standby current and the estimated lifetime of commer-<br>cial IoT nodes at 1% duty cycle. (ALIOTO; SHAHGHASEMI, 2018)                                                                                                                                                                                                                                                                                        | 30 |

| Figure 1.11 System lifetime versus system power $\overline{P_{system}}$ for different batteries.<br>(ALIOTO, 2021; SEPULVEDA; SPEULMANNS; VEREECKEN, 2018). $DC = \frac{T_{on}}{T_{on}+T_{stdby}}$ is the duty cycle ratio which defines how much time the system is between active $(T_{on})$ and standby $(T_{stdby})$ mode.                                                                                                          | 31 |

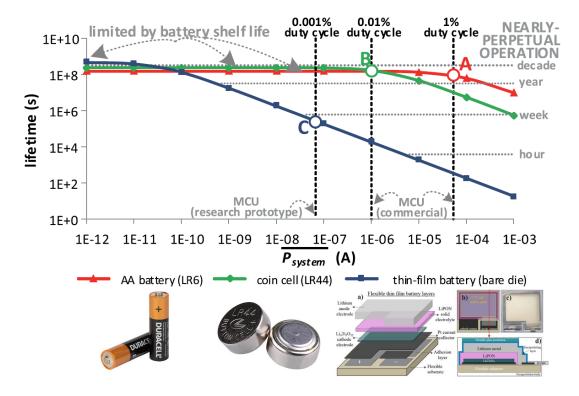

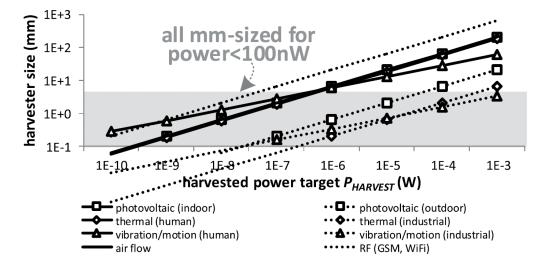

| Figure 1.12 Required harvester size for a given power target for several types of harvesters (ALIOTO, 2021).                                                                                                                                                                                                                                                                                                                            | 32 |

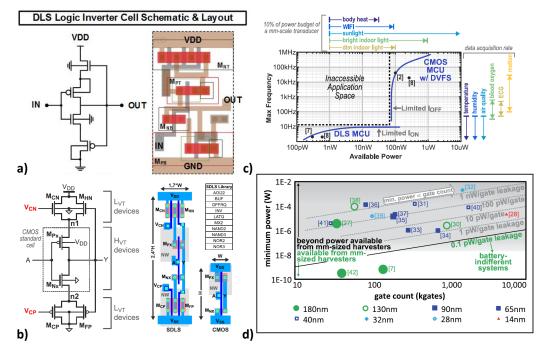

| <ul> <li>Figure 1.13 a) DLS inverter cell, schematic and layout (LIM et al., 2015) b) CMOS and DLS comparison for a MCU implementation (TRUESDELL et al., 2019)</li> <li>c) Dual-Mode Standard Cells (LIN; JAIN; ALIOTO, 2020) or Scalable Dynamic Leakage-Suppression (SDLS) logic style (TRUESDELL et al., 2019)</li> <li>d) Gate count in Kgates versus minimum power consumption in state of the art MCU (ALIOTO, 2021).</li> </ul> | 34 |

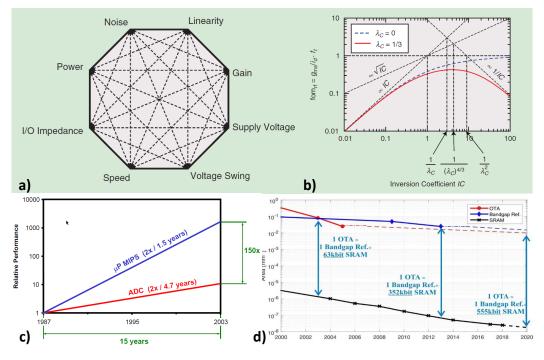

| Figure 1.14 a) analog design octagon b) $g_m/I_D \cdot f_T$ versus the inversion coefficient $IC$ , $\lambda_c$ is the parameter corresponding to the fraction of the channel in which the carrier drift velocity reaches the saturated velocity over a portion of the channel geometrical length (RAZAVI, 2002; ENZ; CHICCO; PEZZOTTA, 2017a) c) Performance difference between analog and digital blocks over time (MURMANN, 2006; Murmann, 2006) d) Area reduction over the years of the |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

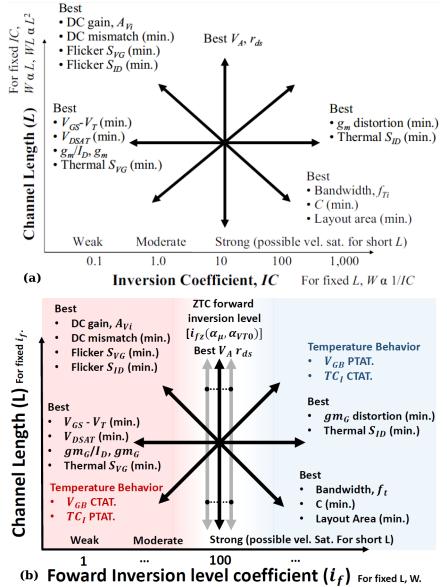

| <ul><li>bitcell SRAM, OTA and Bandgap reference (Aiello; Crovetti; Alioto, 2019)</li><li>Figure 1.15 (a) The MOSFET operating plane illustrating tradeoffs in performance</li></ul>                                                                                                                                                                                                                                                                                                         | 35 |

| for the selected inversion coefficient and channel length. Copyright John Wi-<br>ley and Sons Limited (BINKLEY, 2007). (b) MOSFET operating plane trans-<br>lated to Unified Charge-Control Model (UCCM) (SCHNEIDER; GALUP-<br>MONTORO, 2010; TSIVIDIS; MCANDREW, 2010) model presented before<br>including temperature behavior of MOSFET transistor presented in (COR-<br>DOVA; TOLEDO; FABRIS, 2014; TOLEDO et al., 2015).                                                               | 36 |

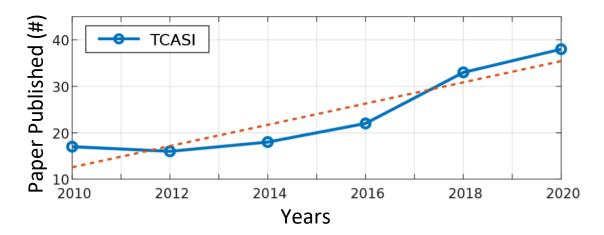

| Figure 1.16 Digital intensive analog/RF building block published in TCASI trans-<br>actions over the last 10 years (TOLEDO et al., 2021)                                                                                                                                                                                                                                                                                                                                                    | 39 |

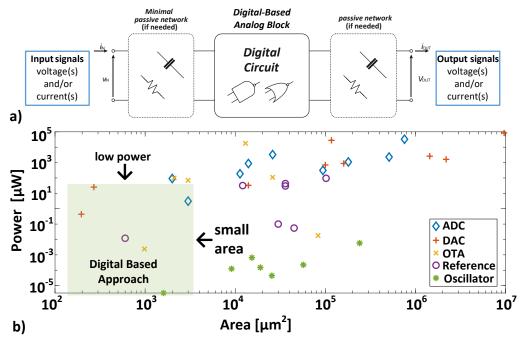

| <ul> <li>Figure 1.17 a) Block diagram of digital-based analog block (TOLEDO et al., 2021)</li> <li>b) Power vs Area for for ADCs (Crovetti, 2017), DACs (Aiello; Crovetti; Alioto, 2019a), OTAs (Toledo et al., 2020), voltage reference (Crovetti, 2015) and oscillators (Aiello et al., 2019).</li> </ul>                                                                                                                                                                                 | 41 |

| and oscillators (Aleno et al., 2017).                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

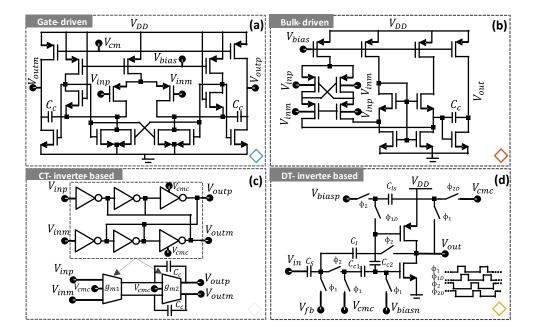

| Figure 2.1 a) Gate-driven (YOON; CHOI; ROH, 2015; DESSOUKY; KAISER, 2001), b) Bulk-driven (Ferreira; Sonkusale, 2014) c,d) Inverter-based (Lv et al., 2019; MICHEL; STEYAERT, 2012).                                                                                                                                                                                                                                                                                                        | 44 |

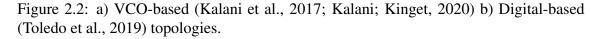

| Figure 2.2 a) VCO-based (Kalani et al., 2017; Kalani; Kinget, 2020) b) Digital-<br>based (Toledo et al., 2019) topologies.                                                                                                                                                                                                                                                                                                                                                                  |    |

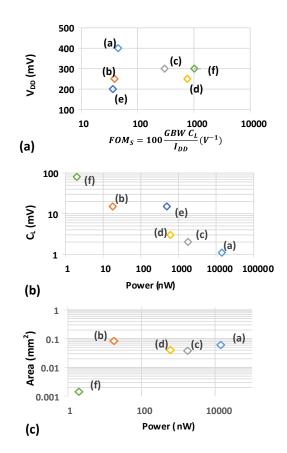

| Figure 2.3 ULV OTA state-of-art comparison plots: $V_{DD}$ (mV) versus $FOM_S = 100 \frac{GBWC_L}{I_{DD}}$ (V <sup>-1</sup> ), $C_L$ (pF) versus Power (nW) and Area ( $mm^2$ ) versus Power (nW). (a) Gate-driven, (b) Bulk-driven, (c)(d) Inverter-based from the Fig. 2.1, (e) VCO-based and (f) Digital-based from the Fig. 2.2                                                                                                                                                         | 46 |

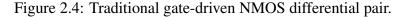

| Figure 2.4 Traditional gate-driven NMOS differential pair.                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

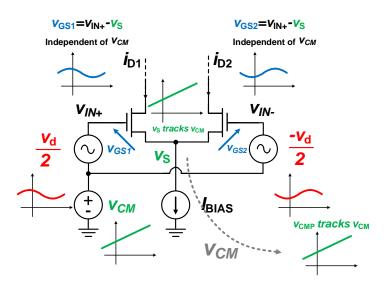

| Figure 2.5 Differential Mode Amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

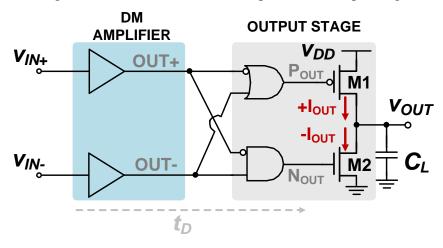

| Figure 2.6 Differential Mode Amplifier and Output stage                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

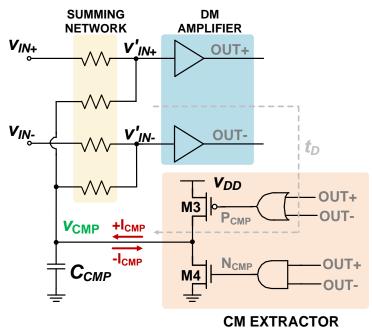

| Figure 2.7 Differential Mode Amplifier and Common Mode Extractor.                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

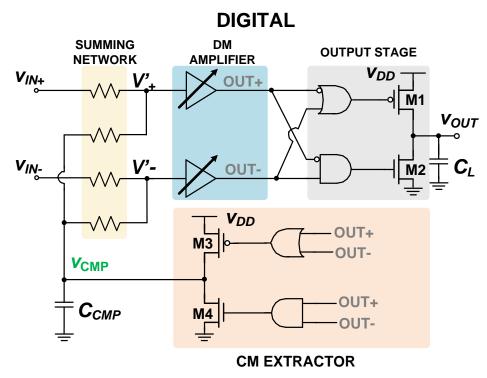

| Figure 2.8 Digital-Based Operational Trasnconductance Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

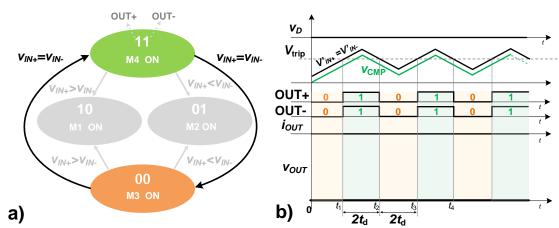

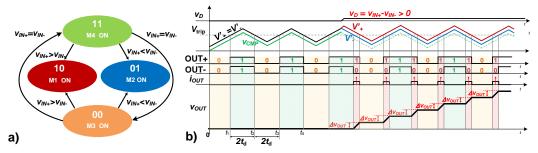

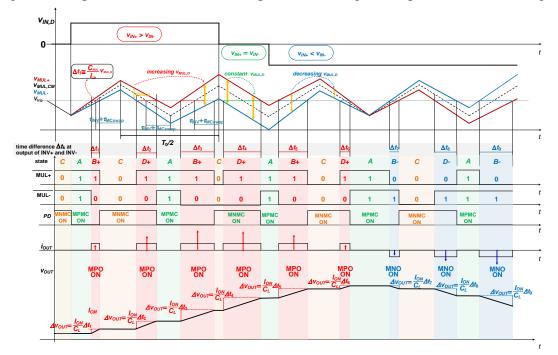

| Figure 2.9 a) DB-OTA state transition graph under only CM mode signal stimulus $(v_d = 0)$ b) time-domain DB-OTA waveforms                                                                                                                                                                                                                                                                                                                                                                  |    |

| Figure 2.10 a) Complete DB-OTA state transition graph b) time-domain DB-OTA waveforms                                                                                                                                                                                                                                                                                                                                                                                                       |    |

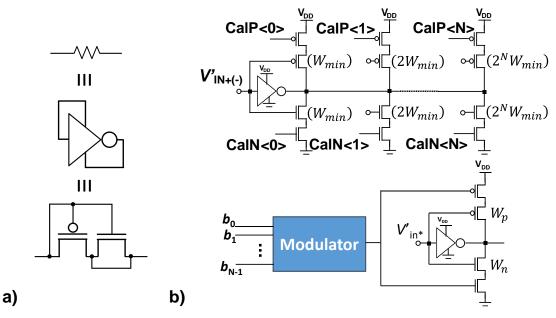

| Figure 2.11 a) inverter-based pseudo-resistor b) Static digital calibration (SDC) and dynamic digital calibration (DDC)                                                                                                                                                                                                                                                                                                                                                                     |    |

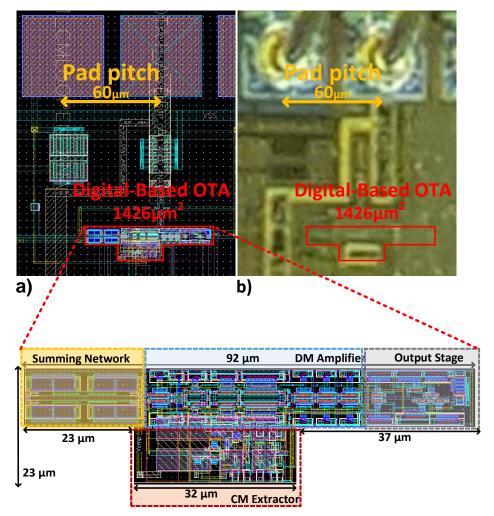

| Figure 2.12 a) DB-OTA layout. Total area of 1,426 $\mu$ m <sup>2</sup> b) Micrograph of the 180-<br>nm test-chip                                                                                                                                                                                                                                                                                                                                                                            |    |

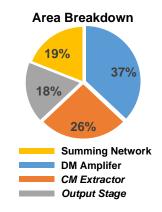

| Figure 2.13 DB-OTA Area Breakdown not containing the DDC; only SDC.                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

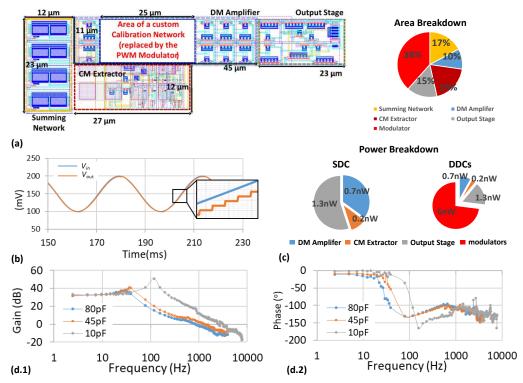

| Figure 2.14 [SIMULATION]a) DB-OTA layout and Area breakdown containing DDC b) $V_{\rm in}$ and $V_{\rm out}$ at 30 Hz frequency, 50 mV peak amplitude and $C_{\rm out} = 80 \mathrm{pF}$ c) Power breakdown d) ULV DB-OTA frequency response (Toledo et                                                                                                                                                                                                                                     |    |

| al., 2020)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58 |

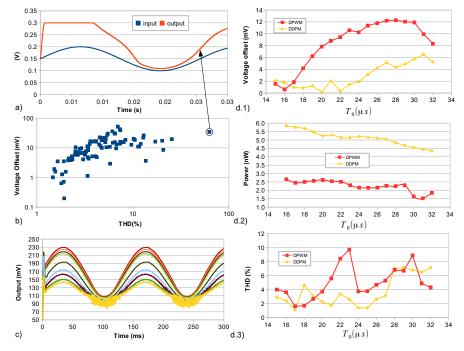

| Figure 2.15 [SIMULATION] a) $V_{in}$ and $V_{out}$ of a bad sample from the MC analysis with 30 Hz frequency, 50 mV peak amplitude and $C_{out} = 80 \text{ pF b}$ ) Thumbnail |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| plot between THD (%) and input offset voltage (mV)—each point is a sampe                                                                                                       |

| of the MC simulation c) Changing the BD-OTA offset through DDC using the                                                                                                       |

| DPWM modulator d) Trade-off between power and signal integrity (THD)                                                                                                           |

| versus $T$ (Toledo et al., 2020)                                                                                                                                               |

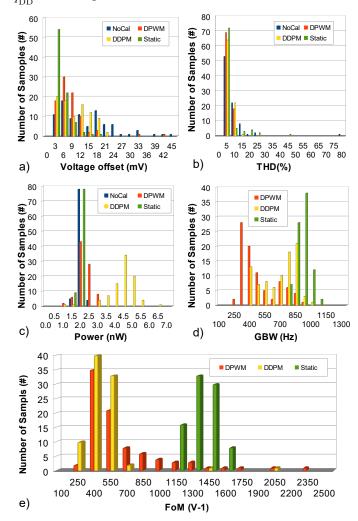

| Figure 2.16 [SIMULATION] a) Voltage offset b) THD c) Power d) GBW e) and                                                                                                       |

| $FOM_S = 100 \frac{GBWC_{Load}}{I_{DD}}$ histograms (Toledo et al., 2020)                                                                                                      |

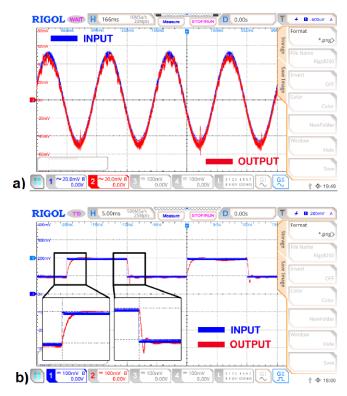

| Figure 2.17 [MEASUREMENTS] a) $V_{IN}$ and $V_{OUT}$ sine waves for $C_L$ =80pF, input                                                                                         |

| amplitude $V_{amp}$ =50mV and frequency $f_{in}$ =3Hz, b) transient response for a                                                                                             |

| square wave input, $C_L$ =80pF, $V_{amp}$ =50mV and $f_{in}$ = 50Hz. The settling time                                                                                         |

| measured at the rising (falling) edge is 1.15 (0.9) ms                                                                                                                         |

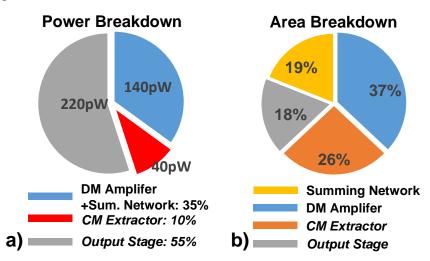

| Figure 2.18 [MEASUREMENTS] a) Power and b) Area breakdown                                                                                                                      |

| Figure 2.19 [MEASUREMENTS] a) THD (%) versus peak Vamp for 3Hz fre-                                                                                                            |

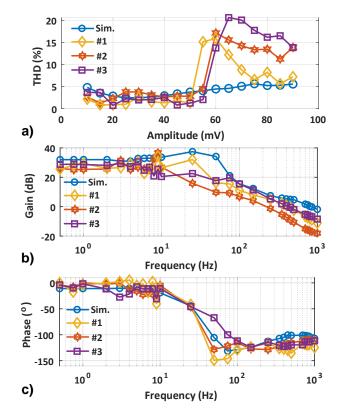

| quency b,c) ULV DIGOTA frequency response                                                                                                                                      |

| Figure 2.20 [MEASUREMENTS and SIMULATION] . State-of-art of ultra-low                                                                                                          |

| voltage OTAs. #1,#2 and #3 are the three die samples measured in this work.                                                                                                    |

| The remaining points within the cloud are results from the Monte Carlo sim-                                                                                                    |

| ulation from (Toledo et al., 2019)                                                                                                                                             |

|                                                                                                                                                                                |

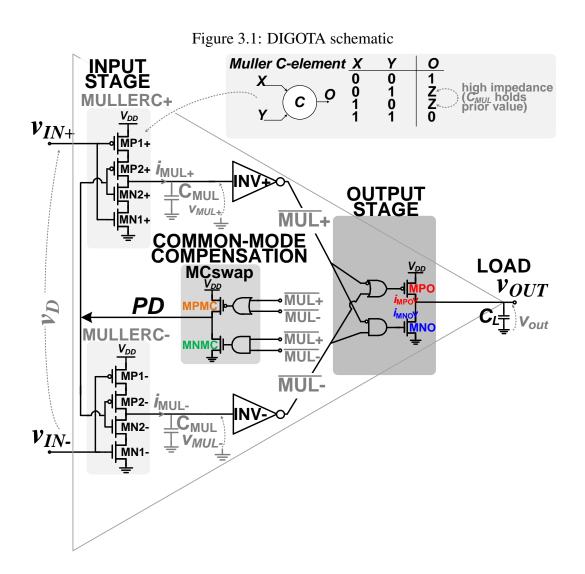

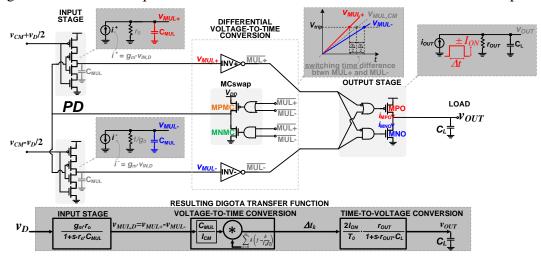

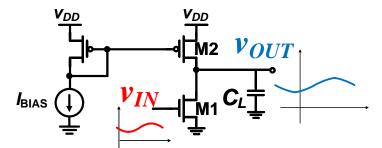

| Figure 3.1 DIGOTA schematic                                                                                                                                                    |

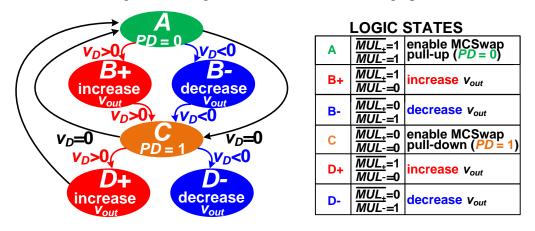

| Figure 3.2 Logic states and state transition graph                                                                                                                             |

| Figure 3.3 DIGOTA circuit details vs logic state under $v_D > 0$ (reverse all direc-                                                                                           |

| tions for $v_D < 0$ ). The state sequence follows the transition graph in Fig. 2b:                                                                                             |

| a) A, b) B+, c) C and d) D+. The subscript + (-) refers to the case $v_D > 0$                                                                                                  |

| $(v_D < 0).$                                                                                                                                                                   |

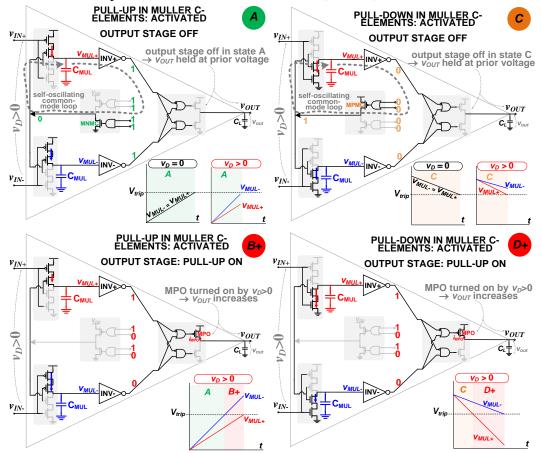

| Figure 3.4 Timing analysis of the self-oscillating loop timing under pure common-                                                                                              |

| mode inputs, and evaluation of the time $T_A$ spent in state A                                                                                                                 |

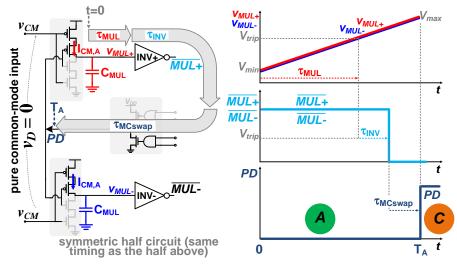

| Figure 3.5 DIGOTA equivalent circuit and transfer function under differential in-                                                                                              |

| put $v_D$                                                                                                                                                                      |

|                                                                                                                                                                                |

| voltages                                                                                                                                                                       |

| •                                                                                                                                                                              |

| lation the required $I_Q$ , the current of left side of the current mirror is neglected77                                                                                      |

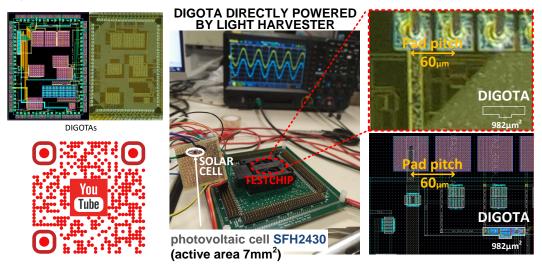

| Figure 3.8 Test bench, micrograph of the DIGOTA 180-nm testchip and layout.                                                                                                    |

| Use the QR code to watch the demo video of the DIGOTA working powered by light harvester (7 $mm^2$ )                                                                           |

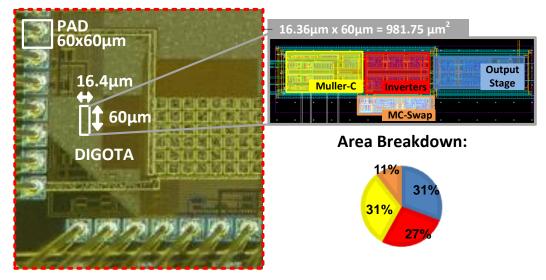

| Figure 3.9 Micrograph of the DIGOTA 180 nm testchip and area breakdown                                                                                                         |

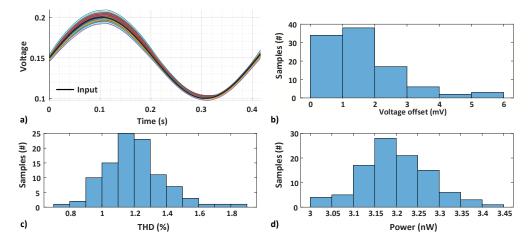

| Figure 3.10 [SIMULATIONS] a) Input and Output waveform in voltage follower                                                                                                     |

| configuration for a 100 samples MC analysis. b) Voltage offset c) THD d)                                                                                                       |

| Power histograms for a 100 samples MC analysis. b) voltage offset c) THD d)                                                                                                    |

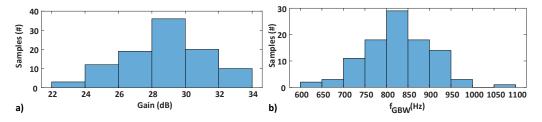

| Figure 3.11 [SIMULATIONS] a) DC gain and b) $f_{GBW}$ histograms for a 100 sam-                                                                                                |

| ples MC analysis                                                                                                                                                               |

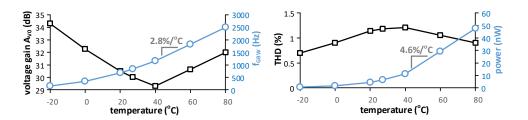

| Figure 3.12 [SIMULATIONS] Temperature dependence of DC voltage gain and                                                                                                        |

| gain-bandwidth product vs. temperature dependence of DC voltage gain and<br>sin-bandwidth product vs. temperature, total harmonic distortion and power81                       |

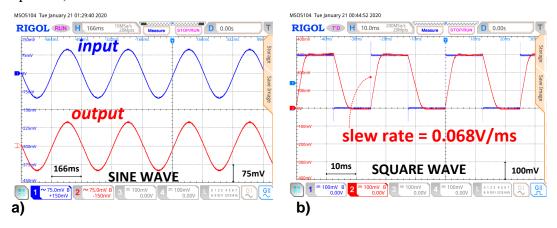

| Figure 3.13 [MEASUREMENTS] a) sine and b) square wave response when di-                                                                                                        |

| rectly powered by a 1-mm2 solar cell at <100 lux (dark overcast day) (2.5-Hz                                                                                                   |

| frequency, 75-mV amplitude)                                                                                                                                                    |

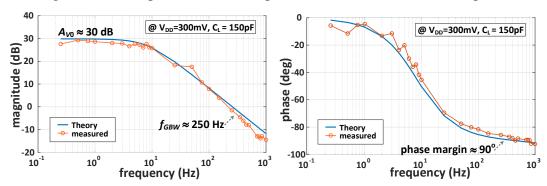

| Figure 3.14 [MEASUREMENTS] Open-loop frequency response at $V_{DD}$ =0.3 V,                                                                                                    |

| $C_L$ =150 pF: a) magnitude and b) phase from testchip measurements and                                                                                                        |

| model in Eq. $(3.16)$                                                                                                                                                          |

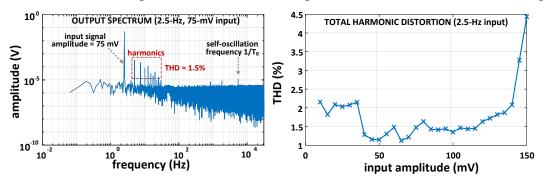

|                                                                                                                                                                                |

| Figure 3.15 [MEASUREMENTS] a) Output spectrum under sine wave input (2.5 Hz, 75-mV), b) THD vs amplitude under sine wave input (2.5 Hz), at $V_{DD}$ =0.3 |                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| V, $C_L$ =150 pF                                                                                                                                          | 83                     |

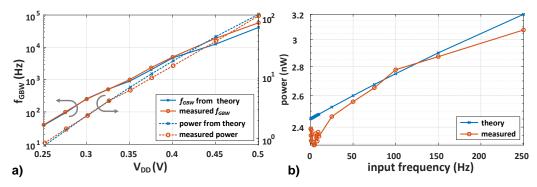

| Figure 3.16 [MEASUREMENTS] a) Power (Eq. (3.20)) and gain-bandwidth prod-                                                                                 |                        |

| uct (Eq. (3.19)) vs $V_{DD}$ , b) power (Eq. (3.20)) vs input frequency (50-mV                                                                            |                        |

| amplitude, $V_{DD}$ =0.3V)                                                                                                                                | 84                     |

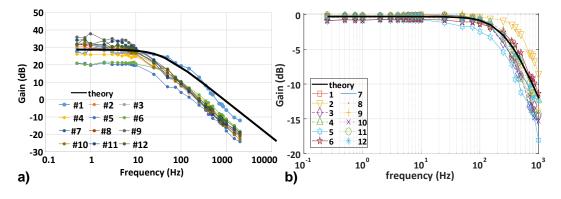

| Figure 3.17 [MEASUREMENTS] a) Magnitude Open-loop frequency response acro                                                                                 | DSS                    |

| twelve DIGOTA dices b) Magnitude response of the closed-loop transfer                                                                                     |                        |

| function of twelve DIGOTA dices in the voltage follower configuration                                                                                     |                        |

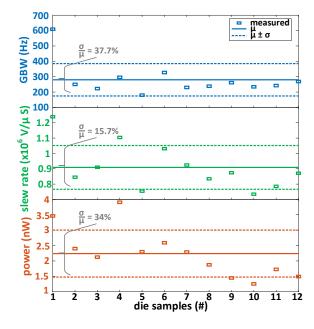

| Figure 3.18 [MEASUREMENTS] a) Measurement results across twelve dice and                                                                                  |                        |

| effect of process variations on gain-bandwidth product, slew rate and power                                                                               |                        |

| consumption ( $V_{DD}$ =0.3 V)                                                                                                                            | 85                     |

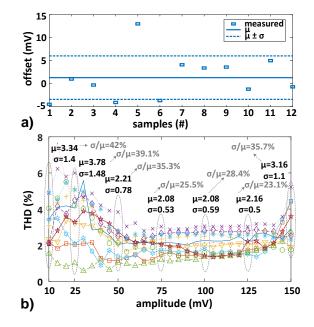

| Figure 3.19 [MEASUREMENTS] a) Measured input offset voltage of twelve DIG-                                                                                | 05                     |

| OTA dice and resulting mean value and standard deviation b) Measured total                                                                                |                        |

| e e                                                                                                                                                       |                        |

| harmonic distortion (THD) of twelve DIGOTA dice, their mean value, and                                                                                    |                        |

| standard deviation vs input sinewave amplitude (2.5 Hz input, $V_{DD}$ =0.3 V,                                                                            | 0.6                    |

| $C_L = 150 \text{ pF}$ .                                                                                                                                  | 86                     |

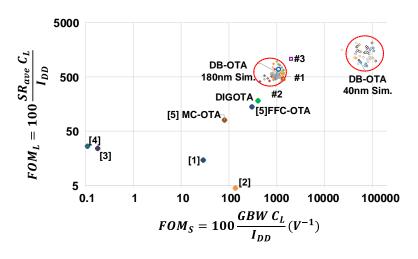

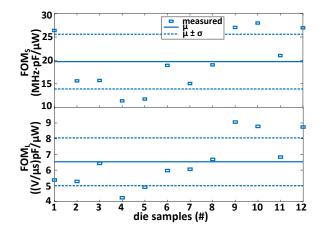

| Figure 3.20 [MEASUREMENTS] Measured figures of merit $FOM_S$ and $FOM_L$                                                                                  |                        |

| across DIGOTA dice. Power has been measured for sine wave (2.5 Hz input,                                                                                  | ~ 7                    |

| $V_{DD}$ =0.3 V, $C_L$ =150 pF)                                                                                                                           | 87                     |

| Figure 3.21 [MEASUREMENTS] $FOM_S$ and $FOM_L$ energy efficiency: compar-                                                                                 |                        |

| ison with OTAs with $V_{DD}$ <500mV and $V_{DD}$ >500mV.                                                                                                  | 88                     |

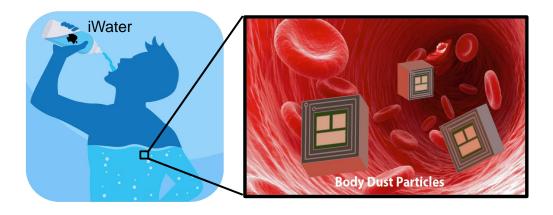

| Figure 4.1 Body dust illustration (CARRARA; GEORGIOU, 2018; Carrara, 2020).                                                                               | 90                     |

| Figure 4.2 Typical requirements for Bioelectronic Interfaces (LIU et al., 2020)                                                                           |                        |

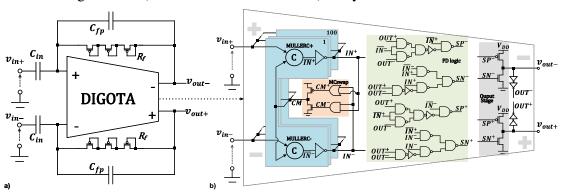

| Figure 4.3 a) BioDIGOTA schematic b) Fully differential DIGOTA.                                                                                           |                        |

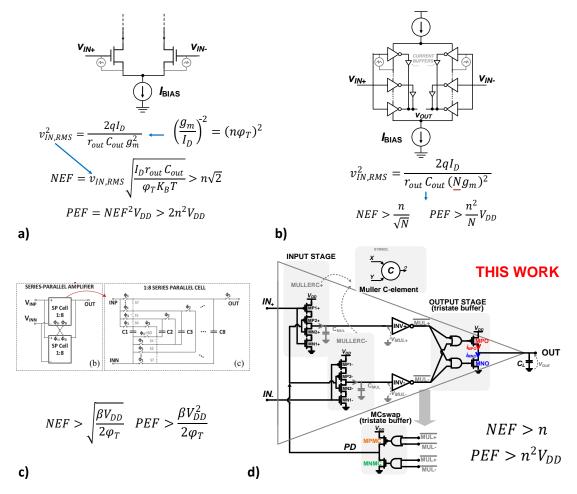

| Figure 4.4 a) NEF and PEF for differential pair, b) for stacked inverter-based (Mon-                                                                      |                        |

| <b>e</b> , , , , , , , , , , , , , , , , , , ,                                                                                                            |                        |

| dal; Hall, 2020), c) Switched-capacitor (Atzeni; AL., 2020), and d) digital                                                                               | 05                     |

| based amplifier of section 2.                                                                                                                             |                        |

| Figure 4.5 BioDIGOTA final layout in CMOS 180nm and chip picture.                                                                                         | 90                     |

| Figure 4.6 [SIMULATIONS] a) BioDIGOTA transient response. b) Wide spec-                                                                                   |                        |

| trum density for output signal from b) for input amplitude of 100 $\mu$ V at 40                                                                           | ~ 7                    |

| Hz                                                                                                                                                        |                        |

| Figure 4.7 [SIMULATIONS] BioDIGOTA frequency response.                                                                                                    |                        |

| Figure 4.8 [SIMULATIONS] BioDIGOTA Noise spectrum density.                                                                                                | 98                     |

| Figure 4.9 [SIMULATIONS] THD Histogram ( $\mu$ =5.13% and $\sigma$ =1.74%) for N=100                                                                      |                        |

| samples and input amplitude of 100 $\mu$ V                                                                                                                | 98                     |

| Figure 4.10 [SIMULATIONS] Integrated Noise Histogram ( $\mu$ =1.97 $\mu$ V <sub>RMS</sub> and $\sigma$ =0.                                                | $813\mu V_{\rm RMS}$ ) |

| for N=100 samples and BW from 0.01Hz to 10kHz.                                                                                                            | 98                     |

| Figure 4.11 [SIMULATIONS] Power Histogram ( $\mu$ =146nW and $\sigma$ =29nW) for N=10                                                                     | 00                     |

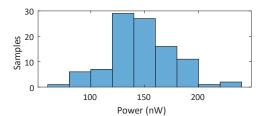

| samples                                                                                                                                                   |                        |

| Figure 4.12 [SIMULATIONS] Gain Histogram ( $\mu$ =28.2dB and $\sigma$ =1.13dB) for N=10                                                                   |                        |

| samples                                                                                                                                                   |                        |

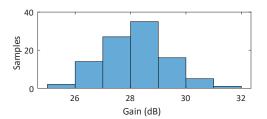

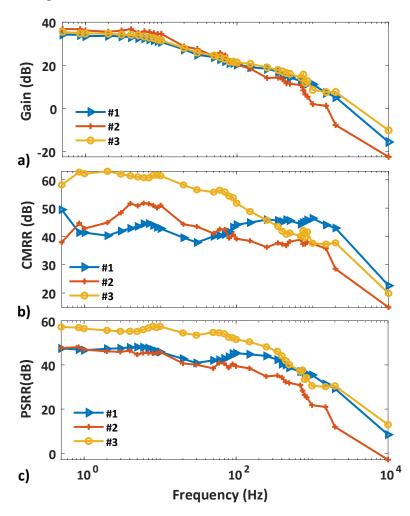

| Figure 4.13 a) Area breakdown and power breakdown of BioDIGOTA b) input and                                                                               |                        |

| output waveforms and c) Wide spectrum density for output signal for input                                                                                 |                        |

| amplitude of 3.5 mV at 3 Hz.                                                                                                                              | 100                    |

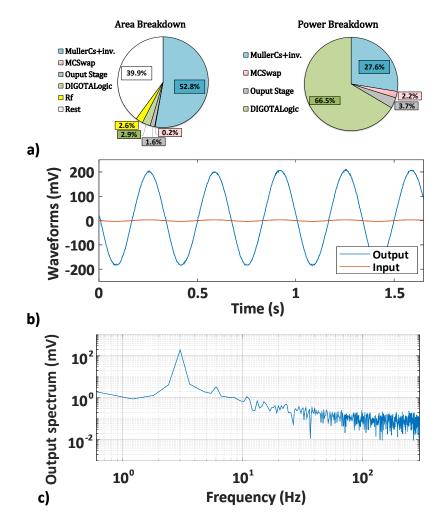

| Figure 4.14 Gain, CMRR and PSRR at $V_{\rm DD} = 400 mV$                                                                                                  |                        |

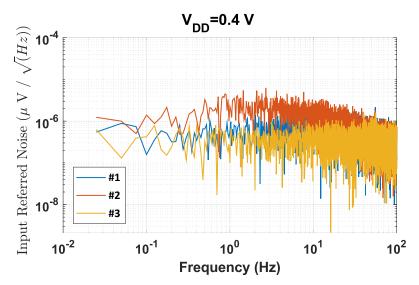

| Figure 4.15 BioDIGOTA measured noise spectrum density for each sample over                                                                                |                        |

| entire bandwidth at $V_{\rm DD} = 400 mV$ .                                                                                                               | 102                    |

| Figure 4.16 NEF and PEF versus Area.                                                                                                                      |                        |

|                                                                                                                                                           |                        |

# LIST OF TABLES

| Table 2.1 Monte Carlo simulation results: statistics parameters                    | 61  |

|------------------------------------------------------------------------------------|-----|

| Table 2.2 PERFORMANCE COMPARISON WITH THE STATE OF THE ART                         |     |

| (BEST PERFORMANCE IN BOLD)                                                         | 63  |

| Table 3.1 Parameters From Simulations, DIGOTA Transistor Sizes                     | 77  |

| Table 3.2       PERFORMANCE COMPARISON WITH STATE-OF-THE-ART OTAS                  |     |

| (BEST PERFORMANCE IN BOLD)                                                         | 87  |

| Table 4.1 Fully-Differential DIGOTA Combinational Logic Truth Table                | 92  |

| Table 4.2 Measured performance for all three samples @ $V_{DD}$ =400mV, 27 °C tem- |     |

| perature, input amplitude of 3.5mV and frequency of 3 Hz.                          | 101 |

| Table 4.3 Performance Summary and Comparison (BEST PERFORMANCE IN                  |     |

| BOLD)                                                                              | 103 |

|                                                                                    |     |

# CONTENTS

| 1 INTRODUCTION                                                          | 17   |

|-------------------------------------------------------------------------|------|

| 1.1 IoT Concept and Applications                                        | 18   |

| 1.2 IoT Network Architecture and Edge Nodes                             |      |

| 1.3 IoT Challenges in IC design                                         | 26   |

| 1.3.1 General Challenges Based on the IoT Nodes Available on the Market | 26   |

| 1.3.2 Digital Circuit Techniques For Power Reduction                    | 32   |

| 1.3.3 Analog Circuit Techniques For Power Reduction                     |      |

| 1.4 Digital-in-Concept Design Methodologies (DCDM)                      |      |

| 1.5 Thesis Organization                                                 |      |

| 2 DIGITAL-BASED OTA                                                     |      |

| 2.1 Previous art of ULV/ULP OTA Design                                  |      |

| 2.2 Circuit Analysis and Design                                         |      |

| 2.2.1 Qualitative Circuit Analysis                                      |      |

| 2.2.2 Quantitative Circuit Analysis                                     |      |

| 2.2.3 Circuit Design                                                    |      |

| 2.3 Layout                                                              |      |

| 2.4 Simulations Results                                                 |      |

| 2.5 Measurements Results                                                |      |

| 3 DIGOTA                                                                |      |

| 3.1 Circuit Analysis and Design                                         |      |

| 3.1.1 Qualitative Circuit Analysis                                      |      |

| 3.1.2 Quantitative Circuit Analysis                                     |      |

| 3.1.3 Circuit Design                                                    |      |

| 3.2 Layout                                                              |      |

| 3.3 Simulations Results                                                 |      |

| 3.4 Measurements Results                                                |      |

| 4 DIGITAL-BASED BIOSIGNAL AMPLIFIER                                     |      |

| 4.1 Circuit Design and Analysis                                         |      |

| 4.1.1 Circuit Analysis                                                  |      |

| 4.1.2 Circuit Design                                                    |      |

| 4.2 Layout                                                              |      |

| 4.3 Simulations Results                                                 |      |

| 4.4 Measurements Results                                                |      |

| 5 CONCLUSION                                                            |      |

| 5.1 Future work                                                         |      |

| REFERENCES                                                              | .108 |

### **1 INTRODUCTION**

The Internet of the Things (IoT) concept aims to turn everyday life objects into smart things by exploiting underlying technologies like ubiquitous and pervasive computing, embedded devices, communication technologies, sensor networks, internet protocols, and applications. The IoT enables physical objects to see, hear, feel, measure, think, and perform tasks by "talking" together, sharing information, and coordinating decisions. The emerging idea of IoT is rapidly finding its momentum throughout our modern life, aiming to increase our comfort and improve our quality of life.

The IoT architecture embracing all abstraction levels needs to be carefully conceived to make this concept reasonably viable. Challenges should be pointed out and addressed, including facts related to the cheapest technology that makes it possible: Complementary Metal Oxide Semiconductor (CMOS) technology. Devices made in CMOS are deployed on the edges of the IoT network gathering information from the physical world and sharing back to the cloud for more ambitious analytic capabilities.

Such edge devices, i.e., integrated circuits (ICs), comprise analog, mixed-signal, radio-frequency (RF), and digital processing capability (for instance, to get precise information from the sensors), and the definition of their architectures, technologies, and design methodologies play a fundamental role in the final performance of the whole system. Such aspects are intrinsically related to the last ICs area and power consumption, which in turn can be several times the IoT chain bottleneck. In other words, often, the edge device performance dictates the final decision to evaluate whether that application is viable or not.

In this introduction, the section 1.1 exposes the IoT concept principles as well as its applications, also showing their current market perspectives. In section 1.2, IoT network architectures are briefly reviewed, focusing on the CMOS edge devices description. Challenges found in such devices during their design are described in section 1.3, outlining the main current analog and digital techniques for power reduction. Based on several examples, the Digital-in-Concept Design Methodology (DCDM) trend is then introduced as an alternative design approach for the next generation of low power analog circuits within IoT nodes in section 1.4. The thesis organization is outlined in section 1.5, stressing how the following chapters are organized and the main thesis contributions.

### **1.1 IoT Concept and Applications**

In 1999, Kevin Ashton, co-founder of the Auto-ID Laboratory at MIT, gave birth to the term Internet of Things (ZHANG et al., 2020); however, the general concept idea has been around for much longer. Back in the early 80s, at Carnegie Mellon University, a group of students designed a system to get their campus Coca-Cola vending machine to report on its contents. They could make the machines let them know whether newly loaded drinks were cold or not. Later, in 1990, John Romkey connected a toaster to the internet for the first time using File Transfer Protocol (FTP) (ROMKEY, 2017).

In the following years, worldwide organizations and research institutes started to become excited about the Internet of Things, and several definitions and visions were proposed and spread. The International Telecommunication Union (ITU) delineates IoT as a universal information infrastructure for the society, permitting advanced and sophisticated services by interconnecting objects based on existing and evolving communication technologies (UNION, 2012). Both the UK Government Office of Science and the European Commission share a similar outlook of the IoT: *a world in which everyday objects are connected to a network so that valuable data can be shared* (ADVISER, 2014; SIOW; TIROPANIS; HALL, 2018). Among all definitions found in the current literature, common characteristics of each of these visions can be narrowed into four well-clear principles:

- Global scale principle: the IoT exists at a global scale (LEE; HANCOCK; HU, 2014).

- Physical world interaction principle: it consists of uniquely identifiable things with sensing or actuating capabilities linked to the physical world (ATZORI; IERA; MORABITO, 2010).

- Interconnection principle: things are interconnected by existing or future technologies so that data can be shared (KORTUEM et al., 2010; YICK; MUKHERJEE; GHOSAL, 2008).

- Servicing principle: analytics derived from gathered data have potential for societal impact through advanced services (SIOW; TIROPANIS; HALL, 2018).

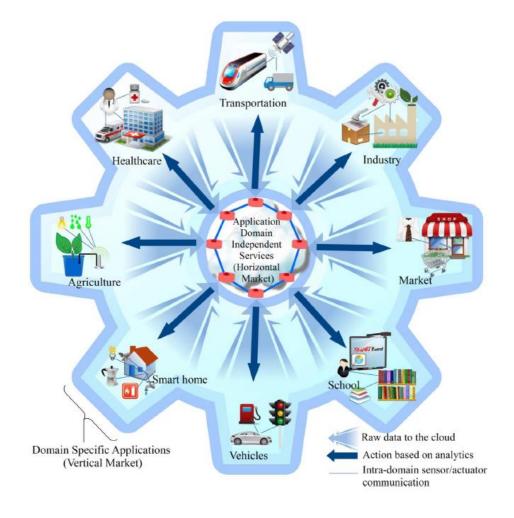

From the most cited paper about IoT in the Institute of Electrical and Electronics Engineers (IEEE) database (AL-FUQAHA et al., 2015), Fig.1.1 illustrates the global and comprehensive IoT concept in which every single domain-specific application is inFigure 1.1: *Vertical markets*: smart things with their supposed functions constitute domain specific applications. *Horizontal markets*: application domain independent services with ubiquitous computing and analytical services (AL-FUQAHA et al., 2015).

terfacing with domain-independent services, whereas in each domain sensors and actuators (IoT nodes or edge devices) broadcast relevant information directly with each other (AL-FUQAHA et al., 2015). Even though Fig. 1.1 summarizes reasonably well the IoT general concept through two abstraction levels/domains; this picture is far away from an authentic representation of the entire IoT network architecture, its challenges, and its real applicability potential. In the following section 1.2, the current state-of-the-art of the IoT architectures is shown, giving special attention to the challenges found on the hardware implementation of the edge devices.

The list of applications is extensive in enterprise settings, numbering more than two hundreds known applications, as reported by McKinsey (FREDRIK et al., 2019), from healthcare to monitoring chemical processes (MUKHERJEE; PAL; MISRA, 2012; CHEN et al., 2016; HOSSAIN; MUHAMMAD, 2016; BANOS et al., 2016; MAK; FAN, 2006; DANNER et al., 2016; JARA; GENOUD; BOCCHI, 2015; PADEN et al., 2016; HE; YAN; XU, 2014; PIOVESAN et al., 2016; CHIANESE et al., 2017; RAZIP et al., 2014; GIMENEZ et al., 2012; PLOENNIGS; SCHUMANN; LÉCUÉ, 2014; KOMNI-NOS; PHILIPPOU; PITSILLIDES, 2014; GUO; ZHANG; WANG, 2011; MUKHER-JEE; CHATTERJEE, 2014; GHOSH; PATIL; VUPPALA, 2013; YAN et al., 2013; JIN et al., 2014; SCHNIZLER et al., 2014; MUKHERJEE et al., 2013; VARGHEESE; DAHIR, 2014; NECHIFOR et al., 2014; ROBAK; FRANCZYK; ROBAK, 2013; VERDOUW; BEULENS; van der Vorst, 2013; KAMILARIS et al., 2016; CHIANG; LU; CASTILLO, 2017). Regardless of its nature, all the above-cited applications needs in general to pursue six goals: identification, sensing, communication, computation, services and semantics (SIOW; TIROPANIS; HALL, 2018). Identification is mandatory for the IoT to name and match services based on the demand. The IoT sensing means gathering data from related objects within the network and sending it back to the cloud. The IoT communication circuits connect heterogeneous objects together to deliver specific smart services. Processing units (e.g., microprocessors (MCU), SOCs, FPGAs) and software applications represent the computational IoT ability. As reported in (SIOW; TIROPANIS; HALL, 2018; FREDRIK et al., 2019), IoT services can be categorized into identity-related services, information aggregation services, collaborative-aware services, and ubiquitous services. In IoT, the definition of *Semantics* attributes to the qualification of distilling knowledge by distinctive sources to afford the required services (SIOW; TIROPANIS; HALL, 2018).

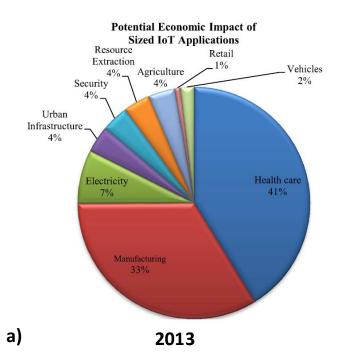

The vast list of applications and their potential services bring an appropriate amount of expectations and, the latter, investments. In 2013, McKinsey had highlighted a 300% growth in connected IoT devices in the last five years and a potential economic growth rate from 2 to 6 trillion annually by 2025. McKinsey had also shown in (JAMES; MICHAEL; JACQUES, 2013) its prediction of market share by 2025, as depicted in Fig.1.2a. In 2019, McKinsey updated these numbers, keeping the same optimism and presenting more interesting parameters (FREDRIK et al., 2019). At that year, the annual economic benefits related to the IoT were expected to reach 3.9 trillion to 11.1 trillion by 2025 (2X times compared to 2013). Moreover, the businesses number that use IoT technologies had increased from 13 % in 2014 to about 25% in 2019, the number of IoT-connected edge nodes around the world was predicted to escalate to 43 billion by 2023, and investments were projected to grow at 13.6% per year through 2022 (JAMES; MICHAEL; JACQUES, 2013; FREDRIK et al., 2019). Fig.1.2b also emphasizes (red square) that there is still room for economic growth in the device layer (edge devices or IoT nodes, which are the

Figure 1.2: a) McKinsey shows in 2013 its prediction of market share by 2025 (JAMES; MICHAEL; JACQUES, 2013) b) Significant opportunities along the IoT technology layers, highlighting a healthy market growth for edge devices (FREDRIK et al., 2019).

Markets for the IoT technology layers hold significant opportunities.

| loT technology<br>stack                        | Description                                                                                                                                                   | Market<br>size | Market growth<br>outlook | Technology<br>maturity |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|------------------------|

| Business<br>applications                       | Customer- or device-facing functionality that uses<br>insights for added value (eg, dynamic dashboard,<br>mobile app and embedded software)                   |                | 1                        |                        |

| Enablement<br>platforms and<br>cloud computing | Enablement platforms<br>Device-enablement platforms (including endpoint<br>protection and access management) for obtaining,<br>importing, and processing data | ¢              | 0                        |                        |

|                                                | Analytics and visualization applications (including artificial<br>intelligence) for insight generation, reporting, and<br>complex event handling              |                |                          |                        |

|                                                | Cloud computing<br>Data processing (usually in real time) within a central<br>cloud server farm or with edge computing                                        | C              |                          |                        |

|                                                | Data storage and integration using standard protocols                                                                                                         |                |                          |                        |

| Connectivity                                   | Data transmission and basic device connectivity<br>features with cellular networks, low-power wide-area<br>networks, local wireless networks                  | •              |                          | •                      |

| Devices                                        | Connected devices (eg, cars, buildings, equipment, wearables)                                                                                                 |                | Ø                        |                        |

|                                                | Sensors providing environmental information (eg,<br>temperature, pressure, motion, filling level, pollution)<br>and actuators                                 |                |                          |                        |

| McKinsey                                       | 2010                                                                                                                                                          |                |                          |                        |

| & Company                                      | <b>2019</b>                                                                                                                                                   |                |                          |                        |

Figure 1.3: The IoT architecture. (a) Three-layer. (b) Middle-ware based. (c) serviceoriented architecture (SOA) based. (d) Five-layer (AL-FUQAHA et al., 2015).

focus of this thesis) within the IoT technological stack. Also, in (FREDRIK et al., 2019), it is quoted that "Smart devices—the foundational layer of the IoT technology stack and the most mature product category—are dominated by large manufacturers and specialist suppliers and enjoy healthy market growth."

Although relatively imprecise, all these speculations point to the potentially significant and fast-paced growth of the IoT, especially applications related to industries and services.

### **1.2 IoT Network Architecture and Edge Nodes**

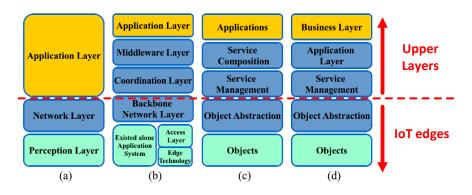

The IoT architecture must be able to interconnect billions (Giga) or trillions (Tera) of heterogeneous objects through the Internet, demanding a flexible layered architecture (AL-FUQAHA et al., 2015). Fig. 1.3 shows the most relevant IoT technological stacks found so far in the literature (AL-FUQAHA et al., 2015). The basic model is the three-layer architecture consisting of the application, network, and perception layers. Some other models have been proposed adding more abstraction such as middle-ware-based, service-oriented architecture (SOA) based, and five-layers (WU et al., 2010).

Once the five layers have a similar network shape as in current internet protocol (i.e., the Transmission Control Protocol/Internet Protocol- TCP/IP), Al-Fuqaha et al. affirm that the research and standardization point to this direction (AL-FUQAHA et al., 2015). Each layer can be described as follows:

• **Business Layer:** The business layer manages the overall IoT system activities and services. Its responsibilities are to build a business model, graphs, flowcharts, etc., based on the received data from the Application layer. In this layer, it is where is

supposed to be implemented most of the analytics (SIOW; TIROPANIS; HALL, 2018). In addition, monitoring and management of the underlying four layers are achieved at this layer. Once it is very close to the final client, this is the layer with the significant market impact.

- Application layer: The application layer provides the services required by the customers (NGU et al., 2017). For instance, the application layer can provide precious information such as data from the sensors to the client who asks for. This layer importance is that it can offer high-relevant smart services to fulfil the customers' needs (NGU et al., 2017).

- Service Management: This specific layer matches services to its requester based on addresses and names (NGU et al., 2017). This layer enables IoT applications to work heterogeneously with the data regardless of the hardware platform found below in the stack. In addition, it processes received data, deciding and delivering the needed services over the network protocols (NGU et al., 2017).

- Object Abstraction: This layer transfers data produced by the Objects layer to the Service Management layer through secure channels (PALATTELLA et al., 2013). The information can be shared through various technologies such as NFC, ZigBee, IrDA, UWB/IR, ANT, DASH7, Z-Wave, RPL, BTLE, 6LowPAN, 802.15.4, SAN, etc (DECUIR, 2014).

- In the first layer (perception layer), the smart objects or edge devices, serves as an IoT external-physical sensors which aim to gather and post-process the relevant information by demand (AL-FUQAHA et al., 2015). Edge devices comprise sensors and/or actuators to perform different functionalities(AL-FUQAHA et al., 2015). Standardized plug-and-play mechanisms still be a challenge in this layer due to their intrinsic heterogeneous characteristics. The perception layer digitizes and transfers data to the Object Abstraction layer through secure channels.

In this entire ecosystem, there is a set of challenges at which one is worthy of being mentioned: availability and reliability. The IoT availability must be considered in the hardware and software levels to provide services for customers anywhere and anytime. Hardware availability refers to the existence of devices that are always compatible with the IoT functionalities and protocols. The challenges related to the hardware system, which generates and collects data (IoT nodes or devices placed on the edges), are deeply investigated here, leading us to conclude the need to design ultra-low-power/area CMOS

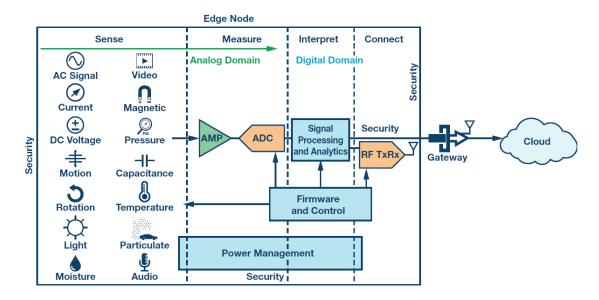

Figure 1.4: Modern edge device with embedded intelligence before connecting to the cloud. Analytics can be applied to pre-process the raw data coming from the sensors before sending it upwards for deeper data mining analysis (BEAVERS, 2018).

systems. These systems also include analog/RF IoT interfaces.

Fig.1.4 shows an ordinary block diagram for an edge device, which affords some capacity to measure and interpret the raw data before connecting to a gateway, and subsequently, to the cloud (BEAVERS, 2018; ALIOTO, 2017). In this case, the data is processed with some analytics before it is sent for deeper data mining. Albeit the block diagram presented here can be further reduced by eliminating the signal processing and analytic subblocks, i.e., leaving these tasks to the cloud to reduce the total node power/area, the current trend is to increase the computing resources on the edges to minimize the big data issue (CHANG et al., 2014; MORGAN, 2016). A wide spectrum of prepossessing strategies have been studied and proposed in the IoT context such as principle component analysis (PCA) (KORAT; ALIMOHAMMAD, 2019), pattern reduction, dimensionality reduction, feature selection (MARCHIONI et al., 2020), compressed sensing (MANGIA et al., 2020), and distributed computing methods (EL-SAYED et al., 2017).

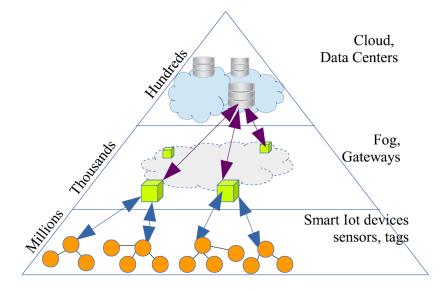

In the IoT architecture context, embedding more and more computing ability on edges is called Fog Computing (a.k.a. cloudlets or edge computing). Fog resources can perform data aggregation to send partially processed data instead of raw data to the cloud data centers for further processing. Fog resources can be positioned either in intelligent objects or before the cloud data centers; thus, providing a better delay-performance trade-off (AL-FUQAHA et al., 2015) (See Fig. 1.5 for better illustration).

Nowadays, hardware availability to gather and process the environment informa-

Figure 1.5: The role of the cloud and fog resources in the delivery of IoT services (AL-FUQAHA et al., 2015).

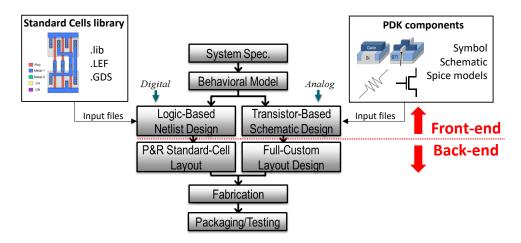

tion is strictly related to the cheapest technology used to develop the IoT nodes, i.e., CMOS technology. Integrated Circuits (IC) techniques connect CMOS devices using electronic design automation (EDA) tools. Such tools follow design flows. The Fig. 1.6 shows a simplified view of the two main IC design flows used to develop the hardware of IoT nodes: digital and analog design flow (MAROLT; SCHEIBLE; JERKE, 2013).

Digital design flow automatically creates the final circuit layout based on a given design specification and design constraints. Depending on a fixed amount of layout components available from a design library as standard cells (logical gates), a high level of automation in digital design is achieved by heuristic algorithms that usually perform the different layout tasks like placement and routing. This automation is also possible due to the discrete nature of digital signals (MAROLT, 2019), reducing the total design time, layout design effort, and time to market.

On the other hand, in the analog/RF domain, design productivity is considerably smaller than for digital circuits, especially in advanced CMOS technologies. As shown in the Fig. 1.6, full custom design flow is adopted to implement analog and RF blocks, simulating their schematic views numerically and doing placements and routing manually to reduce layout-parasitic side effects. This flow is assumed because analog interfaces handle continuous-time, continuous amplitude signals from diverse physical sources (from sensors, for instance), mutual perturbation, and parasitic effects. Such requirements demand to comprehensively harness the entire spectrum and variety of all available degrees of freedom from the process design kit (PDK) components (transistors, capacitors, resis-

Figure 1.6: Simplified IC Digial and Analog Design Flow (MAROLT; SCHEIBLE; JERKE, 2013).

tors, diodes, etc.).

In the next section 1.3, the IC design challenges related to developing IoT nodes are revised based on available devices in the current electronic market, showing the need for new design techniques to reduce analog block power and area. Based on this demand, in the section 1.4, Digital-in-Concept Design Methodologies (DCDM) are introduced and reviewed, defining the fundamental concept for the subsequent thesis chapters.

### **1.3 IoT Challenges in IC design**

#### 1.3.1 General Challenges Based on the IoT Nodes Available on the Market

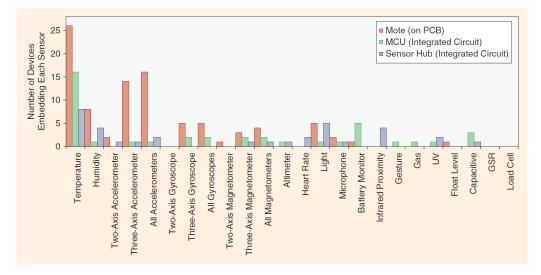

The integrated circuits IoT nodes, depicted in Fig. 1.4, aim to have sensing and processing capabilities, to be communicatively accessible, unobtrusive (reduced form-factor), cost-effective, untethered (self-powered), and long-lived (to avoid maintenance costs) (ALIOTO, 2021). In 2018, (ALIOTO; SHAHGHASEMI, 2018) released a proper survey regarding the current state-of-the-art of commercial IoT devices, comprising Motes (PCBs), MCUs, and sensor hubs. This survey of commercial IoT devices was done world-wide, using platforms such as Digi-Key to collect the data.

Sensing and processing capabilities in IoT nodes are required to process sensed data locally to a certain extent. Fig. 1.7 shows a histogram of commercial IoT devices embedding each type of sensor (ALIOTO; SHAHGHASEMI, 2018). Temperature sensors are the most widely diffused ones mainly due to their intrinsic compatibility with the

Figure 1.7: A histogram of commercial IoT devices embedding each type of sensor (ALIOTO; SHAHGHASEMI, 2018). This survey of commercial IoT devices was done on a worldwide scale, using platforms such as Digi-Key to collect the data.

semiconductor itself. However, a drawback is clearly seen in these devices that concerns the interface resolution. Each sensor resolution needs to be tweaked to the maximum resolution across several applications domain to maximize its flexibility, i.e., to cover the largest possible market, it is common to find ADC overdesign adding a relevant energy waste. On average, an Effective Number of Bits (ENOB) of 6.2 bits is the resolution found in this survey within this broad sensor type spectrum.

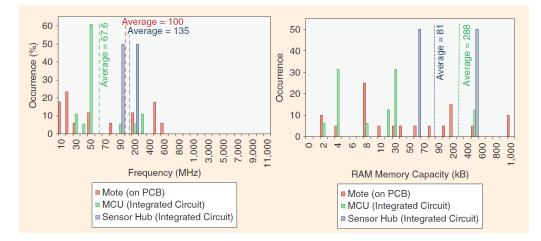

Some computing power is expected to be available in the IoT nodes to partially process the raw data and deliver more enriched information up to the next layer (CAPRA et al., 2019; CAPRA et al., 2020). In (ALIOTO; SHAHGHASEMI, 2018), all types of IoT nodes are based on microcontrollers. Typically, the microcontroller is an ARM Cortex M0-M4, MSP430, 8051, Atmega, XSCALE, and QUARK. Most of the integrated MCU has 50 MHz of maximum clock frequency while containing 288kB of RAM capacity as a mean value, as justified by their on-chip implementation (see Fig. 1.8). For no-volatile memory, the on-chip flash memory capacity in MCUs is typically around to 64 kilobytes (ALIOTO; SHAHGHASEMI, 2018).

The IoT nodes need to transmit raw, preconditioned, compressed, or distilled data (e.g., extracted features). It can be done either in a wireline or wireless mode. Serial peripheral interfaces (SPIs)/inter-integrated circuits (I2Cs) for intra-sensors communication and universal serial buses (USBs)/universal asynchronous receiver-transmitters (UARTs) for setting information sharing inside of cables are the most common wireline interfaces. For wireless communication, most MCUs operate at 2.4 GHz. At the same time, motes

Figure 1.8: A histogram of maximum microcontroller clock frequency and of RAM memory capacity in commercial IoT nodes (ALIOTO; SHAHGHASEMI, 2018).

are more diversified in terms of carrier frequency, being 60% working at ISM-band. In contrast, the remaining ones operate at different available bands (i.e., from 315 to 1,900 MHz). Wireless interfaces are well known for a significant fraction of the IoT device power consumption, with best-in-class commercial radios consuming an energy per bit on the order of a few tens of nanojoules per bit (ALIOTO; SHAHGHASEMI, 2018). However, there are numerous academic prototypes with the energy-efficiency around one nJ/bit. The bad news is that the energy/bit is expected to rest relatively constant in the decade ahead (1.34x/year for sub-GHz and 1.42x/year for GHz frequency carrier (ALIOTO; DE; MARONGIU, 2018)). Even worse, during transmission, the energy per bit cannot be further reduced through improvements in modulation techniques and spectral efficiency for the already existing schemes with reasonably low complexity (e.g., on-off keying). They are only 10 times (or 10 dB) surpassing the minimum theoretical limit (ALIOTO, 2017; OTIS; RABAEY, 2007).

The IoT node size is another vital specification once it could enable or jeopardize the application. Following Bell's law, personal computers have been historically shrinking by 10–100× per decade; hence, the IoT is also expected to harness this size shrinking. Fig. 1.9 shows the form-factor of commercial off-the-shelf IoT devices found in the market until 2018. A sub-10mm-scale MCU (with an average size equal to  $5.5 \text{ mm}^2$ ) is encountered, while the centimeter scale is found for motes mounted in PCB, which have more functionalities than the MCUs alone.

Supposing that the goal is to have one trillion devices connected in the following years (global scale principle from section 1.1), taking from Fig. 1.9 the  $62 \text{ mm}^2$  as the size of each IoT, this will lead to a total area equal to 0.0000416% of total land earth area,

Figure 1.9: The commercial devices size and cost for distributed sensing (ALIOTO; SHAHGHASEMI, 2018).