# Reconfigurable Gate Driver Toward High-Power Efficiency and High-Power Density Converters

Thèse

Mousa Karimi

Doctorat en génie électrique

Philosophiæ doctor (Ph. D.)

Québec, Canada

# **Reconfigurable Gate Driver Toward High-Power Efficiency and High-Power Density Converters**

**Thèse**

Mousa Karimi

Sous la direction de:

Benoit Gosselin, directeur de recherche Mohamad Sawan, codirecteur de recherche

# Résumé

Les systèmes de gestion de l'énergie exigent des convertisseurs de puissance pour fournir une conversion de puissance adaptée à diverses utilisations. Il existe différents types de convertisseurs de puissance, tel que les amplificateurs de puissance de classe D, les demi-ponts, les ponts complets, les amplificateurs de puissance de classe E, les convertisseurs buck et dernièrement les convertisseurs boost. Prenons par exemple les dispositifs implantables, lorsque l'énergie est prélevée de la source principale, des convertisseurs de puissance buck ou boost sont nécessaires pour traiter l'énergie de l'entrée et fournir une énergie propre et adaptée aux différentes parties du système. D'autre part, dans les stations de charge des voitures électriques, les nouveaux téléphones portables, les stimulateurs neuronaux, etc., l'énergie sans fil a été utilisée pour assurer une alimentation à distance, et des amplificateurs de puissance de classe E sont développés pour accomplir cette tâche. Les amplificateurs de puissance de classe D sont un excellent choix pour les casques d'écoute ou les haut-parleurs en raison de leur grande efficacité. Dans le cas des interfaces de capteurs, les demi-ponts et les ponts complets sont les interfaces appropriées entre les systèmes à faible et à forte puissance. Dans les applications automobiles, l'interface du capteur recoit le signal du côté puissance réduite et le transmet à un réseau du côté puissance élevée. En outre, l'interface du capteur doit recevoir un signal du côté haute puissance et le convertir vers la côté basse puissance. Tous les systèmes mentionés ci-dessus nécessitent l'inclusion d'un pilote de porte spécifique dans les circuits, selon les applications. Les commandes de porte comprennent généralement un décalage du niveau de commande niveau supérieur, le levier de changement de niveau inférieur, une chaîne de tampon, un circuit de verrouillage sous tension, un circuit de temps mort, des portes logiques, un inverseur de Schmitt et un mécanisme de démarrage. Ces circuits sont nécessaires pour assurer le bon fonctionnement des systèmes de conversion de puissance. Un circuit d'attaque de porte reconfigurable prendrait en charge une vaste gamme de convertisseurs de puissance ayant une tension d'entrée  $V_{IN}$  et un courant de sortie  $I_{Load}$  variables.

L'objectif de ce projet est d'étudier intensivement les causes de différentes pertes dans les convertisseurs de puissance et de proposer ensuite de nouveaux circuits et méthodologies dans les différents circuits des conducteurs de porte pour atteindre une conversion de puissance avec une haute efficacité et densité de puissance. Nous proposons dans cette thèse de nouveaux circuits de gestion des temps mort, un Shapeshifter de niveau plus élevé et un Shapeshifter de

niveau inférieur avec de nouvelles topologies qui ont été pleinement caractérisées expérimentalement. De plus, l'équation mathématique du temps mort optimal pour les faces haute et basse d'un convertisseur buck est dérivée et expérimentalement prouvée. Les circuits intégrés personnalisés et les méthodologies proposées sont validés avec différents convertisseurs de puissance, tels que les convertisseurs semi-pont et en boucle ouverte, en utilisant des composants standard pour démontrer leur supériorité sur les solutions traditionnelles. Les principales contributions de cette recherche ont été présentées à sept conférences prestigieuses, trois articles évalués par des pairs, qui ont été publiés ou présentés, et une divulgation d'invention.

Une contribution importante de ce travail recherche est la proposition d'un nouveau générateur actif CMOS intégré dédié de signaux sans chevauchement. Ce générateur a été fabriqué à l'aide de la technologie AMS de  $0.35\mu m$  et consomme 16.8mW à partir d'une tension d'alimentation de 3.3V pour commander de manière appropriée les côtés bas et haut d'un demi-pont afin d'éliminer la propagation. La puce fabriquée est validée de façon expérimentale avec un demi-pont, qui a été mis en œuvre avec des composants disponibles sur le marché et qui contrôle une charge R-L. Les résultats des mesures montrent une réduction de 40% de la perte totale d'un demi-pont de 45V d'entrée à 1MHz par rapport au fonctionnement du demi-pont sans notre circuit intégré dédié. Le circuit principal du circuit d'attaque de grille côté haut est le décaleur de niveau, qui fournit un signal de grande amplitude pour le commutateur de puissance côté haut. Une nouvelle structure de décalage de niveau avec un délai de propagation minimal doit être présentée. Nous proposons une nouvelle topologie de décalage de niveau pour le côté haut des drivers de porte afin de produire des convertisseurs de puissance efficaces. Le SL présente des délais de propagation mesurés de 7.6ns. Les résultats mesurés montrent le fonctionnement du circuit présenté sur la plage de fréquence de 1MHz à 130MHz. Le circuit fabriqué consomme 31.5pW de puissance statique et 3.4pJ d'énergie par transition à 1kHz,  $V_{DDL} = 0.8V$ ,  $V_{DDH} = 3.0V$ , et une charge capacitive  $C_L = 0.1pF$ . La consommation énergétique totale mesurée par rapport à la charge capacitive de 0.1 à 100nFest indiquée. Un autre nouveau décalage vers le bas est proposé pour être utilisé sur le côté bas des pilotes de portes. Ce circuit est également nécessaire dans la partie  $R_x$  du réseau de bus de données pour recevoir le signal haute tension du réseau et délivrer un signal de faible amplitude à la partie basse tension. L'une des principales contributions de ces travaux est la proposition d'un modèle de référence pour l'abaissement de niveau à puissance unique reconfigurable. Le circuit proposé pilote avec succès une gamme de charges capacitives allant de 10fF à 350pF. Le circuit présenté consomme des puissances statiques et dynamiques de 62.37pW et  $108.9\mu W$ , respectivement, à partir d'une alimentation de 3.3V lorsqu'il fonctionne à 1MHz et pilote une charge capacitive de 10pF. Les résultats de la simulation post-layout montrent que les délais de propagation de chute et de montée dans les trois configurations sont respectivement de l'ordre de 0.54 à 26.5ns et de 11.2 à 117.2ns. La puce occupe une surface de  $80\mu m \times 100\mu m$ . En effet, les temps morts des côtés hauts et bas varient en raison de la différence de fonctionnement des commutateurs de puissance côté haut et côté bas, qui sont respectivement en commutation dure et douce. Par conséquent, un générateur de temps mort reconfigurable asymétrique doit être ajouté aux pilotes de portes traditionnelles pour obtenir une conversion efficace. Notamment, le temps mort asymétrique optimal pour les côtés hauts et bas des convertisseurs de puissance à base de Gan doit être fourni par un circuit de commande de grille reconfigurable pour obtenir une conception efficace. Le temps mort optimal pour les convertisseurs de puissance dépend de la topologie. Une autre contribution importante de ce travail est la dérivation d'une équation précise du temps mort optimal pour un convertisseur buck. Le générateur de temps mort asymétrique reconfigurable fabriqué sur mesure est connecté à un convertisseur buck pour valider le fonctionnement du circuit proposé et l'équation dérivée. De plus le rendement d'un convertisseur buck typique avec  $T_{DLH}$  minimum et  $T_{DHL}$  optimal (basé sur l'équation dérivée) à  $I_{Load} = 25mA$  est amélioré de 12% par rapport à un convertisseur avec un temps mort fixe de  $T_{DLH} = T_{DHL} = 12ns$ .

### Abstract

Power management systems require power converters to provide appropriate power conversion for various purposes. Class D power amplifiers, half and full bridges, class E power amplifiers, buck converters, and boost converters are different types of power converters. Power efficiency and density are two prominent specifications for designing a power converter. For example, in implantable devices, when power is harvested from the main source, buck or boost power converters are required to receive the power from the input and deliver clean power to different parts of the system. In charge stations of electric cars, new cell phones, neural stimulators, and so on, power is transmitted wirelessly, and Class E power amplifiers are developed to accomplish this task. In headphone or speaker driver applications, Class D power amplifiers are an excellent choice due to their great efficiency. In sensor interfaces, half and full bridges are the appropriate interfaces between the low- and high-power sides of systems. In automotive applications, the sensor interface receives the signal from the low-power side and transmits it to a network on the high-power side. In addition, the sensor interface must receive a signal from the high-power side and convert it down to the low-power side. All the above-summarized systems require a particular gate driver to be included in the circuits depending on the applications. The gate drivers generally consist of the level-up shifter, the level-down shifter, a buffer chain, an under-voltage lock-out circuit, a deadtime circuit, logic gates, the Schmitt trigger, and a bootstrap mechanism. These circuits are necessary to achieve the proper functionality of the power converter systems. A reconfigurable gate driver would support a wide range of power converters with variable input voltage  $V_{IN}$  and output current  $I_{Load}$ . The goal of this project is to intensively investigate the causes of different losses in power converters and then propose novel circuits and methodologies in the different circuits of gate drivers to achieve power conversion with high-power efficiency and density. We propose novel deadtime circuits, level-up shifter, and level-down shifter with new topologies that were fully characterized experimentally. Furthermore, the mathematical equation for optimum deadtimes for the high and low sides of a buck converter is derived and proven experimentally. The proposed custom integrated circuits and methodologies are validated with different power converters, such as half bridge and open loop buck converters, using off-the-shelf components to demonstrate their superiority over traditional solutions. The main contributions of this research have been presented in seven high prestigious conferences, three peer -reviewed articles, which have been

published or submitted, and one invention disclosure.

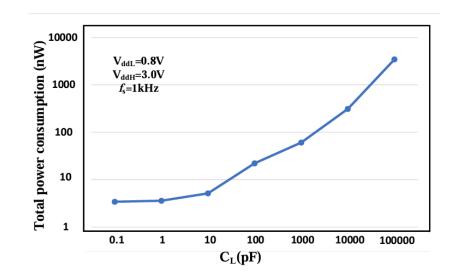

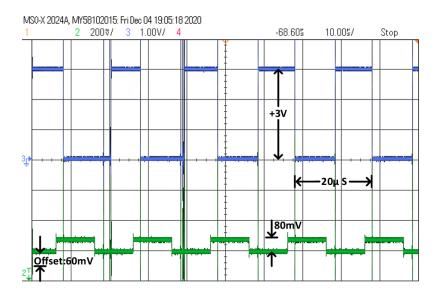

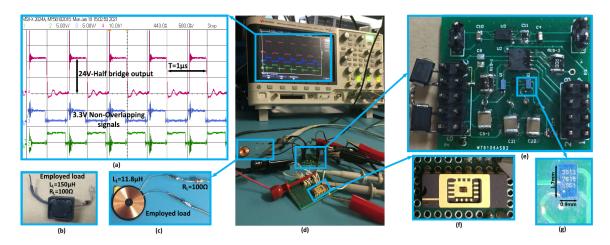

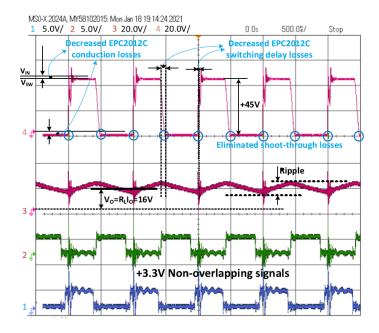

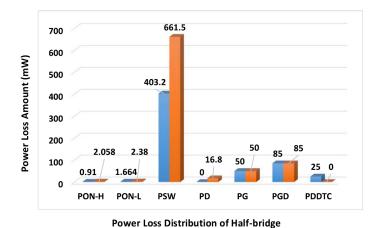

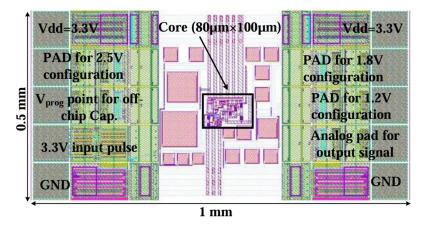

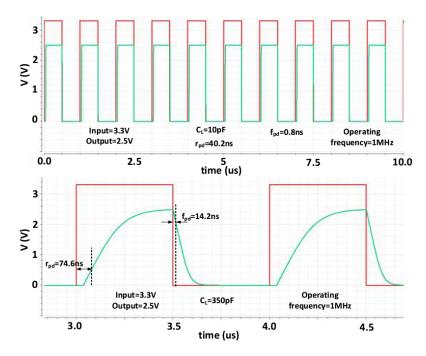

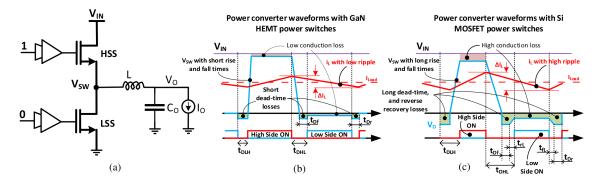

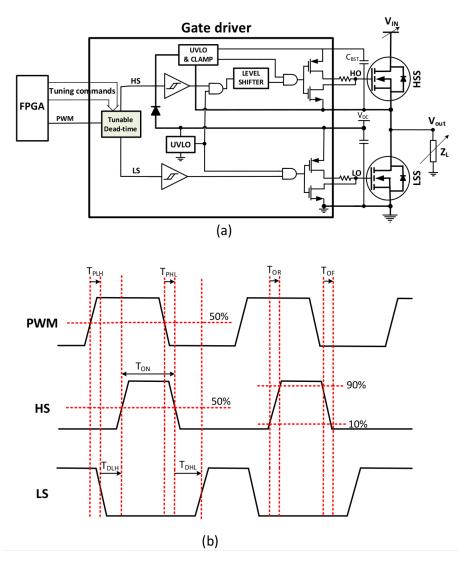

An important contribution of this research work is the proposal of a novel custom integrated CMOS active non-overlapping signal generator, which was fabricated using the  $0.35-\mu m$  AMS technology and consumes 16.8mW from a 3.3-V supply voltage to appropriately drive the low and high sides of the half bridge to remove the shoot-through. The fabricated chip is validated experimentally with a half bridge, which was implemented with off-the-shelf components and driving a R-L load. Measurement results show a 40% reduction in the total loss of a 45-Vinput 1 - MHz half bridge compared with the half bridge operation without our custom integrated circuit. The main circuit of high-side gate driver is the level-up shifter, which provides a signal with a large amplitude for the high-side power switch. A new level shifter structure with minimal propagation delay must be presented. We propose a novel level shifter topology for the high side of gate drivers to produce efficient power converters. The LS shows measured propagation delays of 7.6ns. The measured results demonstrate the operation of the presented circuit over the frequency range of 1MHz to 130MHz. The fabricated circuit consumes 31.5pW of static power and 3.4pJ of energy per transition at 1kHz,  $V_{DDL} = 0.8V$ ,  $V_{DDH} = 3.0V$ , and capacitive load  $C_L = 0.1pF$ . The measured total power consumption versus the capacitive load from 0.1pF to 100nF is reported. Another new level-down shifter is proposed to be used on the low side of gate drivers. Another new level-down shifter is proposed to be used on the low side of gate drivers. This circuit is also required in the  $R_x$  part of the data bus network to receive the high-voltage signal from the network and deliver a signal with a low amplitude to the low-voltage part. An essential contribution of this work is the proposal of a single supply reconfigurable level-down shifter. The proposed circuit successfully drives a range of capacitive load from 10fF to 350pF. The presented circuit consumes static and dynamic powers of 62.37pW and  $108.9\mu W$ , respectively, from a 3.3-V supply when working at 1MHz and drives a 10pF capacitive load. The post-layout simulation results show that the fall and rise propagation delays in the three configurations are in the range of 0.54-26.5ns and 11.2-117.2ns, respectively. Its core occupies an area of  $80\mu m \times 100\mu m$ . Indeed, the deadtimes for the high and low sides vary due to the difference in the operation of the high- and low-side power switches, which are under hard and soft switching, respectively. Therefore, an asymmetric reconfigurable deadtime generator must be added to the traditional gate drivers to achieve efficient conversion. Notably, the optimal asymmetric deadtime for the high and low sides of GaN-based power converters must be provided by a reconfigurable gate driver to achieve efficient design. The optimum deadtime for power converters depends on the topology. Another important contribution of this work is the derivation of an accurate equation of optimum deadtime for a buck converter. The custom fabricated reconfigurable asymmetric deadtime generator is connected to a buck converter to validate the operation of the proposed circuit and the derived equation. The efficiency of a typical buck converter with minimum  $T_{DLH}$  and optimal  $T_{DHL}$  (based on the derived equation) at  $I_{Load} = 25mA$  is improved by 12% compared to a converter with a fixed deadtime of  $T_{DLH} = T_{DHL} = 12ns$ .

# Contents

| R                | ésumé                                                                                                                                                                                                           |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\mathbf{A}$ l   | bstract                                                                                                                                                                                                         |  |

| C                | ontents                                                                                                                                                                                                         |  |

| Li               | st of Tables                                                                                                                                                                                                    |  |

| Li               | st of Figures                                                                                                                                                                                                   |  |

| $\mathbf{R}_{0}$ | emerciements                                                                                                                                                                                                    |  |

| As               | vant-propos                                                                                                                                                                                                     |  |

| In               | atroduction                                                                                                                                                                                                     |  |

| 1                | Methodology1.1 Data-bus Requirements Summary                                                                                                                                                                    |  |

| 2                | A 7.6-ns Delay Subthreshold Level-Shifter Leveraging Parasitic Capacitance Voltage-Controlled Current Source                                                                                                    |  |

|                  | 2.1 Résumé 2.2 Abstract 2.3 Introduction 2.4 Proposed LS Architecture and Operation 2.5 Circuit Implementation and Simulation 2.6 Experimental Results 2.7 Discussion and Performance Comparison 2.8 Conclusion |  |

| 3                | An Active Dead-Time Control Circuit With Timing Elements for a 45-V Input 1-MHz Half-Bridge Converter 3.1 Résumé                                                                                                |  |

|  | 4.1                      | Chip Applications Résumé                                                            |

|--|--------------------------|-------------------------------------------------------------------------------------|

|  | 4.2                      | Abstract                                                                            |

|  | 4.3                      | Introduction                                                                        |

|  | 4.4                      | Proposed Reconfigurable Level Down Shifter                                          |

|  | 4.5                      | Circuit Implementation                                                              |

|  | 4.6                      | Post-Layout Simulation Results                                                      |

|  | 4.7                      | Conclusion                                                                          |

|  | tion                     | for Efficient GaN HEMT Power Converters                                             |

|  |                          |                                                                                     |

|  | 5.1                      | Résumé                                                                              |

|  | 5.1<br>5.2               |                                                                                     |

|  |                          | Résumé                                                                              |

|  | 5.2                      | Résumé                                                                              |

|  | 5.2<br>5.3               | Résumé                                                                              |

|  | 5.2<br>5.3<br>5.4        | Résumé                                                                              |

|  | 5.2<br>5.3<br>5.4<br>5.5 | Résumé Abstract Introduction Proposed Tunable Deadtime Circuit Measured Performance |

# List of Tables

| 0.1 | Ideal switch characteristics                                                    | 5  |

|-----|---------------------------------------------------------------------------------|----|

| 0.2 | Internal capacitances for a power MOSFET                                        | 6  |

| 0.3 | Examples of different power converter leveraging their gate drivers             | 15 |

| 2.1 | Transistor sizes of the Proposed LS in Figure 2.4                               | 28 |

| 2.2 | Performance Summary and Comparison with other solutions. $E_c$ : Energy con-    |    |

|     | sumption; $P_s$ : Static power consumption; FoM=Range/delay                     | 41 |

| 3.1 | Aspect ratios of TS-WSCS transistors                                            | 50 |

| 3.2 | Performance comparison with previous works                                      | 63 |

| 4.1 | Components specifications of the proposed RSS-LDS                               | 70 |

| 4.2 | Internal capacitances for a power MOSFET                                        | 72 |

| 4.3 | Performance comparison of the proposed RSS-LDS configured to generated $2.5V$ . | 73 |

| 5.1 | Dimensions of all components adopted for realizing the circuit. $N/A=Non-$      |    |

|     | Applicable; ST:Schmitt Trigger; MP,P,N,T,MN: are Tagged on Figures 5.4, 5.6;    |    |

|     | CS: Wide Swing Current Source                                                   | 85 |

| 5.2 | Performance Comparison of the proposed WRM-TDCWITH similar works                | 96 |

| 5.3 | GAN Power Loss Formulas                                                         | 98 |

# List of Figures

| 0.1  | Different energy sources, DC-DC conversion, and IC level voltages                    |

|------|--------------------------------------------------------------------------------------|

| 0.2  | Different power switch configurations, (a) Low-Side, (b) High-Side, (c) Half-        |

|      | Bridge, (d) Full-Bridge (H-Bridge)                                                   |

| 0.3  | General block diagram of different power converters in various applications,         |

|      | (a) Class-E power amplifier for wireless power transmission for freely moving        |

|      | animals, (b) Class-D power amplifier for speaker, (c) Buck converter configu-        |

|      | ration, (d) Full-Bridge (H-Bridge) for data bus network, (e) Boost converter         |

|      | configuration                                                                        |

| 0.4  | (a) Ideal switch waveforms, (b) practical switch waveforms, and (c) timing           |

|      | parameters of power switch operation and gate driver waveformes                      |

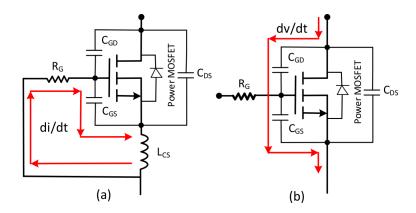

| 0.5  | (a) Source parasitic inductance and (b) parasitic capacitances of power MOSFET.      |

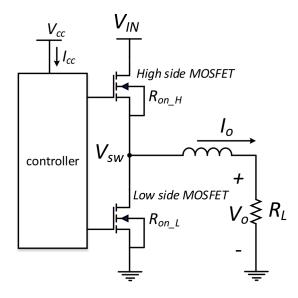

| 0.6  | Simplified power converter circuit for calculating different kinds of loss           |

| 0.7  | Provided waveform for calculating different losses                                   |

| 0.8  | Topology of the differential cascode Class-E PA with driver stages [1]               |

| 0.9  | (a) Die photo of the PA. (b) Simulated and calculated output power, drain            |

|      | efficiency (DE), and power-added efficiency (PAE) against $V_{DD}$ , PA with and     |

|      | without dynamic cascode bias (DCB) [1]                                               |

| 0.10 | Topology overview of the class-D amplifier with $f_{SW}$ regulation [2]              |

| 0.11 | (a) Measured different types of losses of designed Class-D PA, (b) Chip photo-       |

|      | graph of the class-D amplifier, the die measures $3.4mm \times 2.5mm$ [2]            |

|      | Block diagram of the proposed gate driver for GaN power switches [3]                 |

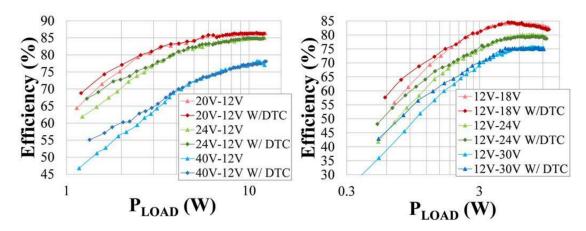

| 0.13 | Efficiency versus load power for the proposed driver in a (a) buck converter; (b)    |

|      | boost converter [3]                                                                  |

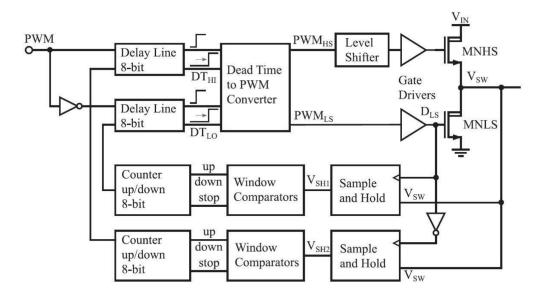

|      | Detailed overview of the proposed mixed-signal dead time control [4] 14              |

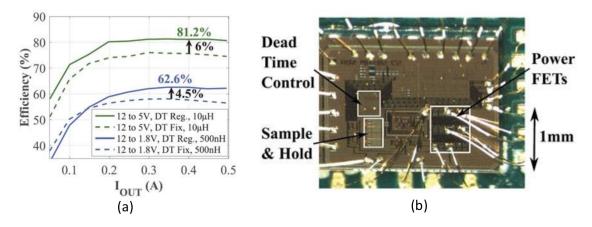

| 0.15 | (a) Measured efficiency of the synchronous buck converter for a $12V$ to $5V$        |

|      | conversion with an inductor of $10\mu H$ and conversion from $12V$ to $1.8V$ with an |

|      | inductor of $500nH$ (b) Microphotograph of the testchip, directly bonded to the      |

|      | PCB [4]                                                                              |

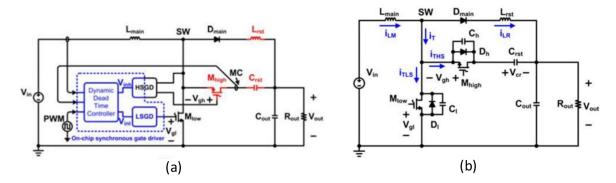

| 0.16 | Schematic of the proposed QSW-ZVS boost converter with a custom-designed             |

|      | dynamic dead-time-controlled synchronous gate driver, and (b) equivalent cir-        |

|      | cuit of the proposed boost converter [5]                                             |

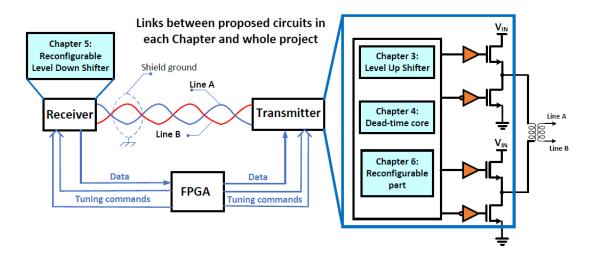

| 1.1  | Links between proposed circuits in each chapter and whole project                    |

|      |                                                                                      |

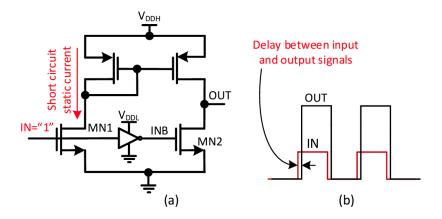

| 2.1  | Simplified level shifter circuit schematic: (a) basic structure of current source-   |

| 0.0  | based LS, (b) propagation delay between input and output signals                     |

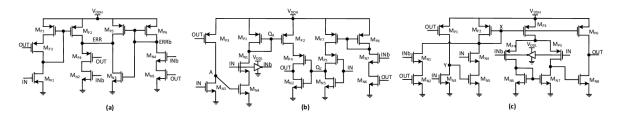

| 2.2  | Different CBLS: (a) CBLS Current source with logic error detection circuit [6],      |

|      | (b) Two stage CBLS [7], (c) CBLS with correction circuit [8]                         |

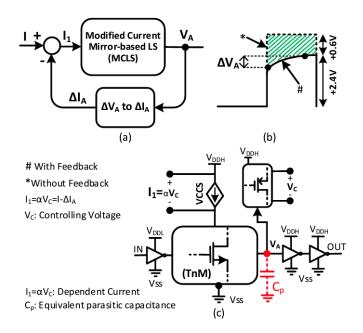

| 2.3        | General block diagram of the proposed CBLS: (a) Operation of the feedback part, (b) Potential of $V_A$ with and without feedback network, and (c) Simplified proposed LS                                                                                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

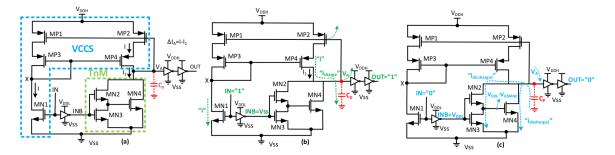

| 2.4        | Implementation and operation of the proposed LS: (a) Transistor level realiza-                                                                                                                                                                                       |

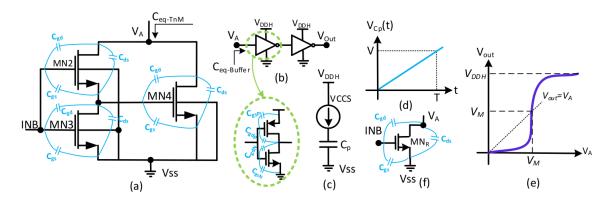

| 2.5        | tion, (b) LS operation when IN="1", and (c) LS operation when IN="0"  The circuit diagram of the TnM with all its parasitic capacitances, (b) The equivalent parasitic capacitance charged by a current source, (c) Voltage across                                   |

| 0.0        | $C_P$ , (d) Simplified circuit of output buffer, (e) Transfer function of a buffer                                                                                                                                                                                   |

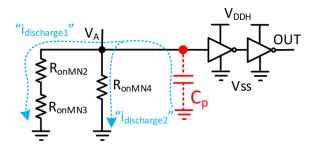

| 2.6<br>2.7 | Equivalent circuit of the presented LS circuit when IN="0"                                                                                                                                                                                                           |

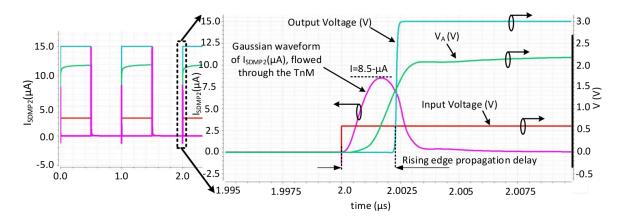

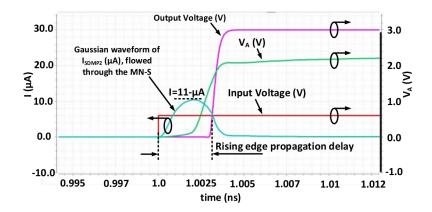

| 2.1        | through the TnM signals of the proposed LS at $1MHz$                                                                                                                                                                                                                 |

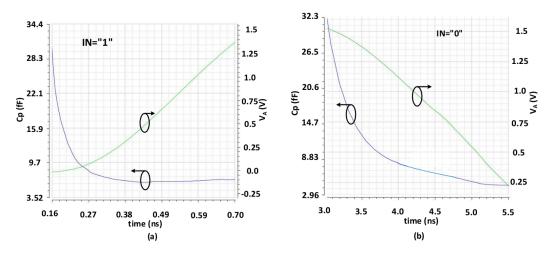

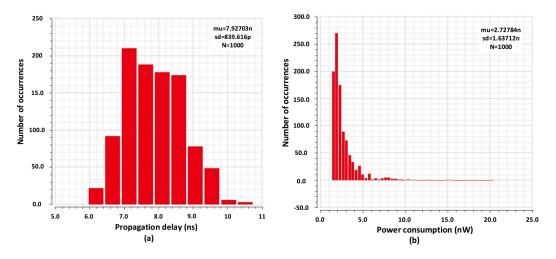

| 2.8        | Simulated $C_p$ and voltage of $V_A$ during the (a) rising (IN="1") and (b) the falling propagation delay (IN="0")                                                                                                                                                   |

| 2.9        | Enlarged view of simulated $0.6V$ input pulse, $3.0V$ pulse output, voltage $V_A$ , and current flowing through the single transistor signals of the LS at $1MHz$ .                                                                                                  |

| 2.10       | Simulated $C_p$ and voltage of $V_A$ when a single transistor is used instead of the TnM during the (a) rising (IN="1") and (b) the falling PD (IN="0")                                                                                                              |

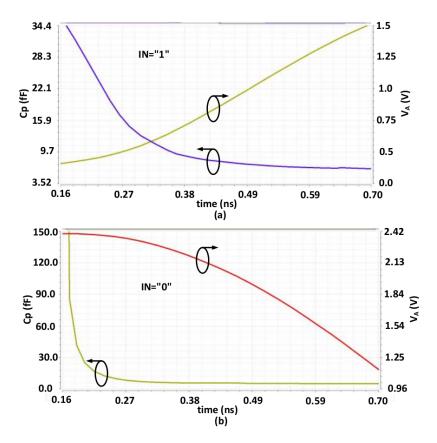

| 2.11       | Evaluation of the proposed LS operation with a Monte-Carlo simulation: (a)  Propagation delay, (b) power consumption                                                                                                                                                 |

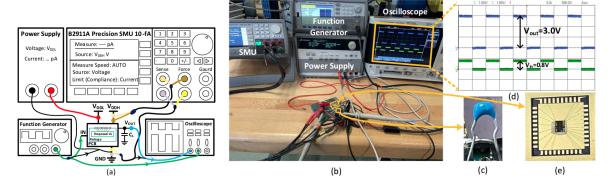

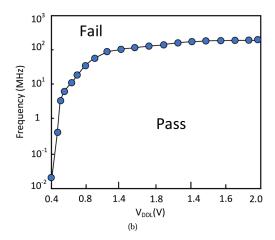

| 2.12       | Test setup, (a) Setup block diagram, (b) Fabricated chip under test, (c) $10pF$ capacitive load, (d) Input and output measured waveforms, (e) Wire-bonded die.                                                                                                       |

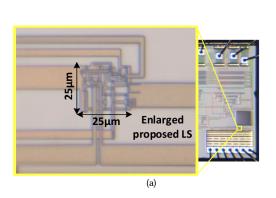

| 2.13       | Experimental performance: (a) Micrograph of the fabricated LS in CMOS AMS                                                                                                                                                                                            |

|            | $0.35\mu m$ and partially enlarged view (area: $25 \times 25\mu m^2$ ), (b) Shmoo plot for                                                                                                                                                                           |

| 2.14       | operating frequency versus $V_{DDL}$                                                                                                                                                                                                                                 |

| 2.15       | $V_{DDH}$ at $V_{DDL} = 0.8V$ and a frequency of $1kHz$                                                                                                                                                                                                              |

|            | $V_{ddL} = 0.8V$ , and $V_{ddH} = 3.0V$                                                                                                                                                                                                                              |

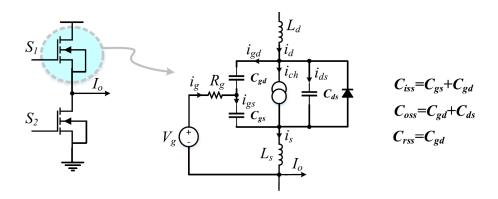

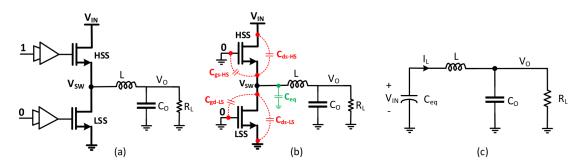

| 3.1        | Half-bridge output stage and equivalent circuit of power switch during operation.                                                                                                                                                                                    |

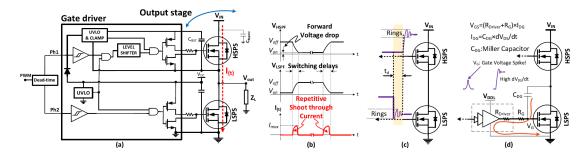

| 3.2        | Power converter and the different sources of shoot-through: (a) half-bridge circuit with simplified dead-time circuit, (b) impact of switching delays, (c) ringing effect due to the output parasitic capacitance $C_{oss}$ of HSPS, and (d) Miller capacitor effect |

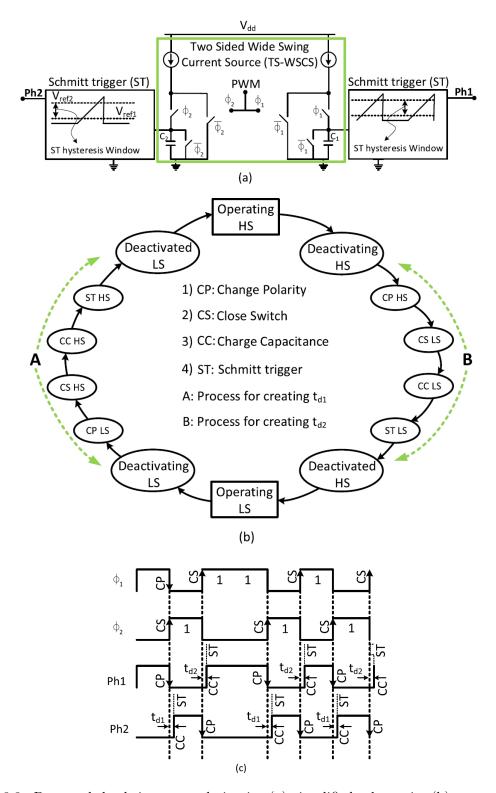

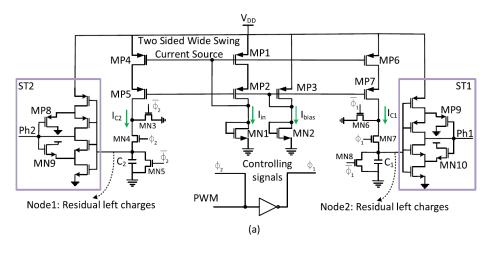

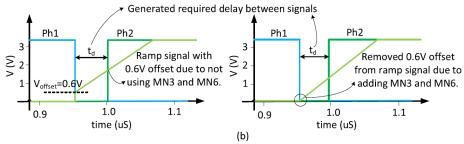

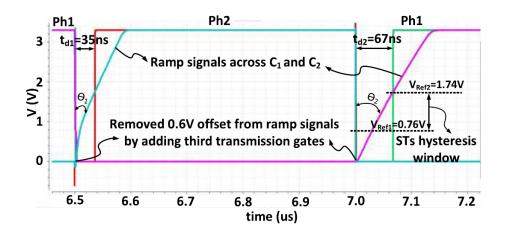

| 3.3        | Proposed dead-time control circuit: (a) simplified schematic, (b) state machine                                                                                                                                                                                      |

| 3.4        | representation, and (c) timing diagram                                                                                                                                                                                                                               |

|            | ramp signal with and without MN3 and MN6                                                                                                                                                                                                                             |

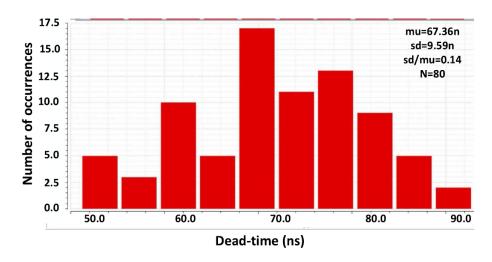

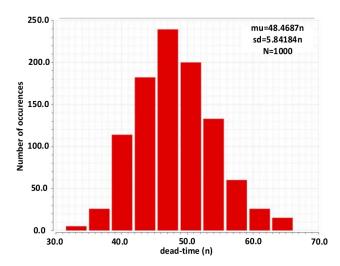

| 3.5        | Evaluation of DTCC operation with a Monte-Carlo simulation                                                                                                                                                                                                                                                       | 53       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.6        | Simulated dead time between signals                                                                                                                                                                                                                                                                              | 53       |

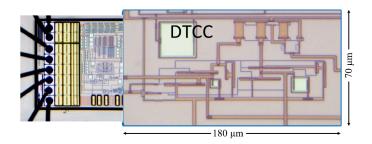

| 3.7        | Chip micrograph of fabricated DTCC in CMOS AMS $0.35\mu M$                                                                                                                                                                                                                                                       | 54       |

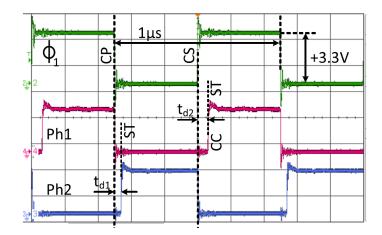

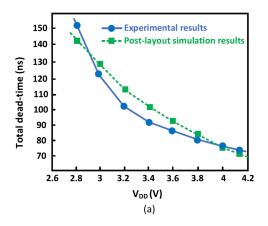

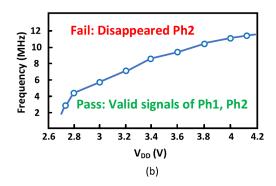

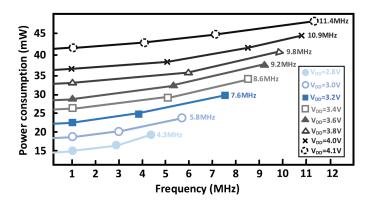

| 3.8<br>3.9 | Measured generated dead-time delays between non-overlapping signals Measured DTCC performances: (a) Comparison of the experimental and post-layout simulation results of the dead-time delays variation versus the power supply voltage $V_{DD}$ . (b) The effect of $V_{DD}$ on the maximum operating frequency | 54       |

| 3.10       | of DTCC                                                                                                                                                                                                                                                                                                          | 55       |

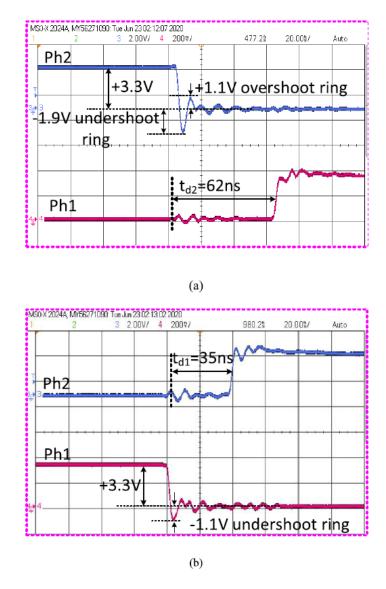

| 3.11       | converter, and the amplitude of individual ringing at the edges of each phase. Measured power consumption variation with respect to the input frequency for different values of $V_{DD}$ for $7.81pF$ estimated capacitive load in each output of $Ph1$ and $Ph2$                                                | 57<br>58 |

|            | Ph1 and Ph2                                                                                                                                                                                                                                                                                                      | 58       |

| 3.14       | dependent loss reduction                                                                                                                                                                                                                                                                                         | 59       |

| 3.15       | Packaged fabricated chip. (g) Power GaN transistor                                                                                                                                                                                                                                                               | 60       |

| 3.16       | Histogram of the calculated power losses of the test half-bridge circuit with and without the fabricated DTCC.                                                                                                                                                                                                   | 62       |

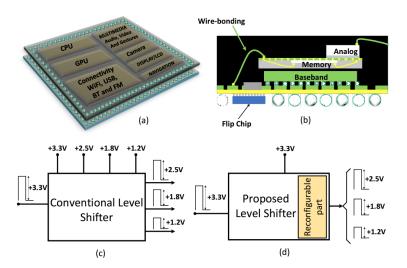

| 4.1        | Conceptual diagrams for: (a) SoC module, (b) SiP module cross section, (c) The conventional LDS, and (d) The proposed LDS                                                                                                                                                                                        | 67       |

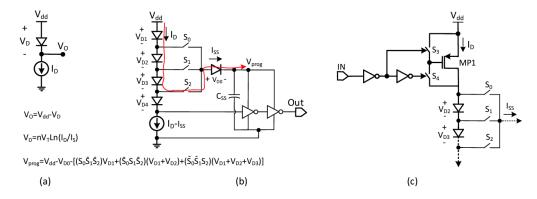

| 4.2        | The proposed RSS-LDS: (a) Main concept, (b) General explanation of system reconfigurability scheme, and (c) Realization of the controller circuit                                                                                                                                                                | 68       |

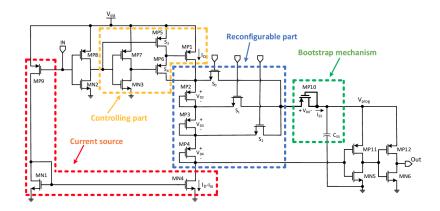

| 4.3        | Circuit diagram of the proposed RSS-LDS                                                                                                                                                                                                                                                                          | 69       |

| 4.4        | Layout view of the proposed RSS-LDS implemented in 0.35 µm CMOS process.                                                                                                                                                                                                                                         | 71       |

| 4.5        | Resulting performance of the RSS-LDS at the three configurations at $V_{dd} = 3.3V$ and operating frequency = $1MHz$                                                                                                                                                                                             | 72       |

| 5.1        | Conventional power converter (a) Simplified schematic, (b) Waveforms with GaN HEMT power switches, and (c) Waveforms with Si MOSFET power switches.                                                                                                                                                              | 76       |

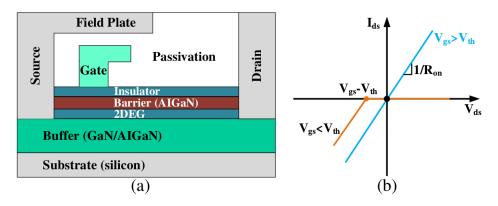

| 5.2        | GaN transistor: (a) Cross section of the lateral structure (b) simplified behavior in $1^{st}$ and $3^{rd}$ quadrant                                                                                                                                                                                             | 77       |

| 5.3        | A power converter with a tunable dead-time generator, and (b) timing diagram of gate driver in PWM mode under no load condition.                                                                                                                                                                                 | 79       |

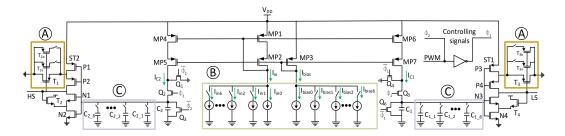

| 5.4        | parts of A, B, and C can receive tunning commands from the FPGA to recon-                                                                                                                                                                  |            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | figure the circuit for creating different required delays between the generated non-overlapping signals on the outputs of HS and LS [9]. All the components                                                                                |            |

|            | of the proposed circuit will be integrated as a part of gate driver for different                                                                                                                                                          |            |

|            | power converter applications                                                                                                                                                                                                               | 80         |

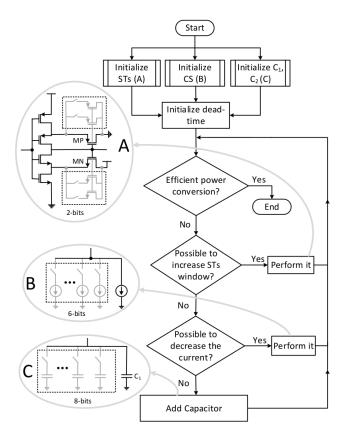

| 5.5        | Flowchart of the operation of proposed deadtime control circuit                                                                                                                                                                            | 82         |

| 5.6        | Transistor level implementation of the tunable A, B, and C parts                                                                                                                                                                           | 83         |

| 5.7<br>5.8 | Evaluation of the proposed WRM-TDC operation with Monte Carlo simulation.<br>Buck converter operation evaluation (a) Simplified circuit while the HSS is<br>turned on and the LSS is turned off (b) operation in the beginning of deadtime | 85         |

|            | with effective parasitic capacitance, and (c) equivalent circuit during deadtime                                                                                                                                                           |            |

|            | operation with the charged equivalent capacitor in the node $V_{SW}$                                                                                                                                                                       | 86         |

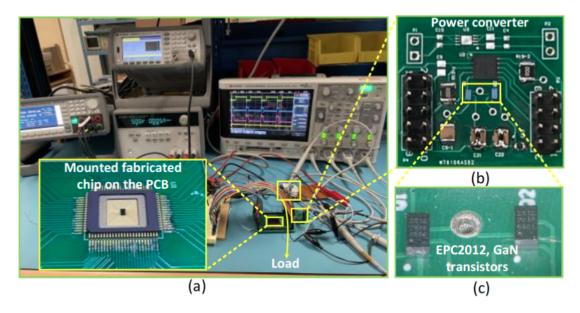

| 5.9        | Experimental setup: (a) equipment to measure the performance of fabricated                                                                                                                                                                 |            |

| 0.0        | WRM-TDC, (b) enlarged power converter, and (c) enlarged power GaN tran-                                                                                                                                                                    | 89         |

| E 10       | Sistors of EPC2012                                                                                                                                                                                                                         | 08         |

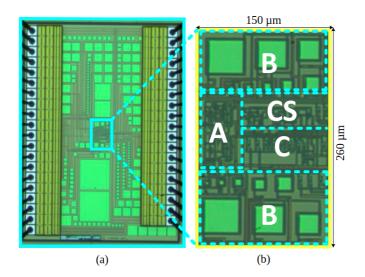

| 0.10       | Chip micrograph of the proposed WRM-TDC fabricated in $0.35\mu m$ CMOS process (a) die micrograph, (b) enlarged core including different circuit parts of A,                                                                               |            |

|            | B, C, and CS                                                                                                                                                                                                                               | 89         |

| 5.11       | Measured generated dead-times by WRM-TDC:(a) minimum produced dead-<br>time of $T_{DLH} = 9.2ns$ at $C_L = 1pF$ , $V_{dd} = 5.0V$ , and $f_s = 1MHz$ ;(b) maximum                                                                          |            |

|            | attained dead-time of $T_{DHL} = 1\mu s$ at $C_L = 5pF$ , $V_{dd} = 3.3V$ , and $f_s = 200kHz$ .                                                                                                                                           | 90         |

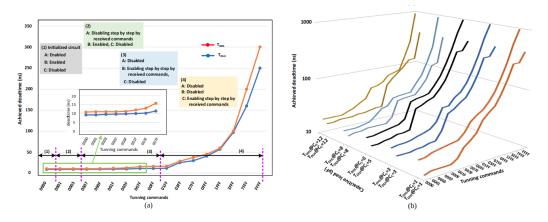

| 5.12       | Measured $T_{DLH}$ and $T_{DHL}$ from the fabricated chip in the various conditions:(a) different configurations of circuit at $V_{dd} = 5.0V$ , capacitive load $C_L = 1pF$ , and                                                         |            |

|            | $f_s = 1MHz$ ; (b) different configurations of the circuit at $V_{dd} = 3.3V$ , capacitive                                                                                                                                                 |            |

|            | between $C_L = 1pF$ to $C_L = 12pF$ , and $f_s = 400kHz$                                                                                                                                                                                   | 91         |

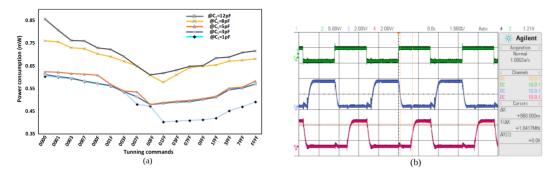

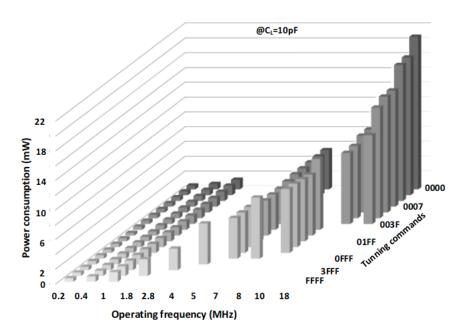

| 5 13       | a) Measured power consumption versus tuning commands at different capacitive                                                                                                                                                               | 91         |

| 0.10       | loads (b) Measured waveforms of proposed circuit at $V_{dd} = 3.3V$ , $f_s = 200khz$ ,                                                                                                                                                     |            |

|            | and capacitive load of $C_L = 10nF$ at each output of chip                                                                                                                                                                                 | 92         |

| 5.14       | Measured power consumption versus operating frequency at different tuning                                                                                                                                                                  | 02         |

| 0.11       | commands                                                                                                                                                                                                                                   | 92         |

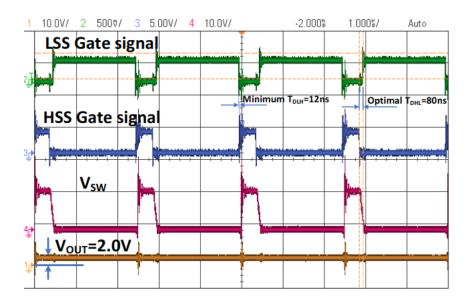

| 5.15       | Buck converter waveforms with optimal $T_{DHL}$ and minimum $T_{DLH}$ under effi-                                                                                                                                                          | ~ <u>-</u> |

| 0.10       | cient design                                                                                                                                                                                                                               | 94         |

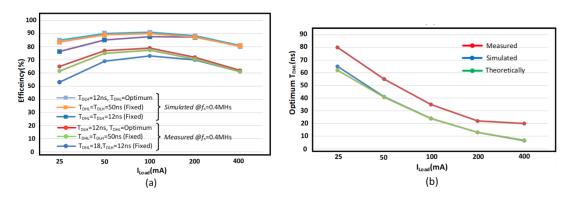

| 5.16       | Measured results(a)achieved efficiency of the implemented buck converter for                                                                                                                                                               |            |

| 0.10       | different $T_{DHL}$ and $T_{DLH}$ at $0.4MHz$ versus different $I_{load}$ , (b) comparing the                                                                                                                                              |            |

|            | measured, simulated, and calculated optimal $T_{DHL}$                                                                                                                                                                                      | 94         |

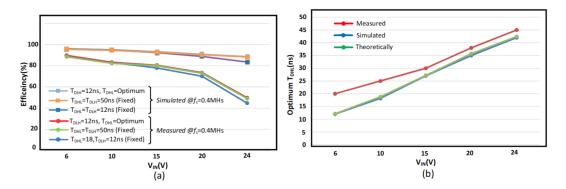

| 5.17       | Measured results(a) achieved efficiency of the implemented buck converter for                                                                                                                                                              | -          |

| -          | different $T_{DHL}$ and $T_{DLH}$ at $0.4MHz$ versus different $V_{IN}$ , (b) comparing the                                                                                                                                                |            |

|            | measured, simulated, and calculated optimal $T_{DHI}$                                                                                                                                                                                      | 95         |

To my wife, Fatemeh, my parents, Mohtaram and Malekmohammad, and all members of my family

# Remerciements

I would like to express my gratitude and appreciation to my research adviser Professor Benoit Gosselin, for his guidance, support, and motivation throughout my Ph.D. study. Thank you for giving me your trust and support for these many years. I would like to thank Professor Mohamad Sawan for his advice and great support. His active contribution and high precious time helped me during my research.

I also would like to thank the jury members whose essential participation, comments, and encouragement.

Then, I would like to express my gratitude to our group members at Biomedical Instrumentation and Microsystem Lab for their valuable comments.

Finally, I am so grateful for my wife and family for their constant love, endless patience, and spiritual supports throughout the study.

# Avant-propos

This dissertation is based on materials that are published or under review in prestigious IEEE Journals and Conferences. Chapter 2 includes papers under review for publication in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems. Chapter 3 includes previously published materials in IEEE Transactions on Circuits and Systems I: Regular Papers. Chapter 4 of this thesis includes a material previously published in IEEE International Symposium on Circuits and Systems. Chapter 5 of this thesis includes papers under review for publication in IEEE Transactions on Circuits and Systems I: Regular Papers. The text and the figures were modified to adopt the thesis template. The papers present the core of this research and include the main contributions. However, throughout this dissertation, several conferences and journals have been published in IEEE. I elaborate my contributions to the one conference paper in Chapter 4, and three transactions are reflected in Chapters 2, 3, and 5.

Paper 1: M. Karimi, M. Ali, A. Hassan, M. Sawan, and B. Gosselin, "A 7.6-ns Delay Subthreshold Level-Shifter Leveraging Parasitic Capacitance Data-dependent Current Source," in IEEE Transactions on VLSI Systems, Submitted. This paper presents a novel high-performance level-up shifter, which is convenient for the high side of gate drivers for implementing a power converter. The custom integrated circuit is tested, and the circuit is fully characterized. I personally propose this novel level shifter under the supervision of Prof. B. Gosselin. The measurement and experimental results were obtained at the Smart Biomedical Microsystem Lab. at Laval University under the supervision of Prof. B. Gosselin and the Polystim Neurotechnology Laboratory, Polytechnique Montreal, under the supervision of Prof. Mohamad Sawan. In this work, the measured results verify a shorter propagation delay and lower power consumption than similar works. Prof. Benoit Gosselin, Dr. M. Ali, Dr. A. Hassan, and Prof. Mohamad Sawan extensively revised the paper's content by adding materials and corrections.

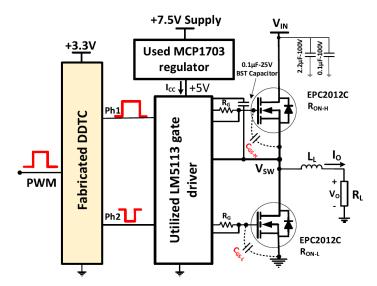

Paper 2: M. Karimi, M. Ali, A. Hassan, M. Sawan, and B. Gosselin, "An Active Dead-Time Control Circuit with Timing Elements for a 45-V Input 1-MHz Half-Bridge Converter," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 1, pp. 30–41, Jan. 2022. This paper presents a new non-overlapping signal generator to provide appropriate signals for the low- and high-sides of a half bridge. The fabricated chip was validated with an implemented half bridge with off-the-shelf components. I proposed the main idea of the paper

under the supervision of Prof. B. Gosselin. The measurement and experimental results were obtained at Smart Biomedical Microsystem Lab. at Laval University under the supervision of Prof. B. Gosselin. In this work, the reduction of half bridge total loss was proven experimentally through a comparison with a half bridge operation without the fabricated chip. Prof. Benoit Gosselin, Dr. M. Ali, Dr. A. Hassan, and Prof. Mohamad Sawan extensively revised the paper's content by adding materials and corrections.

Paper 3: M. Karimi, M. Ali, A. Hassan, M. Sawan, and B. Gosselin, "A Reconfigurable Single-Supply Multiple-Level Down-Shifter for System-on-Chip Applications," 2021 IEEE International Symposium on Circuits and Systems (ISCAS), 2021, pp. 1–5. In this paper, a tunable multi-level down shifter is presented, where only a single supply is required. This novel circuit is utilized as interface between the high-voltage side (data bus network) and the low-voltage side (processors with different supplies). I proposed the main idea of this work under the supervision of Prof. Benoit Gosselin. I prepared the manuscript, and Prof. Benoit Gosselin, Dr. M. Ali, Dr. A. Hassan, and Prof. Mohamad Sawan revised the paper's content by adding materials and corrections.

Paper 4: M. Karimi, M. Ali, A. Aghajani, A. Hassan, M. Sawan, and B. Gosselin, "A 9.2-ns to 1-us Digitally Controlled Multi-Tuned Deadtime Optimization for Efficient GaN HEMT Power Converters" in IEEE Transactions on Circuits and Systems I: Regular Papers, submitted (Invited paper - special issue NEWCAS 2021). In this paper, a multi-tuned deadtime optimization is presented. The fabricated chip is connected to a gate driver that drives two superimposed GaN HEMT power switches. The reconfigurable part of the fabricated chip is controlled digitally to provide asymmetric deadtimes for a buck converter with variable input voltage  $V_{IN}$  and output current  $I_{OUT}$ . The deadtimes are generated based on an accurate derived equation. I proposed the main idea of the paper under the supervision of Prof. Benoit Gosselin. The measurement and experimental results were obtained at Smart Biomedical Microsystem Lab. at Laval University under the supervision of Prof. B. Gosselin. The measured results show the priority of our presented buck converter over recent published works. Prof. Benoit Gosselin, Dr. M. Ali, Dr. A. Hassan, and Prof. Mohamad Sawan extensively revised the paper's content by adding materials and corrections. Amir Aghajani contributed to the derivation of the mathematical equations and the achievement of the experimental results.

### Introduction

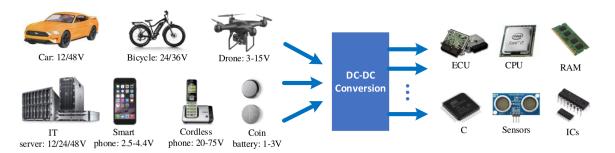

Power converters are the key elements of the growing field of power management units that provide different supply voltage and current values to various electronic blocks from various energy sources [10]. Batteries as an energy source example are used in most electronic devices, including laptops, cell phones, and cameras, to power up their internal blocks, such as processors, displays, and analog circuitry, which require different voltages [11]. Figure 0.1 shows various energy sources in different applications where DC-DC conversion is required to provide appropriate power supplies to their internal blocks, such as processors, sensors, and electronic control units [12]. Some blocks require a higher voltage than the battery voltage, and some require a lower voltage than that of the battery. The battery voltage may be 1.5V, with the digital and analog blocks requiring 1- and 3-V supplies, respectively. Therefore, DC-DC power converters are essential for providing lower or higher voltages than that of the battery. The converter used to provide a lower voltage than that of the battery is known as a buck converter, while that which provides a higher voltage than that of the battery is called a boost converter [13; 14]. Implantable biomedical devices, such as optical stimulators, are usually supplied by a small coin battery with a low output voltage, ranging from 1V to 1.5V, while the required voltage and current for optogenetic stimulation are approximately 4V and 20mA, respectively. Therefore, a DC-DC boost converter must be employed to meet the requirement [15]. Headphone amplifiers are generally expected to have very low noise levels and high linearity for good audio quality, naturally implying high power consumption. In mobile applications, a trade-off must be made between audio quality and battery life due to limited battery capacity. In these applications, high-efficiency Class D amplifiers are essential to decrease the total loss and consequently address the requirement of providing longer battery lifetime and increase the quality of audio [16].

In wireless power transmission applications, two inductive coils must be mutually coupled for wireless power transfer. The primary coil must be in the transmitter output, and the secondary coil must be in the receiver input. The coil is the output component in the topology of Class E power amplifiers, satisfying the easy coupling requirement with the secondary coil in the receiver side. In addition, the efficiency of Class E power amplifiers makes them suitable for wireless power transmission applications [17]. In sensor interface applications, two sides of low and high powers require an interface to communicate. The suitable interfaces in these

Figure 0.1: Different energy sources, DC-DC conversion, and IC level voltages.

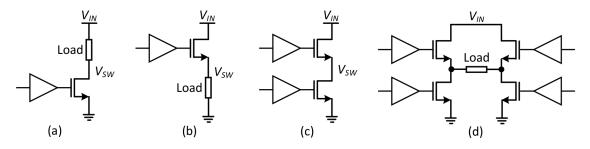

Figure 0.2: Different power switch configurations, (a) Low-Side, (b) High-Side, (c) Half-Bridge, (d) Full-Bridge (H-Bridge).

applications are half and full bridges. The sensor interface is used in automotive applications. In this application, the low voltage side is a processor, and the high voltage side is a network. The equivalent circuit of the network is a R-L load. A half/full bridge would play the role of an interface for receiving the low voltage signal and driving the high voltage side appropriately [18]. The buck-boost configuration is presented to provide a DC voltage that is lower or higher than that of the battery with an opposite polarity (e.g., providing -2V from the 1.5-V battery), and the non-inverting flyback converter in which a single circuit provides both higher and lower voltages than the battery's voltage with the same polarity (e.g., providing either 2 or 1V from a 1.5-V battery) [19].

### Various Topologies of Power Converters

Various topologies of power converters are adopted for different applications and purposes. Power converters consist of gate drivers and power switches. Figure 0.2 presents different configurations of power switches. The power transistors can be on-chip (integrated) or discrete (external). To implement integrated power switches for carrying high current, the width (W) of the power switch must be sufficiently large to have a low  $R_{DS(on)}$ . However, the gate capacitance will be increased when the W increases. Especially for fast switching, the power converter experiences losses. Therefore, a trade-off must be achieved between the  $R_{DS(on)}$  and

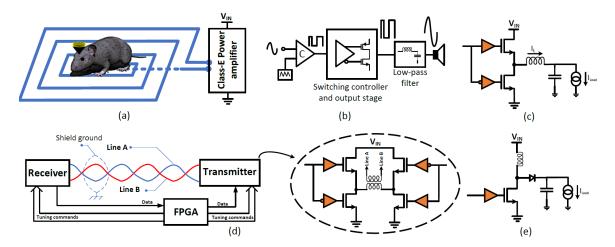

Figure 0.3: General block diagram of different power converters in various applications, (a) Class-E power amplifier for wireless power transmission for freely moving animals, (b) Class-D power amplifier for speaker, (c) Buck converter configuration, (d) Full-Bridge (H-Bridge) for data bus network, (e) Boost converter configuration.

$C_{Gate}$  of the power switch. In high-power and -voltage applications, n-type transistors are preferred due to their low on-resistance  $R_{DS(on)}$ , but the gate supply should be greater than  $V_{IN}$  for high-side n-type power switches for appropriate operation. To elaborate, holes are charge carriers with approximately 2 to 3 times lower mobility than electrons, and to obtain the same On-Resistance  $R_{DS(on)}$ , the p-type W must be 2 to 3 times larger than that of the n-type, resulting in 2 to 3 times more charge gathering in the transistor gate. Consequently, p-type MOSFETs will have a low thermal resistance and a high current rating, which will affect the dynamic performance. Therefore, a convenient power MOSFET must be selected by considering the appropriate  $R_{DS(on)}$  and gate charge. Actually, depending on the switching frequency in different applications, the device on-resistance  $R_{DS(on)}$  and the gate charge  $Q_g$  are considered in MOSFET selection [20].

$$Q_g = \int_{t_0}^{t_s} \frac{V_{DR}}{R_G} e^{-\frac{t}{R_G C_{eff}}} dt \tag{1}$$

Equation 1 shows the gate charge, where  $V_{DR}$  is the peak value of the gate drive voltage, and Ceff is the effective gate input capacitance.  $R_{ds(on)}$  is obtained by  $R_{ON} = R_{silicon} + R_{wire} + R_{lead}$ , where  $R_{silicon} =$  inherent resistance from silicon process,  $R_{wire} =$  bond wire resistance, and  $R_{lead} =$  resistance of the lead frame. Texas Instrument released a detailed application report on June 2016 to explain the importance of  $R_{ds(on)}$  [20].

In Parts (a) and (b) of Figure 0.2, the power switch is used in the low and high sides of the converter, respectively. Figure 0.2.c shows the half-bridge configuration, and Figure 0.2.d presents the full-bridge (H-bridge) configuration, which consists of two half-bridges. Fig. 3

presents the general block diagram of different power converters in some applications. Figure 0.3.a shows a wireless power transmission (WPT) system that is used for freely moving animals. For the part of the system that is implanted in the head-stage of the animal for brain stimulation study, the WPT system must continuously transfer power wirelessly. For WPT implementation, a printed spiral coil would be used to propagate the magnetic flux for the receiver coil inside the head-stage. A Class E power amplifier with a specific gate driver is utilized to perform the functionality appropriately and deliver the power to a given distance [21]. Figure 0.3.b presents the general block diagram of a Class D power amplifier, which is mostly applicable for headphones and speakers. In this design, the weak sinewave of the input signal is compared with a sawtooth waveform, and the results are applied to the switching controller and output stage (SCOS) block. In the SCOS part, a particular gate driver is designed to generate a high-amplitude pulse for the low pass filter. Finally, the extracted high-amplitude sinewave signal is applied to the speaker [22]. Figure 0.3.c shows the general block diagram of a buck converter. In the last stage of this topology, two power switches are used. Afterward, a LC low pass filter is used. Recall that the current through an inductor is an integral of its applied voltage with a proportionality constant of 1/L. This will create a triangular waveform for  $i_L(t)$ . The average of this current,  $i_{L(avg)}$ , is delivered to the load because the capacitor is an open circuit for this DC current. In the configuration in Figure 0.3.c, the gate driver is required for power switches to handle the switches when they are working under high power operation. Figure 0.3.d shows the application of power converters in data bus networks. In the Figure 0.3.d, the enlarged view of transmitter  $T_X$  is presented. As shown, a full bridge would be used to drive the network appropriately. The equivalent circuit of the network is a R-L load, which depends on the length of lines A and B, and the resistance and inductance values are different, consequently requiring various power switches to drive the line conveniently. A level down shifter can be adopted for the receiver  $R_X$  to receive the high amplitude pulse signal from the line and convert down the amplitude to be compatible with the controller in the low power side. In this application,  $T_x$  and  $R_x$  connect to the network through a digital isolating transformer. Figure 0.3.e presents the simplified schematic of a boost converter. In this topology, the combination of a power switch, a diode, an inductor, and a capacitor can create a DC voltage that is higher than the input voltage. The operation of this converter relies on the fact that in one phase, the inductor current reaches its maximum level and will be released to the capacitor from the beginning of the second phase. The power switch used in this converter needs a gate driver to function properly [13; 14].

#### Gate Driver Requirements

In power converters with a single power switch, gate drivers are used to reduce the switching loss by quickly charging the parasitic capacitance. In a converter with two superimposed power switches, gate drivers are responsible for receiving a pulse signal from the controller

Table 0.1: Ideal switch characteristics.

|          | $I_F$           | $R_{ON}$   | $V_{ON}$ | $V_{BR}$ | $I_{OFF}$ | $R_{OFF}$ | $P_G$ | $V_G$ | $I_G$ |

|----------|-----------------|------------|----------|----------|-----------|-----------|-------|-------|-------|

| On-State | High (infinity) | Low (zero) | Low      | -        | _         | _         | Low   | Low   | Low   |

|          | _               | _          |          |          |           | High      |       |       |       |

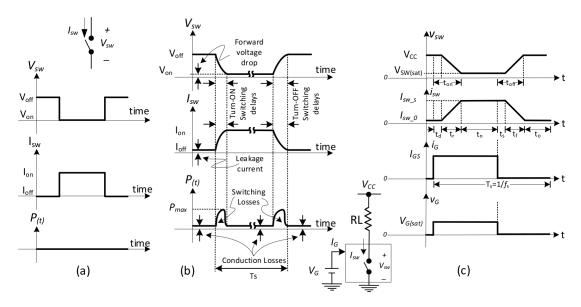

Figure 0.4: (a) Ideal switch waveforms, (b) practical switch waveforms, and (c) timing parameters of power switch operation and gate driver waveformes.

and providing two appropriate driving signals for the low and high sides. Furthermore, a gate driver is required to protect the power switches for secure operation for converters. In addition, in converters with various input voltages  $V_{IN}$  and output loads  $I_{Load}$ , a reconfigurable gate driver is required to tune the internal circuit of the gate driver to implement a high-performance power converter at different  $V_{IN}$  and  $I_{Load}$  values.

To deepen the understanding of the gate driver requirement for power switches in a power converter, the characteristics and specifications of switches must be investigated. The common motivation among different switching devices, which are designed for specific applications, is to obtain the characteristics of a "super device." The characteristic of an ideal super device is a suitable reference for designing a real device. Table 0.1 summarizes the characteristics of an ideal switch where  $I_F$ ,  $R_{ON}$ ,  $V_{ON}$ ,  $V_{BR}$ ,  $I_{OFF}$ , and  $R_{OFF}$  are the forward current, the on-state resistor, the forward voltage drop, the forward or reverse voltage, the leakage current, and the off-state resistor, respectively. Notably, a low  $R_{ON}$  causes a low on-state loss  $P_{ON}$ , and a similar phenomenon occurs for  $R_{OFF}$  and  $P_{OFF}$ . The voltage and current of an ideal power switch during operation and the corresponding power loss are illustrated in Figure 0.4.a.  $P_G$ ,  $V_G$ , and  $I_G$  are the power, voltage, and current of the gate driver, as shown in Figure 0.4.c [20].

Table 0.2: Internal capacitances for a power MOSFET.

|                                                                            | Internal Capacitances                                                   | Values                                               | Conditions                                                                                 |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------|

| $C_{iss} = C_{gs} + C_{gd}$ $C_{oss} = C_{gd} + C_{ds}$ $C_{rss} = C_{gd}$ | Input Capacitance<br>Output Capacitance<br>Reverse Transfer Capacitance | $\begin{array}{c} 1350pF \\ 58pF \\ 3pF \end{array}$ | drain and source terminal shorted<br>gate and source shorted<br>source connected to ground |

For proper operation in high frequencies, the device must be completely turned on and off instantaneously during the turn-on and -off process. Thus, it must have low  $t_d$ ,  $t_r$ ,  $t_s$ , and  $t_f$  which are the delay, rise, storage, and fall times, respectively (Figure 0.4.c). The other parameters of power switching devices are dv/dt and di/dt, which characterize the rapid changes in the voltage across and the rapid increase of the current through the devices. Finally,  $R_{0JA}$  as thermal impedance from the internal junction to the ambient must be low to transmit heat easily to the ambient. The characteristic of a practical switch is shown in Figure 0.4.b with typical waveforms. In this figure, as device current  $I_{SW}$  rises during turn-on, the voltage across the device  $V_{SW}$  falls. The other important parameters shown in Figure 0.4.b are the turn-on time  $t_{on}$  (the sum of the delay and rise times) and turn-off time  $t_{off}$  (the sum of the storage and fall times) of the switching device [20].

A practical switching device requires finite delay time  $t_d$ , rise time  $t_r$ , storage time  $t_s$ , and fall time  $t_f$ . In Figure 0.4.b, the corresponding power losses of the power device are illustrated.

Unlike the ideal switch, which has no losses, practical switches suffer from conducting and switching losses, which are shown in Figure 0.4.b. The switching parameters as inconvenient effects are the objectives of any new device, which should exhibit improvement. For example, the dropped voltage across a conducting power device is usually in the order of 1V or higher in some cases up to several volts.  $P_{ON}$  as the average conduction power loss is equal to  $f_s(\int_0^{t_{on}} pdt)$  where  $f_s$  is the conduction frequency, and "P" is the instantaneous power loss (product of  $V_{sw}$  and  $I_{sw}$ ). is the instantaneous power loss (product of Vsw and Isw).

During the transition from one conduction state to another, the current and the voltage have substantial values. Thus, the power losses increase during the switching and can be calculated as  $P_{sw} = f_s(\int_0^{t_r} p dt + \int_0^{t_s} p dt + \int_0^f p dt)$ , where  $f_s$  is the switching frequency, and  $t_r$ ,  $t_s$ , and  $t_f$  are the rise, storage, and fall times, respectively. Therefore, the power dissipation of a switching device is expressed as  $P_D = P_{ON} + P_{SW} + P_G$ , where  $P_G$  is the gate driver power consumption [20].

Power MOSFETs, which are practical power switches, are used for power converter implementation. When a significant power level must be handled, a power MOSFET as a particular type of transistor must be designed. The main advantages of a power MOSFET over other power components include high switching speed and good efficiency at low voltages. The inherent specifications of power MOSFETs constrain the exchange speed. The limitation is caused by

Figure 0.5: (a) Source parasitic inductance and (b) parasitic capacitances of power MOSFET.

the internal capacitances of the MOSFETs. When the transistor switches, these capacitances must be charged or discharged. Given that the current flow through the mentioned capacitances is restricted by the outer gate driver, charging and discharging can be a slow process. The gate driver will really force the transistor's switching speed [23]. Table 0.2 summarizes the internal capacitances of C3M0075120K as a power MOSFETs to serve as evidence over internal capacitances [24]. These capacitances are shown in Figure 0.3. The comparison in Table 0.2 indicates that the largest capacitance is Cgs, that for a specific power transistor the value of 1347pF is reported.

In addition to internal capacitance, parasitic inductance can be along with each the MOSFETs pins. Parasitic inductance has adverse effects, which are summarized as follows:

The parasitic inductance in any given circuit is actually caused by current gradients. Thus, among the three pins of power MOSFETs, the gate parasitic inductance would be the smallest. However, because of the large input internal capacitance in the gate, a resonance circuit might be created between these two undesirable internal components. Oscillation would occur and lead to the devastation of the power MOSFETs. In very high switching, the internal inductance must always be low enough to avoid this phenomenon [25]. The most effective parasitic inductance is in the source because this inductance creates feedback in the source and tends to consume increased switching time, thereby boosting switching losses. Figure 0.4 shows the source parasitic inductance and its equivalent feedback. These voltages and current fluctuations in Figures 0.3 and 0.4 that are respectively caused by the parasitic capacitances and inductances unintentionally turn on power MOSFETs when they are expected to be turned off. That is, dv/dt and di/dt would charge the  $C_{gs}$ , and the transient response of main switching causes the VGSV<sub>GS</sub> to be higher than the  $V_{th}$ . Eventually, the power MOSFETs would be turned on accidentally [26].

Figure 0.6: Simplified power converter circuit for calculating different kinds of loss.

Figure 0.7: Provided waveform for calculating different losses.

#### Converter's Different Losses

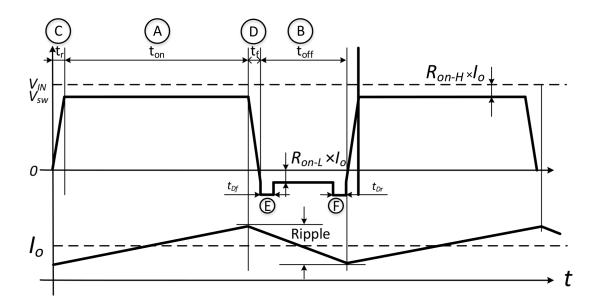

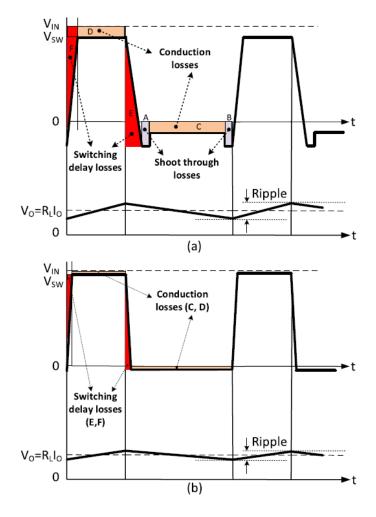

Designing efficient converters requires minimizing losses through appropriate design practices and circuit techniques. Figures 0.6 and 0.7 are provided for calculating the different kinds of losses of a given power converter. The losses in a power converter include conduction, switching (commutation), dead-time, gate charge, and IC operating losses [27].

Important parameters are tagged in waveform in Figure 0.6 as requirements for calculating different losses and summarized as follows:

#### **Conduction Loss**

This loss is calculated in sections of "A" and "B" of the Figure 0.7 waveform. The important parameters of this loss are the on-resistances of the high/low sides (H/L Sides) of the MOSFET [28]. The following equation is employed to calculate this type of loss:

$$P_{ON-H} = I_O^2 \times R_{On-H} \times \frac{V_O}{V_{IN}}$$

$$P_{ON-L} = I_O^2 \times R_{On-L} \times \left(1 - \frac{V_O}{V_{IN}}\right)$$

(2)

where  $V_{IN}$ ,  $V_O$ ,  $I_O$ ,  $R_{On-H}$ , and  $R_{On-L}$  are the respective input voltage, output voltage, and high and low sides of the power MOSFET on-resistance, which are tagged in Figures 0.6 and 0.7. For the calculation of the H/L on-resistances, the drop voltages ( $V_{drop} = R_{on-H} \times I_O$ ) in the waveform of Figure 0.4 are measurable. Then, the on-resistances can be calculated as  $V_{drop}/I_O$ .

#### Switching loss

This loss is calculated in Sections "C" and "D" of the waveform, and the required parameters for calculation are the rise  $t_r$  and fall  $t_f$  times.

$$P_{SW-H/L} = \frac{1}{2} \times V_{IN} \times I_O \times (t_r + t_f) \times f_{SW}$$

(3)

where  $f_{SW}$ ,  $t_r$ ,  $t_f$  are the switching frequency, the high-/low-side MOSFET turn-on rise time, and the high-/low-side MOSFET turn-off fall time, respectively, and  $V_{IN}$  and  $I_O$  are tagged in Figure 0.6.

#### Dead Time Loss

This loss is calculated in Sections "E" and "F" of the waveform, and the required parameters for calculation are the body-diode forward voltage and the dead times in rising  $t_{Df}$  and falling  $t_{Dr}$ . Although this loss is not great in this well-designed half bridge, it is the cause of shoot through and will burn the power MOSFETs in the half bridge because a short circuit is occurring between  $V_{IN}$  and GND in this short time  $(t_{Dr}, t_{Df})$  (Figure 0.6). In this design, the amount of current through power MOSFETs is approximately 60mA, while in high voltage application, this current would be around some decades of Amperes. Therefore, the proposed dead time circuit is practical and useful for high voltage application in protecting expensive power MOSFETs and guaranteeing the functionality of converters.

$$P_D = \frac{1}{2} \times V_D \times I_O \times (t_{Dr} + t_{Df}) \times f_{SW}$$

(4)

where  $V_D$ ,  $t_{Dr}$ , and  $t_{Df}$  are the low-side MOSFET body-diode forward voltage parameters, which are tagged in Figures 0.6 and 0.7.

#### Gate Charge Loss

This loss is due to the left charge in the gate during the switching in which the important parameters are  $C_{g-H}$  and  $C_{g-L}$  (high- and low-side power MOSFET gate capacitances).

$$P_G = (Q_{g-H} + Q_{g-L}) \times V_{gs} \times f_{SW}$$

$$P_G = (C_{g-H} + C_{g-L}) \times V_{gs}^2 \times f_{SW}$$

(5)

where  $Q_{g-H}$ ,  $Q_{g-L}$ ,  $C_{g-H}+C_{g-L}$ ,  $V_{gs}$ ,  $f_{SW}$  are the high-side MOSFET gate electric charge [C], the low-side MOSFET gate electric charge [C], the high-side MOSFET gate capacity [F], the low-side MOSFET gate capacity [F], the gate drive voltage [V], and the switching frequency [HZ].

#### IC Operating Loss

This loss is due to the IC consumption current, which is denoted as  $I_{CC}$  in Figure 0.6.

$$P_{IC} = V_{CC} \times I_{CC} \tag{6}$$

where  $V_{IN}$  and  $I_{CC}$  are the input voltage and the IC consumption current tagged in Figure 0.6.

### Various Topologies of Gate Driver for Different Power Converters

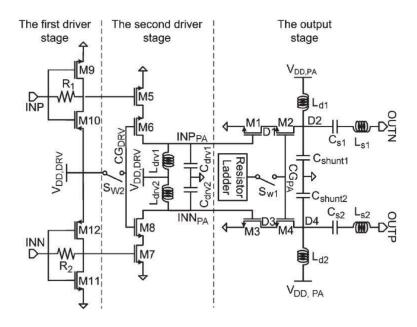

In [1], an integrated Class E power amplifier (PA) is presented, and the operating frequency is 2.45GHz. This PA is implemented in a  $0.18\mu m$  CMOS process. Figure 0.8 shows the topology of this differential cascode Class-E PA with driver stages. In this design, the inductors are designed on-chip.

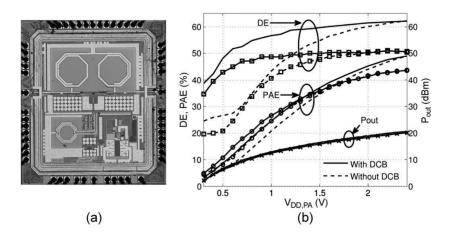

The measured efficiency of the presented differential PA is as high as 43.6%. Figure 0.9.a shows the die micrograph of the PA, while Figure 0.9.b presents the simulated and calculated output powers, the drain efficiency, and the power-added efficiency against  $V_{DD,PA}$  with and without a dynamic cascode bias (DCB). The circuit includes one output and two driver stages, where the output supply and the driver stages are different. In Figure 0.8, the  $L_{d1}$  and  $L_{d2}$  are on-chip inductors whose quality factor (Q) at 2.45GHz is 13. In this design,  $L_{s1}$  and  $L_{s2}$

Figure 0.8: Topology of the differential cascode Class-E PA with driver stages [1].

Figure 0.9: (a) Die photo of the PA. (b) Simulated and calculated output power, drain efficiency (DE), and power-added efficiency (PAE) against  $V_{DD}$ , PA with and without dynamic cascode bias (DCB) [1].

are implemented partly with bond-wire and off-chip inductances. To implement the driver of this Class E PA, the first stage is realized by two inverters with resistive feedback. The second driver stage is implemented by leveraging a LC tank-loaded cascode amplifier to minimize power consumption and allow a sufficient high supply voltage, which is 2.0 V, to drive the Class E stage.

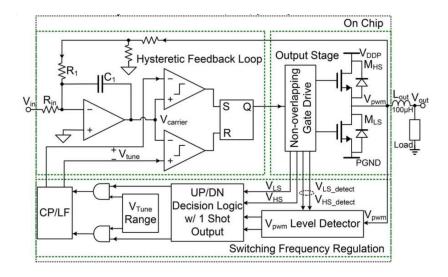

A Class D PA is presented in [2], and its topology is shown in Figure 0.10. In this design, the PA adaptively regulates its switching frequency to achieve optimal power efficiency across the

Figure 0.10: Topology overview of the class-D amplifier with  $f_{SW}$  regulation [2].

Figure 0.11: (a) Measured different types of losses of designed Class-D PA, (b) Chip photograph of the class-D amplifier, the die measures  $3.4mm \times 2.5mm$  [2].

full output power range. The PA is implemented in a  $0.14 - \mu m$  SOI BCD process. The PA achieves 93% efficiency at a 45W output power and > 80% power efficiency down to 4.5W. In this design, all types of loss are calculated based on the measured parameters, while the power output stage works with 80V  $(V_{DDP})$ . The gate driver is supplied by an on-chip 3.3V regulator  $V_{DD}$ . The gate drivers include a two-step level shifter, which can handle a supply bounce higher than the internal supply.

As shown in Figure 0.10, the proposed Class-D PA design includes a non-overlapping gate driver, which is controlled by peripheral circuits of switching frequency regulation and hysteretic feedback loop sections. Figure 0.11.a shows the different power losses versus the switch-

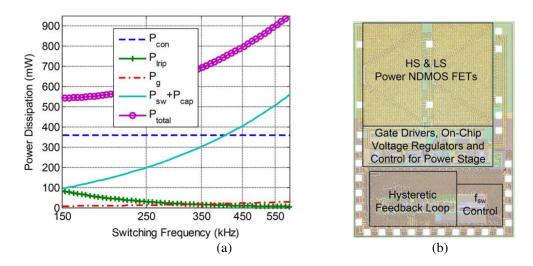

Figure 0.12: Block diagram of the proposed gate driver for GaN power switches [3].

Figure 0.13: Efficiency versus load power for the proposed driver in a (a) buck converter; (b) boost converter [3].