### BENJAMIN SEMAL

## Microarchitectural Covert Channels in Multitenant Computing Environments

Thesis submitted for the degree of Doctor of Philosophy to the ROYAL HOLLOWAY UNIVERSITY OF LONDON

## Declaration of Authorship

This doctoral study was conducted under the supervision of Professor Konstantinos Markantonakis.

The work presented in this thesis is the result of original research carried out by myself whilst enrolled in the Information Security Group as a candidate for the degree of Doctor of Philosophy. This work has not been submitted for any other degree or award in any other university or educational establishment.

| Signature |  |  |  |

|-----------|--|--|--|

|           |  |  |  |

| Date      |  |  |  |

## Abstract

The elastic property of cloud services relies on a dynamic mapping between distinct virtual terminals and shared physical nodes, laying bare correlations between the activity of concurrent tenants and the availability of microarchitectural resource. In this context, this thesis studies the threat posed by microarchitectural covert channels to data confidentiality in multi-tenant computing environments. An empirical study is conducted on the practicality of theses attacks against public Infrastructure-as-a-Service instances, revealing that covert channels achieve a medium severity score with the Common Vulnerability Scoring System. A new evaluation framework is then developed so as to devise metrics for fair comparison and identify conditions for eluding logical isolation on contemporary computing environments. As a result, two new microarchitectural covert channels based on Intel's integrated memory controllers are presented, which enable circumventing existing defense strategies. The first attack allows a privileged adversary to leak information between two processes within a single native environment. The second attack is an extension to cross-VM scenarios for unprivileged adversaries. An exhaustive study on state-of-the-art countermeasures is then realised, revealing a lack of perspective in their design approach. The analysis leads to a new covert channel based on Intel and AMD memory bus implementations. The resulting attack is tested across two AWS EC2 instances, demonstrating that an malicious individual can easily make his way around all existing countermeasures proposed in academia.

## Acknowledgements

I would like to acknowledge and thank the many people who have helped me bringing this thesis to completion.

My initial and foremost thanks goes to Maria for her unwavering confidence in my ability to undertake the PhD. My gratitude also goes to my family for their support and many advice throughout the past three years (and before), and to my newly found family for their trust and caring.

My very special thanks to Raja and Carlton for the invaluable help, guidance, and moral support all along the PhD. I would also like to express my gratitude to my supervisors, Konstantinos, Peter, and Keith, as well as other members of the laboratory, Darren, and Nicola. Many thanks to Jan for his valuable reviews and sense of humour. Finally, I would like to extend my appreciation to Royal Holloway and its members, and to everyone who took part in this work, directly or indirectly.

The PhD is indeed a marathon, and it would not have been possible without your help. Thank you all.

## List of Publications

#### Publications directly related to this thesis.

Benjamin Semal, Konstantinos Markantonakis, Raja Naeem Akram, and Jan Kalbantner. Leaky controller: cross-VM memory controller covert channel on multi-core systems. *IFIP International Conference on ICT Systems Security and Privacy Protection*, pages 3-16. Springer, 2020.

Benjamin Semal, Konstantinos Markantonakis, Raja Naeem Akram, and Jan Kalbantner. A study on microarchitectural covert channel vulnerabilities in Infrastructure-as-a-Service. *International Conference on Applied Cryptography and Network Security*, pages 360-377. Springer, 2020.

Benjamin Semal, Konstantinos Markantonakis, Keith Mayes, and Jan Kalbantner. One covert channel to rule them all: a practical approach to data exfiltration in the cloud. 2020 IEEE 19th International Conference on Trust, Security and Privacy in Computing and Communications, pages 328-336. IEEE, 2020.

#### Other publications.

Benjamin Semal, Konstantinos Markantonakis, Raja Naeem Akram. A certificateless group authenticated key agreement protocol for secure communication in untrusted UAV networks. 2018 IEEE/AIAA 37th Digital Avionics Systems Conference, pages 1-8. IEEE, 2018.

Jan Kalbantner, Konstantinos Markantonakis, Darren Hurley-Smith, Raja Naeem Akram, and Benjamin Semal. P2PEdge: a decentralised, scalable P2P architecture for energy trading in real-time. *Energies*, 14(3):606, 2021.

Jan Kalbantner, Konstantinos Markantonakis, Darren Hurley-Smith, Carlton Shepherd, and Benjamin Semal. A DLT-based smart contract architecture for atomic and scalable trading. arXiv preprint arXiv:2105.02937, 2021.

Carlton Shepherd, Jan Kalbantner, Benjamin Semal, and Konstantinos Markantonakis. A side-channel analysis of sensor multiplexing for covert channels and application fingerprinting on mobile devices. arXiv preprint arXiv:2110.06363, 2021.

Carlton Shepherd, Jan Kalbantner, Benjamin Semal, and Konstantinos Markantonakis. Exploiting sensor multiplexing for covert channels and application fingerprinting on mobile devices. arXiv preprint arXiv:2110.06363, 2021.

Carlton Shepherd, Benjamin Semal, and Konstantinos Markantonakis. Investigating Black-Box Function Recognition Using Hardware Performance Counters. arXiv preprint arXiv:2204.11639, 2022.

# Contents

| 1        | Intr | oduction 2                                    | 21 |

|----------|------|-----------------------------------------------|----|

|          | 1.1  | Setting the Scene                             | 22 |

|          | 1.2  | Motivation and Challenges                     | 23 |

|          | 1.3  |                                               | 25 |

|          | 1.4  | Scope                                         | 26 |

|          | 1.5  | Thesis Outline                                | 27 |

| <b>2</b> | Bac  | rground 2                                     | 29 |

|          | 2.1  | Cloud Ecosystem                               | 30 |

|          |      | 2.1.1 Overview of Cloud Models                | 30 |

|          |      | 2.1.2 IaaS Security Considerations            | 31 |

|          |      | 2.1.3 IaaS Industry Outlook                   | 32 |

|          |      | 2.1.4 IaaS Orchestration                      | 33 |

|          | 2.2  | Computer Architecture                         | 35 |

|          |      | 2.2.1 Processor Core                          | 35 |

|          |      | 2.2.2 Caches                                  | 36 |

|          |      | 2.2.3 Memory Bus                              | 37 |

|          |      | 2.2.4 DRAM Organisation                       | 39 |

|          |      | 2.2.5 Memory Controller                       | 10 |

|          | 2.3  | Operating Systems                             | 11 |

|          |      | 2.3.1 Logical Boundaries                      | 11 |

|          |      | 2.3.2 Virtual-to-Physical Address Translation | 12 |

|          |      | 2.3.3 Memory Access and Latency               | 13 |

|          | 2.4  | Related Work                                  | 13 |

|   |     | 2.4.1  | Microarchitectural Attacks               | 43         |

|---|-----|--------|------------------------------------------|------------|

|   |     | 2.4.2  | Countermeasures                          | 48         |

| 3 | On  | the Se | verity of Covert Channel Attacks in IaaS | <b>5</b> 3 |

|   | 3.1 | Introd | uction                                   | 54         |

|   |     | 3.1.1  | Scope of the Study                       | 55         |

|   |     | 3.1.2  | Structure of this Chapter                | 56         |

|   | 3.2 | Analys | sis of State-of-the-Art Attacks          | 56         |

|   |     | 3.2.1  | Memory Order Buffer                      | 56         |

|   |     | 3.2.2  | Last-Level Cache                         | 57         |

|   |     | 3.2.3  | DRAM Row-Buffer                          | 58         |

|   |     | 3.2.4  | Memory Controller                        | 59         |

|   |     | 3.2.5  | Memory Bus                               | 59         |

|   | 3.3 | Evalua | ation of Attacks                         | 60         |

|   |     | 3.3.1  | Attack Vector                            | 61         |

|   |     | 3.3.2  | Attack Complexity                        | 61         |

|   |     | 3.3.3  | User Interaction                         | 63         |

|   |     | 3.3.4  | Scope                                    | 63         |

|   |     | 3.3.5  | Confidentiality Impact                   | 64         |

|   |     | 3.3.6  |                                          | 65         |

|   |     | 3.3.7  | Exploit Code Maturity                    | 65         |

|   |     | 3.3.8  |                                          | 66         |

|   |     | 3.3.9  |                                          | 66         |

|   |     | 3.3.10 |                                          | 66         |

|   |     | 3.3.11 |                                          | 67         |

|   |     | 3.3.12 |                                          | 68         |

|   |     |        |                                          | 68         |

|   | 3.4 |        |                                          | 69         |

|   | 3.5 |        |                                          | 71         |

|   | 3.6 |        |                                          | 73         |

|   | -   |        |                                          |            |

| 4 | The | Memo   | ory Controller-based Covert Channel      | <b>7</b> 5 |

|   | 4.1 | Introd | uction                                   | 76         |

|   |     | 4.1.1   | Structure of this Chapter                         |

|---|-----|---------|---------------------------------------------------|

|   | 4.2 | Source  | es of Contention                                  |

|   | 4.3 | Privile | eged Native Covert Channel                        |

|   |     | 4.3.1   | Threat Model                                      |

|   |     | 4.3.2   | Principle                                         |

|   |     | 4.3.3   | Design Considerations                             |

|   | 4.4 | Unpri   | vileged Cross-VM Covert Channel                   |

|   |     | 4.4.1   | Threat Model                                      |

|   |     | 4.4.2   | Principle                                         |

|   |     | 4.4.3   | Design Considerations                             |

|   | 4.5 | Evalua  | ation                                             |

|   |     | 4.5.1   | Experimental Setup                                |

|   |     | 4.5.2   | Channel Capacity                                  |

|   | 4.6 | Mitiga  | ation                                             |

|   | 4.7 | Summ    | nary                                              |

| 5 | Elu | ding D  | efences with a Memory Bus-based Covert Channel 91 |

|   | 5.1 | _       | luction                                           |

|   |     | 5.1.1   | Structure of this Chapter                         |

|   | 5.2 | Design  | n Goals                                           |

|   |     | 5.2.1   | Deriving Design Requirements                      |

|   |     | 5.2.2   | Comparison with State-of-the-Art 96               |

|   | 5.3 | Buildi  | ng a Stealthy Covert Channel                      |

|   |     | 5.3.1   | The Memory Bus-based Covert Channel 97            |

|   |     | 5.3.2   | Threat Model                                      |

|   |     | 5.3.3   | Implementation                                    |

|   | 5.4 |         | ation                                             |

|   |     | 5.4.1   | Experimental Setup                                |

|   |     | 5.4.2   | Channel Capacity                                  |

|   |     | 5.4.3   | Effects on Microarchitectural States              |

|   | 5.5 | Discus  | ssion                                             |

|   |     | 5.5.1   | Closing the Memory Bus Covert Channel 105         |

|   |     |         |                                                   |

|              | 5.6 Summary                              | 107 |

|--------------|------------------------------------------|-----|

| 6            | Conclusion                               | 109 |

|              | 6.1 Summary and Conclusions              | 110 |

|              | 6.2 Recommendations for Future Work      | 112 |

| $\mathbf{A}$ | Memory Bus-based Covert Channel Sender   | 115 |

| В            | Memory Bus-based Covert Channel Receiver | 119 |

# List of Figures

| 2.2 | DRAM architecture                                                                                                        | 40  |

|-----|--------------------------------------------------------------------------------------------------------------------------|-----|

| 2.3 | Virtual-to-physical address translation                                                                                  | 42  |

| 2.4 | Virtual-to-physical translation of a 64-bit address on an Intel                                                          |     |

|     | E6550 processor [33]. The cache line offset is determined by                                                             |     |

|     | bits 0 to 5, the cache line index is determined by bits 6 to 14,                                                         |     |

|     | and the page offset is determined by bits 0 to 12. Colour bits                                                           |     |

|     | range from bit 12 to bit 14                                                                                              | 50  |

| 3.1 | Attack setting                                                                                                           | 55  |

| 3.2 | Scoring of cross-VM covert channel attacks under the CVSS                                                                |     |

|     | and CCSS: $\mathbf{a} = \text{LLC}$ [124], $\mathbf{b} = \text{LLC}$ [166], $\mathbf{c} = \text{Memory bus}$             |     |

|     | $[164]$ , $\mathbf{d} = \text{LLC } [92]$ , $\mathbf{e} = \text{LLC } [100]$ , $\mathbf{f} = \text{Row-buffer } [122]$ , |     |

|     | $\mathbf{g} = \text{LLC [101]},  \mathbf{h} = \text{Memory order buffer [140]},  \mathbf{i} = \text{Memory}$             |     |

|     | controller [133], $\mathbf{j} = \text{Memory bus } [132] \dots \dots$                                                    | 71  |

| 4.1 | Memory controller representation                                                                                         | 79  |

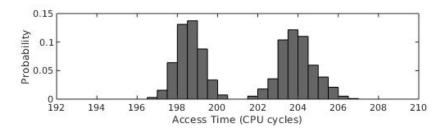

| 4.2 | Effect of active sender upon latency of receiver's memory ac-                                                            |     |

|     | cesses (Ivy Bridge setup)                                                                                                | 85  |

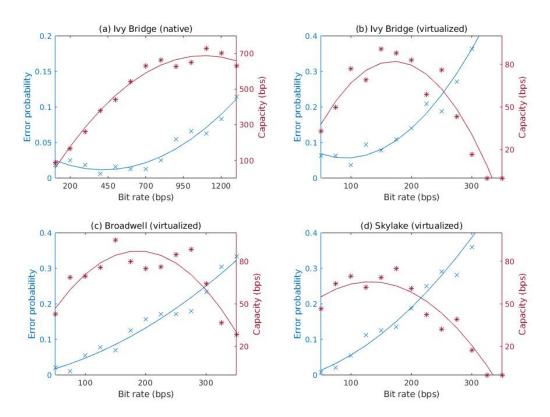

| 4.3 | Effective capacity and error probability measured against raw                                                            |     |

|     | bit rate                                                                                                                 | 87  |

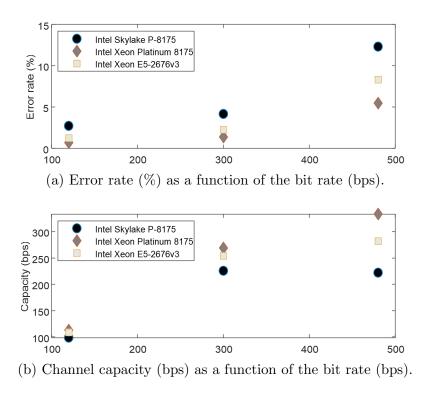

| 5.1 | Error rate and capacity.                                                                                                 | 103 |

# List of Tables

| 2.1 | Resource ownership comparison                                   | 31  |

|-----|-----------------------------------------------------------------|-----|

| 2.2 | Worldwide public IaaS share and revenue (million USD) [47, 48]. | 32  |

| 3.1 | Cross-VM covert channel attacks                                 | 57  |

| 3.2 | Scoring of cross-VM covert channel attacks under the CVSS       |     |

|     | and CCSS                                                        | 72  |

| 3.3 | Average $(\mu)$ and variance $(\sigma^2)$                       | 72  |

| 4.1 | Experimental setups                                             | 85  |

| 4.2 | Experimental results                                            | 88  |

| 5.1 | Cross-VM covert channel attacks against desired design goals.   | 96  |

| 5.2 | Error rate and capacity (raw bitrate of 480 bps)                | 102 |

## List of Abbreviations

**AES** Advanced Encryption Standard

ALU Arithmetic Logic UnitAMD Advanced Micro DevicesAMI Amazon Machine Image

**API** Application Programming Interface

ARM Advanced RISC Machine

AVX Advanced Vector Extensions

AVX2 Advanced Vector Extensions 2

**AWS** Amazon Web Service

BIOS Basic Input Output System

**BTB** Branch Target Buffer

CAT Cache Allocation Technology

CCSS Covert Channel Scoring System

CISC Complex Instruction Set Computer

**CPU** Central Processing Unit

CVE Common Vulnerabilities and ExposuresCVSS Common Vulnerability Scoring System

**DES** Data Encryption Standard

DDR3 Double Data Rate 3DDR4 Double Data Rate 4

**DIMM** Dual-Inline Memory Module

**DRAM** Dynamic Random Access Memory

EC2 Elastic Compute Cloud

**ECC** Elliptic Curve Cryptography

**EPSS** Exploit Prediction Scoring System

FPU Floating Point Unit

FSB Front-Side Bus Gb Gigabit

Gb GigabitGB Gigabyte

GCE Google Cloud Engine

GDPR General Data Protection Regulation

HC Hardware ConfigurationIaaS Infrastructure-as-a-Service

**IBM** International Business Machines

IN Initialisation

**ISA** Instruction Set Architecture

Kb KilobitKB Kilobyte

L1-D Level 1 Data Cache

L1-I Level 1 Instruction Cache

L2 Level 2 Cache

LLC Last-Level Cache

LSU Load-Store Unit

Mb MegabitMB Megabyte

MBA Memory Bandwidth AllocationMMU Memory Management Unit

MOB Memory Order Buffer

**NUMA** Non-Uniform Memory Access

OS Operating System

PaaS Platform-as-a-Service

PC Program Counter

PCIe Peripheral Component Interconnect Express

**PR** Privilege Required

**RAM** Random Access Memory

**RISC** Reduced Instruction Set Computer

**RL** Remediation Level

**ROP** Return Oriented Programming

RSA Rivest Shamir Adleman

RSB Return-Stack Buffer

SaaS Software-as-a-Service

SATA Serial AT Attachment

SGX Software Guard eXtension

SIMD Single Instruction Multiple Data

SMT Simultaneous Multi-Threading

SRAM Static Random Access Memory

SSE Streaming SIMD Extensions

SSH Secure Shell

SSL Secure Sockets Laver

SSVC Stakeholder-Specific Vulnerability Categorization

**TDES** Triple-Data Encryption Standard

**TEE** Trusted Execution Environment

**TLB** Translation Lookaside Buffer

**TSC** Time-Stamp Counter

**TSX** Transactional Synchronization Extension

USD U.S. Dollar

VM Virtual Machine

**VPC** Virtual Private Cloud

**WC** Write-Combining

$\mu$ **OPs** Micro-Operations

# Chapter 1

## Introduction

### Contents

| 1.1 | Setting the Scene         | 22 |

|-----|---------------------------|----|

| 1.2 | Motivation and Challenges | 23 |

| 1.3 | Contributions             | 25 |

| 1.4 | Scope                     | 26 |

| 1.5 | Thesis Outline            | 27 |

This chapter exposes the challenges faced in cloud computing ecosystems and presents the thesis' rationale along with its contributions. The scope of the thesis is then delimited. The reader will also find a discussion on the structure of this manuscript.

### 1.1 Setting the Scene

Today's notion of *cloud computing* dates back from the 1950s, when largescale computing mainframes were introduced. The mainframe would provide a single, powerful computing environment to multiple users. In the 1960s, the Massachusetts Institute of Technology sought for new computers capable of more than one simultaneous user. The stimuli lead International Business Machines (IBM) to design the VM operating system [35], capable of dividing storage and system resources. The technology enabled a single mainframe to have multiple virtual machines (VMs) running concurrently, thus allowing distinct computing environments to co-exist on a single physical node. VMs provided better security since each user was running in its own operating system (OS), and improved reliability as no one user could take down the entire system. Resource usage could also be optimised and return on investment improved, thus making the technology accessible to a wider public. This early form of cloud computing was eventually galvanised by the advent of the Internet in the 1990s. With the costs of hardware coming down as well as a rocketing demand, corporations needed to combine multiple physical nodes together. Single software components, known as orchestrators, allowed managing a pool of hardware servers as if they were a single physical node, and enabled coping with the new demand.

Cloud computing then morphed into multiple shapes, with a cloud service for every need. Anyone who doesn't possess its own server can now rent an *instance* to a cloud provider, and access a seemingly unlimited pool of resources instantaneously. In 2018, it is estimated that 26% of the European Union's enterprises were dependent on cloud services, with a 21% increase in large corporations since 2014 [39]. Furthermore, the study reports that out of these companies relying on cloud computing, 55% use it for financial and accounting software applications, customer relationship management, or business applications that require advanced computational power. The data stored and processed on these cloud platforms can be of sensitive nature, which raises confidentiality issues. IBM Security evaluated the average cost of a data breach to 3.58 million USD, with 80% of the compromised data

being customer personally identifiable information [130].

Since the 1990s, researchers investigated the security aspects of multitenancy [61, 62, 163]. When multiple software components (threads, processes, or VMs) execute simultaneously, they compete with each other for processor resources. Such conflicts can delay the execution of certain instructions, resulting in timing variations to occur. These timing variations can in turn lead to accidental disclosure of secrets, such as cryptographic keys. Despite efforts to raise awareness over the risks associated with hardware optimisation [173, 16, 145, 50], manufacturers carried on regardless of security. A security gap grew progressively which eventually lead to unfortunate breakthroughs. The field of microarchitectural attacks entered its apogee with the release of the Spectre [81] and Meltdown [89] attacks in January 2018. Computer security, which heavily relies on memory isolation, was met with vulnerabilities that could only be addressed by modifying the microarchitecture, either in the form of microcode updates, or new hardware designs. Hardware manufacturers could no longer fall back on application developers to take the responsibility. These new security bugs opened the way to an avalanche of disclosures on newly found vulnerabilities, challenging the foundations on which the security of our computers is based.

### 1.2 Motivation and Challenges

Microarchitectural timing-based attacks exploit the sharing of a processor among multiple tenants, in order to compromise sensitive information. Thus they have the potential to severely compromise the viability of the multitenant computing model. In 2013, the Cloud Security Alliance rated cross-VM leakage channels as the number one threat to cloud computing [11]. Two colluding entities can intentionally create timing variations in order to encode and decode binary information. Based on this principle, microarchitectural covert channel attacks allow tunneling information out of a compromised system when the security policy does not allow doing so. In other words, an attacker can extract information covertly out of a victim's cloud instance. Significant work has been accomplished in the field of microarchitectural at-

tacks, however it almost exclusively focuses on side channels. Also, covert channels are often associated with the hiding of secret information in network protocols. Microarchitectural covert channels have a powerful potential which draws from both disciplines.

Microarchitectural covert channels offer a quieter means to exfiltrate data than network protocols, although they rely on a stronger adversary model. They assume an attacker with advanced capabilities that seeks to maintain long-term access to the victim's instance. This type of adversary has other incentives than simple financial gain or notoriety. Indeed, the IBM Security study reports that 13% of data breaches are carried out by nation state actors [130], which have a more strategic approach to cyber-warfare. Yet, it is not trivial to assess the severity and practicality of these attacks. Although the latest version of the Common Vulnerability Scoring System (CVSS) provides more flexibility, it is still not adequate to assess the severity microarchitectural covert channels. Furthermore, these attacks are not well understood by the community. Security experts tend to associate microarchitectural attacks to side channels, which rely on a substantially different adversary model.

Microarchitectural attacks exploit hardware vulnerabilities that are specific to a processor implementation, also know as a microarchitecture, from the software domain. An attacker that intends to modulate a microarchitectural component must do so at a very low level. The inner mechanics of the Central Processing Unit (CPU) must be well understood. There is a significant amount of operations which are transparent to the developer, and over which the attacker must have fine-grained control, such as memory addressing, pipeline execution, caching, out-of-order execution, dynamic RAM (DRAM) refreshing, etc. In 2020, it is estimated that x86 processors represented 90% of the global revenue generated by the market of cloud servers [64]. Therefore, the vulnerabilities of interest are most often specific to Intel and AMD processors. Beyond the adversary model, the challenge to deploying these attacks is to gain detailed knowledge of the microarchitecture despite the lack of public information provided by hardware manufacturers. For instance, Intel does not reveal its DRAM addressing functions, forcing attackers to undertake reverse engineering studies.

In a context where cloud consumers are facing major cyber-threats, this thesis investigates security guarantees offered by virtualisation on data confidentiality, by exploring new means of compromising logical isolation based on x86 hardware vulnerabilities. Ultimately, it is hoped that this work will further our understanding of complex processor architectures, expose certain security risks oblivious to most of cloud consumers, and encourage considerations for security when designing future processor generations.

### 1.3 Contributions

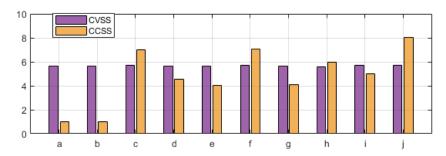

The contribution of this thesis is threefold. First, a study is conducted on the operational constraints related to the deployment of microarchitectural covert channels in Infrastructure-as-a-Service (IaaS), based on an analysis of state-of-the-art attacks. The adversary model is studied under the CVSS v3.1 [113], with a resulting severity score of 5.0. In comparison, the SSLv3 POO-DLE [110] and OpenSSL Heartbleed [109] vulnerabilities achieved respective scores of 3.4 and 7.5. This research thread is the first illustration of the vulnerability of multitenant computing environments to covert channel attacks. Furthermore, a bespoke framework is devised which includes three additional evaluation criteria. The resulting Covert Channel Scoring System (CCSS) is capable of outlining disparities among attacks which the CVSS does not. Eventually, this study reveals the existence of a gap between the direction taken by researchers, and the actual challenges faced by the industry. For instance, the analysis shows that cache-based covert channels, although increasingly popular, are the least viable attacks. The CCSS may serve as a metric for the performance of future publications, by outlining whether the covert channel attack can be deployed in a commercial environment. Eventually, this research thread successfully refutes the erroneous intuition over the lack of practicality of microarchitectural covert channels, and puts forward a new method for evaluating the practicality of these attacks.

Second, a vulnerability on Intel's integrated memory controllers is exposed. For the first time, an instantiation of a covert channel attack is proposed, both in native and virtualised environments. The cross-VM covert

channel is tested across three different Intel microarchitectures, namely Ivy Bridge, Broadwell, and Skylake. The cross-core covert channel achieves a capacity of 729 bps in a native scenario, and up to 95 bps in the cross-VM scenario. This work outperforms other attacks which require the enabling of page sharing, simultaneous multi-threading (SMT), or which can be thwarted by the myriad of existing countermeasures [33, 37, 53, 62, 78, 90, 99, 152, 155, 168]. This research thread successfully demonstrates the presence of remaining vulnerabilities on x86 processors, and that there are alternatives to cache-based timing channels. Potential countermeasures are finally suggested.

Third, a new instance of the memory bus-based covert channel is devised, circumventing every relevant leakage channel countermeasure proposed in academia so far. Indeed, significant efforts have been made in order to address timing channel vulnerabilities, however new attacks tend to disregard the relevant countermeasures, arguing that these have not yet been deployed by OS and cloud providers. This research thread proposes a retrospective analysis on state-of-the-art attack and defence techniques, and shows that all existing covert channels could effectively be closed. The x86 memory bus vulnerability is re-visited in order to discard the usage of artifacts which are theoretically made unavailable by recently proposed countermeasures. The new attack is then deployed on the Amazon Web Service (AWS) Elastic Compute Cloud (EC2) commercial IaaS platform. The new instance of the memory bus-based covert channel effectively demonstrates that x86 microarchitectures (Intel and AMD) still present salient vulnerabilities, and that state-of-the-art defence strategies—even theoretical ones—remain unsuccessful at hindering data leakage in multi-tenant environments.

### 1.4 Scope

Microarchitectural covert channels exploit vulnerabilities in the implementation of a processor's architecture. In contrast, network covert channels abuse network protocols [161, 145]. This thesis examines the side-effects of multitenancy on the confidentiality of cloud-based data and services, therefore the latter case is not consistent with the thesis rationale. Also, not all covert channels have malicious intents. For example, some will be leveraged to add authentication features over existing industrial networks. In this thesis, the term *covert channel* refers exclusively to attacks.

The term leakage channel encompasses both side and covert channels, which differ in the attack scenario. Independently from the adversary model, leakage channels share the underlying mechanisms. The distinction lies in whether timing variations are generated accidentally or intentionally. In addition, some related works classify microarchitectural attacks between storage-based and timing-based channels. A storage-based channel utilises variations in data values as the sole mechanism to encode and interpret information. In contrast, a timing-based channel exploits the time to access this data. In a virtualised ecosystem, only the latter case is relevant.

Finally, a covert channel does not necessarily allow communication across VMs. However, this thesis investigates covert channel attacks in the context of multitenant environments, i.e. virtualised. Therefore, only *cross-VM* covert channels are considered. This study could be applied to environments similar to IaaS, e.g. private clouds. It is worth mentioning that the evaluation of the adversary model presented in Chapter 3 is specific to IaaS, and does not account for variations in similar environments.

### 1.5 Thesis Outline

Chapter 2 concentrates the background related to subsequent chapters, from cloud computing models, through hardware architecture, to logical isolation principles. A literature review is then provided on the field of microarchitectural attacks along with a presentation of covert channel attacks.

Chapter 3 studies the adversary model of microarchitectural covert channel in a cloud environment, and demonstrates the severity of such attacks. A bespoke evaluation framework is then proposed which outperforms the CVSS, notably when comparing one covert channel implementation to another.

Chapter 4 presents a new covert channel attack which leverages timing vulnerabilities in Intel memory controllers. The attack allows leaking information across processes with distinct address spaces, and across VMs (at reduced performance), thus offering an alternative to similar attacks based on the sole exploitation of cache memories. The covert channel is tested in a laboratory environment.

Chapter 5 presents a new technique to elude timing channel countermeasures. It is based on a memory bus covert channel which leverages timing variations incurred by atomic accesses to cache line-crossing memory regions. The attack is tested on both laboratory and commercial environments, namely the Amazon Web Service Elastic Compute Cloud service.

Chapter 6 concludes on the contributions of this thesis and identifies potential research threads related to this thesis.

# Chapter 2

## Background

#### Contents

| 2.1 | Cloud Ecosystem       | 30 |

|-----|-----------------------|----|

| 2.2 | Computer Architecture | 35 |

| 2.3 | Operating Systems     | 41 |

| 2.4 | Related Work          | 43 |

This chapter introduces cloud computing models with a discussion on the current state of the market. Underlying concepts to computer architecture are then presented. Finally, a literature review on microarchitectural transient and timing attacks is provided, with an emphasis on covert channels.

### 2.1 Cloud Ecosystem

Cloud computing is an ubiquitous and yet equivocal term. One can summarise it as the delivery of different services through the Internet. This section defines cloud services under different models, and provides insights into the state of the cloud market.

#### 2.1.1 Overview of Cloud Models

The NIST defines three types of cloud services [102], namely Infrastructure-as-a-Service, Platform-as-a-Service, and Software-as-a-Service. Although not exhaustive, this definition of cloud services is widely adopted in the community, and will therefore be used in the remainder of this thesis. Table 2.1 provides a comparison of resource ownership among the three cloud categories.

Software-as-a-Service (SaaS) offers internet-based software applications to end-users. A characteristic of SaaS is that all resources are managed by the remote third-party. The end-user is not required to install any software on its machine, and security is taken care of by the service provider. Services are typically accessed via a web browser. Examples of SaaS include Microsoft Office 365, Dropbox, Google Docs, etc.

Platform-as-a-Service (PaaS) consists of an internet-accessible environment for developing, maintaining, and executing software applications. Endusers (mostly developers) are provided with a dedicated runtime environment, and are responsible for managing the software application and its associated data. Examples of PaaS include Google App Engine, Amazon Web Service Elastic Beanstalk, Red Hat OpenShift, etc.

Infrastructure-as-a-Service delivers internet-accessible storage, processing, and network resources. The end-user controls every component inside the virtual machine, while the service provider manages servers and orchestrators (or containers). Examples of IaaS include Amazon Web Service Elastic Compute Cloud, Google Compute Engine, etc.

On-Site IaaS PaaS SaaS Application  $\bigcirc$ Data  $\bigcirc$ Runtime  $\bigcirc$  $\bigcirc$ Middleware  $\bigcirc$  $\bigcirc$ OS  $\bigcirc$  $\bigcirc$ Virtualisation  $\bigcirc$  $\bigcirc$  $\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

Table 2.1: Resource ownership comparison.

#### 2.1.2 IaaS Security Considerations

Networking

Server

Storage

As shown in Table 2.1, IaaS users remain in control of their entire virtual environment. Users can interact with the instance as with any other machine (e.g. root access). They also benefit from several web-based application programming interfaces (APIs) that enable managing instances (e.g. selecting a hardware configuration). Therefore, IaaS minimises the trust that needs to be extended to the cloud provider. The user is in control of the (sensitive) data being processed in the virtual machine, including data from any other service built upon it (e.g. platform or software). This suggests that IaaS instances represent the most compelling targets to malicious individuals. An attacker which gains access to an IaaS instance can potentially compromise the entire OS-to-application stack.

Cloud models can be further classified depending on whether the base infrastructure is managed privately or by a third-party. In a public cloud solution, the cloud provider supplies the servers, network, and virtualisation support. The user looses physical control over its data, and the computing environment is somewhat shared with other parties. In a private cloud solution, the base infrastructure is managed locally (e.g. intranet) and can be closed from the public. It implies a significant investment on behalf of

<sup>\*</sup>managed by • the user,  $\bigcirc$  the cloud provider

the organisation, which might not always be justified. This solution is preferred when compliance against high security standards is required. Private clouds will either be physically disconnected from the Internet, or put under a strong firewall. These can still be targeted, however public instances certainly represent a lower-hanging fruit for the attacker.

#### 2.1.3 IaaS Industry Outlook

Cloud providers must deploy tremendous resources in order to cope with the existing demand. Thus the market of public IaaS is dominated by a few large corporations including Amazon Web Service, Microsoft Azure, Alibaba Cloud, Google Compute Engine, Tencent Cloud, and Huawei Cloud. Table 2.2 shows that in 2019 [47], Amazon holds the largest share of the market (45%) with a revenue of 19990 million USD. In 2020 [48], Amazon still holds the largest share (40.8%) with a revenue of 26201 million USD. It can be seen that most cloud providers increase their market share over time, at the exception of Amazon which lost 7.1% between 2019 and 2020. It is also seen that the China-based cloud provider Huawei overtook Tencent in 2020. The most significant observation is the decrease of "other" cloud providers' share, indicating that it will become harder and harder to compete with the top five IaaS vendors.

Table 2.2: Worldwide public IaaS share and revenue (million USD) [47, 48].

| Cloud provider | 2018    |       | 2019    |       | 2020    |       |

|----------------|---------|-------|---------|-------|---------|-------|

|                | Revenue | Share | Revenue | Share | Revenue | Share |

| Amazon         | 15495   | 47.9% | 19990   | 45.0% | 26201   | 40.8% |

| Microsoft      | 5037.8  | 15.6% | 7946.6  | 17.9% | 12658   | 19.7% |

| Alibaba        | 2499.3  | 7.70% | 4060.0  | 9.10% | 6117.0  | 9.50% |

| Google         | 1313.8  | 4.10% | 2365.5  | 5.30% | 3932.0  | 6.10% |

| Tencent        | 611.80  | 1.90% | 1232.9  | 2.80% | -       | -     |

| Huawei         | -       | -     | 882.00  | 1.90% | 2672.0  | 4.20% |

| Others         | 7425.0  | 22.8% | 8858.0  | 19.9% | 12706   | 19.8% |

| Total          | 32382   | 100%  | 44453   | 100%  | 64286   | 100%  |

In a separate study [46], the forecast global revenue is expected to reach 50393 million USD by the end of 2020, 64294 million USD by the end 2021, and 80980 million USD by the end of 2022. Between 2019 and 2022, this represents a 82% increase, which confirms the growing interest of organisations for cloud solutions.

#### 2.1.4 IaaS Orchestration

Cloud orchestration consists of automating the dynamic management of workloads such as assigning storage and processing resource, and instantiating VMs. Orchestration also enables enforcing information flow policies such that permissions to connect and execute workloads are securely handled. Orchestration thus enables the provider to cope with an elastic demand while maintaining logical isolation among tenants. However, the isolation is not necessarily physical. Instances may be mapped to resource within the same processor, same rack, or same cluster of servers [124, 60, 167]. This is referred to as co-tenancy and is transparent to the cloud service user. A tenant is unaware of the activity of co-resident workloads and vice versa. This can cause undesirable effects such as "noise" generated by resource-intensive workloads on neighbour instances. A more serious consequence is the absence of barriers that would prevent a malicious cloud user from spying on its neighbours through the monitoring of the availability of shared hardware resource, i.e. microarchitectural states. Co-tenancy, or co-residency, is a core assumption to the adversary model of every microarchitectural covert and side channel attacks designed for multi-tenant computing environments. We note that cloud service providers propose products known as dedicated instances [32, 134], where the cloud user is guaranteed to be the sole tenant of a hardware platform. It is not known though at which level the physical separation is made (core, processor, NUMA node, etc.). Furthermore, this type of instance is significantly more expensive than non-dedicated instances, e.g. an on-demand EC2 a1.2xlarge instance costs 0.204 USD per hour while a dedicated EC2 a1.2xlarge instance costs 2.2162 USD per hour (at the time of writing).

Depending on the locality between a spy and a trojan, three scenarios exist for establishing microarchitectural covert channels. Let us define a communicating entity (i.e. either trojan or spy) as a process. First, if both processes are executed within the same processor core, these will share core-level microarchitectural resource including level 1 instruction and data caches, execution units, and CPU-level buffers. In fact, the two processes will share every possible components, both inside and outside of the processor core. This scenario is only plausible if SMT is enabled which allows multiple processes to share a single physical processor core. The first generation of microarchitectural covert and side channel attacks made such assumptions [2, 116, 142], which led industry and academia to devise core-level countermeasures such as RPcache [82], hardware cache partitions [37], noise injection [158], or even advocate the disabling of SMT [98]. Second, if both processes execute on separate processor cores but within the same processor die, these will no longer share core-level resource but only processor-level components including the last-level cache. This has been the target of the second generation of microarchitectural timing channels [171, 56, 92], leading to a new set of countermeasures being proposed including cache colouring [33], noise injection on timers [99], and recommending the disabling of memory de-duplication (which only deters the Flush+Reload class of attacks). Finally, if processes are executed on separate processors within a NUMA configuration (i.e. connected by a bus interconnect), core-level resource can still be manipulated although the non-uniform nature of memory requests may prevent accurate resolution of the leaked information. Other resource located beyond processors, such as the interconnect and DRAM row-buffers have been exploited to demonstrate new attack vectors [122, 133, 132]. Potential countermeasures include the partitioning of the memory controller [154], auditing [176], and forcing privileges on flushing instructions [56].

Achieving co-residency is further discussed in Chapter 3. The remainder of the thesis consists in identifying means of exposing that activity of cotenants, and using it to craft rogue communication channels that circumvent logical barriers.

# 2.2 Computer Architecture

This section presents microarchitectural elements involved in routine processor operations and which can be exploited for timing-based covert channels.

### 2.2.1 Processor Core

The term *processor* refers here to the entire die. The processor comprises a last-level cache (LLC) shared among one or more cores, an integrated memory controller, buses, and additional analog components. Each core contains individual instruction (L1-I) and data (L1-D) level 1 caches, and potentially a level 2 (L2) cache depending on the microarchitecture. Cores also contain one or two physical CPU(s) each. The CPU is the set of execution units and other logic required for instruction execution, e.g. arithmetic logic unit (ALU), floating point unit (FPU), load-store unit (LSU), translation lookaside buffer (TLB), return-stack buffer (RSB), branch target buffer (BTB), etc. The execution pipeline involves resources of the CPU as well as L1 and L2 caches. A generic RISC pipeline can be decomposed in five stages, namely instruction fetch, instruction decode, execution, memory access, and write back. In microarchitectures that rely on a x86 instruction set architecture (ISA), execution stages can be different due the varying length of CISC instructions, although the overall principle remains similar. ISA implementations vary significantly from one another, however the reader will find that the above-described components are commonly encountered on modern processors (i.e. found in commercial workstations or servers). ISAs then feature many extensions to provide support for specific operations, including advanced vector extension (AVX), streaming single instruction multiple data (SIMD) extensions (SSE), instructions for optimising AES operations, or transactional synchronization extensions (TSX).

A program is a sequence of instructions which are stored into memory upon execution. The cache is there to decrease the latency of loading repeated instructions and data structures. A dedicated register, known as the program counter (PC), holds the address of the next instruction to be fetched. Unless the program encounters branches, instructions are fetched

sequentially by simple increment of the PC, e.g. plus 4 bytes on a 32-bit ISA. Instructions contain several fields, namely its opcode and operand(s). After being fetched, the instruction's opcode is decoded, thus informing the CPU on how to read the remaining of the instruction and what resources must be allocated, e.g. ALU, LSU, etc. Then, the instruction operands are propagated through the execution units. For instance, the ALU will perform arithmetic or bitwise operations on integer binary numbers, the FPU will compute more complex operations (e.g. square root) on floating-point numbers, etc. Not all instructions are of arithmetic nature. The LSU queues and executes load/store operations occurring between registers and other memory subsystems (e.g. caches). Finally, the result of the execution is written back to registers.

#### 2.2.2 Caches

A cache is a static RAM (SRAM) type of memory. SRAM cells are made of multiple transistors, and are characterised by their ability to perform very fast read and write operations. They act as buffers for frequently requested data structures, thus improving the overall throughput. Caches are organised in several levels, with the lower levels being the closest from execution units (e.g. L1). The L1 cache is further split into an instruction cache (L1-I) and a data cache (L1-D). Other cache levels are unified, meaning they can contain both data and instruction. Other small caches may serve specific roles, such as storing page-table entries for the memory management unit (MMU), i.e. the TLB.

Caches can be directly-mapped, set-associative, or fully-associative. In a directly-mapped cache, a cache line index is used to determine the cache line of interest, and a tag determines whether the cache line contains the memory address. The index is a *n*-bit portion of the address and is therefore not unique. In other words, directly-mapped caches might contain many cache lines with the same index, also known as congruent, resulting in frequent cache line evictions. Set-associative caches somewhat mitigate the congruency issue by mapping the index to a cache set rather than a cache line. The

cache set itself contains multiple cache ways which can be differentiated with the tag. On contemporary processors, most of data and instruction caches are set-associative. Finally, fully-associative caches use the tag to directly resolve the cache way of interest, much like if a set-associative cache had only one large cache set. The TLB is often a fully-associative cache.

Caches also vary depending on their addressing mode. Modern processors allow multiple processes to execute concurrently, with each process having its own (virtualised) address space. As mentioned earlier, set-associative caches rely on a tag and an index in order to address memory. Therefore, the question is whether these two elements are calculated from the virtual (contiguous) or the physical (non-contiguous) address. The virtually-indexed virtually-tagged addressing mode has the benefit that it is faster since it does not require virtual-to-physical address translation. However, it requires the entire process' set of cache lines to be invalidated upon context switches (i.e. when another process takes over the execution pipeline). This is particularly expensive for large caches. The physically-indexed physically-tagged addressing mode suffers from the opposite pros and cons. A sensible approach is to rely on a virtually-indexed physically-tagged addressing mode which uses the virtual address to compute the index, and the physical address to calculate the tag. It enables retrieving the cache set immediately, thus masking the latency of translating the virtual address.

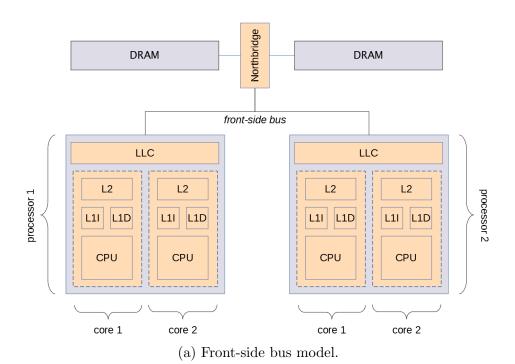

# 2.2.3 Memory Bus

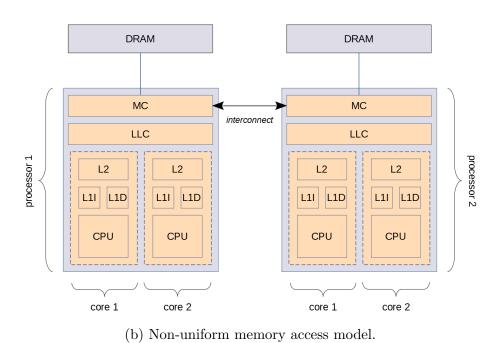

Up until the release of the AMD Opteron and Intel Nehalem microarchitectures, memory accesses to non-cache memory were handled by a chipset composed of a Northbridge and a Southbridge. The Northbridge contained the memory controller and was linked to processors by the front side bus (FSB) (see Figure 2.1a). The Southbridge contained the I/O controller and was connected to other peripherals via dedicated buses, e.g. PCIe, SATA, etc. With the advent of parallel computing, the FSB quickly became a bottle-neck for parallel program execution. An optimisation strategy has consisted in placing memory controllers directly onto processor dies. As a result, each

CPU has been given fast access to a segment of DRAM, without relying on a shared memory bus. An interconnect between processors has also been introduced, in order to provide access to non-local regions of the DRAM. Accesses to local and non-local segments vary in latency, hence this architecture was named non-uniform memory access (NUMA) (see Figure 2.1b). The interconnect technology varies across microarchitectures and manufacturers. It is known as Quick Path Interconnect on Intel processors and HyperTransport on AMD processors. The Southbridge, also known as I/O hub, remains on NUMA architecture.

## 2.2.4 DRAM Organisation

Because cache memories are limited in size due to SRAM cells' higher footprint, memory accesses will often be served from the dynamic RAM (DRAM). A DRAM cell consists of one transistor and one capacitor. In order to read a bit, the word line is raised, enabling the capacitor to discharge in the bit line. In order to write a bit, the bit line is set accordingly to the bit value and the word line is raised long enough to either drain or charge the capacitor. Reading a bit effectively discharges the cell, and the capacitor naturally loses its charge over time. Consequently, cells need to be recharged at regular intervals. The memory controller automatically performs this operation, which can cause the read/write bandwidth to drop occasionally. Furthermore, the time required to charge or discharge the capacitor causes usual read and write operations to take longer than with SRAM cells.

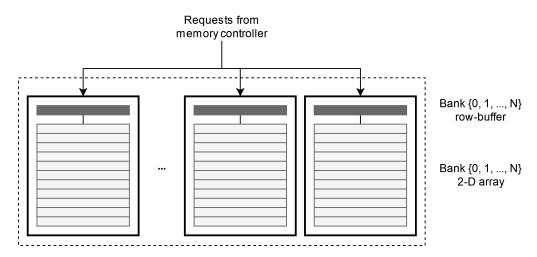

DRAM cells are organised in rows, columns, banks, ranks, and dual-inline memory modules (DIMMs). Typically, a DDR3 DIMM contains two ranks, each one containing four to eight banks. Figure 2.2 represents several banks within a rank. Each bank contains a row-buffer, and a 2-D array, i.e. rows and columns. When the requested data is contained in the row-buffer, it is a *row-hit*, otherwise it is a *row-miss*. Upon row-misses, the row-buffer is updated with the row containing the requested data, before serving the request. As a result, a row-miss has a significantly higher latency than a row-hit.

Figure 2.2: DRAM architecture.

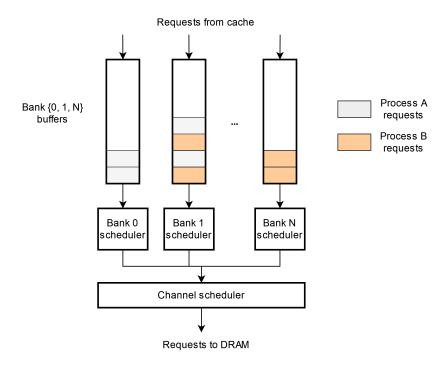

## 2.2.5 Memory Controller

The integrated memory controller, also known as DRAM controller, contains storage and scheduling resources to arbitrate memory accesses. The request is first stored in the buffer matching the DRAM bank that it targets. Then, the bank scheduler prioritises requests according to a scheduling algorithm. Once a request wins bank arbitration, it is rescheduled by a channel scheduler. Again, the scheduling algorithm determines priorities. Usually, requests that target open-pages are served first, so as to mitigate the latency incurred by updating a row-buffer. Before serving the memory access, the memory controller must translate the requested data's physical address into a DRAM map (i.e. channel, rank, bank, row, and column). The physical-to-DRAM address translation is performed according to DRAM addressing functions.

The memory controller's page policy dictates the aliveness of data in the row-buffer. If a close-page policy is enforced, the row-buffer will systematically be cleared after serving a request. Thus, each memory access results in a row-miss, preventing timing variations, but globally slowing down the execution of programs. If an open-page policy is enforced, the row-buffer will retain data until it must be updated with a new row. Thus, it allows the occurrence of row-hits, reducing the global execution time of programs, but introducing exploitable timing variations.

# 2.3 Operating Systems

This section introduces the concept of memory virtualisation and presents the effects of memory operations on microarchitectural elements.

## 2.3.1 Logical Boundaries

Virtualisation of the address space allows the operating system to set access rights and privileges to memory regions, such that two processes cannot have contiguous physical memory. Virtualisation is thus a basic principle of computer security as it enables memory isolation. When a memory operation is performed by one process, the MMU ensures that the targeted region belongs to this process. In other words, a process can never access the address space of other processes running concurrently. In a virtual machine, it is the entire guest's address space that is virtualised. This guarantees logical isolation between the address space of each VM, making possible the sharing of a computing environment while maintaining separate memory spaces. It is worth mentioning that operating systems can feature *shared memory* which occasionally allows a region of physical memory to be shared. This is used to limit redundancies and reduce the global memory footprint, e.g. shared libraries.

An orthogonal concept is the segregation between the user space and the kernel space. A process running in user mode can never be able to access a region of kernel memory. In contrast, a process running in kernel mode (e.g. driver, kernel module, etc.) has unrestricted access to physical memory, including that of user processes. When a user process attempts to access kernel memory, it is an illegal memory access. Kernel privileges should not be mistaken with superuser or administrative privileges. A process running with superuser permissions only has access to the kernel mode features that the kernel exposes to it (e.g. accessing system files). However, it is still a user process, and as such it does not have unrestricted access to peripherals and physical memory. Further modes of operation exist depending on the processor ISA. Seeking to obtain kernel privileges from an unprivileged program is referred to as a privilege escalation attack.

Figure 2.3: Virtual-to-physical address translation.

## 2.3.2 Virtual-to-Physical Address Translation

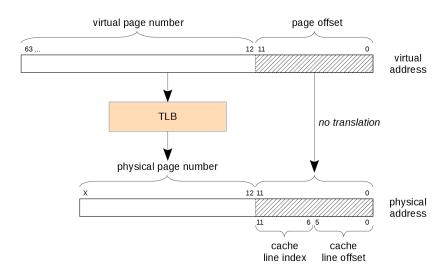

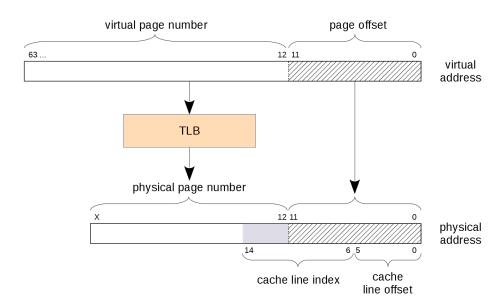

A process running on a processor that employs an addressing mode with virtual indices manipulates data structures using virtual addresses. When a data structure must be read or written to, a memory access occurs. This requires the virtual address of the data to be translated into a physical address. The MMU features its own cache, known as the TLB. The TLB contains the virtual-to-physical map of recently accessed addresses. If the TLB already contains the required entry, it is known as a TLB-hit, otherwise it is a TLBmiss. Upon TLB-misses, the MMU performs a page table-walk to recover the translation map. Once the physical address has been retrieved, the MMU computes the index and the tag of the cache line that contains the requested data. The index is used to point to a set of cache lines, and the tag is used to point to a specific cache line within this set. Finally, an offset computed from the variable's physical address is used to point to a specific portion of the cache line. Figure 2.3 shows how virtual-to-physical address translation is performed. The virtual page number is mapped to a physical page number via the TLB, while the 12-bit page offset is unmodified. Furthermore, the 6-bit cache line offset indicates a cache line size of  $2^6 = 64$  B, and the cache line index indicates a way size of  $2^6 = 64$  entries.

## 2.3.3 Memory Access and Latency

Once that the physical address has been recovered, the access to memory can proceed. If the requested cache line is not present at any cache level, known as a cache miss, a request is issued to the memory controller in order to fetch the data from DRAM. The data is then stored into the cache, known as a cache line fill, and is sent back to the CPU. The next access to the cached data will result in a cache hit. A store operation consists of modifying a cache line, and storing it back to memory (depending on the write-policy) via the store buffer. Prior to modifying data, the cache line must be loaded. If it is not present at any cache level, it is called a write miss, which triggers a cache line fill (except for Pentium processors). Otherwise it is a write hit.

In terms of latency, a TLB-miss will cause a longer access than a TLB-hit. Similarly, a cache-miss will serve the requested data more slowly than a cache-hit. Finally, if the data is served from DRAM (i.e. upon cache-miss), the row-buffer will also influence the latency, i.e. a row-miss causes a row-buffer update to occur before serving the memory access and is therefore slower than a row-miss. If the requested data is still not present in DRAM, it will be fetched from persistent memory, e.g. the disk. Accesses to the disk tend to have a dramatic effect on performance.

## 2.4 Related Work

This section presents the related in the field of microarchitectural attacks, from transient attacks to timing-based covert channels.

#### 2.4.1 Microarchitectural Attacks

The field of microarchitectural attacks encompasses many sub-categories. Due to the large amount of publications, researchers attempted to classify and occasionally draw taxonomies of attack techniques [7, 13, 20, 21, 50, 75, 82, 173, 95, 141]. Certain surveys focus exclusively on vulnerabilities in cryptographic algorithm implementations [15, 38, 42, 43, 94], while others

examine the effects on trusted execution environments [28, 103, 127]. In the following sections, an overview of the different sub-categories is presented.

#### Transient attacks

Transient-execution attacks are those that exploit hardware optimisation features such as out-of-order, speculative execution, etc. Rather than executing instruction sequentially, modern processors have the ability to re-order microoperations ( $\mu$ OPs) so as to optimise resource utilisation. For example, if an  $\mu$ OP requires an execution unit that is not available, it may be postponed such that other  $\mu$ OPs can be treated. Once the unit becomes available, this first  $\mu$ OP is executed, and the results are committed in-order. Occasionally, it is the evaluation of a condition for branching that is executed out-of-order. In such cases, the CPU can bet on the outcome of the condition evaluation, and speculatively execute a set of instructions. Whenever the condition is actually evaluated, if the bet was incorrect, than the CPU rolls back into its previous state.

The Meltdown class of attacks [26, 89, 126, 146, 147] abuses out-of-order execution in order to access kernel memory from a userspace program. The attacker performs an access to a virtual address that maps to kernel memory, causing the OS to raise an exception. To prevent program termination, Lipp et al. [89] suggested to either implement the illegal access into a child process, or use Intel TSX [66] to roll back into a previous state. The transient instruction, i.e. the one executed out-of-order but whose results were never committed, loaded the content of the virtual address into cache memory. The attacker then launches a cache-based covert channel in order to recover the contents of the kernel memory.

The Spectre class of attacks [30, 81, 83, 97] instead leverages speculative execution, in order to access concurrent programs' memory. The attacker mistrains the BTB by repeatedly executing a conditional branch with a valid condition. Once that the BTB is biased, the attacker can trick the CPU into executing speculatively a set of instructions which have a dependency on the targeted secret. To do so, the evaluation of the conditional branch must

depend on resources that are not immediately available, while the secret shall depend on resources that are already available (e.g. if secret = array[x], then array and x must be cached). Finally, the attacker launches a covert channel to recover the secret located in cache memory. Other variants of the Spectre attack have later been developed with different means of extracting the secret data, e.g. through a gadget that can be executed by mistraining the BTB (SpectreV2), using the Meltdown attack principle (SpectreV3), or re-using other covert channel primitives (SpectreV4).

### Timing-based attacks

Timing-based microarchitectural attacks leverage the sharing of hardware resources in order to steal and/or transmit information illegitimately. For instance, several works showed that a hardware thread may spy on the activity of another thread by monitoring the availability of execution units and their associated buffers [3, 4, 12, 25, 40, 157]. Similarly, it was also demonstrated that the TLB [63] and core-level caches (e.g. L1-I) can leak information at runtime [1, 2, 151, 160, 179]. A trivial countermeasure to these attacks consist in segregating threads belonging to different security domains onto separate cores. As a result, attackers moved towards hardware resources that are shared among all processor cores. The LLC is one of such resources, and has enabled a plethora of new cache attacks on both x86 [10, 27, 56, 180, 76, 169] and ARM [88, 174, 177] platforms.

Among these cache attacks, the most eminent one is the PRIME+PROBE [116] technique: the attacker fills one or more sets of a set-associative cache with its own cache lines (i.e. priming), lets the victim execute, and measures the access time to the data stored in these cache lines (i.e. probing). Whenever an access to a cache line is slow (i.e. cache-miss), it indicates that the victim evicted the data due to its own operation, revealing the presence of a shared cache set. Another prominent cache attack is the Flush+Reload [171] technique: the attacker flushes a cache line of shared memory with victim, lets the victim execute, and reloads the same cache line. If the reload is fast (i.e. cache-hit), then it indicates that the shared

cache line has been loaded by the victim. While Flush+Reload relies on the availability of shared memory, it does benefit from a higher resolution than Prime+Probe, i.e. the size of a cache line rather than the size of a cache set.

Osvik et al. [116] also presented the EVICT+TIME technique: the attacker lets the victim execute, causing the cache to fill up, and performs eviction with its own cache lines. Then again, the attacker lets the victim execute, and probes access to its own cache lines. If the latter is slower than normal, then indicates that the victim accessed the cache line of interest. EVICT+TIME is less encountered in the literature, as it does not provide any benefit over its counterpart. Gruss et al. developed the Flush+Flush technique where the attacker measures the elapsed time of each flushing instruction. If the second one has the same latency as the first one, it indicates that the victim performed a cache line fill in between, revealing the victim's data structures at the cache line granularity.

Timing attacks have found multiple applications. For instance, a large body of research has focused on finding vulnerabilities in Intel's Software Guard Extension (SGX). SGX is a proprietary TEE which enables an application running securely within a non-trusted environment. While Intel specifies that its TEE is not designed to safeguard against timing-based attacks, it does present salient flaws related to its caching [36, 54, 103, 104, 129, 153], page-table [59, 148, 153, 165], branch prediction [41, 86], and DRAM addressing [153] mechanisms. Naturally, most of timing-based side channels have also been applied against cryptographic implementations. The amount of related attacks does demonstrate how approved algorithms remain vulnerable under flawed implementations: (T)DES [143, 144], ECC [18, 24, 149, 170], RSA [5, 65, 172], and AES [6, 19, 22, 57, 72, 73, 111, 142, 159]. Nowadays, the literature focuses more on complex mechanisms such as TEEs rather than cryptographic libraries.

#### Focus on timing-based covert channel attacks

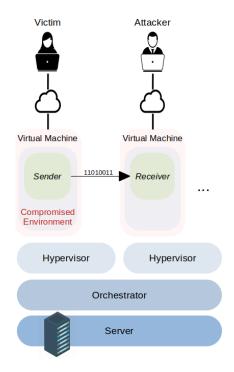

Microarchitectural cross-VM covert channels are software-launched attacks which exploit multi-tenant environments' shared hardware. In a timing-based covert channel, variations in the latency of a program execution are used to encode binary information. The receiver probes its own execution, which is directly influenced by the state of a hardware resource shared with the sender. An entire stream of bits is reconstructed in this way, enabling an attacker to transmit information from a compromised VM to another co-located VM. Ristenpart et al. [124] first studied the problem of VM co-location on the AWS EC2 service. They used the LLC to assert of the co-residency between two communicating VMs. Similarly, Xu et al. [166] explored the vulnerability of L2 caches for covert channel attacks on an EC2 instance. Wu et al. [164] proposed exploiting the memory bus as an alternative to cache-based covert channels, thus overcoming the addressing uncertainty. Later, the memory bus attack was revisited by Liu et al. [93] to use non-temporal instructions on the receiving-end, so as to mitigate the effect of cache pollution. This technique was previously suggested by Guri et al. [58] in their air-gapped covert channel. Pessl et al. [122] suggested using the DRAM row-buffer as a communication medium between two VMs. Their attack also allows crossprocessor information leakage. Liu et al. [92] re-used a PRIME+PROBE primitive in order to build a cross-VM covert channel as a vector for side channel attacks against GnuPG libraries. Maurice et al. [101] designed a robust LLC-based covert channel attack. Their work demonstrated the feasibility of implementing a network protocol on top of a covert channel across AWS EC2 instances. Sullivan et al. [140] revisited the exploitation of SMT using the memory order buffer for cross-VM leakage in the AWS EC2 and Google Cloud Engine (GCE) services. Their experiment highlights the consequence of enabling hyperthreads on public cloud platforms. Schwarz et al. [128] suggested exploiting the latency of powering up the upper-half of the AVX2 unit in order to build a new covert channel, subsequently used in their remote Spectre attack [81].

#### 2.4.2 Countermeasures

This section surveys and analyses relevant mitigation techniques against microarchitectural leakage channels, namely noise injection, software partitioning, and hardware partitioning. Whether a timing variation is created accidentally or intentionally, the mechanisms to modulate microarchitectural states remains similar. Therefore relevant countermeasures against timing-based side channels are also considered. Other countermeasures which are not relevant include constant-time execution, symbolic execution, state flushing, and noise injection within cryptographic implementations.

#### Noise injection on timers

This approach consists of jittering the timestamps of high-resolution timers [62, 152, 99, 93]. Being able to measure the latency of a single memory operation is crucial in timing channel attacks, as it leads to the interpretation of the activity of the victim (or sender). The x86 ISA features the rdtsc and rdtscp instructions which capture a time-stamp from the time-stamp counter (TSC), allowing timing measurements with a sub-nanosecond resolution. These are accessible from any non-privileged user program. Other timing sources, such as the wall clock provided by the operating system, are usually not accurate enough to measure a timing variation of a few clock cycles. For example, in [133], the sender's activity generates an overhead of only 6.5 CPU clock cycles. At a frequency of 2.4 GHz, this amounts to a time span of 2.7 ns. The attacker can neither rely on high-resolution timers, nor on operating system wall-clocks

#### Noise injection on caches

This approach aims at preventing an attacker from learning about the victim's working cache set. Wang and Lee [158] suggested integrating permutations in the cache index computation, while Qureshi et al. [123] used randomised mappings based on the encryption of the cache line's physical address. These will result in the victim's accesses to stop conflicting with the attacker's cache sets. Alternatively, Fang et al. [44] suggested having

the prefetch controller issuing requests to the L1 cache in order to tamper the timing observations of the receiving-end. For instance, in an m-way set associative cache, if m cache misses are observed when sending a 1, and none are observed when sending a 0. the prefetch controller will bring this number to m/2 all the time, such that the receiver is no longer capable of distinguishing a 1 from a 0. If generalised, these strategies can hinder cachebased covert channels that depend on the ability to find congruent addresses. Other proposals [91, 45, 168] studied bespoke cache replacement policies as an alternative to the vulnerable on-demand policy. Taking the example of the random-fill approach [91], if a cache miss occurs, the requested cache line is sent to the CPU but it is not necessarily stored in the cache. Instead, a "neighbour" cache line is randomly selected within a fixed address range around the requested cache line. If the same cache line is requested thereafter, it might result in a cache hit. The uncertainty contributes to inhibiting the leakage of information as to whether the victim accessed a specific cache line or not. This countermeasure is also relevant to cache covert channels such as Flush+Reload [171].

#### Software partitioning

Software cache partitioning, also known as cache colouring, consists of isolating sensitive data by means of isolating a set of cache lines for a given security domain [158, 155, 78]. Recall that in order to address data in (set-associative) caches, the MMU computes an index and an offset from the physical address. The bits that belong to both the physical page number and the cache line index are the *colour bits*. Figure 2.4 is an example of virtual-to-physical translation of a 64-bit address, with 6 bits of offset (i.e. cache line size is  $2^6 = 64$  bytes), 9 bits of index (i.e. way size is  $2^9 = 512$  entries), and 3 colour bits. Cache colouring states that physical pages which differ in any of the colour bits can never be mapped in the same cache set. That is, if the physical memory pages of two processes have at least one different colour bit, these can never exploit congruency to launch cache attacks such as PRIME+PROBE or EVICT+RELOAD [116]. In a sense, cache colour-

Figure 2.4: Virtual-to-physical translation of a 64-bit address on an Intel E6550 processor [33]. The cache line offset is determined by bits 0 to 5, the cache line index is determined by bits 6 to 14, and the page offset is determined by bits 0 to 12. Colour bits range from bit 12 to bit 14.

ing behaves like a dynamic clustering technique which guarantees that two clusters can never share a cache set. Liu et al. [90] suggested another form of software cache partitioning by leveraging Intel's Cache Allocation Technology (CAT) [69], in order to lock down portions of the LLC during execution. As for Flush+Reload, Zhou et al. [181] proposed a state machine which prevents a shared memory page being accessed by two security domains at the same time.

Beyond cache colouring, other forms of software partitioning have been proposed. Disabling page sharing [98] hinders attacks which depend on the availability of shared memory such as FLUSH+RELOAD and FLUSH+FLUSH [56]. Disabling SMT [17] prevents two hardware threads from exploiting contention among CPU-level resources such as execution units [12], the BTB [4], the RSB [25], or the MOB [140].

#### Hardware partitioning

Hardware cache partitioning consists in providing physical isolation among the working cache sets of each tenant [158, 118, 37]. For example, Wang and Lee [158] suggested a cache line locking mechanism, by means of an ISA extension, which prevents another process from evicting the cache line. An L tag indicates whether the cache line is locked, and an ID tag indicates the process to whom the cache line belongs. Fundamentally, hardware cache partitioning results in the same effects as software cache partitioning. The main difference lies in the deployment of the countermeasure. Therefore, hardware cache partitioning does not result in additional requirements. As for other components than caches, Wang et al. [154] proposed a time-division multiplexing technique in order to prevent the exploitation of the shared integrated memory controller. Similarly, Wang et al. [156] devised a prioritybased mechanism for the shared on-chip network. These approaches consist in scheduling accesses to the memory controller and the interconnect such that different security domains cannot conflict with each other. The effect of this countermeasure on DRAM-based covert channels that target external NUMA nodes remains an open-question.

Additionally, Gruss et al. [56] advocated making the rdtsc and clflush instructions privileged. While it would not completely close the covert channels which rely on these instructions, it would severely question the practicality of the attack. The adversary model (see Section 5.3.2) requires for the environment of the victim to be compromised with a malicious colluding software. The above-mentioned countermeasure would force this malware to be executing with privileges.

# Chapter 3

# On the Severity of Covert Channel Attacks in IaaS

| - | Υ. | _  |    |      | _  |    |   |

|---|----|----|----|------|----|----|---|

| • | 70 | 71 | ทา | Г. 6 | 21 | าา | S |

| 3.1 | Introduction                         | 54 |

|-----|--------------------------------------|----|

| 3.2 | Analysis of State-of-the-Art Attacks | 56 |

| 3.3 | Evaluation of Attacks                | 60 |

| 3.4 | Covert Channel Scoring System        | 69 |

| 3.5 | Evaluation Results                   | 71 |

| 3.6 | Summary                              | 73 |

|     |                                      |    |

A question that systematically arises from the audience when presenting a new leakage channel is "How practical is this attack?". Microarchitectural covert channels allegedly rely on a strong adversary model. As a result, security experts from industry tend to overlook malicious covert channels. This chapter intends to clarify the operational constraints associated to the deployment of such attacks in IaaS environments. Furthermore, a dedicated scoring framework that integrates operational constraints in the covert channel's performance score is devised.

## 3.1 Introduction