### Serial Biasing Technique for Rapid Single Flux Quantum Circuits

#### Ashish Shukla

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

2023

© 2023

Ashish Shukla

All Rights Reserved

#### **Abstract**

Serial Biasing Technique for Rapid Single Flux Quantum Circuits

Ashish Shukla

Superconductor electronics based on the Single Flux Quantum (SFQ) technology are considered a strong contender for the 'beyond CMOS' future of digital circuits because of the high speed and low power dissipation associated with them. In fact, digital operations beyond tens of GHz have been routinely demonstrated in the SFQ technology. These circuits have widespread applications such as high-speed analog-to-digital conversion, digital signal processing, high-speed computing, and in emerging topics such as control circuitry for superconducting quantum computing.

Rapid Single Flux Quantum (RSFQ) circuits have emerged as a promising candidate within the SFQ technology, with information encoded in picosecond wide, milli-volt voltage pulses. As is the case with any integrated circuit technology, scalability of RSFQ circuits is essential to realizing their applications. These circuits, based on the Josephson junction, require a DC bias current for the correct operation. The DC bias current requirement increases with circuit complexity, and this has multiple implications on circuit operation. Large currents produce magnetic fields that can interfere with logic operation. Furthermore, the heat load delivered to the

superconducting chip also increases with current which could result in the circuit becoming 'normal' and not superconducting. These problems make reduction of the bias current necessary.

Serial Biasing (SB) is a bias current reduction technique, that has been proposed in the past. In this technique, a digital circuit is partitioned into multiple identical islands and bias current is provided to each island in a serial manner. While this scheme is promising, there are multiple challenges such as design of the driver-receiver pair circuit resulting in robust and wide operating bias margins, current management on the floating islands, etc.

This thesis investigates SB in a systematic manner, focusing on the design and measurement of the fundamental components of this technique with an emphasis on reliability and scalability. It presents works on circuit techniques achieving high speed serially biased RSFQ circuits with robust operating margins and the experimental evidence to support the ideas. It develops a framework for serial biasing that could be used by electronic design tools to automate design and synthesis of complex RSFQ circuits. It also investigates Passive Transmission Lines (PTLs) for use as passive interconnects between library cells in a complex design, reducing the DC bias current required by the active circuitry.

## **Table of Contents**

| List of Fig | guresv                                                                           |

|-------------|----------------------------------------------------------------------------------|

| List of Ta  | bles xvi                                                                         |

| Acknowle    | edgmentsxix                                                                      |

| Chapter 1   | : Introduction                                                                   |

| 1.1         | Overview1                                                                        |

| 1.2         | Fundamentals of Superconductivity                                                |

| 1.3         | Josephson Junctions2                                                             |

| 1.3         | 3.1 Basic Operation of a Josephson Junction                                      |

| 1.3         | 3.2 Circuit Model and Dynamics of Josephson Junctions                            |

| 1.3         | 3.3 Superconducting Quantum Interference Device (SQUID)                          |

| 1.4         | Rapid Single Flux Quantum Circuits                                               |

| 1.4         | 4.1 Single Flux Quantum (SFQ) Pulses                                             |

| 1.4         | 4.2 Josephson Transmission Line (JTL)                                            |

| 1.4         | 4.3 D Flip Flop                                                                  |

| 1.5         | Applications and Challenges of RSFQ circuits14                                   |

| 1.6         | Prior Work on Serial Biasing16                                                   |

| 1.7         | Contributions of this Thesis                                                     |

| 1.7         | 7.1 Current Management Techniques for Serially Biased RSFQ circuits18            |

| 1.7         | 7.2 Driver-Receiver Pair (DRP) Circuit for Serial Biasing                        |

| 1.7         | 7.3 Serial Biasing Technique for Electronic Design Automation in RSFQ Circuits19 |

| 1.7         | 7.4 Passive Transmission Lines for Serially Biased RSFQ Circuits20               |

| 1.8    | Org      | ganization of the thesis                                                  | 21 |

|--------|----------|---------------------------------------------------------------------------|----|

| Chapte | er 2: Pu | lse Interfaces and Current Management Techniques for Serially Biased RSFQ |    |

| Circui | ts       |                                                                           | 23 |

| 2.1    | Intr     | oduction                                                                  | 23 |

| 2.2    | Gra      | pevine Approach                                                           | 26 |

|        | 2.2.1    | General Grapevine Biasing Design                                          | 26 |

|        | 2.2.2    | Going Through a Hole in the Ground Plane                                  | 28 |

|        | 2.2.3    | Example Circuits and DRP Design                                           | 29 |

| 2.3    | Tes      | ting of the DDF Circuit                                                   | 30 |

|        | 2.3.1    | Test Structure Design                                                     | 30 |

|        | 2.3.2    | DDF Test Results                                                          | 32 |

| 2.4    | Tes      | ting of 3x3 Matrix of 3-to-2 Counters                                     | 34 |

|        | 2.4.1    | Test Structure Design                                                     | 34 |

|        | 2.4.2    | Test Results                                                              | 35 |

| 2.5    | Dis      | cussion                                                                   | 40 |

| 2.6    | Cor      | nclusions                                                                 | 41 |

| Chapte | er 3: 60 | -GHz Single Flux Quantum Pulse Transfer Circuit for Serial Biasing        | 43 |

| 3.1    | Intr     | oduction                                                                  | 43 |

| 3.2    | Dri      | ver-Receiver Pair                                                         | 46 |

|        | 3.2.1    | Schematic, Layout, and Cross-Section                                      | 46 |

|        | 322      | Simulation Results                                                        | 48 |

|        | 3.2.2    | DRP Test Structures                                                      | 50 |

|--------|----------|--------------------------------------------------------------------------|----|

| 3.3    | Tes      | t Results                                                                | 51 |

| 3.4    | EM       | Simulations                                                              | 57 |

|        | 3.4.1    | Simulating the DRP Test Structure                                        | 57 |

|        | 3.4.2    | Current Distribution in the Source and Drain Vias                        | 61 |

|        | 3.4.3    | Simulating Position of Drain vias in the GV Biasing Case                 | 65 |

|        | 3.4.4    | Simulating M6 Extension over M4-to-M5 Vias                               | 68 |

| 3.5    | Dise     | cussion                                                                  | 71 |

|        | 3.5.1    | Model-to-Hardware Correlation                                            | 71 |

|        | 3.5.2    | 80-Island Experiment and Future Steps                                    | 76 |

| 3.6    | Con      | clusion                                                                  | 78 |

| Chapto | er 4: Se | rial Biasing Technique for Electronic Design Automation in RSFQ Circuits | 79 |

| 4.1    | Intr     | oduction                                                                 | 79 |

| 4.2    | Des      | ign Primitives Required for Serial Biasing                               | 81 |

|        | 4.2.1    | Grapevine Biasing for the MIT-LL SFQ5ee Fabrication Node                 | 82 |

|        | 4.2.2    | DRP's Core Design                                                        | 83 |

|        | 4.2.3    | Horizontal and Vertical Bias JTLs                                        | 85 |

|        | 4.2.4    | Horizontal and Vertical Composite DRPs                                   | 87 |

| 4.3    | Ass      | embling a Serially Biased Circuit                                        | 90 |

|        | 4.3.1    | Blocks Required                                                          | 90 |

|        | 4.3.2    | Test Circuit Design                                                      | 92 |

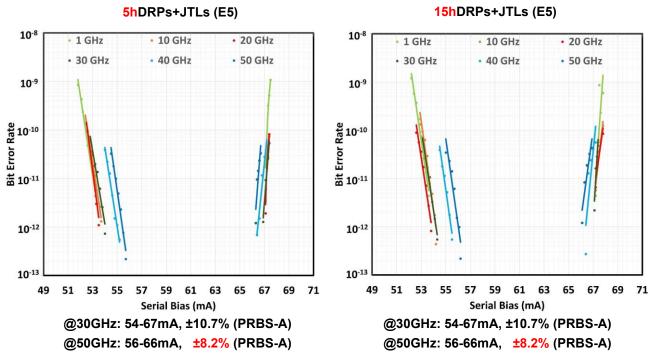

| 4.4   | Mea      | asurement Results                                             | 94  |

|-------|----------|---------------------------------------------------------------|-----|

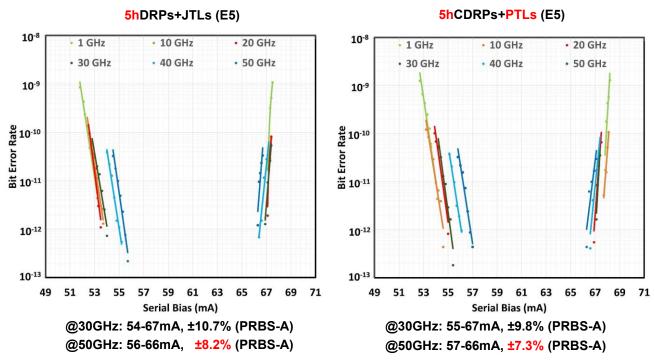

|       | 4.4.1    | Horizontal and Vertical CDRPs                                 | 94  |

|       | 4.4.2    | Comparing Independently Tested Experiments                    | 96  |

|       | 4.4.3    | Crosstalk Experiments                                         | 99  |

|       | 4.4.4    | Different Wafer Locations                                     | 102 |

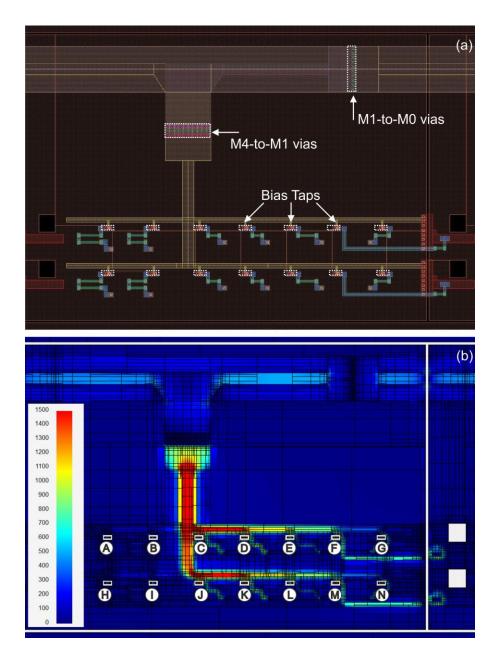

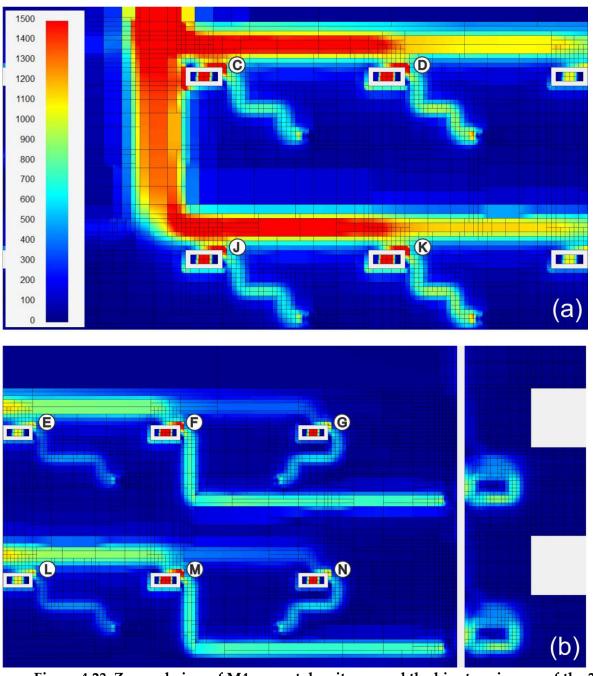

| 4.5   | Ele      | ctromagnetic Simulations                                      | 104 |

|       | 4.5.1    | 2-island CDRP Simulation                                      | 104 |

|       | 4.5.2    | Simulating Vertical M0 Extension over M4-to-M1 Vias           | 109 |

|       | 4.5.3    | Simulating Horizontal M0 and M1 Extensions over M1-to-M0 vias | 111 |

|       | 4.5.4    | Double Current Injection                                      | 113 |

| 4.6   | Dis      | cussion                                                       | 115 |

| 4.7   | Cor      | nclusion                                                      | 118 |

| Chapt | er 5: Pa | ssive Transmission Lines for Serially Biased RSFQ Circuits    | 119 |

| 5.1   | Intr     | oduction                                                      | 120 |

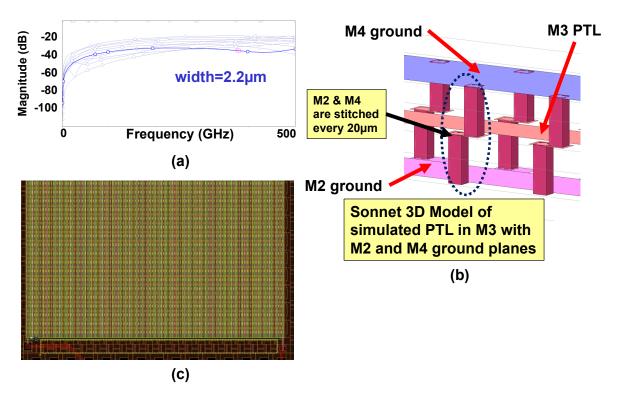

| 5.2   | PTI      | L Characterization                                            | 122 |

|       | 5.2.1    | Electromagnetic simulations to establish PTL width            | 122 |

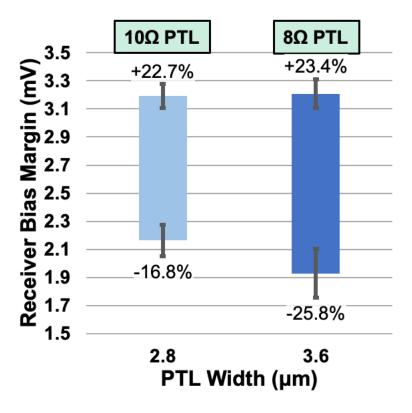

|       | 5.2.2    | PTL Receiver Bias Margins as a function of Impedance          | 124 |

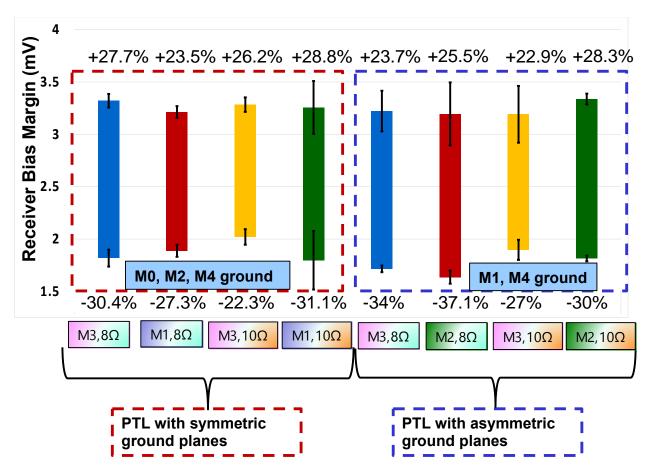

|       | 5.2.3    | Receiver Bias Margins for the 2 PTL architectures             | 125 |

| 5.3   | PTI      | L Circuit Simulations                                         | 126 |

|       | 5.3.1    | Adoption of Multi-Layer Transmission Line Model for PTLs      | 126 |

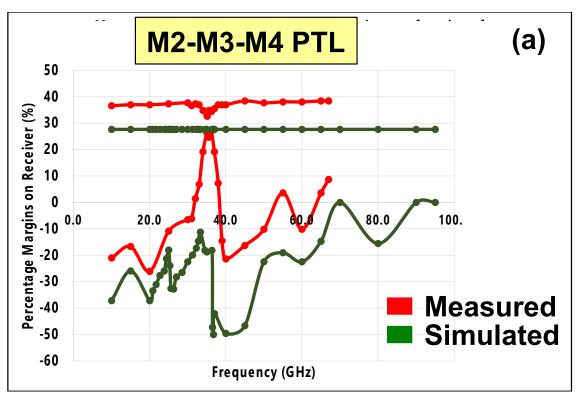

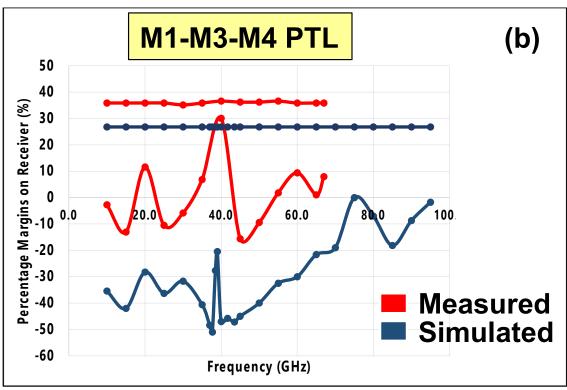

|       | 5.3.2    | Model to Hardware Correlation                                 | 129 |

| 5.4   | Cor      | nclusion                                                      | 131 |

| Conclusion | 132 |

|------------|-----|

|            |     |

| References | 135 |

# **List of Figures**

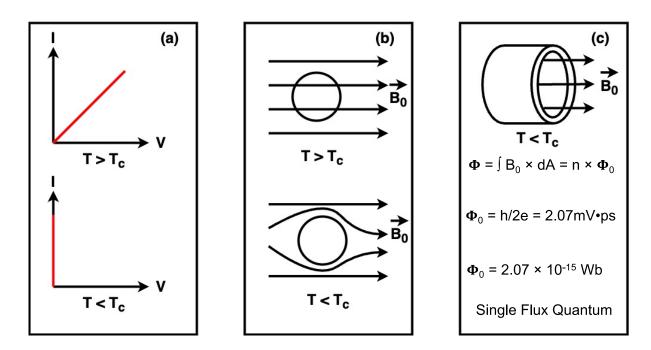

| 1.1 | Resistance drops to zero below the critical temperature (T <sub>c</sub> ) in superconductors (a). The     |

|-----|-----------------------------------------------------------------------------------------------------------|

|     | Meissner effect is illustrated in (b) where the magnetic field, below T <sub>c</sub> is expelled from the |

|     | interior of the superconductor. (c) A magnetic flux inside a superconducting loop must be                 |

|     | quantized in modulo $\Phi_0$                                                                              |

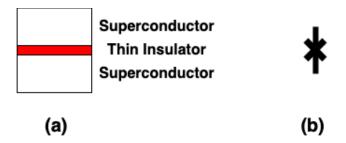

| 1.2 | Josephson junction (JJ) geometry (cross-section) shown in (a). The typical JJ symbol is                   |

|     | shown in (b)5                                                                                             |

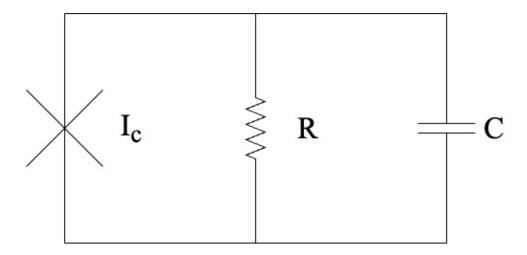

| 1.3 | RCSJ circuit model of the Josephson junction                                                              |

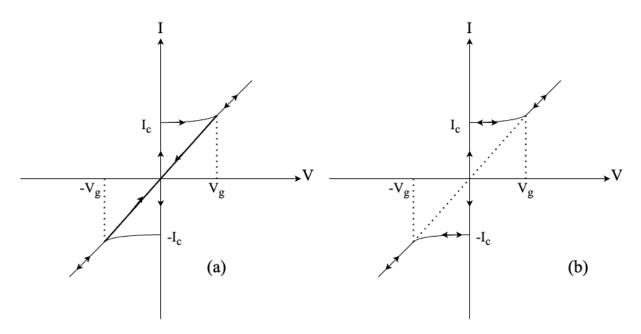

| 1.4 | The hysteretic I-V characteristic for the underdamped JJ which has $\beta_c >> 1$ . A non-                |

|     | hysteretic I-V behavior is observed for the overdamped JJ, with much smaller $\beta_c$ (less than         |

|     | or equal to 1)                                                                                            |

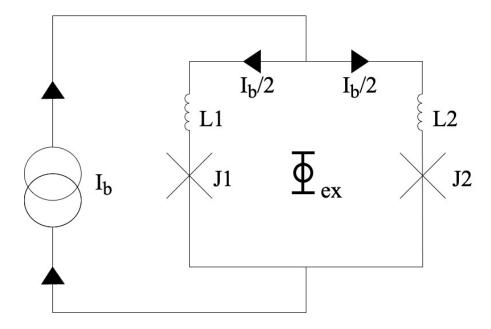

| 1.5 | DC SQUID comprising superconducting loop interrupted by JJs J1 and J28                                    |

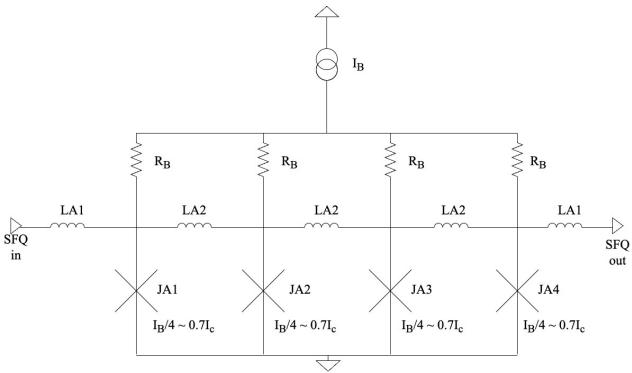

| 1.6 | Josephson Transmission Line comprising 4 junctions with $\beta_c \sim 1$ and inductors for                |

|     | interconnections. Upon receiving an SFQ voltage pulse as an input, the JJs switch in the                  |

|     | order JA1-JA2-JA3-JA4, and then the pulse exits the JTL circuit                                           |

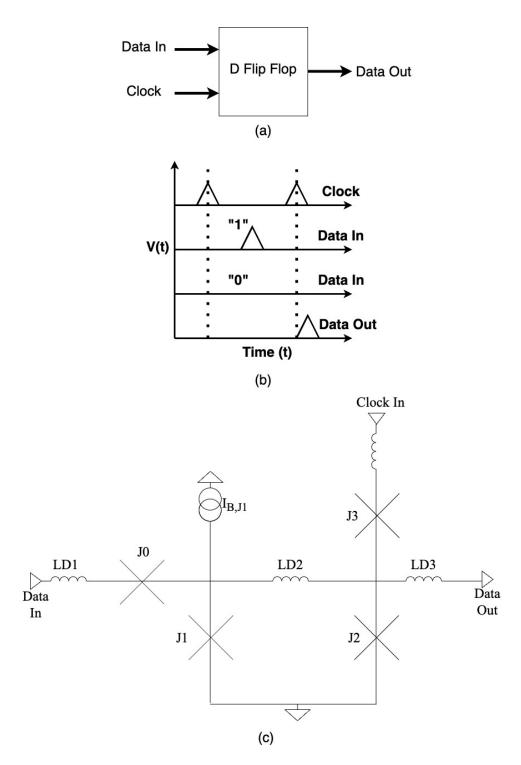

| 1.7 | (a) RSFQ D Flip-Flop (DFF) block diagram showing the input output connections. (b)                        |

|     | Presence of a pulse in a clock window is interpreted as logic "1", the absence is a "0". Note             |

|     | the clock-to-data out delay between the SFQ pulses. The circuit schematic of the DFF is                   |

|     | shown in (c)                                                                                              |

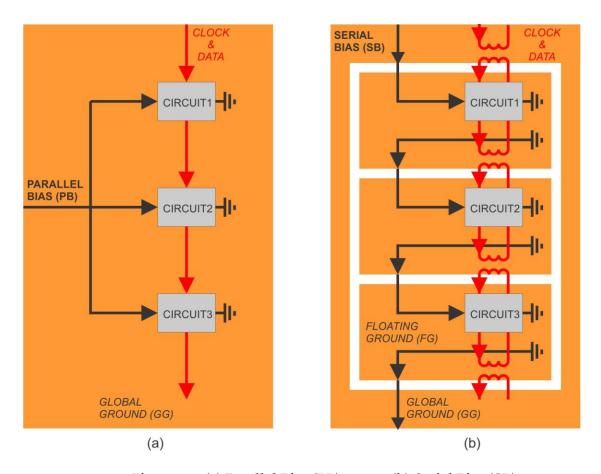

| 2.1 | (a) Parallel Bias (PB) versus (b) Serial Bias (SB)25                                                      |

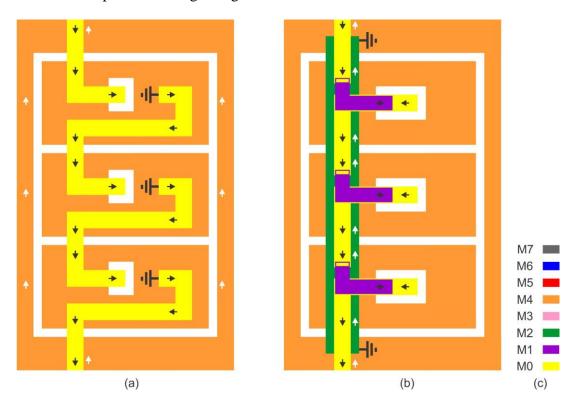

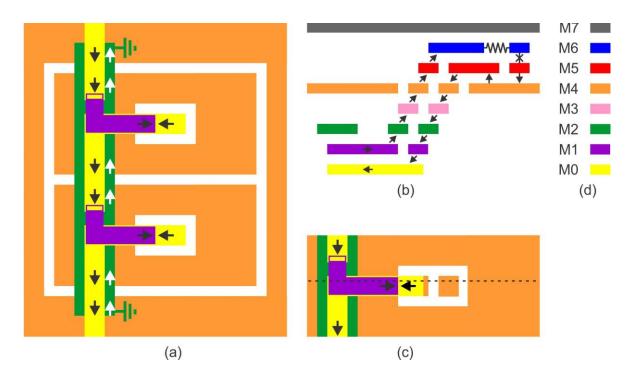

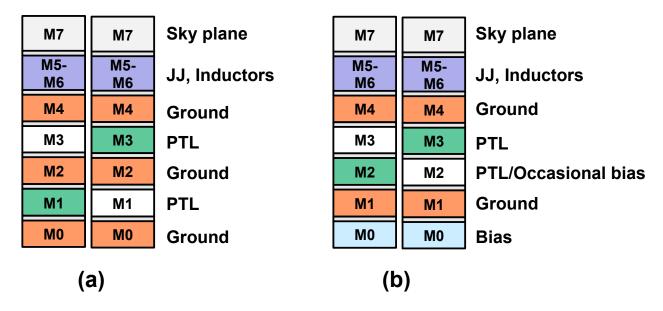

| 2.2 | Straightforward (a) versus Grapevine Approach (b) for MIT-LL SFQ5ee metal stack (c).                      |

|     | Black and white arrows are used to depict bias current and return current respectively26                  |

| 2.3  | Straightforward (a) versus Grapevine Approach (b) for going through a hole in the ground       |

|------|------------------------------------------------------------------------------------------------|

|      | plane for MIT-LL metal layers stack (c). Not all layers are shown in (d) and (e) to simplify   |

|      | visualization. Note that any metal layer to carry "current-in" has a dedicated metal layer to  |

|      | carry "current-out". Cross-sections (a) and (b) correspond to dashed lines in (d) and (e)      |

|      | respectively                                                                                   |

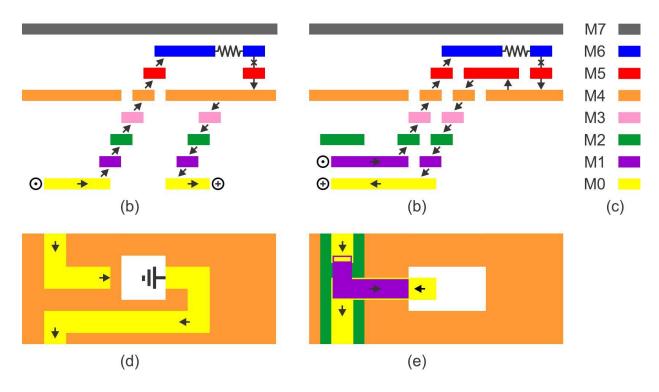

| 2.4  | Chip layout consisting of the PB, SB1, and SB4 test structures (see text for details). The     |

|      | chip was fabricated at MIT-LL using SFQ5ee 10 kA/2Ω fab node31                                 |

| 2.5  | Test structure consisting of 4 serially biased DDF slices on 4 islands (SB4)32                 |

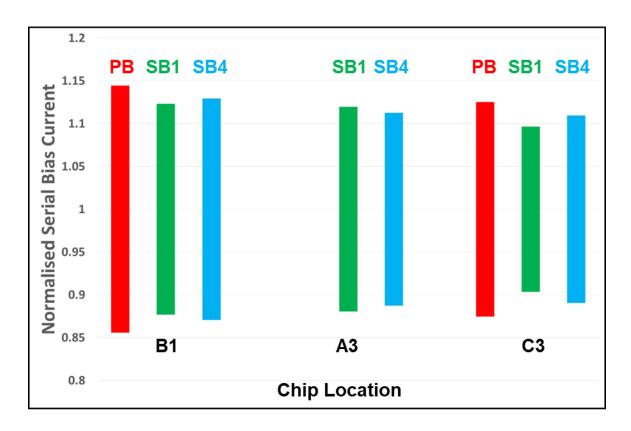

| 2.6  | LF bias margins for PB, SB1, and SB4 test structures for locations B1, A3 and C333             |

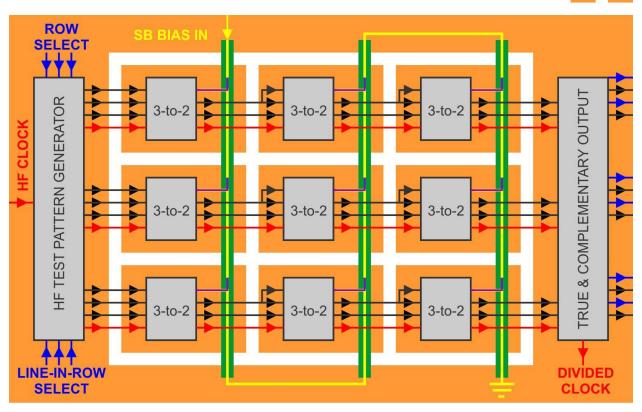

| 2.7  | Block diagram of the serially biased 3x3 matrix of 3-to-2 counters. The MSB output of the      |

|      | 1st 3-to-2 circuit is split in two and provided to two of the unweighted inputs of the         |

|      | subsequent 3-to-2 circuit. Similar MSB splitting is observed for the 3rd in a row 3-to-2       |

|      | circuit as well                                                                                |

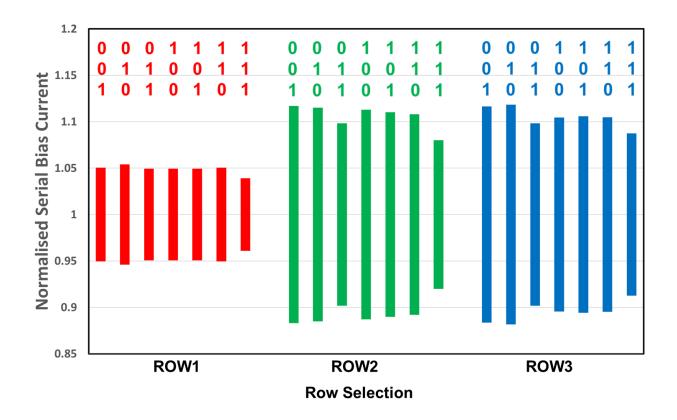

| 2.8  | LF Serial Bias Margins for 7 input patterns, for all rows tested one at a time. The input (for |

|      | e.g., '001') is addressed as 'Top (T)' 'Middle (M)' 'Bottom (B)' in reference to the physical  |

|      | layout location of the inputs on the 3-to-2 circuit (compare with Figure 2.7)36                |

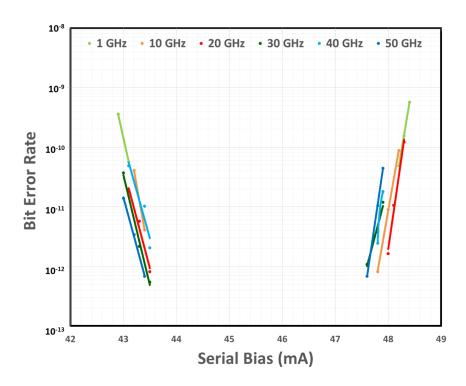

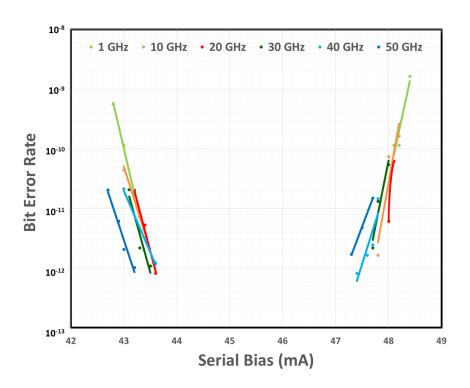

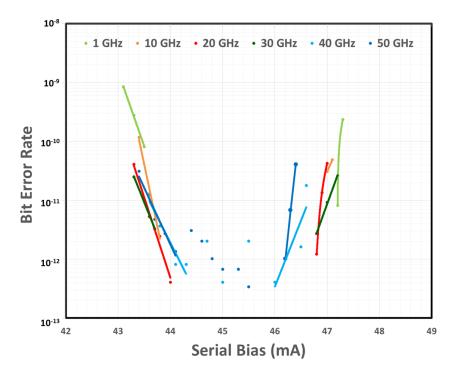

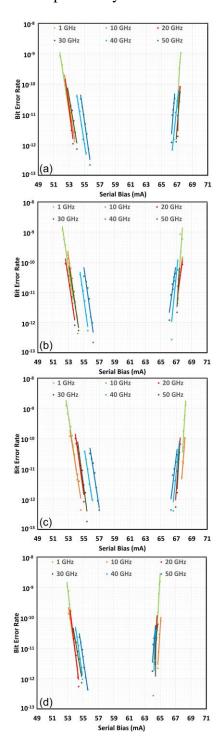

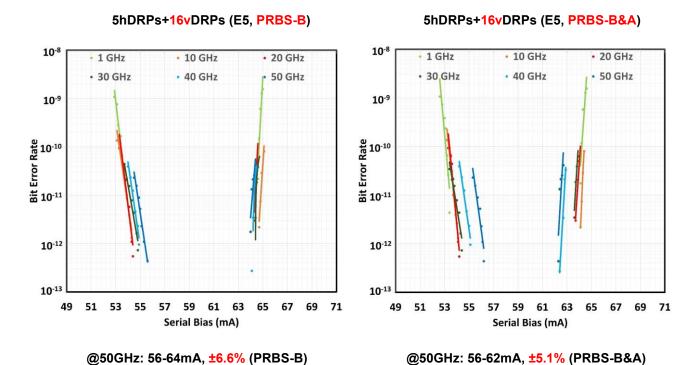

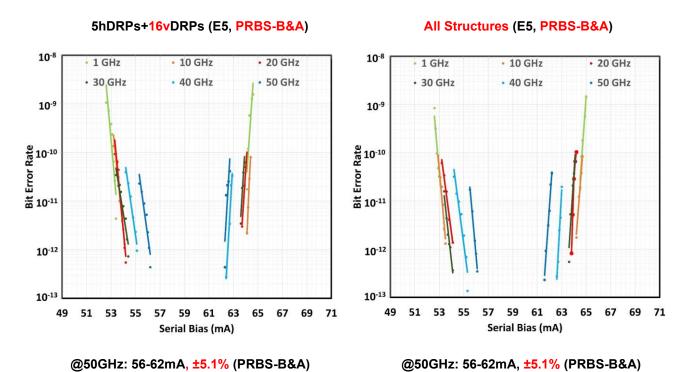

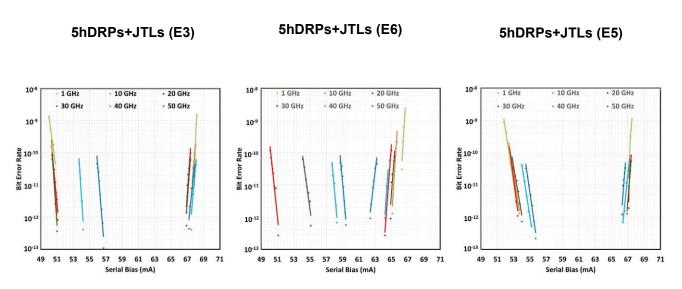

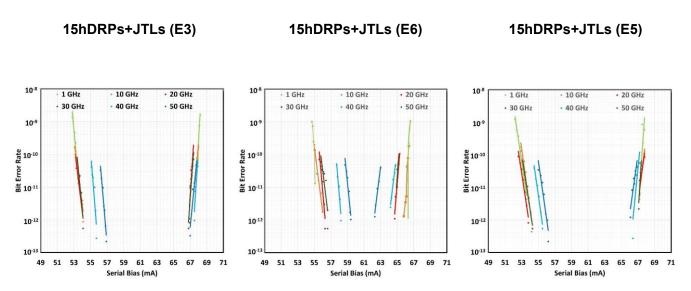

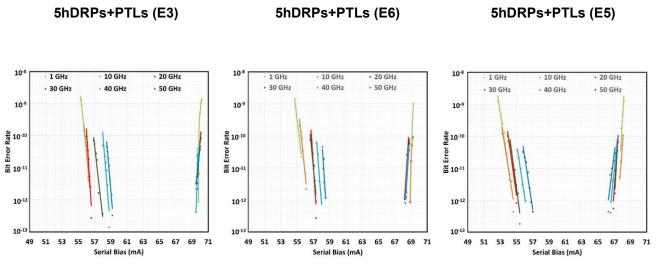

| 2.9  | BER versus serial bias current for the '100' input pattern. Frequency is swept from 1 GHz      |

|      | to 50 GHz. Operational margins do not depend strongly on the clock frequency37                 |

| 2.10 | BER versus serial bias current for the '101' input pattern. Frequency is swept from 1 GHz      |

|      | to 50 GHz                                                                                      |

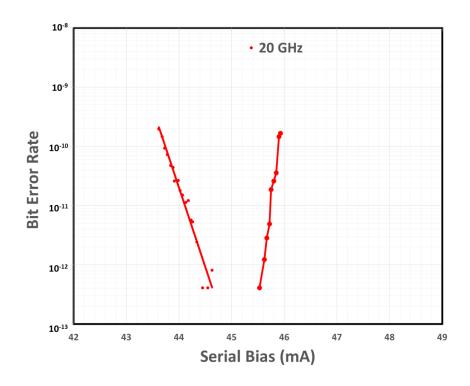

| 2.11 | BER versus serial bias current for the '111' input pattern. Frequency is swept from 1 GHz      |

|      | to 50 GHz38                                                                                    |

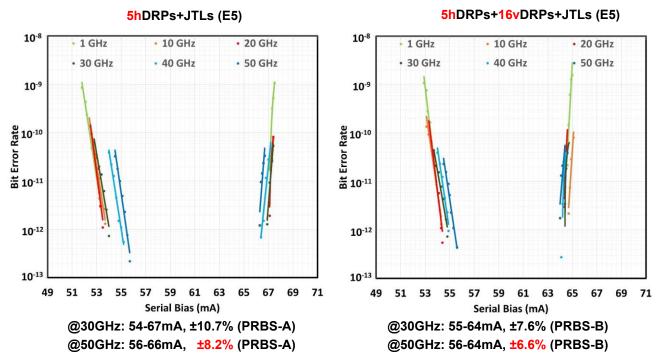

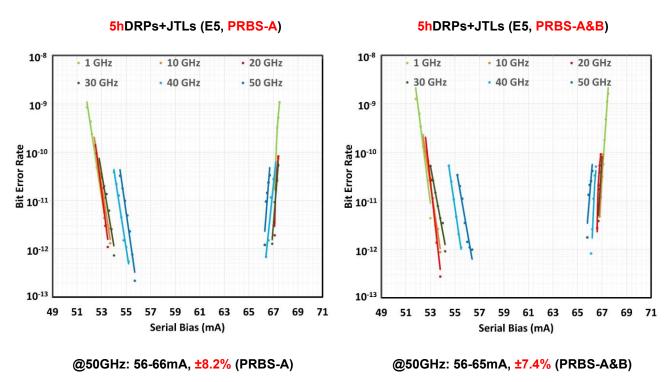

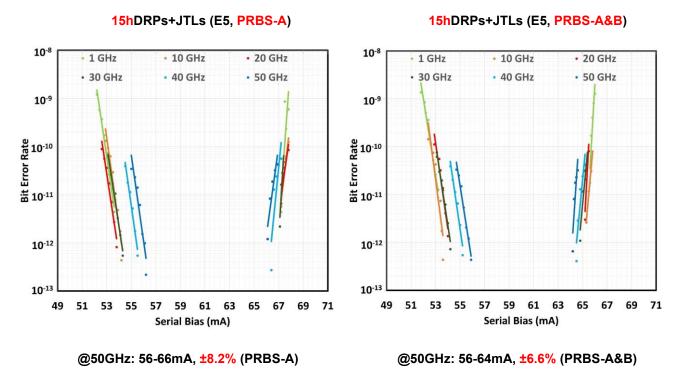

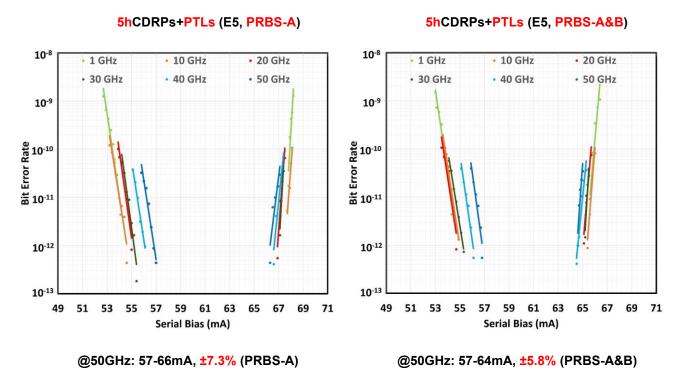

| 2.12 | BER versus serial bias current for the '111' input pattern for simultaneous operation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | at 20 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

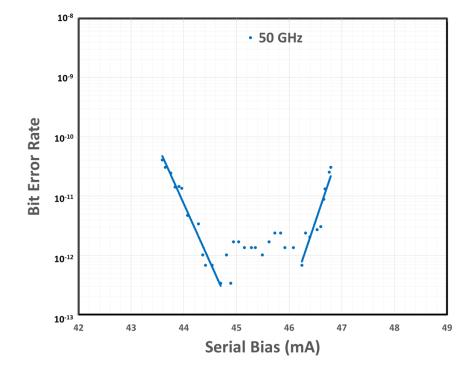

| 2.13 | BER versus serial bias current for the '001' input pattern for simultaneous operation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | at 50 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

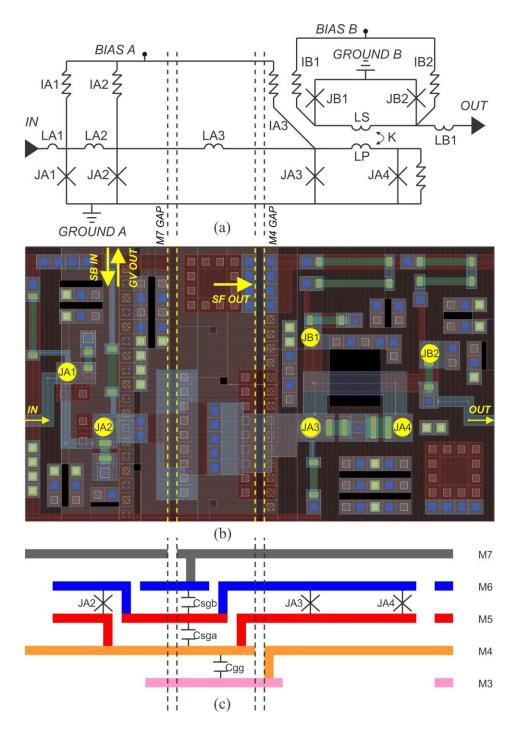

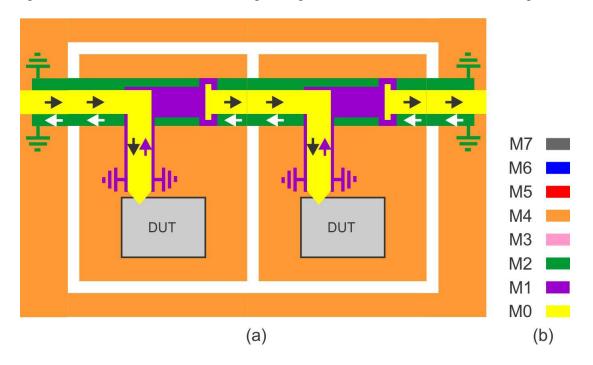

| 3.1  | (a) The grapevine (GV) biasing technique is implemented on two serially biased islands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | using (d) the MIT-LL SFQ5ee metal layers' stack. Any bias-line-in has a dedicated ground-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | line-out to localize the magnetic fields in between the two metal layers and control the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | return current distribution. The dedicated pair of metal paths for current transfer through                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | the M4 hole is formed by means of the double waterfall structure (b). The cross-section in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | (b) is made along the dashed line in (c). Not all layers are shown in (c) to avoid blocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | the view of the M0 and M1 metal layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

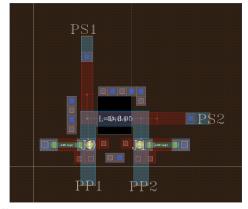

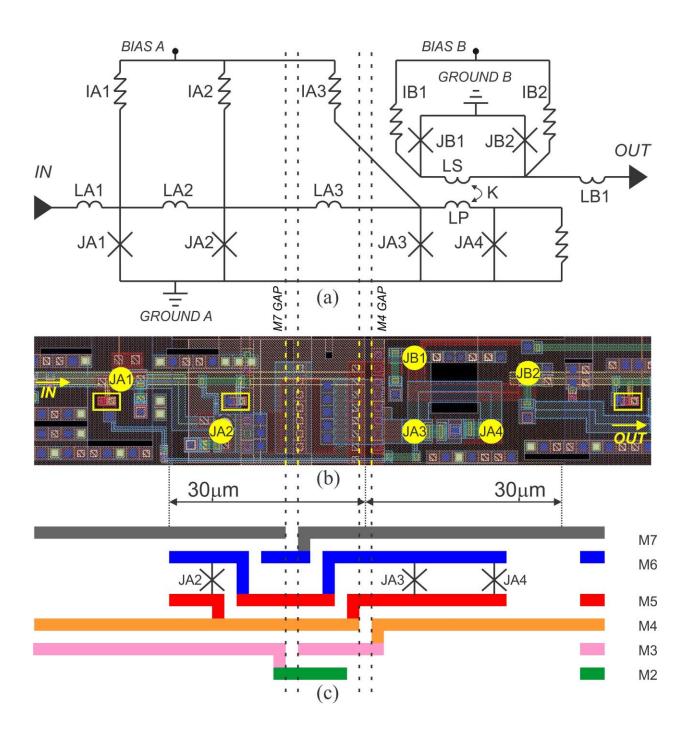

| 3.2  | (a) The DRP schematic (a) comprises the driver's junctions on ground A and the receiver's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | junctions on ground B: JA1=250μA, JA2=350μA, JA3=488μA, JA4=158μA, JB1=94μA,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | $JB2 = 131 \mu A, IA1 = 175 \mu A, IA2 = 245 \mu A, IA3 = 344 \mu A, IB1 = 71 \mu A, IB2 = 100 \mu A, LA1 = 2 pH, LA1 = 100 \mu A, LA2 = 100 \mu A, LA2 = 100 \mu A, LA3 = 10$ |

|      | LA2=2.7pH, LA3=2.1pH, LB1=2.7pH, LP=LS=5.8pH, and k=0.53. The DRP layout (b) is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | shown for MIT-LL SFQ5ee fab node. The shown layout occupies the area of 40μm x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 65μm. All inductances, including the transformer with M4 and M7 holes, were calculated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | using InductEx software. The simplified cross-section (c) is made along the line JA2-JA3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | JA4 in (b)47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

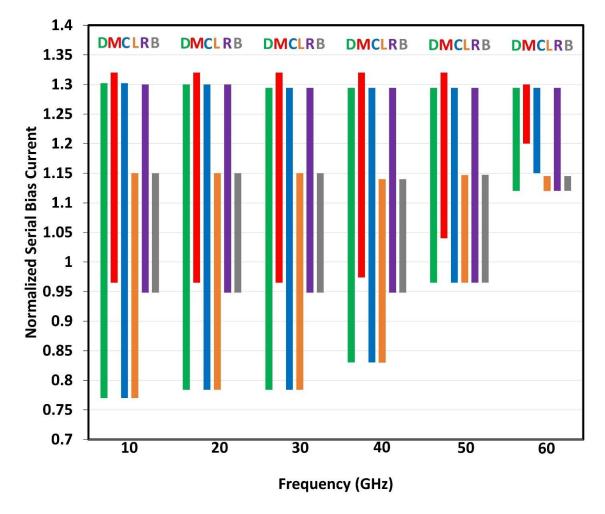

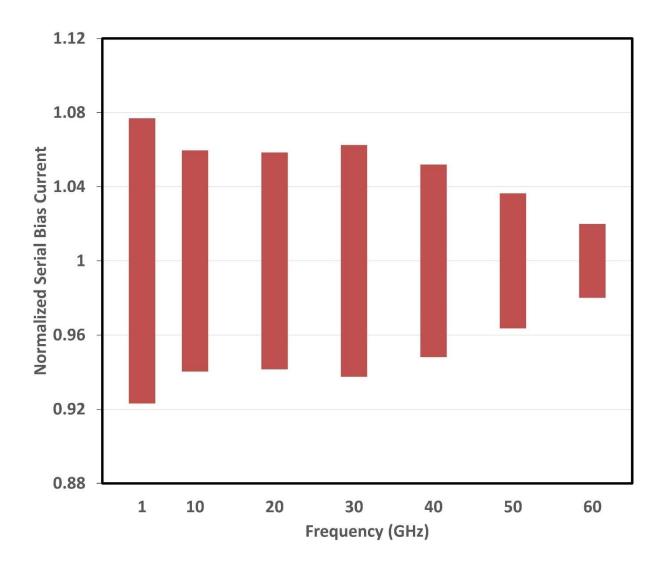

| 3.3  | (a) Simulated margins for the normalized SB current as a function of the input frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | for different configurations of DRP parameters. The 'D' margins correspond to the default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | set of parameters. To calculate the 'M' margins, the mutual inductances in all DRPs were                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | reduced by 20%. The 'C' margins are calculated considering parasitic capacitors placed in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| all DI     | RPs. The 'L' and 'R' margins are calculated for counterclockwise and clockwise flux              |

|------------|--------------------------------------------------------------------------------------------------|

| trappe     | ed in a transformer in a single DRP. The 'B' margins correspond to two fluxes of both            |

| polari     | ities trapped in 2 DRPs49                                                                        |

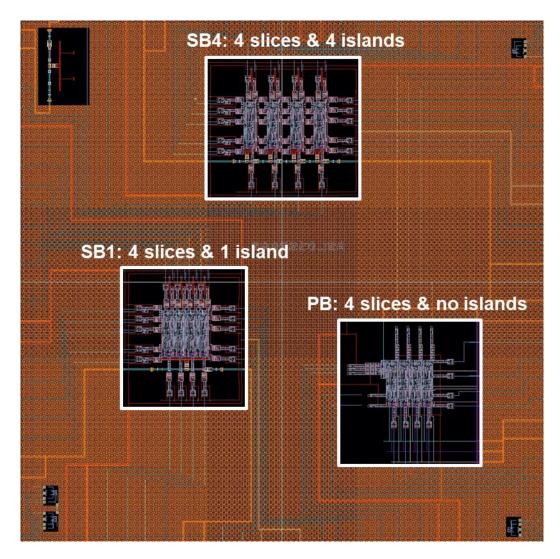

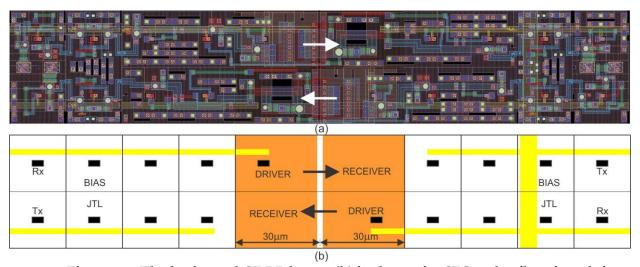

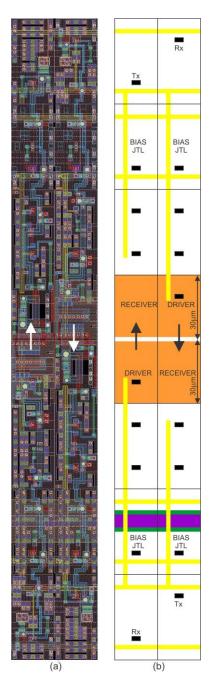

| 3.4 (a) Ty | wo 5-island test structures biased according to SF (a) and GV (b) bias schemes. Both             |

| test st    | ructures are identical except for how the SB bias current injection and extraction are           |

| organ      | ized51                                                                                           |

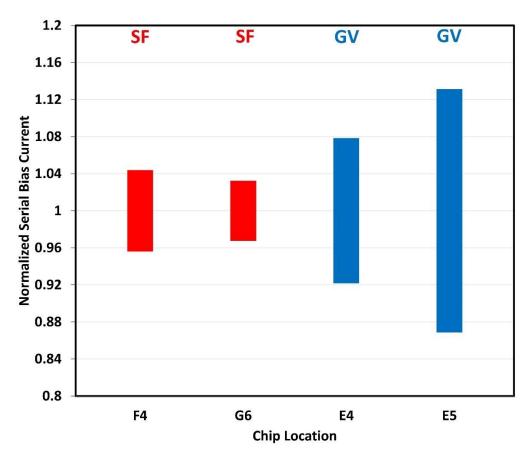

| 3.5 LF bi  | ias margins for the SF (red) and GV (blue) test structures across different chip                 |

| locati     | ons52                                                                                            |

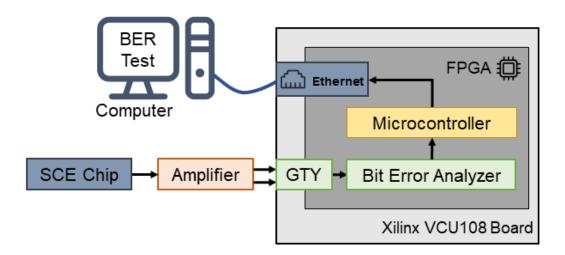

| 3.6 Expe   | rimental setup and block diagram of the FPGA-based Bit Error Rate Tester (BERT).                 |

| The c      | computer allows the user to start a BER measurement and visualize the BER during                 |

| the ex     | xperiment53                                                                                      |

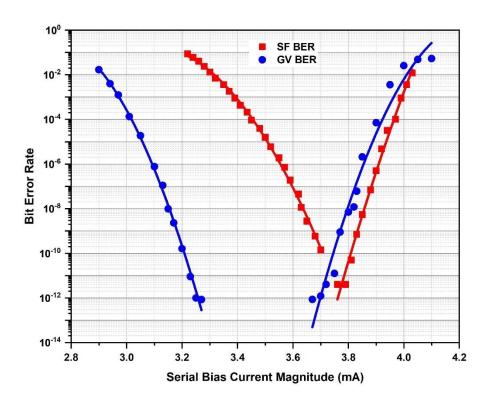

| 3.7 BER    | curves versus serial bias current at 10.16 GHz for the 2 biasing schemes. The GV                 |

| (blue)     | ) margins are wider compared to the SF (red) case and reach the BER level of 10 <sup>-12</sup> . |

|            | 55                                                                                               |

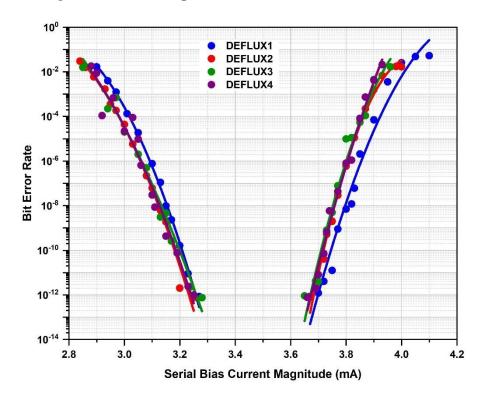

| 3.8 BER    | curves for the GV test structure after 4 deflux procedures55                                     |

| 3.9 Norm   | nalized serial bias current versus clock frequency for the GV test structure. Data are           |

| obtair     | ned by running the output waveform stability test to maintain the BER level better               |

| than 1     | 10 <sup>-12</sup> (see text for details)56                                                       |

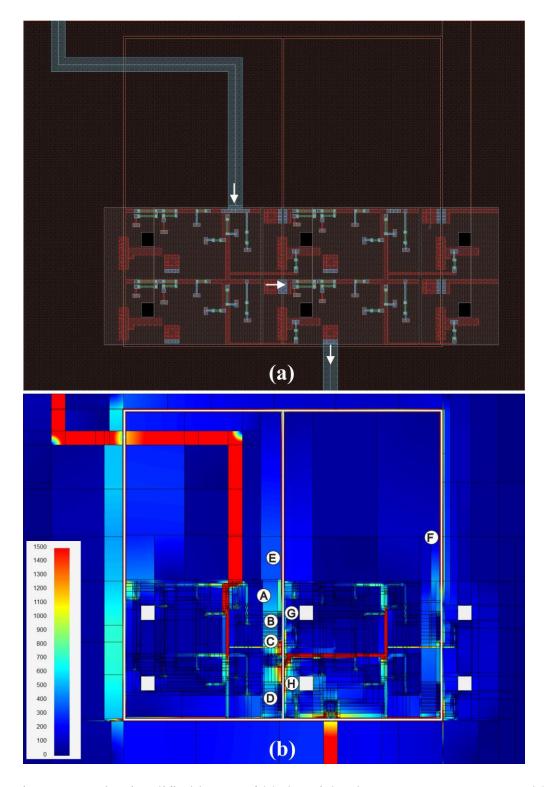

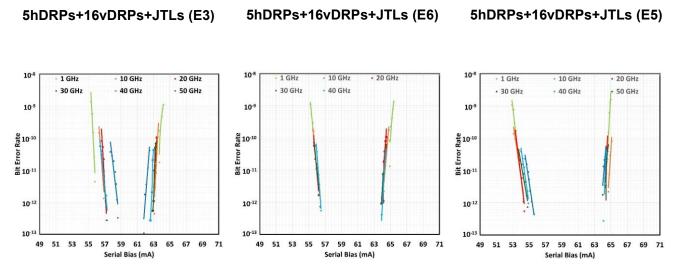

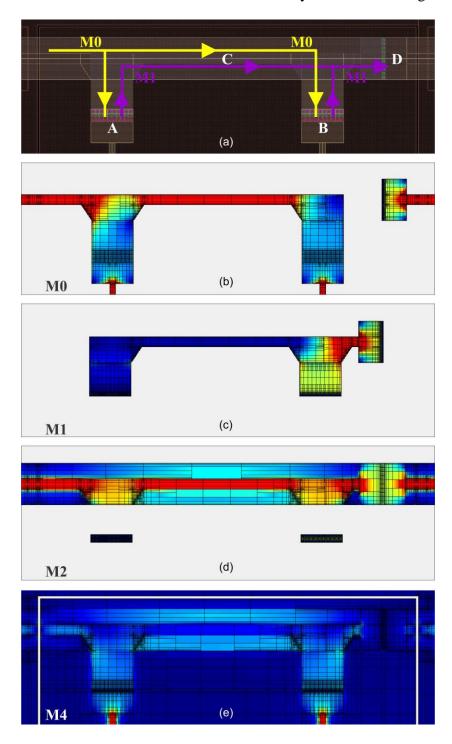

| 3.10 The s | implified layout of (a) the 2-island SF DRP test structure and (b) the calculated current        |

| distril    | bution in the M4 ground plane. The bias current is injected into the first island,               |

| transf     | Ferred to, and extracted from the second island as marked by arrows in (a). The red              |

| straig     | ht segments in (b) correspond to the elements of the power grid where the bias current           |

| was e      | xpected to accumulate58                                                                          |

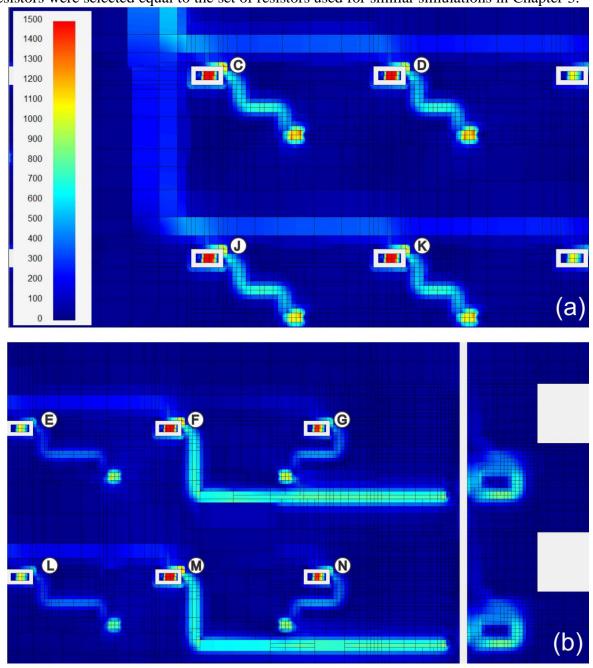

| The simplified layout of (a) the 2-island GV DRP test structure and (b) the calculated             |

|----------------------------------------------------------------------------------------------------|

| current distribution in the M4 ground plane. Any metal layer used to carry the incoming            |

| current has a corresponding dedicated metal layer to carry the outgoing current as marked          |

| by the arrows in (a). For comparison, the labeled locations in (b) are identical to those          |

| selected in the SF case (Figure 3.10(b))                                                           |

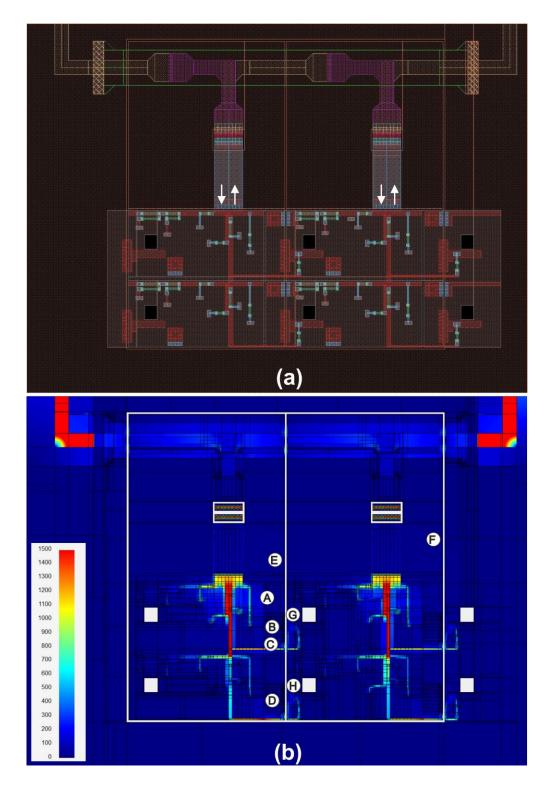

| Layouts of the serially biased island with the GV(a) and SF (b) biasing. In both cases, bias       |

| current enters and exits the island from the top and bottom (white arrows). The load circuit       |

| consists of 5 identical resistors connected to M4 ground. In contrast to the dedicated pairs       |

| of layers in the GV case (a), the metal layers for current flowing in and out do not overlap       |

| for the SF biasing (b)62                                                                           |

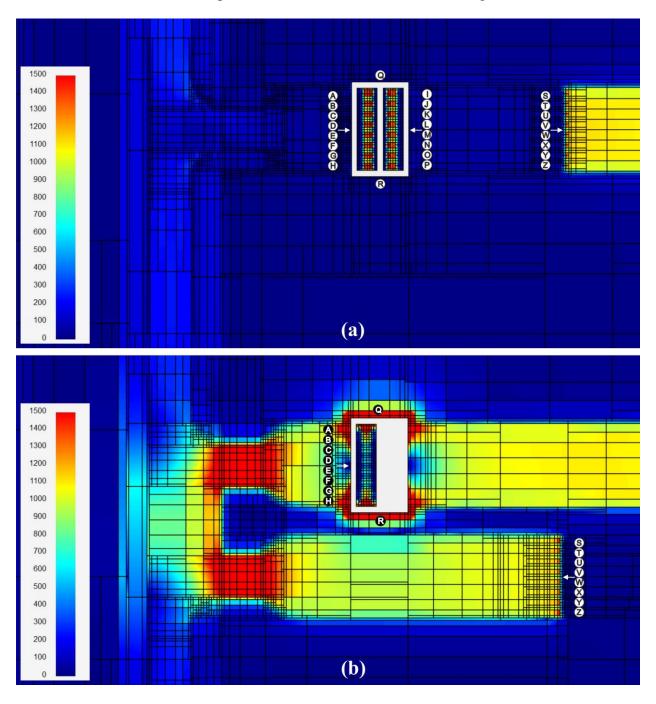

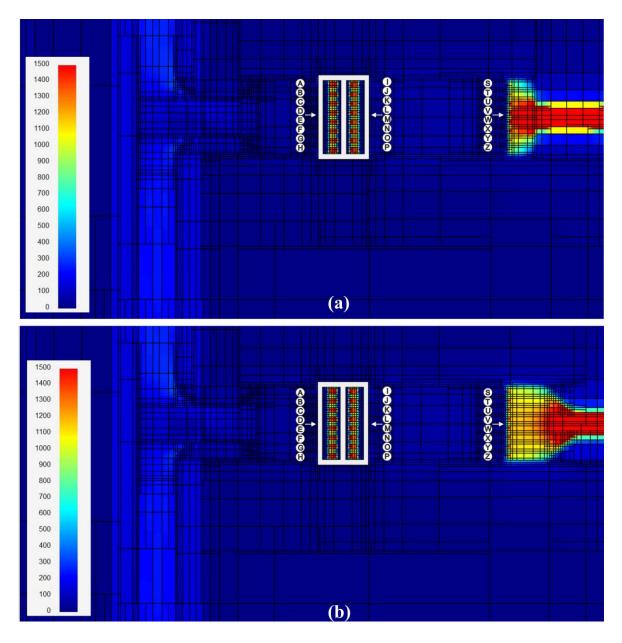

| The current density distribution in the M4 ground layer is shown for GV (a) and SF (b)             |

| biasing cases. The regions shown correspond to the dashed rectangles marked in Figure              |

| 3.12(a) and Figure 3.12(b)63                                                                       |

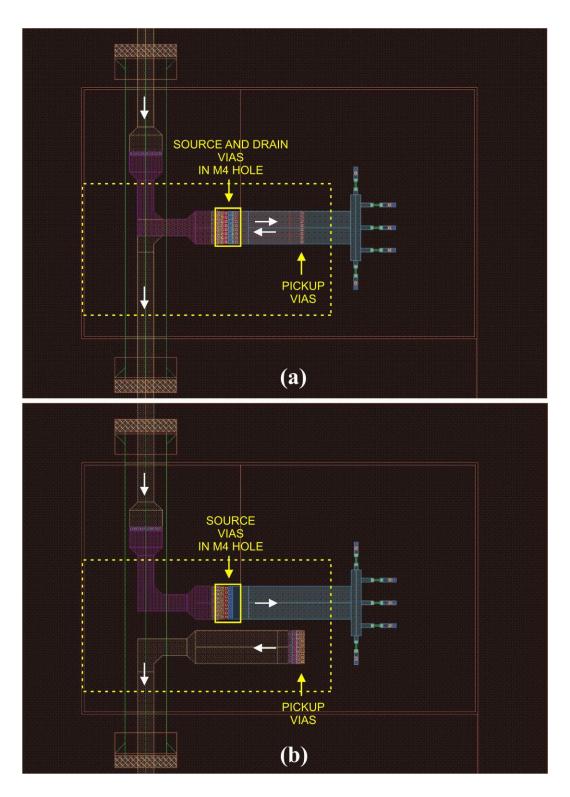

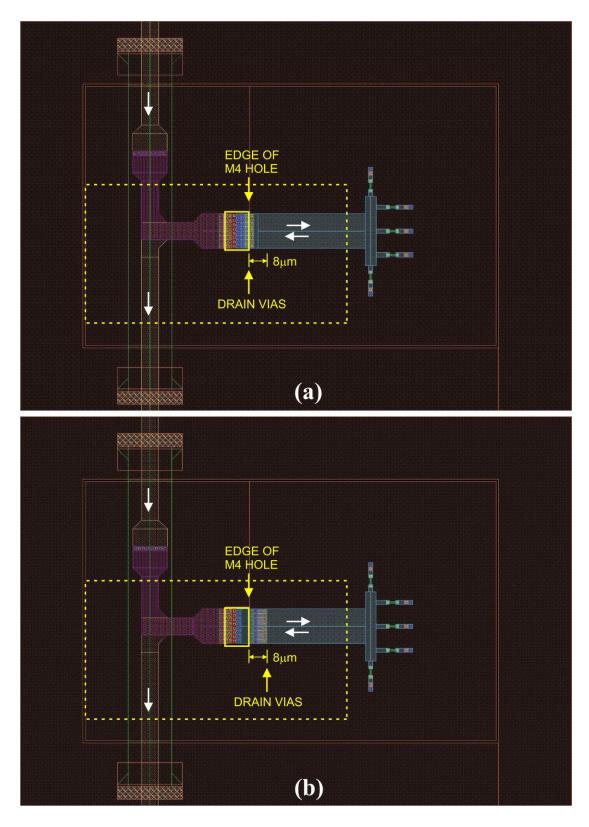

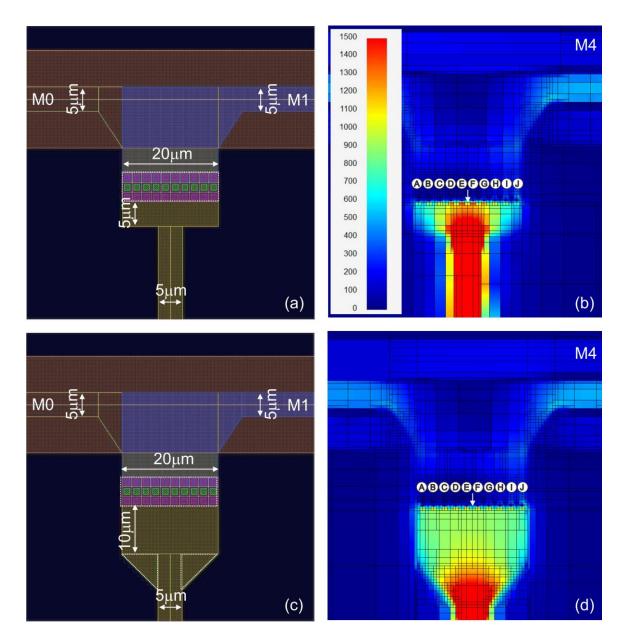

| Layouts of serially biased islands with GV biasing. In (a), the drain vias are located at the      |

| edge of the hole, and in (b), they are located away from the hole at 8 µm distance66               |

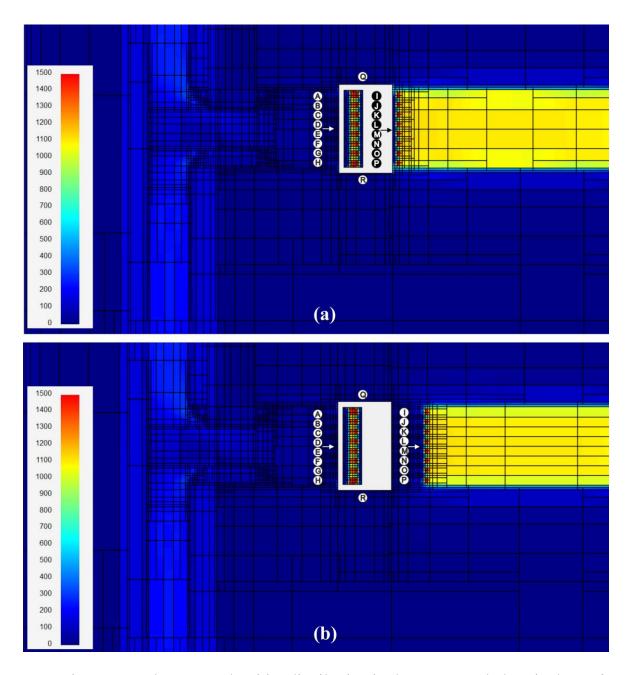

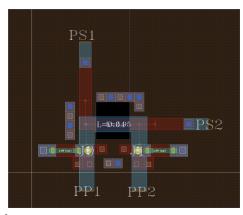

| The current density distribution in the M4 ground plane is shown for different locations of        |

| the drain vias in the GV biasing case. The M4-to-M0 drain vias (I-P) are moved from the            |

| hole to the edge of the M4 ground (a) or placed 8 µm away from the hole edge. The regions          |

| shown correspond to the dashed rectangles marked in Figures 3.14(a) and 3.14(b)67                  |

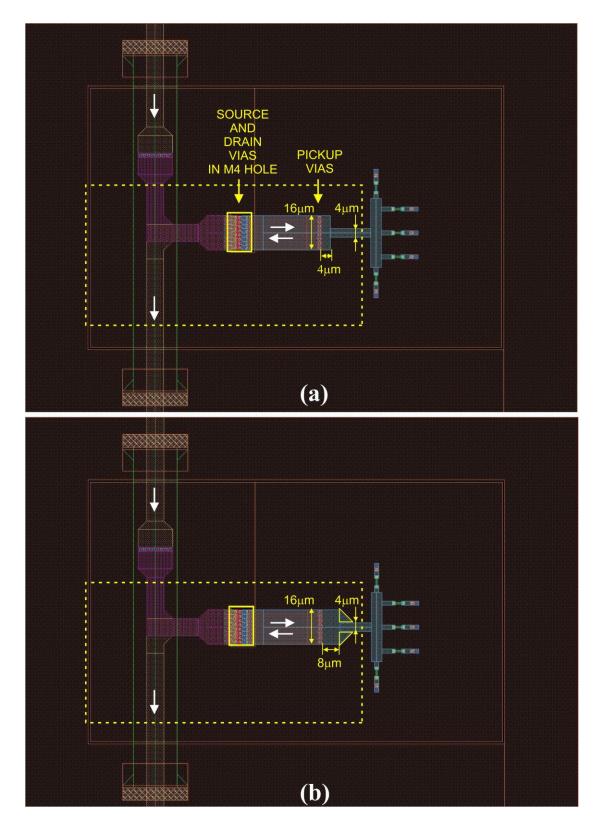

| The M6 strip changes its width from 16 $\mu m$ to 4 $\mu m$ after passing the group of pickup vias |

| with a 4 $\mu$ m extension (a) and 8 $\mu$ m extension combined with 2 chamfers (b) to let the     |

| return current redistribute equally between the individual pickup vias69                           |

|                                                                                                    |

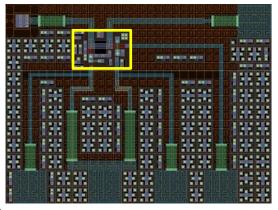

| 3.17 | The current distribution for two implementations of the GV biasing approach depicted in     |

|------|---------------------------------------------------------------------------------------------|

|      | Figure 3.15. The return current is unequally (a) and equally (b) distributed between        |

|      | individual pickup vias (S-Z). The regions shown correspond to the dashed rectangles         |

|      | marked in Figures 3.16(a) and 3.16(b)                                                       |

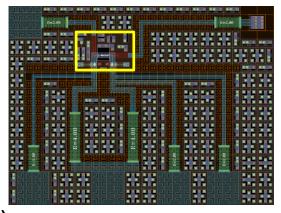

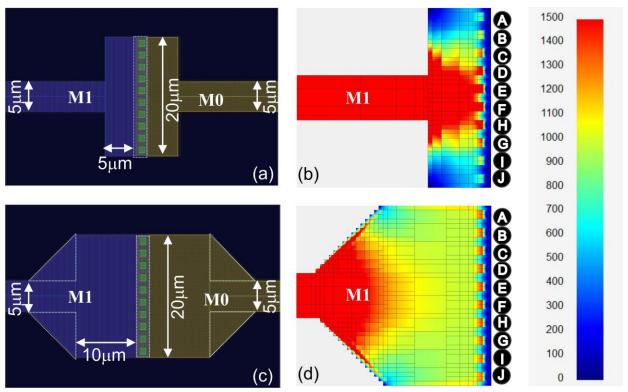

| 3.18 | The SQUID-based test structures (a) and (c) are used to measure the LP and LS for the       |

|      | DRP transformer (seen in the yellow box) respectively. The mutual inductance (M) is         |

|      | obtained from both structures. These were designed, fabricated, and tested in the MIT-LL    |

|      | SFQ5ee $10kA/2\Omega$ fab node. The layouts of (b) and (d) were used to extract the LP, LS  |

|      | respectively, and M, in simulation                                                          |

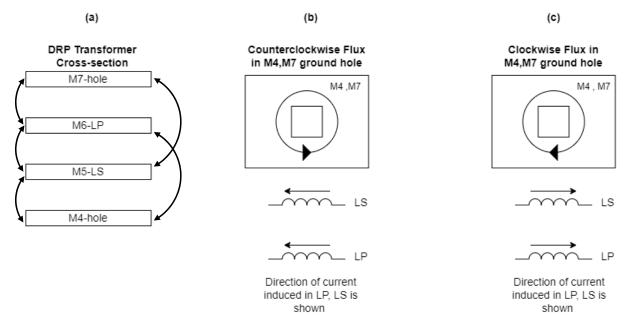

| 3.19 | DRP cross-section (a) shown with all forms of coupling between metal layers. The sign       |

|      | convention for counterclockwise (CCW) and clockwise (CW) flux trapping is shown in (b)      |

|      | and (c) respectively74                                                                      |

| 3.20 | Simplified layout to calculate coupling between M4 ground hole inductor and LP, LS          |

|      | signal inductors of the DRP. InductEx reports a value of $L_{M4}$ ~10 pH, a value in close  |

|      | agreement with a washer inductance of similar geometry reported in [73]74                   |

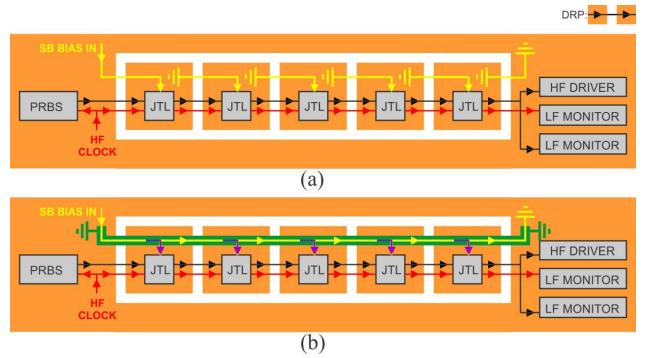

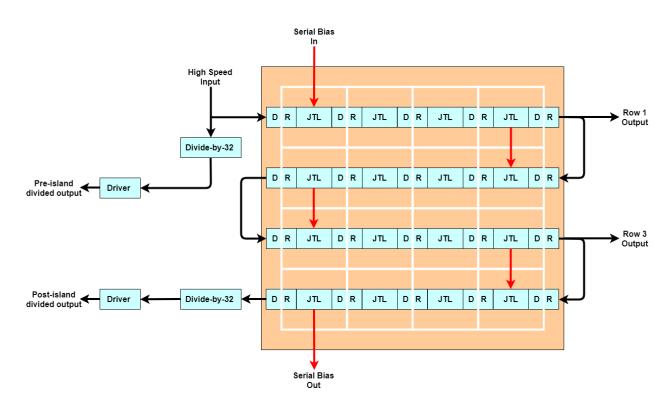

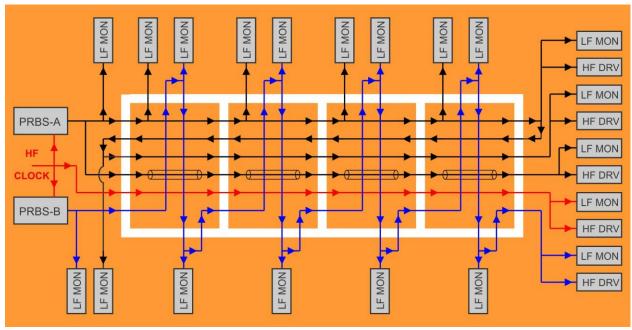

| 3.21 | 16 island (4 rows) example of the serially biased JTL circuit. The experimental circuit has |

|      | total of 80 islands (20 rows). The divide-by-32 circuit used preceding the pre and post-    |

|      | island outputs allows for HF characterization. SF biasing is not shown in the diagram77     |

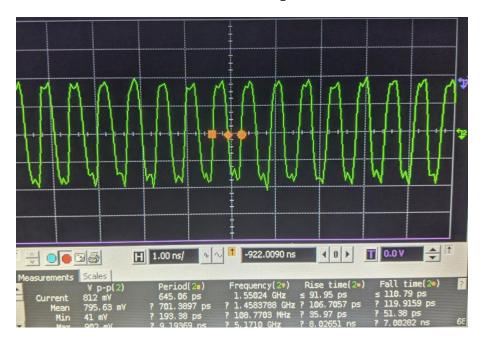

| 3.22 | The divided output is seen at 1.56 GHz. This corresponds to an input frequency of 49.92     |

|      | GHz. Increasing or decreasing the serial bias current results in an unstable waveform77     |

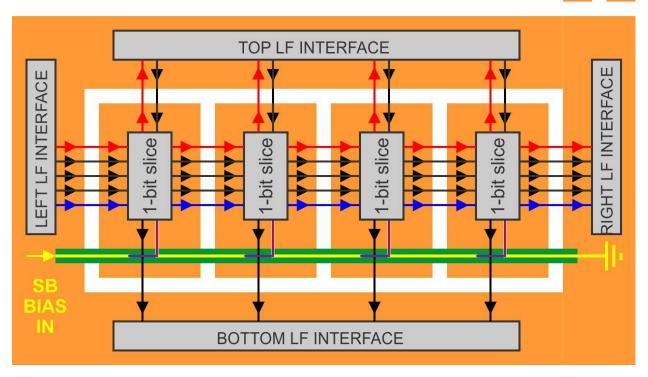

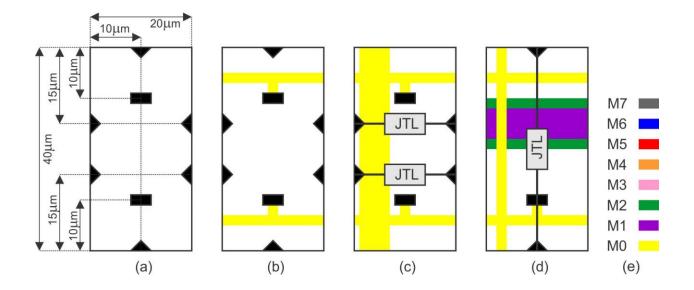

| 4.1  | The grapevine biasing technique implemented on 2 serially biased islands (a) for the MIT-   |

|      | LL SFQ5ee layers stack (b) (see text for details)82                                         |

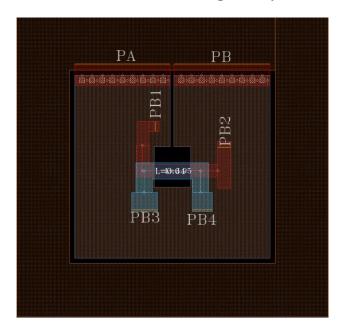

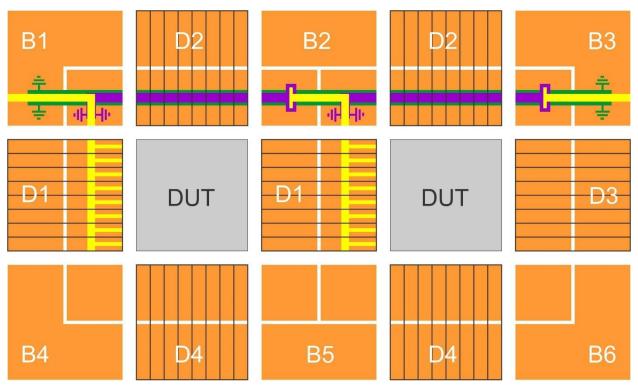

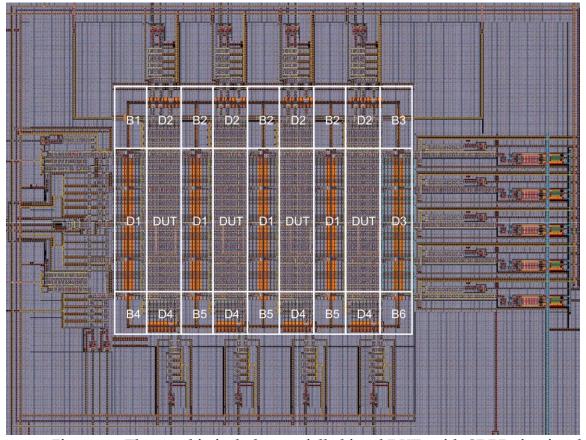

- 4.2 The DRP core (a) comprises driver junctions JA1-JA4 and receiver junctions JB1-JB2 placed on separated grounds A and B. JA1 = 250 μA, JA2 = 350 μA, JA3=488 μA, JA4 =

- $158~\mu A, JB1 = 94~\mu A, JB2 = 131~\mu A, IA1 = 175~\mu A, IA2 = 245~\mu A, IA3 = 344~\mu A, IB1 = 175~\mu A$

- $71~\mu A,~IB2=100~\mu A,~LA1=2~pH,~LA2=2.7~pH,~LA3=2.1~pH,~LB1=2.7~pH,~LP=LS$