#### University of Windsor

#### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

Summer 2021

## Implementation Of An Improved Image Enhancement Algorithm On FPGA

Prit Ghanshyambhai Patel

Follow this and additional works at: https://scholar.uwindsor.ca/etd

Part of the Computer Engineering Commons

#### **Recommended Citation**

Patel, Prit Ghanshyambhai, "Implementation Of An Improved Image Enhancement Algorithm On FPGA" (2021). Electronic Theses and Dissertations. 8842.

https://scholar.uwindsor.ca/etd/8842

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license-CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# Implementation Of An Improved Image Enhancement Algorithm On FPGA

By

#### Prit Ghanshyambhai Patel

A Thesis

Submitted to the Faculty of Graduate Studies

through the Department of Electrical and Computer Engineering

in Partial Fulfillment of the Requirements for

the Degree of Master of Applied Science

at the University of Windsor

Windsor, Ontario, Canada

2021

©2021 Prit Ghanshyambhai Patel

#### Implementation Of An Improved Image Enhancement Algorithm On FPGA

by

#### Prit Ghanshyambhai Patel

# A. Rahimi Department of Mechanical, Automotive and Materials Engineering H. Wu Department of Electrical and Computer Engineering M. Khalid, Co-Advisor Department of Electrical and Computer Engineering

A. Ahmadi, Co-Advisor Department of Electrical and Computer Engineering

May 18th, 2021

#### DECLARATION OF ORIGINALITY

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

#### ABSTRACT

Image processing plays very crucial role in this digital human world and has rapidly evolved with the development of computers, mathematics and the real-life demand of variety of applications in wide range of areas. This wide range of areas includes remote sensing, machine/robot vision, pattern recognition, medical diagnosis, video processing, military, agriculture, television, etc. Image processing has two important components which are image enhancement and information extraction. Since image enhancement works at the front end with the initial raw inputs, it works like a backbone in image processing. When it comes to implementing these image enhancement techniques and developing applications, these tasks are bit demanding in the choice of processing units because the demand of high resolution. This emerges the necessity of a high speed, powerful and cost-effective processing unit. In this thesis we present an improved image enhancement algorithm in terms of performance and its implementation on FPGA as they satiates the necessity of high speed, powerful and cost-effective processing unit by providing flexibility, parallelization, pipelining and reconfigurability. We have performed a high level synthesis by using MATLAB and implemented an improved image enhancement algorithm on Cyclon V by using Quartus Prime. We have considered an X-ray image size of 1000x1920p for implementation and achieved a decent PSNR values and hardware resource utilization along with the better visual interpretability by our proposed improvements. For achieving a better execution time and power consumption we also offer the task parallelism for the algorithm.

#### DEDICATION

Dedicated to my father Ghanshyambhai Ishvarbhai Patel, my mother

Jayshree Ghanshyambhai Patel and my brother Vedant Patel for their

overwhelming enthusiasm, support, love, and for making everything possible.

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to **Dr. Arash Ahmadi** and **Dr. Mohammed Khalid** for their continuous support and inputs through out my work. I could not have imagined a better mentor for my study. I would also like to thank **Dr. Huapeng Wu** and **Dr. Afshin Rahimi** for their inputs that helped me in refining and improving my work and helping me in guiding my work in proper direction and leading my thesis towards a gracious completion.

Also, I would like to thank my all nearest family members especially my cousins Dipesh Patel, Tirth Patel, Rut Patel and Akshay Patel, for keeping me encouraged, without whom I could not have imagined my journey through the University. Special thanks to my teacher Kuntal Patel without whom my journey would not be possible. Cheers to my best friends Pritesh Patel, Hetvi Patel, Dhruvesh Patel, Manan Patel, and Vandan Patel for their constant support.

#### TABLE OF CONTENTS

| DECLARATION OF ORIGINALITY                                                                                                                                                                                                                                                                                                                                                                                                  | III                                                                   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                       |  |  |  |

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |  |  |  |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                            | VI                                                                    |  |  |  |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                              | $\mathbf{X}$                                                          |  |  |  |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                             | XI                                                                    |  |  |  |

| ACRONYM                                                                                                                                                                                                                                                                                                                                                                                                                     | XII                                                                   |  |  |  |

| 1 Background and Thesis Overview 1.1 Digital Image processing:Overview, Classification and Requirements . 1.2 Need for High Level Synthesis                                                                                                                                                                                                                                                                                 | 1<br>1<br>2<br>2<br>2<br>3<br>3<br>3<br>5                             |  |  |  |

| 2.1 Image Enhancement 2.1.1 Spatial Domain Image Enhancement Techniques 2.1.1.1 Point Processing 2.1.1.1.1 Linear Transformation: 2.1.1.1.2 Logarithmic Transform: 2.1.1.1.3 Power-Law Transformation 2.1.1.1.4 Piecewise-Linear Transformation: 2.1.1.2 Frequency Domain Image Enhancement Techniques 2.2 Image Enhancement Operations 2.2.1 Sobel Operator 2.2.2 Laplacian Of An Image 2.2.3 Addition 2.2.4 Wiener Filter | 7<br>7<br>8<br>9<br>9<br>10<br>10<br>11<br>11<br>12<br>13<br>14<br>15 |  |  |  |

| 2.2.5       Multiplication                                                                                                                                                                                                                                                                                                                                                                                                  | 16<br>16<br>17<br>19                                                  |  |  |  |

| 2.3.2 Synthesis                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                                    |  |  |  |

|   |     | 2.3.3 Implementation                                              | 20         |  |  |  |

|---|-----|-------------------------------------------------------------------|------------|--|--|--|

|   |     | 2.3.4 Device Programming                                          | 20         |  |  |  |

|   |     | 2.3.5 Design Verification                                         | 20         |  |  |  |

|   |     | 2.3.5.1 Behavioral Simulation                                     | 20         |  |  |  |

|   |     | 2.3.5.2 Functional Simulation                                     | 21         |  |  |  |

|   |     | 2.3.5.3 Static Timing Analysis                                    | 21         |  |  |  |

|   | 2.4 | HLS and Design Flow                                               | 21         |  |  |  |

| 3 | Re  | Related Works 2                                                   |            |  |  |  |

|   | 3.1 | Implementing Image Enhancement algorithms on FPGAs                | 23         |  |  |  |

|   |     | 3.1.1 Exploiting Parallelism                                      | 23         |  |  |  |

|   |     | 3.1.2 Low-Level Approach                                          | 25         |  |  |  |

|   |     | 0 11                                                              | 26         |  |  |  |

|   |     |                                                                   | 28         |  |  |  |

|   | 3.2 | Fixed Floating Point Configurations and Their Trade-off           | 29         |  |  |  |

| 4 | Me  | ethodology                                                        | 31         |  |  |  |

|   | 4.1 | Overcoming the Limitation of Laplacian Operator by Edge-Aware Im- |            |  |  |  |

|   |     |                                                                   | 32         |  |  |  |

|   |     | 4.1.1 Local Laplacian Filtering Algorithm                         | 33         |  |  |  |

|   |     | 4.1.2 Sampling for acceleration                                   | 35         |  |  |  |

|   | 4.2 | LoG to Solve the Performance Problem in Edge Detection            | 36         |  |  |  |

|   | 4.3 | An Improved Image Enhancement Algorithm                           | 37         |  |  |  |

|   | 4.4 |                                                                   | 36         |  |  |  |

|   | 4.5 | 1                                                                 | 40         |  |  |  |

|   |     |                                                                   | 42         |  |  |  |

|   | 4.6 | • •                                                               | 43         |  |  |  |

|   |     |                                                                   | 43         |  |  |  |

|   |     | v                                                                 | 44         |  |  |  |

|   |     | 4.6.3 PSNR for the quality estimation                             | 44         |  |  |  |

| 5 | Ex  | •                                                                 | <b>4</b> 6 |  |  |  |

|   | 5.1 |                                                                   | 46         |  |  |  |

|   | 5.2 |                                                                   | 49         |  |  |  |

|   | 5.3 | 1 0 1                                                             | 52         |  |  |  |

|   | 5.4 |                                                                   | 55         |  |  |  |

|   | 5.5 | Implementing Power Law Transform                                  | 57         |  |  |  |

|   | 5.6 | Quality Estimation Analysis                                       | 58         |  |  |  |

|   | 5.7 | v                                                                 | 60         |  |  |  |

|   | 5.8 | Visual Interpretability Analysis                                  | 61         |  |  |  |

| 6 |     |                                                                   | 64         |  |  |  |

|   | 6.1 |                                                                   | 64         |  |  |  |

|   | 6.2 | Future Work                                                       | 65         |  |  |  |

| REFERENCES    | 66 |

|---------------|----|

| VITA AUCTORIS | 71 |

#### LIST OF TABLES

| 1.4.1 Problem statements and their proposed solutions                                | 5  |

|--------------------------------------------------------------------------------------|----|

| 5.1.1 Generic Resource Utilization Report of Local Laplacian                         | 48 |

| 5.1.2 Resource Utilization Report of Local Laplacian by Quartus Prime Lite           | 49 |

| 5.2.1 Generic Resource Utilization Report of Sharpening and Noise removal            |    |

| $\bmod el  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 51 |

| 5.2.2 Resource Utilization Report of Sharpening and Noise removal model              |    |

| by Quartus Prime Lite                                                                | 52 |

| 5.3.1 Generic Resource Utilization Report of LoG operator                            | 54 |

| 5.3.2 Resource Utilization Report of LoG by Quartus Prime Lite                       | 55 |

| 5.4.1 Generic Resource Utilization Report of Masking operator                        | 56 |

| 5.4.2 Resource Utilization Report of masking by Quartus Prime Lite                   | 57 |

| 5.5.1 Generic Resource Utilization Report of Power Law Transform                     | 58 |

| 5.5.2 Resource Utilization Report of Power Law Transform by Quartus Prime            |    |

| Lite                                                                                 | 58 |

| 5.6.1 Analysis and comparison of quality estimation of the algorithm                 | 59 |

| $5.7.1$ Resource utilization comparison for edge detection techniques $\dots$ .      | 60 |

| 5.7.2 Resource utilization comparison for Local Laplacian and Laplacian              | 61 |

#### LIST OF FIGURES

| 2.1.1 Gray-level Transformation graph [29]                                                    | 8  |

|-----------------------------------------------------------------------------------------------|----|

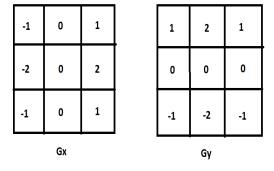

| 2.2.1 Sobel Masks                                                                             | 12 |

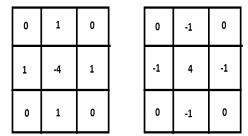

| 2.2.2 Positive and Negative Laplacian Operators                                               | 14 |

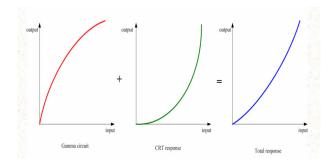

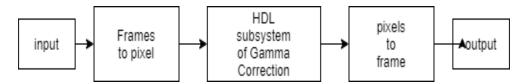

| 2.2.3 Gamma correction in images[29]                                                          | 17 |

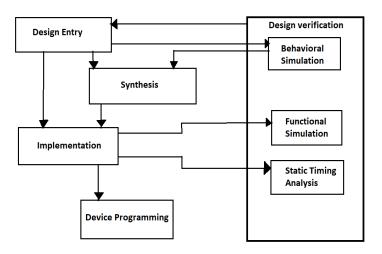

| 2.3.1 FPGA Design Flow                                                                        | 18 |

| 2.4.1 Vivado HLS Design Flow[15]                                                              | 22 |

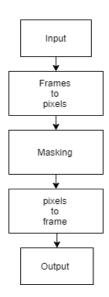

| 4.0.1 Hardware Implementation flow using MATLAB                                               | 32 |

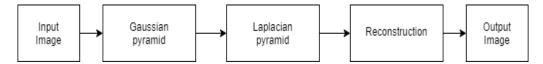

| 4.1.1 General Flow of Local Laplacian Algorithm                                               | 34 |

| 4.1.2 Pseudo code of Local Laplacian Filtering[28]                                            | 35 |

| 4.3.1 An Improved Image Enhancement Algorithm                                                 | 38 |

| 4.4.1 Task Parallelism in proposed algorithm                                                  | 40 |

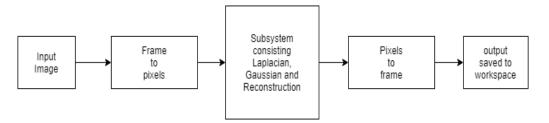

| 5.1.1 Overview of Local Laplacian                                                             | 47 |

| 5.1.2 Main MATLAB model of Local Laplacian                                                    | 47 |

| 5.2.1 Overview of Sharpening and noise removal model                                          | 49 |

| $5.2.2\mathrm{Main}$ MATLAB model of Sharpening and noise removal                             | 50 |

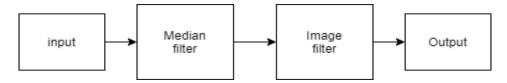

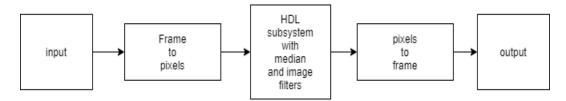

| 5.3.1 Overview of LoG implementation                                                          | 53 |

| 5.3.2 MATLAB script for LoG operation                                                         | 53 |

| 5.4.1 Implementation of Masking operation                                                     | 56 |

| 5.5.1 Overview of Power Law Transform                                                         | 57 |

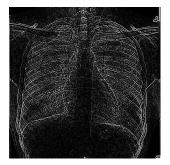

| $5.8.1~\mathrm{X}\text{-ray}$ image of human body(left) [12], Laplacian of the image(right) . | 61 |

| 5.8.2 Sharpened image by addition of two images(left), LoG of the image(right)                | 62 |

| 5.8.3 Smoothened image by filtering(left), masked formed by multiplica-                       |    |

| $tion(right) \ldots \ldots \ldots \ldots \ldots \ldots$                                       | 62 |

| 5.8.4 Sharpened image by second addition(left), gamma transformed im-                         |    |

| age(right)                                                                                    | 63 |

| 5.8.5 Laplacian filtered image(left), Local Laplacian filtered image(right) .                 | 63 |

#### **ACRONYM**

FPGA Field Programmable Gate Arrays

**HLS** High Level Synthesis

LoG Laplacian of Gaussian

PSNR Peak Signal to Noise Ratio

MATLAB MATrix LABoratory

ASICs Application Specific Integrated circuits

CPU Central Processing Unit

**GPU** Graphics Processing Unit

**USB** Universal Serial Bus

**PCIe** Peripheral Component Interconnect express

**LOFAR** Low Frequency Array

**SKA** Square Kilometre Array

**HDL** Hardware Description Language

**SDK** Software Development Kit

**DNNs** Deep Neural Networks

AI Artificial Intelligence

RTL Register Transfer Level

VHDL Very High speed integrated circuit Hardware Description Language

**OCR** Optical Character Recognition

RAM Random Access Memory

${f LUTs}$  Look Up Tables

$\mathbf{ALU}$ Arithmetic Logic Unit

**DSP** Digital Signal Processing

**RGB** Red, Green, Blue

$\mathbf{MSE}\,$  Mean Squared Error

${f ALM}$  Adaptive Logic Module

I/O Input/Output

# CHAPTER 1

# Background and Thesis Overview

# 1.1 Digital Image processing:Overview, Classification and Requirements

No environment is Noise-free and whether it is signal or image, everything needs to be cleaned before its usage to experience a better and optimized output. In other words, there is noise in every system due to various factors such as, sensors, medium, data and so on, and it causes the degradation in the system output as it is directly proportional to the output. Moreover, in these last few decades with the development of the computers, discrete mathematics and the demand of wide range application in different fields from agriculture to medical science and space exploration, the development of digital image processing has been highly affected. Digital image processing is basically a sub-branch of digital signal processing it refers to the improvement in the system output (which is in form of an image) which is very crucial for information extraction and image interpretation[1]. It basically enhances the image quality and provides an ease for human clarification and visualization along with an image data processing for transmission, storage and machine view representation[31]. It is widely useful in remote sensing applications, medical field, machine/robot vision, pattern recognition, video processing, etc[2]. Fundamentally, digital image processing can be classified into five main components which are, acquisition, storage, processing, communication and display. Among these components image processing is a broad subject which consists of different techniques such as Image Restoration, Image Enhancement and information extraction. The focus of this thesis is on the image enhancement since it is the most important fundamental steps of digital image processing.

#### 1.2 Need for High Level Synthesis

With the increase in the processing power, the trend of the image processing in the device itself rather than using a separate computer has been noticed. For example, in context of the digital cameras, these cameras do not only captures the photos but also performs several image processing operations, communicate the images and extract the data[3]. Although, with the advances of the device technologies, low power general processors struggles in coping up with the high processing demands of the image processing applications because of which the smart devices with FPGAs have started gaining popularity these days. The conventional approach for developing such kind of image processing applications is to develop the test bench of the algorithm and then to port them into hardware description language for FPGA implementation once they function as desired. Thus, the user can develop such kinds of applications by porting the algorithm on FPGA by following the process called High Level Synthesis.

#### 1.3 Motivation Behind The Work

The main advantage of FPGA is its capability to be a standalone quantity which does not require any host computer to run because it has its own input and output. Thus a user can save money and energy on the host. Moreover, FPGA can turn out to be very important by leaving single serial processor and GPUs behind in the following parameters:[27]

#### 1.3.1 Low Latency

Latency plays a crucial role when it comes to real time applications such as autopilot mode of a jet and an airbag system of a car. In these kind of applications, the time period between the system response and the input should be as short as possible. CPUs having latency smaller than 50 microseconds would be considered as very good but on the other hand, FPGAs are feasible to achieve a latency around or below 1 microsecond. The main reason for this is that FPGAs do not depend on a generic Operating System and they do not communicate via generic buses.

#### 1.3.2 Connectivity and Bandwidth

In FPGA a user can hook up any data source up such as a sensor or a network interface directly to the pins of a chip whereas, in CPUs or GPUs a source has to be connected via a local standardize bus such as USB or PCIe and depend on the Operating System to deliver the data.

This direct connection to the pins provides very high bandwidth which is very useful in some radio astronomy applications such as LOFAR and SKA because of the usage of specialized sensors in them which generates enormous amount of the data.

#### 1.3.3 Energy Efficiency

FPGAs shine in terms of energy efficiency when it comes to logic and fixed point calculations which makes FPGAs more useful in the field of crypto-currency mining. Even Intel is always acclaiming the energy efficiency of FPGA. Although, nowadays ASICs (Application Specific Integrated circuits) are used for this applications since they are built for only one purpose. Though, they require very large upfront investment and a large number of chips to be produced to be cost effective.

## 1.4 Challenges and Outlined Solution

Now, when it comes to implementing the algorithms the users have different options available and hardware implementation offers a better speed than the software implementation. Though, the development time for the hardware implementation is larger. Most of the designers are familiar with C but the hardware implementation and synthesis require the extensive knowledge of hardware and VHDL or Verilog. Moreover,

there are some tools that offers software to hardware conversion schemes such as Vivado HLS, Altera SDK, MATLAB HDL coder, etc. But again, most of these tools are costly and it requires to restructuring of the code to achieve a better performance. Because of this reason image processing algorithms are very less implemented on a powerful hardware like FPGA even though having a wide range of applications.

- Although the hardware implementation is a bit arduous task, it offers many advantages and provides a better match for these image or video processing algorithms to be implemented. A real time image or video processing algorithm will raise an inconvenience for the single serial processor because it requires images with very large size and high resolution. For example, if we consider a standard 720 pixel video stream at 24 frames per second, it will require at least 66 millions of operations to process that video stream. Moreover, generally most of the image processing algorithms require dozens of the operations on a single pixel. It will turn out be an extreme heavy load for single serial processor.[5] Thus, one can say that FPGAs offer task parallelization which like is a cherry on top.

- Moreover, the Sobel operator which generally is used in the edge detection is very basic and has a performance problem when it is compared to the benchmarks and also it offers very poor signal to noise ratio with the increment in the noise. The overcoming of the performance problem will be done by replacing the Sobel operator with the LoG operator.

- Apart from that, usage of the Laplacian operator is only limited to the greyscale images which makes the area of application for the image enhancement algorithm lesser broad[21]. To solve this problem the Local Laplacian filter will be used for the image enhancement algorithm to be useful for coloured images as well.

- Additionally, the algorithm proposed in [17] is sequential and lacks parallelism which can cost more power and execution time when it comes to implementing

this algorithm on any hardware. Moreover, power consumption and execution time are crucial parameters as they are directly proportional to the flow of the algorithm. So, for this we propose a task parallelism and parallel flow of the algorithm.

The aim of this research is to attempt to improve an image enhancement algorithm and implementing a parallel algorithm on a powerful and flexible hardware- FPGA. This approach would not only provide a viable option for implementing image or video processing algorithm without sacrificing the performance parameter like execution time, chip area and power consumption, but it would improve the execution time and power consumption and allow us to witness the capability of FPGA to be a standalone quantity in the applications.

We tackle the problem with the points stated above which we discuss comprehensively in subsequent chapters of this thesis. To summarize the problem statements and solutions for those problems, we show the table below.

| Problems                                            | Proposed Solutions              |

|-----------------------------------------------------|---------------------------------|

| Performance problem of Sobel operator               | Usage of LoG                    |

| Limitations of Laplacian and scope of the algorithm | Usage of Local Laplacian        |

| Sequential nature of the algorithm                  | Proposal for a task parallelism |

| Long development time for hardware implementation   | Usage of HLS                    |

Table 1.4.1: Problem statements and their proposed solutions

#### 1.5 Thesis Outline

The subsequent chapters of the thesis are organized as follows. In **Chapter 2**, we present the readers with succinct knowledge which lays a technical foundation for the rest of the thesis. As for **Chapter 3**, we present the Literature Survey of related work done in the area. **Chapter 4** explains the implemented Methodology to solve the

#### 1. BACKGROUND AND THESIS OVERVIEW

problem. **Chapter 5** includes the experiment results and analysis of the proposed solution and comparison with other methods. And lastly, In **Chapter 6**, we conclude the thesis and address the work that can be possibly done in the future to refine the proposed solution.

# CHAPTER 2

# Overview of Related Technologies

#### 2.1 Image Enhancement

The motive of Image Enhancement is to amplify or sharpen the details or the features of an image so that an image can be used further in the other applications. It makes an image more appropriate by exploring the hidden details of the image due to the various environmental and hardware factors and make the extraction of the contained details more meaningful. Mainly, Image Enhancement techniques can be classified into two broad categories based on the processing level, Spatial Domain Image Enhancement and Frequency Domain Image Enhancement.

#### 2.1.1 Spatial Domain Image Enhancement Techniques

To begin with the processing level, Spatial Domain Image Enhancement Techniques operate at the pixel level and deal directly with the pixel values. These methods refer more efficient computations as well as they require less processing resources for implementation. Here, the pixel values are manipulated to achieve the desired result. In Spatial Domain Image Enhancement Techniques, the image processing function can be expressed as,

$$g(x,y) = T(f(x,y)) \tag{1}$$

Where, f(x,y): input image, g(x,y): processed image, T(): operator on f defined over some neighbourhood N(x,y)

Spatial Domain Image Enhancement Techniques directly alter the pixel values or gray levels of the pixels and hence directly affect the overall image uniformly. Here, it is not possible to alter information of the selective parts of the image. There are two main approaches in this methods, point processing and spatial filtering.

#### 2.1.1.1 Point Processing

Here, the enhancement of the image depends only on the gray level of one point, i.e., pixel. According to the equation (1) T refers to the gray level transformation of the image so that point processing is also known as Gray Level Transformation. point processing operations take form of,

$$s = T(r) \tag{2}$$

Where, S refers to the processed image pixel values and T refers to the original image pixel values. Mainly there are four types of Gray Level Transformation; Linear, Logarithmic, Power-law and Piecewise-Linear.

Fig. 2.1.1: Gray-level Transformation graph [29]

**2.1.1.1.1 Linear Transformation:** Linear Transformation has two categories; Negative Transformation and Identity Transformation.

Negative Transformation: Images as a sets of pixels are digitally stored in form of digital values. A pixel of a gray-scale image has two values; 0 and 1. 1 refers to colour white and 0 refers to the colour gray(or black). The most common pixel format, byte image has the pixel value in form of 8-bit integer from 0 to 255. Here, 0 is considered as black and 255 is considered to be white. The values between them are considered to be the different shades of gray.Now, when negative transformation is applied to the image, the brightest areas are transformed into the darkest areas and the darkest areas are converted into the brightest areas. The negative transformation can be defined as,

$$s = L - 1 - r \tag{3}$$

Where, L-1 is maximum pixel value and r is the targeted pixel value.

**Identity Transformation:** This type of transformation is used when a user wants identical input and output. Here, each value of the input image is directly mapped to each other values of the output images which results in the same or identical output.

**2.1.1.1.2** Logarithmic Transform: This method can be used for the low light images since it expands the values of the dark pixel and compresses the value of the bright pixel. It maps the narrow range of the low gray level intensities to wide range of output values. This transformation can be defined as,

$$s = C * log(1+r) \tag{4}$$

Where r and s are input pixel value and output pixel value respectively. C is scaling constant. Inverse-log Transform is the opposite to the Log Transform.

2.1.1.1.3 Power-Law Transformation It is also known as Gamma Correction or Gamma Transformation and it is used in enhancing images for different types of display devices since the gamma value of different display devices is different. Different display devices project different intensity levels and clarity according to the built in gamma correction inside them have different ranges. This transformation can be defined as,

$$s = C * r^{\gamma} \tag{5}$$

Where, s is output pixel value, r is input pixel value and  $\gamma$  is a gamma value of a pixel. Here, the variations in  $\gamma$  causes the variation in the enhancement of an image.

**2.1.1.1.4** Piecewise-Linear Transformation: Piecewise-Linear Transformation is arbitrary user defined transform which can be categorized in three sub-categories; Intensity Level Slicing, Contrast Stretching and Bit-Plane Slicing.

Intensity Level Slicing: It highlights the specific intensity level of an image as desired. Intensity Level Slicing can emphasize a group level intensity by diminishing all others or vice versa.

Contrast Stretching: Contrast Stretching basically works on entire image and enhances low contrast images. Here, Contrast is the intensity value difference between the pixels. This operation can be performed in three ways; Multiplying each input pixel intensity by a constant scalar, using histogram equivalent or applying the transform which makes the dark area more darker and the bright area more brighter.

Bit-Plane Slicing: In Bit-Plane Slicing the image is considered to be as the stack of the multiple binary images and really useful in Steganography to hide the secret data. The images close to the bottom are considered to be insignificant and the images close to the top are considered to be significant.

#### 2.1.1.2 Frequency Domain Image Enhancement Techniques

Frequency Domain Image Enhancement Techniques are based on orthogonal transform or on the convolution theorem. Here, it is supposed that g(x,y) is an image formed by the convolution of an input image f(x,y) and a linear position invariant operator h(x,y). Therefore,

$$q(x,y) = h(x,y) \star f(x,y) \tag{6}$$

Now, applying the convolution theorem,

$$G(u,v) = H(u,v) \cdot F(u,v) \tag{7}$$

Where, G, H and F are Fourier Transformation of g, h and f respectively. The orthogonal transformation has two components; magnitude and phase. Magnitude consists of frequency contents of the image while phase is used to restore the image back to spatial domain.

In frequency domain image enhancement techniques, an image is first transferred into frequency domain by Fourier transformation and various image enhancement operations are performed and then the resultant image is achieved by applying the inverse Fourier Transformation.

#### 2.2 Image Enhancement Operations

As discussed above, Image enhancement methods or algorithms generally are either spatial domain or frequency domain and every step has its own importance according to its characteristics and its working. Some algorithms consist only spatial domain image enhancement methods and some algorithms consist only frequency domain methods to enhance the input image by means of contrast, dynamic range, noise, details, etc. Here, in this thesis a unique image enhancement method is used to enhance the image and it consists of both, spatial and frequency domain methods. Some image enhancement operations or functions used in this algorithm are as below

in detail:

#### 2.2.1 Sobel Operator

A Sobel operator is generally used for the edge detection in the digital image processing applications. Edge detection plays a vital role in information extraction as well as for the visual perception. The better the edges of the subject and objects are, the easier its perception gets.

Now, when we talk about edge detection by using a Sobel operator, it gives an approximation to a derivative of the image. It basically separates the edges vertically and horizontally, in other words in x-direction and in y-direction. For this task a kernel or mask is used which is  $3 \times 3$  metrics. There are two different kernels for each directions.

Fig. 2.2.1: Sobel Masks

Here, in figure 2.2.1 two masks of a Sobel operator are shown. Gx is a gradient or mask in X-direction and similarly, Gy is a gradient or a mask in Y-direction. In this technique, basically the mask or the gradient is placed on the image and convoluted on all over the image in order to find out the edges. Edges are basically the intensity difference of the neighbouring pixels. These both kernels can be applied to a single image simultaneously to find two separate orientations and the vertical and horizontal edges can be enhanced by finding their magnitude. An approximate magnitude is shown below in equation.

$$|G| = |Gx| + |Gy| \tag{8}$$

#### 2.2.2 Laplacian Of An Image

Generally, a Laplacian operator is used to highlight the details of an image in image processing applications. It can also be used before sharpening operation since it highlights the details and then those details can be sharpened to make it more visible. A Laplacian operator is basically a 2-D isotropic measure of second order derivative of an image. It also directly deals with the pixel values so we can say that the Laplacian operator is also a spatial domain image enhancement method. The main difference between a Laplacian and other spatial edge detection masks like Sobel and Prewitt is Laplacian is second order mask unlike those other masks. Moreover, a Laplacian operator does not differentiate the edges of image in any particular directions like the other masks, it differentiate the edges inwards or outwards.

Laplacian Operator can be classified into two categories, Positive Laplacian Operator and Negavtive Laplacian Operator. In postive Laplacian operator the center element is negative and the elements of the boundary are positive. Similarly, in negative Laplacian operator, center element is positive and the boundary elements are negative. Positive Laplacian Operator enhances the outward edges and Negative Laplacian Operator enhances the inward edges. These two different operators are shown below in image.

Fig. 2.2.2: Positive and Negative Laplacian Operators

We only can use one of these operators on an image at a time. Laplacian operator basically uses the gray level discontinuities to enhance the edges of gray-scale images. The Laplacian of an image having pixel intensity I(x,y) can be calculated as,

$$L(x,y) = \frac{\nabla^2 I}{\nabla x^2} + \frac{\nabla^2 I}{\nabla y^2} \tag{9}$$

A convolution filter is used to calculate this equation. These kernels are very sensitive to the noise since they are a approximation of the second derivative of the image. Thus, before using the Laplacian, the Gaussian smoothing is used to smooth the image. In other words, to reduce the high frequency noise components.

#### 2.2.3 Addition

In digital image processing, Addition of the image is used as sharpening operator or for the noise reduction. As the images are considered to be the set of the pixel, we can sharpen an image by increasing the values of each pixels. This increment in the value can be done by adding a constant to the image or by adding the image to the image. Thus, it also makes Addition, a spatial domain image enhancement technique. An Addition operation of two images I1 and I2 can be calculated by,

$$I(x,y) = I_1(x,y) + I_2(x,y)$$

(10)

Similarly, an addition of a constant to an image is done by,

$$I(x,y) = I_1(x,y) + C$$

(11)

#### 2.2.4 Wiener Filter

Wiener Filtering is considered to be a most important technique of a blur removal. A blur in images can be the product of the linear motion or an unfocused optics. From the image processing point of view, the linear motion is nothing but the poor sampling. If the shutter speed of a camera is too slow to realize the motion of the camera, it causes a blur in the image. Each pixel in the image represents the intensity of a fixed particular point of an image, but if the shutter speed is too slow to experience the motion of the camera, the focus gets mixed with the intensities of the other points. Wiener filtering is a frequency domain image enhancement technique as it includes the Fourier transformation of an image.

Wiener filtering approach is based on the stochastic framework in which an image is first considered to be distorted by the gaussian noise and then that image is recovered by the inverse filtering by trading off between additive noise and inverse filtering since an inverse filtering is very sensitive to additive noise.

The difference between an uncorrupted image f(x,y) and the estimated image f'(x,y) gives us the mean square error.

$$e^{2} = E[f(x,y) - f'(x,y)]^{2}$$

(12)

The approximate image estimation satisfies the minimum error function in the frequency domain. It can be shown by,

$$F'(u,v) = \left[\frac{1}{H(u,v)} \cdot \frac{|H(u,v)|^2}{|H(u,v)|^2 + K}\right] \cdot G(u,v) \tag{13}$$

The mean square error(MSE) and signal to noise ratio(SNR) in their statistical form can be given by,

$$MSE = \frac{1}{MN} \cdot \sum_{x=0}^{M-1} \sum_{y=0}^{N-1} [f(x,y) - f'(x,y)]^2$$

(14)

$$SNR = \frac{\sum_{u=0}^{M-1} \sum_{v=0}^{N-1} |F(u,v)|^2}{\sum_{u=0}^{M-1} \sum_{v=0}^{N-1} |N(u,v)|^2}$$

(15)

#### 2.2.5 Multiplication

Like Addition, Multiplication in image processing comes with two main forms, multiplying by an image and multiplying by a constant. Generally, Multiplication is used for creating masks of an image in image processing. It is a spatial domain image enhancement technique.

Multiplication of two images can be shown as,

$$I(x,y) = I_1(x,y) \times I_2(x,y) \tag{16}$$

Multiplication of an image with a constant is given by,

$$I(x,y) = I_1(x,y) \times C \tag{17}$$

#### 2.2.6 Gamma Correction

It is also known as Gamma Transformation or Power-law Transformation. The general form is given by,

$$S = C \cdot r^{\gamma} \tag{18}$$

S is an output pixel value and r is an input pixel value. C and  $\gamma$  are positive constants. A human eye perceives the light by following a approximate transfer function according to Stevens' power law for perception of brightness. According to that function, we can observe that the human eye is more sensitive to the changes in the dark than the changes in the light. But unlike the functioning of the human eye, the camera shares a linear relationship. That means if we increase the light falling on the camera by the

factor 2, the output also will increase by the factor 2. So the actual problem comes in the picture at the time of displaying the output because various displays also have their own intensity to voltage response curves which is in power function instead of linear. So, any input signal from a camera is transformed by that gamma and the result appears darker than it is expected. So, we apply the gamma correction to this signal by applying complementary voltage which cancels out the gamma effect.

To summing up the whole procedure looks like the figure shown below.

Fig. 2.2.3: Gamma correction in images[29]

#### 2.3 Field Programmable Gate Arrays

Field Programmable Gate Arrays are widely known as FPGAs which are basically semiconductor based devices. They are mainly the matrix of configurable logic blocks and they are connected via interconnects between them. These configurable logic gates are nothing but the arrays of the logic gates, memory or other elements. Unlike the processors and ASICs (Application Specific Integrated Circuits) the user can change the functionality of FPGAs anytime by programming the hardware. This is the main advantage of FPGAs which is also known as Reconfigurability of FPGAs. These FPGAs can either be a set of simple function consisting of few logic gates or a very complex function consisting of thousands of logic gates and other elements and can acts as a comprehensive multi-core processor. This shows the capability of FPGAs which is very massive. They can be used to run millions of different operations in parallel which can be really useful in making a parallel hardware to achieve a very high speed configuration.

FPGAs offer a wide range of applications which are from video and image processing to medical and space applications. Particularly they are used as a building block for prototyping the ASICs or processors. They could be reprogrammed until the final bug-free design of ASICs before the actual manufacturing process. Even the giant companies like Intel and Nvidia use FPGAs to prototype new circuits.

Talking about the versatility offered by FPGAs, they are gaining elevation in the field of DNNs(Deep Neural Networks) which are used in the AI(Artificial Intelligence) applications since running of DNN models require a large amount of processing power. Generally, GPUs(Graphics Processing Units) are used to accelerate the processing powers but high performance FPGAs can actually outperform those GPUs when it comes to analyzing an enormous amount of data for Machine Learning. For an actual example, developers can harness the power of FPGAs without purchasing and configuring specialized software or hardware by using Microsoft services which let the developers work with common open source tools such as TensorFlow AI development Toolbox and Microsoft Cognitive Toolkit. An FPGA based design flow is shown below in figure.

Fig. 2.3.1: FPGA Design Flow

#### 2.3.1 Design Entry

There are multiple ways to design the FPGAs such as schematic based method, Hardware Description Language based method and the combined method which consists of both. The choice of these methods depends on the developers. If the developer seeks in dealing with hardware, schematic based method is the right choice. In dealing with the complex design or the design which can be though of as an algorithm, HDL method is better which is faster but lags in performance and density. HDL lets developers to isolate themselves from the details of hardware description whereas, schematic based method provides a wide visibility to the developers into the hardware. If one can think of a hardware design in the series of different states, state machine based method can come in handy but the tools for state machine method are limited. Each of these methods have their own pros and cons. The schematic based method is used for small designs and easy to read and comprehend whereas, HDL method is the most popular design method for FPGAs since it is faster and easy to implement.

#### 2.3.2 Synthesis

In this step the code is actually translated into real circuit elements such as gates, flip-flops and multipliers once the design is entered in the form of code. The input in form of HDL is converted into the the netlist which consists a list of the interconnects and logic elements which are going to be used for the project. This process begins with the syntax check and then optimized by the elimination or reduction of the redundant logic once a user feeds HDL based design. This optimization leads into the reduction of the design which allows faster implementation of this design. The final step is technology mapping which consists of the connection of the design to the logic, estimation of the associated time and the production of the design netlists. FPGA synthesis is done by using the dedicated synthesis tools provided by different companies such as Xilinx, Cadence, Synopsys, etc.

#### 2.3.3 Implementation

This step has three main steps, translation, mapping and place & route. These steps are provided by the vendors since they know better how to translate the synthesized netlist into FPGA.

The first step basically gathers all the information related to the constrains of the design that are set by the user. These constraints can be anything in terms of design, area, power consumption and time. It can be exemplify in the form of the maximum delay or the assignment of the pin positions. After that, the tool maps out the actual available resources on the FPGA board that is going to be used with the implementation by comparing them. Then it divides the circuits in form of logic blocks or sub blocks elements which results in the placement of the design into specific logic blocks which is mapped out in FPGA. The final step is to connect and route all the signals according to the set constraints.

#### 2.3.4 Device Programming

This is the last step of the FPGA design flow. It consists of loading the routed FPGA design into FPGA by generating the Bitstream file.

#### 2.3.5 Design Verification

The user has an opportunity to simulate and test the design at the end of every design steps of FPGA design flow but generally it is done at three essential design steps; at design entry, at post synthesis and post implementation. It would not be exaggeration to say that verifying the implemented designed functionality is very important part of the FPGA design flow.

#### 2.3.5.1 Behavioral Simulation

It is also known as RTL (Register Transfer Level) simulation and it is done before synthesis or at design entry. This is a fast simulation which is done quickly in order to check the functionality of the design without considering the constraints. A user can use this simulation frequently to test the code and to find the logical errors.

#### 2.3.5.2 Functional Simulation

This simulation is performed after the completion of the synthesis. It mainly verifies the functionality of the design by ignoring the timing constraints. It is also known as netlist level simulation.

#### 2.3.5.3 Static Timing Analysis

It is generally done at implementation and also known as timing simulation. It provides the most accurate picture of the design behavior to the user. It takes almost every constraints and the components into consideration such as wiring, delays and logic block functionality if the target FPGA. It takes a longer time since it provides the detailed simulation unlike the other steps.

#### 2.4 HLS and Design Flow

HLS which stands for High Level Synthesis is generally known as C synthesis, behavioral synthesis, Electronic System Level synthesis or algorithm synthesis. It is a design process that creates the digital hardware implementing the desired behavior of an algorithm. It starts with the high-level specification which accepts an input as the subsets of C, C++, MATLAB, System C, etc. Then that input code is analyzed, architecturally constrained and compiled into RTL (Register-Transfer Level) design in HDL (Hardware Description Language).

The designers can build and verify the hardware design efficiently since HLS provides a better control over optimizing the design and the designer can design at every abstraction levels including gate-level, RTL-level and algorithmic-level. HLS can be performed on different platforms by using various tools provided by the different companies. Some wellknown HLS tools are Quartus II by Altera, SpeedSim by Cadence, VCS by Synopsys, Vivado simulator by Xilinx, etc.

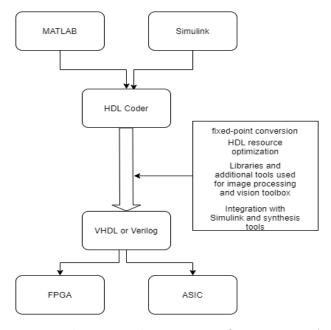

Moreover, there are some tools that allow rapid prototyping in which users has to implement their algorithm in high level language and port those algorithms into HDL codes for the FPGA systems. For example, MATLAB HDL coder allows users to input the algorithm in form of matlab files and it creates HDL code. Also PYNQ which allows users to implement their algorithms in Python and implement them of hardware. Although these design tools use hardware libraries and overlays for this and some tools do not support every kinds of data structures. In figure, HLS design flow by xilinx is shown below.

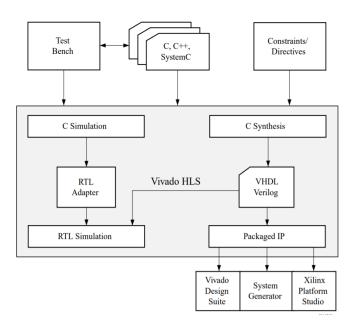

Fig. 2.4.1: Vivado HLS Design Flow[15]

### CHAPTER 3

### Related Works

# 3.1 Implementing Image Enhancement algorithms on FPGAs

The main reasons for implementing Image Enhancement algorithms on FPGAs are the ability of FPGAs to be standalone quantity to run the algorithms by providing compelling performance in terms of trading off with constraints and real time realization of the algorithms. It is desirable to have real time processing ability in any hardware which acts as a standalone quantity and performs task these days. When it comes to image processing applications, serial processors have some limitations as these applications consist of complex mathematical operations, high quality images and larger datasets. FPGAs do not only provide alternatives to implement these image processing algorithms, they also allow users to be able to trade off with hardware constraints by giving options for hardware implementation in different configurations by achieving parallelism.

#### 3.1.1 Exploiting Parallelism

Parallelism in image processing algorithms exists in two major forms[10]; Spatial and Temporal. Spatial Parallelism means to divide an image in multiple parts or the sections and to process the different parts of the image simultaneously. Whereas, Temporal Parallelism means to represent an algorithm as a time sequence of a different simultaneous steps or operations. FPGA implementations can possibly achieve these

both types of parallelism by using the amalgamation of two methods. To exemplify that, FPGA can be configured to divide an image and separate those sections via pipelines and all of those sections can be processed simultaneously.

Although the degree of parallelism depends on the processing mode and the hardware constraints introduced by the system. These constraints can be classified in three parts; Timing constraints, Resource constraints and Bandwidth constraints. These constrains make the mapping of the algorithm to desired hardware more difficult as they are inseparably linked with both the approaches that are low-level approach and high-level approach. The mapping of an algorithm to hardware is basically a technique to specify any image processing algorithm in any hardware language that can be compiled into a netlist.

Talking about the parallel hardware, in [32] the authors have successfully designed a highly parallel architecture model of the algorithm for enhancing the retinal fundus image to achieve high throughput. Their algorithm is based on brightness control, contrast stretching and histogram equalization as well as they have achieved temporal parallelism. For example, the brightness control algorithm has been implemented in parallel to maintain the same brightness level in image for multiple pixels. This algorithm is designed by interconnecting the different blocks such as constant, compare to the constant, add, etc. The constant block generates different constants which are compared by the different inputs by the compare to constant blocks. If the comparison is true the output is 1 and if the comparison is false the output is 0. The view of the input values is enabled by the display block which accepts real and complex signals. The input value is taken as the pixel value as the constant, it is added to the brightness factor and compared with 255. If the addition is less than 255 than it is taken as the output otherwise it is adjusted to the maximum value 255.

The algorithm is mapped using high-level mapping approach and MATLAB Simulink platform is used for interactive graphical environment since it provides the set of block libraries for design, simulation and implementation. Then the Bit-file is generated for the hardware implementation. The hardware implementation is done on Spartan 3E FPGA of Xilinx family and for software development Xilix ISE 14.1 tool is used.

#### 3.1.2 Low-Level Approach

At this level of implementation, a designer has to deal with all the constraints manually and to achieve this level of abstraction the design must be specified at the RTL (register Transferred Level) to maintain the better control and optimization. This approach provides a better control over the constrains and flexible optimization since it deals with the low-level languages such as VHDL and Verilog. Success and significant speed increment over a sequential architectures have also been shown in the low-level mapping which is used in this approach[13].

The better control feature of this approach refers that the user has to be ready to deal with the hardware constraints and its implementations directly. The timing constraints of real time image processing applications introduce some additional complexities such as memory bandwidth, resource conflicts and the necessity for the pipeline.

Although, design at this level of abstraction requires an intimate hardware knowledge since programming for RTL for hardware at this level is similar to assembly level language in software domain which is considered to be difficult and time consuming due to the usage of complex image processing algorithms and larger image sizes. So, this approach is used to implement very small applications. Moreover, these days there are number of tools available in market which make easy to map the algorithm to hardware in very little time and they also allow the users to program in high-level languages which basically hide the low-level details. Because of this this approach is not widely used.

Talking about the low-level mapping[30] the authors have successfully performed the hardware implementation of a simple yet effective image enhancement method for automatic vehicle number plate detection. Their method was based on sharpness control, brightness control, histogram equalization and contrast stretching. The main motive of this method of image enhancement method was to improve the image quality which is going to be used in some specific application like Optical Character Recognition(OCR). The main cause for poor image quality is low light in this application and

an alternative option which is to use a flash light with camera will raise problems for the drivers. The algorithm have been implemented in form of different blocks such as sharpness control, brightness control, contrast stretching and histogram equalization. These blocks have been implemented by using Flip-Flops, multiplexers, comparator, adder, multiplier, etc. Xilinx synthesizer for FPGAs by using verilog HDL codes has been used to generate the hardware architecture according to the arrangement. They also have provided separate block diagram for each operations referring their internal architectures. They used Verilog HDL for all the coding and synthesis that on Xilinx ISE v14.7. A Xilix Virtex V has been used to verify the hardware implementation. Power calculations were done by using Xilinx power estimator tool. Along with this timing analysis and device utilization report have been shown. The only limitation of their method was limited image size 500x200 pixels due to limited memory.

#### 3.1.3 High Level Approach

Unlike the low-level approach, the high-level approach is associated with the highlevel languages and their compilers based on their popular software languages [10]. The ultimate motive of these high-level languages is to hide low level details from the developers such as pipelines and scheduling. In this approach the parallelism and scheduling is exploited by the compiler based on various optimization techniques such as loop unrolling to exploit spatial parallelism and automatic pipeline to exploit temporal parallelism. So, for hardware designing, this high-level approach would be easy and simple for the users to design any hardware in short time of period without engaging in the low-level details since the users only have to make few changes in the existing programs, compile it and to generate a resulting FPGA file. This allows a more algorithmic approach to a hardware design and appears to be a perfect solution for image processing, which already has a large stable code base of well defined software algorithms for implementing so many common image processing operations[10]. It also makes mapping of netlist from algorithm easier for the users who do not have that much knowledge of low-level issues of hardware design. Although, this hardware design by using software turns out be unwise in some cases when it comes to implementing some mathematical expressions such as multiplication and square root since they turn out to be very costly in hardware design. From software point of view they are too easy to exploit because it reinforce the software mindset but they are costly at the hardware end. So, in some cases it may not represent the best algorithm to used for some specific processing modes of FPGAs and this algorithm may need to be rewritten to meet the hardware constraints which leads to low-level mapping. Authors in [24] have used the high-level approach to map the multi-directional Sobel algorithm to FPGA. According to their paper, hardware implementation of edge detection algorithms for real time image processing applications is one of the major issue in the field of hardware implementation as edge detection technique plays an important role in texture analysis, image segmentation and pattern recognition. In image processing applications generally Sobel operator is used for edge detection. So the authors tried to propose an FPGA based hardware architecture of real time edge detection technique based on Sobel operator. In their proposed architecture the edges of an image can be detected into four different directions; vertical, horizontal, left diagonal and right diagonal. Moreover, there are two outputs of the algorithm that are resultant of vertical and horizontal directions and resultant of left diagonal and right diagonal direction. These output are used according to the necessity of the applications. The size of input image is taken as 1024 x 1024 pixels in gray scale. The input to their algorithm comes from a camera in form of serial single bits of pixel by a synchronous clock and entered into 3 x 3 arrays. Then gradient calculation is performed by three cascade shift registers. After that in the window processor block four different gradients are calculated simultaneously and the output of this block is given to the comparator block in the form of positive, negative or zero. Now, the comparator block has main three functions; taking the absolute values of the four inputs, calculating the resultant values and to perform the thresholding operations on all results so that they do not exceed 255. The data flow is controlled by the the controller block which also decides when to save the data. Apart from that it also controls the counter which generates addresses for the RAM block.

For simulation they have used Xilinx Spartan3 XC3S200 FPGA chip. For synthesiz-

ing the VHDL modeling codes the ISE9.2 and MATLAB have been used and then device utilization summary has been shown. This high-level approach was successfully employed in their method since it was very simple and small algorithm for edge detection technique. Moreover, the power consumption and timing constraints were not considered in their method.

#### 3.1.4 Design Patterns: A more flexible solution

The both mapping approaches discussed above have their own disadvantages. Highlevel approach reinforces software mindset which results in less optimal mappings. Whereas, low-level approach helps in overcoming the shortcomings imposed by highlevel approach but is it more labour intensive and puts more emphasis on the hardware reusability which has lead to some common challenges. Design patterns proposed in [13] is a common methodology for design in software engineering but it taken to the image processing on FPGA from architectural engineering. Design patterns basically are the pattern which correlate the possible mapping techniques used to manage the constraints as we envision applying them. Then it focuses on the key elements of the solutions that may possibly be reused in mapping. A way to convey the design experience is provided by the recorded patterns in informative and structured manner by locking the essence of solution. These generalized solutions offer suitable abstraction for hardware and emerging languages in this fast paced area because their usage is not restricted to any particular suitable platform or language. In this approach while dealing with some complex mathematical operations such as square root and multiplication which can possibly be expensive and lead to an inefficient usage of resources, generally precalculated expression values are used. Those values are generally stored in look-up tables(LUTs) in this method which is general enough so that we can use it for any future situations which uses complex expression multiple times. Although, this design patterns are more useful to the problem which is occurring over and over. So it is more suitable for the instance when the mass production is being done of the hardware.

# 3.2 Fixed Floating Point Configurations and Their Trade-off

Architecture wise, the digital signal processing units can be commonly classified in two parts; floating point configuration and fixed point configuration. These configurations refer to the format which is used to store and manipulates the numbers or the pixel values in the device. Now that most of the image processing applications consist of complex algorithms which are generally based on the mathematical operators, the designers ought to consider the ways for storing the values and manipulating them. From these two types fixed point configuration allows higher precision as per the bit-width representation [23] but not all the cases are about only higher precision, sometimes data representation also plays an important role especially in the high performance computer system to achieve suitable dynamic range. Thus, in this case floating point configuration provides a feasible solution. Although these floating point algorithms are generally implemented on software and run on microprocessors, which results in performance penalty in data transfer between ALU and program memory Talking about image processing applications using FPGA, also known as Bottleneck Problem. This problem can be overcome by the usage of multi-core processor. Nowadays, GPUs are the microprocessor based solution and they improve the performance by working with higher frequency, though results in a bottleneck problem and higher power consumption which is a major drawback. Now, talking about the implementation of the complex algorithms on FPGA, the designers can improve the performance by using the hardware resources and capabilities of parallelism of FPGA. But, ideally only fixed point arithmetic is provided by FPGAs which in turn binds in limited dynamic range. Thus it is up to designers to trade-off between the cost in area and the bit-width representation. But nowadays, many platforms such as Intel, Xilinx and MATLAB provide users to efficiently use the floating point configuration for hardware implementation for impactful DSP designs considering FPGA as suitable environment to implement floating point algorithms due to parallelism and pipeline.

In [4] authors have compared fixed and floating point configuration for the implementation of their deflectometry algorithm and acclaimed that the fixed point configuration is efficient for FPGAs. Mainly, in deflectometry an automatic analysis of the reflected patterns of the target surface is performed which can be useful in such applications as to finding the irregularities in surface area and collecting the topographical information of target material. Their algorithm basically analyses the series of reflected image patterns and determines the defects or irregularities on the surface. These patterns are generated by using camera and reflected on the computer screen in form of horizontal and vertical fringes. Zynq based internal architecture consisting all blocks such as memory, controller, and processing has been proposed along with the FPGA based architecture of their method. They used Xilinx HLS design tool for rapid prototyping and synthesis. After that, Vivado design suite was used for the complete design and Xilinx SDK was used for software design.

Mainly two approaches were used in their design; 32-bit fixed and floating point as well as the timing and utilization for each approaches were compared and shown. They have acclaimed that the fixed point configurations were 35% faster in terms of execution time than floating point approach. Moreover, the fixed point configuration in their method consumed lesser, almost half of the resources as compared to the floating point configuration.

### CHAPTER 4

### Methodology

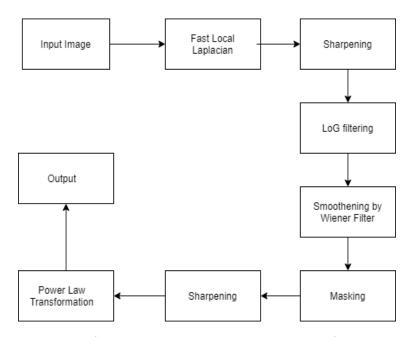

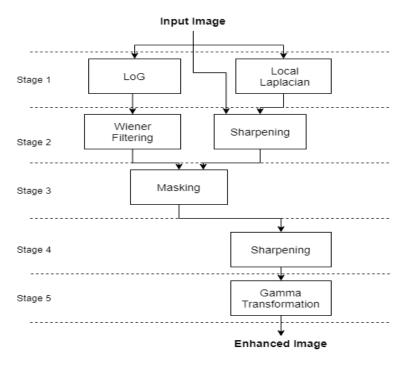

To tackle the problem statements proposed in the first chapter we would like to propose these following methods. First, to overcome the limitation of the image enhancement algorithm due to the usage of the Laplacian Operator, we would like to use Local Laplacian operator in order to make the image enhancement algorithm useful for even coloured images. Moreover, it would help us in improving execution time as the Fast Local Laplacian operator is faster than the Laplacian operator in terms of run time. Secondly, to overcome the performance problem of Sobel operator in edge detection application we would use LoG operator which would improve the effectiveness of edge detection. At last as resource management, power consumption and execution time are very important parameters in hardware implementation, we would like to implement an image enhancement algorithm on parallel hardware to achieve better power consumption and execution time. For the initial implementation, Python3 platform has been used to verifying different image enhancement operations of the algorithm. For RTL simulation MATLAB has been used as it is one of the best platform to implement image processing algorithms because it offers an ease in processing 2D and 3D data or image and provides different DSP (Digital Signal Processing) blocks to develop algorithms and design. To test, verify the generated HDL script generated by MATLAB Coder on a targeted hardware, Quartus Prime Lite has been used. Quartus Prime provides optimization and physical synthesis which makes the design performance better in terms of area and compilation time. The implementation flow of this algorithm has been shown below in the figure.

Fig. 4.0.1: Hardware Implementation flow using MATLAB

## 4.1 Overcoming the Limitation of Laplacian Operator by Edge-Aware Image Processing

Edge detection techniques are indisputably important in image processing since they link with different applications with different domains. Generally, in image enhancement methods Laplacian operator is used for edge detection or in simple words making the edges more appealing in the beginning of the algorithm. Laplacian Operator is basically second order derivative of an image which can be developed by convolving the mask around the targeted image whose kernel computes the addition of the weighted gray level differences between the pixel and its neighbours. So, its performance in image enhancement of gray scale images is remarkably good but its application is only limited to gray scale images. This operator can be extended by applying it to each separate R, G, B component and combining those results to bring in the sharpened coloured image. But, it has been reported that the simple extension like this is not the best possible solution[16]. So, to overcome the mentioned problem, Local Laplacian operator really comes handy as it operates on the principle of edge-aware

image processing.

The Edge-aware image processing aims to modify the input image I into output image I' in order to maintain or retain the large discontinuities of image I i.e, edges. Moreover, it also aims to retain the overall shape or profile of those discontinuities without making edge transitioning smoother or sharpen irrespective of the increment or decrement in the amplitude of the edges. This edge-aware image processing technique is significant for some techniques that deals with manipulating the images in spatial domain. Although if the user fails in implementing these techniques, the result would cause haloing, shifted edges reversals of gradient, etc. The local laplacian operator has been developed based on the pyramid-based edge aware filtering to provide a further approach to edge-aware image processing, using a multi-scale representation using Gaussian/laplacian pyramid or a wavelet decomposition[17]. The author of [17] has proposed an algorithm to implement the local laplacian operator based on the Laplacian pyramid.

#### 4.1.1 Local Laplacian Filtering Algorithm

Giving an overview of the algorithm, an image is fed as an input and then each pixels of Gaussian pyramid of the input image is mapped by pointwise function and then intermediate Laplacian pyramid is generated from these intermediate results. At last the appropriate pixel is copied in the output Laplacian pyramid. The whole process is repeated over all scales for every pixel of the input image until the pyramid is filled which then gives the final result. The user can generate only some intermediate parts of the image for more efficient computation instead of the whole image. The general flow of the Local Laplacian algorithm has been shown below in the figure.

The major available components of this algorithm are  $\alpha$ ,  $\beta$  and  $\sigma$ . A user can freely manipulate the details of the targeted image without specifying the decomposition of an image into these components proposed by [28]. These components have their own functions and are used to control the output such as:

•  $\alpha$  controls the details of the image. if  $\alpha > 1$  then it depicts detailed enhancement

Remapped sub-image

Gaussian Pyramid

Remapped Laplacian pyramid

Output Laplacian pyramid

Fig. 4.1.1: General Flow of Local Laplacian Algorithm

and  $\alpha < 1$  then it depicts the detailed smoothening.

- $\beta$  controls overall appearance of an image.  $\beta > 1$  depicts intensity range expansion and  $\beta < 1$  depicts intensity range compression.

- $\sigma$  is a constant which gives a threshold to fix what comprises the details.

First of all Gaussian pyramid G for each levels  $(l_1, l_2, l_3...)$  of the input image I is created from bottom to top, i.e.,  $G_0, G_1, ..., G_l - 1$ . Then the Laplacian pyramid L is computed from top to bottom, i.e.,  $L_l - 1, L_l - 2, ..., L_0$ . The output O of this algorithm is the collapse of all the Laplacian pyramid levels. The function is shown as below.

$$Q_k, q = LocalFilter_{\alpha,\beta},_{\sigma}(I_k, q)$$

(1)

The algorithm to implement local Laplacian proposed by [17] is shown below.

#### Algorithm 1 Local Laplacian Filtering

**Input**: Image  $I, \alpha, \beta, \sigma$