## University of Arkansas, Fayetteville

## ScholarWorks@UARK

**Graduate Theses and Dissertations**

5-2022

## High Power Density and High Efficiency Converter Topologies for Renewable Energy Conversion and EV Applications

Dereje Lemma Woldegiorgis University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### Citation

Woldegiorgis, D. (2022). High Power Density and High Efficiency Converter Topologies for Renewable Energy Conversion and EV Applications. Graduate Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/4497

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

# High Power Density and High Efficiency Converter Topologies for Renewable Energy Conversion and EV Applications

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Dereje Lemma Woldegiorgis

Arba Minch University

Bachelor of Science in Electrical and Computer Engineering, 2009

University of Oviedo

Master of Science in Sustainable Transportation and Electrical Power Systems, 2014

## May 2022 University of Arkansas

| This dissertation is approved for recom | nmendation to the Graduate Council. |  |

|-----------------------------------------|-------------------------------------|--|

| H. Alan Mantooth, Ph.D.                 |                                     |  |

| Dissertation Director                   |                                     |  |

| Juan C. Balda, Ph.D.                    | Yue Zhao, Ph.D.                     |  |

| Committee Member                        | Committee Member                    |  |

|                                         |                                     |  |

| David Huitink, Ph.D.                    |                                     |  |

| Committee Member                        |                                     |  |

#### **ABSTRACT**

This dissertation work presents two novel converter topologies (a three-level ANPC inverter utilizing hybrid Si/SiC switches and an Asymmetric Alternate Arm Converter (AAAC) topology) that are suitable for high efficiency and high-power density energy conversion systems. The operation principle, modulation, and control strategy of these newly introduced converter topologies are presented in detail supported by simulation and experimental results. A thorough design optimization of these converter topologies (Si/SiC current rating ratio optimization and gate control strategies for the three-level ANPC inverter topology and component sizing for the asymmetric alternate arm converter topology) are also presented.

Performance comparison of the proposed converter topologies with other similar converter topologies is also presented. The performance of the proposed ANPC inverter topology is compared with other ANPC inverter topologies such as an all SiC MOSFET ANPC inverter topology, an all Si IGBT ANPC inverter topology and mixed Si IGBT and SiC MOSFET based ANPC inverter topologies in terms of efficiency and cost. The efficiency and cost comparison results show that the proposed hybrid Si/SiC switch based ANPC inverter has higher efficiency and lower cost compared to the other ANPC inverter topologies considered for the comparison. The performance of the asymmetric alternate arm converter topology is also compared with other similar voltage source converter topologies such as the modular multilevel converter topology, the alternate arm converter topology, and the improved alternate arm converter topology in terms of total device count, number of switches per current conduction path, output voltage levels, dc-fault blocking capability and overmodulation capability. The proposed multilevel converter topology has lower total number of devices and lower number of devices per current conduction path hence it has lower cost and lower conduction power loss. However, it has lower number of output voltage

levels (requiring larger ac interface inductors) and lacks dc-fault blocking and overmodulation operation capabilities.

A converter figure-of-merit accounting for the hybrid Si/SiC switch and converter topology properties is also proposed to help perform quick performance comparison between different hybrid Si/SiC switch based converter topologies. It eliminates the need for developing full electrothermal power loss model for different converter topologies that would otherwise be needed to carry out power loss comparison between different converter topologies. Hence it saves time and effort.

© 2022 Dereje Woldegiorgis All Rights Reserved

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to express my sincere gratitude to my advisor, Prof. H. Alan Mantooth for his continued guidance, support, and mentorship during my PhD study and research. His tremendous research experience, broad knowledge, critical thinking, great leadership, and personality benefited me a lot to grow personally and academically. He is an inspiring role model that I look up to in my future career growth.

I am also very grateful to my other dissertation and advising committee members, Profs. Juan C. Balda, Yue Zhao, and David Huitink for their valuable suggestions and helpful discussion during my PhD study and research. I am also thankful to the NCREPT test engineers, Dr. Chris Farnell and Justin Jackson, for their technical support during testing at NCREPT. My appreciation also goes to all my colleagues with whom I have worked together on multiple projects and have had valuable discussion and collaboration with.

## **DEDICATION**

This dissertation is dedicated to my parents and friends who helped me achieve this goal. My heartfelt gratitude goes to them for their continued support throughout my entire life.

## TABLE OF CONTENTS

| CHAPTER  | 1 INTRODUCTION AND BACKGROUND                                     | 1          |

|----------|-------------------------------------------------------------------|------------|

| 1.1      | Renewable Energy and Electric Vehicle (EV) Market Trends          | 1          |

| 1.2      | Role of Power Electronics in Renewable Energy and EV Applications | 8          |

| 1.3      | The Future Power Electronics Demand                               | 10         |

| 1.3.1    | High Efficiency and High-Power Density                            | 11         |

| 1.3.2    | Low Cost                                                          | 12         |

| 1.4      | Solutions for the Future Power Electronics Needs                  | 14         |

| 1.4.1    | Semiconductor Device Solutions                                    | 14         |

| 1.4.2    | Power Converter Topology Solutions                                | 17         |

| 1.4.3    | Passive Component Solutions                                       | 19         |

| 1.4.3.1  | Dc-link Capacitor Choice                                          | 19         |

| 1.4.3.2  | Inductor Choice                                                   | 20         |

| 1.4.4    | New Design Approaches                                             | 21         |

| 1.5      | Dissertation Objectives and Organization                          | 22         |

| 1.6      | Reference                                                         | 24         |

| CHAPTER  | 2 THE THREE-LEVEL ANPC INVERTER EMPLOYING HYBI                    | RID Si/SiC |

| SWITCHES |                                                                   | 29         |

| 2.1      | Introduction to Three-level Inverter Topologies                   | 29         |

| 2.2      | ANPC Inverter Modulation Strategies                               | 31         |

| 2.3      | State of the Art ANPC Inverter Topologies                         | 34         |

| 2.4      | The Proposed ANPC Inverter Employing Hybrid Si/SiC Switches       | 36         |

| 2.4.1    | Modulation and Semiconductor Device Configuration                 | 36         |

| 2.4.2    | Electro-thermal Power Loss Model                                  | 37         |

| 2.4.3    | Hybrid Si/SiC Switch Design Considerations                        | 44         |

| 2.4.3.1  | Si/SiC Switch Gate Control Strategies                             | 44         |

| 2.4.3.2  | Si/SiC Switch Current Rating Ratio Optimization                   | 45         |

| 2.5      | Performance Comparison with Other ANPC Inverter Topologies        | 49         |

| 2.5.1    | Power Loss and Efficiency Comparison                              | 50         |

| 2.5.2    | Cost Comparison                                                   | 55         |

| 2.6      | Experimental Validation                                              | 56    |

|----------|----------------------------------------------------------------------|-------|

| 2.7      | Conclusion                                                           | 62    |

| 2.8      | Reference                                                            | 63    |

| CHAPTER  | 3 FIGIRE OF MERIT FOR HYBRID Si/SiC SWITCHES                         | 68    |

| 3.1      | Introduction                                                         | 68    |

| 3.2      | Review of Semiconductor Device Figure of Merits                      | 70    |

| 3.3      | Improved Figure of Merit for Hybrid Si/SiC switches                  | 73    |

| 3.3.1    | Improved Device Figure of Merit                                      | 73    |

| 3.3.2    | Converter Figure of Merit                                            | 78    |

| 3.4      | Experimental Validation                                              | 81    |

| 3.5      | Demonstration of the Applicability of the Proposed Figures of Merits | 86    |

| 3.6      | Conclusion                                                           | 91    |

| 3.7      | Reference                                                            | 93    |

| CHAPTER  | 4 THE ASSYMETRIC ALTERNATE ARM CONVERTER (AAAC) TOPO                 | LOGY: |

| A NEW MU | JLTILEVEL CONVERTER TOPOLOGY FOR HVDC APPLICATIONS                   | 97    |

| 4.1      | Introduction                                                         | 97    |

| 4.2      | Topology Structure and Operation                                     | 100   |

| 4.3      | Modulation and Control Strategy                                      | 104   |

| 4.3.1    | Ac Side Control Strategy                                             | 104   |

| 4.3.2    | Dc Side Control Strategy                                             | 106   |

| 4.3.3    | Modulation Strategy                                                  | 107   |

| 4.3.4    | Submodule Capacitor Voltage Balancing Strategy                       | 109   |

| 4.4      | Converter Dimensioning                                               | 111   |

| 4.4.1    | Number of Devices                                                    | 111   |

| 4.4.2    | Submodule Capacitor Sizing                                           | 112   |

| 4.5      | Simulation and Experimental Results                                  | 113   |

| 4.6      | Performance Comparison with Other Similar HVDC Converter topologies  | 117   |

| 4.7      | Conclusion                                                           | 123   |

| 4.8      | Reference                                                            | 125   |

| CHAPTER  | 5 PRACTICAL SUBMODULE DESIGN CONSIDERATIONS FOR DIFF                 | ERENT |

| HVDC CO  | NVERTER TOPOLOGIES                                                   | 129   |

|   | 5.1      | Introduction                                                        | 129 |

|---|----------|---------------------------------------------------------------------|-----|

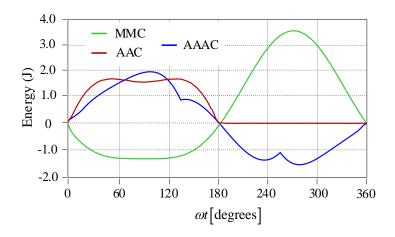

|   | 5.2      | Arm Energy Deviation of Existing Common HVDC Converter Topologies   | 131 |

|   | 5.2.1    | Arm Energy Deviation of the MMC Converter Topology                  | 131 |

|   | 5.2.2    | Arm Energy Deviation of the AAC Converter Topology                  | 133 |

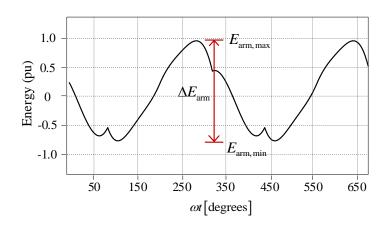

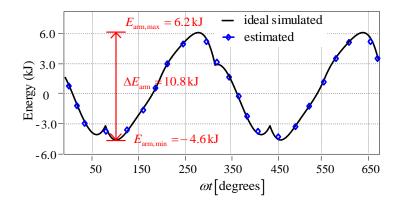

|   | 5.3      | Arm Energy Deviation of the AAAC Topology                           | 135 |

|   | 5.3.1    | Analytical Arm Energy Derivation                                    | 135 |

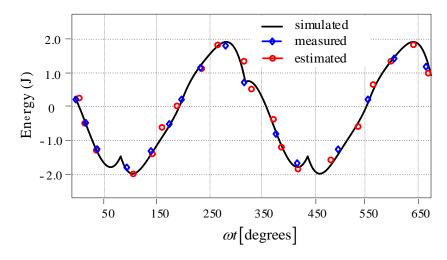

|   | 5.3.2    | Arm Energy Model Validation                                         | 138 |

|   | 5.4      | Energy Storage requirement Comparison for Different HVDC Converters | 146 |

|   | 5.5      | Conclusion                                                          | 147 |

|   | 5.6      | Reference                                                           | 149 |

| C | HAPTER 6 | 5 SUMMARY AND FUTURE WORK                                           | 152 |

|   | 6.1      | Summary                                                             | 152 |

|   | 6.2      | Future work                                                         | 153 |

## LIST OF FIGURES

| Figure 1-1 World total energy supply in EJ.                                                                                                                       | 1    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1-2 Global annual CO <sub>2</sub> emission.                                                                                                                | 2    |

| Figure 1-3 Global cumulative wind installation.                                                                                                                   | 4    |

| Figure 1-4 Global cumulative PV installation.                                                                                                                     | 5    |

| Figure 1-5 Annual PV system cost reduction.                                                                                                                       | 6    |

| Figure 1-6 PV panel efficiency improvement.                                                                                                                       | 6    |

| Figure 1-7 Annual passenger-car and light-duty vehicle sale.                                                                                                      | 7    |

| Figure 1-8 US actual and forecast EV sale.                                                                                                                        | 8    |

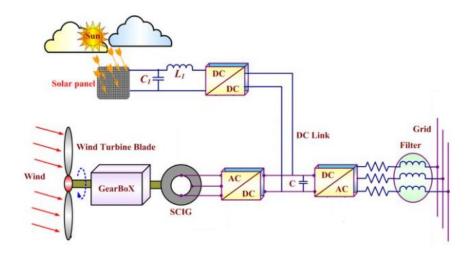

| Figure 1-9 Integration of Wind and PV energy to the grid.                                                                                                         | 9    |

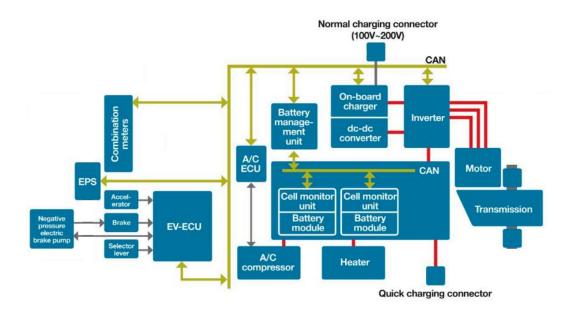

| Figure 1-10 Diagram of typical electric vehicle system.                                                                                                           | . 10 |

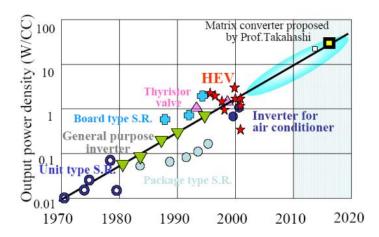

| Figure 1-11 Converter power density improvement over time.                                                                                                        | . 11 |

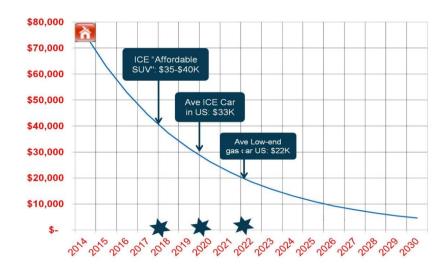

| Figure 1-12 Cost decline for EVs with 200 miles battery capacity.                                                                                                 | . 13 |

| Figure 1-13 LCOE of PV systems: progress and goals.                                                                                                               | . 13 |

| Figure 1-14 Physical properties of different semiconductor devices.                                                                                               | . 14 |

| Figure 1-15 Power loss comparison between Si IGBT and SiC MOSFET.                                                                                                 | . 15 |

| Figure 1-16 Si IGBT and SiC MOSFET cost comparison for EV application                                                                                             | . 16 |

| Figure 1-17 Efficiency comparison between different converter topologies                                                                                          | . 18 |

| Figure 1-18 Total semiconductor chip area comparison for different converter topologies.                                                                          | . 18 |

| Figure 1-19 Dc-link capacitor technology comparison.                                                                                                              | . 19 |

| Figure 1-20 Comparison of different inductor technologies                                                                                                         | . 20 |

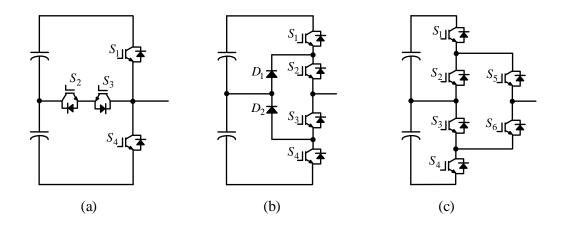

| Figure 2-1 Three level voltage source inverter topologies: (a) T-type inverter, (b) Neutral Policy (NPC) inverter, (c) Active Neutral Point Clamp (ANPC) inverter |      |

| Figure 2-2 Switching diagram for modulation type I: (a) P state, (b) O+ state, (c) O- state, (d) N state.                                                         |      |

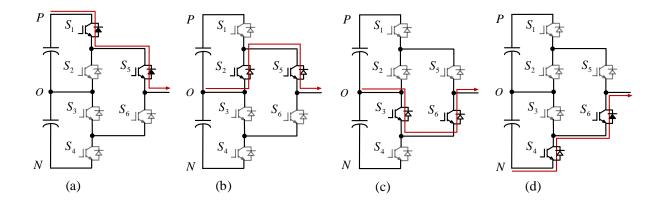

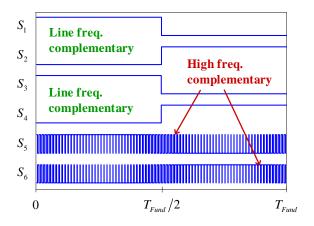

| Figure 2-3 Gate signals for modulation type I                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

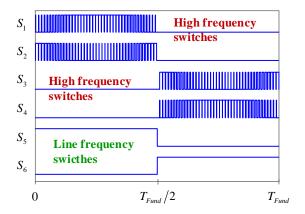

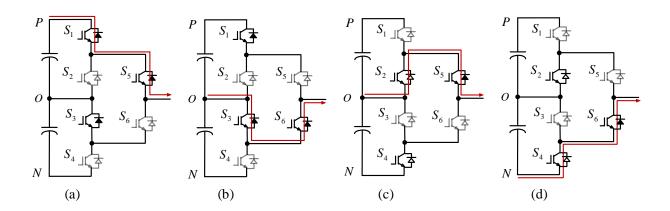

| Figure 2-4 Switching diagram for modulation type II: (a) P state, (b) O <sup>+</sup> state, (c) O <sup>-</sup> state, and (d) N state                                                                                                               |

| Figure 2-5 Gate signals for modulation type II                                                                                                                                                                                                      |

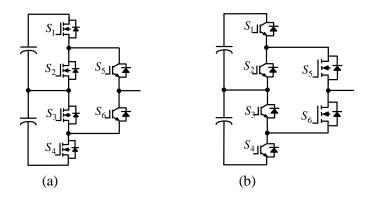

| Figure 2-6 State of the art ANPC inverter topologies: (a) topology proposed in [2.14] and [2.15], (b) topology proposed in [2.16] and [2.17]                                                                                                        |

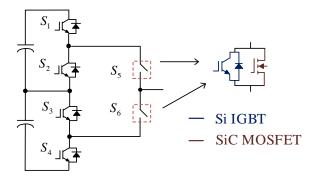

| Figure 2-7 Hybrid Si/SiC switches based ANPC inverter topology proposed in this chapter.                                                                                                                                                            |

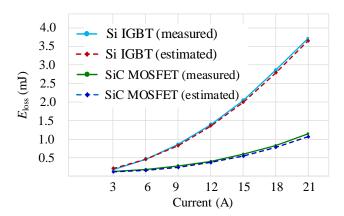

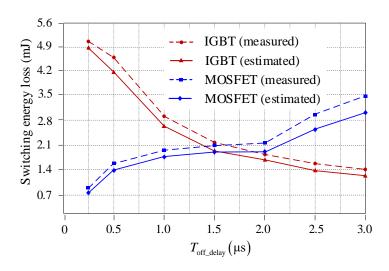

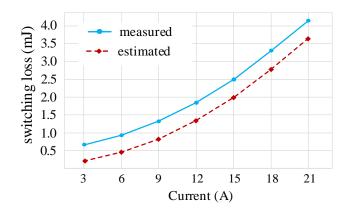

| Figure 2-8 Estimated and measured switching energy losses of the Si IGBT and the SiC MOSFET ( $T_{\rm j} = 25^{\circ}\text{C}$ , $V_{\rm GE} = 15\text{V}$ , $R_{\rm G,IGBT} = 10\Omega$ , $V_{\rm GS} = 18\Omega$ , $R_{\rm G,MOSFET} = 0\Omega$ ) |

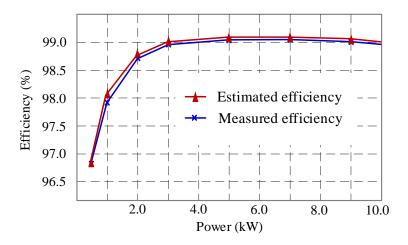

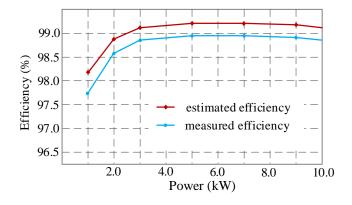

| Figure 2-9 Comparison of measured and calculated efficiency for the proposed ANPC inverter for different power levels                                                                                                                               |

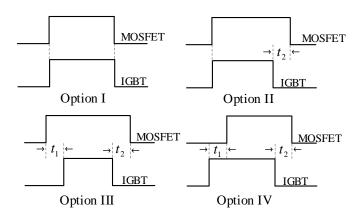

| Figure 2-10 Gate control options for hybrid Si/SiC switches                                                                                                                                                                                         |

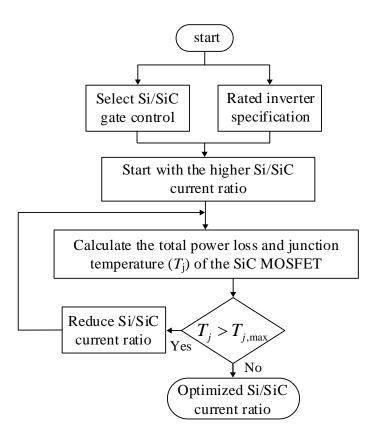

| Figure 2-11 Si/SiC current rating ratio optimization algorithm                                                                                                                                                                                      |

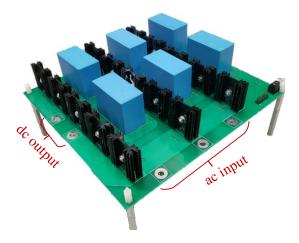

| Figure 2-12 Experimental prototype picture of a 10-kW hybrid Si/SiC switch based ANPC inverter                                                                                                                                                      |

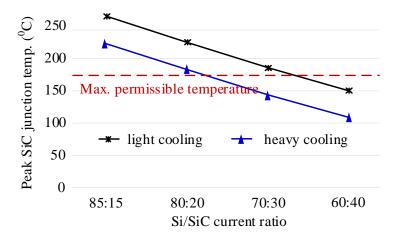

| Figure 2-13 Peak junction temperature of the SiC MOSFET for different Si/SiC current ratios                                                                                                                                                         |

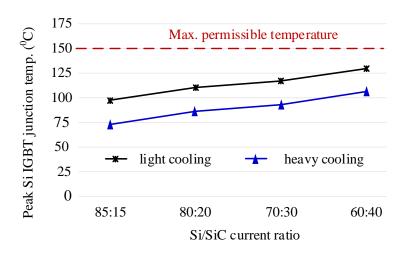

| Figure 2-14 Peak junction temperature of the Si IGBT for different Si/SiC current ratios 49                                                                                                                                                         |

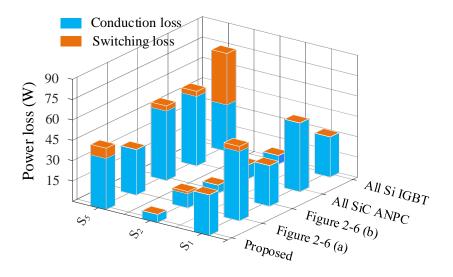

| Figure 2-15 Power loss distribution for the different ANPC inverter topologies under unity power factor                                                                                                                                             |

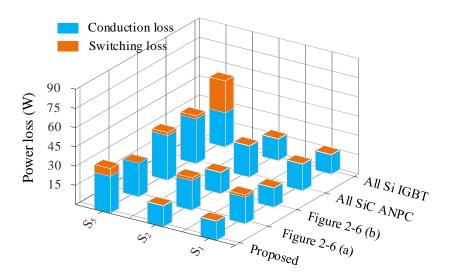

| Figure 2-16 Power loss distribution for the different ANPC inverter topologies for low power factor (pf = $0.6$ ).                                                                                                                                  |

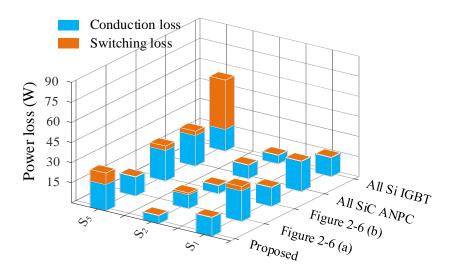

| Figure 2-17 Power loss distribution for the different ANPC inverter topologies for low modulation index ( $m_a = 0.4$ ).                                                                                                                            |

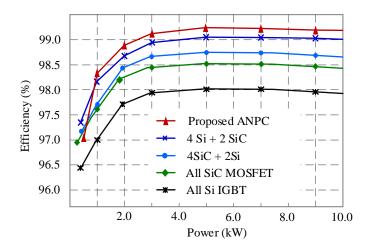

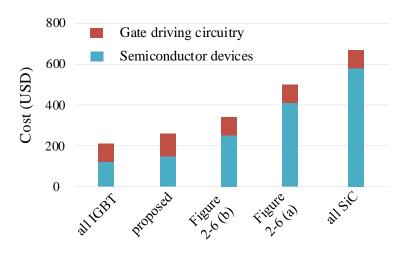

| Figure 2-18 Efficiency comparison between the proposed ANPC inverter and other ANPC inverters for inverter operation                                                                                                                                |

| Figure 2-19 Efficiency comparison between the proposed ANPC inverter and other ANPC inverters for rectifier operation                                                                                                                               |

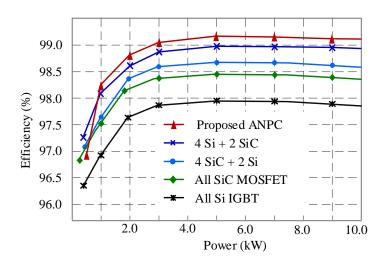

| Figure 2-20 Variable inverter cost comparison for different ANPC inverter configurations. 55                                                                                                                                                        |

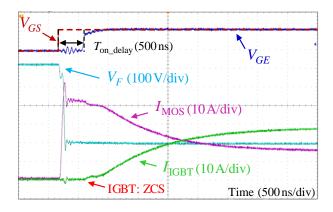

| Figure 2-21 Turn on characteristics of the hybrid Si/SiC switches                                                                                                                                                                                   |

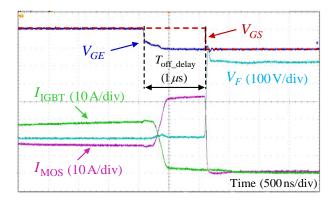

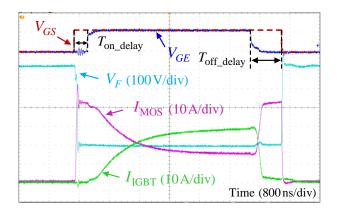

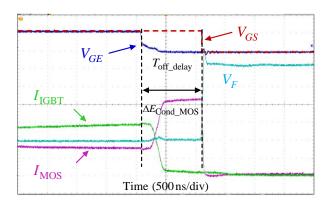

| Figure 2-22 Turn off characteristics of the hybrid Si/SiC switches                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-23 Switching and conduction characteristics of the hybrid Si/SiC switches 59                                                                                                                                                                         |

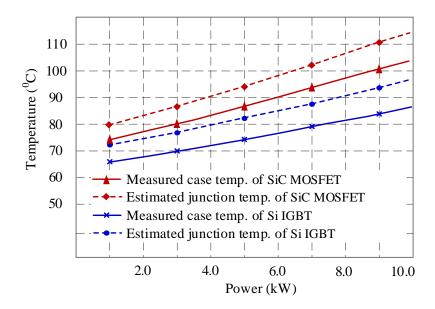

| Figure 2-24 Measured case temperature and estimated junction temperature for the hybrid Si/SiC switches for different power levels                                                                                                                            |

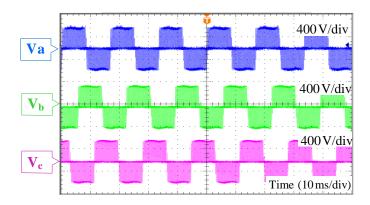

| Figure 2-25 Inverter phase output voltage waveforms                                                                                                                                                                                                           |

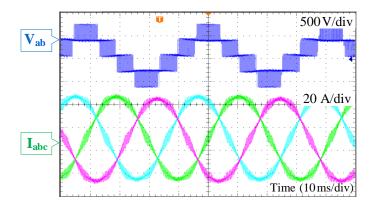

| Figure 2-26 Inverter output line-to-line voltage and three-phase to output current waveforms.                                                                                                                                                                 |

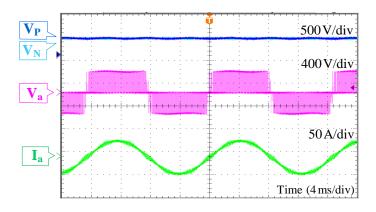

| Figure 2-27 Dc-link capacitor voltages, output voltage and output current waveforms 61                                                                                                                                                                        |

| Figure 3-1 Turn-off characteristics of hybrid Si/SiC switches with turn-off delay time 75                                                                                                                                                                     |

| Figure 3-2 Comparison of measured and estimated minimum hard-switching energy loss for the hybrid Si/SiC switches.                                                                                                                                            |

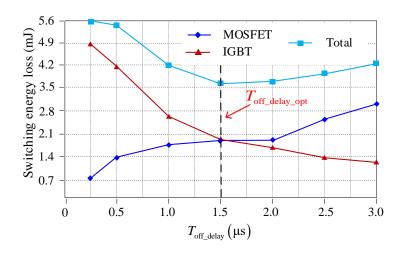

| Figure 3-3 Switching energy loss dependency on gate turn-off delay time for hybrid Si/SiC switches                                                                                                                                                            |

| Figure 3-4 Comparison of measured and estimated minimum hard-switching energy losses for the hybrid Si/SiC switches                                                                                                                                           |

| Figure 3-5 Comparison of measured and estimated converter efficiency                                                                                                                                                                                          |

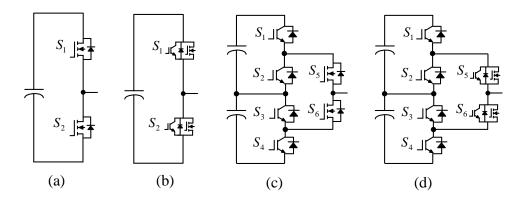

| Figure 3-6 Topologies considered for comparison: (a) two-level SiC MOSFET inverter, (b) two-level hybrid Si/SiC switch inverter [3.16], (c) three-level mixed "Si+SiC" switch ANPC inverter [3.44], (d) three-level hybrid Si/SiC switch ANPC inverter [3.37] |

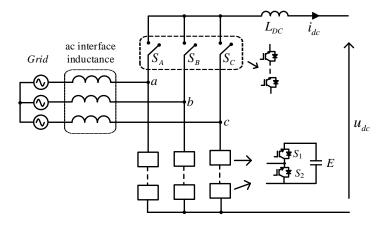

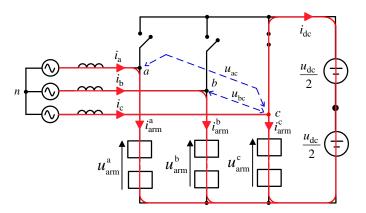

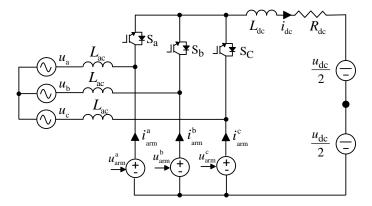

| Figure 4-1 Proposed hybrid voltage source converter topology                                                                                                                                                                                                  |

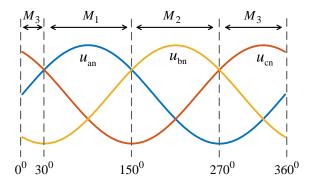

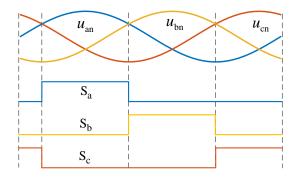

| Figure 4-2 Conduction intervals for upper arm switches                                                                                                                                                                                                        |

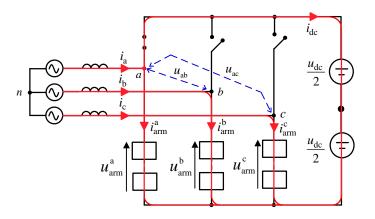

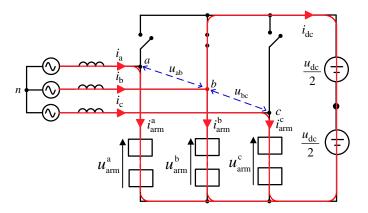

| Figure 4-3 Converter equivalent circuit during operation mode I                                                                                                                                                                                               |

| Figure 4-4 Converter equivalent circuit during operation mode II                                                                                                                                                                                              |

| Figure 4-5 Converter equivalent circuit during operation mode III                                                                                                                                                                                             |

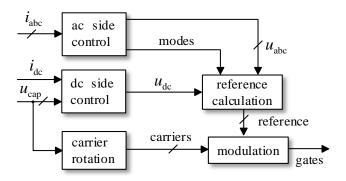

| Figure 4-6 Overall converter control strategy                                                                                                                                                                                                                 |

| Figure 4-7 Ac side converter control strategy                                                                                                                                                                                                                 |

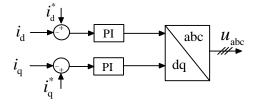

| Figure 4-8 Converter energy and output dc current control strategy                                                                                                                                                                                            |

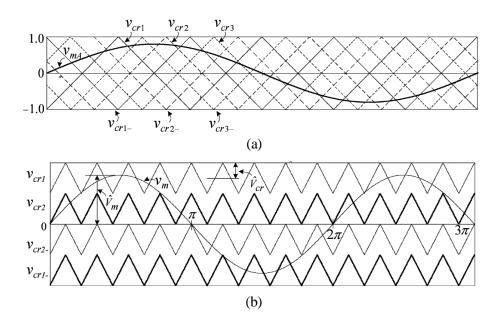

| Figure 4-9 Multicarrier modulation strategies: (a) phase shifted carrier modulation, (b) level shifted carrier modulation strategies                                                                                                                          |

| Figure 4-10 Sorting and rotation algorithm for submodule capacitor voltage balancing 110                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-11 Simulated converter arm energy using ideal circuit simulation                                                                                                                                                          |

| Figure 4-12 (a) converter modulating signals, (b) current through the upper converter arms, (c) current through the lower converter arms                                                                                           |

| Figure 4-13 Simulation results of the converter operation: (a) input ac currents, (b) output phase voltage, (c) output phase-to-phase voltage, and (d) output dc current                                                           |

| Figure 4-14 Experimental prototype picture of the proposed hybrid voltage source converter topology                                                                                                                                |

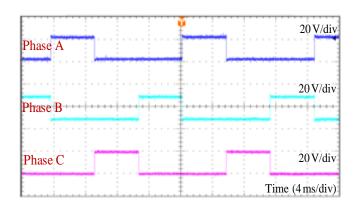

| Figure 4-15 Experimental results of the gate voltages for the converter upper arm switches.                                                                                                                                        |

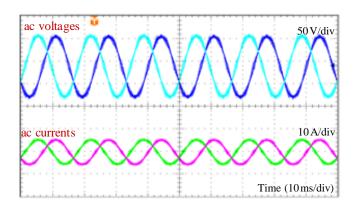

| Figure 4-16 Experimental results of the converter input ac voltages and ac currents 117                                                                                                                                            |

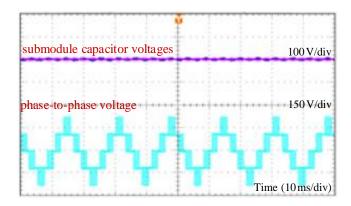

| Figure 4-17 Experimental results of the converter submodule capacitor voltages and the converter phase to phase voltage                                                                                                            |

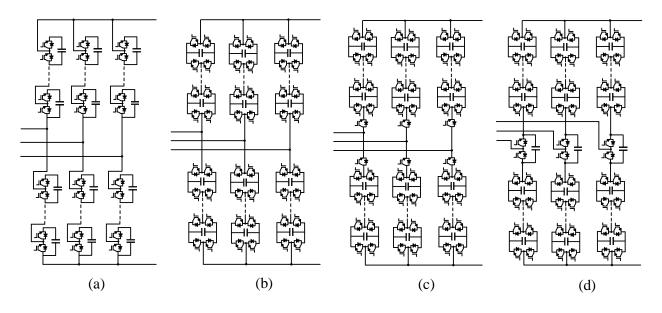

| Figure 4-18 Modular Multilevel Converter topologies based on the basic switching cells: (a) Half bridge MMC (HB MMC), (b) Full bridge MMC (FB MMC), (c) Alternate Arm Converter (AAC), (c) Improved Alternate Arm Converter (IAAC) |

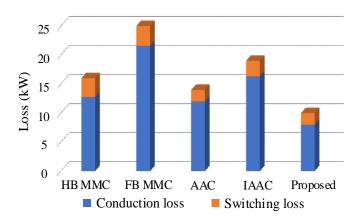

| Figure 4-19 Conduction and switching losses of the semiconductor devices for the different HVDC converter topologies                                                                                                               |

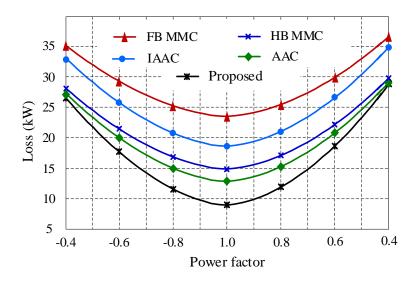

| Figure 4-20 Semiconductor device power loss for the different converter topologies for different power factor values                                                                                                               |

| Figure 5-1 Normalized converter arm energy for power factor of 0.925 leading                                                                                                                                                       |

| Figure 5-2 Ideal converter topology simulation configuration                                                                                                                                                                       |

| Figure 5-3 Gate signals for the converter upper arm switches                                                                                                                                                                       |

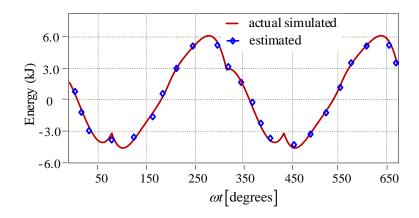

| Figure 5-4 Comparison of theoretically estimated and ideally simulated converter arm energy values.                                                                                                                                |

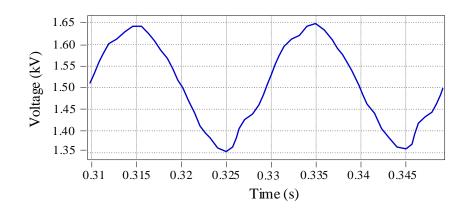

| Figure 5-5 Theoreticallty estimated submodule capacitor voltage waveform                                                                                                                                                           |

| Figure 5-6 Comparison of the theoretically estimated and actual simulated converter arm energy values                                                                                                                              |

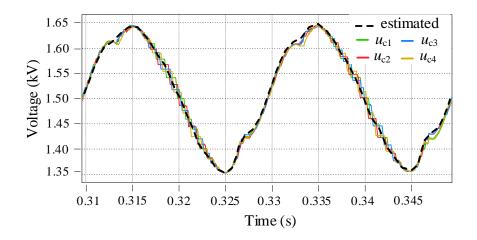

| Figure 5-7 Estimated and simulated submodule capacitor voltage waveforms                                                                                                                                                           |

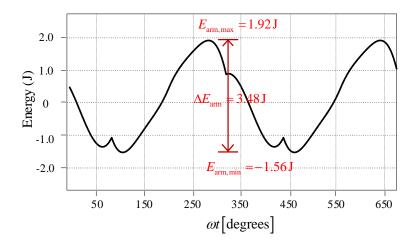

| Figure 5-8 Estimated converter arm energy                                                                                                                                                                                          |

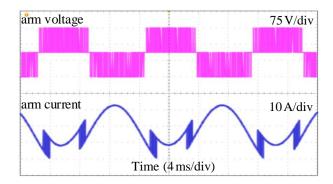

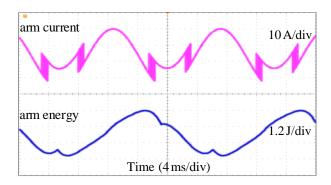

| Figure 5-9 Experimental results of converter arm voltage and converter arm current 145                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Figure 5-10 Experimental results of converter arm current and arm energy                                                                      |  |

| Figure 5-11 Comparison of the estimated converter arm energy, simulated converter arm energy and experimentally measured converter arm energy |  |

| Figure 5-12 Comparison of energy storage requirement for different HVDC converter topologies                                                  |  |

## LIST OF TABLES

| Table 2-1 Switching table for modulation type I                                       |

|---------------------------------------------------------------------------------------|

| Table 2-2 Switching table for modulation type II                                      |

| Table 2-3 Converter specification                                                     |

| Table 2-4 Devices selected for current ratio optimization                             |

| Table 2-5 Converter specification for performance comparison                          |

| Table 3-1 Converter specification                                                     |

| Table 3-2 D-FOM of selected hybrid Si/SiC switches for 10 kW ANPC inverter 86         |

| Table 3-3 Device parameters for C-FOM comparison of different converter topologies 89 |

| Table 4-1 Switching state of half-bridge submodule                                    |

| Table 4-2 Determination of the Converter Operation Modes                              |

| Table 4-3 Reference Voltages for Converter Modulation                                 |

| Table 4-4 Specification for Performance Comparison                                    |

| Table 4-5 Comparison of the Proposed Converter with Other Similar MMC Converters 119  |

| Table 5-1 Converter specification for simulation                                      |

| Table 5-2 Converter specification for the experimental prototype                      |

#### LIST OF PUBLICATIONS

- [1] D. Woldegiorgis, Y. Wu, Y. Wei and H. A. Mantooth, "A High Efficiency and Low Cost ANPC Inverter Using Hybrid Si/SiC Switches," in *IEEE Open Journal of Industry Applications*, vol. 2, pp. 154-167, 2021. (published). (**Chapter 2**).

- [2] D. Woldegiorgis and H. A. Mantooth, "A Converter Figure-of-Merit Accounting for Hybrid Si/SiC Switches and Converter Topology Properties," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*. (under review). (**Chapter 3**).

- [3] D. Woldegiorgis and H. A. Mantooth, "A New Hybrid Voltage Source Converter with Reduced Active Switch Count for HVDC Applications," in *IEEE Transactions on Energy Conversion*, vol. 37, no. 1, pp. 612-622, March 2022. (published). (**Chapter 4**).

- [4] D. Woldegiorgis and H. A. Mantooth, "Arm Energy Investigation and Submodule Capacitor Sizing for the Asymmetric Alternate Arm Converter Topology," in *IEEE Transaction on Power Electronics*. (under review). (Chapter 5).

#### **CHAPTER 1**

#### INTRODUCTION AND BACKGROUND

## 1.1 Renewable Energy and Electric Vehicle (EV) Market Trends

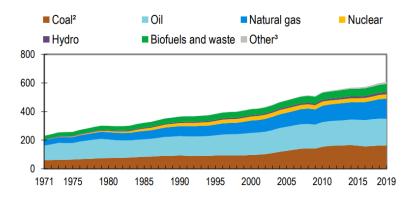

With the increase in population and industrialization, the annual world energy consumption is also increasing constantly. Figure 1-1 shows the total world energy supply in EJ from 1971 to 2019 from conventional energy resources such as coal, oil, natural gas, nuclear, hydro and biofuels [1.1]. As can be seen from this figure, the world total energy supply from these energy resources is constantly increasing year to year and this trend is expected to continue in the years following 2019 [1.2]. Two factors attribute to this annual increase in world energy consumption: the increasing global industrialization and the increasing annual domestic electricity utilization. Prompted by the increase in world population, there has been a constant increase in industrial development around the world especially in developing countries to respond to the needs of the population [1.3], [1.4]. As a result, several new manufacturing, processing, and packaging industries have been built, and the capacity of some of the existing industries such as hotels, tourism, and leisure has been constantly growing over the last couple of decades. The second factor attributing to the annually increasing total energy demand is the annual increase in domestic energy

Figure 1-1 World total energy supply in EJ.

consumption [1.5]. The number and type of energy consuming home appliances such as refrigerators, entertainment, cooking, and cleaning appliances has been constantly increasing year to year especially in developed nations. Not only the number of these appliances is increasing, but also the amount of time they are being used is increasing. This is true especially after the change in lifestyle due to the COVID-19 pandemic [1.6].

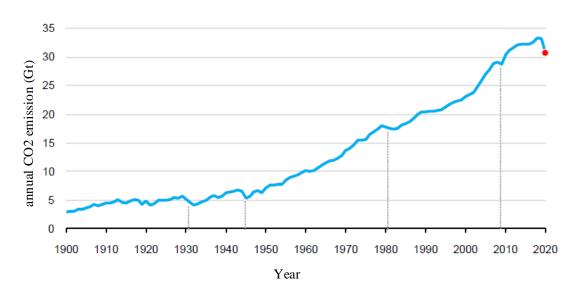

The increasing energy consumption however has brought a significant challenge to the world. The annual CO<sub>2</sub> emission from industries and manufacturing plants into the atmospheric air is parallelly increasing as shown in Figure 1-2 [1.7]. This causes depletion of the ozone layer, which protects the earth from harmful ultraviolent radiations [1.8]. With the depleted ozone layer, the increased concentration of CO<sub>2</sub> and other greenhouse gases such as methane and Nitrous Oxide increases the absorption and emission of radiant energy from the environment causing an annual mean temperature increase to the world, a phenomenon called global warming. This phenomenon causes changing weather patterns such as extreme weather events, melting icebergs, and sea level rise. These changes affect the polar and marine ecosystems [1.9].

Figure 1-2 Global annual CO<sub>2</sub> emission.

To mitigate the harmful effect of CO<sub>2</sub> and other greenhouse gases, several actions have been taken by many stakeholders to reduce the emission of these harmful gases into the atmosphere. Following the Paris climate agreement in 2015, several nations pledged to reduce their CO<sub>2</sub> emission into the atmosphere by fostering the use of alternative clean and renewable energy resources such as Photovoltaic (PV), wind, geothermal, and hydropower through government incentives such as investment tax credits and lower tax rates [1.14], [1.15]. This brought forth a new era in the energy sector where renewable energy resources are increasingly being used.

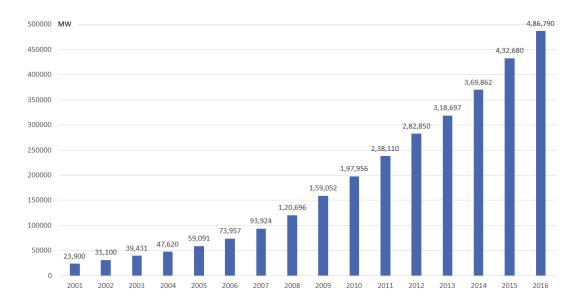

Among the renewable energy resources, wind energy and Photovoltaic (PV) energy resources are the most widely harvested renewable energy resources in recent decades. Figure 1-3 for example shows the global cumulative wind energy installation from 2001 to 2016 [1.10]. As can be seen from the figure, the global annual installed wind energy capacity has been increasing exponentially and this trend has continued in the years following 2016 [1.11] – [1.13]. The high penetration of wind energy generation is primarily derived by several factors such as recent wind energy generation technology advancements, grid modernization, and government incentives [1.14] – [1.16]. The wind energy generation technology has been constantly advancing in the last couple of decades. The size of wind turbines and towers has been increasing year to year, new gearbox and coupling technologies have been introduced and improved generator technologies such as the doubly fed induction generator (DFIG) [1.17] have been developed allowing increased wind energy harvesting. The modernization of the grid such as the introduction of the distributed (non-centralized) grid concept allowing bidirectional power flows also promotes large scale deployment of wind energy generations [1.18], [1.19]. Government incentives through carbon credits and lower tax rates for renewable energy generations has also been one of the main drivers for the increased wind energy generation penetration worldwide [1.14], [1.15].

Figure 1-3 Global cumulative wind installation.

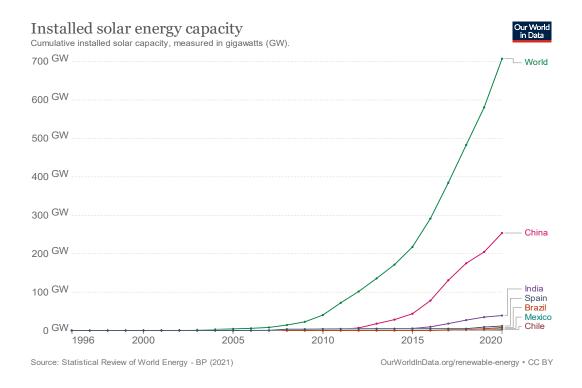

There has also been a rapid increase of Photovoltaic (PV) energy generation in the past couple of decades. As can be seen from Figure 1-4 [1.20], the world global annual installed solar energy capacity has been increasing exponentially, and this trend is expected to continue in the coming years [1.21]. In recent years, many countries especially China have bolstered their annual energy generation from solar energy to migrate from conventional energy resources into clean renewable energy resources to combat the detrimental effect of global warming. Despite its intermittent nature, the solar energy resource continues to be one of the most attractive renewable energy resources in the shift towards clean energy resources.

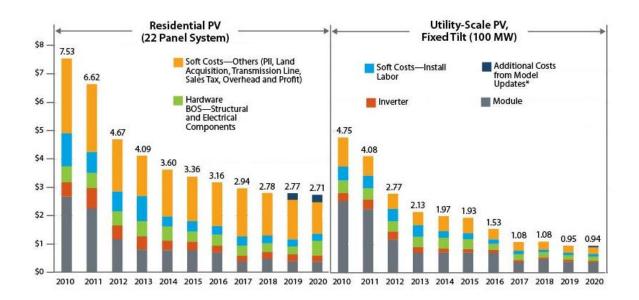

Several factors attribute to the rapid growth of solar energy generation in the last couple of decades. One of such factors is the continuous decline of the cost of solar panels. As can be seen from Figure 1-5 [1.22], the cost of solar panels is constantly dropping annually, and this trend is expected to continue in the coming years according to the US Solar Energy Technology Office

Figure 1-4 Global cumulative PV installation.

(SETO) 2020 Q1 Solar Photovoltaic System and Energy Storage Cost Benchmark [1.22]. The constant solar panel technology advancement and market competition between different manufacturers drives the solar panel cost reduction [1.23], [1.24].

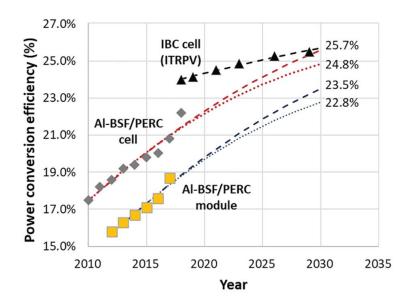

Solar panel efficiency improvement is another factor promoting the increase of solar energy generation. In the last couple of decades, there has been a successful research and development effort that improved the energy conversion efficiency of solar panels. Figure 1-6 shows the achieved and expected solar panel efficiency improvement from 2010 to 2035 [1.25]. As can be seen from the figure, several new higher efficiency solar panel technologies are being introduced. New solar panel materials with lower losses (higher energy conversion efficiency) will continue to be introduced through government funded and industrial research and development programs.

Figure 1-5 Annual PV system cost reduction.

Figure 1-6 PV panel efficiency improvement.

The transportation sector is the next highest producer of greenhouse gases after coal power plants and industries. It produces about 25 percent of the annual greenhouse gases emitted into the atmosphere [1.26]. Therefore, like the energy sector, the transportation sector has also received attention in the last couple of decades in the effort to reduce greenhouse gas emission.

Promoted by government incentives such as investment tax credits, lower tax rates, and ample research and development funds, the last decade has seen increased electrification of the transportation sector starting from small passenger commuter cars to heavy-duty trucks and ships. Several research consortia such as the Center for Power Optimization of Electro-Thermal Systems (POETS), and research and development projects such as the More Electric Aircraft and Horizon 2020 have been established to accelerate the electrification of the transportation sector. As a result of this, automakers have already started cashing in a large amount of revenues annually.

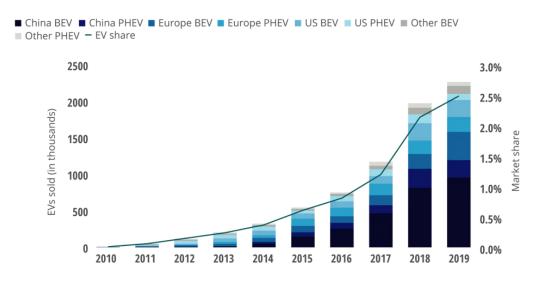

Figure 1-7 shows the number of electric passenger-cars and light-duty vehicles sold annually in the last decade [1.27]. As can be seen from the figure, the number of small electric vehicles sold annually has increased exponentially starting from the birth of the business in 2010. China has the highest share of the market currently, but this is sure to change in the future as government regulation of the transportation sector starts to change in the other parts of the world especially in Europe and the USA.

Figure 1-7 Annual passenger-car and light-duty vehicle sale.

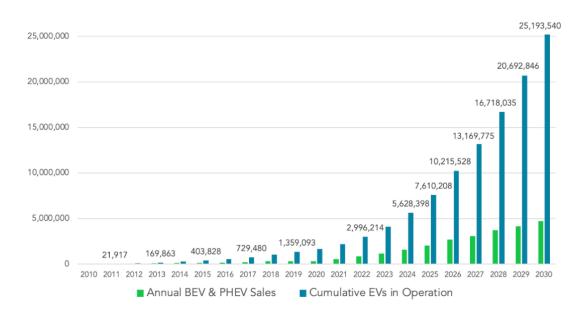

Figure 1-8 shows the number of electric vehicles sold annually in the United States between 2010 and 2021, and the expected sale up to 2030 [1.28]. Like the rest of the world, the annual electric vehicles sale in the United States has also been increasing exponentially, and it is expected to maintain this trend in the coming years. The electric vehicle (EV) business started slowly in the US because of government reluctance to adopt policies and regulations favoring the EV market and scarcity of charging infrastructures. However, this has significantly changed in the second half of the last decade when states started to change their transportation and market regulations to favor EVs and more charging infrastructures are being built around the US.

Figure 1-8 US actual and forecast EV sale.

## 1.2 Role of Power Electronics in Renewable Energy and EV Applications

Power electronics plays an integral role in renewable energy generation and electric vehicle applications. Because of their intermittent nature, renewable energy resources cannot be directly integrated into the electric grid. The daily and seasonal fluctuation in wind and solar energy resources causes fluctuation in the harvested energy from these renewable energy resources. This

energy fluctuation would cause voltage and frequency oscillation to the grid if directly integrated [1.29].

To mitigate this problem, renewable energy resources are usually integrated to the grid through power electronic converters as shown in Figure 1-9 to smooth out the power fluctuation injected into the grid from these energy resources [1.30]. Solar farms are connected to the grid via a frontend dc/dc converter which performs a Maximum Power Point Tracking (MPPT) functionality and a back-end dc/ac inverter which regulates the active and reactive power injected into the grid. Wind farms on the other hand are integrated to the grid through a front-end ac/dc rectifier which controls the pitch angle of the turbine blades to regulate the energy extracted from the wind and a back-end dc/ac inverter that regulates the active and reactive power injected into the grid.

Figure 1-9 Integration of Wind and PV energy to the grid.

Power electronics is also an important component of an electric vehicle system. Figure 1-10 shows diagram of a passenger electric car system [1.31]. As can be seen from the diagram, an electric vehicle consists of several power electronic units such as the on-board charger, dc/dc converter and dc/ac inverter. The on-board charger regulates the charging profile of the battery

packs to ensure their safety and reliability. The dc/dc converter converts the dc voltage level of the battery packs into the different dc voltage levels required by the electric vehicle system. Three dc voltage levels may be present in a typical electric vehicle – a 12 V dc bus for the 12 V vehicle components, a 24 V dc bus for the 24 V vehicle components and an 800 V dc bus supplying the traction dc/ac inverter.

Figure 1-10 Diagram of typical electric vehicle system.

#### 1.3 The Future Power Electronics Demand

The rapid penetration of renewable energy generation and the increasing electrification of the transportation sector in the last couple of decades, however, has brought a challenge to the design of energy conversion systems. Promoted by market competition and other system operational needs, the future power electronic systems need to be designed to offer high efficiency, high power density, high reliability, and lower cost.

## 1.3.1 High Efficiency and High-Power Density

Not only the penetration of renewable energy resources has been increasing in the last couple of decades but also the size of the generation plants has been continuously increasing. However, when the size of the energy generation plants increases, the power processing capability of the front-end power electronic converter needs to be increased as well. This presents a significant challenge to the design of the front-end converter. It needs to have high conversion efficiency to reduce the power losses in the converter. Otherwise, an advanced thermal management system needs to be employed to extract the heat generated by the semiconductor devices and other components in the converter. This increases the cost of the converter and reduces its power density.

Power density is another design challenge for future power electronic conversion systems, especially for applications where space is a premium such as offshore wind energy generation and electric vehicles. In these applications, the converter weight and volume are very significant. Even though significant progress has already been made in converter power density improvement as shown in Figure 1-11 [1.32], there is still a demand for further improvement especially for EV applications where the converter size and weight are critical design parameters.

Figure 1-11 Converter power density improvement over time.

#### 1.3.2 Low Cost

Another design need for the future power electronic conversion is cost reduction. This is primarily driven by market competition. In the early years of the last decade, government incentives through investment tax credits and lower tax rates were one of the main drivers of the rapid growth of the renewable energy and electric transportation markets [1.14], [1.15]. These incentives were primarily given to increase the awareness of customers on these market sectors and to help with their huge investment cost. However, as customers became more friendly with these new market sectors, the government incentives started to reduce and will likely be stopped entirely in the coming years [1.33]. Therefore, these market sectors need to be economically competitive with the conventional fuel-based energy and transportation sectors to keep their current market momentum. This requires cost reduction in renewable energy generation and electric vehicle systems.

Figure 1-12 shows the cost decline for small passenger electric vehicles with 200 miles battery capacity from 2014 to 2022 [1.34]. When passenger electric vehicles were initially introduced to market, they were quite expensive more so than the conventional Internal Combustion Engine (ICE) passenger vehicles, but their price has been dropping exponentially since then with the advancement in power converter technologies and the technology maturity. Currently, the price of an electric passenger car is almost equivalent to the price of a similarly sized ICE passenger car. However, more cost reduction is still expected for electric vehicles in the future. Unlike the ICE vehicle technology, the electric vehicle technology is not yet fully matured especially in the battery technology. There are still several research and development activities to improve the performance and reduce cost of EVs.

Figure 1-12 Cost decline for EVs with 200 miles battery capacity.

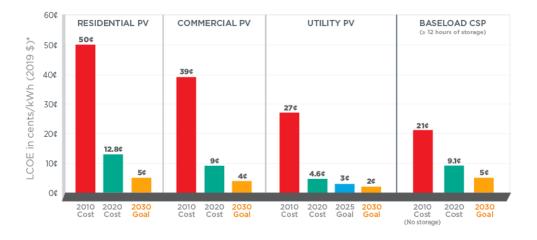

Figure 1-13 shows the cost decline in PV systems from 2010 to 2020 [1.22]. As can be seen from the figure, the Levelized Cost of Energy (LCOE) for PV systems has drastically reduced from 2010 to 2020. The introduction of new efficient solar panels and power converter topologies is the main drivers for this cost reduction. Despite the significant cost reduction that has already been recorded in PV systems, there is still a need for cost reduction to make this energy sector even more competitive. According to the US Solar Energy Technology Office (SETO) 2020 Q1 report [1.22], further cost decline of PV systems is still expected in 2030.

Figure 1-13 LCOE of PV systems: progress and goals.

#### 1.4 Solutions for the Future Power Electronics Needs

#### 1.4.1 Semiconductor Device Solutions

Silicon based semiconductor devices were the workhorse for power converters in many applications such as energy conversion, automotive, and industrial applications until the beginning of the 21<sup>st</sup> century. This semiconductor device technology is quite matured and converter design using these semiconductor devices is well established. Therefore, there is not much room for further performance improvement of power converters using silicon devices.

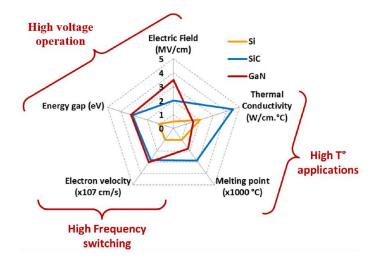

At the beginning of the 21<sup>st</sup> century, Wide Band Gap (WBG) semiconductor devices such as Silicon Carbide (SiC) MOSFETs and Gallium Nitride (GaN) devices have emerged as the next bricks for building power electronic converters. These semiconductor devices have superior performance indices compared to silicon devices as shown in Figure 1-14 [1.35]. They have a higher breakdown electric field offering lower on-state resistance, higher electron saturation velocity providing faster switching speed (higher switching frequency), higher bandgap energy allowing higher junction temperature operation capability, and higher thermal conductivity providing higher converter power density compared to silicon devices [1.36].

Figure 1-14 Physical properties of different semiconductor devices.

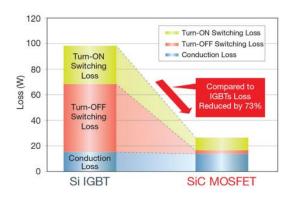

Because of their relative maturity compared to GaN devices, SiC devices are the primary pick for designing high efficiency and high power density power conversion systems. They provide significant switching loss reduction compared to silicon devices due to their higher switching speed and their very small reverse recovery loss (only due to the current needed to discharge their junction capacitor) [1.37]. Figure 1-15 for example shows the power loss comparison between Si IGBTs and SiC MOSFETs for a 2.5 kW dc/dc converter application [1.38]. For this application, SiC MOSFETs reduce the switching loss of the converter by about 73 percent. In addition, these devices can be operated at much higher switching frequency than silicon devices, hence the passive components can be designed much smaller than their silicon counterpart enabling compact and lower weight converter design for applications where space and weight is a premium such as aerospace applications. Moreover, combined with their excellent thermal conductivity, the reduced switching loss of SiC devices provides significant reduction in the thermal management of power converters employing SiC devices.

Figure 1-15 Power loss comparison between Si IGBT and SiC MOSFET.

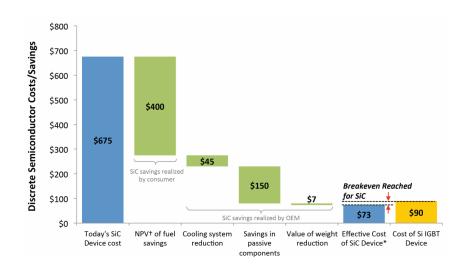

The major drawback of SiC devices currently is their high cost. As shown in Figure 1-16, the investment cost of SiC devices for a power converter is almost seven times the cost of Si devices [1.39]. However, this is expected to change in the future with the advancement in SiC device

manufacturing technology and market competition between SiC device manufacturers. In addition, despite their high initial investment cost, SiC devices provide cost savings in the overall converter system due to the reduction in the cooling system requirement, passive components, and converter enclosure. They also provide indirect cost savings for consumers during operation. For Hybrid Electric Vehicles (HEV) and Electric Vehicle (EV), consumers will have savings from the fuel cost cutting and for renewable energy applications, higher conversion efficiency means higher annual energy yield so utility companies will see increased revenue when using SiC based power converters for renewable energy generation.

Figure 1-16 Si IGBT and SiC MOSFET cost comparison for EV application.

However, there are still several research and development activities to further improve the performance of wide band gap devices through new packaging and gate driver technologies as well as improvements in the voltage and current handling capabilities of the devices themselves especially for GaN devices. In addition, the performance benefits of new device configurations such as hybrid Si/SiC switches [1.40] – [1.42] also need to be well investigated and converter design methods suitable for these device configurations need to be developed.

## 1.4.2 Power Converter Topology Solutions

Another room for finding answer for the high efficiency and high-power density energy conversion system need is converter topology. Converter efficiency and power density depend on the converter topology structure and operation. The converter conduction power loss depends on the number of devices per current conduction path while its switching power loss depends on the converter blocking voltage requirement both of which in turn depend on the converter topology structure and operation [1.43], [1.44]. The converter power density on the other hand is dependent on the number, size, and weight of the components that the converter is made from [1.45]. These factors are also dependent on the converter topology structure and operation. The converter topology determines the total number of semiconductor devices and the size of its passive components (the size of the passive components depends on the effective switching frequency of the converter topology). Therefore, converter topology is critical for achieving the desired efficiency and power density target for energy conversion systems.

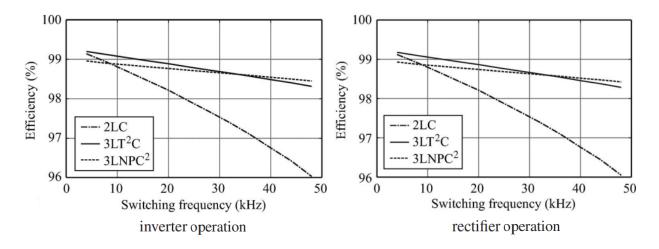

Figure 1-17 for example shows efficiency comparison of three converter topologies for a 10-kW motor derive application [1.46]. As can be seen from the figure, the Three-Level T-Type Converter (3LT<sup>2</sup>C) has higher efficiency compared to the Three-Level Neutral-Point Clamp Converter (3LNPC<sup>2</sup>) and the Two-Level Converter (2LC) for lower switching frequencies both for inverter and rectifier operation modes. For higher switching frequencies (> 35 kHz), the 3LNPC<sup>2</sup> has higher efficiency compared to the other two converter topologies in both operation modes. On the other hand, the two-level converter (2LC) has the lowest efficiency compared to the other three-level converter topologies for both operation modes and wide switching frequency range. This shows conversion efficiency is dependent on the converter topology and its operating conditions such as switching frequency.

Figure 1-17 Efficiency comparison between different converter topologies.

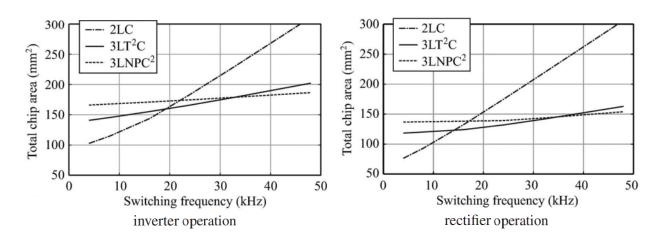

The power density of a converter also depends on its topology structure as shown in Figure 1-18 [1.46]. The two-level converter (2LC) topology has the lowest total semiconductor chip area (higher power density) compared to the other two three-level converter topologies for low switching frequencies (< 20 kHz). For medium switching frequency values (between 20 kHz and 35 kHz), the three-level T-type converter offers the highest power density compared to the other two converter topologies and, for high switching frequency (> 35 kHz), the three-level NPC converter offers the highest power density compared to the other two converter topologies.

Figure 1-18 Total semiconductor chip area comparison for different converter topologies.

## 1.4.3 Passive Component Solutions

#### 1.4.3.1 Dc-link Capacitor Choice

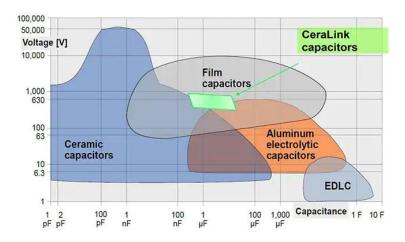

Different dc-link capacitor technologies have different physical and functional characteristics that play a great role in converter efficiency and power density. Figure 1-19 shows a comparison of three different dc-link capacitor technologies [1.47]. Ceramic capacitors are usually available in low capacitance and voltage rating, but they offer great energy density and very low Equivalent Series Resistance (ESR) compared to the other capacitor technologies [1.48]. Therefore, they are good choice to maximize converter efficiency and power density especially if they are used in conjunction with WBG devices.

Film capacitors on the other hand are available in relatively higher capacitance and voltage rating than ceramic capacitors. They also offer low ESR, and high energy density compared Aluminum Electrolytic capacitors [1.49]. Aluminum Electrolytic capacitors are probably the most matured capacitor technology. They are available in higher capacitance compared to the other two capacitor technologies. They also have good energy density. However, they have relatively higher ESR than Film and Ceramic capacitors especially at higher switching frequencies.

Figure 1-19 Dc-link capacitor technology comparison.

#### 1.4.3.2 Inductor Choice

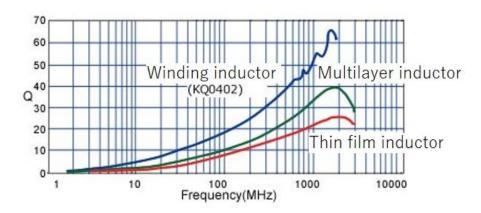

The choice of inductor also affects the efficiency and power density of a converter. Depending on the type of inductors used, different converter efficiency and power density can be achieved. The Quality factor (Q) of an inductor is a good indicator of the power loss of the inductor – a higher Q value indicates lower power loss and better high frequency stability [1.50], [1.51]. Figure 1-20 for example shows the Q-factor of three types of inductors [1.52]. As can be seen from the figure, winding inductors have higher Q-factor values especially at higher switching frequency hence they have lower power loss while thin film inductors have lower Q-factor or higher power loss compared to winding inductor and multilayer inductor technologies. The inductor core size is also important design parameter since it affects the power density of the converter.

However, inductors are primarily selected based on their functionality such as ripple current filtering or EMI suppression. The power loss and power density of the inductor comes next to these parameters and hence it very difficult to get a good tradeoff between their primary functionality, and converter efficiency and power density.

Figure 1-20 Comparison of different inductor technologies.

#### 1.4.4 New Design Approaches

Another way forward for the future power electronics high efficiency and high-power density needs is a paradigm shift in converter design approach. Traditionally, the different converter design aspects such as the electrical design parameters, mechanical design parameters, and thermal design parameters are dealt separately and sequentially despite that these parameters are interrelated. This approach results in unoptimized converter performance in terms of the electrical, mechanical, and thermal aspects.

Recently, a new converter design approach has been introduced where the converter design space is expanded to include all the electrical, mechanical, and thermal aspects of the converter. Such design approach is called co-design or co-engineering [1.53], [1.54]. A co-design approach moves away from the conventional sequential design approach where the electrical design parameters, thermal design parameters, and mechanical design parameters are considered separately and replaces it with an approach where these design parameters are all simultaneously considered during the initial design. This design approach offers an optimized design in terms of the electrical, mechanical, and thermal performance of the converter.

However, the accuracy of this design approach depends on the design rules which defines the relationship between the electrical, thermal, and mechanical parameters of the converter [1.55]. Developing such design rule is not straightforward and it is a subject of the current research. But, with the ongoing research effort, simplified converter electrical, thermal, and mechanical models will surely be developed, and this design approach will soon be helpful.

### 1.5 Dissertation Objectives and Organization

Despite several converter topologies that have already been proposed to improve efficiency and power density of power converters, there is still much room for further improvement in terms of the tradeoff between efficiency, power density, and cost. Much effort is still expected to find a new converter topology with lower device count, lower power loss, and higher effective switching frequency to facilitate the tradeoff between efficiency, power density, and cost. This dissertation presents two novel high efficiency and high-power density converter topologies for renewable energy generation and EV applications. The first converter topology is a three-level ANPC inverter employing hybrid Si/SiC switches [1.56] and the second converter topology is a modified alternate arm converter topology termed as the Asymmetric Alternate Arm Converter (AAAC) topology [1.57]. The operation principle, control strategy and novel features of these converter topologies are discussed in detail and validated by both simulation and experimental results.

This dissertation is organized as follows. Chapter 2 presents the three-level ANPC inverter employing hybrid Si/SiC switches. The novel features of this topology, its operation and control strategy, and the converter design optimization in terms of the Si/SiC gate control and current rating ratio optimization are discussed in detail. Simulation and experimental results validating the operation and control strategies of the converter are also presented.

Chapter 3 introduces an improved converter Figure of Merit for hybrid Si/SiC switches combining the high-level semiconductor device properties such as on-state resistance and input/output capacitances and converter topology properties such blocking voltage and switching frequency. The detailed derivation of the proposed converter figure of merit is shown, and its accuracy is validated by experimental power loss and efficiency data using the hybrid Si/SiC switch ANPC inverter presented in Chapter 2.

Chapter 4 introduces a new hybrid voltage source converter topology termed as the Asymmetric Alternate Arm Converter (AAAC) that resembles the modular multilevel converter and the alternate arm converter topologies both in structure and operation. The structure, operation principle, control strategy, novel features, and design optimizations of this new converter topology are discussed in detail. Simulation and experimental results verifying the operation and control strategy of the proposed converter topology are also presented.

Chapter 5 presents the investigation of the converter arm energy for the topology presented in chapter 4 with aim of driving an expression of the maximum arm energy deviation of this converter topology that is needed to determine the minimum submodule capacitance of this converter topology. Validation of the derived maximum arm energy deviation equation with simulation and experimental results is also shown. In addition, arm energy deviation and the submodule capacitance requirement comparison between the proposed converter topology in Chapter 4 and other similar converter topologies is also given.

Chapter 6 presents conclusion to the work described in this dissertation and highlights the main future works for the topics discussed in the dissertation.

#### 1.6 Reference

- [1.1] IEA (2021), World Energy Outlook 2021, IEA, Paris <a href="https://www.iea.org/reports/world-energy-outlook-2021">https://www.iea.org/reports/world-energy-outlook-2021</a>.

- [1.2] T. Hong, P. Pinson, Y. Wang, R. Weron, D. Yang and H. Zareipour, "Energy Forecasting: A Review and Outlook," in *IEEE Open Access Journal of Power and Energy*, vol. 7, pp. 376-388, 2020.

- [1.3] United Nations Industrial Development Organization, 2021. *Industrial Development Report 2022. The Future of Industrialization in a Post-Pandemic World. Overview.* Vienna.

- [1.4] World Bank. 2022. *Global Economic Prospects, January 2022*. Washington, DC: World Bank.

- [1.5] IEA (2020), Electricity Market Report December 2020, IEA, Paris <a href="https://www.iea.org/reports/electricity-market-report-december-2020">https://www.iea.org/reports/electricity-market-report-december-2020</a>.

- [1.6] G. T. Ayele, P. Haurant, B. Laumert, B. Lacarrière, "An extended energy hub approach for load flow analysis of highly coupled district energy networks: Illustration with electricity and heating," *Applied Energy*, vol. 212, pp 850-867, 2018.

- [1.7] IEA, Global energy-related CO2 emissions, 1900-2020, IEA, Paris <a href="https://www.iea.org/data-and-statistics/charts/global-energy-related-co2-emissions-1900-2020">https://www.iea.org/data-and-statistics/charts/global-energy-related-co2-emissions-1900-2020</a>.

- [1.8] B. K. Bose, "Global Warming: Energy, Environmental Pollution, and the Impact of Power Electronics," in *IEEE Industrial Electronics Magazine*, vol. 4, no. 1, pp. 6-17, March 2010.

- [1.9] A. Bindra, "Global Climate Change: A Norwegian Perspective," in *IEEE Power Electronics Magazine*, vol. 6, no. 4, pp. 34-35, Dec. 2019.

- [1.10] GWEC (2019), GWEC | Global Wind Report 2019, <a href="https://gwec.net/global-wind-report-2019">https://gwec.net/global-wind-report-2019</a>.

- [1.11] L. Gertmar, L. Liljestrand and H. Lendenmann, "Wind Energy Powers-That-Be Successor Generation in Globalization," in *IEEE Transactions on Energy Conversion*, vol. 22, no. 1, pp. 13-28, March 2007.

- [1.12] A. Qazi et al., "Towards Sustainable Energy: A Systematic Review of Renewable Energy Sources, Technologies, and Public Opinions," in *IEEE Access*, vol. 7, pp. 63837-63851, 2019.

- [1.13] P. Roy, J. He, T. Zhao and Y. Singh, "Recent Advances of Wind-Solar Hybrid Renewable Energy Systems for Power Generation: A Review," in *IEEE Open Journal of the Industrial Electronics Society*, early access.

- [1.14] M. Esmaeili and A. Anvari-Moghaddam, "The Effect of Ratio-Based Incentive on Wind Capacity Development and Investment Risk of Wind Units: A System Dynamics Approach," in *IEEE Access*, vol. 9, pp. 110772-110786, 2021.

- [1.15] I. Das, K. Bhattacharya and C. Cañizares, "Optimal Incentive Design for Targeted Penetration of Renewable Energy Sources," in *IEEE Transactions on Sustainable Energy*, vol. 5, no. 4, pp. 1213-1225, Oct. 2014.

- [1.16] V. Yaramasu, B. Wu, P. C. Sen, S. Kouro and M. Narimani, "High-power wind energy conversion systems: State-of-the-art and emerging technologies," in *Proceedings of the IEEE*, vol. 103, no. 5, pp. 740-788, May 2015.

- [1.17] P. S. Barendse and P. Pillay, "A doubly-fed induction generator drive for a wind energy conversion system," in *SAIEE Africa Research Journal*, vol. 97, no. 4, pp. 274-280, Dec. 2006.

- [1.18] J. D. Taft, "Grid Architecture: A Core Discipline for Grid Modernization," in *IEEE Power and Energy Magazine*, vol. 17, no. 5, pp. 18-28, Sept.-Oct. 2019.

- [1.19] J. Romero Aguero and A. Khodaei, "Grid Modernization, DER Integration & Utility Business Models Trends & Challenges," in *IEEE Power and Energy Magazine*, vol. 16, no. 2, pp. 112-121, March 2018.

- [1.20] BP (2021), Statistical Review of World Energy 2021 | 70th edition <a href="https://www.bp.com/en/global/corporate/energy-economics/statistical-review-of-world-energy.html">https://www.bp.com/en/global/corporate/energy-economics/statistical-review-of-world-energy.html</a>.

- [1.21] K. Sugibuchi, I. Kaizuka, H. Yamaya, T. Ohigashi and O. Ikki, "150GW by 2030: PV Market Outlook for Japan," 2018 IEEE 7th World Conference on Photovoltaic Energy Conversion (WCPEC), 2018, pp. 3841-3844.

- [1.22] Feldman, David, Vignesh Ramasamy, Ran Fu, Ashwin Ramdas, Jal Desai, and Robert Margolis. 2021. U.S. Solar Photovoltaic System Cost Benchmark: Q1 2020. Golden, CO: National Renewable Energy Laboratory. NREL/TP-6A20-77324. <a href="https://www.nrel.gov/docs/fy21osti/77324.pdf">https://www.nrel.gov/docs/fy21osti/77324.pdf</a>.

- [1.23] S. Jiang, C. Wan, C. Chen, E. Cao and Y. Song, "Distributed photovoltaic generation in the electricity market: status, mode and strategy," in *CSEE Journal of Power and Energy Systems*, vol. 4, no. 3, pp. 263-272, September 2018.

- [1.24] S. Wang, "Current status of PV in China and its future forecast," in *CSEE Journal of Power and Energy Systems*, vol. 6, no. 1, pp. 72-82, March 2020.

- [1.25] Oberbeck, L, Alvino, K, Goraya, B, Jubault, M. IPVF's PV technology vision for 2030. *Prog Photovolt Res Appl.* 2020; 28: 1207–1214.

- [1.26] E. W. Martin and S. A. Shaheen, "Greenhouse Gas Emission Impacts of Carsharing in North America," in *IEEE Transactions on Intelligent Transportation Systems*, vol. 12, no. 4, pp. 1074-1086, Dec. 2011.

- [1.27] Deloitte Insights, Electric Vehicles setting a course for 2030 <a href="https://www2.deloitte.com/us/en/insights/focus/future-of-mobility/electric-vehicle-trends-2030.html">https://www2.deloitte.com/us/en/insights/focus/future-of-mobility/electric-vehicle-trends-2030.html</a>.

- [1.28] Evadoption, EV sales forecasts <a href="https://evadoption.com/ev-sales/ev-sales-forecasts">https://evadoption.com/ev-sales/ev-sales-forecasts</a>.

- [1.29] I. Akhtar, S. Kirmani and M. Jameel, "Reliability Assessment of Power System Considering the Impact of Renewable Energy Sources Integration into Grid with Advanced Intelligent Strategies," in *IEEE Access*, vol. 9, pp. 32485-32497, 2021.

- [1.30] R. G. Wandhare and V. Agarwal, "Novel Integration of a PV-Wind Energy System with Enhanced Efficiency," in *IEEE Transactions on Power Electronics*, vol. 30, no. 7, pp. 3638-3649, July 2015.

- [1.31] A. Emadi, Y. J. Lee and K. Rajashekara, "Power Electronics and Motor Drives in Electric, Hybrid Electric, and Plug-In Hybrid Electric Vehicles," in *IEEE Transactions on Industrial Electronics*, vol. 55, no. 6, pp. 2237-2245, June 2008.

- [1.32] R. Bosshard and J. W. Kolar, "All-SiC 9.5 kW/dm3 On-Board Power Electronics for 50 kW/85 kHz Automotive IPT System," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 1, pp. 419-431, March 2017.

- [1.33] A. Izadian, N. Girrens and P. Khayyer, "Renewable Energy Policies: A Brief Review of the Latest U.S. and E.U. Policies," in *IEEE Industrial Electronics Magazine*, vol. 7, no. 3, pp. 21-34, Sept. 2013.

- [1.34] I. Husain et al., "Electric Drive Technology Trends, Challenges, and Opportunities for Future Electric Vehicles," in *Proceedings of the IEEE*, vol. 109, no. 6, pp. 1039-1059, June 2021.

- [1.35] Z, Zhang, "Characterization and realization of high switching-speed capability of SiC power devices in voltage source converter," Ph.D. dissertation, Univ. TN, Knoxville, TN, 2015.

- [1.36] L. Zhang, X. Yuan, X. Wu, C. Shi, J. Zhang and Y. Zhang, "Performance Evaluation of High-Power SiC MOSFET Modules in Comparison to Si IGBT Modules," in *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1181-1196, Feb. 2019.

- [1.37] S. Yu, J. Wang, X. Zhang, Y. Liu, N. Jiang and W. Wang, "The Potential Impact of Using Traction Inverters with SiC MOSFETs for Electric Buses," in *IEEE Access*, vol. 9, pp. 51561-51572, 2021.

- [1.38] M. J. Rogers, E. R. Motto and M. Steiner, "Performance Comparison of State-of-the-Art 300A/1700V Si IGBT and SiC MOSFET Power Modules," in *IEEE Power Electronics Magazine*, vol. 7, no. 3, pp. 44-51, Sept. 2020.

- [1.39] H. Zhang, L. M. Tolbert and B. Ozpineci, "Impact of SiC Devices on Hybrid Electric and Plug-In Hybrid Electric Vehicles," in *IEEE Transactions on Industry Applications*, vol. 47, no. 2, pp. 912-921, March-April 2011.

- [1.40] M. Rahimo et al., "Characterization of a Silicon IGBT and Silicon Carbide MOSFET Cross-Switch Hybrid," in *IEEE Transactions on Power Electronics*, vol. 30, no. 9, pp. 4638-4642, Sept. 2015.

- [1.41] L. Li, P. Ning, X. Wen and D. Zhang, "A 1200 V/200 a half-bridge power module based on Si IGBT/SiC MOSFET hybrid switch," in *CPSS Transactions on Power Electronics and Applications*, vol. 3, no. 4, pp. 292-300, Dec. 2018.

- [1.42] P. Ning, L. Li, X. Wen and H. Cao, "A hybrid Si IGBT and SiC MOSFET module development," in *CES Transactions on Electrical Machines and Systems*, vol. 1, no. 4, pp. 360-366, December 2017.

- [1.43] A. K. Sadigh, V. Dargahi and K. A. Corzine, "Investigation of Conduction and Switching Power Losses in Modified Stacked Multicell Converters," in *IEEE Transactions on Industrial Electronics*, vol. 63, no. 12, pp. 7780-7791, Dec. 2016.

- [1.44] M. M. Islam, M. A. Rahman and M. R. Islam, "Power Loss and Thermal Impedance Modeling of Multilevel Power Converter with Discontinuous Modulation," in *IEEE Transactions on Energy Conversion*, vol. 36, no. 1, pp. 36-47, March 2021.

- [1.45] J. Liu, D. Dong and D. Zhang, "A Hybrid Modular Multilevel Converter Family with Higher Power Density and Efficiency," in *IEEE Transactions on Power Electronics*, vol. 36, no. 8, pp. 9001-9014, Aug. 2021.

- [1.46] M. Schweizer, T. Friedli and J. W. Kolar, "Comparative Evaluation of Advanced Three-Phase Three-Level Inverter/Converter Topologies Against Two-Level Systems," in *IEEE Transactions on Industrial Electronics*, vol. 60, no. 12, pp. 5515-5527, Dec. 2013.

- [1.47] K. S. Rajashekara, V. Rajagopalan, A. Sevigny and J. Vithayathil, "DC Link Filter Design Considerations in Three-Phase Voltage Source Inverter-Fed Induction Motor Drive System," in *IEEE Transactions on Industry Applications*, vol. IA-23, no. 4, pp. 673-680, July 1987.

- [1.48] H. Wang and F. Blaabjerg, "Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview," in *IEEE Transactions on Industry Applications*, vol. 50, no. 5, pp. 3569-3578, Sept.-Oct. 2014.

- [1.49] E. Rachev and V. Petrov, "DC link capacitor selection for DC-DC converters," 2020 12th Electrical Engineering Faculty Conference (BulEF), 2020, pp. 1-5

- [1.50] S. Christian, R. A. Fantino, R. Amir Gomez, J. C. Balda, Y. Zhao and G. Zhu, "150-kW Three-Port Custom-Core Transformer Design Methodology," *2020 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2020, pp. 1020-1024, doi: 10.1109/APEC39645.2020.9124265.

- [1.51] M. Leibl, G. Ortiz, and J. W. Kolar, "Design and Experimental Analysis of a Medium-Frequency Transformer for Solid-State Transformer Applications," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 5, no. 1, pp. 110–123, Mar. 2017.

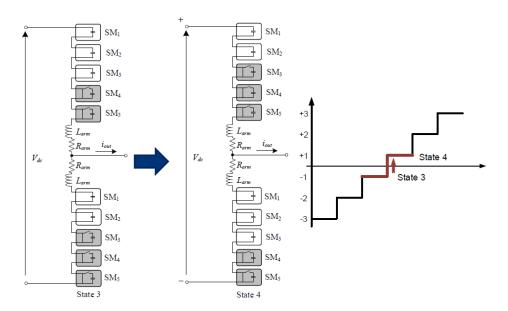

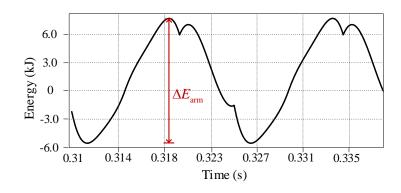

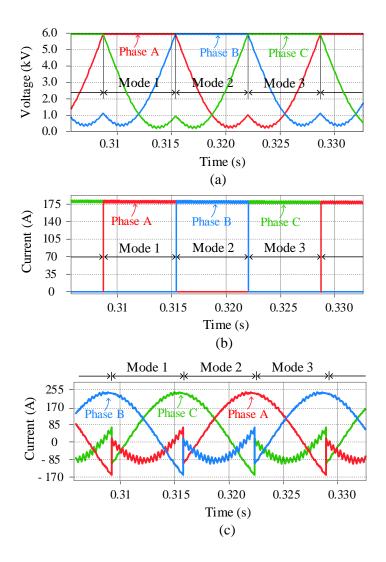

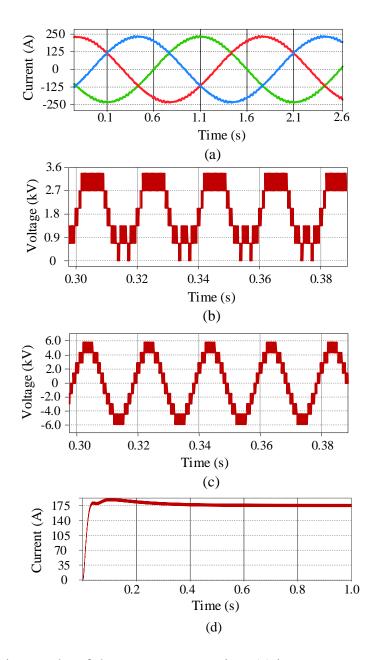

- [1.52] C. William and T. McLyman, Transformer and Inductor Design Handbook. Taylor & Francis Group, 2011.