# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: **Moule, Taylor G**  *Title:* **Electrical and thermal characterisation of -Ga2O3 devices**

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

#### Take down policy

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

· Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Electrical and Thermal Characterisation of $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Devices

Breakdown, Self-Heating, Electrical Performance and Electron Trapping

By

TAYLOR MOULE

Department of Physics UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Physics.

School of Physics May 2022

Word count: 47400

ABSTRACT

Begin that can routinely handle high electric fields. The operating temperatures of such devices have to be minimised in order to maximise their lifetimes. Despite reaching a number of key research milestones, several unresolved problems continue to hinder the commercialisation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices, while deep-level states have been observed to increase device on-resistance and induce threshold voltage instabilities. The investigation of these effects is the focus of this thesis.

High-bias stressing of trench-MOS Schottky-barrier diodes was used to investigate device breakdown. Analysis of the reverse bias leakage current of these diodes revealed two distinct leakage regimes, a low bias leakage current dominated by leakage over the Schottky-barrier, and a high bias leakage dominated by leakage paths through the  $Al_2O_3$  dielectric. Breakdown of the diodes was attributed to the high-bias degradation of the dielectric.

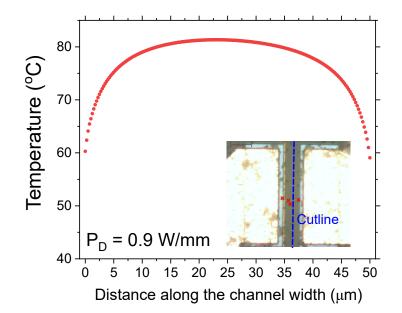

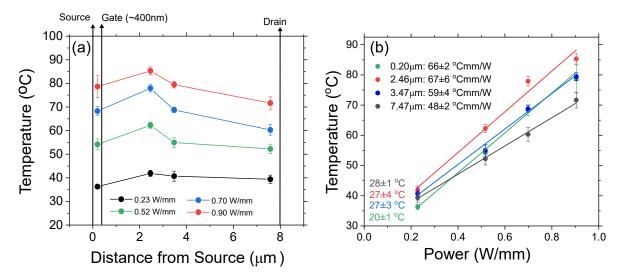

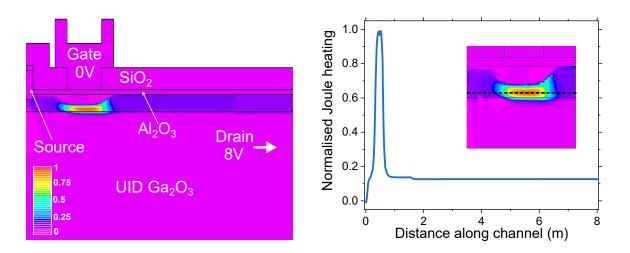

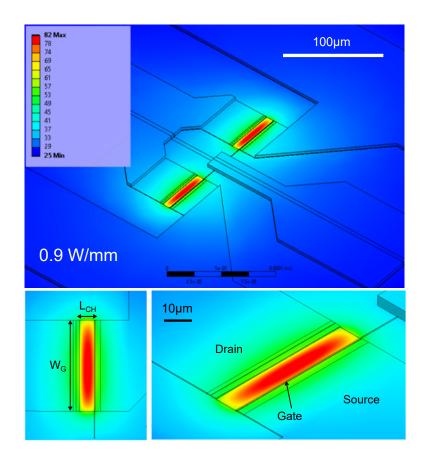

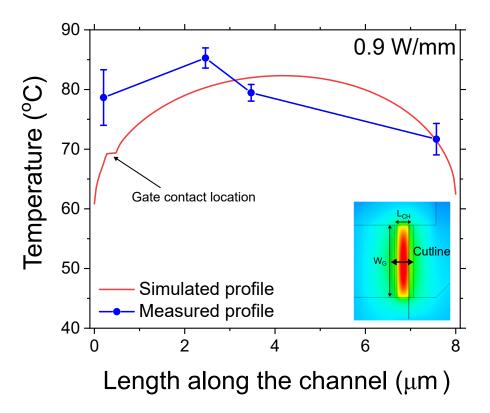

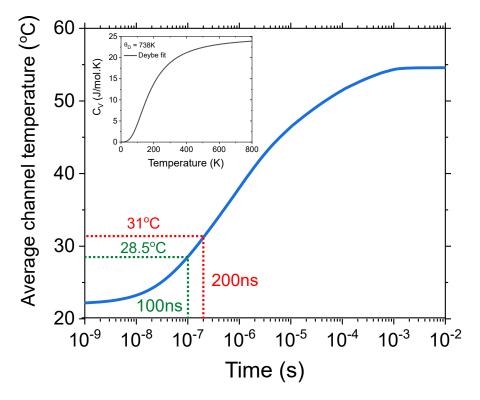

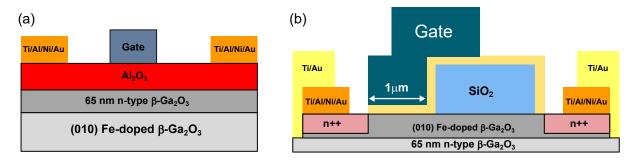

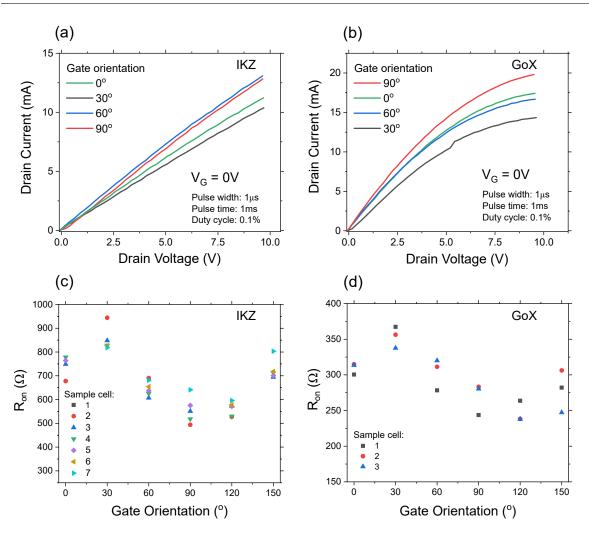

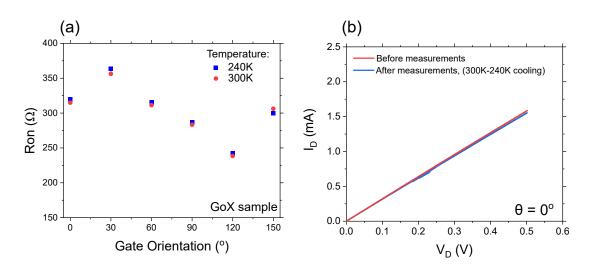

Self-heating in thin-channel  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs was then investigated using Raman nanothermography. These measurements revealed an absence of hot-spots for operating powers up to 0.9 W/mm. This was attributed to distributed heating effects in the MOSFET, with the resistive heating in the channel being comparable to that of heating in the high-field region at the drainside of gate. A comparison of these measurements to a pulsed IV method for extracting averaged channel temperatures, previously reported in the literature, demonstrated a high degree of agreement between the two methods. 3D simulations of the channel temperature profile support this conclusion. Potential anisotropy in the electrical performance of  $\beta$ - Ga<sub>2</sub>O<sub>3</sub> MOSFETs was then investigated using pulsed IV characterisation. A large anisotropy in device on-resistance was observed as a function of device orientation relative to the substrate. Raman measurements of the substrate orientation demonstrated that this anisotropy did not correlate with the underlying substrate orientation across two sample sets. The variation in on-resistance was attributed to artifacts in the fabrication of the device.

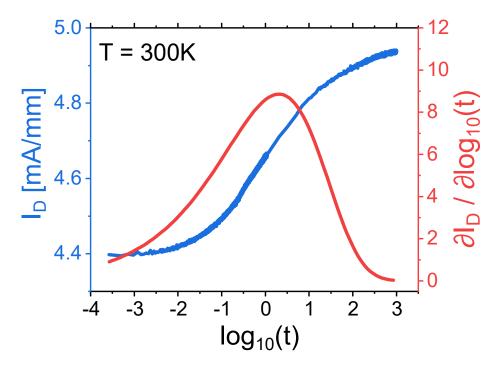

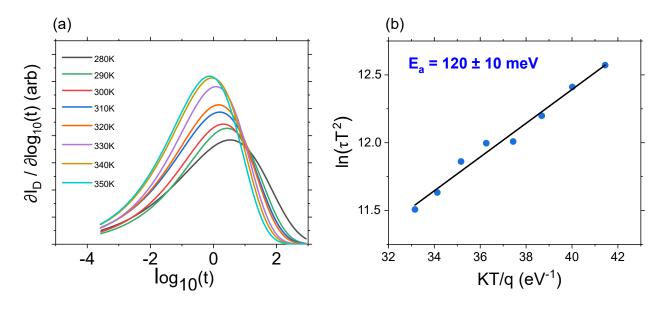

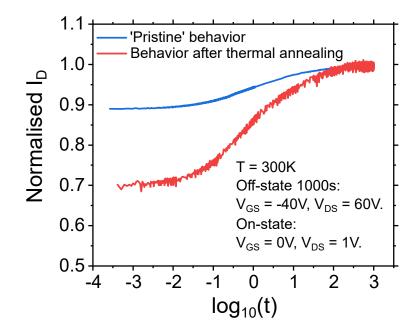

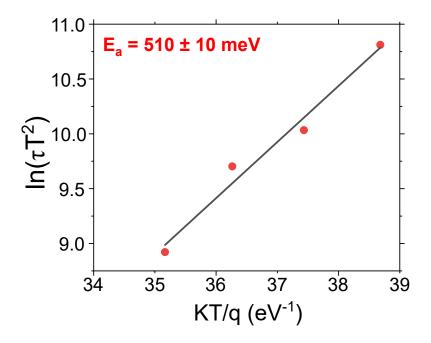

Electron trapping at a Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> interface was investigated using capacitance-voltage characterisation of a MOS-CAP structure. The presence of a distinct ledge in the up-sweep of the capacitance-voltage characteristic, after high bias stressing of the device, was attributed to the presence of an interface trapping state. TCAD simulations demonstrated that the presence of such a state is sufficient to explain the ledge and an observed hysteresis in the capacitance-voltage characteristic. An upper bound of 2.3 eV for the trap state conduction band offset was determined. Finally, bulk trapping in  $\beta$ - Ga<sub>2</sub>O<sub>3</sub> MOSFETs was investigated using deep-level transient current spectroscopy. The presence of a trapping state with an activation energy of 120 meV was consistent with a previously reported trapping state in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Thermal stressing of the device lead to the emergence of a new device behaviour, with activation energy of 510 meV. This new behaviour was suppressed after a 350K anneal of the substrate, with a semi-permanent reduction in the drain-current observed. This behaviour was attributed to the charging of electrically isolated regions in the device. The deep-level transient current spectroscopy method is not well suited to the investigation of such charging effects, with a conductive substrate required to separate the impact of buffer trapping from surface trapping. The fabrication of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices on a conductive substrate is necessary to model this behaviour.

#### **DEDICATION AND ACKNOWLEDGEMENTS**

**F** irst I would like to thank Martin Kuball and Michael Uren for their supervision, patience and support throughout the PhD. Their experience and interest in my work has made it a thoroughly rewarding experience. I would also like to thank my collaborators, without whom this thesis would not have been possible. In particular, I would like to express my gratitude to Huili Grace Xing from Cornell University, Andrew Green from the Air Force research Laboratory, and Masataka Higashiwaki from NICT Japan for the samples they have provided and for their feedback on my work. I would also like to give special thanks to Manikant Singh, Stefano Dalcanale, James Pomeroy and Abhishek Mishra for their guidance and training over the past four years, and for the many fruitful discussions we have had.

My time in Bristol would not have been half as an enjoyable without everyone in the PhD office and without my colleagues in the CDTR. All the people to have passed through the group in the last four years have made working on my PhD better than I could have hoped for. To everyone in cohort 4 of the CDT, I would like to say thank you for keeping from me from working too hard, and for all of the memories across Bath, Bristol and Scotland. I must also thank my family for the all the support and encouragement they have given me, not just over the PhD, but over the past eight years of study. Their belief in me has been invaluable. Finally, I would like express my gratitude for the financial support I have received from the EPSRC centre for doctoral training in condensed matter physics.

## **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

SIGNED: ...... DATE: .....

# TABLE OF CONTENTS

|    |                   |        | F                                                                                                                         | Page |

|----|-------------------|--------|---------------------------------------------------------------------------------------------------------------------------|------|

| Li | List of Tables xi |        |                                                                                                                           |      |

| Li | st of             | Figure | es                                                                                                                        | xiii |

| 1  | Intr              | oducti | ion                                                                                                                       | 1    |

|    | 1.1               | Thesis | s Outline                                                                                                                 | 4    |

| 2  | Bac               | kgroui | nd                                                                                                                        | 7    |

|    | 2.1               | Galliu | um Oxide                                                                                                                  | 7    |

|    |                   | 2.1.1  | Raman Scattering and Phonon Dispersion in the Monoclinic Structure                                                        | 10   |

|    |                   | 2.1.2  | Electron Transport in $\beta$ -Ga <sub>2</sub> O <sub>3</sub>                                                             | 14   |

|    |                   | 2.1.3  | Thermal Conductivity of $\beta$ -Ga $_2O_3$                                                                               | 16   |

|    |                   | 2.1.4  | Applications of $\beta$ -Ga <sub>2</sub> O <sub>3</sub>                                                                   | 18   |

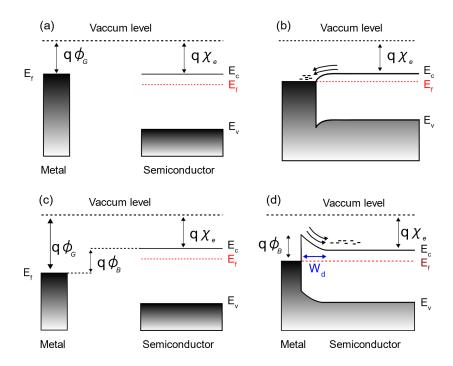

|    | 2.2               | Device | e Physics                                                                                                                 | 20   |

|    |                   | 2.2.1  | Metal-semiconductor Contacts                                                                                              | 21   |

|    |                   | 2.2.2  | The MOS-capacitor                                                                                                         | 21   |

|    |                   | 2.2.3  | MOSFETs                                                                                                                   | 24   |

|    |                   | 2.2.4  | Schottky-barrier Diode Devices                                                                                            | 28   |

|    | 2.3               | Growt  | th and Fabrication of $\beta$ -Ga $_2O_3$ Devices $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 32   |

|    | 2.4               | Device | e Reliability                                                                                                             | 40   |

|    |                   | 2.4.1  | Leakage Currents and Device Breakdown                                                                                     | 40   |

|    |                   | 2.4.2  | Electron Trapping                                                                                                         | 43   |

|    |                   | 2.4.3  | Device Self-heating                                                                                                       | 49   |

| 3  | Cha               | racter | risation Techniques                                                                                                       | 53   |

|    | 3.1               | Measu  | urement Environment                                                                                                       | 53   |

|    | 3.2               | Electr | rical Characterisation Techniques                                                                                         | 56   |

|    |                   | 3.2.1  | Transmission Line Measurements                                                                                            | 56   |

|    |                   | 3.2.2  | Current-voltage Characterisation                                                                                          | 57   |

|    |                   | 3.2.3  | Pulsed Current-voltage Characterisation                                                                                   | 57   |

|   |      | 3.2.4    | Capacitance-voltage Characterisation                                                                        | 61  |

|---|------|----------|-------------------------------------------------------------------------------------------------------------|-----|

|   |      | 3.2.5    | Cryogenic Measurements                                                                                      | 62  |

|   | 3.3  | Rama     | n Spectroscopy                                                                                              | 63  |

|   | 3.4  | Simul    | ations                                                                                                      | 65  |

|   |      | 3.4.1    | Silvaco ATLAS                                                                                               | 65  |

|   |      | 3.4.2    | ANSYS                                                                                                       | 68  |

| 4 | Bre  | akdow    | n Mechanisms in $eta$ -Ga $_2$ O $_3$ Trench-MOS Schottky-barrier Diodes                                    | 71  |

|   | 4.1  | Introd   | luction                                                                                                     | 71  |

|   | 4.2  | Exper    | imental Details                                                                                             | 73  |

|   |      | 4.2.1    | Devices                                                                                                     | 73  |

|   |      | 4.2.2    | Measurement Configuration                                                                                   | 74  |

|   |      | 4.2.3    | Analysis of Leakage Current Noise                                                                           | 76  |

|   | 4.3  | Result   | ts                                                                                                          | 79  |

|   |      | 4.3.1    | Simulations                                                                                                 | 79  |

|   |      | 4.3.2    | Impact of Fin Geometry on the Breakdown of Trench-MOS SBDs                                                  | 83  |

|   |      | 4.3.3    | Leakage Currents and Breakdown Mechanisms in Trench-MOS SBDs                                                | 84  |

|   |      | 4.3.4    | Leakage Currents in MOS-CAPs and Planar SBDs                                                                | 86  |

|   | 4.4  | Discus   | ssion                                                                                                       | 88  |

|   | 4.5  | Conclu   | usions                                                                                                      | 93  |

| 5 | Self | f-heatiı | ng Effects and Orientation Dependence of Electrical and Thermal                                             |     |

| - |      |          | s in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> MOSFETs                                                        | 95  |

|   | 5.1  | -        | luction                                                                                                     | 95  |

|   | 5.2  |          | eating Effects in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> MOSFETs                                           |     |

|   |      | 5.2.1    | Devices and Experimental Details                                                                            |     |

|   |      | 5.2.2    | Raman Nanothermography Results                                                                              |     |

|   |      | 5.2.3    | Simulation Results                                                                                          |     |

|   |      | 5.2.4    | Effect of Device Orientation on Self-heating                                                                |     |

|   |      | 5.2.5    | Pulsed IV Method for Measuring Channel Temperature                                                          |     |

|   |      | 5.2.6    | Discussion                                                                                                  |     |

|   | 5.3  | Invest   | Signation of Anisotropic Electrical Performance in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> MOSFETs $\ldots$ | 113 |

|   |      | 5.3.1    | Devices and Experimental Details                                                                            |     |

|   |      | 5.3.2    | Measurements                                                                                                |     |

|   |      | 5.3.3    | Results of Electrical Charaterisation                                                                       |     |

|   |      | 5.3.4    | Measurement of Substrate Orientation                                                                        |     |

|   |      | 5.3.5    | Discussion                                                                                                  | 120 |

|   |      |          | usions                                                                                                      |     |

| 6  | The         | Locat   | ion and Impact of Trapping States on $eta	ext{-}	ext{Ga}_2	extbf{O}_3$ Devices                                                             | 125   |

|----|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | 6.1         | Introd  | uction                                                                                                                                     | . 125 |

|    | 6.2         | Trapp   | ing at $Al_2O_3/\beta$ -Ga $_2O_3$ Interfaces $\ldots \ldots \ldots$ | . 126 |

|    |             | 6.2.1   | High-voltage CV Characterisation                                                                                                           | . 127 |

|    |             | 6.2.2   | Modelling and Simulations                                                                                                                  | . 129 |

|    |             | 6.2.3   | Discussion                                                                                                                                 | . 136 |

|    | 6.3         | Long-   | lifetime Trapping and Memory Effects in $eta	ext{-}	ext{Ga}_2	ext{O}_3	ext{ MOSFETs}$                                                      | . 138 |

|    |             | 6.3.1   | Devices                                                                                                                                    | . 138 |

|    |             | 6.3.2   | The Impact of Bias Stress on the Device Output Characteristics                                                                             | . 138 |

|    |             | 6.3.3   | Deep-level Current Transient Spectroscopy                                                                                                  | . 142 |

|    |             | 6.3.4   | Discussion                                                                                                                                 | . 148 |

|    | 6.4         | Conclu  | asions                                                                                                                                     | . 150 |

| 7  | Conclusions |         |                                                                                                                                            |       |

|    | 7.1         | Futur   | e Work                                                                                                                                     | . 156 |

| A  | Арр         | endix   | Α                                                                                                                                          | 159   |

|    | A.1         | List of | Publications                                                                                                                               | . 159 |

|    | A.2         | List of | Presentations                                                                                                                              | . 160 |

| Bi | bliog       | raphy   |                                                                                                                                            | 161   |

LIST OF TABLES

| TABLE |                                                                                     | Page |

|-------|-------------------------------------------------------------------------------------|------|

| 2.1   | A comparison of the material properties and figures of merit of some commonly cited | ł    |

|       | semiconductors                                                                      | . 20 |

# **LIST OF FIGURES**

Page

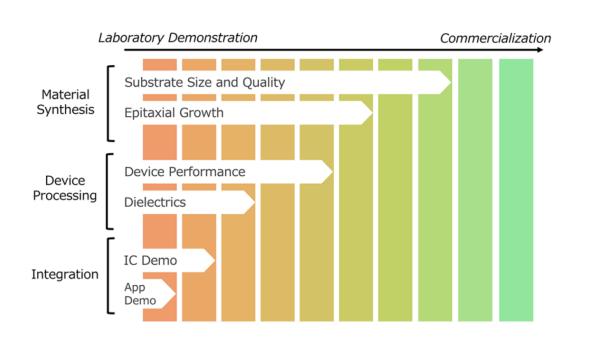

| 1.1  | The current status of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> research and progress towards device commercialisation. | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | The unit cell of $\beta$ -Ga $_2O_3$                                                                                  | 8  |

| 2.2  | The Brillouin zone and band diagram of $\beta$ -Ga $_2O_3$                                                            | 9  |

| 2.3  | The phonon dispersion and phonon density of states of $eta	ext{-}	ext{Ga}_2	ext{O}_3$ $\dots \dots \dots \dots$       | 10 |

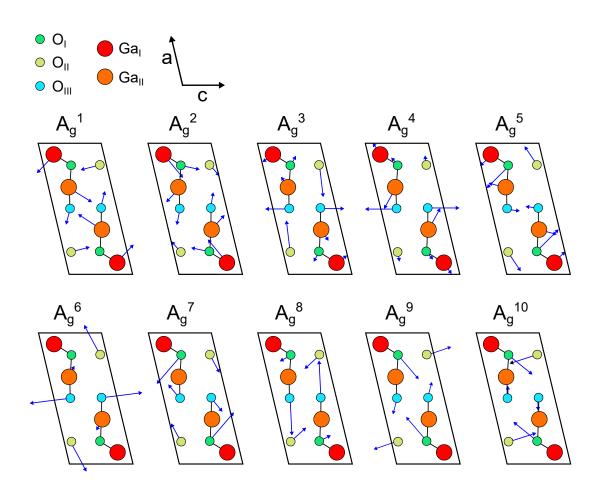

| 2.4  | The displacement of atoms for the $A_g$ Raman modes                                                                   | 11 |

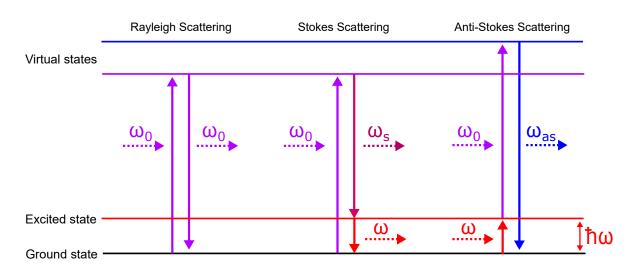

| 2.5  | Principle of Raman scattering in a lattice.                                                                           | 12 |

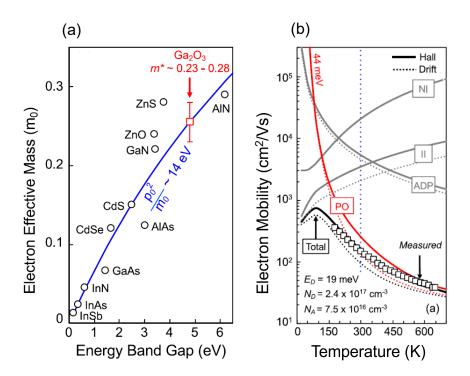

| 2.6  | The effective electron mass and temperature dependence of electron mobility in $\beta$ -Ga $_2O_3$                    | 15 |

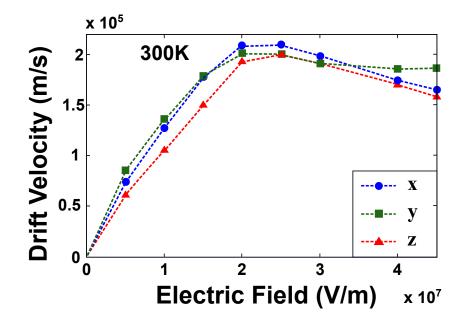

| 2.7  | Velocity-field relationship for electrons in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> calculated using full band Monte |    |

|      | Carlo simulations                                                                                                     | 16 |

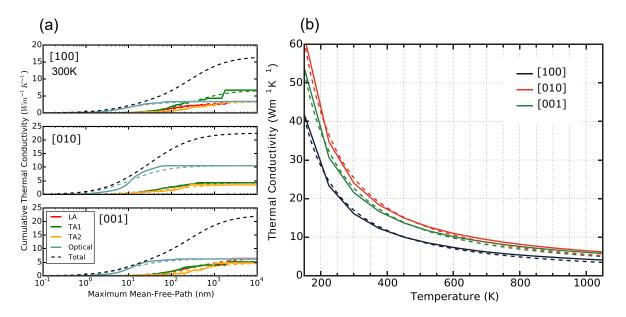

| 2.8  | The contribution of acoustic and optical phonon modes to the thermal conductivity of                                  |    |

|      | $\beta$ -Ga <sub>2</sub> O <sub>3</sub>                                                                               | 17 |

| 2.9  | Experimentally determined thermal conductivity of $\beta$ -Ga $_2O_3$                                                 | 18 |

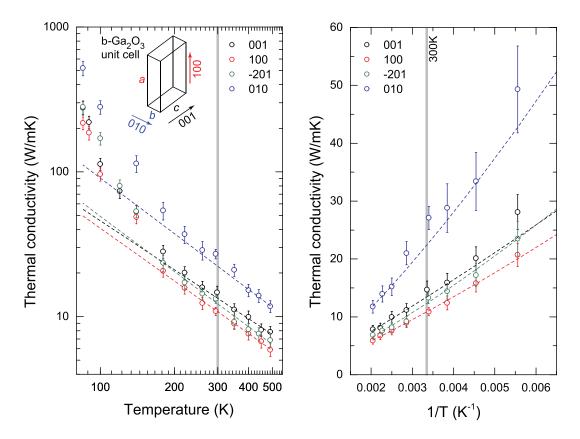

| 2.10 | A comparison of some widely cited wide-bandgap semiconductors                                                         | 19 |

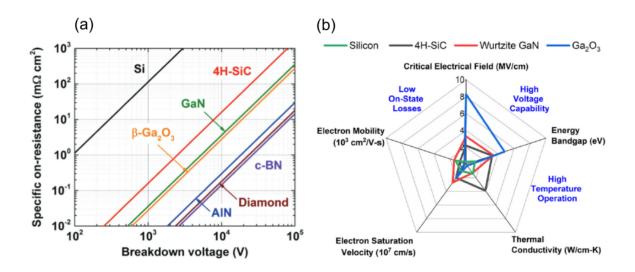

| 2.11 | Band diagrams demonstrating the formation of metal-semiconductor contacts                                             | 22 |

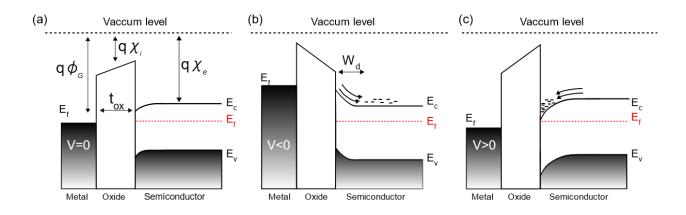

| 2.12 | Band diagram of a metal-oxide-semiconductor interface                                                                 | 23 |

| 2.13 | The capacitances of a MOS-CAP in the accumulation and depletion regimes.                                              | 24 |

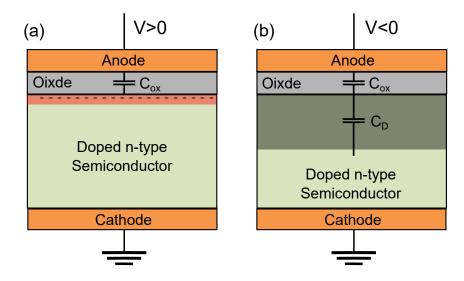

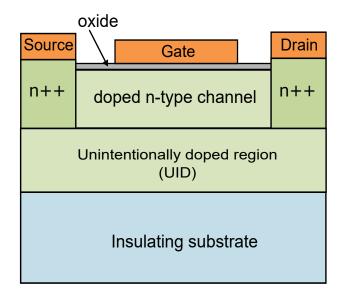

| 2.14 | Schematic of an n-channel MOSFET                                                                                      | 25 |

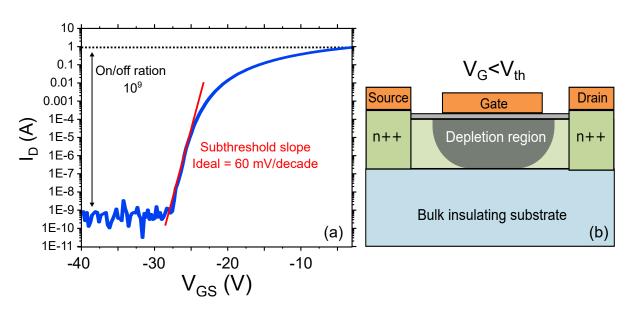

| 2.15 | Typical $I_D$ -V <sub>GS</sub> characteristic of a MOSFET                                                             | 26 |

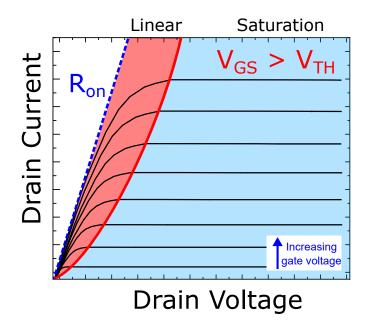

| 2.16 | Typical $I_D$ - $V_{DS}$ characteristic of a MOSFET                                                                   | 27 |

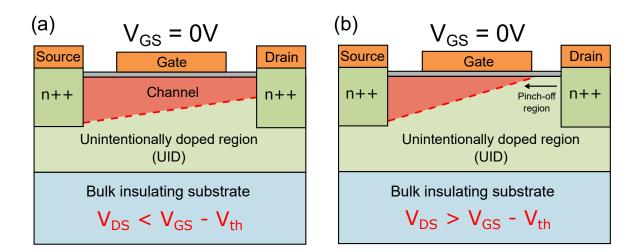

| 2.17 | Schematic demonstrating the principle of current pinch-off in a MOSFET.                                               | 28 |

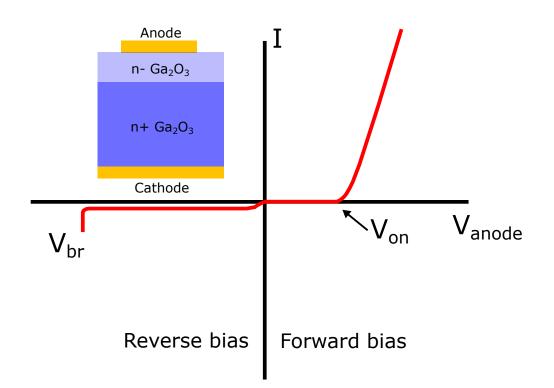

| 2.18 | Typical IV characteristic of a Schottky-barrier diode.                                                                | 29 |

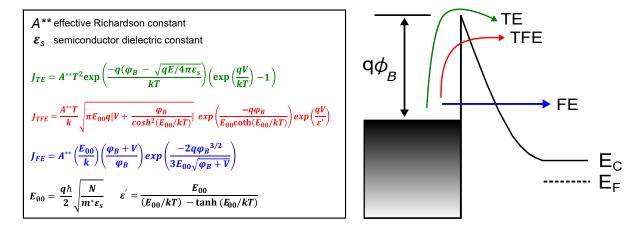

| 2.19 | Reverse bias leakage mechanisms across a Schottky-barrier.                                                            | 30 |

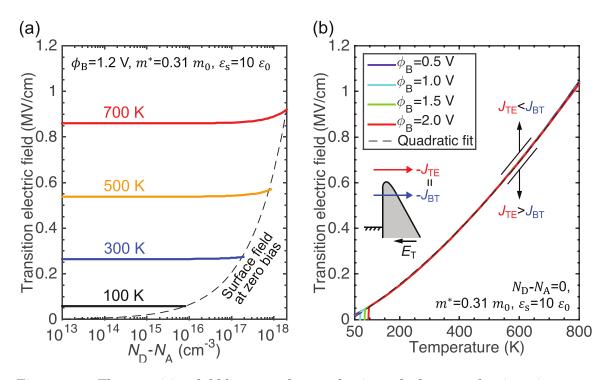

| 2.20 | The dominant leakage mechanisms over a $\beta$ -Ga $_2O_3$ Schottky-barrier as a function of                          |    |

|      | electric field.                                                                                                       | 30 |

| 2.21 | Demonstration of the RESURF effect in trench-MOS Schottky-barrier diodes                                              | 32 |

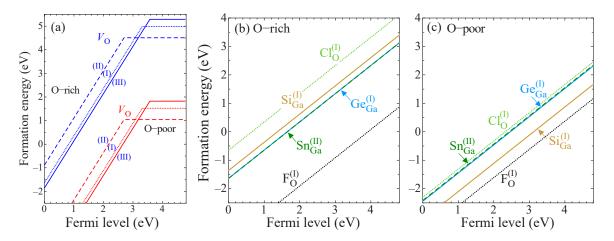

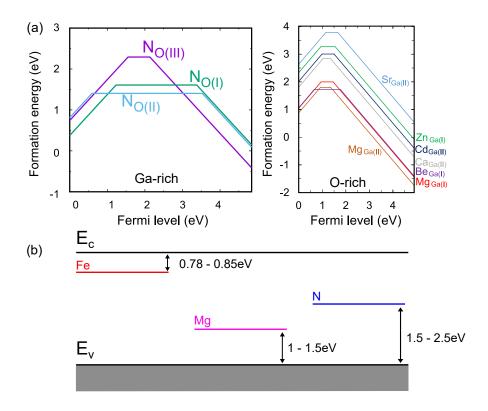

| 2.22 | Formation energies of donors in $\beta$ -Ga $_2O_3$                                                                   | 33 |

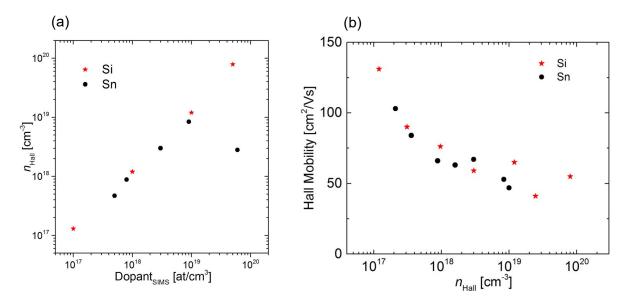

| 2.23 | Electron concentration and mobility as a function of Si and Sn donor density                                          | 34 |

| 2.24 | Formation energies of acceptors in $\beta$ -Ga <sub>2</sub> O <sub>3</sub>                                            | 35 |

FIGURE

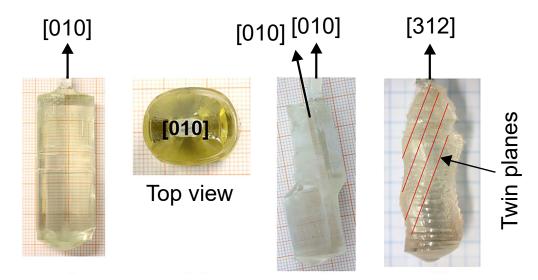

| 2.25         | Several $\beta$ -Ga <sub>2</sub> O <sub>3</sub> crystals grown down different crystalline directions using the Czochral- |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------|-----|

|              | ski method                                                                                                               | 36  |

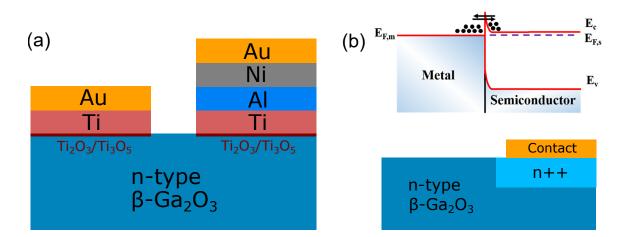

| 2.26         | A schematic of the typical metal stacks used to form ohmic contacts in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> devices.  | 39  |

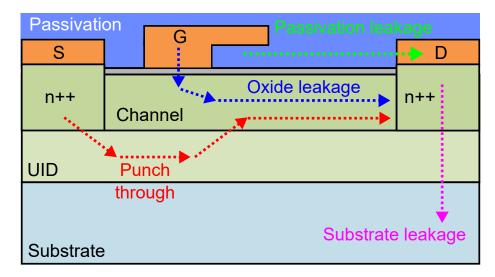

| 2.27         | Typical leakage paths in a MOSFET                                                                                        | 41  |

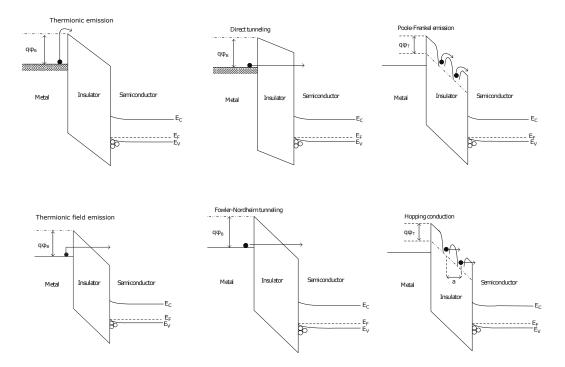

| 2.28         | Leakage mechanisms across a MOS interface.                                                                               | 42  |

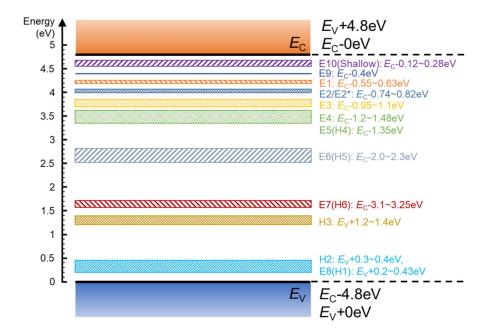

| 2.29         | Deep-level traps in $\beta$ -Ga <sub>2</sub> O <sub>3</sub>                                                              | 43  |

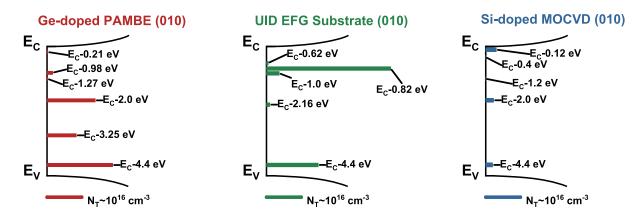

| 2.30         | Measured deep-level trap density for three growth methods.                                                               | 44  |

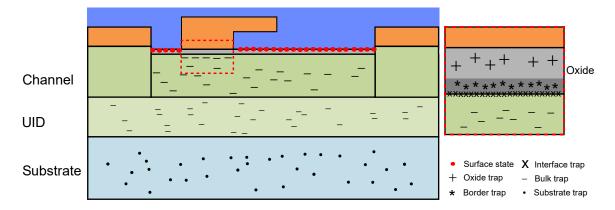

| 2.31         | The potential locations of trap states in a typical MOSFET.                                                              | 45  |

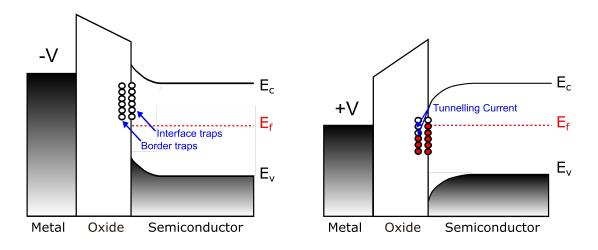

| 2.32         | Charging mechanism of interface and border traps                                                                         | 46  |

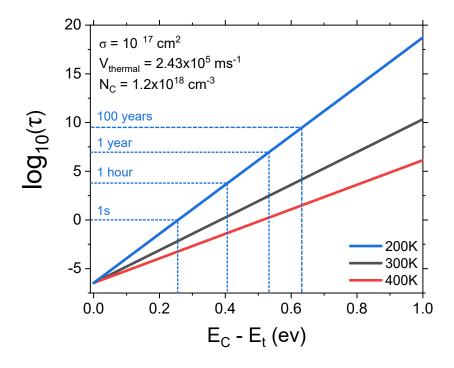

| 2.33         | Impact of conduction band offset on the detrapping time constant of an electron in GaN.                                  | 47  |

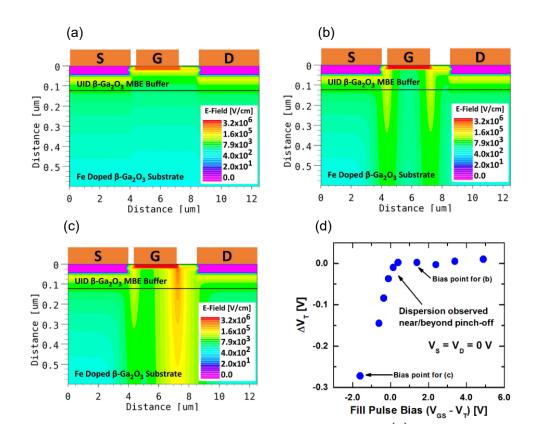

| 2.34         | Impact of stress bias on buffer trapping in a delta-doped $eta	ext{-}	ext{Ga}_2	ext{O}_3$ MESFET                         | 48  |

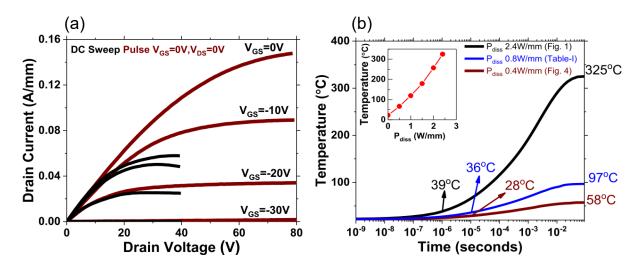

| 2.35         | Impact of device self-heating on the output characteristics of a $\beta$ -Ga $_2O_3$ MOSFET                              | 50  |

| 2.36         | Self-heating as a function of drain bias in a GaN HEMT                                                                   | 50  |

| 2.37         | A mean-time-to-failure Arrhenius plot for a set of GaN HEMTs.                                                            | 51  |

| 0.1          |                                                                                                                          | - 4 |

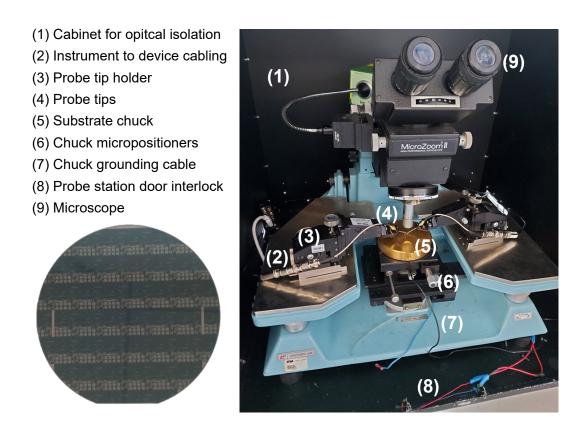

| 3.1          |                                                                                                                          | 54  |

| 3.2          |                                                                                                                          | 55  |

| 3.3          |                                                                                                                          | 55  |

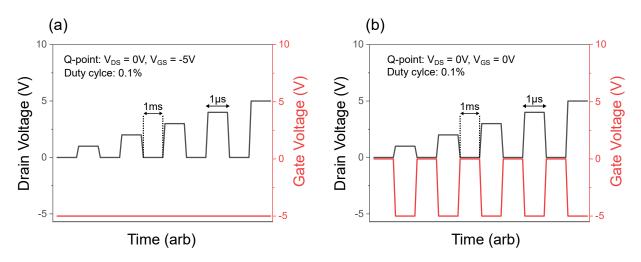

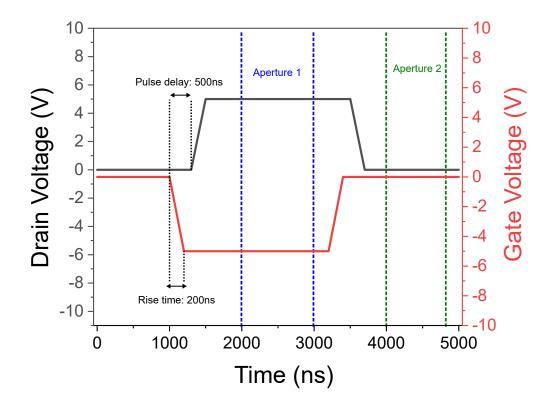

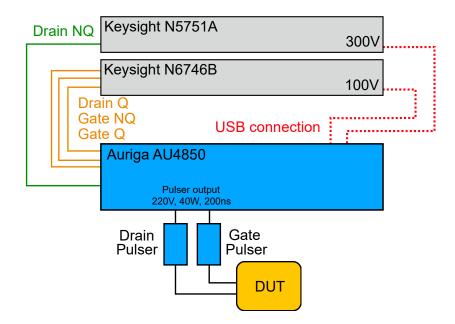

| 3.4          |                                                                                                                          | 58  |

| 3.5          |                                                                                                                          | 59  |

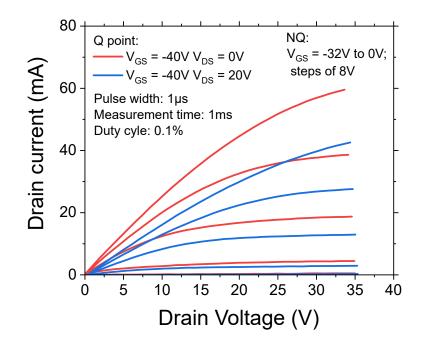

| 3.6          | Impact of quiescent point voltage on the pulsed output characteristics of a device                                       |     |

|              |                                                                                                                          | 60  |

| 3.7          |                                                                                                                          | 60  |

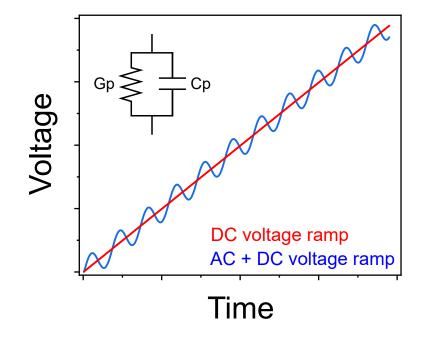

| 3.8          | Plot of a typical bias sweep used for capacitance-voltage characterisation.                                              | 62  |

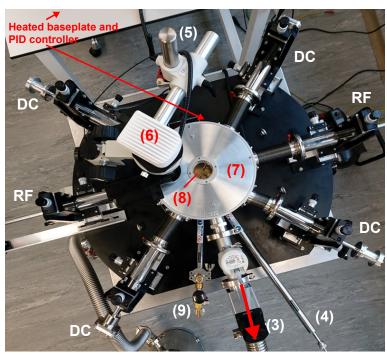

| 3.9          | Layout of the cryogenic characterisation probe station.                                                                  | 63  |

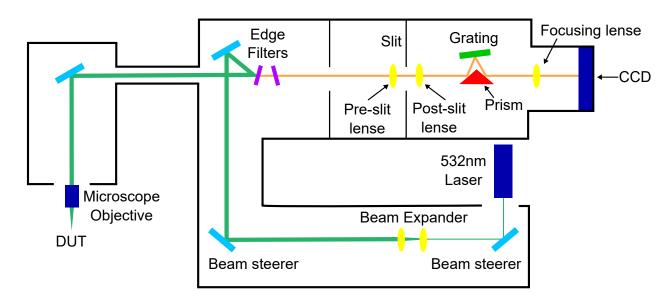

| 3.10         | Schematic of a Renishaw inVia Raman spectrometer.                                                                        | 64  |

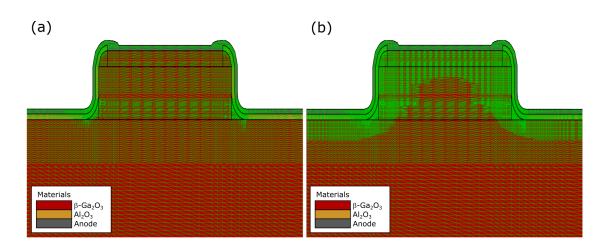

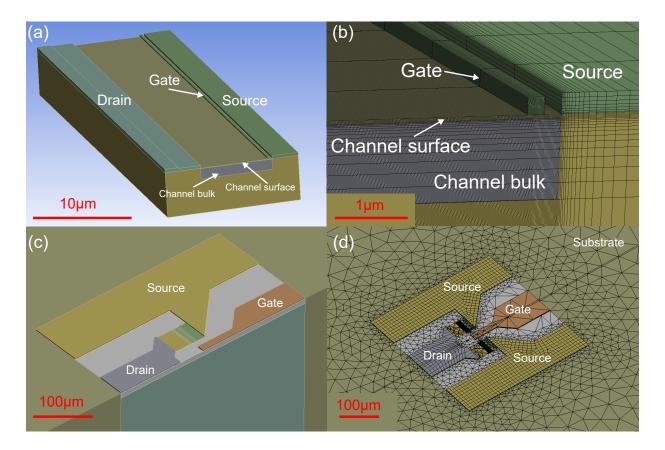

| 3.11         | A typical mesh used for device simulations in Silvaco ATLAS.                                                             | 67  |

| 3.12         | Example meshing for a device simulation in ANSYS.                                                                        | 69  |

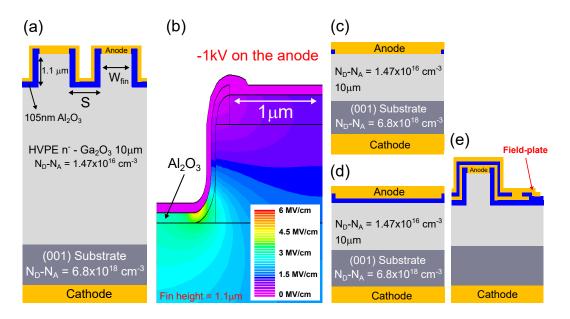

| 4.1          | Schematic of devices used to investigate the breakdown of trench-MOS Schottky-                                           |     |

| <b>T</b> . I | -                                                                                                                        | 73  |

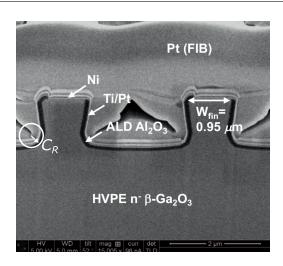

| 4.2          | FIB cross-section of a trench-MOS Schottky-barrier diode                                                                 | 74  |

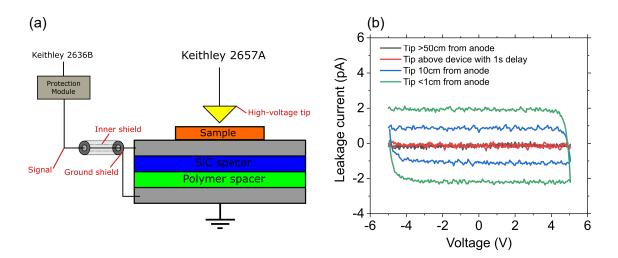

| 4.3          | Schematic of a high-voltage leakage current measurement system.                                                          | 75  |

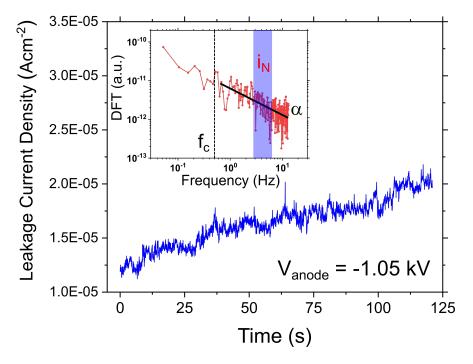

| 4.4          | Example leakage current trace and discrete Fourier transform.                                                            | 77  |

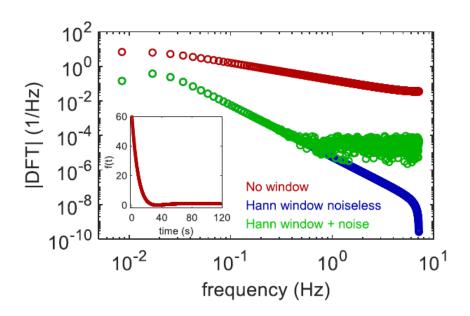

| 4.5          | The impact of a Hann windowing function on the discrete Fourier transform of a                                           | ••  |

| 1.0          | dummy function.                                                                                                          | 78  |

| 4.6          |                                                                                                                          | 80  |

| 4.0<br>4.7   | Simulated impact of trench-MOS fin width and separation on the expected peak                                             | 00  |

| т. 1         |                                                                                                                          | 81  |

|              | VIOVULIV IIVIU,                                                                                                          | υı  |

| 4.8  | Simulated MOS-CAP band-diagram and field-voltage scaling.                                                             | 82  |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | Step-stressed breakdown measurements as a function of fin width and separation                                        | 83  |

| 4.10 | Step-stressed breakdown measurements for three devices with the same fin width                                        |     |

|      | and separation                                                                                                        | 84  |

| 4.11 | Step-stressed breakdown measurements for three representative trench-MOS Schottky-                                    |     |

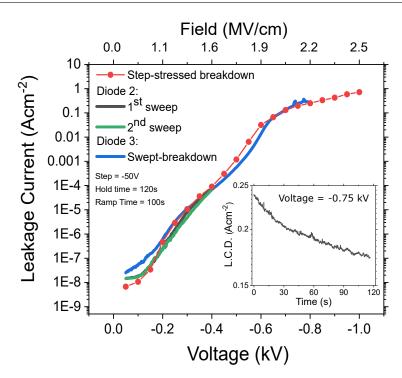

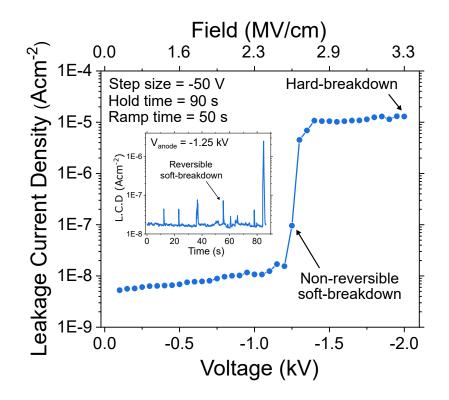

|      | barrier diodes.                                                                                                       | 85  |

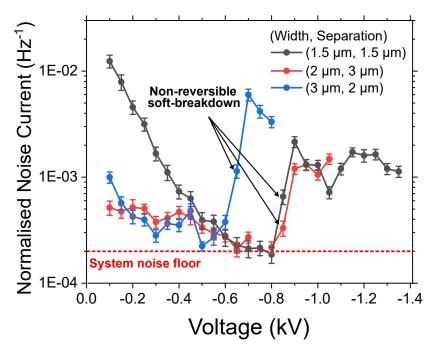

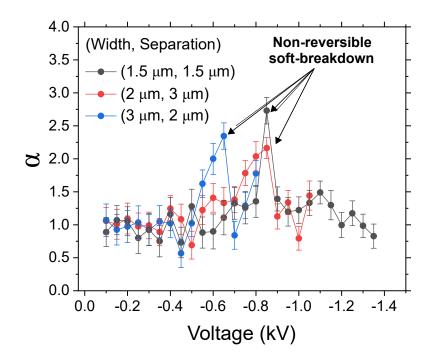

| 4.12 | Normalised noise currents extracted for three trench-MOS Schottky barrier-diodes. $% \mathcal{A}^{(n)}_{(n)}$ .       | 85  |

| 4.13 | The extracted power spectral density exponent for three trench-MOS Schottky barrier-                                  |     |

|      | diodes                                                                                                                | 87  |

| 4.14 | Stepped-stress breakdown and voltage-sweep measurements of planar Schottky-                                           |     |

|      | barrier diodes.                                                                                                       | 88  |

| 4.15 | Stepped-stress breakdown of a MOS-CAP.                                                                                | 89  |

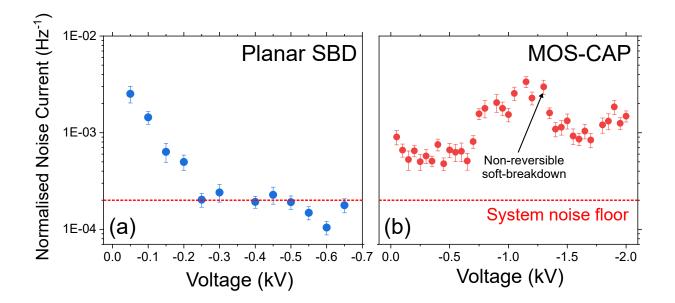

| 4.16 | Normalised noise current of a planar Schottky-barrier diode and MOS-CAP                                               | 90  |

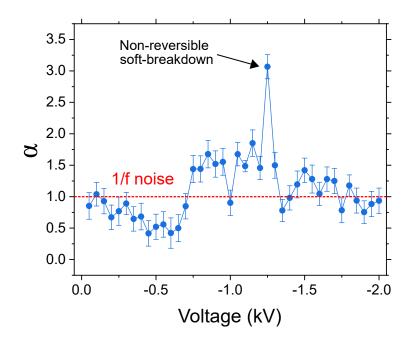

| 4.17 | Power spectral density exponent extracted for a MOS-CAP.                                                              | 90  |

| 5.1  | Previously reported MOSFET channel temperature profiles measured using Raman                                          |     |

|      | nanothermography.                                                                                                     | 98  |

| 5.2  | A schematic of the $\beta$ -Ga $_2O_3$ MOSFETs used for Raman nanothermography measure-                               |     |

|      | ments.                                                                                                                | 98  |

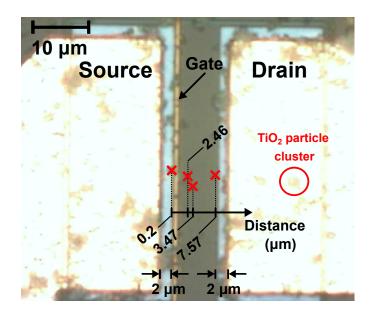

| 5.3  | Distribution of $TiO_2$ particles across the MOSFET channel.                                                          | 99  |

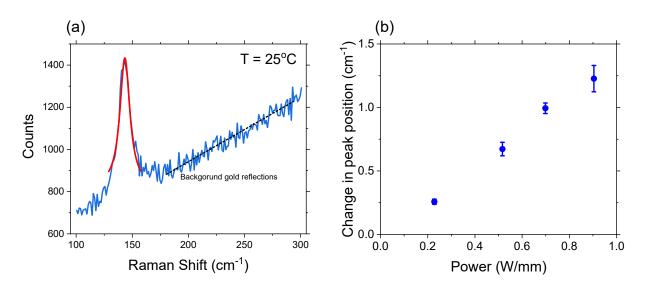

| 5.4  | Calibration of $TiO_2$ particle Raman shift with temperature                                                          | 100 |

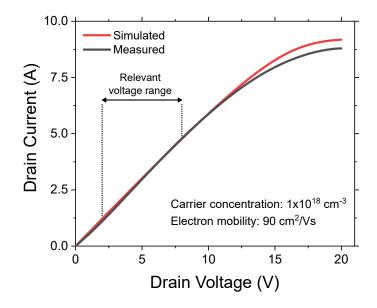

| 5.5  | Simulated vs measured $I_D$ -V $_{DS}$ curves.                                                                        | 101 |

| 5.6  | ANSYS simulation of the temperature profile of the MOSFET channel                                                     | 102 |

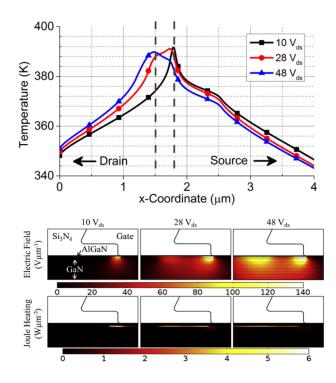

| 5.7  | Channel temperature profiles measured using Raman nanothermography                                                    | 103 |

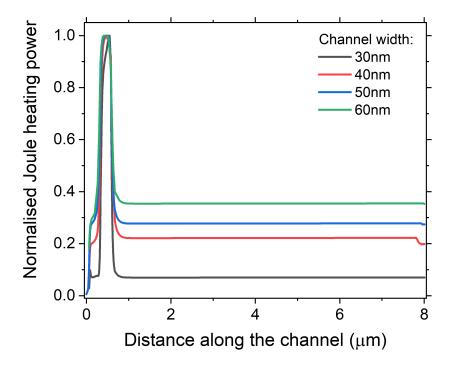

| 5.8  | TCAD simulation of channel Joule heating power for a MOSFET under bias                                                | 104 |

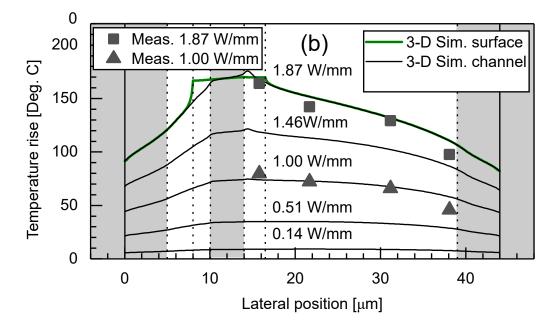

| 5.9  | 3D ANSYS simulations of the MOSFET temperature profile.                                                               | 105 |

| 5.10 | A comparison of temperature profiles extracted from simulations and measured using                                    |     |

|      | Raman nanothermography.                                                                                               | 106 |

| 5.11 | The impact of channel thickness on Joule self-heating.                                                                | 107 |

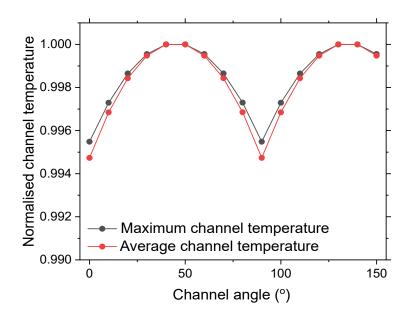

| 5.12 | Impact of device orientation on self-heating.                                                                         | 108 |

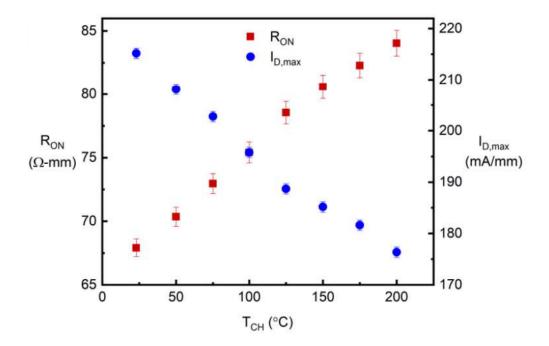

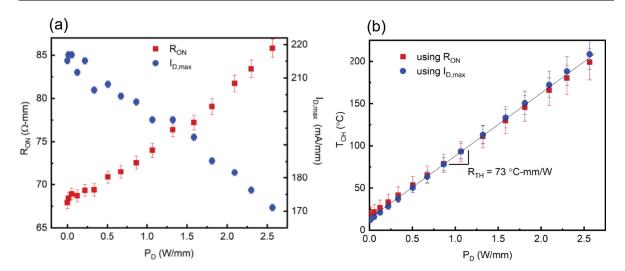

| 5.13 | Pulsed IV calibration of $I_D$ and $R_{on}$ with temperature.                                                         | 109 |

| 5.14 | Thermal resistance of the channel extracted using pulsed IV measurements. $\ldots$ .                                  | 110 |

| 5.15 | Transient thermal simulation of channel self-heating.                                                                 | 111 |

| 5.16 | Schematic of devices used to investigate anisotropic electrical behaviour                                             | 113 |

| 5.17 | Fabrication and layout of MOSFETs used to investigate anisotropic electrical behaviour.                               | 114 |

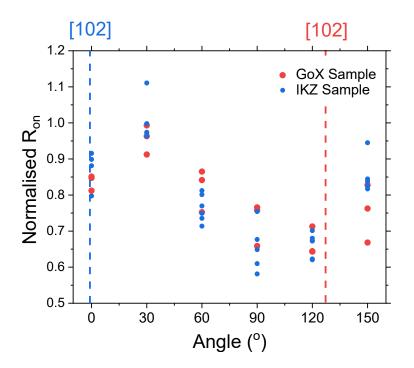

| 5.18 | Variation in device $R_{on}$ as a function of device orientation                                                      | 115 |

| 5.19 | Temperature dependence of device $R_{on}$ as a function of orientation                                                | 116 |

| 5.20 | Previously reported Raman scattering intensities of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> crystals as a function of |     |

|      | incident laser polarisation angle.                                                                                    | 117 |

| 5.21 | Measured change in a Raman spectra after a $60^{\circ}$ rotation of the device, relative to                            |

|------|------------------------------------------------------------------------------------------------------------------------|

|      | laser polarisation                                                                                                     |

| 5.22 | Measured variation in the intensity of three Raman modes, as a function of a substrate                                 |

|      | orientation relative to laser polarisation                                                                             |

| 5.23 | Extracted crystal orientations superimposed onto images of the sample substrates 119                                   |

| 5.24 | Variation in $R_{on}$ as a function of device orientation, relative to the sample substrate. 120                       |

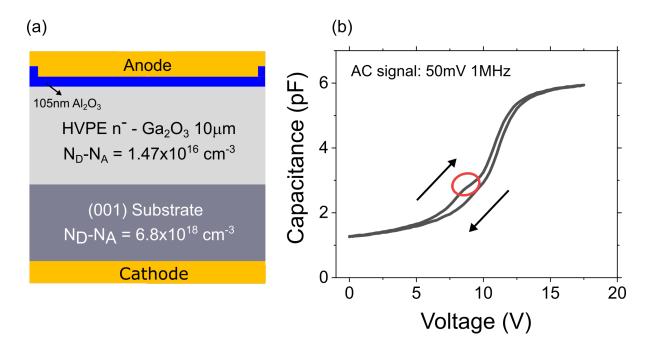

| 6.1  | Demonstration of a kink in the up-sweep of a MOS-CAP CV characteristic 127                                             |

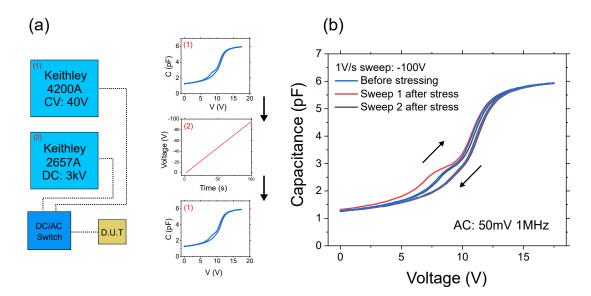

| 6.2  | High voltage CV measurement configuration                                                                              |

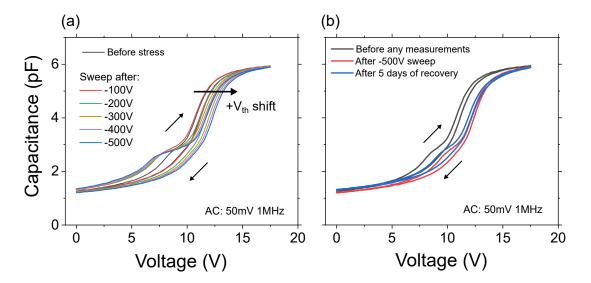

| 6.3  | Ledge in the CV characteristics, observed after negative bias stressing of the anode $129$                             |

| 6.4  | Interface charge stored in the MOS-CAP, extracted by integrating its CV characteristics.131                            |

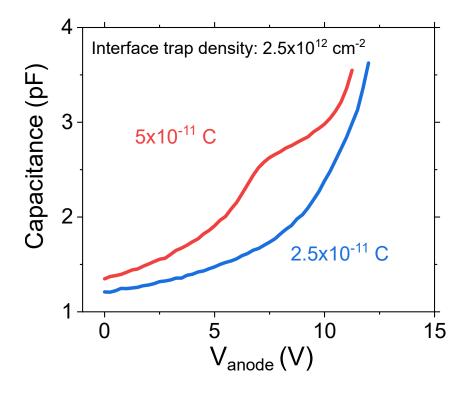

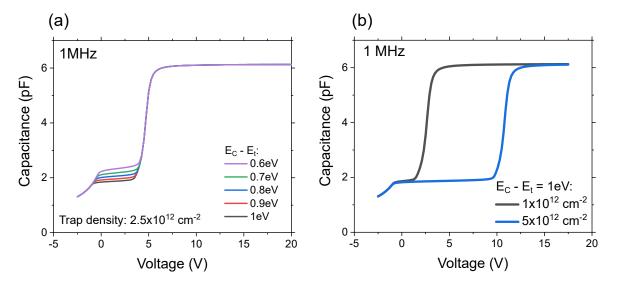

| 6.5  | Simulated steady-states CV characteristic of a MOS-CAP with interface traps 131 $$                                     |

| 6.6  | Simulated band diagram of a MOS-CAP with interface traps                                                               |

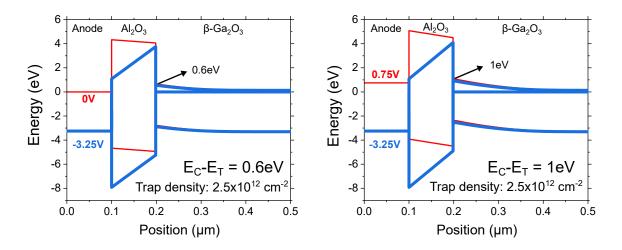

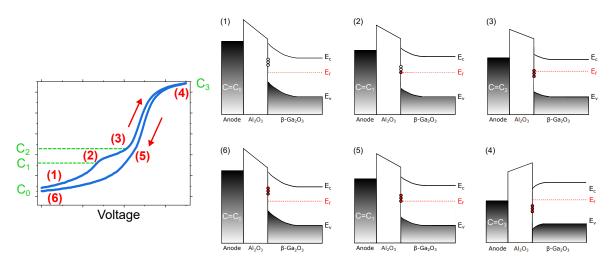

| 6.7  | Proposed interface trap model to explain hysteresis in CV characteristics 133                                          |

| 6.8  | Simulation of hysteresis in CV characteristics using interface traps and the Heiman                                    |

|      | model                                                                                                                  |

| 6.9  | Simulated vs measured CV curves used to extracted background trap density in the                                       |

|      | MOS-CAP                                                                                                                |

| 6.10 | A schematic of the field-plated MOSFET used to investigate bulk traps in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> . 139 |

| 6.11 | Impact of pulsed stress measurements on the MOSFET output characteristics 139                                          |

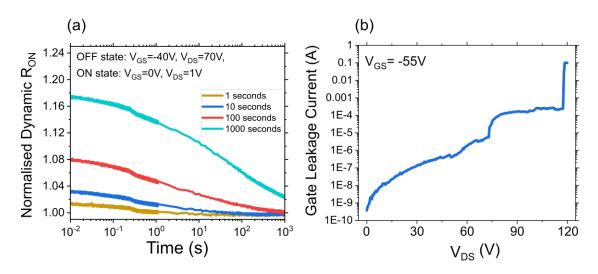

| 6.12 | Impact of long duration bias time on $R_{on}$                                                                          |

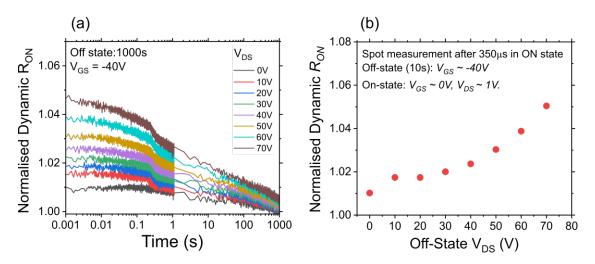

| 6.13 | Impact of stress bias on normalised Ron 141                                                                            |

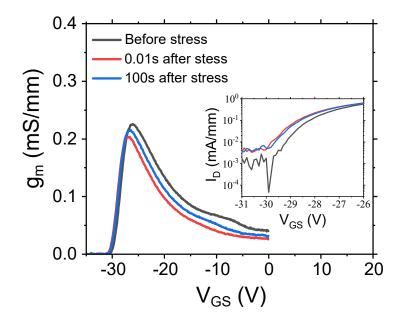

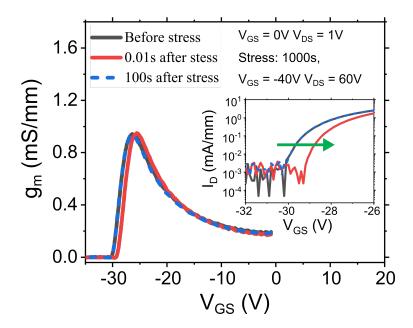

| 6.14 | Impact of bias stress on the MOSFET transfer characteristics                                                           |

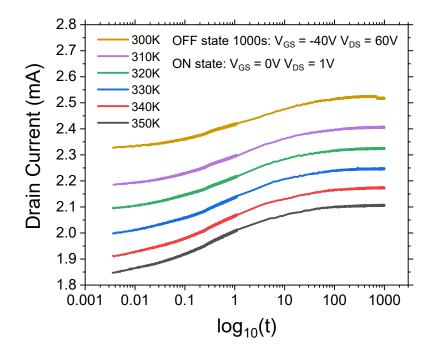

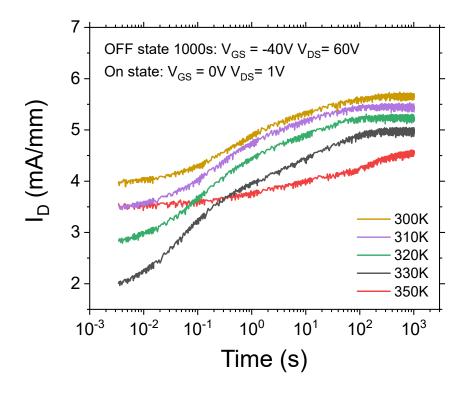

| 6.15 | Transient current recovery curves over the temperature range 300K-350K 143                                             |

| 6.16 | Principle of DLTS demonstrated using an $I_D$ recovery curve at 300K                                                   |

| 6.17 | Extracted detrapping time constants and the associated Arrhenius plot                                                  |

| 6.18 | Recovery in $I_D$ after thermal cycling of the sample between 100K-300K 146                                            |

| 6.19 | Arrhenius plot for the trapping behaviour after thermal cycling                                                        |

| 6.20 | Impact of bias stress on the MOSFET transfer characteristics after thermal cycling $147$                               |

| 6.21 | Observed transition in trapping behaviour at 350K                                                                      |

# LIST OF ACRONYMS AND INITIALISMS

- 2DEG Two Dimensional Electron Gas

- ALD Atomic Layer Deposition

- BFOM Baliga Figure of Merit

- CV Capacitance-voltage

- CVD Chemical Vapour Deposition

- CVU Capacitance Voltage Unit

- DFT Discrete Fourier Transform

- DLTS Deep-level Transient Spectroscopy

- DUT Device Under Test

- FE Field Emission

- FET Field Effect Transistor

- FIB Focused Ion Beam

- FN Fowler-Nordheim

- FOM Figure of Merit

- FWHM Full-width Half Maxima

- GND Ground

- GSG Ground-signal-ground

- HEMT High-electron-mobility Transistor

- HV High Voltage

- HVDC High-voltage Direct Current

- HVPE Halide Vapour Phase Epitaxy

- IV Current-voltage

- JFOM Johnson Figure of Merit

- MBE Molecular Beam Epitaxy

- MESFET Metal-semiconductor Field-effect Transistor

- MOCVD Metal Organic Chemical Vapor Deposition

- MOS Metal-oxide-semiconductor

- MOS-CAP Metal-oxide-semiconductor Capacitor

- MOSFET Metal-oxide-semiconductor Field-effect Transistor

- MTTF Mean-time-to-failure

- NNC Normalised Noise Current

- NQ Non-quiescent

- PLD Pulsed Laser Deposition

- Q Quiescent

- RESURF Reduced Surface Field

- RF Radio-frequency

- RIE Reactive Ion Etching

- SB Schottky-barrier

- SBD Schottky-barrier Diode

- SIMS Secondary Ion Mass Spectrometry

- SMU Source Measure Unit

- TE Thermionic Emission

- TFE Thermionic Field Emission

- TLM Transmission Line Measurement

- UID Unintentionally Doped

#### INTRODUCTION

In 2019 global CO<sub>2</sub> emissions were approximately 32Gt, with almost 13Gt being directly related to electricity generation [1][2]. Network transmissions losses equate to 8% of electricity generation in the UK, and as much as 18% in some regions globally [3]. In total, these transmission losses are responsible for approximately 1Gt of global CO<sub>2</sub> emissions [4]. Therefore, there is a pressing need for high efficiency, high power electronic components for improving grid efficiency and for aiding with the integration of renewable energy with existing power grids. This has spurred interest into components such high-voltage direct current (HVDC) converters for flexible grid operation, electric vehicle power trains, high-voltage wind farm components and photovoltaic inverters [5]. The commercialisation of such components has the potential to significantly impact global electricity demand and its associated CO<sub>2</sub> emissions.

Research into power electronics over the past 30 years has focused on improving the efficiency of silicon power devices [6]. However, as a mature technology, further optimisation of silicon power devices offers diminishing returns, with only another factor of two improvement in 30V FETs thought to be economically feasible [6]. Furthermore, in the area of high power electronics, silicon is limited by its relatively low breakdown field of 0.3 MV/cm [7]. These limitations have initiated the search for new wide-bandgap semiconductors for high-power applications, which will require voltage ratings that are beyond the practical limits of silicon [8]. In particular, research into wide bandgap semiconductors over the past few decades has focused on gallium nitride (GaN) and silicon carbide (SiC). Both of these semiconductors have significantly larger bandgaps than silicon (1.1eV): 3.2eV for 4H-SiC and 3.4eV for GaN. The wider bandgap afford these materials several key advantages in the design of power devices. Firstly, the bandgap of a semiconductor ( $E_g$ ) is directly related to its intrinsic breakdown field ( $E_{br}$ ), with an increase in  $E_g$  leading to an increase in  $E_{br}$ . The power-law relationship between  $E_g$  and  $E_{br}$ , ( $E_{br} \propto E_g^{\alpha}$ ), depends on the breakdown

mechanism of the semiconductor, and on whether it has a direct or an indirect bandgap, with the value of  $\alpha$  being determined empirically [9].  $\alpha$  is approximately 3 in the case of direct bandgap semiconductors, and between 2.5 and 3 in the case of indirect bandgap semiconductors [10]. As such, the breakdown fields of GaN and SiC are significantly higher than silicon, allowing for devices with higher voltage ratings. In addition, the aggressive scaling down of the device dimensions, in comparison to an equivalent silicon device with the same voltage rating, is made possible by the high breakdown fields of GaN and SiC; both GaN and SiC are capable of handling the higher electric fields associated with a reduction in device dimensions. This scaling down of dimensions leads to a reduction in carrier transit times in a device channel and a reduction in the intrinsic capacitances of the device, both of which are critical for radio-frequency applications. Finally, a wider bandgap is related to a reduced on-resistance  $(R_{on})$  of devices, as thinner drift regions and higher levels of doping can be achieved without triggering device breakdown [11]. The ability to fabricate GaN HEMTs with a 2DEG helps to further reduce the typical R<sub>on</sub> of power devices [12]. This lower R<sub>on</sub> leads to lower conduction losses, critical for efficient high-power device operation. The rapid progress in the field of wide bandgap semiconductors has been such that both GaN and SiC power devices are now commercially available [13][14].

As the power ratings of GaN and SiC power devices have increased, so has interest in high-voltage applications that will be difficult to achieve with commercially available devices. In particular, it will be difficult to push GaN and SiC device voltage ratings beyond 3kV and 20kV, respectively [5]. As such, research has shifted over the past decade to (ultra)wide-bandgap semiconductors, with potential voltage handling capabilities in excess of both that of GaN and SiC. By far, the most progress has been made in the field of  $\beta$ -gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) power electronics. The bandgap of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (4.9eV) is significantly larger than that of the competing wide-bandgap materials, corresponding to an intrinsic breakdown field of 8 MV/cm, (far in excess of SiC and GaN).  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has the added advantage that high-quality, large area crystals can be fabricated from the melt, using the inexpensive Czochralski method [15] [16]. This is in contrast to SiC and GaN; SiC substrates continue to be expensive, while GaN devices suffer from trapping effects associated with heterointerfaces in the substrate epitaxy [17]. Currently, melt grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafers remain expensive, however, a 20-fold decrease in the cost per wafer is expected by 2027 if production volumes reach 1 million wafers per year [18].

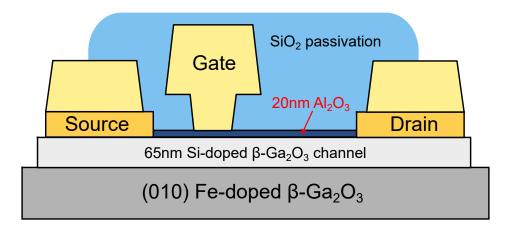

The first  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices, reported by Higashiwaki *et al.*, were single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MESFETs [19]. The high breakdown voltage and well behaved DC IV characteristics of these MESFETs spurred research into more sophisticated lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. A range of lateral MOS-FET devices have been achieved, with Al<sub>2</sub>O<sub>3</sub> now used as the standard insulator, due to its wide-bandgap (8.82eV), and ability to alloy with gallium oxide for lattice parameter matching [20][21]. MOSFETs with breakdown voltages as high as 750V were quickly achieved [22], and by 2018 breakdown voltages >1.8 kV had been reported [23]. As of 2022, lateral MOSFETs with breakdown voltages >8kV have been demonstrated [24].  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> HEMTs have

Figure 1.1: The current progress towards the commercialisation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. Figure reproduced from [18].

been successfully fabricated by Zhang et al., utilising a delta-doping architecture [25]. Interest in vertical devices has also grown over the last few years, as such devices can achieve higher breakdown voltages than lateral MOSFETs and HEMTs (due to their larger channel widths, and the associated lower electric fields). Vertical MOSFETs with breakdown voltages >1kV have been reported [26], with Mg-doped and N-doped charge blocking layers also having been successfully implemented in such devices [27][28][29]. Progress has also been made in the realisation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky-barrier diodes (SBDs) for low-frequency power switching applications. A number of different structures have been reported, with the most common being planar SBDs with field-plates, small-angle beveled field-plated SBDs, and trench-MOS SBDs [30]. A breakdown voltage of 1kV has been reported for the planar field-plated SBD structure [31], with a breakdown voltage of 1.1kV reported for beveled SBD structures [32]. Breakdown voltages >2.4 kV have been realised in the trench-MOS SBD architecture [33]. Despite the rapid progress made over the last few years,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power electronics remain a long way from commercialisation, as shown in Fig.1.1. The growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates are nearing commercial viability, with the epitaxial growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device channels not far behind. In contrast, device performance reported in the literature and the fabrication of dielectrics is lacking the quality and consistency required for industrial applications. Without resolving these key issues, a realisation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>'s potential is not possible at the system level. Several unresolved problems currently hinder device performance and reliability in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Arguably the most significant of these is the low thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. With a maximum thermal conductivity 10 times smaller than that of GaN, and 6 times smaller than that of SiC, self-heating is a critical design consideration [34]. Self-heating of power devices in the on-state can seriously degrade device performance, and lead to premature device failure [35]. Several thermal management solutions have been suggested in the literature, with heat sinking using metal layers, or the integration of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with diamond being the most promising [36][37]. However, adequate thermal management in power devices is yet to be demonstrated.

Even if the problem of self-heating is addressed, reliability would still be currently limited by the high-voltage operation required of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. This problem is ubiquitous to power devices, but is particularly acute in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>; its breakdown field of 8MV/cm is close to that of the insulating materials used for device dielectric layers and passivisation. As such, the fields that  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices are routinely expected to handle will pose a particular problem for device reliability, as the degradation of dielectric layers often trigger premature device failure. The degradation of device dielectrics has already been attributed to the premature failure of trench-MOS diodes [38], while the presence of interface states at an Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface has been demonstrated to degrade device performance in the form of an increased on-resistance [39]. Addressing the problem of dielectric reliability remains a key aim of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> research.

Finally, the wide bandgap of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> presents its own problem, in the form of deep-level trapping states. While the (ultra)wide-bandgap of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is indisputably an asset for high power applications, it also allows for large (>1eV) conduction and valence band offsets for defect and impurity states. The lifetime of such states can be arbitrarily long, and can easily exceed the lifetime of the device. Therefore, the charging of deep-level states can result in significant, semi-permanent, changes in device behaviour. The problem of deep-level trapping states is by no means unique to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, having previously been addressed in the case of C-doped GaN buffers [40]. However, GaN has benefited from two decades of research, over which the understanding of deep-level trapping states and modelling of their impact on device behaviour was refined. A similar effort is now required if  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device reliability is ever to be of a high enough standard for industrial applications.

## **1.1 Thesis Outline**

Investigating and understanding some of the unresolved issues that will hinder the commercialisation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices is the aim of this thesis. Both vertical and lateral devices are used to explore electrical and thermal issues that affect device performance, with device breakdown, self-heating, anisotropic electrical effects and trapping states all covered in the subsequent results chapters. A brief outline of the structure and content of the thesis follows.

Chapter 2 provides the necessary theoretical background required to understand the subsequent results chapters. This chapter begins with a discussion of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>'s structure, and its resulting band diagram, phonon modes, and phonon dispersion. The electrical and thermal properties of

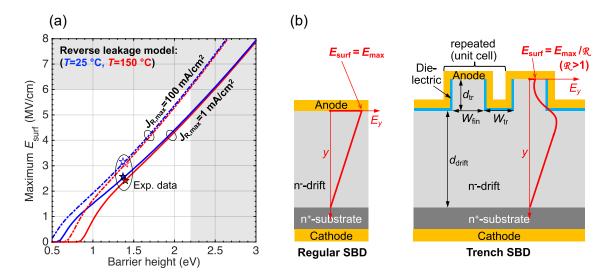

the material are then outlined, with particular attention paid to the parameters that impact device performance. The potential applications of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> are then discussed, with a comparison to other commonly cited (ultra)wide-bandgap semiconductors. The relevant device physics is then discussed, with an overview of metal-semiconductor contacts and metal-oxide-semiconductor (MOS) interfaces presented. The physics of these interface are then used to describe the operation of MOS field-effect-transistors. The applications and operation of Schottky barrier diodes (SBDs) is then introduced, along with the reduced surface field (RESURF) effect in trench-MOS SBDs: a critical technique for achieving breakdown voltages >1kV in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. The fabrication of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices is then outlined. Finally, some critical problems with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device reliability are discussed: instabilities in the electrical performance of devices are presented in the context of electron trapping and leakage current, and the lifetime limiting effect of device self-heating is reviewed.

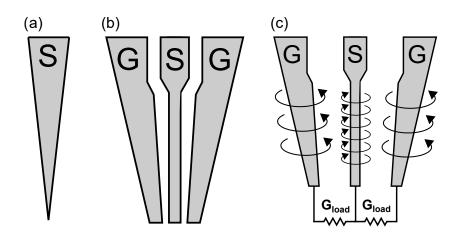

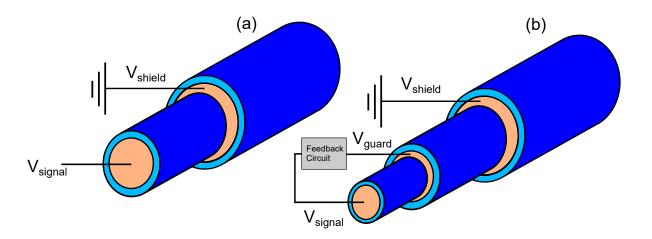

Chapter 3 details the experimental methods used throughout this thesis. The typical measurement environment used during the electrical characterisation of devices is introduced. The impact of different probe tips and cabling on the resolution of measurements is then discussed. Electric characterisation techniques are then discussed in detail. The DC characterisation and pulsed characterisation are explained, with the former used to measure device output characteristics and the latter to investigate self-heating and electron trapping. An overview of low-voltage capacitance-voltage measurements is then given. All three of the electrical characterisation techniques covered in chapter 3 can be integrated with a cryogenic probe station. The layout and the specifications of this probe station are briefly discussed. The functioning of a Raman spectrometer is then outlined, along with the resolution limits imposed by the choice of microscope objective, with this being relevant for the thermal characterisation of devices in later chapters. This chapter ends by detailing the simulation techniques used to support and corroborate measured data. Electrical simulations are performed using the Silvaco ATLAS drift-diffusion simulator and thermal simulations performed using the 3D ANSYS simulator. The models and meshing techniques relevant to both the the simulators are outlined.

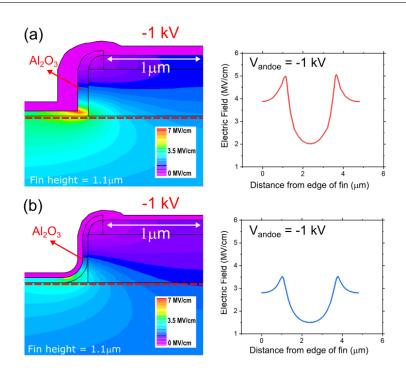

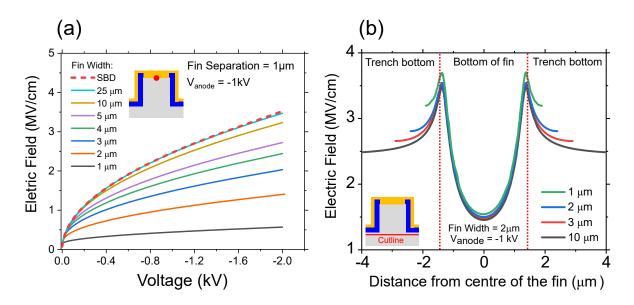

Chapter 4 focuses on the breakdown mechanisms in vertical trench-MOS  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottkybarrier diodes (SBD). These diodes employ a RESURF effect in order to achieve reverse bias operation far in excess of a planar Schottky-barrier diode architecture. The reverse leakage characteristics of these devices exhibited soft-breakdown events, in which a sharp increase in the leakage current is observed. A novel noise technique, developed by Dalcanale *et al.* [41], is applied to analyse the leakage current noise of these devices. A comparison of this noise data with that of planar Schottky-barrier diodes and planar MOS-CAP structures reveals a transition in the dominant leakage path of the trench-MOS diodes, from the Schottky barrier interface to oxide leakage. This change in leakage path is attributed to degradation of oxide layers in these diodes. The architecture of the trench etched inherently leads to high fields over the oxide layers, and so the observed device failure due to oxide degradation poses a significant problem to the commercialisation of such devices. Optimising the barrier height of the Schottky interface, to allow for a less aggressive RESURF effect, is the key to extending the lifetime of the trench-MOS Schottky-barrier diode structure.

Chapter 5 details potential issues in lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. Initially, device self-heating is characterised using the Raman nanothermography technique, with a direct measurement of channel temperature profiles performed. This data is compared to values of channel averaged temperature extracted using a pulsed IV technique, previously reported by Blumenschein et al. [42]. A high degree of agreement is observed between the Raman nanothermography technique and the pulsed IV technique. The agreement between these two techniques is attributed to the lack of thermal hotspots in the device channel. The anisotropy in device self-heating, with respect to gate orientation on the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate, is then investigated using 3D finite element thermal simulations. For simulated devices on a [010] orientated substrate, no significant anisotropy in the channel temperature is observed as a function of gate orientation. This is despite the anistropic thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Potential electrical anisotropy in device behaviour is then investigated, with low-field values of device Ron extracted across a number of MOSFETs with varying gate orientations. A large anisotropy is observed across two sample sets, however, Raman spectroscopy measurements demonstrates that this anisotropy is not correlated any underlying crystalline direction in the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate. As such, the anisotropy is attributed to the process and fabrication of these devices. Variations in device processing appear to dominate over any intrinsic anisotropy in the properties of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. This highlights the continuing problem of device quality in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>; as a relatively novel material, considerations such as thermal and electrical anisotropies should be secondary to optimising device quality.

Finally, chapter 6 is concerned with electron trapping in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices and its impact on device performance. Trapping at an Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface is explored using CV measurements of a MOS-CAP device after high-bias stressing. A distinct trapping ledge is attributed to the presence of interface traps and a model is proposed to explain the hysteretic effects observed in the CV characteristics. By considering the behaviour of the surface potential during the measurements, and by considering background charging effects, an upper bound of 2.3eV for the conduction band offset of the interface trap level is determined. Bulk traps in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs are then investigated using deep-level transient current spectroscopy measurements. Two large transitions in trapping behaviour are observed after thermally cycling the devices, with semi-permanent changes in device behaviour induced. A conclusive model of this behaviour could not be proposed, but it is likely that it is related to the charging of electrically isolated regions in the device. These problems are similar to those initially faced by other (ultra)wide-bandgap semiconductors, such as GaN, and highlights the importance of further research into the location and behaviour of deep-level trapping states in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. Chapter 7 presents the conclusions drawn from the results chapters of this thesis.

BACKGROUND

he focus of this chapter is to provide the theory and background required in the subsequent results chapters. This chapter will also discuss some relevant growth techniques, semiconductor physics and the background to some key measurement techniques. A key aim of this chapter is to benchmark the properties of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> against some other commonly cited (ultra)wide-bandgap semiconductors, as  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> remains a relatively novel material.

#### 2.1 Gallium Oxide

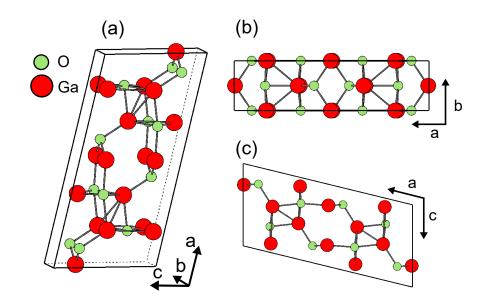

Gallium oxide is a compound semiconductor with six distinct polymorphs;  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$ ,  $\epsilon$  and  $\kappa$ . The  $\alpha$ -phase has a rhombohedral structure, the  $\beta$ -phase a monoclinic structure, the  $\gamma$ -phase a cubic structure and the  $\epsilon$ -phase an orthorhombic structure [43][44][45]. These four phases constitute the bulk of research into Gallium Oxide, with the  $\kappa$  and the  $\delta$  phase being the least studied [46][47]. The three principle phases targeted by device research are the  $\alpha$ ,  $\beta$  and the  $\epsilon$  phase. Of these phases, only the  $\beta$  phase is thermally stable, with all other phases being metastable. The formation free energies of the phases varies between phases in the following way:  $\beta < \epsilon < \alpha < \delta < \delta$  $\gamma$  [48]. The  $\alpha$  phase is stable up to growth temperatures of 800°C and has the corundum structure common to other oxides, e.g.  $Al_2O_3$  [46]. Therefore, this phase is well suited for integration with with other wide-bandgap semiconductors, e.g. the formation of heterojunctions. The  $\epsilon$  phase has an intrinsic polarisation due to crystal symmetry [49], and so is potentially of interest for the fabrication of gallium oxide high-electron-mobility-transistors (HEMTs) [50]. However, the vast majority of research into gallium oxide has focused on the  $\beta$ -phase. This thesis focuses exclusively on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices, and as such, the rest of this chapter will focus on the properties of this phase. The unit cell of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is shown in Fig.2.1. This cell contains 20 atoms (8 Ga and 12 O) and belongs to the space group C2/m. There are two inequivalent gallium sites, one with an octahedral

Figure 2.1: (a) The monoclinic structure of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, with the black lines marking the outline of the unit cell. The angle between the a and the c axes is 103.7°, with the a and b axes being orthogonal. (b) The unit cell viewed down the c direction (c) and the b direction.

coordination and the other with a tetrahedral coordination. The oxygen atoms sit in a distorted cubic structure, with three inequivalent sites. Two of these sites have a three-fold coordination and one site has a fourfold coordination.

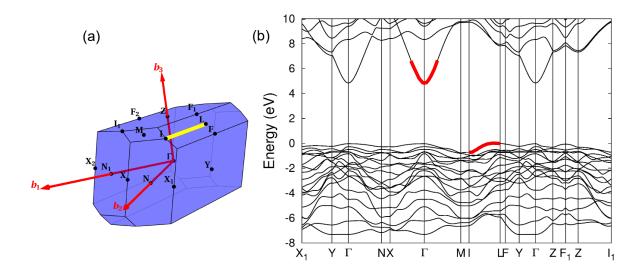

The first Brillouin zone of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>'s monoclinical crystal is required to understand its electronic properties. The Brillouin zone is defined as the reciprocal space Wigner-Seitz cell. A Wigner-Seitz cell is a primitive cell (a cell containing exactly one lattice point) around a lattice point. The points inside the cell are closer to the enclosed lattice point than any lattice points outside the cell [52]. While any number of primitive cells can be defined for a given lattice in reciprocal space, the Wigner-Seitz cell is unique [53]. Fig.2.2(a) shows the first Brillouin zone of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. The point  $\Gamma$ at the centre of the cell represents zero momentum state, with other points of high-symmetry labelled on across the cell. It can be shown that any reciprocal space momentum point outside of the first Brillouin zone is equivalent to a corresponding point within the zone. Therefore, the first Brillouin zone is all that is required to describe the energy-momentum relationship of carriers in the lattice [52]. This relationship is key to understanding the dynamics of carriers in a crystal, and is determined by the band structure of the material. Conventionally, the band structure is obtained by solving the Schrödinger equation for a single electron in the crystal [52],

$$\left[\frac{\hbar^2}{2m_e^*}\nabla^2 + V(\mathbf{r})\right]\Psi(\mathbf{r},\mathbf{k}) = E(\mathbf{k})\Psi(\mathbf{r},\mathbf{k}), \qquad (2.1)$$

where  $m_e^*$  is the effective mass of the electron,  $V(\mathbf{r})$  is the electronic potential of the lattice,  $E(\mathbf{k})$  is the electron energy and  $\Psi(\mathbf{r}, \mathbf{k})$  is the electron wave function. The Bloch theorem states that, if

Figure 2.2: (a) The first Brillouin zone of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, with the high-symmetry points labelled. The yellow line between the I and L point indicates the position of the valence band maxima. (b) The corresponding band structure, with the conduction band minia and valence band maxima outlined in red. Figure reproduced from [51].

$V(\mathbf{r})$  is periodic, then the solution to Eqn.2.1 will take the form of a Bloch function,

$$\Psi(\mathbf{r}, \mathbf{k}) = e^{(j\mathbf{k}.\mathbf{r})} U_b(\mathbf{r}, \mathbf{k}), \tag{2.2}$$

where  $U_b(\mathbf{r}, \mathbf{k})$  is a function with the same periodicity as the lattice; the Bloch function takes the form of an electron plane wave [54]. By solving Eqn.2.1 for each momentum state, the electronic band structure can be determined. Fig.2.2(b) shows the band-structure of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, with the high symmetry points labelled. Both the conduction band minima and the valence and maxima are highlighted in red, with the corresponding position of the valence band maxima indicated in Fig.2.2(a) by the yellow line. The key feature of this band structure is the approximately flat valence band. While  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is an indirect bandgap semiconductor, the small variation in the valence band means that the direct bandgap at  $\Gamma$ , and the indirect bandgap between  $\Gamma$  and L, have approximately the same energies (4.88eV and 4.84eV respectively) [51]. Low indirect bandgap transition probabilities, and the small energy difference between the direct and indirect bandgaps, means that  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> effectively acts as a direct bandgap semiconductor [15].

The flat valence band also has a strong impact on the carrier dynamics. The effective mass of carriers in a semiconductor are, to first order, determined by the curvature of the bands. In the vicinity of a band minia or maxima, the energy-momentum relationship can approximated using the quadratic expression:

$$E(k) = \frac{\hbar^2 k^2}{2m^*},$$

(2.3)

where  $m^*$  is the effective mass of the carrier. The conduction bands minima at  $\Gamma$  gives rise to an effective electron mass of  $0.27m_e$  [15], while the approximately flat valence band leads to

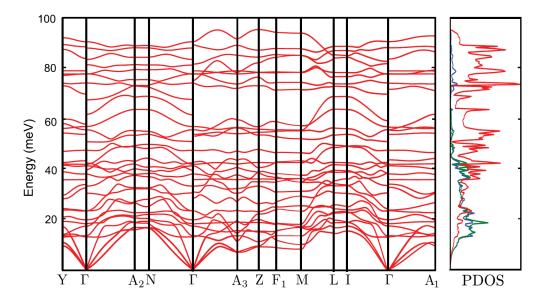

Figure 2.3: The phonon dispersion and phonon density of states for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Figure adapted from [61].

an incredibly high effective hole mass. This behaviour can be explained with reference to the hybridisation of electron orbitals. The conduction band is mainly composed of delocalised Ga 4s derived states, while the valence band is mainly formed by occupied O  $2p^6$  derived states with minor hybridization of the Ga 3d, 4p, and 4s orbitals [55] [56]. The tightly bound O 2p states give rise to the high effective hole mass, in common with other oxides [57]. It has been observed that holes are effectively static in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, as the result of the formation of static polaron states [58]. As such,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is a unipolar material, and only semiconductor devices exploiting n-type mobility are thought to be achievable [59].

#### 2.1.1 Raman Scattering and Phonon Dispersion in the Monoclinic Structure

In order to understand thermal transport in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> it is necessary to understand the vibrational modes of the lattice, with these modes being primarily responsible for the storage and transport of heat. For a unit cell with N atoms, there are 3N degrees of freedom, with each degree of freedom giving rise to a vibrational mode. Of these 3N modes, 3N-3 are optical modes, and 3 are acoustic [54]. The acoustic modes represent collective vibrations that are in phase across the unit cell, while the optical modes represent out of phase vibrations.

The vibrational modes of a lattice can represented as quantised bosonic excitations, or as phonon modes.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has 30 phonon modes (27 optical and 3 acoustic), as its primitive cell contains 10 atoms with three translational degrees of freedom. The dispersion and density of states of these modes is shown in Fig.2.3, with the high-symmetry points of the Brillouin zone labelled. The 27 optical modes can be represented by irreducible representations at the  $\Gamma$ -point [60],

Figure 2.4: The displacement of atoms in the primitive cell of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> for the Raman-active modes with A<sub>g</sub> symmetry. The primitive cell is viewed down the [010] direction. The relative size of the arrows indicates the relative amplitude of the atomic displacements, with values taken from [62].

$$\Gamma^{opt} = 10A_g + 5B_g + 4A_u + 8B_u, \tag{2.4}$$

where the  $A_g$  and  $B_g$  modes are Raman active, and the  $A_u$  and  $B_u$  modes are IR active. A and B correspond to a symmetry of the mode, with the A modes being symmetric with respect to principal axis of symmetry, and the B modes being antisymmetric. Fig.2.4 shows the physical displacement of atoms in the primitive cell for each of the 10  $A_g$  modes, with the primitive cell viewed down the [010] direction. The relative amplitude of each displacement is represented by the relative size of each arrow.

The scattering of light can be used to measure the properties of a crystal, such as the lattice temperature, the degree of atomic disorder present in the crystal and the presence strain fields. One such process is Raman scattering, in which the interaction between light and phonon modes leads to the inelastic scattering of photons. Raman scattering can be modelled both classically

#### CHAPTER 2. BACKGROUND

Figure 2.5: Energy transitions relevant to Raman scattering. Rayleigh scattering correspond to an elastic scattering event, whereas Raman scattering is an inelastic process. Stokes and anti-Stokes scattering are both types of Raman scattering.

and using quantum mechanics. A treatment of the classic view of Raman scattering is present by Ferraro *et al.* [63], while a quantum mechanical picture is detailed by Szymanski *et al.* [64]. In this section, the quantum mechanical picture will be outlined.

Raman scattering can be explained with reference to a simplified energy level system, with three scattering schemes shown in Fig.2.5. Initially the system exists in the zero-vibration ground state. If a photon energy  $\hbar\omega_0$  is incident on the crystal, it can be elastically scattered (Rayleigh scattering). The system is excited to a virtual energy state and then relaxes, emitting a photon of the same energy. This process accounts for the vast majority of all scattering events, with only 1 in  $10^{6}$ - $10^{8}$  photons scattered inelastically [65]. Raman scattering consists of two inelastic processes: Stokes scattering and anti-Stokes scattering. In the case of Stokes scattering, the incident photon excites the system from the ground state to a virtual energy state. The system then relaxes to the ground state through the generation of photon, energy  $\hbar\omega_s$ , and a phonon with energy  $\hbar\omega$ , with a net transfer of energy from the photon to the lattice. In the case of anti-Stokes scattering, the lattice is initially excited to an excited state via the absorption of lattice phonon with an energy of  $\hbar\omega$ . The incident photon is then absorbed, promoting the system to a higher energy virtual state. Relaxation to the ground state leads to an emission of a photon with energy  $\hbar\omega_{as}$ , with a net transfer of energy from the lattice to the photon. The energies of the Stokes and the anti-Stokes photons are given by the following expressions,

$$Stokes: \hbar\omega_s = \hbar(\omega_0 - \omega) \tag{2.5}$$

$$anti-Stokes: \hbar\omega_{as} = \hbar(\omega_0 + \omega). \tag{2.6}$$

The relative intensities of the two Raman scattering processes is determined by the ground state configuration of the system. At finite temperature T, the population of states will be distributed

between the ground state and higher energy vibration states. As phonons are bosons, the relative population of the ground state and higher energy states is determined by Bose-Einstein statistics. In the case where  $\omega \ll \omega_0$ , the Bose-Einstein distribution can be simplified to a Boltzmann factor, yielding a relationship between the Stokes intensity ( $I_s$ ) and anti-Stokes intensity ( $I_{as}$ ) of the form [66]:

$$\frac{I_{as}}{I_s} \approx exp\left(-\frac{\hbar\omega}{kT}\right). \tag{2.7}$$

At room temperature, the majority of vibration modes will have an energy greater than the Boltzmann factor, and so the Stokes scattering intensity will be greater than that of the anti-Stokes scattering intensity. This disparity increases with increasing phonon mode energy. As such, the contribution of the anti-Stokes component to the Raman scattering intensity can often be discounted.

The Raman scattering intensity is also dependent on the polarisation of the incident photons relative to the lattice. The scattering intensity can be expressed in the form,

$$I \propto |\hat{e}_0 \cdot \mathscr{R} \cdot \hat{e}_s|, \tag{2.8}$$

where  $\hat{e}_0$  is the polarisation of the incident photon,  $\hat{e}_s$  the polarisation of the scattered photon and  $\mathscr{R}$  the Raman tensor. The Raman tensor is a second order tensor whose elements are determined by the symmetry of the phonon mode. In the case of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, the Raman tensors for the A<sub>g</sub> and B<sub>g</sub> modes are,

$$A_{g}: \mathscr{R} = \begin{pmatrix} a & d & 0 \\ d & b & 0 \\ 0 & 0 & c \end{pmatrix}, \quad B_{g}: \mathscr{R} = \begin{pmatrix} 0 & 0 & e \\ 0 & 0 & f \\ e & f & 0 \end{pmatrix},$$

(2.9)

where a, b, c, d and e are constants. The structure of these tensors leads to selection rules that can result in either set of modes being suppressed, based on the polarisation configuration of the measurement. For instance,  $B_g$  modes are forbidden on the (010) plane [67]. Eqn.2.8 is valid when the incident polarisation of the photons is well defined and the scattering can be approximated as point-scattering [67]. In the case of highly anistropic crystals, these assumptions are not valid. A significant degree of birefringence in anistropic crystals leads to a change in polarisation of the incident photons: from linear polarisation to elliptically polarisation [68]. A full treatment of the Raman tensor elements for the anisotropic monoclinic structure is given by Kranert *et al.* [67]. The frequency of Raman modes are temperature dependent, and so can be utilised to study temperature changes in a semiconductor. A decrease in the frequency of modes is observed as temperature increases. Several physical effects induce change in frequency, with damping of phonons, induced strain in the crystal and changes in the crystal volume all contributing. The frequency of a mode at a given temperature ( $\omega(T)$ ) is simply given by subtracting each of these contributions from the harmonic phonon frequency ( $\omega_0$ ):

$$\omega(T) = \omega_0 - \Delta \omega_s(T) - \Delta \omega_d(T) - \Delta \omega_v(T).$$

(2.10)

$\Delta \omega_s(T)$  represents the thermal strain generated between materials with different coefficients of thermal expansion, with this term equal to zero for a single crystal.  $\Delta \omega_d(T)$  represents damping of phonons with temperature, and  $\Delta \omega_v(T)$  represents changes in frequency due to thermal expansion of the crystal volume. Each of these terms has a complex temperature dependence. Cui *et al.* proposed an empirical formula to fit the temperature dependence of phonon frequencies in general [69],

$$\omega(T) = \omega_0 - \frac{A}{e^{(Bhc\omega_0/kT)} - 1},$$

(2.11)

where A and B are fitting parameters. At high temperature this expression can be approximated with the following linear expression,

$$\omega(T) = -\frac{Ak\Delta T}{Bhc\omega_0}.$$

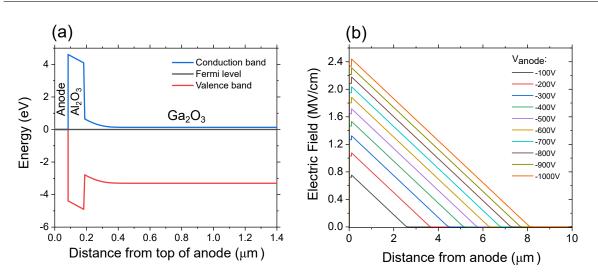

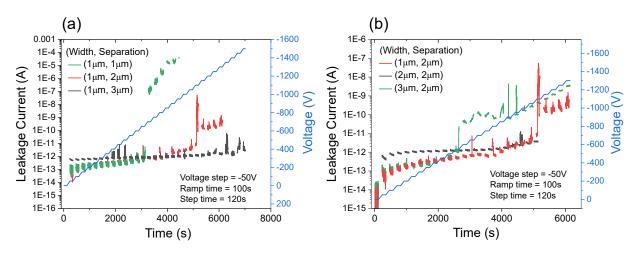

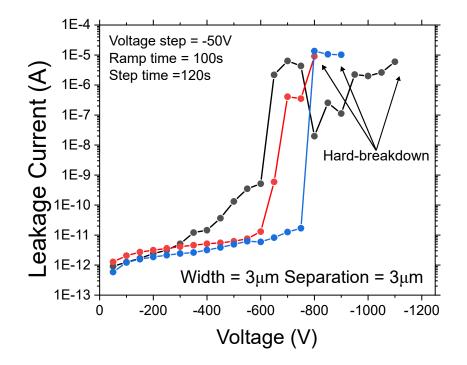

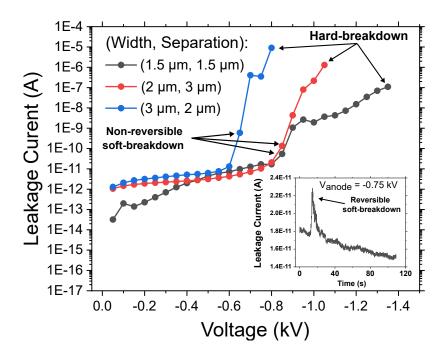

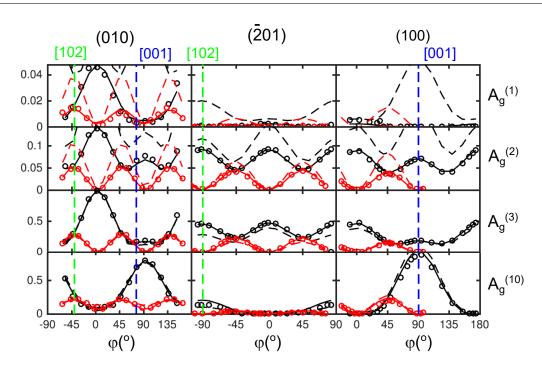

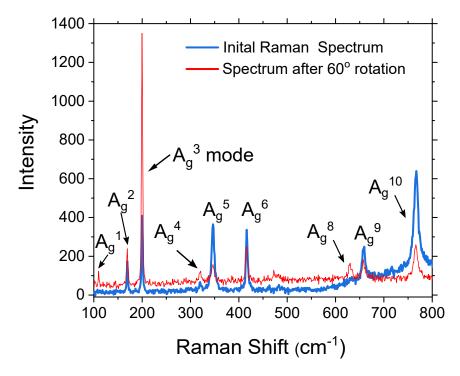

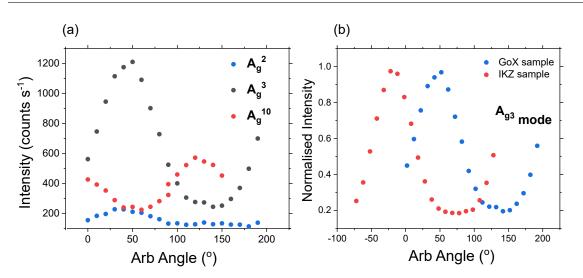

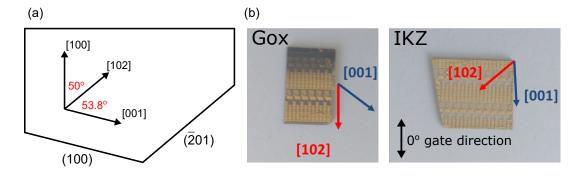

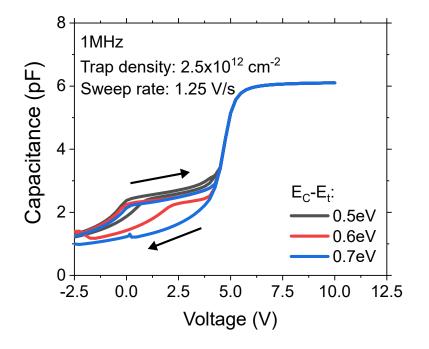

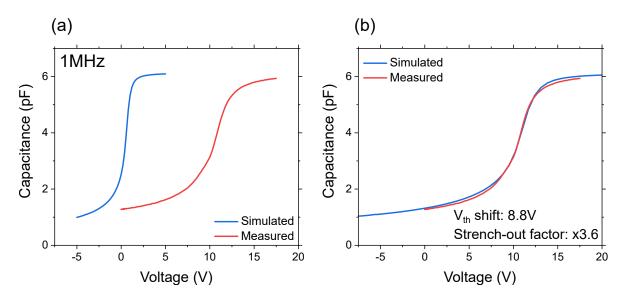

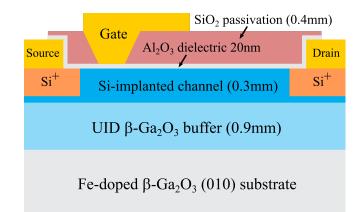

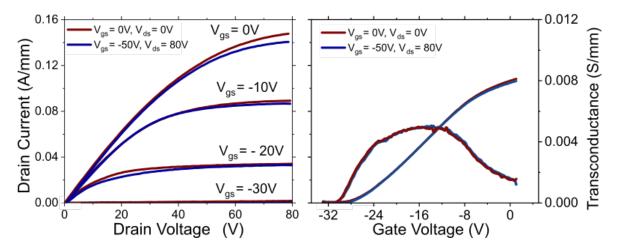

(2.12)