## This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author:

Scott, John R

**Classical Control Systems for Photonic Quantum Computing**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

- · Bibliographic details for the item, including a URL

- An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# CLASSICAL CONTROL SYSTEMS FOR PHOTONIC QUANTUM COMPUTING

#### John Scott

A dissertation submitted to the University of Bristol in accordance with the requirements for award of the degree of Doctor of Philosophy (PhD) in the Faculty of Engineering, School of Computer Science, Electrical and Electronic Engineering, and Engineering Maths

October, 2022

Word count: 43,000

#### Abstract

Photonic quantum computing is based on the use of single photons as qubits. There are many proposed architectures for the realisation of photonic quantum computers; however, the design of electronic control systems for these architectures is substantially less well understood. Furthermore, most of these proposals for photonic quantum computing use measurement-based quantum computing (MBQC), or similar schemes that avoid the necessity for long-lived photons in the system. These schemes can appear quite abstract and theoretical, and cause a barrier to entry for electronic engineers hoping to design control systems for photonic quantum computing.

This thesis has two primary objectives. First, to present a methodology for evaluating prospective control system designs for photonic quantum computers based on MBQC, based on the analysis of timing constraints that these implementations impose on the full quantum computing system. These timing constraints are derived by analysing a concrete design, targeting a simple model for photonic quantum computing, in a case where the control system is simple enough to design without needing hardware emulation to evaluate design trade-offs. Constraints in a more complicated (and more realistic) setting, involving photonic quantum computing using incomplete cluster states, are addressed by emulating one possible choice of algorithms that could be used as the basis for a control system in this case. This latter emulation provides a framework for analysing other prospective algorithms, and forms the basis for an analysis system that could be modified to investigate other photonic quantum computing models.

The second objective is to present MBQC-based photonic quantum computing in a simple diagrammatic form, which focuses on the control system specification rather than the mathematics of MBQC. It is hoped that this lowers the barrier to entry for engineers interested in photonic quantum computing control system design.

#### Acknowledgements

This thesis would not have been possible without the support from a great many of my colleagues, friends, and family.

I would like to thank my supervisor, Krishna Coimbatore Balram, for providing constant support throughout my PhD, and for many interesting and varied discussions during our regular weekly meetings. His ideas and suggestions have materially improved this thesis, and I will miss our discussions surrounding the future development of control systems in photonic quantum computing.

I would also like to thank the staff and students in the Quantum Engineering Centre for Doctoral Training, who have provided a supportive and friendly environment in which to conduct a PhD. In particular, I would like to thank Alex Qiu, Naomi Solomons and Oliver Thomas, for our entertaining weekly discussions involving our PhD projects and other miscellany! I would like to especially thank Oliver Thomas, for all the other discussions we have had over the last four years, and all his helpful suggestions relating directly to my PhD.

I would like to extend my warm thanks to Lana Mineh, who has not only been a constant source of support, but also helped me solve programming problems, aided me in checking calculations, and discussed ideas with me relating to many aspects of this thesis. Her contribution cannot be overstated.

Finally, my sincere gratitude goes to my family, for providing constant help and support to me over the last four years, and for their help checking and offering suggestions relating to this thesis.

### Declaration

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

| CICINIDID | DATE:      |

|-----------|------------|

| SICENIELD | 1) A 1 H:  |

| DICHTED.  | <br>D111 L |

## Contents

|    | Ack    | tract                                                      | i<br>iii<br>v |

|----|--------|------------------------------------------------------------|---------------|

| Li | st of  | Figures                                                    | xi            |

| Li | ist of | Tables                                                     | xii           |

| Li | st of  | Abbreviations                                              | xiii          |

| 1  | Intr   | roduction                                                  | 1             |

|    | 1.1    | Why investigate control system design?                     | 3             |

|    | 1.2    | Comparison of classical and quantum computers              | 9             |

|    | 1.3    | Gate-based quantum computing                               | 13            |

|    |        | 1.3.1 Quantum gates                                        | 15            |

|    |        | 1.3.2 Measurement                                          | 17            |

|    | 1.4    | Photonic qubits                                            | 19            |

|    | 1.5    | Reading this thesis                                        | 21            |

| 2  | Ove    | erview of photonic MBQC                                    | 23            |

|    | 2.1    | Measurement-based quantum computing                        | 26            |

|    |        | 2.1.1 Logical qubits and measurement patterns in MBQC $$ . | 27            |

|    |        | 2.1.2 Performing the cluster qubit measurements            | 29            |

|    |        | 2.1.3 Measurement basis angles and adaptive measurements . | 30            |

|    |        | 2.1.4 Byproduct operator calculations                      | 33            |

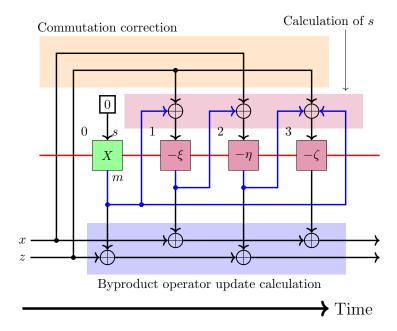

|    |        | 2.1.5 Commutation corrections                              | 34            |

|    | 2.2    | Simplified model of photonic quantum computing             | 37            |

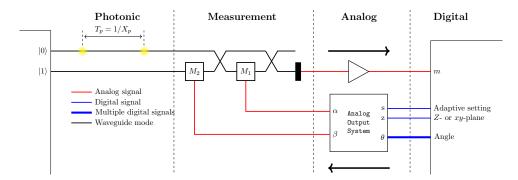

|    |        | 2.2.1 Photonic MBQC                                        | 37            |

|    |        | 2.2.2 Timing constraints on the cluster state              | 38            |

|    |        | 2.2.3 The full MBQC system                                 | 39            |

|    | 2.3    | Summary                                                    | 42            |

| 3  | Cor    | ntrol system design for photonic MBQC                      | 45            |

|    | 3.1    | Overall system design                                      | 45            |

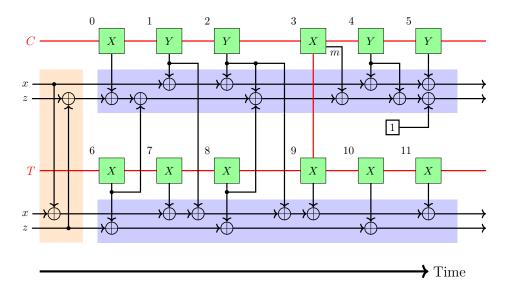

|    |        | 3.1.1 Logical qubit unit cells                             | 47            |

|   |     | 3.1.2 Clock planning                                              |  |

|---|-----|-------------------------------------------------------------------|--|

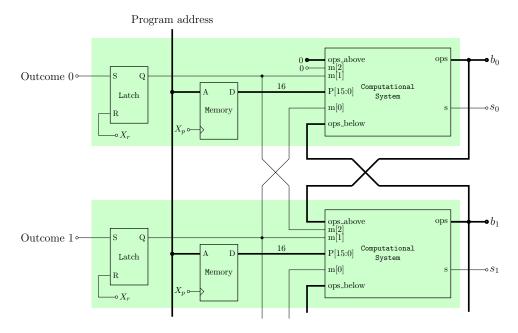

|   | 3.2 | Computational system design                                       |  |

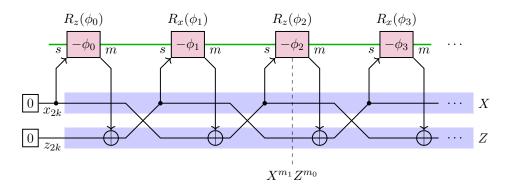

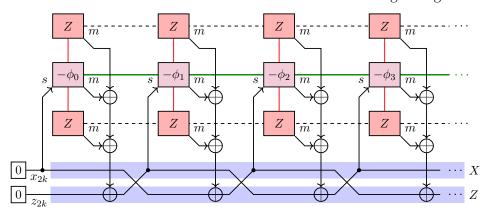

|   |     | 3.2.1 Adaptive measurement setting generation 51                  |  |

|   |     | 3.2.2 Byproduct operator calculation 53                           |  |

|   |     | 3.2.3 Commutation corrections                                     |  |

|   |     | 3.2.4 Program word                                                |  |

|   | 3.3 | FPGA implementation of the design                                 |  |

|   | 3.4 | Timing analysis                                                   |  |

|   | 3.5 | Discussion of extensions to the design 64                         |  |

|   | 3.6 | Summary                                                           |  |

| 4 | Des | ign simulation and verification 67                                |  |

|   | 4.1 | Measurement pattern verification                                  |  |

|   |     | 4.1.1 Cluster-state simulation by recycling the state vector 69   |  |

|   |     | 4.1.2 A resizeable quantum computer simulator                     |  |

|   |     | 4.1.3 Performing measurement patterns                             |  |

|   |     | 4.1.4 Verification of the simulator                               |  |

|   |     | 4.1.5 Simulator input and output 79                               |  |

|   | 4.2 | Verification of the FPGA design 81                                |  |

|   |     | 4.2.1 One logical qubit                                           |  |

|   |     | 4.2.2 Multiple logical qubits                                     |  |

|   | 4.3 | Summary                                                           |  |

| 5 | Alg | orithmic overheads due to incomplete cluster states 87            |  |

|   | 5.1 | Photonic MBQC using incomplete cluster states 89                  |  |

|   |     | 5.1.1 Steps involved in implementing IMBQC 91                     |  |

|   |     | 5.1.2 The need for hardware emulation of IMBQC 94                 |  |

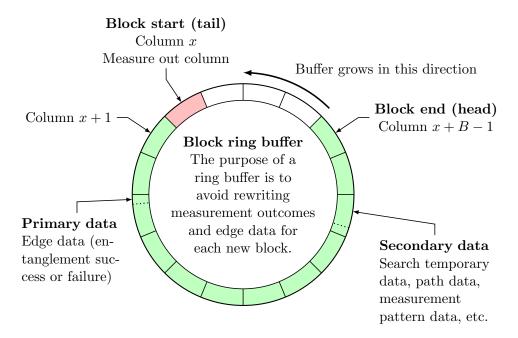

|   |     | 5.1.3 The ring-buffer model of control system implementation 96   |  |

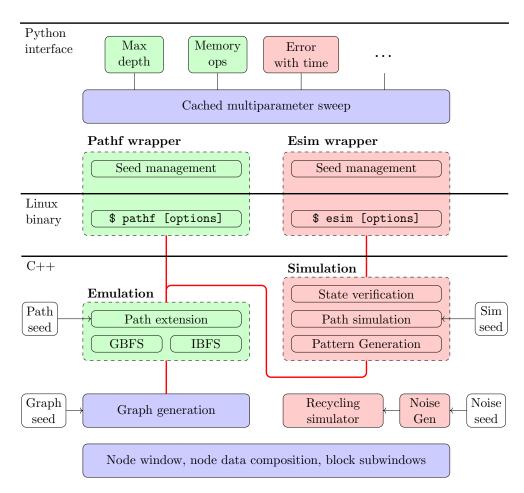

|   | 5.2 | Overall design of MBQCSIM                                         |  |

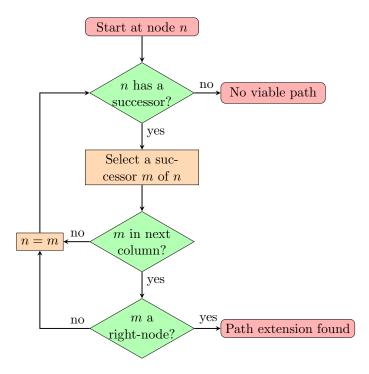

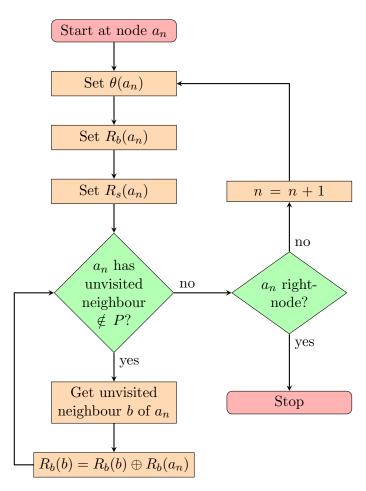

|   | 5.3 | Path extension using right-nodes                                  |  |

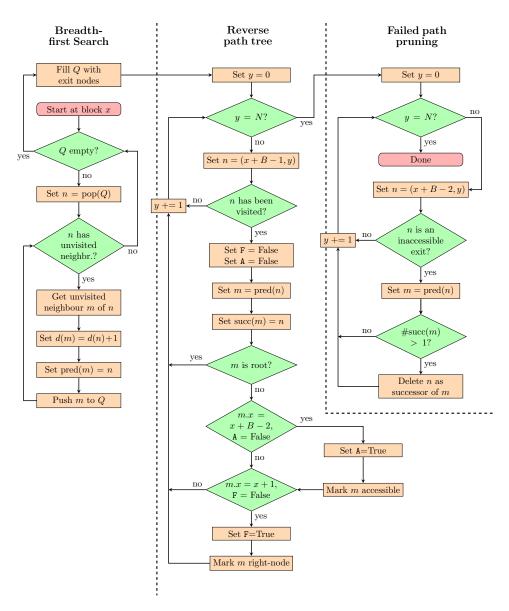

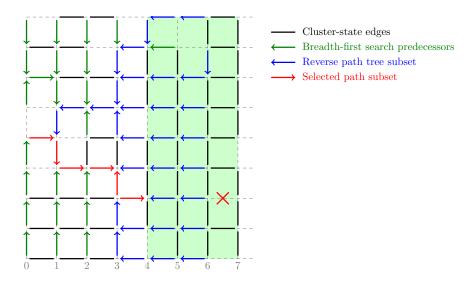

|   | 5.4 | Search algorithm implementation                                   |  |

|   |     | 5.4.1 Global breadth-first search 105                             |  |

|   |     | 5.4.2 Incremental breadth-first search 108                        |  |

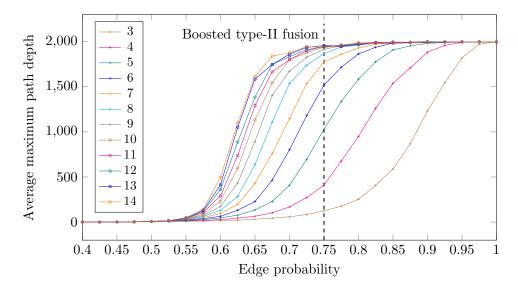

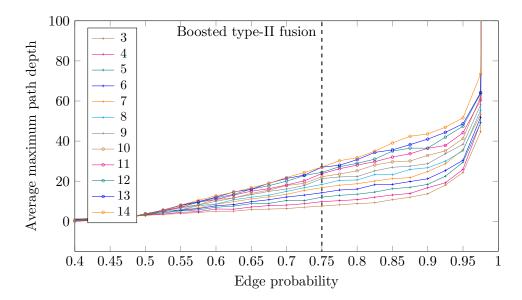

|   | 5.5 | Analysing algorithm performance using pathf                       |  |

|   |     | 5.5.1 Average maximum path depth 115                              |  |

|   |     | 5.5.2 Algorithmic overhead of pathfinding 116                     |  |

|   | 5.6 | Conclusion                                                        |  |

| 6 | Dyr | namic measurement pattern generation and analysis of              |  |

|   | ana | log voltage noise 123                                             |  |

|   | 6.1 | Effect of non-idealities in MBQC circuits                         |  |

|   | 6.2 | One-qubit measurement patterns in incomplete cluster states . 125 |  |

|   |     | 6.2.1 Cutting out qubits around the path 126                      |  |

|   |     | 6.2.2 One-qubit gate along an arbitrary path                      |  |

|    | 6.3                             | Dynamic measurement pattern generation in MBQCSIM                                                                                                                                                                                                                                           | 131                                                         |

|----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

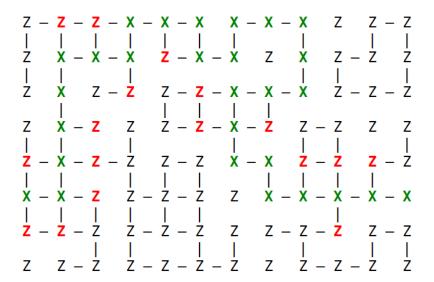

|    |                                 | 6.3.1 Restrictions imposed by implementation considerations                                                                                                                                                                                                                                 | 132                                                         |

|    |                                 | 6.3.2 Local measurement-pattern rules                                                                                                                                                                                                                                                       | 133                                                         |

|    | 6.4                             | Simulating generated measurement patterns                                                                                                                                                                                                                                                   | 138                                                         |

|    |                                 | 6.4.1 Adapting the cluster-state simulator to IMBQC                                                                                                                                                                                                                                         | 139                                                         |

|    |                                 | 6.4.2 Simulating analog voltage noise in modulators                                                                                                                                                                                                                                         | 141                                                         |

|    | 6.5                             | Verification of the simulation                                                                                                                                                                                                                                                              | 142                                                         |

|    |                                 | 6.5.1 Calculating left-nodes                                                                                                                                                                                                                                                                | 143                                                         |

|    |                                 | 6.5.2 Verification byproduct operators                                                                                                                                                                                                                                                      | 145                                                         |

|    | 6.6                             | Analysing fidelity as a function of time using esim                                                                                                                                                                                                                                         | 147                                                         |

|    | 6.7                             | Summary and conclusion                                                                                                                                                                                                                                                                      | 149                                                         |

| 7  | Con                             | clusions                                                                                                                                                                                                                                                                                    | 151                                                         |

|    | 7.1                             | The need for a non-mathematical approach to photonic MBQC                                                                                                                                                                                                                                   | 151                                                         |

|    | 7.2                             | Control system design is better than emulation                                                                                                                                                                                                                                              | 152                                                         |

|    | 7.3                             | What to investigate next?                                                                                                                                                                                                                                                                   | 153                                                         |

| Aj | ppen                            | dices                                                                                                                                                                                                                                                                                       | 155                                                         |

| A  | Mat                             | chematics of MBQC                                                                                                                                                                                                                                                                           | 157                                                         |

|    | A.1                             | CNOT measurement pattern                                                                                                                                                                                                                                                                    | 157                                                         |

|    | A.2                             | One-qubit gates in incomplete cluster states                                                                                                                                                                                                                                                | 161                                                         |

|    |                                 | A.2.1 Arbitrary X-rotation                                                                                                                                                                                                                                                                  |                                                             |

|    |                                 | 11.2.1 1115101011 1 1 1 0 0 0 0 1 0 1 1 1 1 1                                                                                                                                                                                                                                               | 163                                                         |

|    |                                 | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  |                                                             |

|    |                                 | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | $165 \\ 167$                                                |

|    |                                 | A.2.2 Arbitrary $Z$ -rotation                                                                                                                                                                                                                                                               | $165 \\ 167$                                                |

|    |                                 | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | $165 \\ 167$                                                |

| В  | Imp                             | A.2.2 Arbitrary $Z$ -rotation                                                                                                                                                                                                                                                               | 165<br>167<br>168                                           |

| В  | Imp<br>B.1                      | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | 165<br>167<br>168<br>170<br><b>173</b>                      |

| В  | -                               | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | 165<br>167<br>168<br>170<br><b>173</b><br>173<br>175        |

| В  | B.1                             | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | 165<br>167<br>168<br>170<br><b>173</b><br>173<br>175        |

| В  | B.1<br>B.2                      | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | 165<br>167<br>168<br>170<br><b>173</b><br>173<br>175<br>175 |

| В  | B.1<br>B.2<br>B.3               | A.2.2 Arbitrary Z-rotation  A.2.3 Arbitrary one-qubit gate  A.2.4 One-qubit gate along a linear cluster  A.2.5 One-qubit gate through a 2D cluster state  Clementation details of MBQCSIM  Modelling incomplete cluster states  Reproducibility and seeding in MBQCSIM  Generation of seeds | 165<br>167<br>168<br>170<br><b>173</b><br>173<br>175<br>175 |

| В  | B.1<br>B.2<br>B.3<br>B.4<br>B.5 | A.2.2 Arbitrary Z-rotation                                                                                                                                                                                                                                                                  | 165<br>167<br>168<br>170<br><b>173</b><br>173<br>175<br>175 |

## List of Figures

| 1.1  | The Bloch sphere                                               | 4 |

|------|----------------------------------------------------------------|---|

| 1.2  | Dual rail encoding of photonic qubits                          | 9 |

| 1.3  | Variable beamsplitter for realising $R_x$ rotations            | 0 |

| 2.1  | Cluster-state quantum computation                              | 7 |

| 2.2  | Arbitrary one-qubit-gate measurement pattern                   | 0 |

| 2.3  | CNOT gate measurement pattern                                  | 1 |

| 2.4  | Photonic MBQC system diagram                                   | 0 |

| 3.1  | Multi-qubit digital system diagram                             | 8 |

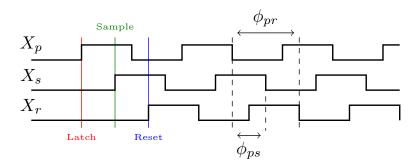

| 3.2  | Clocks in the FPGA design                                      | 0 |

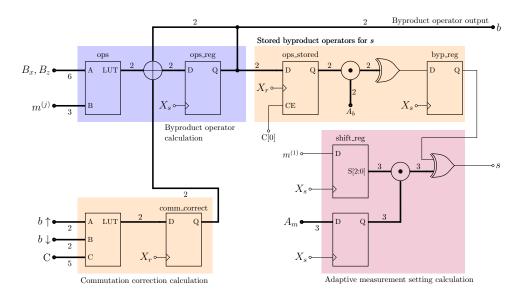

| 3.3  | Control system schematic diagram                               | 1 |

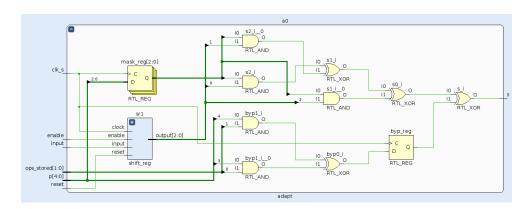

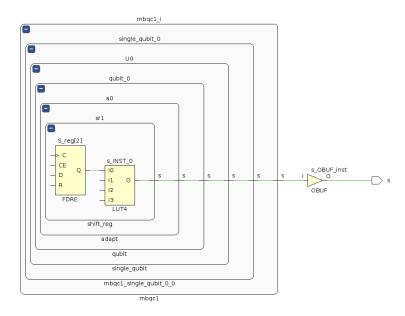

| 3.4  | Elaborated design of adapt entity                              | 3 |

| 3.5  | Critical timing path on the input side 60                      | 0 |

| 3.6  | Critical timing path on the output side 6                      | 1 |

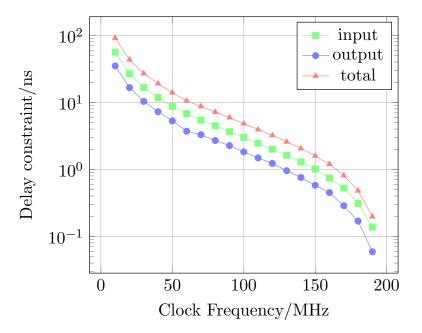

| 3.7  | I/O delays with frequency 6                                    | 2 |

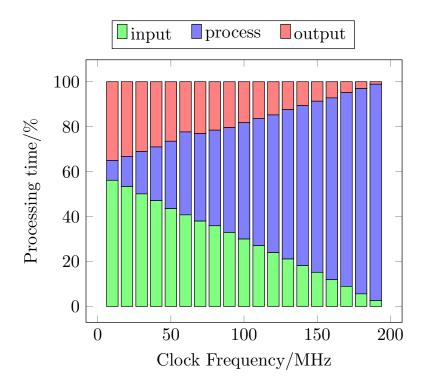

| 3.8  | Digital processing share of the clock cycle, with frequency 6. | 3 |

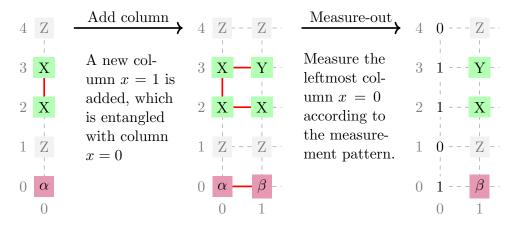

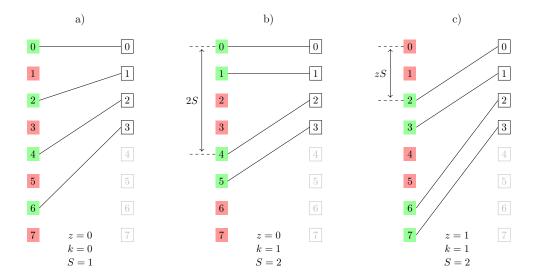

| 4.1  | Column-by-column simulation of measurement patterns            | 1 |

| 4.2  | Efficient scheme for measurement-and-removal of a qubit        |   |

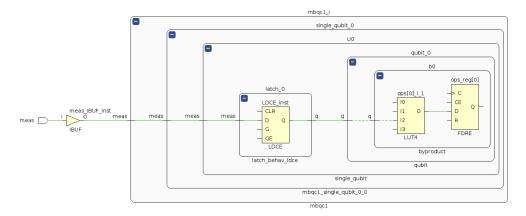

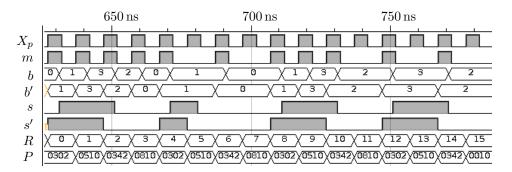

| 4.3  | Single-qubit control system functional verification            | 2 |

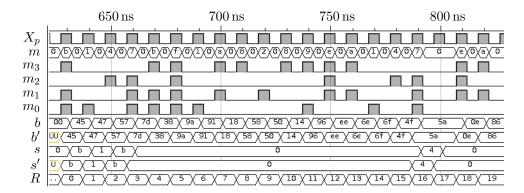

| 4.4  | Multi-qubit control system functional verification             | 4 |

| 5.1  | Block search implementation of photonic IMBQC 9                | 2 |

| 5.2  | Ring-buffer implementation model for IMBQC 9                   | 6 |

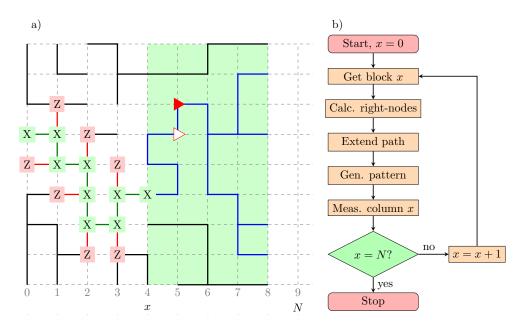

| 5.3  | Block diagram of MBQCSIM                                       | 9 |

| 5.4  | Algorithm for extending the path                               | 3 |

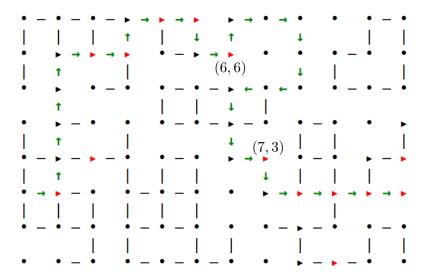

| 5.5  | Program output showing an example path with right-nodes 10-    | 4 |

| 5.6  | Global breadth-first search (GBFS) algorithm                   | 6 |

| 5.7  | Incremental breadth-first search (IBFS) algorithm              | 9 |

| 5.8  | Most common failure case in the IBFS algorithm                 | 3 |

| 5.9  | Average maximum path depth achieved using GBFS 11              | 5 |

| 5.10 | Average maximum path depth achieved using IBFS 11              | 7 |

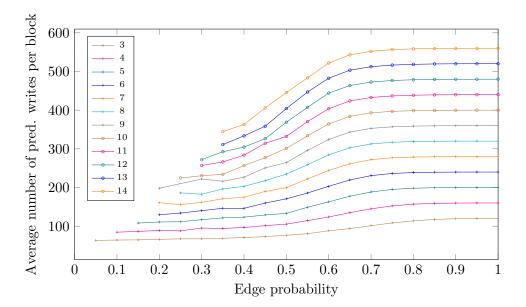

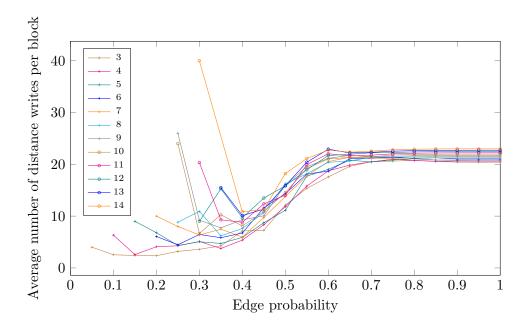

| 5.11 | Average predecessor writes when using GBFS                     | 8 |

| 5.12 | Average predecessor writes when using IBFS                     | 9 |

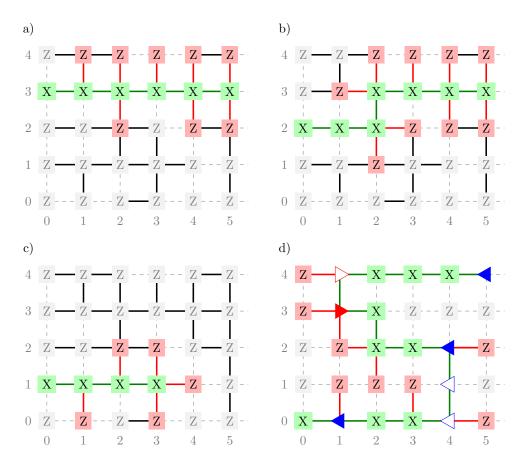

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Different types of cut-out qubits                                    |

|----------------------------------------|----------------------------------------------------------------------|

| 6.7                                    | Average fidelity as a function of analog voltage noise and time 148  |

| A.1                                    | Correlation centres in the CNOT measurement pattern 158              |

| C.1                                    | Cluster-state simulation and verification                            |

|                                        |                                                                      |

|                                        | ist of Tables  Modulator rotations required for MROC measurements.   |

| $\mathbf{L}_{2.1}$                     | ist of Tables  Modulator rotations required for MBQC measurements 41 |

|                                        |                                                                      |

| 2.1<br>3.1<br>3.2                      | Modulator rotations required for MBQC measurements                   |

| 2.1<br>3.1<br>3.2<br>3.3               | Modulator rotations required for MBQC measurements                   |

| 2.1<br>3.1<br>3.2                      | Modulator rotations required for MBQC measurements                   |

Secondary data required for GBFS and IBFS . . . . . . . . . . . . . . . . . 107

Secondary data required for local measurement-pattern rules . . . 134

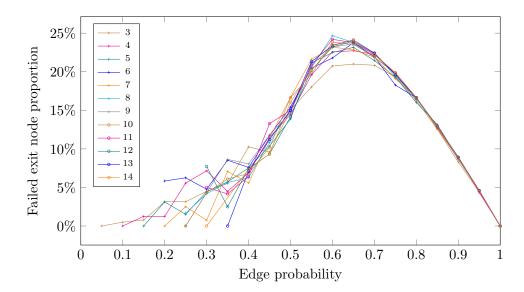

5.13 Average proportion of failed exit nodes using IBFS . . . . . . . . . 120

## List of Abbreviations

ADC Analog-to-digital converter.

**ASIC** Application-specific integrated circuit.

**BFS** Breadth-first search.

CSV Comma-separated variable.

**DAC** Digital-to-analog converter.

**DRAM** Dynamic random-access memory (for larger main memory).

**FIFO** First-in first-out (data structure).

FPGA Field-programmable gate array.

**GBFS** Global breadth-first search.

I/O Input/output.

**IBFS** Incremental breadth-first search.

IMBQC Incomplete-cluster-state measurement-based quantum computing.

KLM Knill-Laflamme-Milburn (scheme for photonic quantum computing).

LUT Look-up table.

MBQC Measurement-based quantum computing.

MMCM Mixed-mode clock manager.

**QSL** Quantum simulation library.

RAM Random-access memory.

${\bf SNSPD}$  Superconducting-nanowire single-photon detector.

**SOI** Silicon-on-insulator (platform for photonic integrated circuits).

**SRAM** Static random-access memory (for fast on-chip memory).

VHDL Very high-speed integrated circuit hardware description language.

## Chapter 1

## Introduction

With the invention and subsequent development of computers, we have become accustomed to a rate of technological improvement unequalled by any other human invention. In the last 75 years, electronic computers have risen from relatively simple arithmetic computing machines to become the basis for an infrastructure layer that touches nearly every aspect of our lives. The incredibly rapid rate of improvement is due to the ability to miniaturise computers, and scale up their computing power, at a rate that has been exponential with time – a fact predicted by Moore in 1965 [1]: from the year 1965 to nearly the present day, the number of transistors on a chip has doubled every 18 months. The layered complexity of computing services that now exist makes it nearly impossible to comprehend how the whole system works, from the services provided by cloud computing all the way down to the functioning of the individual transistors.

Quantum computing is a fundamentally different approach to problem solving using physical devices. Instead of using a classical logical building block such as the transistor, and then encoding every problem in digital terms, quantum computers seek to use the behaviour of quantum systems themselves to provide the solution to problems. An important motivation for this is that quantum systems are difficult for classical computers to simulate – a fact that Feynman noted in one of the earliest discussions of quantum computing [2] – meaning that quantum computers may be capable of solving problems that classical computers cannot. On the other hand, to make use of a quantum computer, it is necessary to turn a problem into something that is equivalent to the evolution of a quantum system. The difficulty of this task is the reason that

only relatively few quantum algorithms exist today, and it is an active area of research to find practical problems that quantum computers can solve [3].

Comparisons between quantum and classical computers are inevitable. So too are efforts to cast quantum computers in a framework similar to classical computing. For example, the qubit, or quantum bit, is named by analogy with the classical bit; and the quantum operations that a quantum computer performs are called quantum gates, by analogy with classical logic gates. There is also a desire to "front-run" the ideas that made classical computers successful, such as quantum software frameworks and cloud-based access to quantum computers [4]. However, there is an apparent contradiction between the state of quantum hardware, which is analogous to the state of early classical computing hardware, and the plethora of higher-level quantum tools, which, to an outside observer, give quantum computing the impression of being "done". A glance at the various competing quantum computing technologies, all with their own unique problems, shows that this is very far from the case. It has only recently been shown that current quantum computers can do something that a classical computer cannot [5], and the validity of this demonstration is disputed [6, 7]. Scalability, in a sense analogous to Moore's law, is not currently achieved by any quantum computing technology [8].

It is universally agreed that the ideal end-goal of quantum computing would be the construction of a large-scale, integrated, quantum computer, analogous to the high performance classical processors that exist today.

However, the incredible performance achieved by microprocessors is due to a very complicated mix of design choices – often trade-offs between non-ideal systems – which have been optimised by a long process of trial-and-error lasting decades. For example, the use of the memory hierarchy<sup>1</sup> [9] to hide the extremely long latency of main memory (computer RAM) is not an intrinsic feature of computing systems; it arises from the particular memory technology (DRAM) used as the basis for main memory. The (unlikely) discovery of a new type of memory that has the capacity of DRAM but the speed capabilities of SRAM (which is used for caches and other on-chip memory) would entail an entire redesign of modern microprocessors. Current microprocessor design

<sup>&</sup>lt;sup>1</sup>The memory hierarchy is the use of several different memory stages that optimise for high speed and low latency (e.g. cache levels) near the processor, and optimise for large capacity and error-correction far from the processor (e.g. main memory, and disk-based storage). The objective is to mimic a single quite-large and quite-fast memory technology, from the point of view of software.

#### 1.1. Why investigate control system design?

involves a very complicated balancing of different competing factors to achieve a design with improved performance compared to its predecessors [10]. None of these factors have anything to do with the high-level design of computers; for example, the use of the stored-program architecture, or the use of classical logic gates or transistors in its construction<sup>2</sup>.

It is possible that the success of quantum computing will similarly rest on a combination of specific device characteristics, and trade-offs in device design and construction. At a very high level, a prospective quantum computing system is considered to be made up of a physical system that represents the qubits, and an associated control system, made from digital and analog electronics and classical computing systems. In each of the computing quantum computing technologies, there are many different proposals<sup>3</sup> for how to realise large-scale quantum computers; those with thousands or millions of qubits, which are able to compete with classical computers at solving problems. In these proposals, the quantum aspects of the system are often discussed at length and worked out in detail. For example:

- How to make/manufacture the qubits?

- How to perform high-fidelity quantum operations (gates)?

- How to perform error correction, or build it in, so that the output from the qubits is reliable?

What is often missing from these proposals is similarly detailed information about how the classical control system will work. This thesis is focused entirely on this control system design, for the case of photonic quantum computers based on measurement-based quantum computation. The main purpose of this investigation is to establish whether the control systems constrain the design of photonic quantum computers.

#### 1.1 Why investigate control system design?

Analog and digital electronic circuits, and classical computing systems required to control quantum computers are often seen as an implementation

<sup>&</sup>lt;sup>2</sup>Nowadays, different transistor technologies are being explored as a method to increase processor performance. However, in the past, the primary technique enabling Moore's law was the gradual miniaturisation of transistors, not any fundamental changes in their design.

$<sup>^3</sup>$ Often called quantum computer architectures.

detail in quantum computing architecture design, to be worked out after the qubits have been fully understood. The purpose of this thesis is to promote the design of the control system as equally important, or more important, than the design of the qubits. The reason for this is threefold:

1. Classical control system design is starting to be seen as a real engineering problem in relation to scaling quantum computers. For example, in superconducting qubit systems (the current leading qubit technology by number of qubits), the control system is already a serious bottleneck.

Google's 54-qubit superconducting qubit processor uses 277 digital-to-analog converters (DACs) and two stages of cryogenic analog signal processing (one at 3 K and one at 10 K) to interface to their qubits [5]. Outside the cryostat, the pulse-generating hardware is mounted in four 6U-chassis (about 27 cm tall), each of which controls approximately 15 qubits.

The use of external rack-mounted electronics is infeasible for large-scale quantum computer, containing thousands of qubits. Although custom-made electronics can alleviate some of the problems relating to size and power consumption, there still remains a physical limit to the number of wires that can be routed into a cryostat [11], from both a mechanical and thermal point of view. As a result, there is a large amount of current research into the development of cryogenic electronics that can be integrated much closer to the superconducting qubits [12].

2. Analog and digital electronics, particularly classical computing systems, are very highly developed disciplines, where there is limited room for improvement on the state of the art.

This means that if the electronic control system imposes a limit on a quantum computing architecture, it may be very difficult to remove the imposed limitation by trying to improve the electronics. In the context of photonic quantum computing, the most important limitation relates to the timing characteristics of the control system.

On the other hand, quantum technologies are relatively new, and may be expected to see a great deal of development. It may therefore be much more important to prioritise the limitations arising from the control system over considerations relating purely to the quantum architecture of the system.

#### 1.1. Why investigate control system design?

3. Like classical computers, the success of large-scale quantum computers may come down to highly specific trade-offs between different parts of the qubit technologies and the associated control system. Analysis of these trade-offs requires the implementation details of the control system and quantum system to be known in detail; these systems must be designed in tandem, on an equal footing.

This thesis is about control system design for photonic quantum computers, where the physical system used as the qubit is a single photon. This subject has a particularly elaborate set of proposals for realising large-scale quantum computers [13–16], compared to other quantum computing platforms, mainly arising from the limited interaction between different photons. Despite the breadth of research into photonic quantum computing architectures, there is almost no research on the subject of control systems for photonic quantum computers. This may lead newcomers to the subject to believe that the control systems are not an important problem for photonic quantum computers.

This is partially true, because even simple building blocks required for the use of photonic qubits do not yet exist. For example, on-demand single-photon sources, with the high purity required for any implementation of (discrete-variable) photonic quantum computing, have been a subject of research for the last 20 years, but an ideal source does not yet exist [17]. Very good quality single-photon detectors are well established [18], but it is currently unknown how to integrate them into a prospective large-scale photonic quantum computer, and manage the cryogenic constraints they impose on the rest of the system [19].

However, many simple details of these control systems can be worked out now, based on available prospective architectures for photonic quantum computers, without needing all the prerequisite components to exist. Based on this analysis, it is clear that there may be substantial implementation problems relating to the design of electronic systems for photonic quantum computing. These problems essentially arise from the need for the speed of the electronics to compete with the speed of light. The characteristic timescale for photons moving through a photonic quantum computer is hundreds of picoseconds, which imposes a serious timing constraint on how fast the electronic control system must be able to operate. Based on point two listed above, it is very

important to understand what limitations control system electronics may impose, because these kind of limitations may render one architecture or another unviable.

Another feature of photonic quantum computing architectures is that they are relatively mathematically complicated. This may be a significant barrier to entry for electronic engineers, who would be able to provide the most assistance with the difficult control system implementation problems described above. The complexity is due to the use of measurement-based quantum computing (MBQC) as the basis of most architectures for photonic quantum computing. MBQC is used in photonic quantum computing because it allows photons to be used in a relatively short-lived manner, where each individual photon is produced and then measured (and destroyed) quickly. This is primarily necessary to mitigate the effect of propagation loss<sup>4</sup>. No single photon corresponds to a qubit in the quantum computer, but together, the photons interact in such a way as to simulate a set of qubits. By measuring the individual qubits according to particular rules, it is possible to realise quantum gates on these qubits. However, the rules are not as intuitive as the gate-based model of quantum computation, which makes photonic quantum computing more abstract than other quantum computing platforms (for example, superconducting qubits or trapped ions, where each qubit is easily mapped to a physical device).

Therefore, this thesis seeks to achieve two goals:

- Provide a practical description of MBQC. Throughout this thesis, the focus is on practical discussions of the implementation of MBQC algorithms in hardware and software, rather than mathematically rigorous analysis of measurement patterns, which are treated in great detail elsewhere [20, 21].

- Investigate constraints imposed by electronic control systems on photonic quantum computing architectures. We consider two simple models for photonic quantum computing based on MBQC, one involving ideal (fully-connected) cluster states, and one where the cluster state may contain missing edges. Chapters 2, 3 and 4 contain hardware design and verification for a control system for the first model. Chap-

$<sup>^4\</sup>mathrm{Where}$  a photon is absorbed by its transmitting medium: an optical fibre, or a waveguide.

#### 1.1. Why investigate control system design?

ters 5 and 6 contain the design of an emulation and simulation library, MBQCSIM, whose purpose is to analyse implementation constraints involved in the second model.

Even though it is not realistic, we consider the simple fully-connected model of photonic quantum computing first, because it leads to a control system which: does not involve complicated algorithms; does not involve difficult design trade-offs; and provides a clear indication of where control system constraints may appear in more complicated (and more realistic) models for photonic quantum computing. At the same time, a concrete hardware design targeting a high-performance field-programmable gate array (FPGA) provides a strong starting point for analysing design-imposed constraints, and offers an introductory system for others wishing to learn about control-system implementation for photonic quantum computing.

The simplest realistic model of photonic quantum computing, based on MBQC, uses an incomplete cluster state – one with missing edges<sup>5</sup>. These missing edges arise because there is no known deterministic mechanism for generating entanglement between photons, of the kind required for the cluster state which is the basis for MBQC. Instead, fusion gates (the generators of entanglement between photons) only succeed with some edge probability p (e.g. 50% [13] or 75% [15, 22]). Therefore, any realistic system of photonic quantum computing must be based on incomplete cluster states. For brevity, we refer to this model as IMBQC (for incomplete-cluster-state MBQC).

The use of an incomplete cluster state introduces many new algorithmic complications, such as the need to map measurement patterns onto random cluster states [14], and the need to implement this mapping in real time by searching for paths through the cluster state [23, 24]. This increased complexity makes it infeasible to design a control system for photonic quantum computing without first emulating the control system, in order to analyse design trade-offs between different algorithm choices and other implementation questions (such as the memory model for algorithm data storage). This kind of emulation is analogous to the techniques used in microprocessor architecture design, to evaluate whether one design choice or another will lead to a better overall system [10]. This emulation is not necessary for the model based on the fully-connected cluster state discussed above, because measurement pat-

<sup>&</sup>lt;sup>5</sup>A cluster state can be thought of as a graph, where the nodes correspond to photons, and the edges correspond to entanglement between photons.

terns are static in that case, and the algorithms which must be implemented reduce to simple fixed arithmetic operations.

Hardware emulation is able to provide concrete answers to questions relating to how a particular implementation will behave. Timing constraints may be obtained from the emulation by making reasonable assumptions on the hardware that may be used to realise the emulated system. However, this does not replace a full system design, which is the single valid method to establish what constraints the control system will really impose on the quantum computer.

A side-effect of the verification of the designs discussed in this thesis is the development of an MBQC simulator, which is capable of simulating measurement patterns on cluster states of arbitrary width, and height at most 14<sup>6</sup>. In addition to verification of measurement patterns and algorithms, this tool can be used as the basis for an analysis of how noise in the analog components in the control system affects the quantum output states from the system. This is discussed in detail in Chapter 6.3.

This thesis aims to advocate an "engineering-focused" approach for photonic quantum computing research: by completely isolating the control system specification from the quantum computing architecture, and approaching it entirely as an isolated electronic engineering problem, it may be brought within the scope of highly developed design methodologies for high-performance electronic systems [25, 26]. The current landscape of theoretical photonic quantum computing architectures provides almost unlimited material for this kind of investigation. It requires, as a prerequisite, that the control system is entirely extricated from the quantum architecture, and is presented in a form amenable to electronic circuit design. We have tried to achieve this separation for the models we discuss in this thesis. We also present some simple designs that satisfy these specifications. However, the true advantage of this approach is that others may now take the same decoupled specification (or modify it as they see fit), and improve upon and optimise the designs. Here, we take a simple minimalist approach, and focus on the digital aspects of the control system. However, it is the analog parts of the system (especially if the cryogenic requirement is incorporated) that offer the real design challenge, and will impose the toughest constraints on the overall system. The problems involved in this latter case are simply too complicated to address without first

<sup>&</sup>lt;sup>6</sup>On an ordinary laptop.

obtaining a rigorously specified behaviour for all parts of the control system, which is completely devoid of quantum mechanical considerations.

The remainder of this introduction is organised as follows. Section 1.2 contains a brief historical summary of the development of quantum computers, specifically highlighting relationships with the development of classical computers, and provides some comparison between the two different approaches to solving problems. A goal of this thesis is to point out similarities and differences between the implementation of quantum and classical computers, and draw on the development of classical computers to inform the development of control systems for quantum computing.

Section 1.3 provides a brief overview of the gate-based model for quantum computing, and other aspects of quantum information theory that are necessary for understanding this thesis. Section 1.4 contains an overview of the basics of (discrete-variable) photonic quantum computing, using single photons as qubits. It does not cover in detail the substantial information available in the literature on the various components required for the realisation of photonic quantum computers, including the underlying photonic platform for waveguides (e.g. silicon-on-insulator or lithium niobate); heralded [27] or multiplexed [28, 29] single-photon sources; single-photon detectors [30]; modulators [31]; and architectural components such as fusion gates [13], or the generation of cluster states [15]. This information is covered in great detail in the references provided, and much of the development of photonic devices is ongoing research which is outside the scope of this thesis. Instead, it provides a simple operational overview of the aspects of photonic quantum computing which are directly relevant for control system implementation. Finally, Section 1.5 contains a guide for the reader about how to approach this thesis.

# 1.2 Comparison of classical and quantum computers

Quantum computing is a relatively recent idea in the history of quantum physics. While quantum mechanics originated near the turn of the 1900s, the first ideas of quantum computing began to develop in the 1970s and 80s – about 20 years after quantum effects had been used for the invention of the transistor, and the subsequent development of classical computers. The idea of quantum computers arose as the intersection of three different strands of

#### thinking:

- Investigation of the boundaries of theoretical computational models such as the Turing machine.

- Research into the possibility of extremely low-energy (classical) computers, via reversible computation.

- The question whether physics can be simulated using computers.

There was a great deal of interest in the 1970s and 80s in the question whether are any fundamental energy limits inherent in the process of classical computation [32]. Such energy limits arise if a computational process is irreversible, because thermodynamics guarantees that energy will be lost in that process. Following the work of Landauer in 1961 on intrinsic energy dissipation in computers [33], it was widely thought that computation was not a reversible process. By designing a scheme of classical computation based on ideal billiard balls, Edward Fredkin showed that this was not true [34]. The key insight was the use of a reversible classical logic gate known as the Fredkin gate, or controlled-SWAP. Being somewhat outside academia, Fredkin did not publish his results, and Bennett (independently) showed in 1973 that reversible computation is possible [35], leading to the theoretical possibility of an extremely low energy computer. Feynman, with an interest in physical computation inspired by Fredkin, found that there are essentially no lower energy limits due to quantum mechanics either [36]. In doing so, he created a model of classical computation using reversible quantum mechanical elements; a type of quantum computer.

Although presented in the context of reversible computation, Feynman's true interest in the problem lay in the question whether the study of the computer simulation of physics could cast a new light on quantum theory [2]. Feynman argued that the simulation of physics could only be achieved by using computers based on the laws of quantum physics. The opposite point of view, held by Edward Fredkin due to his strongly-held belief in finite physical laws [34], was that digital electronic computers could exactly simulate physical phenomena. In his keynote address [2], Feynman laid out the important concept of the exponential scaling of the classical simulation of physics, and suggested the goal of finding a "universal" quantum computer, analogous

#### 1.2. Comparison of classical and quantum computers

to the universal Turing machine. This talk is seen by many as the birth of quantum computing.

The concept of the Turing machine has been a cornerstone of theoretical computer science since it was introduced in 1936 [37]. A Turing machine is a simple abstract type of (classical) computer which consists of an infinite memory, and a processor that can read and write to the tape according to special rules<sup>7</sup>. The importance of the Turing machine is that there exist universal Turing machines, which are able to simulate any other Turing machine. This is achieved by using the tape to store a "program" for the computer, in addition to its role as a scratch pad for data processing. The revolutionary concept of universality - via the stored-program concept - formed the abstract basis for the design of the EDVAC, one of the first large-scale general purpose computers. The design, laid out by von Neumann in his famous draft [39], described the physical realisation of a universal Turing machine, with the addition of practical details, such as the presence of higher level arithmetic processing operations, and a mechanism for fetching instructions<sup>8</sup>. Although the stored-program concept is often described as the crucial characteristics of post-World War II computers, the really revolutionary aspect of these computers was their universality [40].

The importance of the universal computer is cemented by the Church-Turing thesis, which states, approximately, that any real-world problem can be solved using a universal Turing machine. With the vast improvement in technology, particularly the increase in the size of memory, computers have approached the ideal universal Turing machine, implying that they can solve any problem at all – provided they are fast and large enough. The enormous array of applications of classical computers shows that this is certainly very nearly the case. However, the Church-Turing thesis has received continuous scrutiny to attempt to discover whether any computations lie outside the scope of traditional universal digital computers.

In 1985, David Deutsch reformulated the Church-Turing thesis to specify the simulation of finitely-realisable physical systems by finite computing systems [41]. A Turing machine does not satisfy this stronger variant of the Church-Turing thesis, because a finite physical system (being continuous) can-

<sup>&</sup>lt;sup>7</sup>Rules such as "move one step to the left" and "write zero to the tape" [38].

<sup>&</sup>lt;sup>8</sup>The origins of the design of the stored-program concept and the design of the all-purpose computer caused a great deal of controversy. See [40] for a much more complete account.

not be simulated using a discrete Turing machine based on classical physics. Within this framework, Deutsch introduced the concept of the universal quantum computer, a machine that contained a finite processing quantum system, and an infinite "tape" of quantum memory (like the traditional Turing machine), where quantum operations can be performed with unitary dynamics. For Deutsch, one of the critical aspects of the quantum computer was its "programmability"; it must be possible to reconfigure the same fixed computing system to realise different universal quantum computers, in contrast to Feynman's quantum computer. Deutsch and Jozsa introduced a simple algorithm to exploit quantum effects in this new type of computer [42]. Despite the contrived nature of the problem, the Deutsch-Jozsa algorithm is simple proof that a quantum computer can solve some problems "faster" than an ordinary classical computer<sup>9</sup>.

A much more important quantum algorithm, that kick-started widespread interest in quantum computing, is Shor's algorithm for factoring numbers into their prime factors [43]. The algorithm has undoubted significance, due to the possibility that it could undermine RSA, one of the most widely used cryptographic algorithms. Later, Grover introduced an algorithm for performing certain types of search tasks faster than ordinary computers [44]. Although the speed-up from using this algorithm is less impressive than Shor's algorithm, Grover's algorithm attracts interest due to its applicability to a more general type of problem.

The development of other quantum algorithms has turned out to be a very difficult problem; so much so that today, more than 25 years after their invention, Shor's algorithm and Grover's algorithm are still the highest profile quantum algorithms<sup>10</sup>. This shows that, in practice, the universality achieved by quantum computers is significantly less than that of classical computers (where any algorithm based on arithmetic and conditional logic is within the scope of implementation). It also leads to significant differences between classical and quantum computers. For example, a quantum analogue for the stored-program concept does not exist; the data in a quantum computer are quantum states, whereas the program (the specification of a quantum algo-

<sup>&</sup>lt;sup>9</sup>In this context, "faster" means "using fewer operations". Quantum computers are not well-enough developed yet to decide whether they can solve any problem faster than classical computers, in the sense of wall-clock time.

<sup>&</sup>lt;sup>10</sup>There are, however, many envisioned applications of variations of these algorithms to real-world problems [45].

#### 1.3. Gate-based quantum computing

rithm in terms of gates) remains in classical form<sup>11</sup>. As a result, quantum computers will remain fundamentally under the control of classical devices.

Despite this, many aspects of classical computing have been imported wholesale into the quantum ecosystem, under the assumption that they will eventually be useful. For example, many quantum programming languages<sup>12</sup> already exist, and big companies such as Microsoft and IBM have already rolled out large-scale software stacks for quantum computing infrastructure that does not yet exist [47, 48]. The disconnect between the apparent infrastructure in place surrounding quantum computing, and the actual readiness of real quantum computers has lead to concern about the level of "quantum hype" [49], which may negatively impact research into quantum computing. In order to meet the high expectations laid out for quantum computers, it is necessary that large-scale quantum computers are available at some point relatively soon. Even if large-scale quantum computers cannot be created immediately, it is certainly feasible to perform a detailed analysis of the type of analog and digital electronics necessary to control them. This information may be used to accelerate the process of large-scale quantum computer development, by ruling out as quickly as possible designs that will fail due to classical electronics-imposed constraints. This thesis is an attempt to offer some methodologies and tools for this analysis in the case of photonic quantum computing.

### 1.3 Gate-based quantum computing

The basic unit of quantum computation is the qubit, which is a two-state system, analogous to a bit, except complex linear combinations of the zero-state (denoted  $|0\rangle$ ) and the one-state (denoted  $|1\rangle$ ) are also valid states. The states  $|\psi\rangle$  of a qubit are elements of the complex vector space  $\mathbb{C}^2$  spanned by  $|0\rangle$  and  $|1\rangle$ , which are expressed as

$$|\psi\rangle = a|0\rangle + b|1\rangle = \begin{bmatrix} a \\ b \end{bmatrix}, \quad a, b \in \mathbb{C};$$

(1.1)

the coefficients a and b are called amplitudes.

<sup>&</sup>lt;sup>11</sup>It has been shown that there is no benefit to generalising the program to include quantum elements. Specifically, it is not possible to create a fixed quantum gate array that can implement universal quantum operations controlled by a finite quantum program, unless the quantum computer is allowed to be non-deterministic [46].

<sup>&</sup>lt;sup>12</sup>Most of which amount to gate listings.

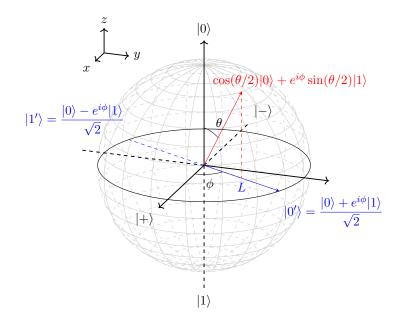

Figure 1.1: The state of a single qubit can be represented as a point on the Bloch Sphere. A measurement of a single qubit can be made along any straight line through the Bloch sphere. Measurements along lines L in the xy-plane of the Bloch sphere are particularly important in MBQC; these are parametrised by a single angle  $\phi$ . Computational basis measurements are made along the vertical line through  $|0\rangle$  and  $|1\rangle$ .

For any particular physical realisation, the qubit can only ever be observed (measured) in the basis states  $|0\rangle$  or  $|1\rangle$ , with probabilities given by the ratio of  $|a|^2$  to  $|b|^2$ . These states correspond to the natural measurable states of the physical system<sup>13</sup>. The absolute values of a and b have no independent physical meaning, so the condition  $|a|^2 + |b|^2 = 1$  is imposed so that the probabilities of each outcome are  $|a|^2$  and  $|b|^2$ . Likewise, only the difference between arguments of the complex numbers a and b has physical meaning, so it is possible to impose  $a \in \mathbb{R}$  without loss of generality. The argument of b is then the relative phase between  $|0\rangle$  and  $|1\rangle$ .

The states of a single qubit can be identified with points on the surface of a sphere, called the Bloch sphere, as shown in Figure 1.1. The mapping between the coefficients a and b and the angles  $\theta$  and  $\phi$  is given by the identity:

$<sup>^{13}</sup> For the purposes of this discussion, we have dual-rail-encoded photonic qubits in mind (see Section 1.4). As explained in that section, measurements correspond to clicks of photon detectors, which can only result in the <math display="inline">|0\rangle$  or  $|1\rangle$  state.

#### 1.3. Gate-based quantum computing

$$a|0\rangle + b|1\rangle = \cos(\theta/2)|0\rangle + e^{i\phi}\sin(\theta/2)|1\rangle.$$

The angle  $\phi$  in the equator of the Bloch sphere is the relative phase between  $|0\rangle$  and  $|1\rangle$ , and the angle  $\theta$  controls the probability of observing  $|0\rangle$  or  $|1\rangle$  upon measurement.

The states of two qubits can be expressed analogously to Equation (1.1) as

$$|\psi\rangle = a|00\rangle + b|01\rangle + c|10\rangle + d|11\rangle = \begin{bmatrix} a \\ b \\ c \\ d \end{bmatrix},$$

(1.2)

where  $a, b, c, d \in \mathbb{C}$ . The sum is taken over all four possible states that the two qubits could be observed in, which are the basis states of the tensor product  $\mathbb{C}^2 \times \mathbb{C}^2$ . As each new qubit is added, the number of amplitudes required to express the state doubles. This leads to the inability of classical computers to simulate quantum circuits containing large numbers of qubits. As with the single qubit case, the condition  $|a|^2 + |b|^2 + |c|^2 + |d|^2 = 1$  is imposed, and the probability of obtaining, for example,  $|01\rangle$ , is given by  $|b|^2$ . There is no equivalent of the Bloch sphere for graphically presenting the states of two qubits.

In computer simulations of quantum circuits, the state of the N-qubit system is stored in a vector of complex numbers (amplitudes), of size  $2^N$ :

$$|\psi\rangle = \begin{bmatrix} a_0 \\ a_1 \\ \vdots \\ a_{2^N-1} \end{bmatrix}. \tag{1.3}$$

The vector is normalised, so that the  $\sum |a_i|^2 = 1$ . We discuss the efficient computer simulation of MBQC measurement patterns at length in Chapter 4.

#### 1.3.1 Quantum gates

The state of a multi-qubit system can be changed by applying a quantum gate, which is the term used in quantum computing for a unitary transformation <sup>14</sup>.

<sup>&</sup>lt;sup>14</sup>The word gate is used to draw an analogy between the operations that can be performed on a qubit and the classical logic gates used in digital circuit design.

The gates U on a single qubit, called one-qubit gates, are  $2 \times 2$  unitary matrices U, which satisfy  $U^{\dagger}U = I$ . It can be shown that they correspond to a rotation of the points on the Bloch sphere about any axis, by any angle. The gates which perform rotations of the state about the x, y and z axes are denoted  $R_x(\alpha)$ ,  $R_y(\alpha)$  and  $R_z(\alpha)$ , where  $\alpha$  is the angle of rotation according to the right-hand rule. They are given by

$$R_x(\alpha) = \begin{bmatrix} \cos(\alpha/2) & -i\sin(\alpha/2) \\ -i\sin(\alpha/2) & \cos(\alpha/2) \end{bmatrix}, \tag{1.4}$$

$$R_y(\alpha) = \begin{bmatrix} \cos(\alpha/2) & -\sin(\alpha/2) \\ \sin(\alpha/2) & \cos(\alpha/2) \end{bmatrix}, \tag{1.5}$$

$$R_z(\alpha) = \begin{bmatrix} e^{-i\alpha/2} & 0\\ 0 & e^{i\alpha/2} \end{bmatrix}. \tag{1.6}$$

An arbitrary one-qubit rotation can be formed by applying  $R_x$ - and  $R_z$ rotations in sequence as  $R_x(\zeta)R_z(\eta)R_x(\xi)$  (applied from right to left). This

follows from the decomposition using Euler angles of an arbitrary rotation

into  $R_x$ - and  $R_z$ -rotations. Alternatively, it may be verified by direct matrix

multiplication of the gates in Equations (1.4), (1.5) and (1.6) [50].

The Pauli matrices are important special cases of the rotation matrices defined above, given by  $X = iR_x(\pi)$ ,  $Y = iR_y(\pi)$  and  $Z = iR_z(\pi)$  (the global phase i has no effect on the quantum gate that is performed). The Pauli operators are also important for representing measurement, as described in Section 1.3.2.

Two-qubit gates cannot be visualised as rotations; instead, they are expressed as  $4 \times 4$  matrices. An example of a two-qubit gate is the controlled-NOT (CNOT) gate, which is described by the following matrix:

$$CNOT = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}. \tag{1.7}$$

If the state given by Equation (1.2) is multiplied on the left by the matrix for the CNOT gate, then the amplitudes for the states  $|10\rangle$  and  $|11\rangle$  are reversed. The interpretation of this gate is that qubit one controls whether an X-gate

#### 1.3. Gate-based quantum computing

(which has the effect of a NOT gate) is applied to qubit zero<sup>15</sup>. Qubit one is therefore called the control qubit, and qubit zero is called the target <sup>16</sup>.

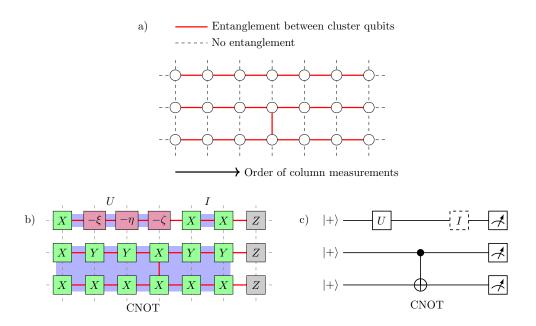

Analogously to the way that a NAND gate is universal for digital logic, the CNOT gate combined with the basic rotations  $R_x(\alpha)$ ,  $R_y(\alpha)$  and  $R_z(\alpha)$  are universal for quantum computation. To build up any complicated computation, all that is required is to apply the correct string of one- and two-qubit gates, one after the other, to a set of qubits. For example, in Figure 2.1c, an arbitrary one-qubit gate  $U = R_x(\zeta)R_z(\eta)R_x(\xi)$  is applied to the top qubit, and a CNOT gate is applied between the bottom two qubits.

In general, arbitrarily large multi-qubit gates may be applied to multiqubit systems. For example, a five-qubit gate would be described by a  $2^5 \times 2^5$ unitary matrix. Often, these larger gates are broken down into smaller gates, because it is expected that quantum hardware will not be able to perform arbitrary multi-qubit gates on more than two qubits.

#### 1.3.2 Measurement

When a qubit is measured, it always collapses to either the state  $|0\rangle$ , with probability  $|a|^2$ , or the state  $|1\rangle$ , with probability  $|b|^2$ . This is called a computational basis measurement.

However, it is possible to generalise the concept of measurement so that an "observation" causes the qubit to collapse into the state  $|0'\rangle$  or the state  $|1'\rangle$ , which are any two antipodal points on the Bloch sphere, joined by a line L. This generalised observation is made by using one-qubit gates to transform the line L to the line through  $|0\rangle$  and  $|1\rangle$ , and then making a computational basis measurement. For example, to measure along the line denoted L in Figure 1.1, it is necessary to apply a z-rotation  $R_z(-\phi + \pi/2)$  to align the state  $|0'\rangle$  with the positive y axis, followed by an x-rotation  $R_x(\pi/2)$  to obtain  $|0\rangle$ . It is important to realise that these measurements involve the application of a one-qubit gate before making a computational basis measurement.

<sup>&</sup>lt;sup>15</sup>In this thesis, we will follow a little-endian convention and describe the rightmost qubit as qubit zero (indexing from zero rather than one). For example, in an expression such as  $|0011\rangle$ , qubit zero is in the state  $|1\rangle$  and qubit three is in the state  $|0\rangle$

<sup>&</sup>lt;sup>16</sup>The (classical) CNOT gate originated in the study of reversible classical computers, as part of a wider investigation into the minimum energy required for classical computation [36]. Since all quantum gates are reversible (being unitary), reversible classical gates such as the CNOT naturally give rise to quantum gates as well.

It is possible to measure along any (arbitrary) line by applying an arbitrary one-qubit gate  $R_z(\alpha)R_x(\beta)R_z(\gamma)$  and then measuring in the computational basis. However, measurements that lie in the xy-plane are very important for MBQC, and form the basis for arbitrary one-qubit measurement patterns (see Sections 2.1.1 and 6.2.2).

Measurements with two outcomes can be characterised in terms of observables. These are Hermitian operators whose eigenvalues represent the outcomes from the measurement, and whose associated orthogonal eigenvectors are the states that result when each outcome is observed. The Pauli operators are all examples of observables. For example,

$$Z = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix} \tag{1.8}$$

is already diagonal. Its eigenvalues are +1 and -1, and the corresponding eigenvectors are  $|0\rangle$  and  $|1\rangle$ , showing that Z represents a computational basis measurement<sup>17</sup>. All the other Pauli operators (and all other measurements in this thesis) have outcomes  $\pm 1$ . We represent the two outcomes in the form  $(-1)^m$ , where  $m \in \{0,1\}$ . This allows the outcome to map more intuitively onto the state produced (m = 0 when the outcome is  $|0\rangle$  and m = 1 when the outcome is  $|1\rangle$ ). We use m exclusively throughout this thesis to refer to measurement outcomes.

The measurement represented by

$$X = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix} \tag{1.9}$$

is an xy-plane measurement along the x-axis (see Figure 1.1), because its eigenvectors are  $|0\rangle + |1\rangle$  and  $|0\rangle - |1\rangle$ , which<sup>18</sup> are denoted  $|+\rangle$  and  $|-\rangle$  respectively.

The observable representing a general xy-plane measurement at an angle  $\phi$  to the x-axis is given by  $R_z(\phi)XR_z(-\phi)$ , because its eigenvectors lie along the blue line L in Figure 1.1 (this is because the  $R_z$  rotations rotate this line to the x-axis, which are the eigenvectors of X).

$<sup>^{17}\</sup>mathrm{As}$  a result, we use the terms Z-measurement and computational basis measurement interchangeably throughout this thesis.

$<sup>^{18} \</sup>text{We}$  will omit normalisation in expressions such as these (here, division by  $\sqrt{2})$  to simplify the expression.

#### 1.4. Photonic qubits

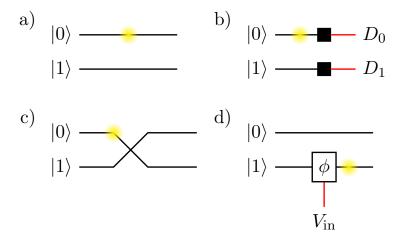

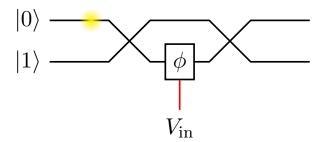

Figure 1.2: a) A single photon in two waveguides can be used as a qubit. If the photon is in the top waveguide, then the qubit is in the  $|0\rangle$  state, whereas if it is in the bottom waveguide, the qubit is in the  $|1\rangle$  state. b) Computational basis measurements can be performed by placing a single-photon detector at the end of the waveguides. Basic one-qubit operations can be realised using linear optical elements such as c) beamsplitters and d) modulators. Complex operations can be realised by placing the elements one after the other.

#### 1.4 Photonic qubits

In (discrete-variable) photonic quantum computing, a qubit is realised using a single photon. In the dual-rail encoding, a single photon passes through one waveguide or another depending on whether the qubit it represents is in the state  $|0\rangle$  or  $|1\rangle$ , as shown in Figure 1.2. A qubit encoded like this can be measured in the computational basis by placing a single-photon detector at the end of the pair of waveguides. It is important to realise that this process destroys the qubit (by absorbing the photon), unlike a matter-based qubit which can be re-used after measurement.

The advantage of photonic quantum computing is that passive linear optical elements (modulators and beamsplitters) can be used to realise an arbitrary one-qubit gate, as follows. First, a modulator in the  $|1\rangle$  waveguide realises an arbitrary  $R_z$ -rotation, shown in Figure 1.2d. Then, the variable beamsplitter shown in Figure 1.3 realises an arbitrary  $R_z$ -rotation. Finally, a second modulator in the  $|1\rangle$  waveguide realises another arbitrary  $R_z$ -rotation, which completes the decomposition  $R_z(\alpha)R_z(\beta)R_z(\gamma)$ .

We consider a simple model for modulators in this thesis, where the phase

Figure 1.3: A variable beamsplitter, which realises an  $R_x(\phi)$  rotation, is formed by placing two fixed beamsplitters on either side of a modulator.

$\phi$  realised by the modulator is a linear function of the applied voltage  $V_{\rm in}$ :  $\phi = \pi V_{\rm in}/V_{\pi}$ . The magnitude of the voltage required to drive the modulator is defined by  $V_{\pi}$ : the voltage required to realise a  $R_z(\pi)$ -rotation. There are other important electronic attributes of modulators (for example, small-signal characteristics [51]) which we do not consider here, because we are primarily interested in the digital aspects of electronic control systems for photonic MBQC. A good review of high-speed modulator design for lithium-niobate platforms is [31].

Similarly, we consider single-photon detectors to be devices that output a voltage pulse, compatible with digital logic levels (e.g.  $\sim 1.5\,\mathrm{V}$ ), when a photon arrives. We have high-speed detectors such as superconducting-nanowire single-photon detectors (SNSPDs) in mind [30]; however, we ignore the cryogenic amplification of the detector signal, and how to design reset circuitry [52]. These investigations are outside the scope of the thesis, which contains primarily digital control system analysis.

In contrast to many other physical realisations of quantum computing, including superconducting qubits and trapped ions, that have a natural way to implement two-qubit operations [53], there is no way to implement a deterministic two-qubit photonic entangling gate using passive linear optical elements [54]. However, it was shown that one can implement an artificial nonlinear gate that works probabilistically by using additional auxiliary photons and photodetection [55], giving rise to the Knill-Laflamme-Milburn (KLM) scheme for photonic quantum computing. This approach is not robust in the face of photon loss; as a result, modern approaches to photonic quantum computing are based on photonic cluster states [56].

We describe a simple model for photonic quantum computing using a fully-

#### 1.5. Reading this thesis

connected cluster state in Section 2.2. We treat the generation of a photonic cluster state as a black box, and consider the system inputs and outputs to be modulator voltages and detector output pulses, respectively. In Chapter 5, where we consider incomplete cluster states, the success/failure signal for each edge in the cluster state is also assumed to be an input to the system. These models are described fully in the main body of the thesis.

#### 1.5 Reading this thesis

This thesis is partially intended to make the subject of control system design for photonic MBQC easier to understand. In order to help achieve this goal, important information throughout the text is highlighted in boxes, shown below.

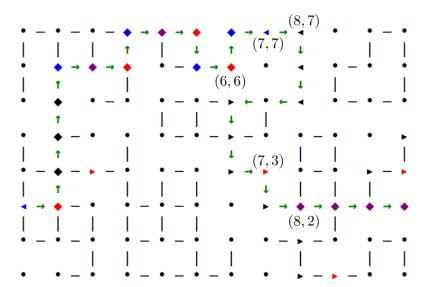

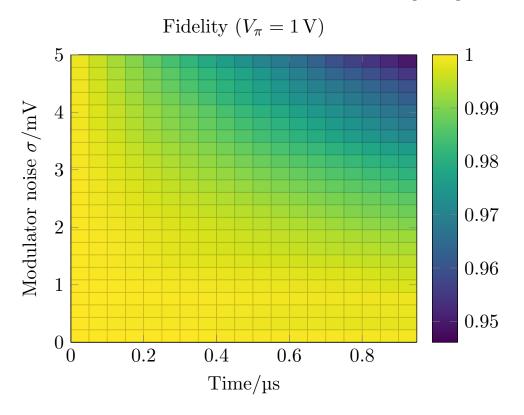

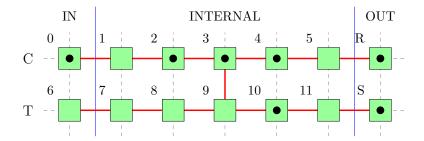

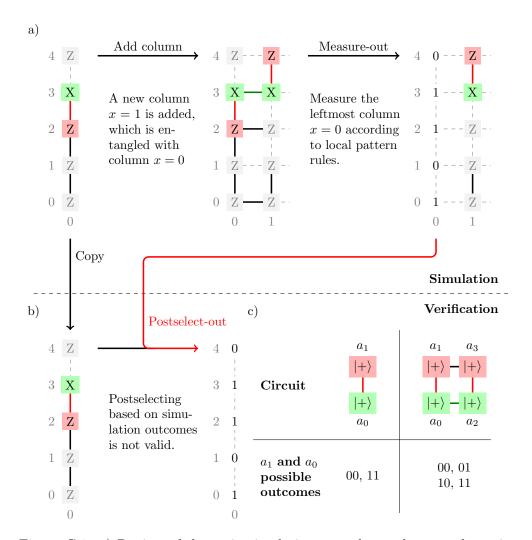

#### Key points