# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Wach, Filip M

Title:

Electrical and Thermal Characterisation of GaN-based Devices for RF and Power Electronics

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

Take down policy Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

· Your contact details

Bibliographic details for the item, including a URL

An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Electrical and Thermal Characterisation of GaN-based Devices for RF and Power Electronics

By

FILIP WACH

School of Physics UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements of the degree of DOCTOR OF PHILOSOPHY in the School of Physics.

$A {\tt PRIL} \ 2022$

Word count: 44 400

## ABSTRACT

he rapid increase in global energy demand in the period of significant environmental concern requires us to look beyond standard Si based electronics and towards the wide bandgap semiconductors. AlGaN/GaN based heterostructures are capable of fast switching, larger breakdown voltages and higher power densities, offering a viable alternative to conventional Si solutions. GaN-based devices are predicted to dominate key automotive, consumer and industrial markets in the next decade however, to achieve widespread commercial application a number challenges relating to electrical and thermal reliability have to be overcome.

In this thesis, the relationship between vertical charge transport processes in GaN buffers is explored. By combining electrical characterisation of GaN-on-Si power HEMTs with TCAD simulations the dominant vertical charge transport processes are identifies as 3D variable range hopping most likely in the defect band in the carbon-doped GaN buffer and 1D hopping along the dislocation in the unintentionally doped GaN channel. The effect of these charge transport process on dynamic On-resistance ( $R_{ON}$ ) is studied by examining the temperature and field dependence of dynamic  $R_{ON}$  in the transfer length method (TLM) structures and in lateral Schottky barrier diodes grown on the identical epitaxy. The results indicate that the variation in dynamic  $R_{ON}$  is dominated by charge transport processes in GaN layers and not by trapping.

In addition, comprehensive electrical and thermal characterisation of early generation "bufferfree" GaN-on-SiC RF HEMTs (where thin GaN channel is grown directly on AlN nucleation layer) is combined with computational simulations to determine device design for optimised electrical and thermal performance. Removal of thick doped buffer eliminates the issue of trapping in this layer and brings the high thermal conductivity substrate closer to the source of Joule heating during device operation. However, reduction in GaN thickness results in significant decrease in thermal conductivity of this layer offsetting some of the benefits of "buffer-free" design. The effects of GaN thickness and thermal interface between the GaN channel and SiC substrate are discussed in detail. Moreover, the position of Fermi level in the AlN nucleation layer becomes a critical parameter for carrier confinement, with thicker GaN layers showing increase in short channel effects.

Finally, electrical and thermal characterisation of proof-of-concept GaN HEMTs bonded onto SiC substrate using novel low-temperature technique is demonstrated. The bonding process utilises thin water layers trapped between the AlGaN/GaN heterostructure and the bond substrate to create a covalent bond. The devices are characterised before and after bonding showing no evidence of compromised electrical performance, while exhibiting all the major benefits associated with new high thermal conductivity substrate. This bonding technique could provide a promising solution to hetero-integration of III-V micro-electronic devices.

### **DEDICATION AND ACKNOWLEDGEMENTS**

would like to take this opportunity to thank all the people who have supported me throughout my PhD. First and foremost, I would like to thank my wife Katie for her continuous support especially during the highs and lows of the past four years. The experience of completing a PhD can be quite stressful, let alone the coinciding global pandemic right in the middle of my studies. I would certainly not have made it alone. Thank you so much for your patience. I would also like to thank a very special community of friends and family in Nailsea, Bristol, West Sussex and Poland for all the great times we have had together.

In addition, I would like to convey my gratitude to Prof. Martin Kuball and Prof. Michael Uren for their supervision and guidance, which were of tremendous value for my academic and personal growth. I must also thank Dr. James Pomeroy for his time and patience particularly in the area of thermal measurements, as well as Dr. Matt Smith for his advice and encouragement especially in the final months of my PhD.

I would like to thank all my colleagues and friends at the CDTR in Bristol, who made my time there so much more interesting and enjoyable, even when faced with most tedious of tasks. Finally, I would also acknowledge the financial support of EPSRC and to thank all our collaborators for providing me with very some very interesting samples and devices.

Overall, there are too many people to acknowledge here by name, but I wholeheartedly hope I made my gratitude clear to all.

# **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

SIGNED: ...... DATE: .....

# TABLE OF CONTENTS

|    |       |         |                                    | Page |

|----|-------|---------|------------------------------------|------|

| Li | st of | Tables  | 3                                  | xi   |

| Li | st of | Figure  | es                                 | xiii |

| 1  | Intr  | oducti  | ion                                | 1    |

|    | 1.1   | Thesis  | s outline                          | . 6  |

| 2  | The   | oretica | al Background                      | 9    |

|    | 2.1   | Mater   | rial Properties                    | . 9  |

|    |       | 2.1.1   | Crystal Structure                  | . 9  |

|    |       | 2.1.2   | Polarization Effects               | . 12 |

|    |       | 2.1.3   | Phonon Dispersion                  | . 15 |

|    |       | 2.1.4   | Heat Transport in Semiconductors   | . 17 |

|    |       | 2.1.5   | Thermal Conductivity of GaN        | . 19 |

|    | 2.2   | AlGaN   | N/GaN HEMT Structure               | . 21 |

|    |       | 2.2.1   | Substrate                          | . 22 |

|    |       | 2.2.2   | Nucleation and Strain Relief Layer | . 23 |

|    |       | 2.2.3   | Buffer Layer and Carbon Doping     | . 24 |

|    |       | 2.2.4   | AlGaN Barrier and Capping          | . 27 |

|    |       | 2.2.5   | Ohmic and Schottky Contacts        | . 29 |

|    |       | 2.2.6   | Passivation                        | . 32 |

|    | 2.3   | GaN I   | HEMTs and Diodes Operation         | . 33 |

|    |       | 2.3.1   | DC Performance                     | . 33 |

|    |       | 2.3.2   | GaN HEMT as Power Switch           | . 35 |

|    |       | 2.3.3   | GaN HEMT as RF Switch              | . 38 |

|    |       | 2.3.4   | Schottky Barrier Diode Operation   | . 38 |

|    | 2.4   | GaN I   | Device Reliability                 | . 40 |

|    |       | 2.4.1   | Trapping in GaN                    | . 41 |

|    |       | 2.4.2   | Dislocations in GaN Buffer         | . 43 |

|    |       | 2.4.3   | Short Channel Effects              | . 43 |

|   |                                                                         | 2.4.4   | Surface Trapping                                             | 44  |  |  |  |

|---|-------------------------------------------------------------------------|---------|--------------------------------------------------------------|-----|--|--|--|

|   |                                                                         | 2.4.5   | Buffer Trapping                                              | 46  |  |  |  |

|   |                                                                         | 2.4.6   | Device Breakdown                                             | 47  |  |  |  |

|   |                                                                         | 2.4.7   | Self-Heating and Reliability Implications                    | 49  |  |  |  |

| 3 | Exp                                                                     | erimei  | ntal Techniques and Methods                                  | 53  |  |  |  |

|   | 3.1                                                                     | Exper   | imental Equipment and Capabilities                           | 53  |  |  |  |

|   |                                                                         | 3.1.1   | Measurement Environment                                      | 53  |  |  |  |

|   |                                                                         | 3.1.2   | Electrical Connections and Cabeling                          | 54  |  |  |  |

|   |                                                                         | 3.1.3   | Probe Stations for Electrical Measurements                   | 55  |  |  |  |

|   |                                                                         | 3.1.4   | Probe Station for Thermal Measurements                       | 57  |  |  |  |

|   |                                                                         | 3.1.5   | Measurement Instrumentation                                  | 58  |  |  |  |

|   | 3.2                                                                     | Electr  | ical Characterisation Techniques                             | 62  |  |  |  |

|   |                                                                         | 3.2.1   | DC & Pulsed Current-Voltage Measurements                     | 62  |  |  |  |

|   |                                                                         | 3.2.2   | Substrate Ramp Sweeps                                        |     |  |  |  |

|   |                                                                         | 3.2.3   | Current Transient Measurements                               | 66  |  |  |  |

|   | 3.3                                                                     | Rama    | n Spectroscopy for Temperature Measurements                  | 71  |  |  |  |

|   |                                                                         | 3.3.1   | Raman Scattering                                             | 71  |  |  |  |

|   |                                                                         | 3.3.2   | Raman Thermography                                           | 73  |  |  |  |

|   |                                                                         | 3.3.3   | Mechanical Strain Correction                                 | 76  |  |  |  |

|   | 3.4                                                                     | Comp    | utational Simulations                                        | 79  |  |  |  |

|   |                                                                         | 3.4.1   | Electrical 2D TCAD Simulations                               | 79  |  |  |  |

|   |                                                                         | 3.4.2   | Thermal 3D FEA Simulations                                   | 81  |  |  |  |

| 4 | Low-Field Vertical Charge Transport Processes in GaN Channel and Buffer |         |                                                              |     |  |  |  |

|   | Lay                                                                     | ers     |                                                              | 83  |  |  |  |

|   | 4.1                                                                     | Introd  | uction                                                       | 84  |  |  |  |

|   | 4.2                                                                     | Exper   | imental Details                                              | 85  |  |  |  |

|   |                                                                         | 4.2.1   | Sample Description                                           | 85  |  |  |  |

|   |                                                                         | 4.2.2   | Experimental Method                                          | 86  |  |  |  |

|   | 4.3                                                                     | Result  | $\bar{\mathbf{S}}$                                           | 87  |  |  |  |

|   | 4.4                                                                     | Discus  | ssion                                                        | 89  |  |  |  |

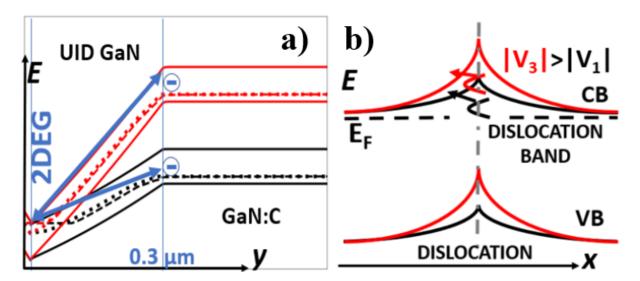

|   | 4.5                                                                     | Simul   | ations                                                       | 97  |  |  |  |

|   | 4.6                                                                     | Conclu  | isions                                                       | 99  |  |  |  |

| 5 | The                                                                     | Effect  | ts of Charge Transport Processes on Dynamic On-Resistance in |     |  |  |  |

|   | GaN                                                                     | l-on-Si | Schottky Barrier Diodes                                      | 103 |  |  |  |

|   | 5.1                                                                     | Introd  | uction                                                       | 104 |  |  |  |

|   | 5.2                                                                     | Exper   | imental Method                                               | 104 |  |  |  |

|   |     | 5.2.1    | Sample Description                                             | 104 |

|---|-----|----------|----------------------------------------------------------------|-----|

|   |     | 5.2.2    | Experimental Method                                            | 106 |

|   | 5.3 | Result   | ${f s}$                                                        | 108 |

|   |     | 5.3.1    | TLM Structures                                                 | 108 |

|   |     | 5.3.2    | Schottky Barrier Diodes                                        | 112 |

|   | 5.4 | Discus   | $\operatorname{sion}$                                          | 116 |

|   |     | 5.4.1    | TLM Structures and Vertical Transport Mechanisms               | 116 |

|   |     | 5.4.2    | Schottky Barrier Diodes - Computational Simulations            | 117 |

|   |     | 5.4.3    | Schottky Barrier Diodes - Trapping Phase                       | 118 |

|   |     | 5.4.4    | Schottky Barrier Diodes - Recovery Phase                       | 120 |

|   | 5.5 | Conclu   | isions                                                         | 124 |

| 6 | Ele | ctrical  | and Thermal Characterisation of "Buffer-Free" GaN-on-SiC HEMTs | 125 |

|   | 6.1 | Introd   | uction                                                         | 126 |

|   | 6.2 | Experi   | imental Details                                                | 127 |

|   | 6.3 | Result   | s                                                              | 130 |

|   |     | 6.3.1    | Electrical Characterisation                                    | 130 |

|   |     | 6.3.2    | Thermal Characterisation                                       | 136 |

|   | 6.4 | Discus   | $\operatorname{ssion}$                                         | 138 |

|   |     | 6.4.1    | Electrical Measurements                                        | 138 |

|   |     | 6.4.2    | Electrical Simulations                                         | 140 |

|   |     | 6.4.3    | Thermal Analysis of Conventional GaN-on-SiC HEMTs              | 145 |

|   |     | 6.4.4    | Thermal Analysis of "Buffer-Free" GaN HEMTs                    | 146 |

|   | 6.5 | Conclu   | isions                                                         | 152 |

| 7 | Ele | ctrical  | and Thermal Characterisation of GaN-on-SiC HEMTs Covanlently   |     |

|   | Bon | nded by  | Adaptive Low-temperature Method                                | 155 |

|   | 7.1 | Introd   | uction                                                         | 156 |

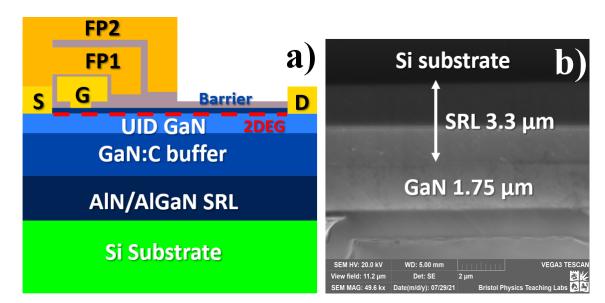

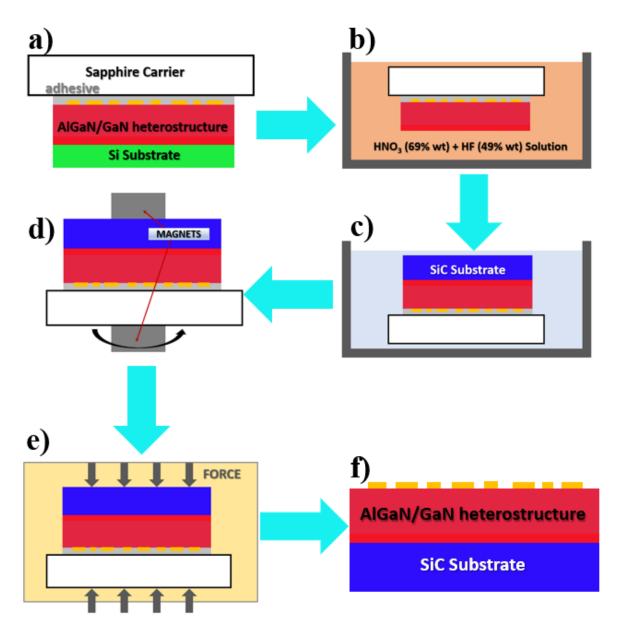

|   | 7.2 | Experi   | imental Details                                                | 157 |

|   |     | 7.2.1    | Sample Description                                             | 157 |

|   |     | 7.2.2    | Bonding Technique                                              | 158 |

|   |     | 7.2.3    | Experimental Details                                           | 160 |

|   | 7.3 | Result   | s                                                              | 162 |

|   | 7.4 | Discus   | $\operatorname{sion}$                                          | 169 |

|   | 7.5 | Conclu   | isions                                                         | 175 |

| 8 | Sun | nmary    | and Conclusions                                                | 177 |

| A | Apr | oendix . | A                                                              | 183 |

|   |     |          | ations                                                         |     |

| A.2    | Presentations | 183 |

|--------|---------------|-----|

| Biblio | graphy        | 185 |

# **LIST OF TABLES**

| Тав          | LE                                                  | Pa | ge |

|--------------|-----------------------------------------------------|----|----|

| 1.1          | Figure of Merit Relative to Si                      |    | 3  |

| 2.1          | Substrate Material For GaN Growth                   | •  | 22 |

| 4.1          | Hopping Conductivity Models                         | •  | 95 |

|              | Thermal Conductivity Values for Ansys Simulations I |    |    |

| $7.1 \\ 7.2$ | GaN Phonon Temperature Dependence Coefficients      |    |    |

# **LIST OF FIGURES**

| FIG  | URE                                                                                           | age      |

|------|-----------------------------------------------------------------------------------------------|----------|

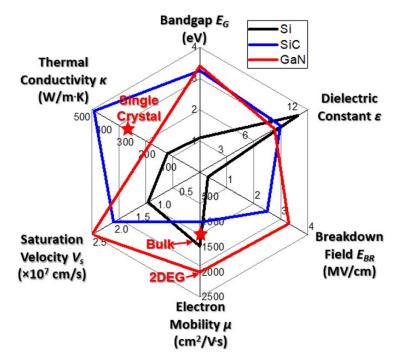

| 1.1  | Spider diagram Si, SiC and GaN                                                                | <b>2</b> |

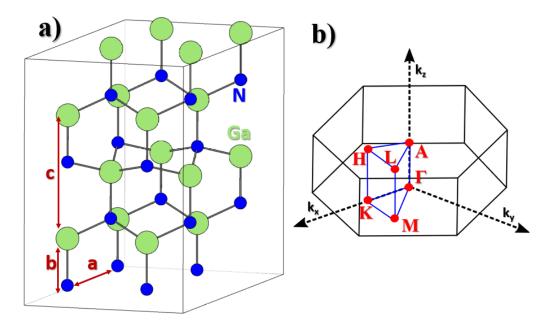

| 2.1  | Wurtzite GaN structure and first Brillouin zone.                                              | 10       |

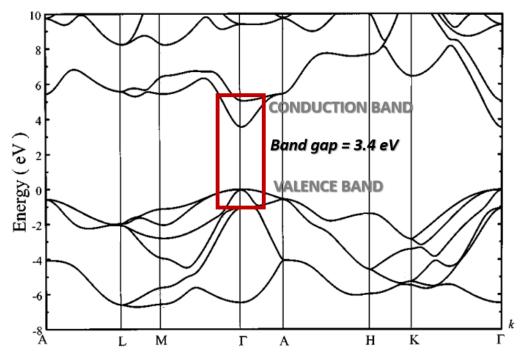

| 2.2  | GaN electronic band diagram in the first Brillouin zone                                       | 11       |

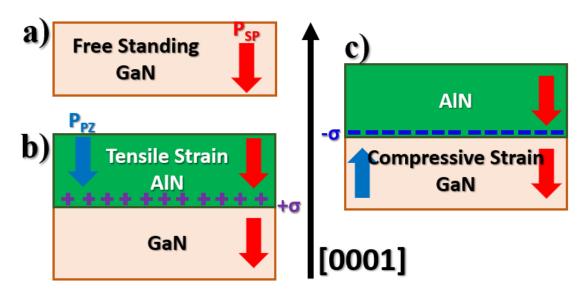

| 2.3  | Spontaneous and piezoelectric polarization in AlN/GaN heterostructures                        | 13       |

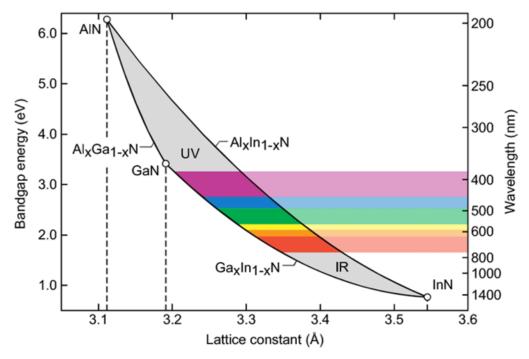

| 2.4  | Lattice constant and band gap relationship for GaN, AlN and InN material systems.             | 14       |

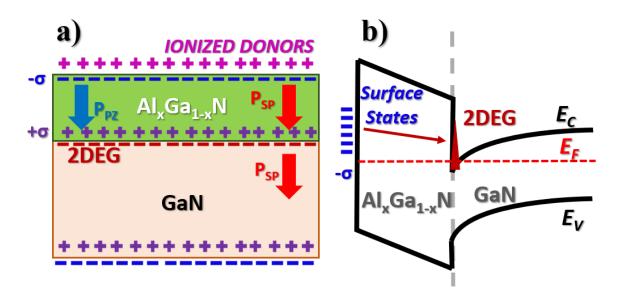

| 2.5  | Polarization and band diagram for an AlGaN/GaN heterostructure                                | 15       |

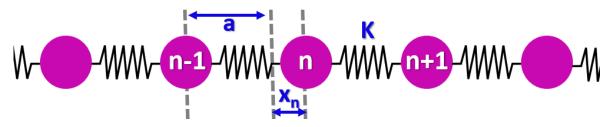

| 2.6  | 1D atomic balls and springs diagram.                                                          | 15       |

| 2.7  | Phonon dispersion for a diatomic 1D chain of atoms and full dispersion diagram for            |          |

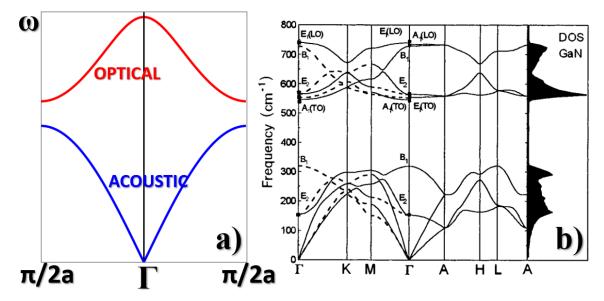

|      | wurtzite GaN                                                                                  | 16       |

| 2.8  | Normal and Umklapp phohon scattering processes                                                | 18       |

| 2.9  | GaN thermal conductivity dependence of temperature, dislocation density and layer             |          |

|      | thickness                                                                                     | 20       |

| 2.10 | Typical AlGaN/GaN-on-Si HEMT epitaxial stack.                                                 | 21       |

| 2.11 | Three main types of strain relief layers.                                                     | 23       |

| 2.12 | Schematic representation of edge and screw dislocations. $\ldots \ldots \ldots \ldots \ldots$ | 24       |

| 2.13 | Position of some of the common extrinsic dopants in the GaN bandgap                           | 25       |

| 2.14 | Formation energies for C incorporation into GaN                                               | 26       |

| 2.15 | Free hole concentration and resistivity relation                                              | 28       |

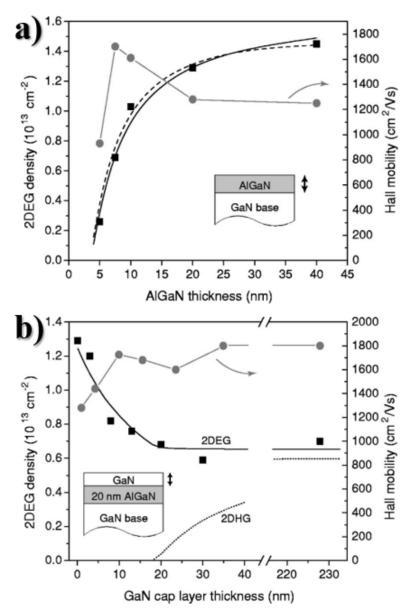

| 2.16 | The effects of AlGaN and GaN cap thickness on 2DEG concentration                              | 29       |

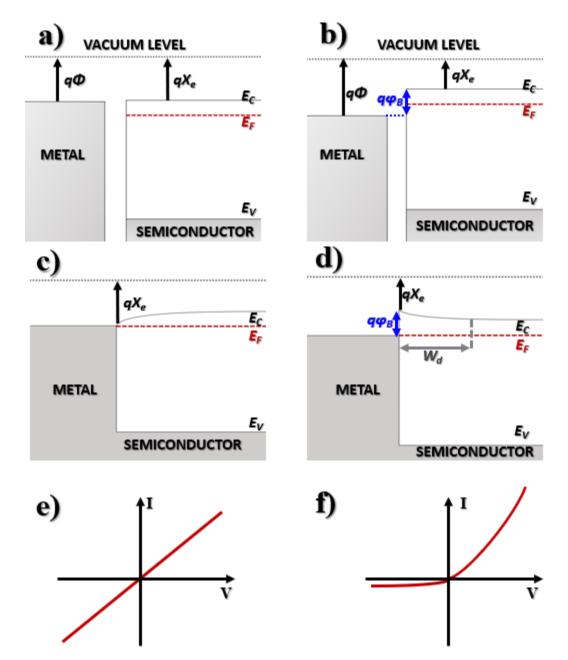

| 2.17 | Formation of Ohmic and Schottky contacts.                                                     | 30       |

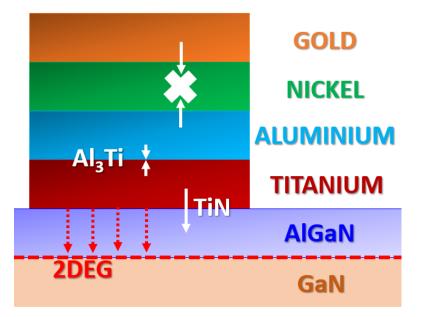

| 2.18 | Typical Ohmic contact stack.                                                                  | 31       |

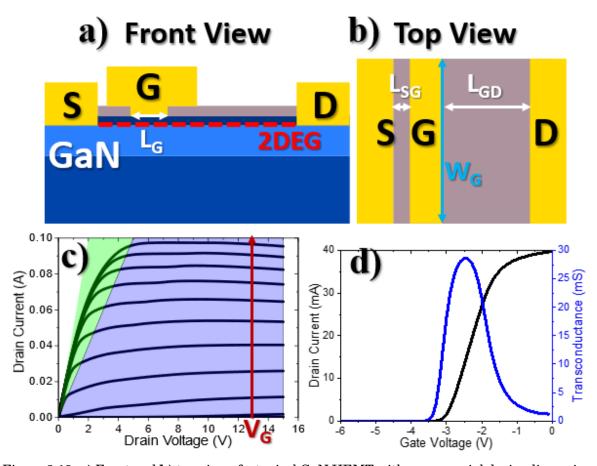

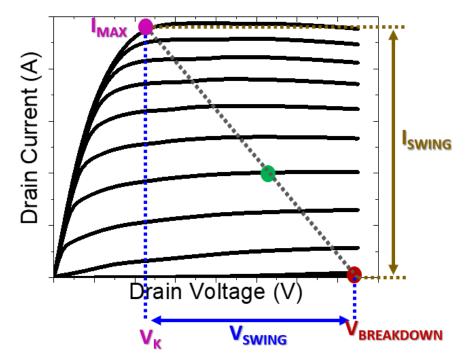

| 2.19 | HEMT geometry and IV characteristics.                                                         | 34       |

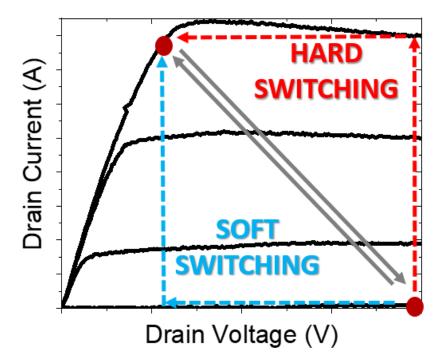

| 2.20 | Hard and soft switching in power GaN HEMT                                                     | 36       |

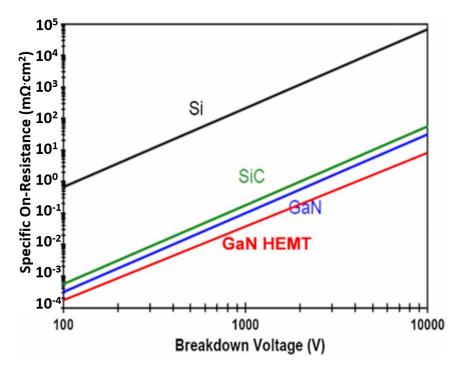

| 2.21 | Specific On-resistance of Si, SiC and GaN.                                                    | 37       |

| 2.22 | GaN RF HEMT operation.                                                                        | 39       |

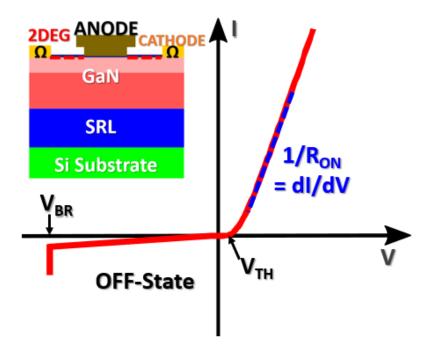

| 2.23 | Lateral GaN Schottky diode structure and IV characteristics                                   | 39       |

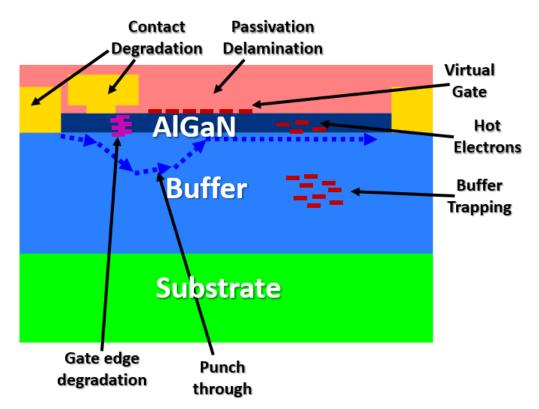

| 2.24 | Main degradation mechanisms in GaN HEMTs                                                      | 40       |

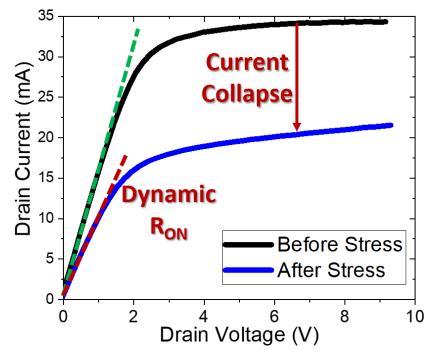

| 2.25 | The effects of trapping on HEMT IV characteristics.                                           | 42       |

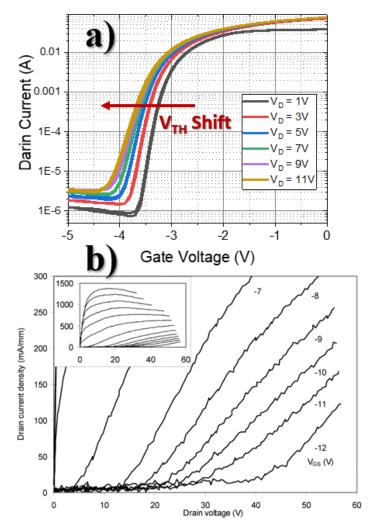

| 2.26 | Short channel effects in GaN HEMTs.                                                   | 44 |

|------|---------------------------------------------------------------------------------------|----|

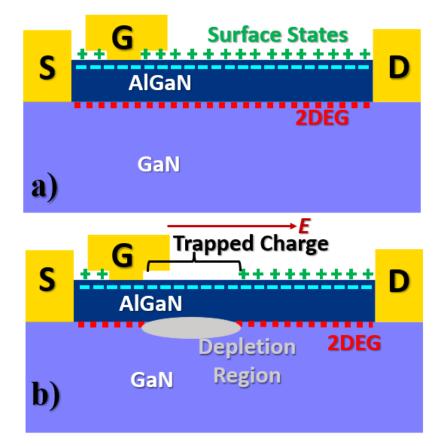

| 2.27 | Effects of surface trapping in GaN HEMT.                                              | 45 |

| 2.28 | Charge distribution during GaN HEMT operation.                                        | 46 |

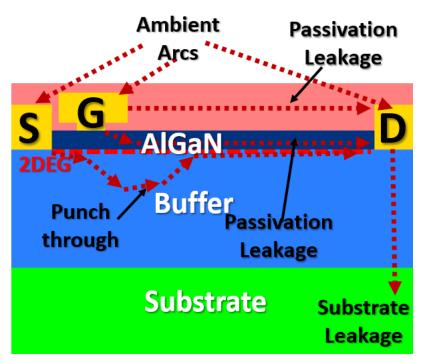

| 2.29 | Major leakage paths in GaN HEMTs.                                                     | 48 |

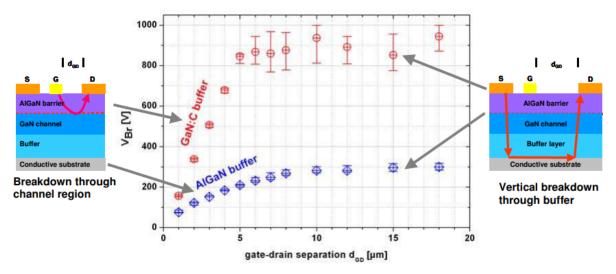

| 2.30 | Effects of gate-drain spacing on HEMT breakdown.                                      | 49 |

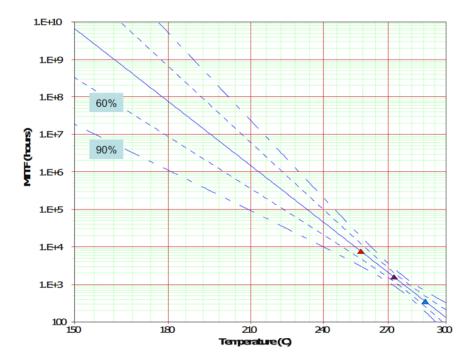

| 2.31 | Typical plot for calculation of the mean time to failure                              | 50 |

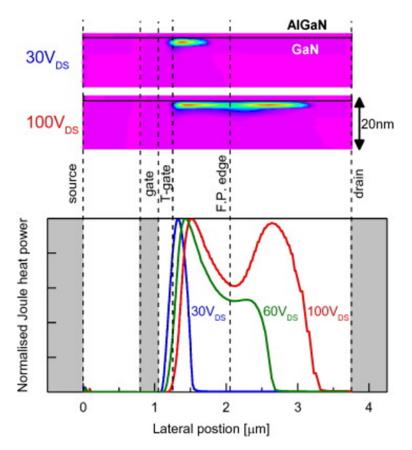

| 2.32 | Joule heating profile simulations for GaN HEMT.                                       | 51 |

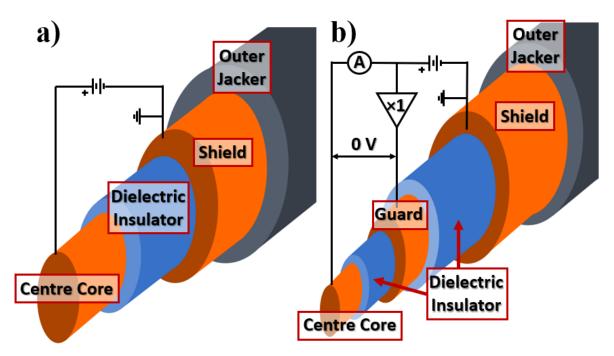

| 3.1  | Coaxial and triaxial cables.                                                          | 54 |

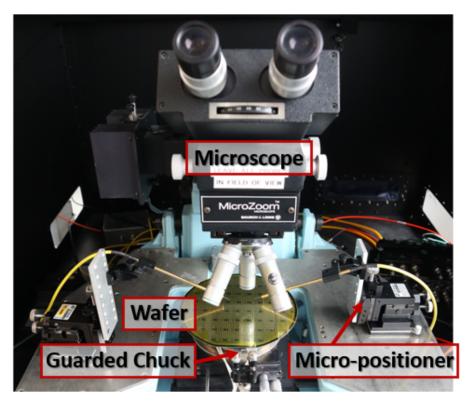

| 3.2  | Probe station for electrical measurements.                                            | 55 |

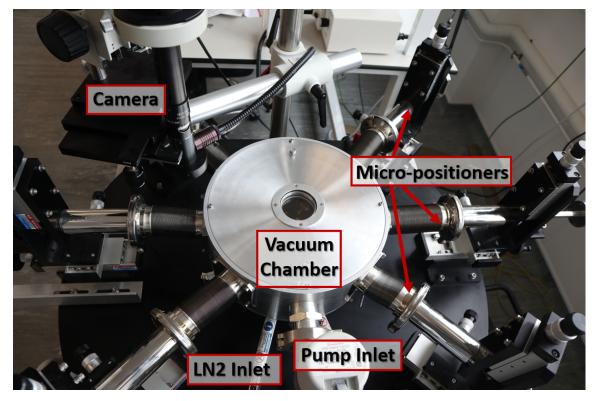

| 3.3  | Cryogenic probe station for electrical measurements.                                  | 56 |

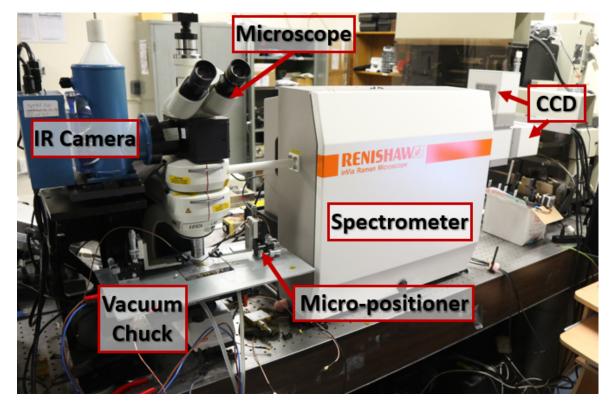

| 3.4  | Probe station for thermal measurements.                                               | 57 |

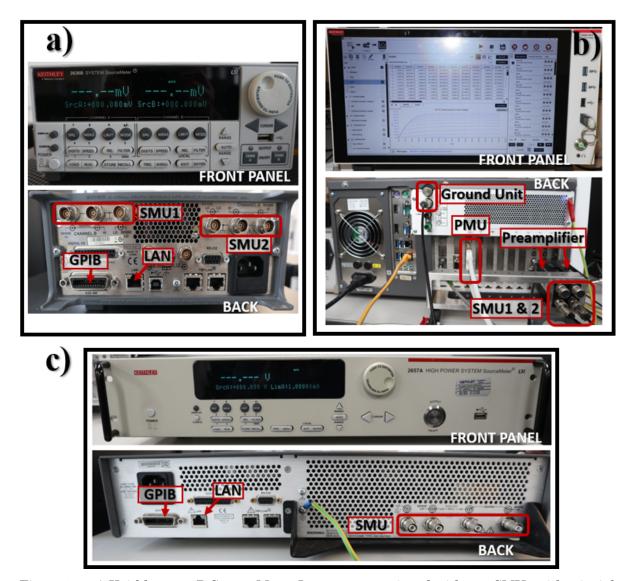

| 3.5  | Main instruments used for electrical characterisation.                                | 58 |

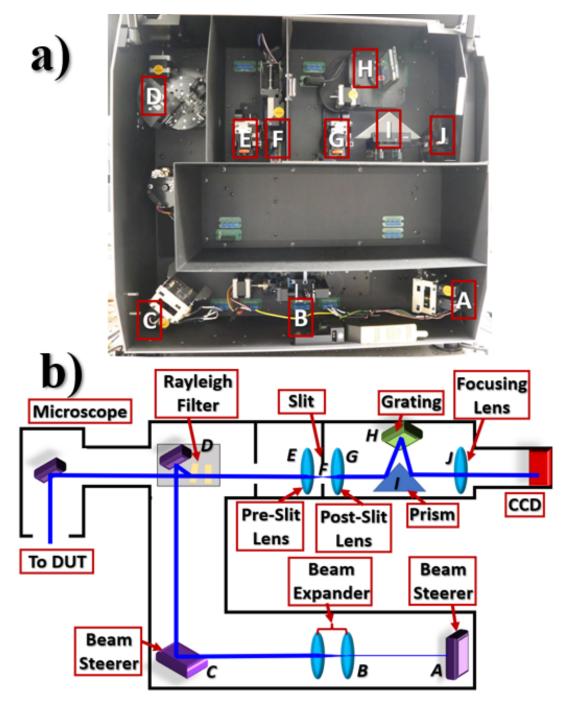

| 3.6  | Major components of the Raman spectrometer and the corresponding optical path         | 60 |

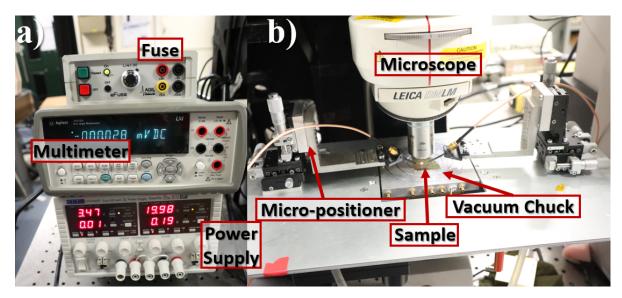

| 3.7  | Probe station and instruments for device biasing during thermal measurements          | 61 |

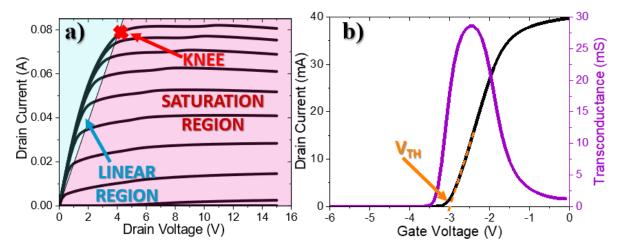

| 3.8  | GaN HEMT typical IV characteristics.                                                  | 62 |

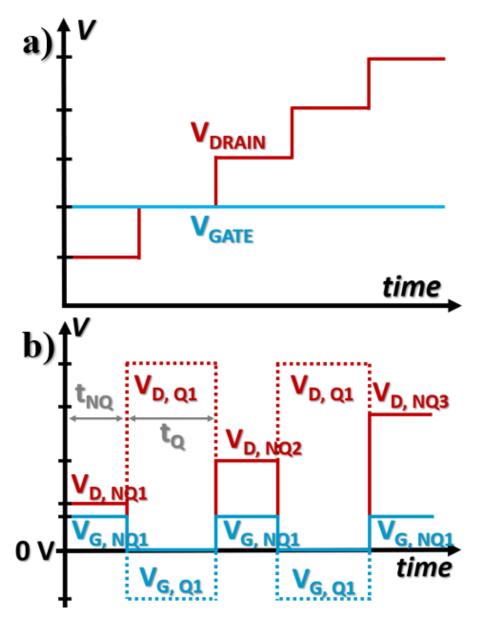

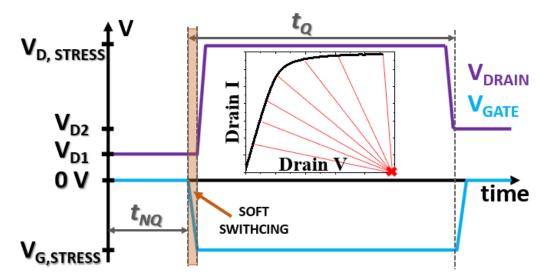

| 3.9  | Pulsed IV measurement timeline and bias conditions.                                   | 63 |

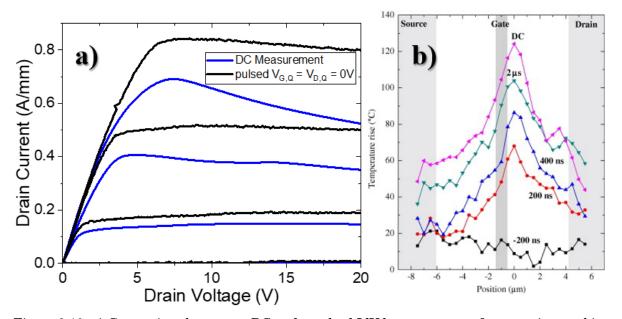

| 3.10 | THe effects of self heating on GaN HEMT IV characteristics.                           | 64 |

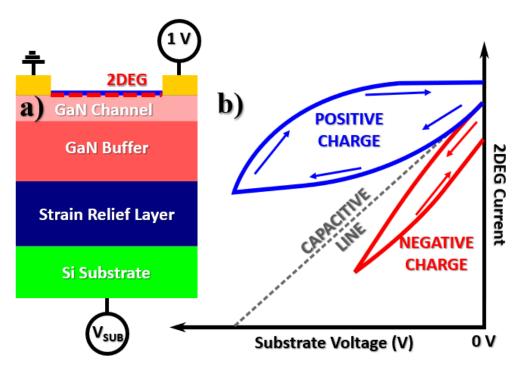

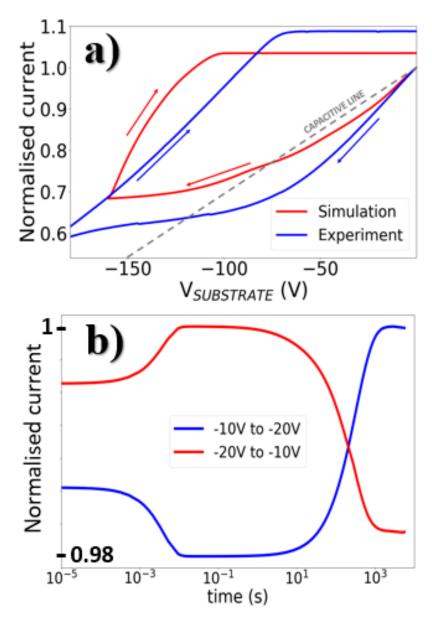

| 3.11 | Bidirectional substrate ramp sweep biasing conditions and interpretation              | 65 |

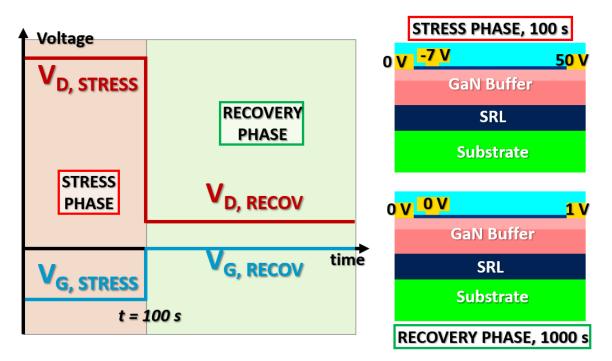

| 3.12 | Timeline and schematic representation of a typical current transient measurement.     | 67 |

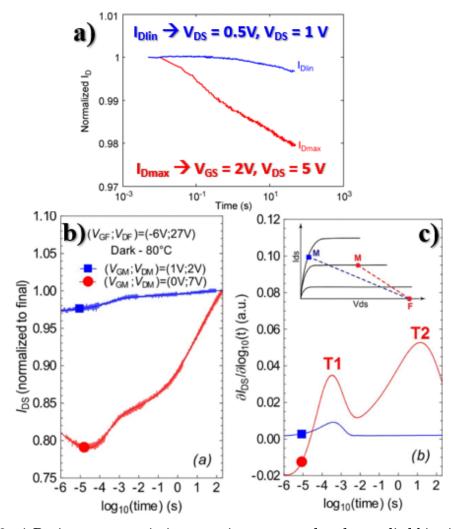

| 3.13 | Comparison of current transient measurements performed in the linear and saturation   |    |

|      | region                                                                                | 68 |

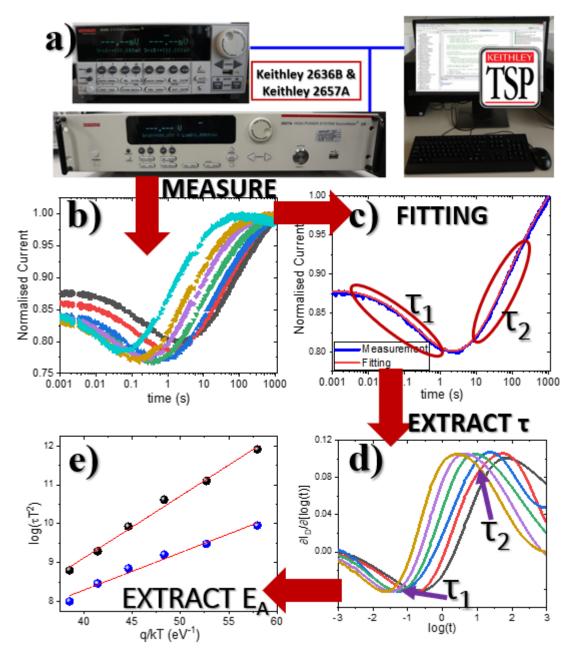

| 3.14 | General overview of current transient measurement and data analysis process           | 69 |

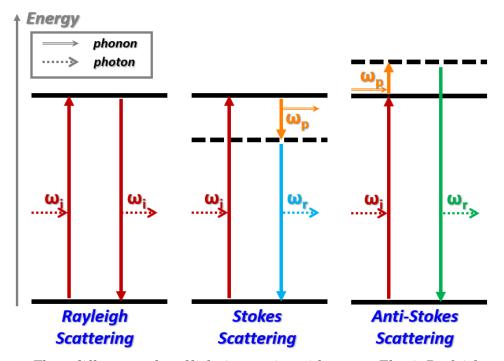

| 3.15 | Different types of Raman scattering.                                                  | 71 |

| 3.16 | Optical phonon modes in wurtzite GaN.                                                 | 73 |

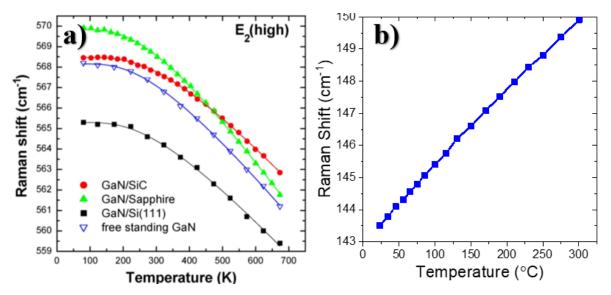

| 3.17 | Temperature calibration of GaN $E_2$ phonon mode and $TiO_2 E_g$ mode                 | 74 |

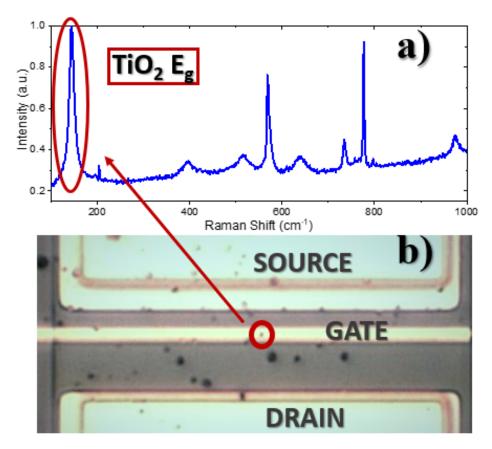

| 3.18 | Raman spectrum of $TiO_2$ nanoparticles.                                              | 76 |

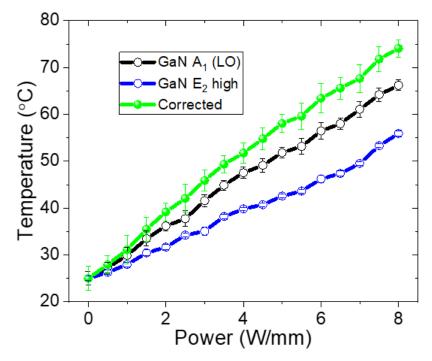

| 3.19 | Thermomechanical stress correction based on shift in GaN $E_2$ and $A_1$ Raman modes. | 78 |

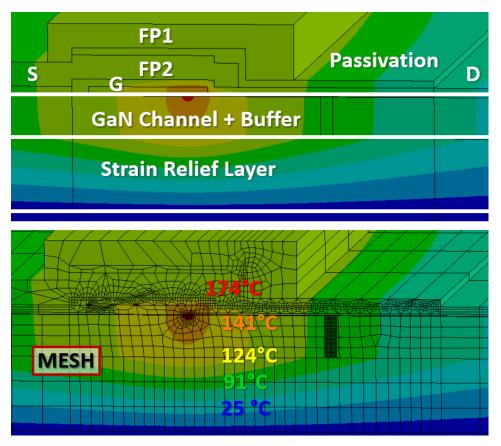

| 3.20 | Meshing of a lateral GaN Schottky Diode in Silvaco Atlas TCAD software                | 79 |

| 3.21 | Meshing of a GaN HEMT in Ansys FEA software                                           | 81 |

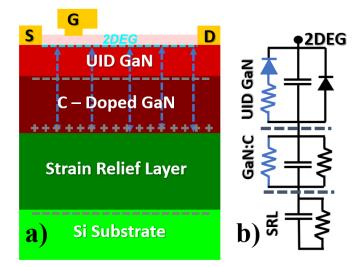

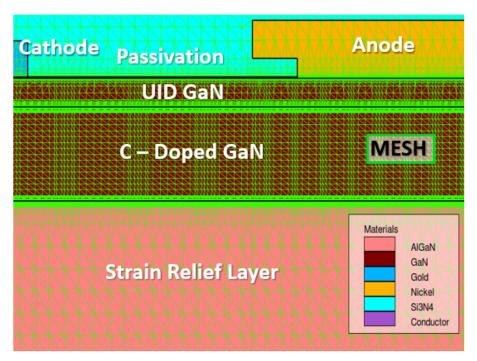

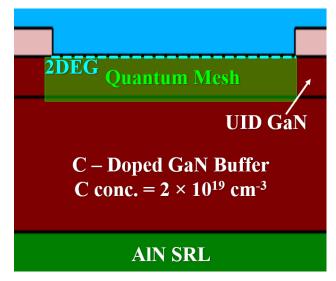

| 4.1  | Device epitaxial stack and test structures.                                           | 85 |

| 4.2  | Substrate stress transients: measurement timeline.                                    | 87 |

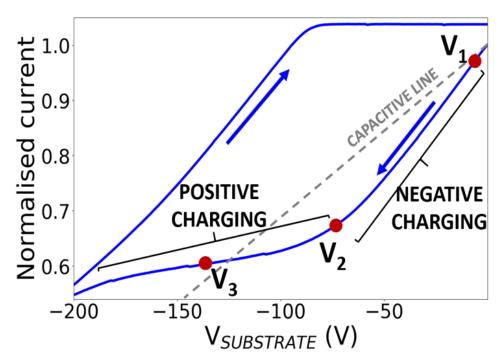

| 4.3  | Bidirectional substrate ramp sweep with relevant charging regions marked              | 88 |

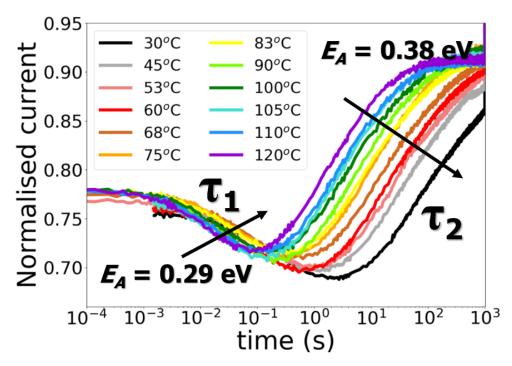

| 4.4  | Temperature substrate stress transient measurement                                    | 89 |

| 4.5  | Forward stepped substrate stress transient measurements of the potential difference   |    |

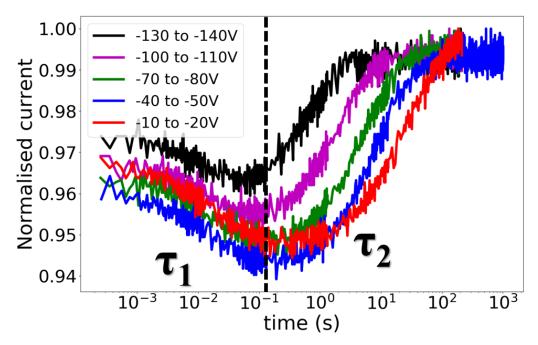

|      | of 10 V                                                                               | 90 |

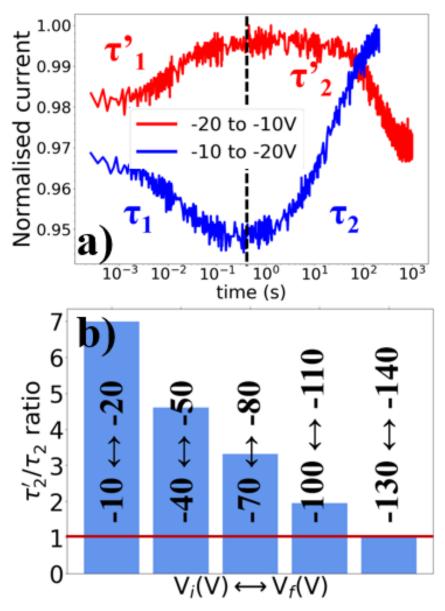

| 4.6  | Bidirectional substrate ramp transients of the potential difference of 10 V           | 91 |

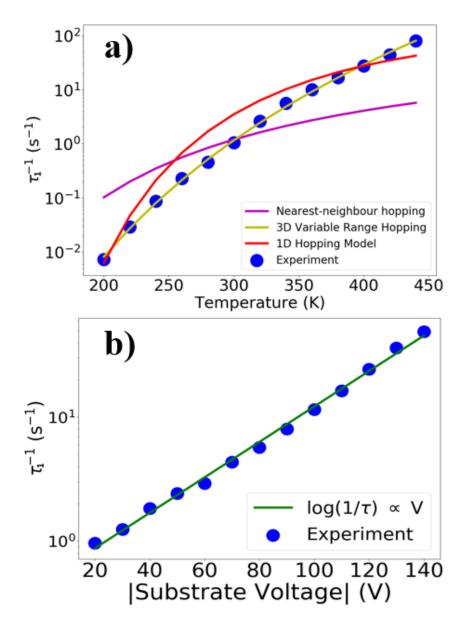

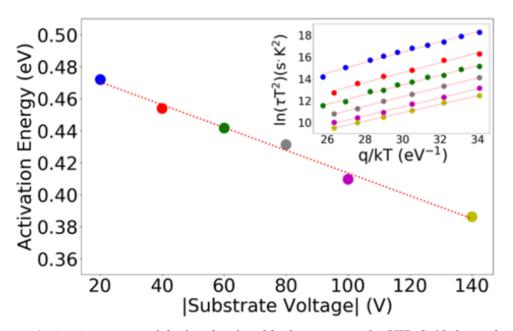

| 4.7  | Temperature and field dependence of the process $\tau_1$                              | 92 |

| 4.8  | Temperature and field dependence of the process $\tau_2$                                     |

|------|----------------------------------------------------------------------------------------------|

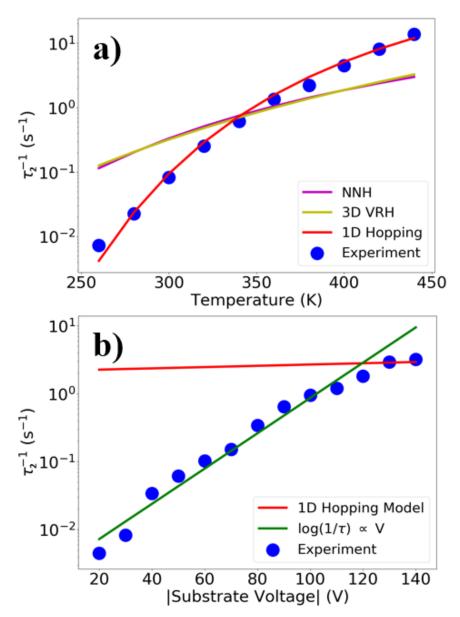

| 4.9  | Updated 1D lumped element diagram of the expitaxy                                            |

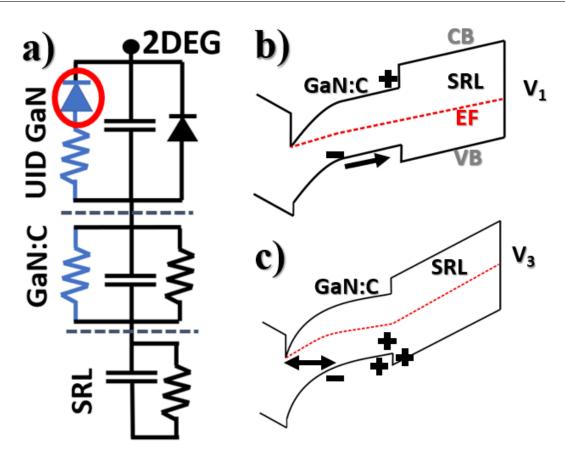

| 4.10 | Band diagrams showing charge transport in the epitaxy during and after applying              |

|      | stress                                                                                       |

| 4.11 | Activation energy of the band-to-band leakage across the UID GaN channel 98                  |

| 4.12 | Simulated TLM structure in Silvaco Atlas TCAD Software                                       |

| 4.13 | Simulated substrate ramps and substrate stress transients                                    |

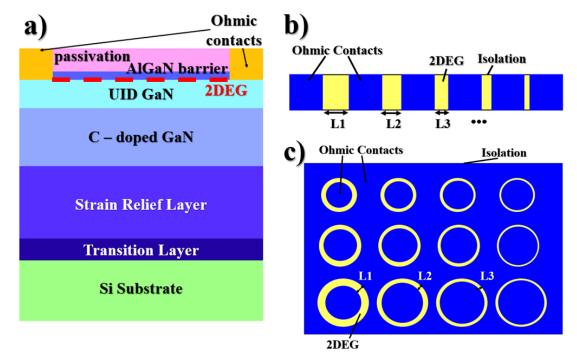

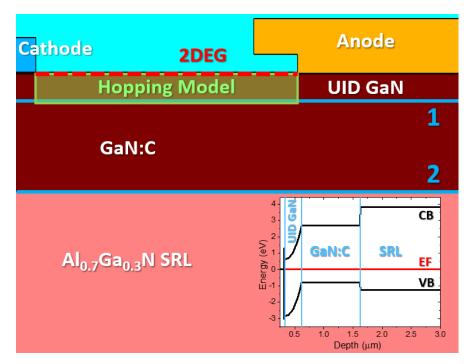

| 5.1  | Schematic diagram of experimental structure and the epitaxy                                  |

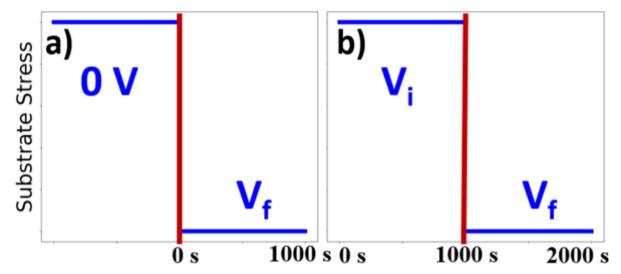

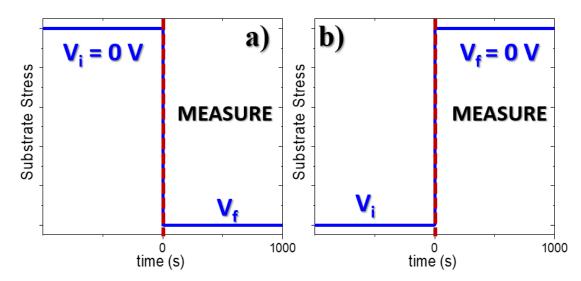

| 5.2  | Substrate stress transient measurement timeline                                              |

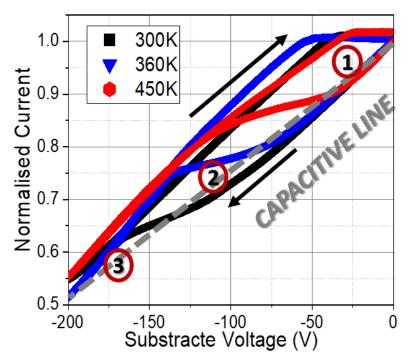

| 5.3  | Bidirectional substrate ramp sweeps for temperatures between 300 - 450 K 108 $$              |

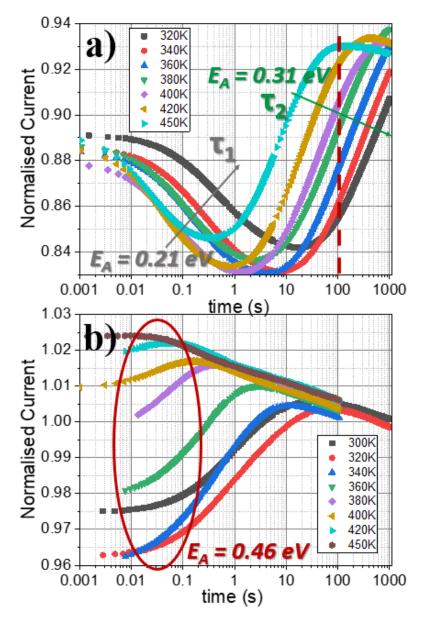

| 5.4  | Temperature dependence of substrate stress transient measurements of TLM struc-              |

|      | tures and corresponding recovery curves                                                      |

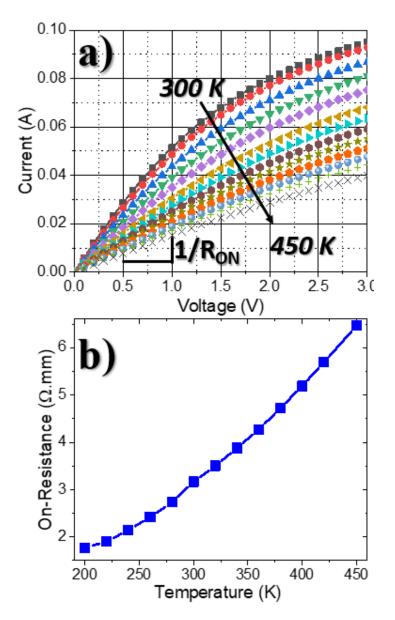

| 5.5  | On-resistance measurements of TLM structures with no stress applied 111                      |

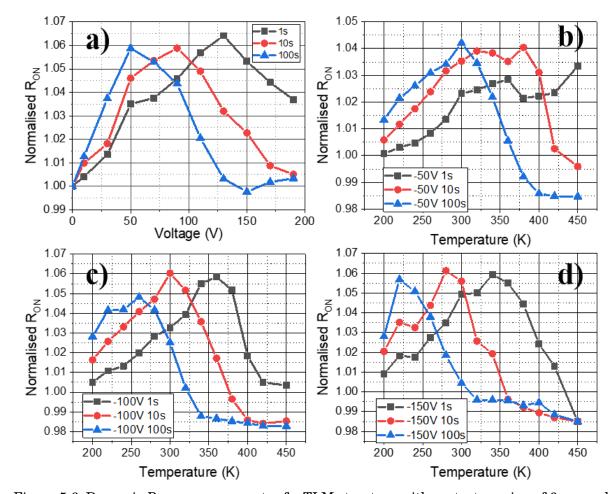

| 5.6  | Temperature and field dependence of dynamic $R_{ON}$ of TLM structures                       |

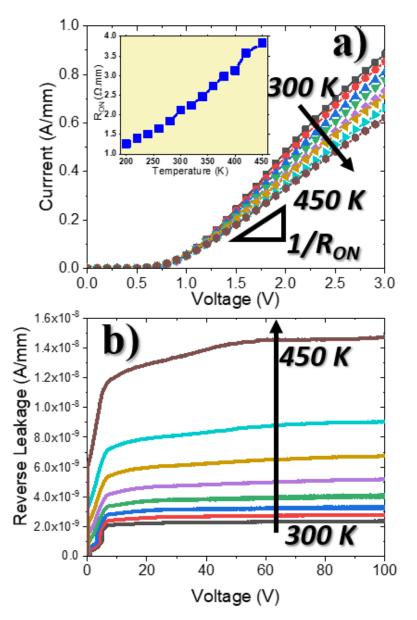

| 5.7  | IV characteristics and On-resistance of Schottky diodes in the absence of applied stress.113 |

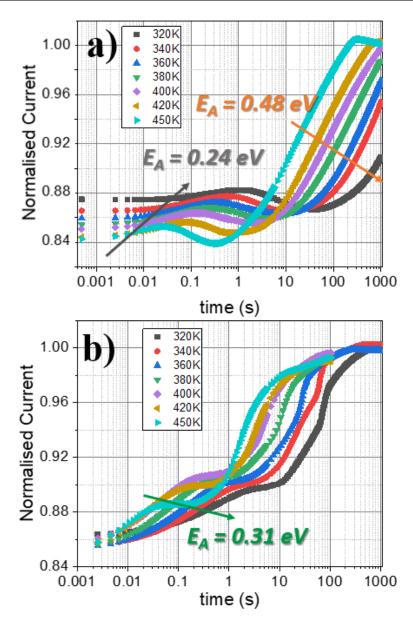

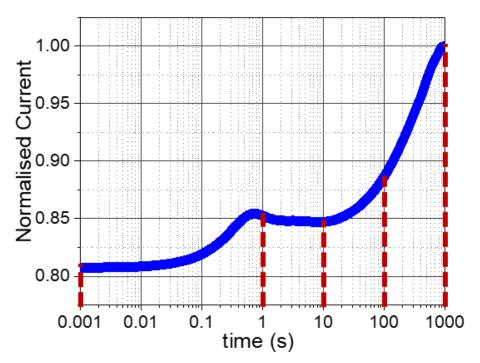

| 5.8  | Schottky diode recovery transients from reverse bias stress                                  |

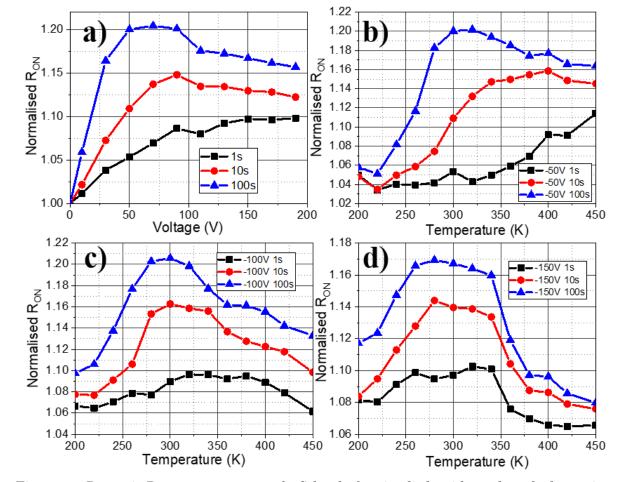

| 5.9  | Temperature and field dependence of dynamic $R_{ON}$ measured for Schottky diodes 115        |

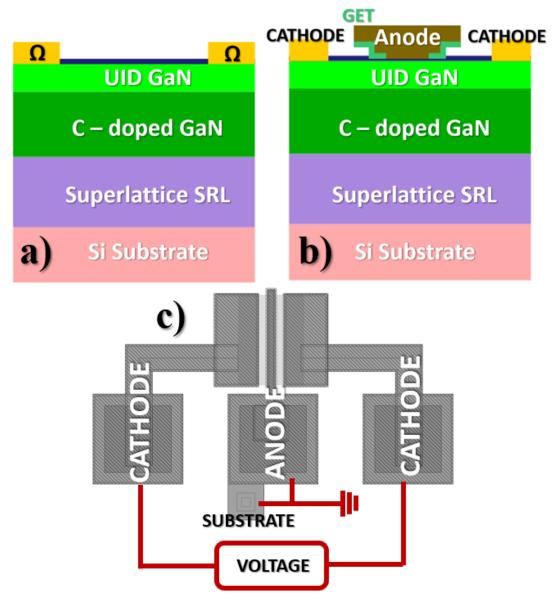

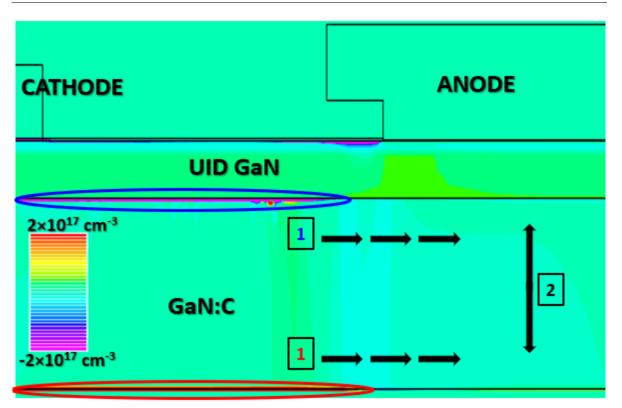

| 5.10 | Diagram of Schottky diode simulated in Silvaco Atlas TCAD software                           |

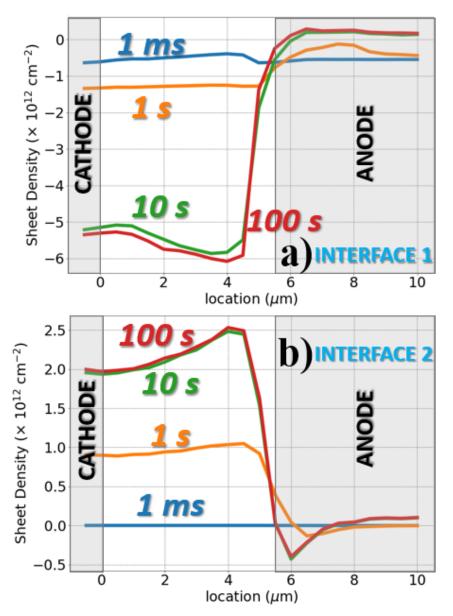

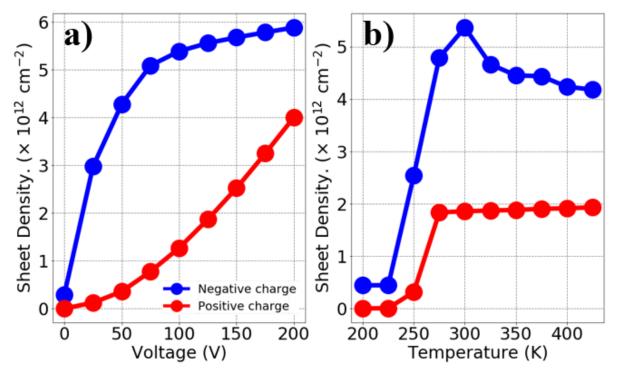

| 5.11 | Time dependence of the total net sheet charge density at the top and bottom of GaN:C         |

|      | buffer during trapping                                                                       |

| 5.12 | Simulated recovery transient for a Schottky barrier diode                                    |

| 5.13 | Time dependence of the total net sheet charge density at the top and bottom of GaN:C         |

|      | buffer during recovery from reverse bias stress                                              |

| 5.14 | Total net charge distribution immediately after stress in the Schottky diode 122             |

| 5.15 | Simulated maximum total net sheet charge concentration at the top and bottom of              |

|      | GaN:C buffer as a function of applied stress and temperature                                 |

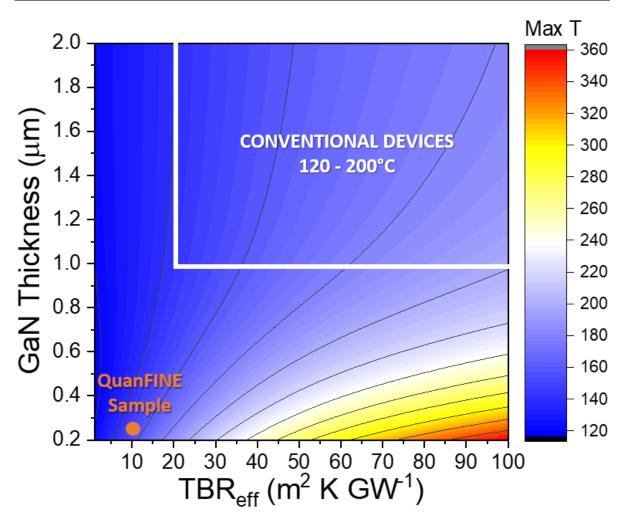

| 6.1  | QuanFINE ("buffer-free") technology compared to conventional GaN-on-SiC HEMT. 127            |

| 6.2  | Pulsed IV measurement timeline                                                               |

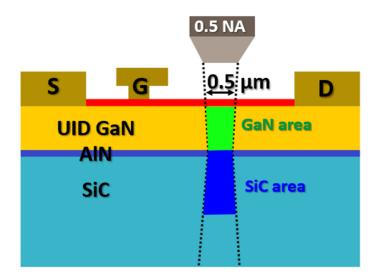

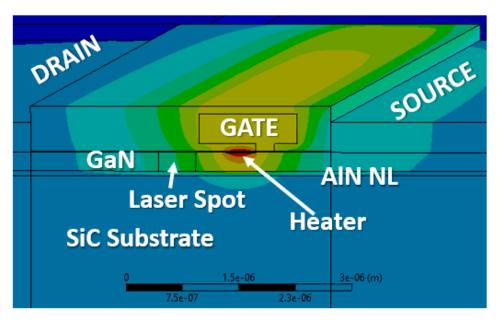

| 6.3  | Schematic diagram of micro-Raman thermography measurement on "buffer-free" HEMT.129          |

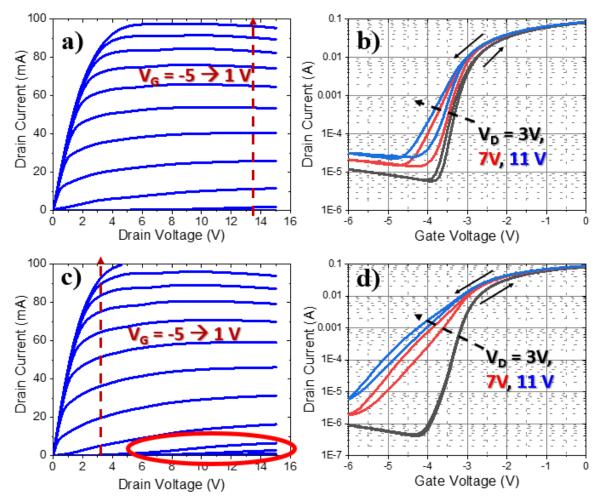

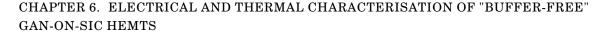

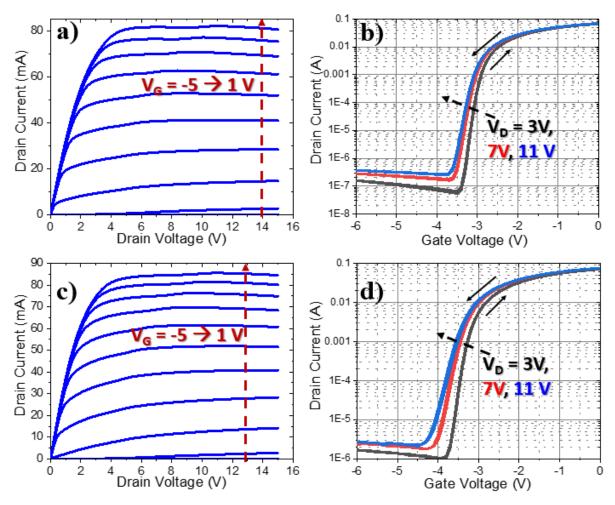

| 6.4  | DC IV characteristics of "buffer-free" GaN-on-SiC HEMTs 130                                  |

| 6.5  | DC IV characteristics of conventional GaN-on-SiC HEMTs                                       |

| 6.6  | Vertical leakage current for "buffer-free" and conventional GaN-on-SiC HEMTs. $\ldots$ 133   |

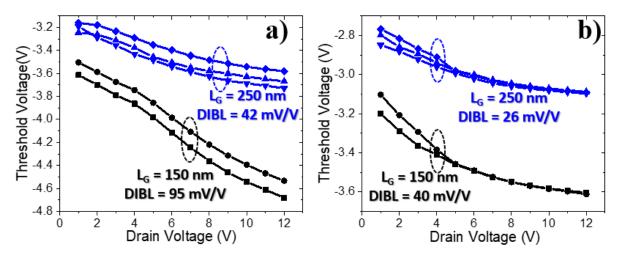

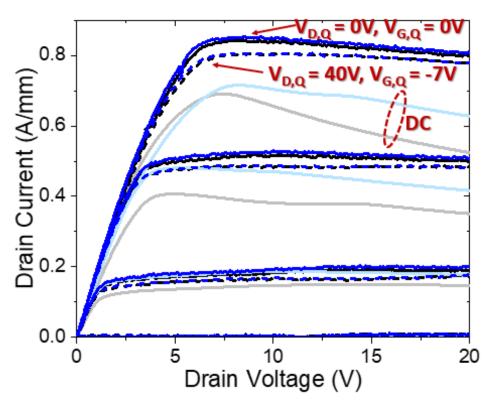

| 6.7  | DIBL measurements of "buffer-free" and conventional GaN-on-SiC HEMTs 133                     |

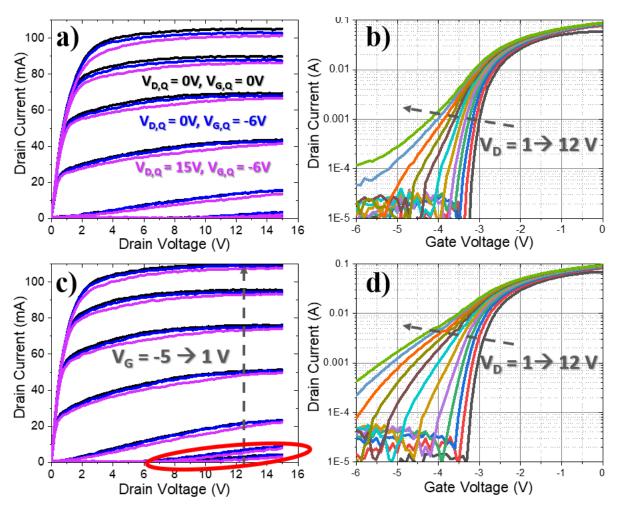

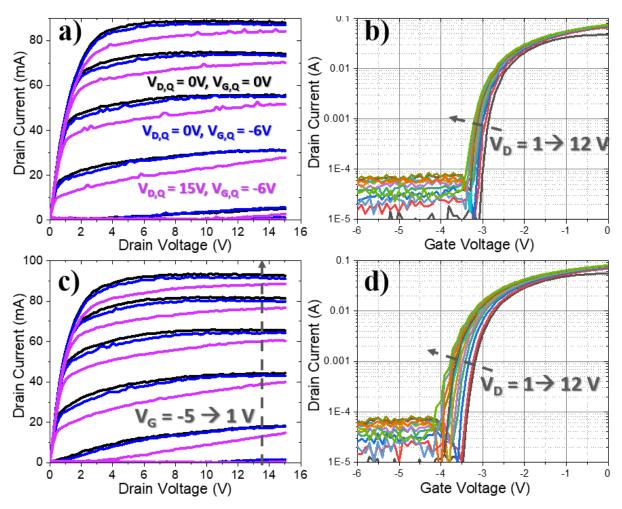

| 6.8  | Pulsed IV measurements of "buffer-free" GaN-on-SiC HEMTs                                     |

| 6.9  | Pulsed IV measurements of conventional GaN-on-SiC HEMTs                                      |

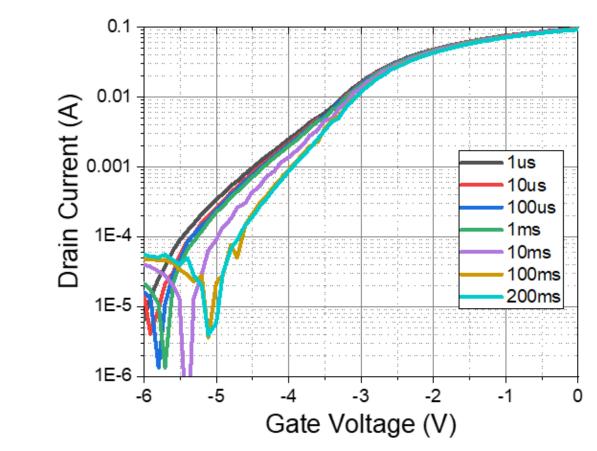

| 6.10 | Pulsed IdVg dependence on quiescent bias point duration for "buffer-free" GaN-on-SiC         |

|      | HEMTs                                                                                        |

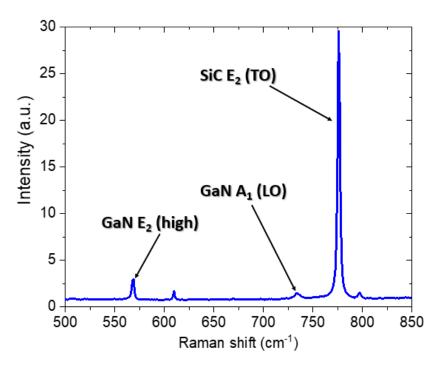

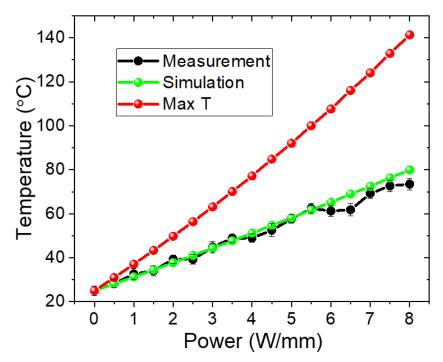

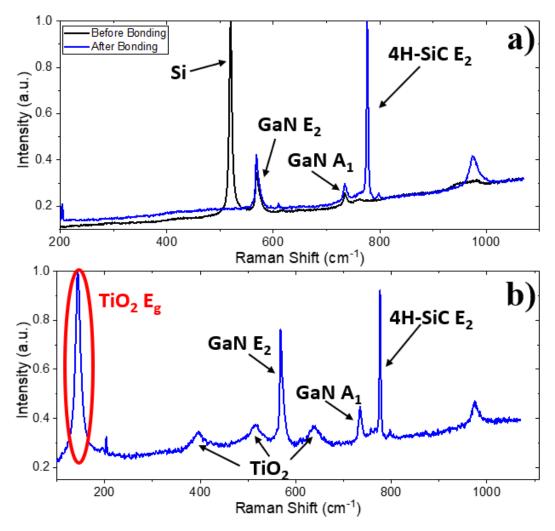

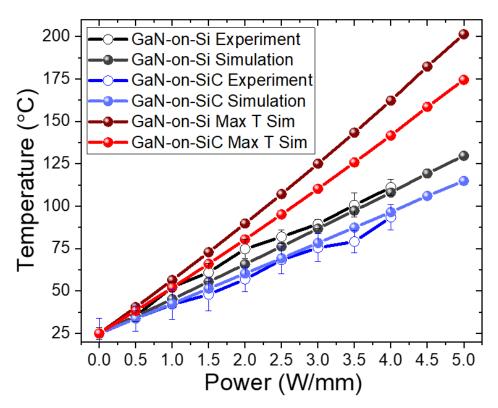

| 6.11 Raman spectrum of "buffer-free" GaN-on-SiC HEMTs.                                    | 137    |

|-------------------------------------------------------------------------------------------|--------|

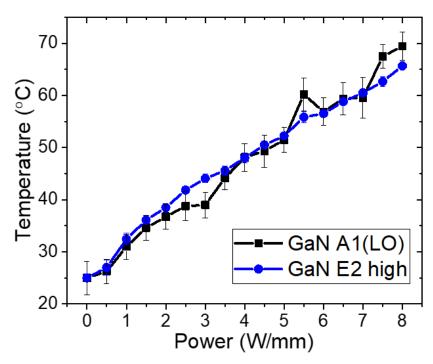

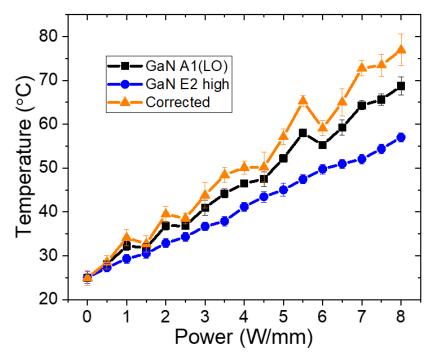

| 6.12 Operating temperatures of "buffer-free" HEMTs as a function of power dissipation     | on 138 |

| 6.13 Operating temperatures of conventional GaN-on-SiC HEMTs as a function of per         | ower   |

| dissipation                                                                               | 139    |

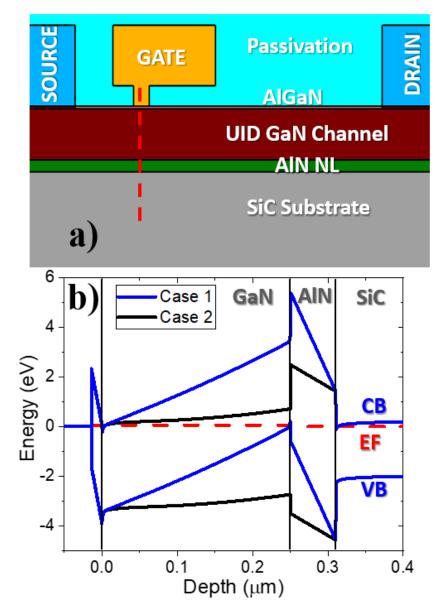

| 6.14 Simulated "buffer-free" GaN-on-SiC structures and corresponding band diagram         | s 141  |

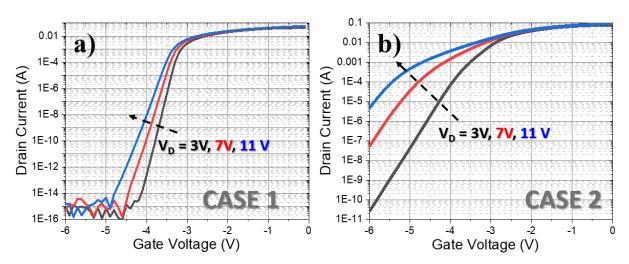

| 6.15 Simulated IdVg measurements corresponding to Case 1 and Case 2 band diagram          | ms 142 |

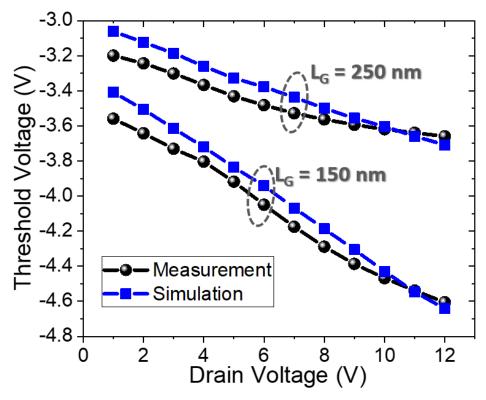

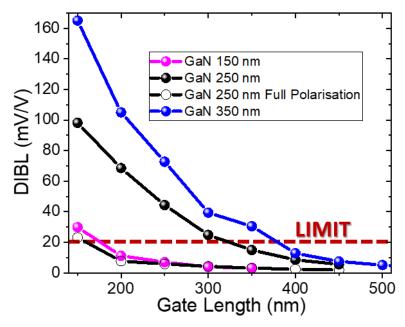

| 6.16 DIBL measurement and simulations for "buffer-free" GaN-on-SiC HEMTs                  | 142    |

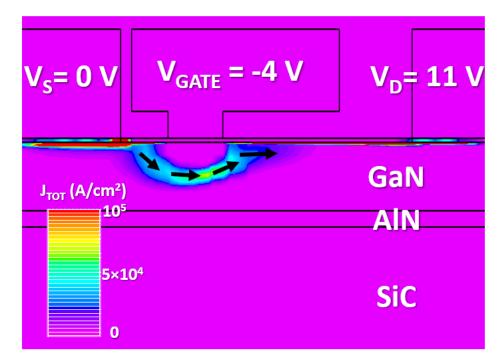

| 6.17 Simulated Off-state density for "buffer-free" GaN-on-SiC HEMTs                       | 143    |

| 6.18 Cross-sectional TEM images of AlN nucleation layer and interfaces for conventi       | onal   |

| devices and QuanFINE technology                                                           | 144    |

| 6.19 DIBL as a function of gate length and GaN thickness.                                 | 144    |

| 6.20 Comparison between micro-Raman measurement and Ansys simulations for con             | iven-  |

| tional GaN-on-SiC HEMTs.                                                                  | 147    |

| 6.21 "Buffer-free" GaN-on-SiC HEMT structure simulated in Ansys.                          | 147    |

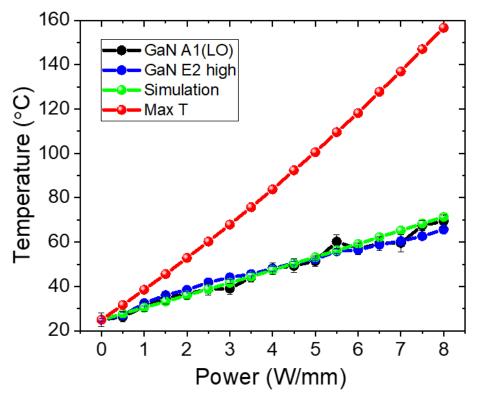

| 6.22 Comparison between micro-Raman measurement and Ansys simulations for "bu             | ıffer- |

| free" GaN-on-SiC HEMTs                                                                    | 149    |

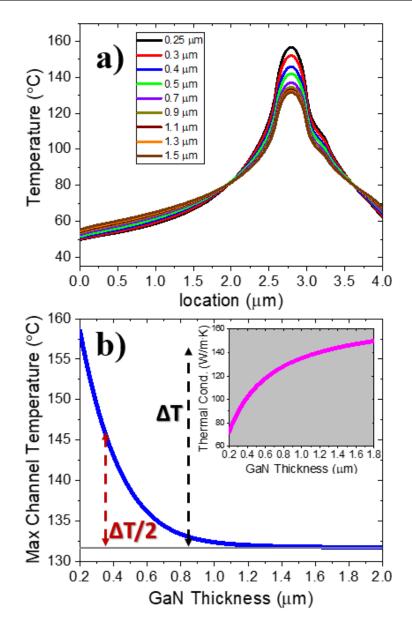

| 6.23 Lateral temperature profiles and peak channel temperature as a function of (         | GaN    |

| thickness                                                                                 | 150    |

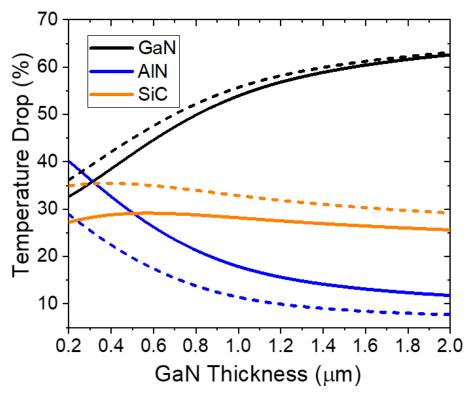

| 6.24 Percentage temperature drop across each epitaxial layer as a function of total (     | GaN    |

| thickness                                                                                 | 151    |

| 6.25 Peak chennel temperature as a function of total GaN thickness and $TBR_{eff}$ for pe | ower   |

| dissipation of 8 W/mm.                                                                    | 152    |

| 7.1 Original device structure and epitaxy.                                                | 157    |

| 7.2 Schematic representation of key steps involved in the bonding technique investig      |        |

| in this study.                                                                            |        |

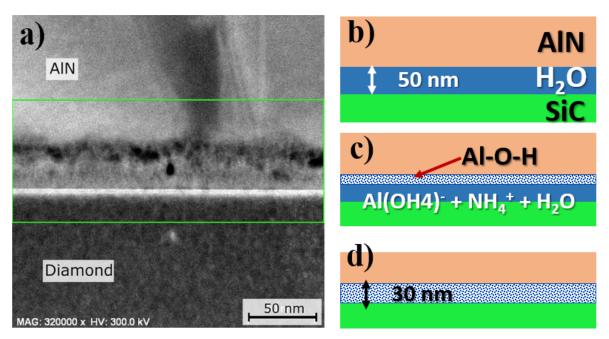

| 7.3 TEM image of bonded interface between AlN (bottom of AlGaN/GaN heterostruc            |        |

| thin film) and the bond substrate.                                                        |        |

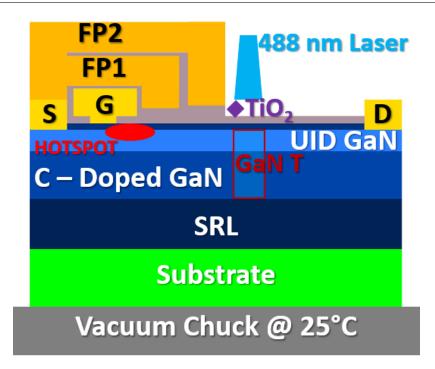

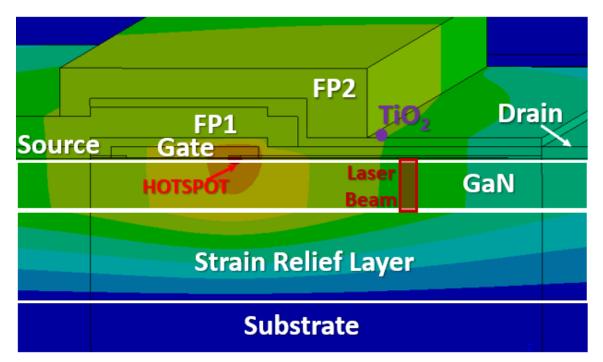

| 7.4 Schematic diagram showing micro-Raman thermography measurement of GaN HE              |        |

| before and after bonding.                                                                 |        |

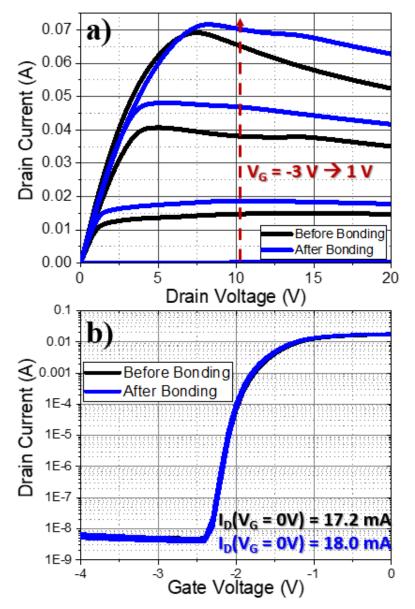

| 7.5 DC IV characterisation before and after bonding.                                      |        |

| 7.6 Pulsed IV characterisation before and after bonding                                   |        |

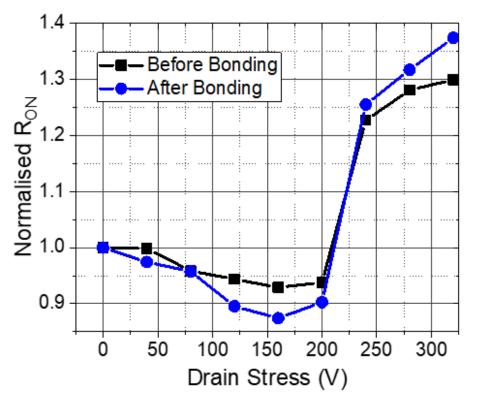

| 7.7 Dynamic $R_{ON}$ measurement performed on the devices before and after bonding.       |        |

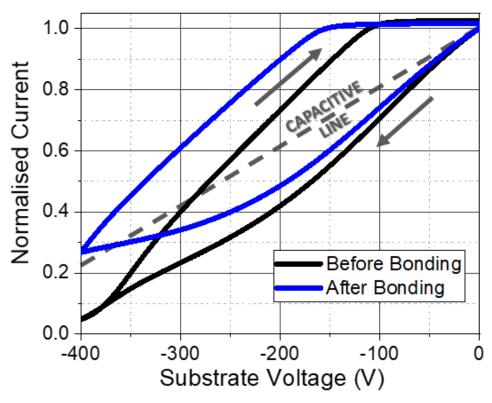

| 7.8 Bidirectional substrate ramp sweep performed on a single finger GaN HEMT be           |        |

| and after bonding.                                                                        |        |

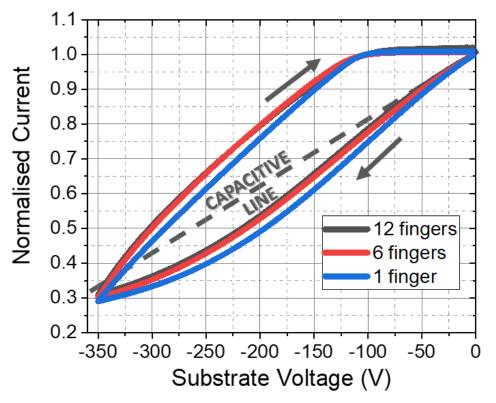

| 7.9 Bidirectional substrate ramp sweep dependence on device active area                   |        |

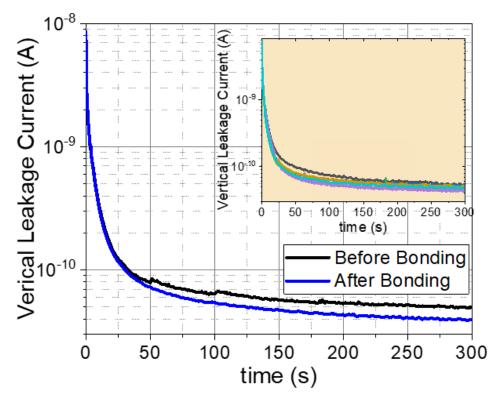

| 7.10 Vertical leakage measurements before and after bonding.                              |        |

| 7.11 Raman spectra of GaN HEMTs before and after bonding.                                 |        |

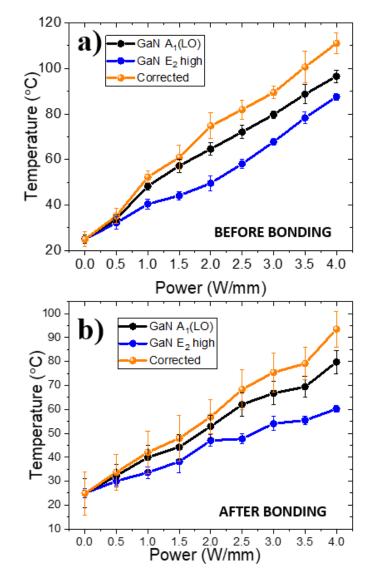

| 7.12 GaN temperatures as a function of power dissipation before and after bonding.        | 170    |

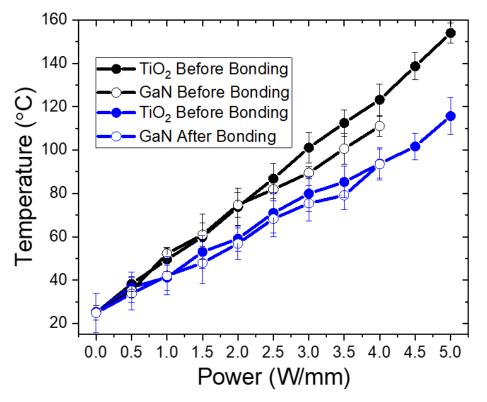

| 7.13 | Comparison between surface temperature (based on ${\rm TiO}_2$ nanoparticles) and GaN                                   |

|------|-------------------------------------------------------------------------------------------------------------------------|

|      | measurements for devices before and after bonding. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 171$ |

| 7.14 | GaN HEMT structure simulated using Ansys FEA Software                                                                   |

| 7.15 | Teperature measurements and Ansys simulations for devices before and after bonding. $174$                               |

|      |                                                                                                                         |

# LIST OF ACRONYMS AND INITIALISMS

- 2DEG Two Dimensional Electron Gas

- 2DHG Two Dimensional Hole Gas

- AFM Atomic Force Microscopy

- BFOM Baliga Figure of Merit

- BHFFOM Baliga High Frequency Figure of Merit

- CB conduction band

- CCD Charge Coupled Device

- CFOM Combined Figure of Merit

- CTE Coefficient of Thermal Expansions

- CVD Chemical Vapour Deposition

- CVU Capacitance-Voltage Unit

- DB Defect Band

- DIBL Drain Induced Barrier Lowering

- DOS Density Of States

- DUT Device Under Test

- EFL Electron Fermi Level

- FEA Finite Element Analysis

- FET Field Effect Transistor

- FOM Figure of Merit

- FP Field Plate

- GET Gated Edge Termination

- GSG Ground-Signal-Ground

- HEMT High Electron Mobility Transistor

- HVPE Halide Vapour Phase Epitaxy

- JFOM Johnson Figure of Merit

- KFOM Keyes Figure of Merit

- LED Light Emitting Diode

- LO Longitudinal Optical

- LPCVD Low Pressure Chemical Vapour Deposition

- MBE Molecular Beam Epitaxy

- MOCVD Metal Organic Chemical Vapour Deposition

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- MTTF Mean Time To Failure

- NA Numerical Aperture

- NL Nucleation Layer

- NNH Nearest-Neighbour Hopping

- PECVD Plasma Enhanced Chemical Vapour Deposition

- PL Photoluminescence

- PMU Pulse Measurement Unit

- RF Radio Frequency

- SEM Scanning Electron Microscopy

- SIMS Secondary Ion Mass Spectroscopy

- SBD Schottky Barrier Diode

- SMU Source Measurement Unit

- SRL Strain Relief Layers

- STEM Scanning Transmission Electron Microscopy

- TBR Thermal Boundary Resistance

- $TBR_{eff}$  Effective Thermal Boundary Resistance

- TCAD Technology Computer-Aided Design

- TEM Transmission Electron Microscopy

- TLM Transfer Length Method

- UID Unintentionally Doped

- UHV Ultra High Vacuum

- VB Valence Band

- VRH- Variable Range Hopping

#### INTRODUCTION

Go lobal energy demand grows rapidly each year and is predicted to increase by almost 50% from 2020 to 2050 [1], which in combination with current concerns about the direction of climate change and its impact on human life worldwide calls for more efficient energy solutions across all the sectors. Si-based power electronics has dominated the market for over 60 years thanks to continuous optimization of device processing and development of new structures such as insulated gate bipolar transistors (IGBTs) and thyristors [2]. However, despite Si devices nearing their theoretical limits, over 90% of power electronics is still made up of Si [3] [4]. The demand for higher blocking voltages, faster switching speeds as well as more compact and efficient modules creates a unique opportunity for novel wide bandgap semiconductors to exploit.

Figure 1.1 shows a comparison of some critical material parameters between Si, SiC and GaN. The parameteres shown in the figure represent typical values quoted in the literature, however they do not fully reflect the anisotropic nature of some material properties. Out of the three, GaN shows the highest critical electric field, exceeding that of Si by an order of magnitude, indicating GaN transistors are capable of withstanding 10 time the voltage of equivalent Si device of the same size, making it a good candidate for high power electronics. In addition, GaN exhibits high electron mobilities on the order of 1250 cm<sup>2</sup>/V·s for bulk (see red star in Fig. 1.1) and 2000 cm<sup>2</sup>/V·s for 2DEG, which in combination with high saturation velocity of the carriers offer higher switching speeds and wider bandwidth that can be effectively utilised in 5G power amplifiers. It has to be noted that carrier mobilities for each of the considered materials will exhibit anisotropic behaviour, due to anisotropy in effective masses of the carrier and is describe in more detail in the following chapter.

Although thermal conductivity ( $\kappa$ ) of GaN as measured in most heteroepitaxially grown devices is ~half of silicon carbide's, GaN single crystals have been measured with  $\kappa$  as high as

Figure 1.1: **a**) Spider diagram comparing key material properties of Si, SiC and GaN. Reported values found in [5].

269 W m<sup>-1</sup> K<sup>-1</sup> [6], with theoretical predictions in excess of 400 W m<sup>-1</sup> K<sup>-1</sup> at room temperature [7] [8] [9]. However, thermal conductivities of SiC and GaN are anisotropic in nature, resulting in reduced  $\kappa$  in certain crystallogrpahic directions. For GaN the anisotropy results in up to 14% difference in  $\kappa$  at 300 K [10], while for SiC, the difference can be as high as ~30% [11].

GaN-on-SiC RF HEMTs offer the advantages of GaN-based heterostructure with added thermal benefits of SiC substrate. Even though existing technologies based on GaAs and InP HEMTs allow for higher achievable operating frequencies, small bandgaps of these materials limit their power handling capabilities. For RF application GaN enables significant improvements in power capacity of the devices compared to aforementioned materials.

In addition to GaN and SiC other prominent materials have emerged over the past few decades competing for a share of a market previously occupied by Si. Some notable examples include gallium arsenide, indium phosphite (both mentioned above), and very recently gallium oxide in its beta phase ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) as well as diamond. GaAs and InP show outstanding electron mobilities up to 5400 and 8400 cm<sup>2</sup>/V·s respectively, however their bandgap exceed that of Si only by a small margin, limiting their application to relatively low voltages. Due to its ultra wide bandgap,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> can achieve breakdown fields three times larger than GaN. However, low electron mobility (and lack of available p-type conduction due to flat valence bands) in combination with very low thermal conductivity limit the application of this material to a high-voltage, low frequency region [12]. Lastly, despite its excellent breakdown fields, high electron mobilities and outstanding thermal conductivity, diamond poses a variety of challenges on a more

| Figure of Merit                              | $\mathbf{Si}$ | SiC | GaN       |

|----------------------------------------------|---------------|-----|-----------|

| Baliga ( $\epsilon \mu E_G^3$ )              | 1             | 223 | 190 (330) |

| Keyes ( $\kappa \sqrt{c v_s/4\pi\epsilon}$ ) | 1             | 3.6 | 1.8       |

| Baliga High Frequency ( $\mu E_C^2$ )        | 1             | 45  | 36 (63)   |

| Johnson ( $E_C^2 v_s^2/4\pi^2$ )             | 1             | 215 | 400       |

Table 1.1: Figure of Merit Relative to Si

Data taken from [15], and [5]. Some FOMs for GaN quoted using bulk mobility values with added values based on 2DEG mobility in the brackets.

practical level. Deep p-dopant in the form of boron and lack of n-doping, high costs of growth, difficult processing as well as issues in diamond integration with other materials are only some of the problems facing this technology [13] [14]. Although these materials can possibly play an important role in future electronic devices for power and RF applications, currently SiC and GaN show most promise in replacing Si in the existing applications.

To assess the suitability of a chosen technology for a chosen application, some key performance parameters need to be considered. For power electronics, qualities such as breakdown field and voltage, area specific On-resistance, peak saturation current and peak power output are particularly important [15]. For this reason wide bandgap semiconductors such as SiC and GaN are more suitable, offering reliable performance while being able to handle large power densities. For RF electronics, the suitability of a device high frequency switching applications can be assessed by examining quantities such as carrier mobility, On / Off drain current ratio, peak drain current, transconductance,  $f_T$  and  $f_{max}$ . In RF electronics, capacity to handle is less important, while minimising switching losses is of crucial importance. Therefore, semiconductors with large electron mobilities such as GaAs and InP are more suitable for RF applications.

In addition to examining key device parameters and material properties, figures of merit (FOMs) have been developed to quantify combined material parameters in the chosen area of interest. Table 1.1 shows a comparison between SiC and GaN relative to Si across five major FOMs.Performance of a power device switching at low frequencies can be assessed based on Baliga figure of merit (BFOM), which attempts to quantify conduction losses that are dominant in this application mode. Here, despite comparable bandgap and dielectric constant of GaN and SiC, HEMTs based on GaN heterostructures have an edge over the latter material mainly due to high electron mobility of the 2DEG. However, bulk mobility of GaN is significantly lower then that of the 2DEG (see Fig. 1.1), which would reduce the BFOM of GaN by around 40%. To quantify suitability of a given material for high frequency applications, Johnson's figure of merit (JFOM) and Baliga's High Frequency figure of merit (BHFFOM). The first one has been derived to define the switching losses for a low voltage transistor from a power-frequency product, while the latter attempts to describe the efficiency of a FET in high power applications [16] [17]. In both

metrics GaN devices utilising high electron mobility of the 2DEG outperform both Si and SiC indicating suitability of this technology for high frequency applications. The conduction losses of a power FET can be quantified based on Baliga figure of merit (BFOM), which is defined as the product of carrier mobility, dielectric constant and the bandgap of the device. In this metric GaN heterostructures show significant improvement on SiC transistors predominantly due to high electron mobility of the carriers in the 2DEG.

In addition, Keyes figure of merit (KFOM) describes the thermal limits for switching applications and is defined by thermal conductivity of the material and saturation velocity of the carriers [18]. Due to its excellent thermal conductivity SiC significantly outperforms GaN, which due to the compromised quality of heteroepitaxially grown films falls short of theoretically predicted thermal conductivities and experimentally measured values for single crystals. Although GaN HEMTs show improved performance in this metric, SiC devices outperform bulk GaN due to significantly higher thermal conductivity and comparable bulk carrier mobilities. Overall, despite improved switching and conduction losses in GaN, SiC is a more suitable material for high power applications as it offers improved thermal management and reliability at more extreme operating conditions.

Despite very promising performance of AlGaN/GaN HEMTs in comparison to competing technologies, commercialisation of GaN based micro-electronic devices took decades starting in the late 1960s with the first report of single crystal GaN film grown on 2 cm<sup>2</sup> sapphire substrate by Maruska and Tietjen [19]. Early GaN films were very defective and contained large quantities of impurities, defects and unintentional dopants, but throughout 1970s and 80s major improvement in growth quality and doping control have been made [20], culminating in development of first GaN-based blue LEDs by Nakamura *et al.* [21] that has been awarded with Noble Prize in Physics in 2014.

The first demonstration of a 2DEG in an AlGaN/GaN heterostructure was carrier out by Khan *et al.* in 1992 by growing a high electron mobility transistor on sapphire using a low-pressure MOCVD method [22], however soon after GaN HEMTs started being grown on SiC and eventually Si [23] [24]. Despite significant lattice and themal expansion coefficient mismatch, the cheap cost of production was the main driving force for developing modern GaN-on-Si HEMTs. Over the years, growth and fabrication techniques have improved significantly in combination with the introduction of field plates and reliable passivation leading to more robust transistors compared to the early devices. In addition, various techniques have been developed (such as p-GaN, recessed and tri-gates) to allow for commercial production of E-mode HEMTs, which are defined by positive threshold voltage [25] [26] [27].

Modern GaN based devices are gradually becoming more commercially available for power and RF applications, however there are still some major issues relating to device reliability preventing GaN technology from dominating the semiconductor markets. Despite best efforts to optimise growth conditions, GaN devices still contain significant concentrations of impurities, unintentional dopants and crystalline defects that provide avenues for device degradation especially at high voltage operation. Nowadays surface effects are well controlled using carefully designed field plates and passivation layers, however there are still unresolved issues relating to the impact of buffer layers on device performance. Since modern GaN transistors are grown on foreign substrates, effects of lattice and thermal expansion coefficient mismatch result in significant strain and dislocation inside the epitaxy especially near the heterointerfaces. This situation makes it necessary to include thick buffer layers in order to reduce the quantities of defects and to separate electrically active regions from the highly defective areas. The buffer layer is therefore of critical importance for GaN HEMT operation, and is the main focus of the work presented in this thesis.

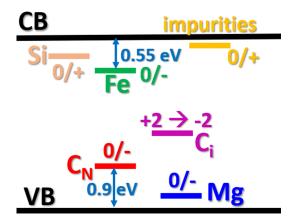

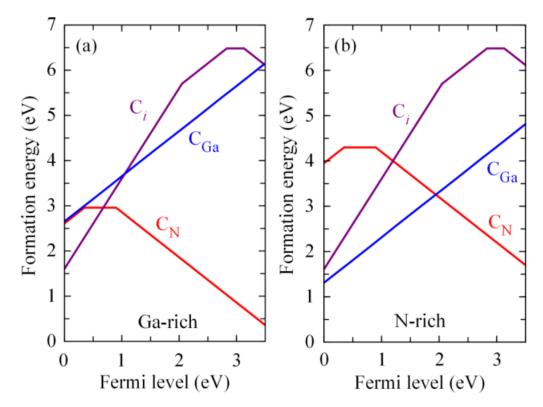

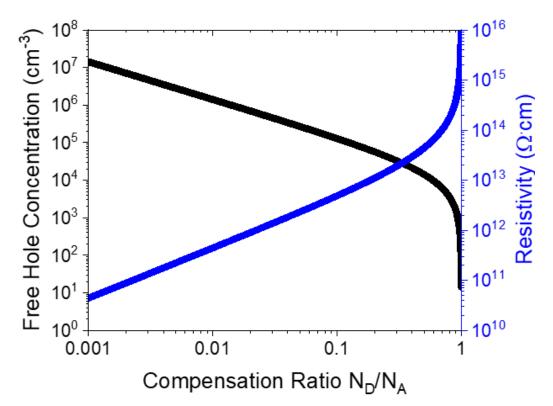

To ensure device operation at high voltages, GaN buffers have to be insulated by the introduction of extrinsic dopants, mainly iron (Fe) and carbon (C). Fe is the dopant of choice for RF applications, with typical doping concentrations in excess of ~  $10^{18}$  cm<sup>-3</sup> and its main purpose is to suppress vertical leakage currents and to ensure appropriate carrier confinement in the channel. In addition, Fe-doped buffers in combination with well designed field plates have delivered record power outputs [28] [29]. However, Fe is insufficient to provide adequate insulation for power applications, therefore carbon doping is commonly used in power transistors with the doping concentrations on the order of 10<sup>19</sup> cm<sup>-3</sup>. C doping results in lower Off-state leakage and higher breakdown voltages in comparison to Fe. Although introduction of these dopants performs its intended function of insulating GaN buffers, some aspects of their electrical behaviour are not well understood. Recent work on C-doping in GaN indicates the variation in doping concentration can have a significant impact of charging and discharging properties of the buffer [30]. Moreover, despite providing excellent insulation, C-doped buffers are susceptible to phenomena such as dynamic R<sub>ON</sub>, where the device On-resistance increases temporarily (in some cases for 1000s of second) following a period of Off-state stress. A solution to the issue of dynamic R<sub>ON</sub> has been proposed by Panasonic with their gate-injection transistor (GIT) [31], however introduction of p-GaN region for hole injection carries its own significant reliability challenges [32]. In any case, it is impossible to completely avoid incorporation of C during device growth by MOCVD method and even relatively small concentrations of this dopant can have significant impact on electrical performance of the devices.

In addition to electrical considerations, the push towards higher achievable power densities and faster switching speeds poses significant challenges for thermal performance of GaN based devices. As the device power output increases, so does the peak channel temperature. Since the device lifetime is directly related to operating temperatures by the Arrhenius equation, effective heat conduction away from the hot spot is of paramount importance. The heat diffusion inside the device can be affected by a variety of factors such as thermal conductivities of the epitaxial layers, quality of the interfaces and even the device design and geometry. Modern solutions for thermal management of commercially available devices involve combination of GaN with high-thermal conductivity substrates such as SiC and diamond (if possible), as well as careful engineered packaging including microfluidic cooling.

The main theme of this thesis revolves around understanding of the electrical and thermal performance GaN - based RF and power device by performing experimental measurements on novel GaN structures and combining these results with computational simulations to build a deeper understanding of physical mechanisms limiting their performance. From the electrical perspective, the effects of C doping on the dynamic electrical behaviour of the buffer are studied in detail, followed by the analysis of new ideas involving complete buffer removal and its benefits for RF electronics. From the thermal perspective, the impact of individual epitaxial layers and interfaces on heat dissipation in an operating devices is studied.

# **1.1 Thesis outline**

The main theme of this thesis is the electrical and thermal characterisation of GaN - based power and RF devices. For this reason, Chapter 2 includes some fundamental concepts relating to electrical and thermal properties of GaN. In this chapter, device operation as well as key reliability issues will be discussed to provide an appropriate context and motivation for the work presented here. In addition, Chapter 3 gives an outline of experimental techniques for electrical and thermal characterisation used in this thesis, giving a comprehensive description of experimental environment, hardware and software used throughout this work. This part of the thesis concludes the introductory segment of this work and is followed by the chapters outlining key research outputs of the thesis.

Chapter 4 describes a study carried out on GaN-on-Si transfer length method (TLM) structures, aimed at investigating the charge transport processes in the C - doped GaN buffer and channel layers. This study involves substrate ramp sweep measurements and current transient measurements aimed at separating and identifying key charge transport mechanisms taking place in the GaN layers in the voltage range up to 200 V. Chapter 5 constitutes a continuation and extension to the previous chapter. Here, the ideas developed on simple TLM structures are applied to lateral GaN-on-Si Schottky barrier diodes. The relationship between dynamic On-resistance and charge transport processes in the buffer is explored using a combination of electrical measurements and computational simulations.

In chapter 6, novel "buffer-free" GaN-on-SiC HEMTs are characterised from the electrical and thermal perspective and their performance is compared to conventional GaN-on-SiC HEMTs with thick Fe - doped buffer. The experimental measurements are combined with computational simulations to obtain a comprehensive image of the device performance in each of the investigate areas. Further computational parametric analysis is carried out and a device design for optimised electrical and thermal performance is proposed.

Chapter 7 focuses on electrical and thermal characterisation of proof-of-concept GaN HEMT

devices transferred and bonded onto SiC substrates using novel adaptive low-temperature resulting in covalent bonding between the transferred heteroepitaxial film and the bond substrate. Using a combination of experimental measurements and computational simulations, this work serves as a demonstration of the benefits of this technique, as can be applied to a wide range of III-nitride devices and substrates. The main findings of this thesis are concluded in Chapter 8.

# **THEORETICAL BACKGROUND**

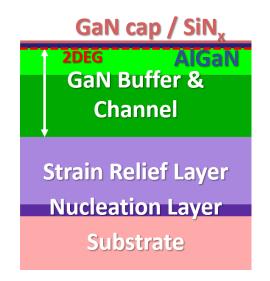

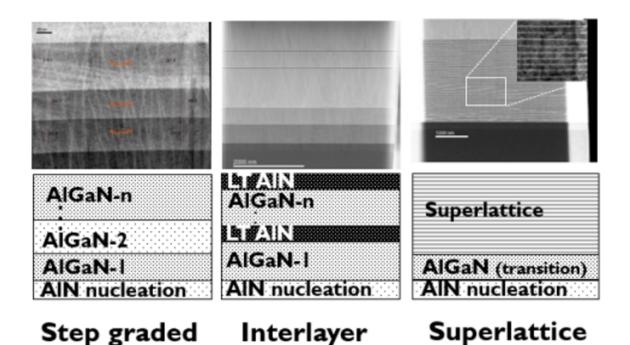

his chapter describes key theoretical concepts relating to GaN-based RF and power microdevices including electrical and thermal properties of the material. Epitaxial structure of typical GaN-based transistors and diodes is discussed with particular focus on device operation, reliability and challenges involved in growth and fabrication of GaN on foreign substrates.

# 2.1 Material Properties

This section introduces key theoretical concepts relating to fundamental material properties that allow for creation of GaN-based electronic devices, starting on a molecular level with crystal structure and polarization effects, and moving on to band diagrams, phonons and heat transfer in semiconductor materials.

#### 2.1.1 Crystal Structure

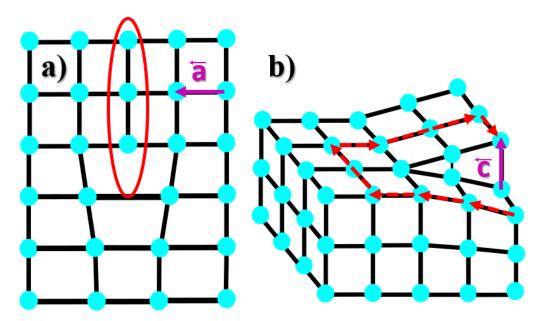

Gallium nitride is a group III-V binary, direct band gap semiconducting material that exists in three possible structures: rocksalt - represented by face-centered cubic lattice of Ga and N atoms, zinc-blende - consisting of face-centred tetrahedral lattice with only half of the available sites occupied by atoms, and wurtzite. GaN rocksalt phase is meta-stable and therefore currently unsuitable for device fabrication. However GaN-based devices can be manufactured from zincblend and wurtzite structures, with the latter being far more common and well established, therefore it will be the main focus of this thesis. Wurtzite GaN cell structure shown in Fig. 2.1a consists of intermittent layers of hexagonal close packed gallium (Ga) and nitrogen (N) atoms, misaligned in relation to one another by 5/8 of the c lattice constant. The c lattice constant lies in

Figure 2.1: **a**) Schematic representation of GaN wurtzite structure in real space. The ratio of c/a is an important parameter affecting spontaneous polarization of the crystal. **b**) First Brillouin zone of a hexagonal structure in momentum space with key symmetry points indicated.

the [0001] direction (axial direction of the hexagonal column) and describes the closest distance between two equivalent atoms in the unit cell. Most GaN-based devices have Ga-face (grown in the [0001] direction) at the top face, however successful device fabrication based on N-faced GaN (grown in the [0001] direction) has also been reported [33] [34]. The conventional N-rich conditions and high temperatures present during MOCVD growth favour formation of Ga-polar GaN, hence the devices grown in [0001] direction are more prevalent than the N-polar alternative, which is more challenging to realise. The polar nature of Ga-N bond results from the difference in electronegativity, which is defined as atom's ability to attract electrons. Nitrogen is ~70% more electronegative than gallium, resulting in a dipole moment along the bond. Due to lack of inversion symmetry in the GaN structure, the choice of face termination will affect the direction of polarization in the crystal and will have a significant impact on thermal stability, chemical behaviour and adatom mobility [35].

Transformation of crystal Wigner-Seitz unit cell (primitive unit cell in real space) of GaN wurtzite structure into reciprocal space gives the first Brillouin zone, which is shown in Figure 2.1b. The first Brillouin zone is constructed from perpendicular bisectors of the reciprocal lattice vectors starting at the origin. The centre of Brillouin zone is denoted by the point  $\Gamma$ , which corresponds to reciprocal lattice wavevector k = 0. Wavevectos  $k_x$ ,  $k_y$  and  $k_z$  correspond to transformation of Cartesian coordinates into the reciprocal lattice space. According to Bloch theorem, if the energy in the real lattice space is periodic, then the wavefunction that satisfies the Schrödinger equation can be expressed as a function that is periodic in the reciprocal lattice

space. Consequently, Bloch theorem also predicts periodicity of energy in the reciprocal space. Thus, when considering electronic band diagrams of a material, it is sufficient to investigate it only within the first Brillouin zone.

Figure 2.2: Electronic band diagram of wurtzite GaN with direct band gap of 3.4 eV at room temperature (highlighted by a red box). The other forms of GaN structures include rocksalt and zinc-blende, which differ in electronic band diagrams. Figure adapted from [36] with the permission of AIP Publishing.

Figure 2.2 shows the electronic band diagram of GaN across the first Brillouin zone. At temperatures exceeding 0 K only the bands closest to the Fermi level (within thermal energy  $k_BT$ ) will be partially filled and therefore they will determine the electrical properties of the material. For GaN, the minimum band gap is located at the point  $\Gamma$ , with the energy of 3.4 eV at 300 K. The curvature of the band determines the effective mass of the carriers. Due to high curvature of the conduction band (see the red box in Fig. 2.2) effective mass of electrons in GaN is low resulting in high mobility of the carriers. However, the curvature of the valence bands at  $\Gamma$  point for wurtzite GaN is not isotropic, consequently leading to anisotropy in effective mass of the carriers. In the direction parallel to c axis, the electrons are heavier than in the perpendicular direction, with effective masses of  $m_{e,par}^* = 0.2 m_0$  and  $m_{e,perp}^* = 0.18 m_0$ , where  $m_0$  denotes the mass of a free electron. For comparison effective mass of electrons in Si  $m^* = 1.06 m_0$ , while in SiC  $m_{e,par}^* = 0.29 m_0$  and  $m_{e,perp}^* = 0.42 m_0$  [37] [38]. In addition, at the  $\Gamma$  point valence band of GaN is made up doubly degenerate band, corresponding to effective hole masses of  $m_{h,par}^* = 1.10 m_0$  and  $m_{h,perp}^* = 1.65 m_0$  and a split-off band with hole masses  $m_{h,par}^* = 0.15 m_0$  and  $m_{h,perp}^* = 1.10 m_0$  [39].

As the minimum of the conduction band and maximum of the valence band coincide at  $\Gamma$  point, wurtzite GaN is a direct band gap semiconductor. Based on experimental data collected for a wide range of semiconducting materials, breakdown electric field  $E_B$  for direct band gap semiconductors can be described according to an empirical formula as:

$$E_B \propto E_G^{2.5} \tag{2.1}$$

where  $E_G$  is the band gap [40] [41]. Thus, wide band gap semiconductors such as GaN are less susceptible to breakdown due to impact ionization, resulting in critical field of GaN of 3.3 MV/cm.

#### 2.1.2 Polarization Effects

Nitrogen, unlike gallium and other group III elements, is a highly electronegative element, which in combination with lack of inversion symmetry leads to formation of dipole in the unit cell of GaN. Thus, group III-V semiconductors possess strong polarization fields, which can be divided into two components: spontaneous and piezoelectric polarization. Spontaneous polarization ( $P_{SP}$ ) is a direct result of difference in electronegativity between Ga and N, where the effective Coulomb attraction of the N nucleus is greater than that of the metal leading to polarization along the [0001] direction in an unstrained crystal. Spontaneous polarization strongly depends on the molecular symmetry, with AlN exhibiting higher  $P_{SP}$  than GaN, due to increase in bond length and reduction in the c/a ratio (see Fig. 2.1a) [42]. III-V nitrides show positive correlation between deviation of lattice parameter ratios from the ideal closed packed hexagonal structure and the magnitude of spontaneous polarization [43].

Moreover, if the material is strained such that the ideal lattice parameters change, an additional component of polarization - piezoelectric polarization ( $P_{SP}$ ) will be induced in the lattice. Piezoelectric polarization can be described according to Hooke's law as:

$$P_{PZ,i} = \sum_{j} e_{ij} \varepsilon_{ij} \tag{2.2}$$

where  $e_{ij}$  denotes the piezoelectric constant and  $\epsilon_{ij}$  is the deformation potential. The total polarisation of a crystal  $P_{TOT}$  is simply defined as the sum of these two components:

$$P_{TOT} = P_{SP} + P_{PZ}.$$

(2.3)

Piezoelectric polarization is very sensitive to stress and plays an important role during pseudomorphic growth of III-V nitrides with different lattice constants, as the lattice mismatch will induce strain in the top layer. Thus, the total polarization can be affected by application of stress that results in change in dipole moment along the [0001] axis. Figure 2.3 shows variation in polarization of a heterostructure consisting of AlN and GaN (both materials have wurtzite lattice structure, but differ in lattice constant) with applied stress compared to unstrained free-standing GaN layer (Fig. 2.3a). If tensile stress is applied to AlN, then the total polarization increases due

Figure 2.3: Direction of spontaneous (red) and piezoelectric (blue) polarization vectors and polarization charges  $\sigma$  for **a**) free standing GaN, **b**) tensile-strained AlN on GaN and **c**) compressive-strained GaN on AlN.

to both  $P_{SP}$  and  $P_{PZ}$  acting along the same direction (Fig. 2.3b). On the other hand, if GaN is grown on top of AlN resulting in biaxial compressive strain, the negative polarization charge will accumulate at the heterointerface as the piezoelectric polarization acts in the opposite direction to spontaneous polarization vectors of AlN and GaN (Fig. 2.3c).

The example shown in Figure 2.3 demonstrates the importance of stress on the formation of polarization charges in heterostructures. Heterostructure is defined as a system consisting of two materials grown one on top of the other with different energy bandgap, which leads to formation of band offset at the interface due to discontinuity in valence and conduction bands. All the work presented in this thesis revolves around AlGaN/GaN heterostructure. AlGaN is an alloy created by addition of Al atoms to GaN. At first approximation, many physical properties of ternary compounds such as AlGaN can be determined using Vegard's law, which involves linear interpolation of property in question [44]. Vegard's law has been established empirically, and can be successfully applied to estimate parameters such as band gaps and lattice constant of various compound semiconductors [45] [46]. Thus, the bandgap of  $Al_xGa_{1-x}N$  would be expressed as:

$$E_{G}(x) = x E_{G}^{AlN} + (1 - x) E_{G}^{GaN}$$

(2.4)

where x denotes the molar fraction of Al in  $Al_xGa_{1-x}N$ , with  $E_G^{AlN} = 6.2 \text{ eV}$  and  $E_G^{GaN} = 3.4 \text{ eV}$ . Unfortunately, Vegard's law is an approximation and on closer inspection for a number of different materials Vegard's law shows significant discrepancy with the experimental results, thus other non-linear models have been proposed [47] [48]. Therefore, bandgap of a ternary compound such as AlGaN can be expressed more accurately by the equation:

$$E_G(x) = x E_G^{AlN} + (1 - x) E_G^{GaN} + b x (1 - x)$$

(2.5)

where the term bx(1-x) accounts for the curvature of the bandgap as a function of molar fraction x, with b denoting the bowing parameter [15].

Figure 2.4: Lattice constant and band gap relationship for GaN, AlN and InN material systems. Figure adapted from [49].

As suggested by Eq. 2.5 and shown in Figure 2.4, incorporation of Al into GaN leads to increase in bandgap of the alloy. The growth of AlGaN on GaN will therefore result in an abrupt interface between the two materials. In addition, increase in Al molar fraction causes the increase in lattice constant of AlGaN. Thus, AlGaN layer grown on top of Ga-face GaN will be under biaxial tensile strain, which means the directions of spontaneous and piezoelectric polarization will align creating a region of positive polarisation charge at the heterointerface  $\sigma$ , which can be expressed as [42]:

$$|\sigma| = |P_{PE,AlGaN} + P_{SP,AlGaN} - P_{SP,GaN}|.$$

$$(2.6)$$

Figure 2.5a shows the direction of different polarization components and distribution of polarization charges. The induced positive polarization charge at the interface between GaN and AlGaN attracts the electrons, which will concentrate at the top of GaN layer right at the very heterointerface, but will not enter the AlGaN layer as the difference in its bandgap relative to GaN will act as a barrier to these charges. This high concentration of negative charge carriers within a very small space is know as the 2D electron gas (2DEG). The source of these electrons is attributed to the donor like surface states at the top of the AlGaN layer. By releasing the electrons to form 2DEG, the Fermi level is pinned at the energy level of the surface donors, creating surface potential and internal electric field in AlGaN [50]. This process is schematically shown in Figure 2.5b.

Figure 2.5: **a**) Total polarization and resulting charges in a typical  $Al_xGa_{1-x}N/GaN$  heterostructure. **b**) Corresponding band diagram indicating the movement of electrons away from surface states towards heterointerface to form the 2DEG.

## 2.1.3 Phonon Dispersion

Figure 2.6: Schematic representation of a 1D lattice of atoms as balls on sprigs with spring constant K, with interatomic spacing of a and possible displacement of  $x_n$ .

Phonons represent vibrations in the crystal lattice resulting in displacement of atoms around their equilibrium position and are extremely helpful in understanding heat flow in solid materials. Figure 2.6 shows an infinite 1D monoatomic chain, with atoms represented as point masses and bonds as springs with the spring constant K. The displacement of the  $n^{th}$  atom in the chain can be described in relation to its neighbouring atoms by combining Newton's 2nd law and Hook's law according to the expression:

$$m\frac{d^2t}{dx^2} = K(x_{n+1} + x_{n-1} - 2x_n)$$

(2.7)

where  $x_i$  denotes the displacement of an atom at the position  $n_i$  and m denotes its mass. By solving the above differential equation, we obtain the dispersion relation for the vibrational frequency of the atoms  $\omega$ :

$$\omega = \sqrt{\frac{2K}{m}} \left| \sin\left(\frac{ka}{2}\right) \right| \tag{2.8}$$

where k stands for wavevector in the inverse space.

The solution to diatomic lattice of masses  $m_1$  and  $m_2$  can be obtained by solving simultaneous equations based on Eq. 2.7. Thus, the dispersion relation for this system becomes:

$$\omega^{2} = K \left( m_{1}^{-1} + m_{2}^{-1} \right) \pm K \sqrt{\left( m_{1}^{-1} + m_{2}^{-1} \right)^{2} - \frac{4sin^{2}(ka)}{m_{1}m_{2}}}.$$

(2.9)

At  $\Gamma$  point of the Brillouin zone k=0, which simplifies the above equation to:

$$\omega_{\Gamma} = \sqrt{K\left(m_1^{-1} + m_2^{-1}\right) \pm K\left(m_1^{-1} + m_2^{-1}\right)}.$$

(2.10)

Equation 2.9 implies there are two possible frequencies at  $\Gamma$ : one with  $\omega = 0$  and one with  $\omega = \sqrt{2K(m_1^{-1} + m_2^{-1})}$ . The phonon branch with zero energy is call the acoustic branch – this mode represents coherent movement of atoms in the lattice, while the branch with non-zero energy is call optical branch – these modes represent out-of-phase motion of adjacent atoms in the lattice. Figure 2.7 shows a wavevector-frequency dispersion relation for a diatomic chain of atoms. Although optical phonons display higher frequency oscillations, the group velocity of acoustic branch is much higher, meaning they are significantly more efficient in heat conduction in a semiconductor material.

Figure 2.7: **a**) Calculated wavevector-frequency curve for a diatomic 1D chain of atoms with two separate phonon branches: acoustic (blue) and optical (red). **b**) Full wavevector-frequency phonon dispersion for wurtzite GaN. Figure reprinted from [51] with the permission of APS.

In general, for a unit cell with N atoms there will be 3N phonon branches with 3 acoustic and 3N-3 optical branches. Phonon dispersion can either be obtained using computational methods (e.g. dynamic lattice calculations and density-functional perturbation theory) [51] [52] or measured using inelastic neutron scattering (suitable for large crystals), X-ray or Raman scattering [53]. Figure 2.7b shows a phonon dispersion for GaN with acoustic and optical modes separated by a gap, which in general case of III-V semiconductor will widen as the mass difference between the atoms increases.

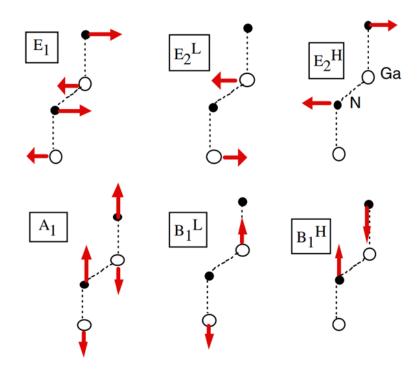

In a crystal structure phonon motions are characterised by their displacement vectors which are determined by the symmetry operation of the crystal. The symmetry operations of the crystal can be described using group theory. By assessing the symmetry of an infinite crystal in equilibrium it is possible to assign a space group, which for wurtzite structures is  $C_{6v}$  – indicating cyclic symmetry with 6-fold rotational axis. The phonon modes included in this point group include two  $A_1$  modes, two  $B_1$  modes, two  $E_1$  and further two  $E_2$ , all of which are marked in Fig. 2.7b. Further discussion of the phonon modes in GaN and their application for temperature measurements are presented in the next chapter.

Due to lack of spin, phonons are classified as bosons and as such they follow Bose-Einstein statistics. The population of phonons with an energy E at the temperature T can therefore be described according to the equation:

$$n(E,T) = \frac{1}{e^{\frac{E}{k_B T}} + 1}.$$

(2.11)

In addition, phonons do not follow Pauli exclusion principle and thus, as temperature tends to 0 K, phonons accumulate in their ground state resulting in no available heat carriers. As the temperature increases, when the thermal energy  $k_BT >> E$  the equation 2.11 tends to Rayleigh-Jeans limit:

$$n = \frac{k_B T}{E} \tag{2.12}$$

suggesting linear increase in thermal conductivity of the material with temperature. This idea was further developed in Debye model where by applying equipartition theorem to lattice vibrations in 3D, the variation of specific heat with temperature was derived. At temperatures above the Debye temperature  $T_D$  the specific heat tends to  $3k_B$  in agreement with Dulong-Petit law, as all the phonon modes are occupied and active. However, below  $T_D$  specific heat increases approximately as  $T^3$  due to increasing number of active phonons in the lattice. The Debye temperature can be describe according to:

$$T_D = \frac{hv}{2k_B} \sqrt{\frac{6N}{\pi V}}$$

(2.13)

where h, v, N and V are the Planck's constant, speed of sound, number of particle and volume respectively.  $T_D$  represents the temperature at which the highest vibrational mode of the lattice becomes active.

# 2.1.4 Heat Transport in Semiconductors

The process of heat diffusion in 1D can be described according to the equation:

$$J_x = -\kappa \frac{dT}{dx} \tag{2.14}$$

where  $J_x$  is the heat flux,  $\kappa_x$  is the thermal conductivity and  $\frac{dT}{dx}$  is the temperature gradient. By considering the kinetic theory of gases it can be demonstrated that the flux of particles in 1D can be described by  $0.5n_p < v_x >$ , where  $n_p$  is the concentration of particles and  $< v_x >$  is the mean velocity of particles. When a particle moves through a temperature gradient, the energy it released in the process is equal to  $c\Delta T$ , where c is the heat capacity of the particle and  $\Delta T$  is the difference between the starting and final temperature.

For particles travelling over a distance l under a thermal gradient, the flux J can be expressed as:

$$J = -\frac{1}{3}n_p < v^2 > lc\frac{dT}{dx} = -\kappa\frac{dT}{dx}.$$

(2.15)

Therefore, thermal conductivity can be described according to the expression:

$$\kappa = \frac{1}{3} cvl. \tag{2.16}$$

In semiconductors and insulators heat transport is mainly facilitated by phonons, with the thermal conductivity described by the equation 2.16, which implies its strong dependence on specific heat capacity of the phonons and their mean free path. At low temperatures, specific heat capacity increases as  $T^3$  according to Debye theorem as the phonons only scatter with the crystal boundaries and impurities in the lattice. Since collisions with the lattice and impurities do not change the momentum of individual phonons, they cannot bring about the thermal equilibrium. However, increase in temperature leads to anharmonicity in the lattice motion resulting in scattering of phonons with each other.

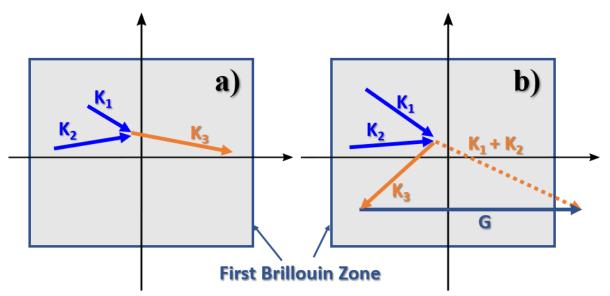

Figure 2.8: Two incoming phonons  $\vec{K_1}$  and  $\vec{K_2}$  scattering with one another. **a**) Normal scattering process - the resultant phonon  $\vec{K_3}$  is still within the first Brillouin zone. **b**) Umklapp scattering, where the resultant phonon ends up outside of the first Brillouin zone.

The two possible modes of phonon interactions with one another are called normal and Umklapp scattering. Normal scattering process can be described as a three-phonon collision according to:

$$\vec{K}_1 + \vec{K}_2 = \vec{K}_3 + \vec{G} \tag{2.17}$$

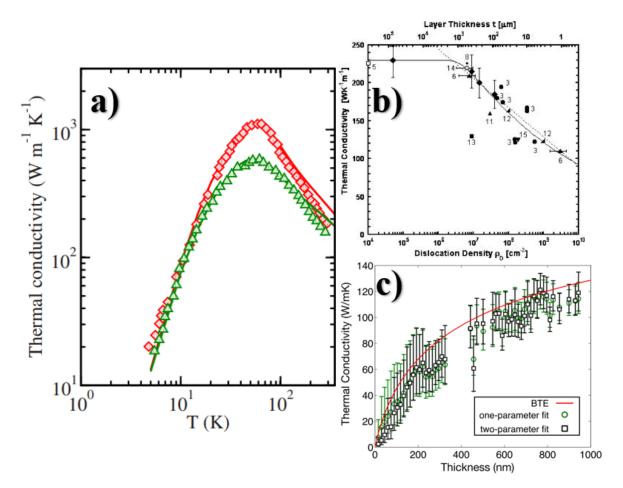

where  $\vec{K_1}$ ,  $\vec{K_2}$  and  $\vec{K_3}$  indicate the two interacting phonons and the resultant wavevector respectively, while  $\vec{G}$  represents the reciprocal lattice vector, which for a normal process is equal to 0 (see Figure 2.8a). For a perfect crystal normal scattering process does not lead to thermal equilibrium as the total phonon momentum remains the same. If, on the other hand, the resultant wavevector  $\vec{K_3}$  exists outside of the first Brillouin zone, it has to be mapped back with the reciprocal lattice vector  $\vec{G}$  as seen in Fig. 2.8b (see eq. 2.14 with  $\vec{G} \neq 0$ ). Umklapp processes lead to change in phonon momentum and therefore facilitate establishing of thermal equilibrium in the material. Umklapp scattering results in the thermal resistance of a material and as the lattice temperature approaches the Debye temperature, it leads to 1/T temperature dependence of thermal conductivity [54] [55]. Figure 2.9a shows as an example of measured variation in thermal conductivity of GaN with temperature.

## 2.1.5 Thermal Conductivity of GaN