# **ARCHITECTING SECURE PROCESSOR CACHES**

A Dissertation Presented to The Academic Faculty

By

Gururaj Saileshwar

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2022

© Gururaj Saileshwar 2022

# ARCHITECTING SECURE PROCESSOR CACHES

Thesis committee:

Dr. Moinuddin Qureshi, Advisor School of Computer Science *Georgia Institute of Technology*

Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Taesoo Kim School of Computer Science Georgia Institute of Technology Dr. Milos Prvulovic School of Computer Science Georgia Institute of Technology

Dr. Christopher Fletcher Department of Computer Science University of Illinois Urbana-Champaign

Date approved: July 8, 2022

Genius is one percent inspiration, ninety-nine percent perspiration

Thomas Alva Edison

To my parents

#### ACKNOWLEDGMENTS

This PhD has been a long journey and I wouldn't be at the finish line without all the help and support I received from my mentors, family, and friends.

#### **Mentors and Colleagues**

First, I am deeply thankful to my advisor Prof. Moinuddin Qureshi. I knew very little about doing good research before I started working with him. So, I am extremely grateful he took a bet on me when he first offered me an internship and then mentored me through my PhD all these years. All of my research accomplishments, I owe to Moin.

I am as grateful to my mentor from my undergraduate program at IIT-Bombay, Prof. Bipin Rajendran. Without Bipin's encouragement to apply to graduate school and his timely recommendation to Moin, I would not be where I am today.

A lot of what I learned at Georgia Tech, I learned from my colleagues in the Memory Systems Lab, who over the years became friends and family. I am extremely grateful for the mentorship of Prashant Nair (friend, philosopher and guide) and the companionship of Swamit Tannu (labmate, roommate, coffee-buddy) – the path through my PhD became considerably easier because I followed in your footsteps. The PhD journey has been extremely enjoyable thanks to the great company of other colleagues ahead of me (Chia-Chen Chou, Jian Huang, Vinson Young) and also those after me (Mohammad Arjomand, Poulami Das, Sanjay Kariyappa, Anish Saxena, Aditya Rohan, Ramin Ayanzadeh, Narges Alavisamani).

I am deeply thankful to my collaborators who have taught me a lot more than I could have learned on my own – Prof. Chris Fletcher, who mentored me when I was just starting my work on side channels, and Prof. Taesoo Kim, with whom I wrote my first security conference paper. I am also very grateful to Prof. Daniel Gruss who welcomed me to his group in TU Graz, Austria for a summer internship – I learned a lot about offensive security research from him and his students.

I am also thankful to all my internship mentors – Wendy Elsasser, Prakash Ramrakhyani, and Jose Joao at ARM Research, Ken Grewal at Intel Labs, Muntaquim Chowdhury at Microsoft, and Rick Boivie, Alper Buyuktosunoglu, and Tong Chen at IBM Research – their guidance, advice, and industry perspective helped me grow considerably as a researcher.

I feel fortunate to have had great mentor figures in the computer architecture community. I am thankful for all the conversations about research I have had with Mengjia Yan, who has been a guiding light for a better part of my PhD. I am also thankful to Akshitha Sriraman, Wenjie Xiong, Dimitrios Skarlatos, Nader Sehatbaksh, and Saugata Ghose, for their advice during my job search.

Lastly, I am grateful to my thesis committee – Prof. Tushar Krishna, Prof. Milos Prvulovic, Prof. Taesoo Kim, and Prof. Chris Fletcher – I am glad to have had their mentorship and their constructive feedback throughout the PhD.

#### **Friends and Well-Wishers**

This PhD journey seems unimaginable without the support of my close friends, Ananda Samajdar, Poulami Das, Moumita Dey, Divyakiran Kadiyala, and earlier in my PhD, Karthik Rao, Swamit Tannu, Amruta Vidwans, and Vinson Young. You guys have been there with me through all the ups and downs. Also, life in the US would not have been as joyful without the friendship of Jayant and Vrushali in the initial days in Atlanta, or the companionship of Gaurav, Bhowmick, and Akshat on road trips to national parks. Special thanks to Gaurav and Anushree for welcoming me to their home and giving me the comforts of home-cooked food as I write this thesis.

I would also like to thank some of my favorite coffee shops – Octane, Amelie's, East Pole, and Chattahoochee Coffee in Atlanta, Mozart's and Spokesman in Austin, Insomnia in Hillsboro, and Zoka and Milstead in Seattle – their WiFi and electricity supported the writing of several of my papers and their delicious Cortados fueled the ideas in those papers.

### Family

Lastly, my PhD would not have been possible without the relentless support and sacrifices from my family. I am forever thankful to my girlfriend and now-fiance, Anisha, for her support. She has been my rock throughout this journey, kept me grounded through the highs of paper acceptances and the lows of COVID, and helped me succeed in this endeavor.

I am also thankful to my brother, Siddesh. His early encouragement and support were instrumental in my going to graduate school and getting a PhD. He has been an inspiration and one of my biggest cheerleaders throughout this journey.

To my parents, I dedicate this thesis. They always encouraged me to follow my dreams; they supported my decision to quit my job and pursue graduate studies abroad. Through ups and downs, and in sickness and in health, they've continued their unwavering support and given me the courage to pursue my ambitions. I am forever indebted to them for the values they instilled in me, that kept me going throughout this PhD and in life. Amma and Appa – thank you for everything.

# TABLE OF CONTENTS

| Acknov    | vledgm        | ents                                                                         | v           |

|-----------|---------------|------------------------------------------------------------------------------|-------------|

| List of ' | <b>Fables</b> |                                                                              | <b>v</b> vi |

| List of ] | Figures       |                                                                              | /111        |

| Summa     | ry            |                                                                              | xiv         |

| Chapte    | r 1: Int      | roduction                                                                    | 1           |

| 1.1       | Under         | standing the Problem of Cache Side-Channel Attacks                           | 2           |

| 1.2       | Challe        | enges in Mitigating Cache Side-Channel Attacks                               | 2           |

| 1.3       | Goals         | of this Thesis                                                               | 4           |

| 1.4       | Thesis        | Statement                                                                    | 5           |

| 1.5       | Thesis        | Overview and Contributions                                                   | 5           |

|           | 1.5.1         | Developing the Fastest Cache Covert Channel Attack with Fewer<br>Limitations | 5           |

|           | 1.5.2         | Designing Principled Randomization-Based Defenses                            | 6           |

|           | 1.5.3         | Designing Scalable Cache-Partitioning Defenses                               | 7           |

|           | 1.5.4         | Securing Caches Against Transient Information Leakage                        | 7           |

| 1.6       | Organ         | ization of the thesis                                                        | 8           |

| Chapte            | r 2: Bac                                                                    | kground on Cache Attacks                                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1               | Cache (                                                                     | Organization in Modern Processors                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.2               | Cache S                                                                     | Side-Channel Attacks                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | 2.2.1                                                                       | Conflict-Based Cache Side-Channel Attacks                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | 2.2.2                                                                       | Shared-Memory Based Cache Side-Channel Attacks           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | 2.2.3                                                                       | Cache-Occupancy Based Side-Channel Attacks               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3               | Cache (                                                                     | Covert-Channel Attacks                                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | 2.3.1                                                                       | Attacks Exploiting Shared Memory                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | 2.3.2                                                                       | Attacks Exploiting Set Conflicts (Without Shared Memory) | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4               | Transie                                                                     | nt Execution Attacks                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5               | Goals o                                                                     | of this Thesis                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chante            | r 3. Stra                                                                   | eamline - a New Cache Covert Channel Attack              | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapte            | 1 5. 500                                                                    |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1               |                                                                             | t: Why Investigate Cache Covert Attack Capabilities?     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -                 | Context                                                                     |                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1               | Context<br>Key Ide                                                          | t: Why Investigate Cache Covert Attack Capabilities?     | 17<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.1<br>3.2        | Context<br>Key Ide<br>Backgro                                               | t: Why Investigate Cache Covert Attack Capabilities?     | 17<br>18<br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1<br>3.2        | Context<br>Key Ide<br>Backgro<br>3.3.1                                      | t: Why Investigate Cache Covert Attack Capabilities?     | 17<br>18<br>21<br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1<br>3.2        | Context<br>Key Ide<br>Backgro<br>3.3.1<br>3.3.2                             | t: Why Investigate Cache Covert Attack Capabilities?     | 17<br>18<br>21<br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1<br>3.2        | Context<br>Key Ide<br>Backgro<br>3.3.1<br>3.3.2<br>3.3.3                    | t: Why Investigate Cache Covert Attack Capabilities?     | <ol> <li>17</li> <li>18</li> <li>21</li> <li>21</li> <li>21</li> <li>21</li> <li>21</li> <li>21</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1<br>3.2        | Context<br>Key Ide<br>Backgro<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4           | t: Why Investigate Cache Covert Attack Capabilities?     | <ol> <li>17</li> <li>18</li> <li>21</li> <li>2</li></ol> |

| 3.1<br>3.2<br>3.3 | Context<br>Key Ide<br>Backgro<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Deep-D | t: Why Investigate Cache Covert Attack Capabilities?     | <ol> <li>17</li> <li>18</li> <li>21</li> <li>2</li></ol> |

|        | 3.4.3   | Access-Pattern to Tolerate Sender-Receiver Slack    | 28 |

|--------|---------|-----------------------------------------------------|----|

|        | 3.4.4   | Techniques to Bound Sender-Receiver Slack           | 32 |

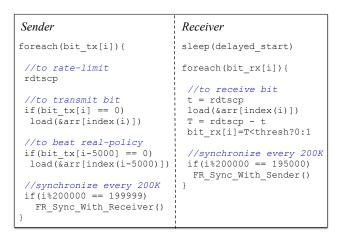

|        | 3.4.5   | Overall Algorithm for Streamline                    | 34 |

| 3.5    | Result  | s                                                   | 34 |

|        | 3.5.1   | Methodology                                         | 34 |

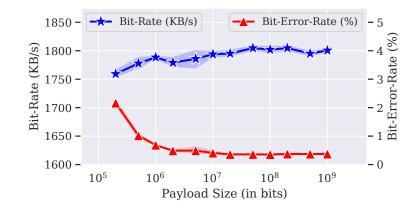

|        | 3.5.2   | Streamline Channel Bit Rate and Error Rate          | 35 |

|        | 3.5.3   | Analysis of Errors and Error-Correction             | 36 |

|        | 3.5.4   | Sensitivity to Shared Array Size                    | 37 |

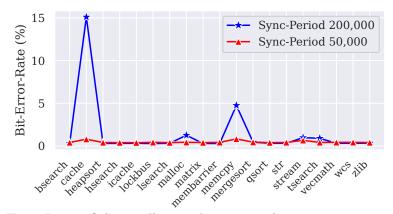

|        | 3.5.5   | Sensitivity to Synchronization Period               | 38 |

| 3.6    | Discus  | sion                                                | 39 |

|        | 3.6.1   | Resilience to System Noise                          | 39 |

|        | 3.6.2   | Limiter for Covert-Channel Bit-rate                 | 40 |

|        | 3.6.3   | Real-World Applicability                            | 41 |

| 3.7    | Compa   | arison with Prior Work                              | 42 |

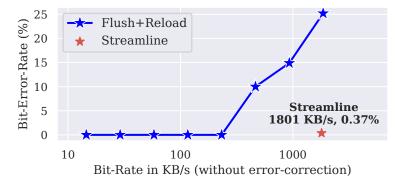

|        | 3.7.1   | Comparing Flush+Reload and Streamline               | 42 |

|        | 3.7.2   | Comparison with other Covert-Channels               | 43 |

| 3.8    | Mitiga  | tion Strategy                                       | 45 |

| 3.9    | Impact  | t of this Research                                  | 47 |

|        | 3.9.1   | Demonstrating Vulnerability of Existing Defenses    | 47 |

|        | 3.9.2   | New Cache Attacks and Defenses                      | 48 |

| Chante | r 4: MI | RAGE - A Fully-Associative Randomized Cache Defense | 49 |

| -      |         |                                                     |    |

| 4.1    | Contex  | t: Why Study Randomized Cache Defenses?             | 49 |

| 4.2 | Backg   | round: History of the Arms Race in Randomized Caches   | 51 |

|-----|---------|--------------------------------------------------------|----|

|     | 4.2.1   | Threat Model                                           | 51 |

|     | 4.2.2   | Eviction Set Discovery in Conflict-Based Cache Attacks | 51 |

|     | 4.2.3   | Advances in Attacks and Defenses                       | 51 |

|     | 4.2.4   | Goal: A Practical Fully-Associative LLC                | 53 |

| 4.3 | Design  | a: Full Associativity via MIRAGE                       | 54 |

|     | 4.3.1   | Overview of Mirage                                     | 54 |

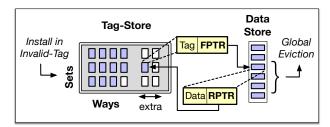

|     | 4.3.2   | Tag-to-Data Indirection and Extra Tags                 | 55 |

|     | 4.3.3   | Skewed-Associative Tag-Store Design                    | 56 |

|     | 4.3.4   | Load-Aware Skew Selection                              | 56 |

| 4.4 | Securi  | ty Analysis of Mirage                                  | 57 |

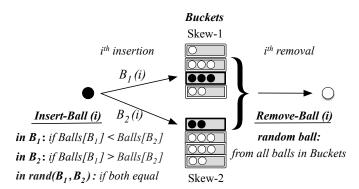

|     | 4.4.1   | Bucket-And-Balls Model                                 | 59 |

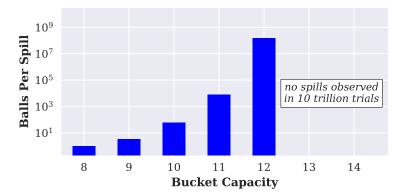

|     | 4.4.2   | Empirical Results for Frequency of Spills              | 60 |

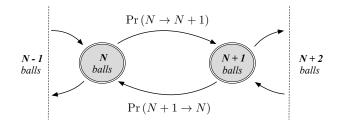

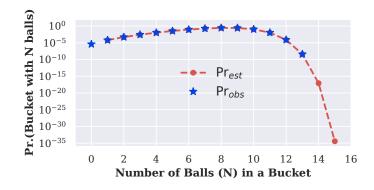

|     | 4.4.3   | Analytical Model for Bucket Spills                     | 61 |

|     | 4.4.4   | Analytical Results for Frequency of Spills             | 64 |

| 4.5 | Protect | ting against Shared-Memory Attacks                     | 65 |

| 4.6 | Discus  | sion                                                   | 66 |

|     | 4.6.1   | Requirements for Randomizing Function                  | 66 |

|     | 4.6.2   | Key Management in Mirage                               | 67 |

|     | 4.6.3   | Security for Sliced LLC Designs                        | 67 |

|     | 4.6.4   | Security as Baseline Associativity Varies              | 68 |

|     | 4.6.5   | Implications for Other Cache Attacks                   | 68 |

| 4.7 | Mirage  | e with Cuckoo-Relocation                               | 69 |

|      | 4.7.1   | Design of Cuckoo-Relocation                | 69 |

|------|---------|--------------------------------------------|----|

|      | 4.7.2   | Results: Impact of Relocation on SAE       | 70 |

|      | 4.7.3   | Security Implications of Relocation        | 71 |

| 4.8  | Perform | nance Analysis                             | 71 |

|      | 4.8.1   | Methodology                                | 71 |

|      | 4.8.2   | Synthesis Results for Cache Access Latency | 72 |

|      | 4.8.3   | Impact on Cache Misses                     | 73 |

|      | 4.8.4   | Impact on Performance                      | 74 |

|      | 4.8.5   | Sensitivity to Cache Size                  | 75 |

|      | 4.8.6   | Sensitivity to Cipher Latency              | 75 |

| 4.9  | Cost A  | nalysis                                    | 76 |

|      | 4.9.1   | Storage Overheads                          | 76 |

|      | 4.9.2   | Power Consumption Overheads                | 77 |

|      | 4.9.3   | Logic Overheads                            | 78 |

| 4.10 | Related | d Work                                     | 78 |

|      | 4.10.1  | Secure Caches with High Associativity      | 78 |

|      | 4.10.2  | Cache Associativity for Performance        | 80 |

|      | 4.10.3  | Isolation-based Defenses for Set-Conflicts | 81 |

| 4.11 | Key Co  | ontributions and Impact of this Research   | 81 |

|      | 4.11.1  | Key Contributions                          | 81 |

|      | 4.11.2  | Potential Impact of this Research          | 82 |

|      |         |                                            |    |

Chapter 5: Bespoke Cache Enclaves For Scalable Cache Partitioning .... 83

| 5.1 | Introd | uction                                     |

|-----|--------|--------------------------------------------|

| 5.2 | Backg  | ground on Cache Partitioning               |

|     | 5.2.1  | Threat Model                               |

|     | 5.2.2  | Prior Cache-Partitioning Based Defenses    |

|     | 5.2.3  | Goal: Scalable & Flexible LLC Isolation    |

| 5.3 | Desig  | n of Bespoke Cache Enclaves                |

|     | 5.3.1  | Overview of BCE                            |

|     | 5.3.2  | Cluster-Indirection Module: Maps Clusters  |

|     | 5.3.3  | Load-Balancing Hash: Maps Lines            |

|     | 5.3.4  | Software Interfaces to Request Clusters    |

|     | 5.3.5  | Putting it Together: BCE Operation         |

|     | 5.3.6  | Support Required from System Software      |

| 5.4 | Securi | ty Analysis                                |

| 5.5 | Evalua | ation Results                              |

|     | 5.5.1  | Methodology                                |

|     | 5.5.2  | Impact on Cache Misses                     |

|     | 5.5.3  | Impact on Performance                      |

|     | 5.5.4  | Sensitivity to Increase in LLC Latency     |

|     | 5.5.5  | Sensitivity of Performance to LLC Size     |

|     | 5.5.6  | Benefits of BCE's Fine-Grained Allocations |

|     | 5.5.7  | Storage Overheads                          |

| 5.6 | Relate | ed Work                                    |

|     | 5.6.1  | Cache-Partitioning for Security            |

|        | 5.6.2    | Cache-Partitioning for Performance                        |

|--------|----------|-----------------------------------------------------------|

|        | 5.6.3    | Alternative Cache Side-Channel Defenses                   |

| 5.7    | Key C    | ontributions and Impact of this Research                  |

|        | 5.7.1    | Key Contributions                                         |

|        | 5.7.2    | Potential Impact                                          |

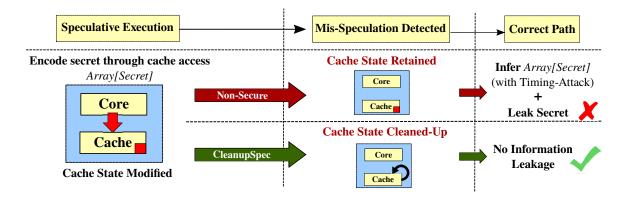

| Chapte | r 6: Cle | eanupSpec - Securing Caches Against Transient Leakage 111 |

| 6.1    | Introd   | uction                                                    |

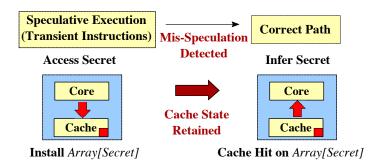

| 6.2    | Backg    | round and Motivation                                      |

|        | 6.2.1    | Threat Model                                              |

|        | 6.2.2    | Speculation-Based Attacks                                 |

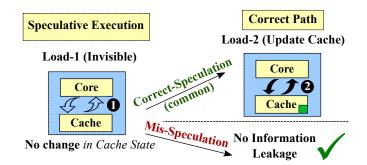

|        | 6.2.3    | InvisiSpec: A Prior Redo-Based Mitigation                 |

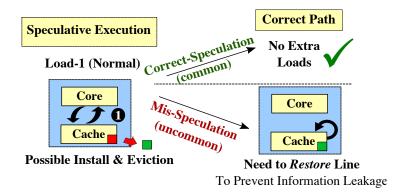

|        | 6.2.4    | Undo Approach: Benefits and Challenges                    |

|        | 6.2.5    | Goal of this Work                                         |

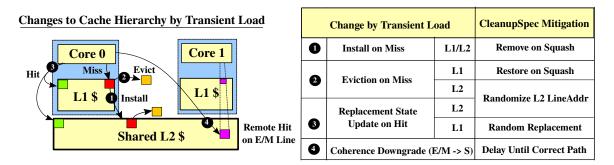

| 6.3    | Design   | n of CleanupSpec                                          |

|        | 6.3.1    | Overview of CleanupSpec Design                            |

|        | 6.3.2    | Randomizing L2 Lines & L1 Replacement                     |

|        | 6.3.3    | Removing L1 and L2 Installs                               |

|        | 6.3.4    | Restoring Lines Evicted due to L1 Installs                |

|        | 6.3.5    | Delaying Coherence State Downgrades                       |

|        | 6.3.6    | Protecting Installs in Speculation Window                 |

| 6.4    | Securi   | ty Analysis                                               |

| 6.5    | Experi   | imental Methodology                                       |

|         | 6.5.1   | Simulation Framework                    |

|---------|---------|-----------------------------------------|

|         | 6.5.2   | Workloads                               |

|         | 6.5.3   | Configuration                           |

| 6.6     | Result  | s                                       |

|         | 6.6.1   | Proof-of-concept Defense                |

|         | 6.6.2   | Performance                             |

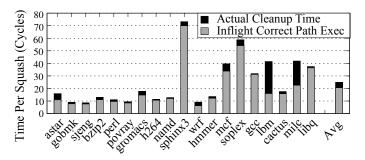

|         | 6.6.3   | Main Cause of Slowdown - Cleanup Stalls |

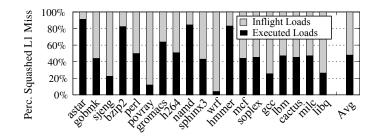

|         | 6.6.4   | Analysis of Loads Requiring Cleanup     |

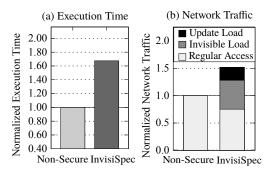

|         | 6.6.5   | Comparison with InvisiSpec              |

|         | 6.6.6   | Storage Overhead                        |

| 6.7     | Relate  | d Work                                  |

|         | 6.7.1   | Types of Speculation-Based Attacks      |

|         | 6.7.2   | Software and Microcode Based Defenses   |

|         | 6.7.3   | Hardware-Based Defenses                 |

| 6.8     | Potent  | ial Impact of this Research             |

| Chapte  | r 7: Co | nclusion and Future Work                |

| 7.1     | Conclu  | uding Remarks                           |

| 7.2     | Future  | e Works                                 |

| Referen | ices .  |                                         |

| Vita .  |         |                                         |

# LIST OF TABLES

| 2.1 | Prior Cache Covert Channels (Bit-Rate > 50 KB/s)                                                                                                                       | 14 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | LLC Miss-Rate for a Sequence accessing every $xth$ cacheline in a page, with $y$ pages accessed at a time. (Higher miss-rate implies sequence fools prefetcher better) | 30 |

| 3.2 | Breakup of Error-Rates for Different Payload Sizes                                                                                                                     | 37 |

| 3.3 | Streamline with and without Error-Correction (parenthesis includes margin-<br>of-error for 95% confidence interval)                                                    | 37 |

| 3.4 | Streamline with Different Shared Array Sizes (parenthesis includes margin-<br>of-error for 95% confidence interval)                                                    | 38 |

| 3.5 | Streamline with Different Synchronization Periods (parenthesis includes margin-of-error for 95% confidence interval)                                                   | 38 |

| 3.6 | Comparison with Prior Cache Covert Channels (Bit-Rate>50 KB/s) $\ldots$                                                                                                | 43 |

| 4.1 | Frequency of Set-Associative Eviction (SAE) in Mirage as extra ways per skew increase (assuming a baseline of 16-MB LLC with 16-ways and 1ns per install)              | 58 |

| 4.2 | Parameters for Buckets and Balls Modeling                                                                                                                              | 59 |

| 4.3 | Terminology used in the analytical model                                                                                                                               | 61 |

| 4.4 | Cacheline installs Per SAE in Mirage as the baseline associativity of the LLC tag-store varies                                                                         | 68 |

| 4.5 | Frequency of SAE in Mirage with 50% extra tags (4 extra ways/skew) as the number of relocation attempts increase                                                       | 70 |

| 4.6 | Baseline System Configuration                                                                                                                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7 | Average LLC MPKI of Mirage and Scatter-Cache                                                                                                                                                                                                 |

| 4.8 | Storage Overheads in Mirage for 64B line size                                                                                                                                                                                                |

| 4.9 | Energy and Power Consumption for Mirage                                                                                                                                                                                                      |

| 5.1 | Baseline System Configuration                                                                                                                                                                                                                |

| 5.2 | Average LLC MPKI for Non-Secure, DAWG, Page-Coloring, and BCE 102                                                                                                                                                                            |

| 5.3 | Storage Overheads for BCE Structures                                                                                                                                                                                                         |

| 6.1 | Performance Impact of Randomization for L2 (2MB) and Random Replacement for L1 DCache (64KB) vs LRU-Baseline                                                                                                                                 |

| 6.2 | Coherence state transitions in a remote core, caused due to actions initiated by transient instruction                                                                                                                                       |

| 6.3 | Workload Characteristics                                                                                                                                                                                                                     |

| 6.4 | System configuration (similar to InvisiSpec [34])                                                                                                                                                                                            |

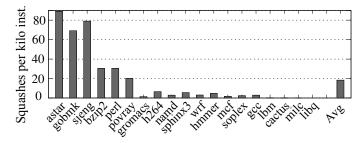

| 6.5 | Cleanup statistics – Squash per kilo instruction (PKI), Loads/Squash, State<br>of the load when squashed – Not issued (NI), L1-Hit (L1H), L2-Hit (L2H)<br>or L2-Miss (L2M). Cleanup is needed only for Squashed Loads that are<br>L2H or L2M |

| 6.6 | Overheads for CleanupSpec vs InvisiSpec, normalized to a Non-Secure baseline                                                                                                                                                                 |

# LIST OF FIGURES

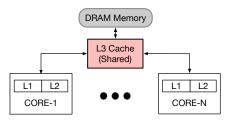

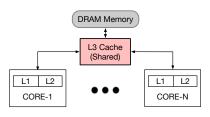

| 2.1 | Threat Model: Shared LLC is the focus of cache attacks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

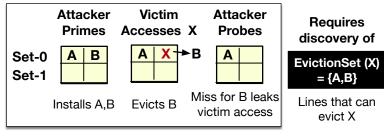

| 2.2 | Example of Conflict-Based Attack (Prime+Probe)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11 |

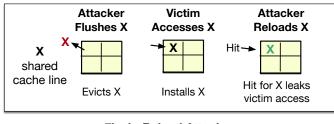

| 2.3 | Example of Shared-Memory-Based Attack (Flush+Reload)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12 |

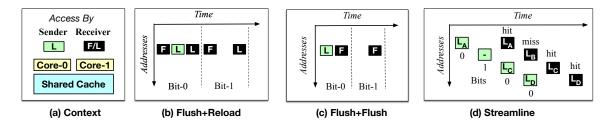

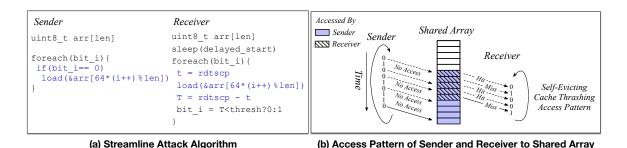

| 3.1 | (a) Cache covert-channel attacks allow the colluding sender and receiver processes to transmit information via timing differences on accesses to shared caches. (b,c) Prior covert-channel attacks require synchronized transmission and flushes (F) in addition to loads (L) for each bit sent between the sender and the receiver: this limits the channel bit-rates to 298 KB/s (Flush+Reload) and 498 KB/s (Flush+Flush). (d) In Streamline, the sender and receiver asynchronously communicate on a large sequence of addresses without flushes (each bit transmitted on a new address), achieving a bit-rate of 1801 KB/s. | 18 |

| 3.2 | State-of-the-art covert-channel attacks. All existing attacks require sender<br>and receiver to communicate each bit in a synchronized epoch and wait till<br>the epoch ends before starting the next bit. Cross-core attacks Flush+Reload<br>and Flush+Flush achieve bit-rates of 298KB/s and 496KB/s, while same-<br>core Take-a-way achieves 588 KB/s                                                                                                                                                                                                                                                                         | 22 |

| 3.3 | Overview of the Streamline Attack. The sender and receiver communicate asynchronously via accesses to a shared array arr (larger than the LLC). The sender keeps transmitting on sequential entries of the array, without waiting for the receiver to decode. By the time the sequential access wraps around to the start of the array, the entries accessed in the previous iteration are evicted from the LLC due to the cache-thrashing access pattern                                                                                                                                                                        | 25 |

| 3.4 | A naive channel encoding scheme causes a rate-mismatch between the sender and receiver. If the receiver goes ahead of the sender or falls too far behind, it observes erroneous LLC-Misses (in red), leading to errors                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |

| 3.5  | Modulating payload bits (PB- $i$ ) with a random sequence (PRNG- $i$ ) and then transmitting (TB- $i$ ) ensures the Receiver is slower than Sender (with equal LLC-misses, but more LLC-Accesses), regardless of payload values                                                                                                                              | 28 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

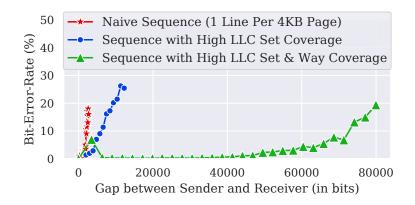

| 3.6  | Error-rate versus Sender-Receiver Gap. With a sequence of addresses that covers a majority of LLC sets and ways, Streamline builds considerable tolerance to slack between the sender and receiver                                                                                                                                                           | 31 |

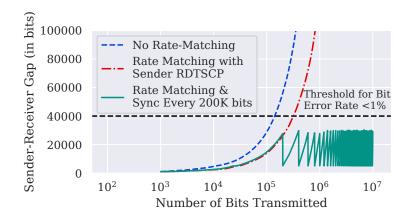

| 3.7  | Gap between Sender and Receiver vs Number of bits transmitted. Rate-<br>limiting the sender to match its rate with the receiver and using coarse-<br>grain synchronization to halt the sender every 200,000 bits, ensures the gap<br>is maintained below 40,000 bits (within this threshold, the error-rate stays<br>below 1%).                              | 33 |

| 3.8  | Algorithm for Sender and Receiver in Streamline to achieve fast and asyn-<br>chronous communication, incorporating techniques to ensure low error-rates.                                                                                                                                                                                                     | 34 |

| 3.9  | Covert-channel Bit-rate and Bit-error-rate vs Payload Size (shaded regions represent 95% CI, <i>i.e.</i> confidence intervals). Streamline has a bit-rate of 1801 KB/s at an error-rate of 0.37% (note the non-zero start of the Y-Axis for bit-rate).                                                                                                       | 36 |

| 3.10 | Error-Rate of Streamline under co-running stress-ng workloads, for sender-receiver synchronization periods of 200,000 and 50,000 bits                                                                                                                                                                                                                        | 40 |

| 3.11 | Bit-rate and bit-error-rate (without error-correction) of Flush+Reload attack versus Streamline                                                                                                                                                                                                                                                              | 43 |

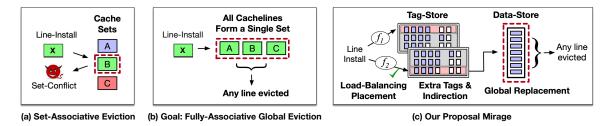

| 4.1  | (a) Traditional LLCs have set-associative evictions (SAE) which leak in-<br>formation of installed addresses. (b) MIRAGE provides Global Evictions<br>(GLE) to provide an abstraction similar to a fully-associative cache to elim-<br>inate this information leakage. (c) Mirage enables GLEs and eliminates<br>SAEs with practical set-associative lookups | 50 |

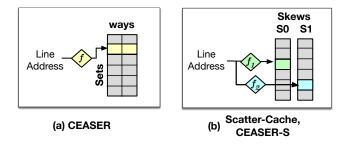

| 4.2  | Recent Works on Randomized Caches                                                                                                                                                                                                                                                                                                                            | 52 |

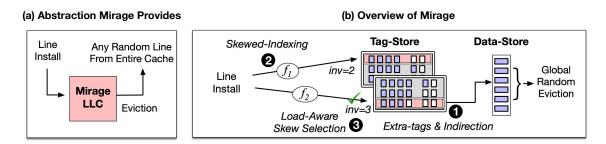

| 4.3  | (a) Mirage provides the abstraction of a fully-associative design with glob-<br>ally random evictions. (b) It achieves this by using extra tags and indi-<br>rection between tags and data blocks, skewed indexing, and load-aware<br>skew-selection.                                                                                                        | 54 |

| 4.4  | Overview of the cache substrate used by Mirage with indirection and extra tags (inspired by V-Way Cache).                                                                                                                                                                                                                                                    | 56 |

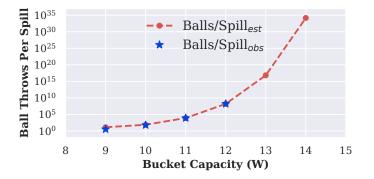

| 4.5  | Buckets-and-balls model for Mirage with 32K buckets (divided into 2 skews), holding 256K balls in total to model a 16MB cache. The bucket capacity is varied from 8-to-14 to model 8-to-14 ways per skew in Mirage                                                                                                                                                                                            | 59 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6  | Frequency of bucket spills, as bucket capacity is varied. As bucket-capacity increases from 8 to 14 (i.e. extra-tags per set increase from 0% to 75%), bucket spills (equivalent to SAE) become more infrequent.                                                                                                                                                                                              | 60 |

| 4.7  | Bucket state modeled as a Birth-Death chain, a Markov Chain where the state variable $N$ (number of balls in a bucket) increases or decreases by one at a time, due to a birth (insertion) or death (deletion) of a ball                                                                                                                                                                                      | 61 |

| 4.8  | Probability of a Bucket having N balls – Estimated analytically $(Pr_{est})$ and Observed $(Pr_{obs})$                                                                                                                                                                                                                                                                                                        | 63 |

| 4.9  | Frequency of bucket-spill, as bucket-capacity varies – both analytically estimated (Balls/Spill <sub>est</sub> ) and empirically observed (Balls/Spill <sub>obs</sub> ) results are shown.                                                                                                                                                                                                                    | 64 |

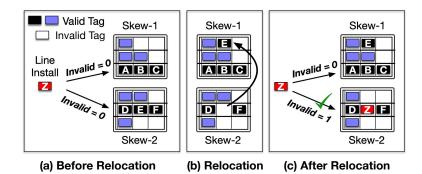

| 4.10 | Cuckoo Relocation, a technique to avoid an SAE if Mirage is implemented with 50% extra tags.                                                                                                                                                                                                                                                                                                                  | 70 |

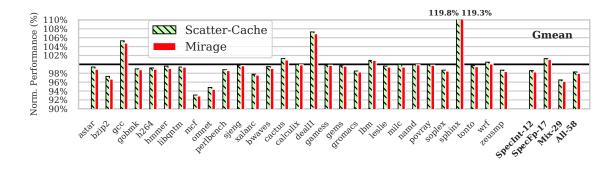

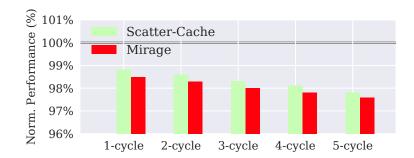

| 4.11 | Performance of Mirage and Scatter-Cache normalized to Non-Secure Base-<br>line (using weighted speedup metric). Over 58 workloads, Mirage has a<br>slowdown of 2%, while Scatter-Cache has a slowdown of 1.7% compared<br>to the Non-Secure LLC.                                                                                                                                                              | 74 |

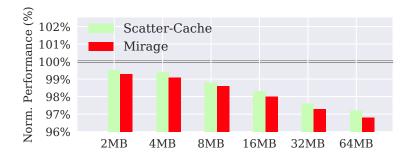

| 4.12 | Sensitivity of Performance to Cache-Size.                                                                                                                                                                                                                                                                                                                                                                     | 75 |

| 4.13 | Sensitivity of Performance to Cipher Latency.                                                                                                                                                                                                                                                                                                                                                                 | 76 |

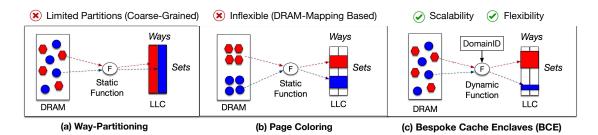

| 5.1  | (a) Prior way-partitioning solutions provide few partitions, restricted by the LLC associativity (b) Prior page-coloring solutions have finer allocations but do not allow flexible use of DRAM and LLC in different ratios. (c) Our solution BCE seeks to allow a large number of fine-grained cache allocations and flexible memory usage, with dynamic indexing to guide lines to allocated cache regions. | 85 |

| 5.2  | Threat model focuses on shared LLC attacks.                                                                                                                                                                                                                                                                                                                                                                   | 85 |

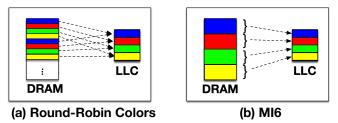

| 5.3  | Page-coloring based cache partitioning. (a) Typical schemes assign con-<br>secutive colors to consecutive physical pages. (b) MI6 [14] partitions the<br>DRAM and cache sets into 64 contiguous regions and assigns a DRAM and<br>cache region a single color.                                                                                                                                                | 87 |

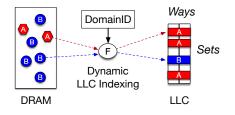

| 5.4  | Overview of BCE Capabilities. BCE allows a configurable number of LLC clusters to be allocated to each domain, independent of memory allocations.                                                                                                                                                                                    | 89  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

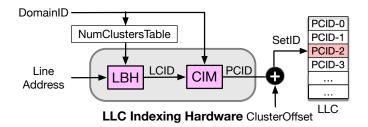

| 5.5  | Overview of BCE Cache Indexing. The Load-Balancing Hash (LBH) uni-<br>formly hashes addresses among Logical Clusters of a Domain (LCID) and<br>the Cluster-Indirection Module (CIM) maps LCIDs to Physical Cluster IDs<br>(PCIDs) of the LLC. PCID and the cluster-offset together form the set in-<br>dex.                          | 90  |

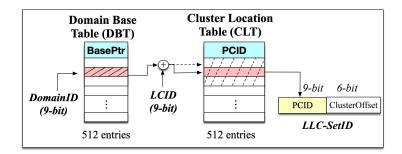

| 5.6  | Design of the CIM. The DBT provides the base entry location (LCID-0) of a domain in the CLT. The base location added to the LCID, points to the CLT-entry containing the required PCID.                                                                                                                                              | 92  |

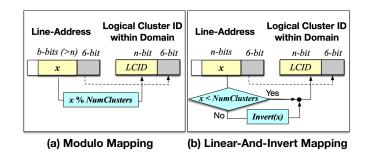

| 5.7  | Candidates for LBH (mapping addresses to LCID): (a) Modulo mapping is uniform but requires multi-cycle hardware implementation. (b) Linear-And-Invert mapping is single-cycle but results in imbalance.                                                                                                                              | 94  |

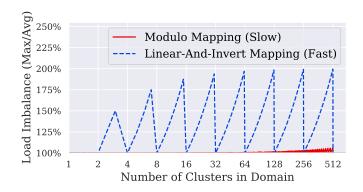

| 5.8  | Load imbalance with Modulo and Linear-And-Invert mappings as the num-<br>ber of clusters in a domain varies from 1 to 512. Modulo is close to ideal<br>but slow. Linear-And-Invert is fast but has up to 2x imbalance                                                                                                                | 94  |

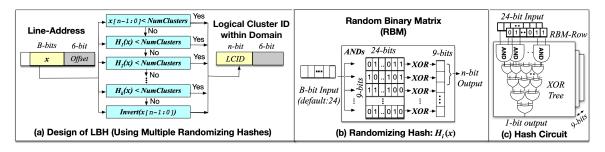

| 5.9  | Design of Load-Balancing Hash (LBH). (a) Mapping of line addresses to LCID via multiple randomizing hashes (b) Implementation of randomizing hash $H_i(x)$ using Random-Binary-Matrix (RBM) (c) Hash Circuit Logic: Circuit has a critical path of 1 AND and 4 XORs (three 2 input and one 3-input in XOR Tree).                     | 95  |

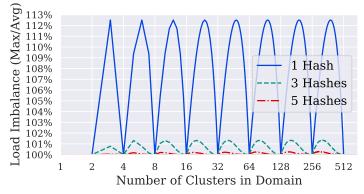

| 5.10 | Load Imbalance with LBH using multiple randomizing hashes (24-bits of line address as input) as the number of clusters in a domain varies from 1 to 512. With 3–5 hash functions, imbalance is within 1% of ideal.                                                                                                                   | 96  |

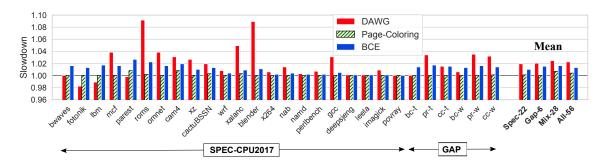

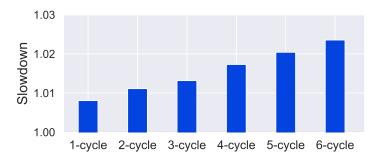

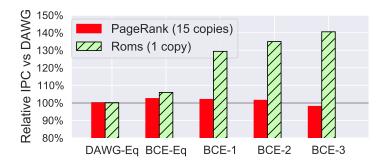

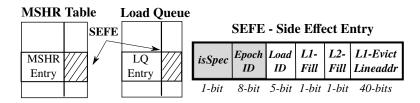

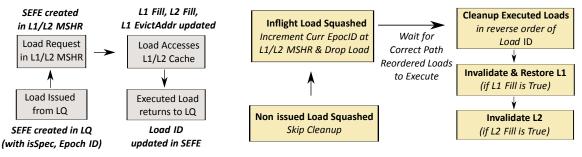

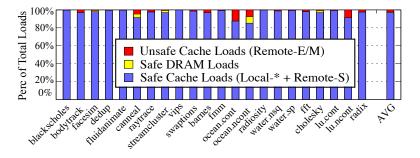

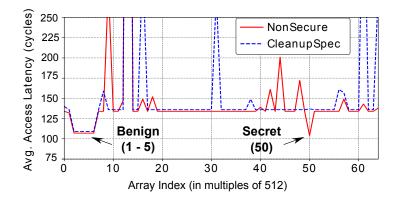

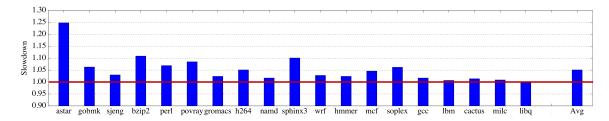

| 5.11 | Slowdown of BCE compared with DAWG [16] and Page-Coloring [15].<br>All numbers are normalized to a Non-Secure baseline without partition-<br>ing. Across 56 workloads (sorted high to low by MPKI in SPEC and GAP<br>suites), BCE has an average slowdown of 1.3%, while DAWG and Page-<br>Coloring have slowdowns of 2.2% and 0.4%. | 103 |