## DOMAIN-AWARE GENETIC ALGORITHMS FOR HARDWARE AND MAPPING OPTIMIZATION FOR EFFICIENT DNN ACCELERATION

A Dissertation Presented to The Academic Faculty

By

Sheng-Chun Kao

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Georgia Institute of Technology Department of Electrical and Compute Engineering

Georgia Institute of Technology

August 2022

© Sheng-Chun Kao 2022

## DOMAIN-AWARE GENETIC ALGORITHMS FOR HARDWARE AND MAPPING OPTIMIZATION FOR EFFICIENT DNN ACCELERATION

Thesis committee:

Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Callie Hao School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Vivek Sarkar School of Computer Science *Georgia Institute of Technology*  Dr. Alexey Tumanov School of Computer Science *Georgia Institute of Technology*

Dr. Angshuman Parashar Research Scientist NVIDIA

Dr. Suvinay Subramanian Senior Software Engineer *Google*

Date approved: May 16, 2022

#### ACKNOWLEDGMENTS

First of all, I would like to thank my advisor, Professor Tushar Krishna for the guidance and support during my PhD journey in the past four years. I learn many technical skills and also the great characteristics of being a researcher: commitment, passion, curiosity, endeavors, and so on. I am truly grateful to have him as my advisor and mentor. In my PhD journey, there are ups and downs. He is the one I can always count on, who is giving me endless support, keeping my chin up, and always cheering for me. I also learn many life advice from him. I sincerely appreciate him for being a great role model I could learn from.

I would like to pay special thanks to my mentor and collaborator throughout my PhD journey, Dr. Suvinay Subramanian. I learn many technical insights and life advice from you. My PhD journey could not be completed without your guidance.

I would like to pay special thanks to my collaborators in different exciting projects, Dr. Michael Pellauer, Dr. Angshuman Parashar, Dr. Po-An Tsai, Dr. Amir Yazdanbakhsh, Gaurav Agrawal, Dr. Shivani Agrawal, and Dr. Arun Ramamurthy. I appreciate for invaluable learning opportunities and countless hours for discussing research ideas, which led to major contributions of this thesis.

I would like to thank Dr. Hyoujhun Kwon for mentoring me in my first year of PhD and helps me understand MAESTRO thoroughly which opens up many research opportunities in my PhD. I would like to thanks Yannan (Nellie) Wu for all the help and discussion about Timeloop via emails. I thank all the members in Synergy Lab for collaborating and helping out for different tasks.

I would like to thank Dr. Tushar Krishna , Dr. Vivek Sarkar, Dr. Alexey Tumanov, Dr. Callie Hao, Dr. Angshuman Parashar, and Dr. Suvinay Subramanian for taking out time to serve on my thesis committee.

Lastly, I would like to thank my parents and family for their unconditional and endless support.

# TABLE OF CONTENTS

| Acknow    | vledgmo  | ents                                                              | iii |

|-----------|----------|-------------------------------------------------------------------|-----|

| List of ' | Tables   | • • • • • • • • • • • • • • • • • • • •                           | xii |

| List of ] | Figures  |                                                                   | XV  |

| Summa     | nry      |                                                                   | iii |

| Chapte    | r 1: Int | roduction                                                         | 1   |

| 1.1       | Challe   | nges                                                              | 2   |

|           | 1.1.1    | Linkage between HW Accelerator Flexibility and Map Space          | 2   |

|           | 1.1.2    | Efficient Mapper                                                  | 3   |

|           | 1.1.3    | Scalability of MSE                                                | 3   |

|           | 1.1.4    | Mapping and HW Co-exploration                                     | 4   |

| 1.2       | Thesis   | Contributions                                                     | 5   |

|           | 1.2.1    | Flexion: Accelerator Flexibility and Map Space                    | 5   |

|           | 1.2.2    | Gamma: Efficient DNN Mapper                                       | 5   |

|           | 1.2.3    | Demystifying MSE: Techniques for Improving the Scalability of MSE | 6   |

|           | 1.2.4    | DiGamma: Mapping and HW Co-exploration                            | 6   |

|           | 1.2.5    | MAGMA: Mapping across Multi-Accelerators                          | 7   |

|        | 1.2.6 ConfuciuX: Automated DNN Accelerator Design                                                | 8  |

|--------|--------------------------------------------------------------------------------------------------|----|

|        | 1.2.7 FLAT: Dataflow Technique for Mapping Attention Operation                                   | 8  |

| 1.3    | Thesis Statement                                                                                 | 9  |

| 1.4    | Thesis Overview                                                                                  | 9  |

| Chapte | r 2: Background                                                                                  | 12 |

| 2.1    | DNN Workloads                                                                                    | 12 |

| 2.2    | Accelerator Hardware Configuration                                                               | 13 |

| 2.3    | Dataflow and Mapping                                                                             | 14 |

| 2.4    | The Impact of Mapping                                                                            | 15 |

|        | 2.4.1 Optimal Mappings                                                                           | 15 |

|        | 2.4.2 Efficient Mappings Example                                                                 | 15 |

|        | 2.4.3 Performance-efficient v.s. Energy-efficient Mappings                                       | 18 |

|        | 2.4.4 Map Space Exploration                                                                      | 21 |

| 2.5    | DNN Accelerator Cost Model                                                                       | 21 |

| 2.6    | Optimization Methods                                                                             | 22 |

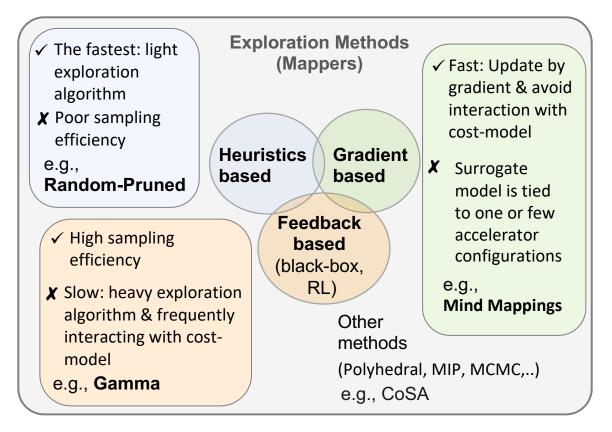

|        | 2.6.1 Heuristics-based                                                                           | 23 |

|        | 2.6.2 Feedback-based                                                                             | 23 |

|        | 2.6.3 Gradient-based                                                                             | 27 |

| 2.7    | Summary                                                                                          | 27 |

| Chapte | r 3: Flexion: A Formalism of DNN Accelerator Flexibility and the Impli-<br>cation of Map Space 2 | 28 |

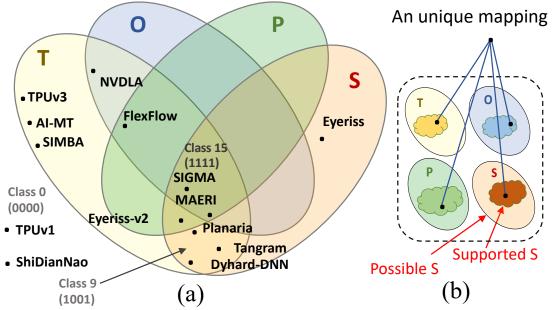

| 3.1    | Axes of Accelerator Flexibility                                                                  | 29 |

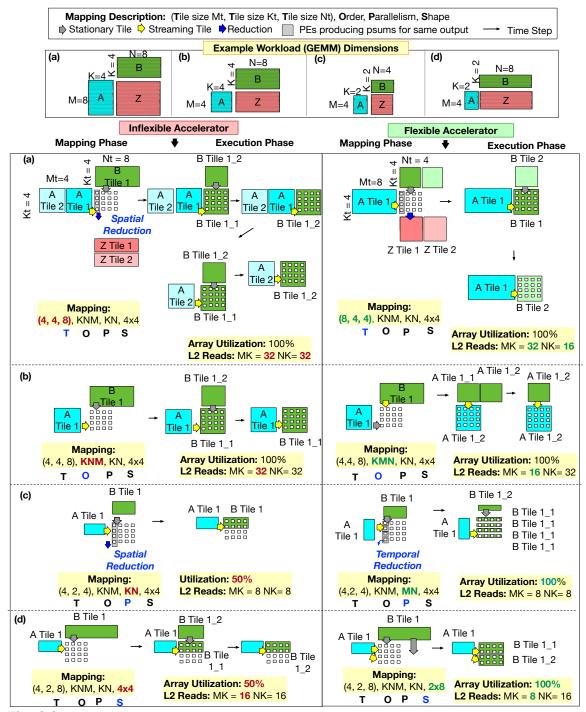

|        | 3.1.1    | Axes Taxonomy                                | 30 |

|--------|----------|----------------------------------------------|----|

|        | 3.1.2    | Classes of Accelerator Flexibility           | 33 |

|        | 3.1.3    | Benefits of Mapping Flexibility Per Axis     | 33 |

|        | 3.1.4    | Hardware Support for Flexibility Per Axis    | 35 |

| 3.2    | Formal   | Flexibility-Constrained Map Space Definition | 37 |

|        | 3.2.1    | Definitions of Map Space and Flexibility     | 37 |

|        | 3.2.2    | Full and Partial Flexibility                 | 39 |

| 3.3    | Flexibi  | lity-Aware Design-Space Exploration          | 40 |

| 3.4    | Evalua   | tion I: Isolation Study on Flexibility Axes  | 41 |

|        | 3.4.1    | Methodology                                  | 42 |

|        | 3.4.2    | Isolation: Tile Flexibility                  | 43 |

|        | 3.4.3    | Isolation: Order Flexibility                 | 47 |

|        | 3.4.4    | Isolation: Parallelism Flexibility           | 47 |

|        | 3.4.5    | Isolation: Shape Flexibility                 | 49 |

| 3.5    | Evalua   | tion II: Accelerator Future-Proofing         | 52 |

| 3.6    | Related  | d Work                                       | 55 |

| 3.7    | Summa    | ary                                          | 55 |

| Chapte | r 4: Gar | nma: A GA-based Mapper                       | 57 |

| 4.1    | Challer  | nges with Baseline Methods                   | 58 |

| 4.2    | Genetic  | c Algorithms (GA)                            | 58 |

| 4.3    | Method   | dology                                       | 59 |

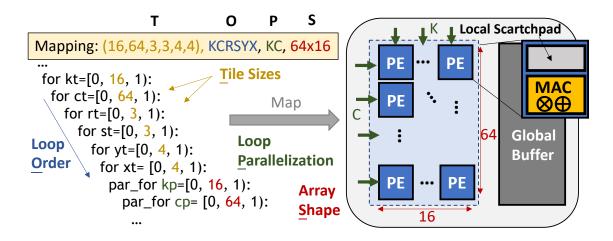

|        | 4.3.1    | GAMMA Encoding scheme                        | 59 |

|       | 4.3.2     | Decoding Genomes into a Mapping                                 | 60 |

|-------|-----------|-----------------------------------------------------------------|----|

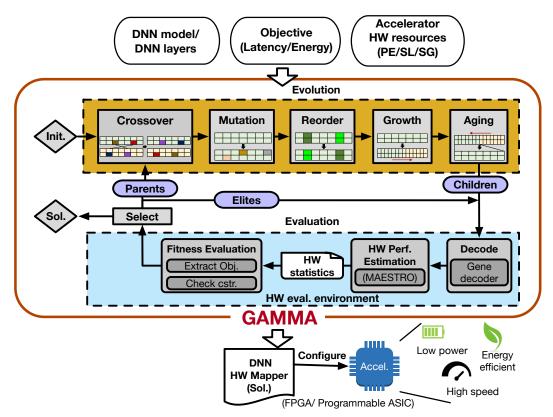

|       | 4.3.3     | Algorithm Flow                                                  | 63 |

|       | 4.3.4     | Flow for Automated Mapping Search                               | 64 |

| 4.4   | 4 Evalua  | ation of GAMMA                                                  | 65 |

|       | 4.4.1     | Target Search Methods and Parameters                            | 66 |

|       | 4.4.2     | S1: Fixed 2D Accel.                                             | 66 |

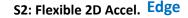

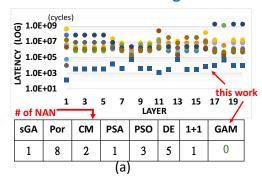

|       | 4.4.3     | S2: Flexible 2D Accel                                           | 69 |

|       | 4.4.4     | S3: Scale-out Flexible 2D Accel                                 | 70 |

|       | 4.4.5     | Two-stage Optimization for Inter-layer                          | 73 |

| 4.5   | 5 Relate  | d Works                                                         | 75 |

|       | 4.5.1     | Dataflow Design in DNN Accelerators                             | 75 |

|       | 4.5.2     | HW Mapping Space Search and Exploration                         | 75 |

| 4.6   | 5 Summ    | ary                                                             | 76 |

| Chapt | ter 5: De | mystifying Map Space Exploration and the Improvement Techniques | 77 |

| 5.1   | Map S     | Space Exploration (MSE)                                         | 78 |

|       | 5.1.1     | Evaluation Method (Cost Model)                                  | 79 |

|       | 5.1.2     | Representation                                                  | 80 |

|       | 5.1.3     | Exploration Method (Mapper)                                     | 80 |

|       | 5.1.4     | Why MSE Matters                                                 | 81 |

| 5.2   | 2 Quant   | itative MSE Analysis                                            | 82 |

|       | 5.2.1     | Methodology                                                     | 82 |

|       | 5.2.2     | Size of Map Space                                               | 84 |

|        | 5.2.3    | Understanding Mapper Sampling Efficiency          |

|--------|----------|---------------------------------------------------|

|        | 5.2.4    | Understanding Mapper Search Operators             |

|        | 5.2.5    | Understanding Sparse Accelerator Mappings         |

|        | 5.2.6    | Lessons Learnt                                    |

| 5.3    | Improv   | ving MSE                                          |

|        | 5.3.1    | Warm-start                                        |

|        | 5.3.2    | Sparsity-aware MSE                                |

| 5.4    | Relate   | d Works                                           |

| 5.5    | Summ     | ary                                               |

| Chapte | r 6: Di( | Gamma: A HW-Mapping Co-exploration Mapper 107     |

| 6.1    | Techni   | ical Approach                                     |

|        | 6.1.1    | High-level Overview                               |

|        | 6.1.2    | HW-Mapping Co-optimization Framework              |

|        | 6.1.3    | Encoding of Design Point                          |

| 6.2    | Optim    | ization Algorithm                                 |

|        | 6.2.1    | Leveraging Existing Algorithms                    |

|        | 6.2.2    | Background of Genetic Algorithm                   |

|        | 6.2.3    | DiGamma: Domain-aware Genetic Algorithm           |

| 6.3    | Evalua   | ations                                            |

|        | 6.3.1    | Setup                                             |

|        | 6.3.2    | Comparisons with Baseline Optimization Algorithms |

|        | 6.3.3    | Comparisons with Baseline HW-Mapping Schemes      |

|        | 6.3.4   | Explanation of Found Solutions                       | . 122 |

|--------|---------|------------------------------------------------------|-------|

| 6.4    | Relate  | d Work                                               | . 122 |

| 6.5    | Summ    | ary                                                  | . 123 |

| Chapte | r 7: MA | AGMA: A GA-based Mapper for Multi-accelerator System | . 124 |

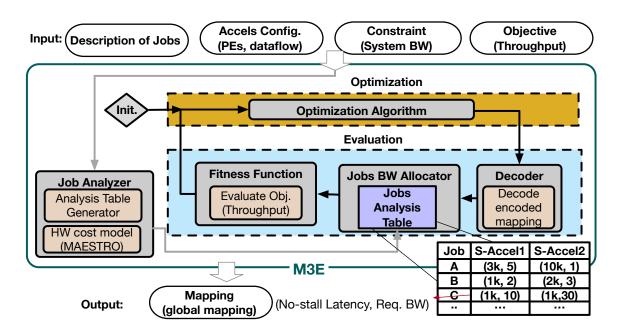

| 7.1    | Optim   | ization Framework (M3E)                              | . 125 |

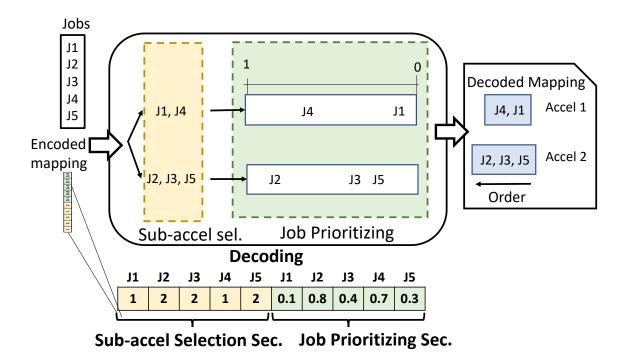

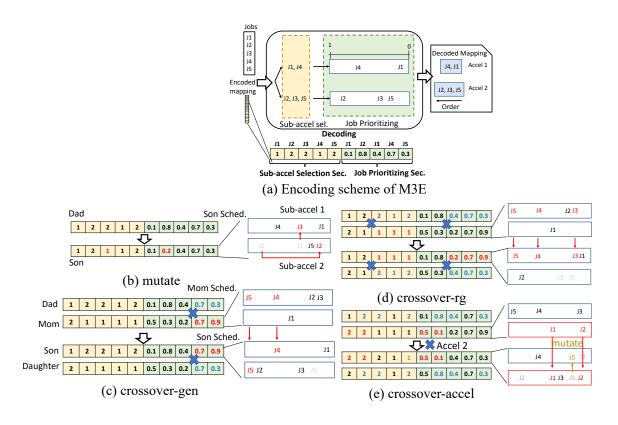

|        | 7.1.1   | Encoding                                             |       |

|        |         |                                                      |       |

|        | 7.1.2   | Optimization Algorithms Supported                    | . 126 |

|        | 7.1.3   | Objective and Constraints                            | . 127 |

|        | 7.1.4   | Building Blocks of M3E                               | . 128 |

|        | 7.1.5   | M3E Workflow                                         | . 130 |

|        | 7.1.6   | Search Space                                         | . 131 |

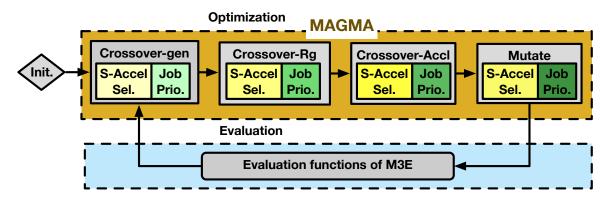

| 7.2    | Optim   | ization Algorithm (MAGMA)                            | . 131 |

|        | 7.2.1   | Why GA?                                              | . 133 |

|        | 7.2.2   | MAGMA Algorithm Details                              | . 133 |

|        | 7.2.3   | Warm-Start of MAGMA                                  | . 136 |

| 7.3    | Evalua  | ations                                               | . 137 |

|        | 7.3.1   | Methodology                                          | . 137 |

|        | 7.3.2   | Mapper Settings.                                     | . 139 |

|        | 7.3.3   | Latency-BW Characteristics of DNNs                   | . 140 |

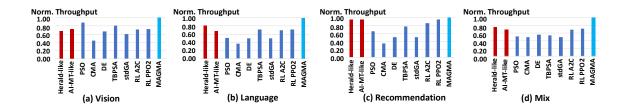

|        | 7.3.4   | Homogeneous Accelerators                             | . 141 |

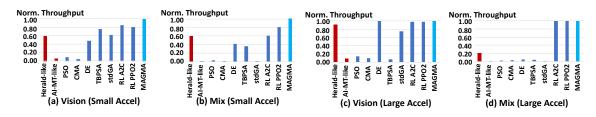

|        | 7.3.5   | Heterogeneous Accelerators                           | . 142 |

|        | 7.3.6   | Flexible Accelerator                                 | . 145 |

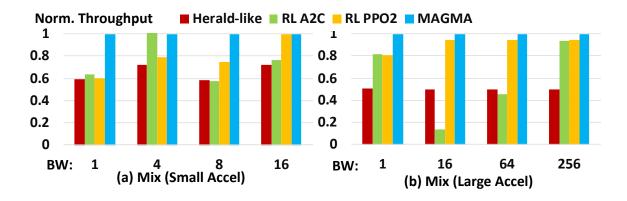

|        | 7.3.7  | More about MAGMA Algorithm                               |

|--------|--------|----------------------------------------------------------|

| 7.4    | Relate | 2d Works                                                 |

| 7.5    | Summ   | ary                                                      |

| Chapte |        | nfuciuX: A RL-based HW Resource Allocation Algorithm for |

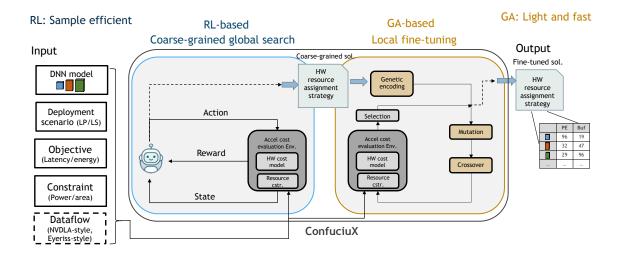

| 8.1    | Metho  | odology                                                  |

|        | 8.1.1  | DNN Model Deployment on Accelerators                     |

|        | 8.1.2  | RL Agent                                                 |

|        | 8.1.3  | Observation (State)                                      |

|        | 8.1.4  | Action Space                                             |

|        | 8.1.5  | Platform Constraint and Objective                        |

|        | 8.1.6  | Reward Function                                          |

|        | 8.1.7  | Interactive Environment (Env)                            |

|        | 8.1.8  | Local fine-tuning using GA                               |

| 8.2    | Evalua | ations of ConfuciuX                                      |

|        | 8.2.1  | Methodology                                              |

|        | 8.2.2  | Per-layer study for LS deployment                        |

|        | 8.2.3  | LP Deployment                                            |

|        | 8.2.4  | Dataflow-HW co-automation                                |

|        | 8.2.5  | Benefit of Two-stage Optimization                        |

|        | 8.2.6  | LP deployment at compile time                            |

|        | 8.2.7  | Policy Network Exploration                               |

|        | 8.2.8  | Summary                                                  |

| 8.3     | Relate  | d Works                                                               |

|---------|---------|-----------------------------------------------------------------------|

| 8.4     | Summ    | ary                                                                   |

| Chapte  | r 9: Co | nclusions and Future Works                                            |

| 9.1     | Summ    | ary of Contributions                                                  |

|         | 9.1.1   | Formalism of DNN Accelerator Flexibility and the Implied Map Space180 |

|         | 9.1.2   | Deep Analysis and Improvement of MSE for DNN Workloads 181            |

|         | 9.1.3   | Search Algorithm/ Mapper                                              |

| 9.2     | Future  | Work                                                                  |

|         | 9.2.1   | MSE for Both Intra- and Inter- Layers                                 |

|         | 9.2.2   | MSE for Heterogeneous System                                          |

|         | 9.2.3   | MSE for new DNN Operation                                             |

|         | 9.2.4   | Sparsity as new Mapping Axis                                          |

|         | 9.2.5   | Pre-trained Mapper and Transfer Learning                              |

|         | 9.2.6   | Mapping and Neural Architecture Co-Exploration                        |

| Append  | lices . |                                                                       |

| App     | endix A | : FLAT: An Optimized Dataflow for Mitigating Attention Bottlenecks188 |

| Referei | nces .  |                                                                       |

| Vita .  |         |                                                                       |

# LIST OF TABLES

| 3.1 | Hardware resources and baseline flexibility TOPS                                                                                                                                                                                                                                                                                                                                                                                             | 41 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Area cost of accelerators with different flexibility.                                                                                                                                                                                                                                                                                                                                                                                        | 41 |

| 3.3 | Definition of Map Space and Flexibility.                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |

| 4.1 | Terminology in Genetic Algorithm (GA).                                                                                                                                                                                                                                                                                                                                                                                                       | 59 |

| 4.2 | The HW resources in different platforms                                                                                                                                                                                                                                                                                                                                                                                                      | 66 |

| 4.3 | Three target systems (Accel's infrastructures)                                                                                                                                                                                                                                                                                                                                                                                               | 66 |

| 4.4 | Supported optimization algorithms in M3E                                                                                                                                                                                                                                                                                                                                                                                                     | 68 |

| 4.5 | End-to-end performance and energy on S3 for a suite of DNN models using fixed mappings versus GAMMA. Bold means lowest values.                                                                                                                                                                                                                                                                                                               | 72 |

| 4.6 | Two stage optimization for inter-layer parallelism on ResNet-18 * and VGG16 <sup>†</sup> for a multi-accelerator (S3) pipelined deployment. In the 1st state, we optimize for latency and identify the bottleneck layer (highlighted in bold), which determines the pipeline latency. In the 2nd stage, we optimize for energy (or power) by allowing the latency of other layers to increase, while staying less than the pipeline latency. | 73 |

| 5.1 | The description of the relevant workloads and accelerator configurations used across evaluations.                                                                                                                                                                                                                                                                                                                                            | 84 |

| 5.2 | MSE for workload with weight sparsity. In each columns, the blue cell<br>shows the performance of the optimized mapping for the sparse workload;<br>the rest of the cells shows the performance of the same mapping tested with<br>the workload with different sparsity. We highlight the best-performing cell<br>of each row by green text. We can observe that the blue cells overlap with<br>green texts, indicating that different workload with different sparsity levels<br>do require different mapping to optimize the performance                                                          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3 | The optimized EDP performance of inner and outer product style mapping<br>on sparse-dense GEMM workloads in Bert-large model [69]. The workload<br>density indicates the density of the sparse matrix. Bert-large KQV: the key/<br>query/ value projection operations. Bert-large Attn: the attention operation,<br>Bert-large FC: the FC operations at the end of attention blocks                                                                                                                                                                                                                 |

| 5.4 | Comparisons of sparsity-aware technique and static-density heuristic when tackling the activation sparsity. The static-density heuristic searches mapping for a fixed density level (1.0, 0.5, or 0.1), marked as blue cells. Sparsity-aware technique searches the mapping scored with its performance across 5 density level (1.0, 0.8, 0.5, 0.2, and 0.1). We highlight the best-performing one in each row with green text. It indicates that sparsity-aware technique can find mapping with comparable performance to the static-density ones across a range of sparsity (density 1.0 - 0.05). |

| 7.1 | Terminology used in MAGMA Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.2 | Accelerators configurations/ settings of the experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.3 | Supported optimization algorithms in M3E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.4 | The performance of warm-start on (a) Mix, S4, BW=1. (b) The averaged performance across different tasks and different accelerator (S1-S6) under BW=1. All the values are normalized by the values of Trf-100-ep of each columns. Raw (highlighted in orange) is the throughput without warm-start. Trf-0-ep (highlighted in green) is warm-start and before further optimization. Trf-1-ep is warm-start with one epoch of optimization, and likewise for Trf-30-ep. Trf-100-ep (highlighted in blue) represents a full optimization                                                                |

|     | process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8.1 | The level values of action pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8.2 | Platform constraint settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.3 | Converged solution of LP deployment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.4 | Converged solutions after 5000 epochs for various optimization methods across four platforms with different constraints. DNN=MobileNet-V2, Dataflow=NVDLA-style, Deployment=LP |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.5 | Comparison of search-time and converged solutions across state-of-the-art<br>RL techniques                                                                                     |

| 8.6 | Dataflow and Hardware co-automation                                                                                                                                            |

| 8.7 | Two-stage optimization of ConfuciuX                                                                                                                                            |

| 8.8 | Resource assignments for LP deployment at compile time of ConfuciuX 176                                                                                                        |

| 8.9 | Different configurations of the policy network                                                                                                                                 |

| A.1 | Buffer requirement for tiling granularity. M: batched Multi-head, B: Batch,<br>H: Head, R: Row                                                                                 |

| A.2 | Comparisons Dataflow Configurations                                                                                                                                            |

| A.3 | The HW resource configuration of cloud and edge accelerators in the evalu-<br>ation sections                                                                                   |

# LIST OF FIGURES

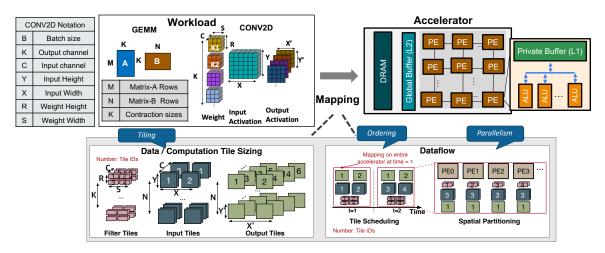

| 1.1  | The overview of DNN Workload, Accelerator, and Mapping                                                                                                                                                                                                      | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

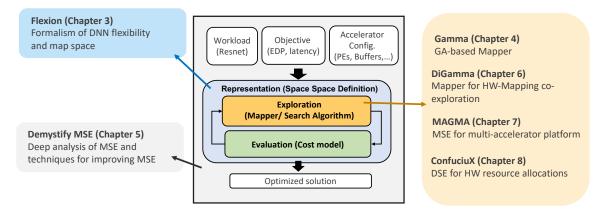

| 1.2  | The proposed optimization loop for Map Space Exploration (MSE) or De-<br>sign Space Exploration (DSE).                                                                                                                                                      | 5  |

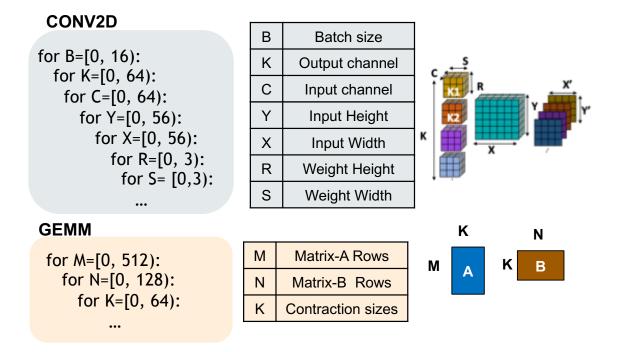

| 2.1  | The loop-nest representation of CONV2D and a Matrix Multiplication (GEMM).                                                                                                                                                                                  | 13 |

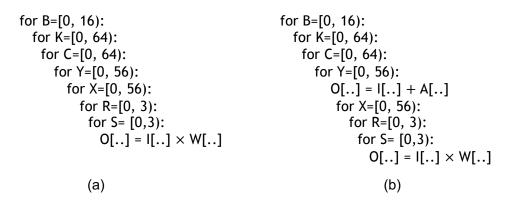

| 2.2  | An example of (a) perfect loop-nest and (b) imperect loop-nest                                                                                                                                                                                              | 14 |

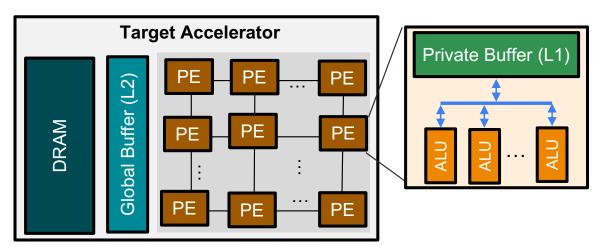

| 2.3  | A DNN accelerator architecture template.                                                                                                                                                                                                                    | 14 |

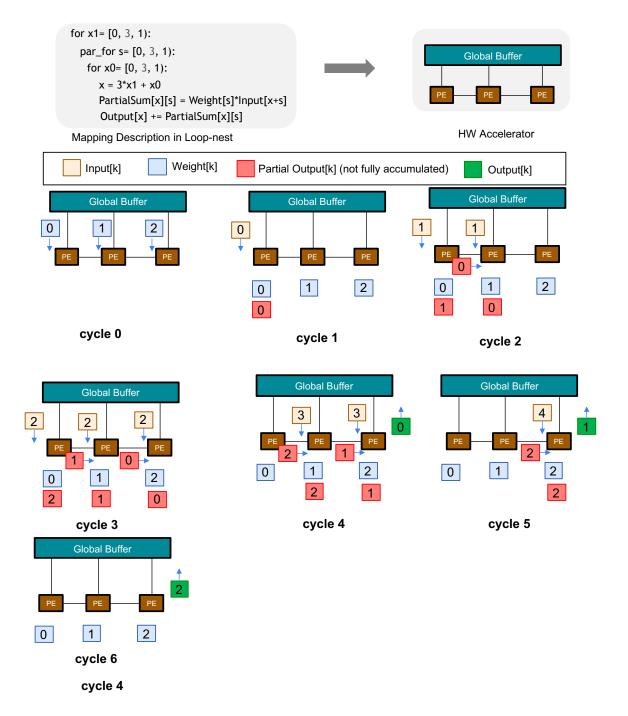

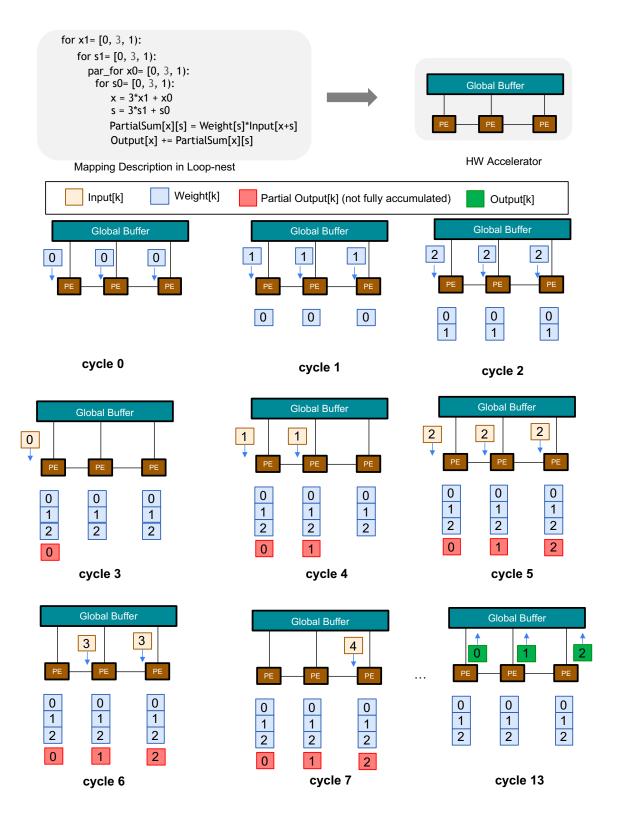

| 2.4  | A weight-stationary example. This is example is referenced from [88]                                                                                                                                                                                        | 16 |

| 2.5  | An output-stationary example. This is example is referenced from [88]                                                                                                                                                                                       | 17 |

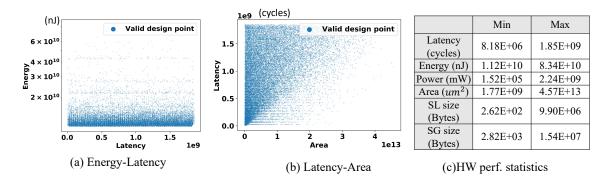

| 2.6  | The HW performance of randomly sampled HW-mapping in the design<br>space on an example layer (second layer of VGG16). (a) The Energy to<br>Latency plot, (b) The Latency to Area plot, and (c) The HW performance<br>statistics of the sampled HW mappings. | 18 |

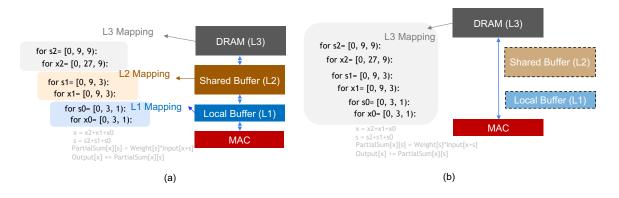

| 2.7  | The level of buffer mapping effects. (a) option 1 mapping between MAC and L1, L2 and off-chip, (b) option 2 mapping between MAC and off-chip                                                                                                                | 19 |

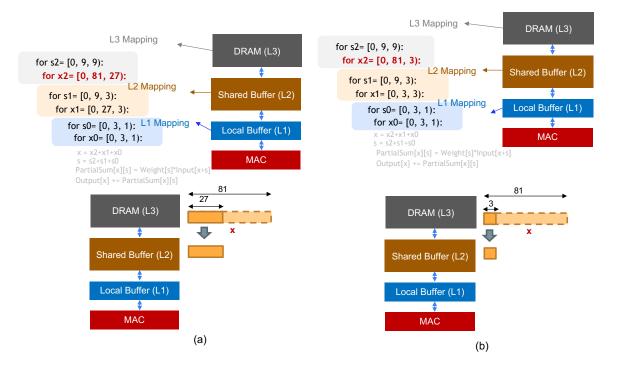

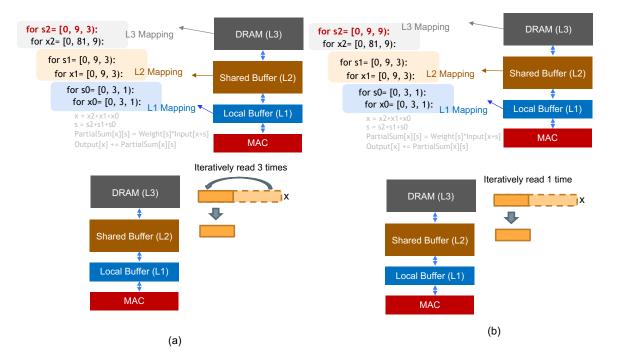

| 2.8  | The Effect of tile sizes on ameliorating BW bottleneck. (a) option 1 with larger input tile size, (b) option 2 with smaller input tile size                                                                                                                 | 20 |

| 2.9  | The Effect of tile sizes on reuse. (a) option 1 with larger weight tile sizes, (b) option 2 with smaller weight tile sizes                                                                                                                                  | 21 |

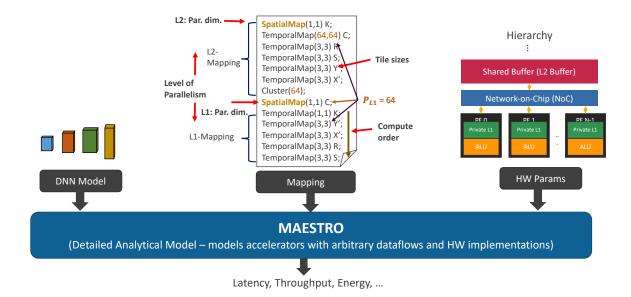

| 2.10 | The workflow of MAESTRO [68]                                                                                                                                                                                                                                | 22 |

| 2.11 | The categories of different exploration algorithms (Mappers) in Map Space Exploration.                                                                                                                                                                      | 23 |

| 3.1  | (a) Flexibility TOPS and prior work. (b) For any workload, a unique mapping involves choosing individual points from the map-space actually supported by the target accelerator.                                                                                                                                                                                                         | 30 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | The benefit of having flexibility in (a) Tile, (b) Order, (c) Parallelism, and (d) Shape.<br>Example GEMM operation of $Z_{MN} = A_{MK} \times B_{KN}$ on 4x4 PE array. The subscript <i>t</i> indicates that these are tiles of the overall computation. The inflexible accelerator is weight stationary (tensor <i>B</i> ), using a loop ordering of $K \rightarrow N \rightarrow M$ . | 31 |

| 3.3  | DNN accelerator with NVDLA-style mapping.                                                                                                                                                                                                                                                                                                                                                | 32 |

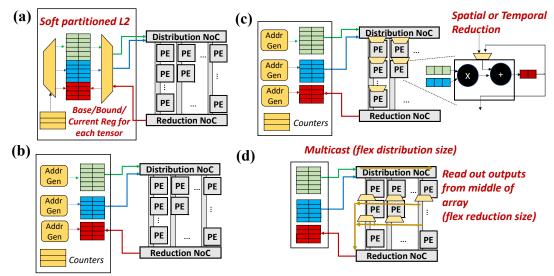

| 3.4  | HW Overhead for Flexibility Support (highlighted in yellow). (a) Flexible Tile Size<br>HW Support: Soft-partitioned Scratchpads. (b) Flexible Loop Order HW Support:<br>Configurable Address Generators. (c) Flexible Parallelism HW Support: Spatial<br>and Temporal Reduction. (d) Flexible Shape HW Support: NoC support for PE<br>clustering.                                        | 35 |

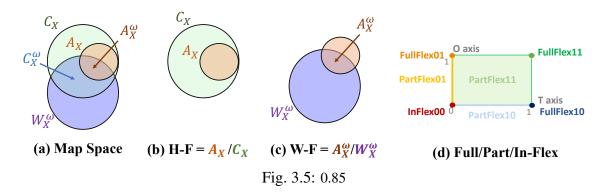

| 3.5  | 0.85                                                                                                                                                                                                                                                                                                                                                                                     | 37 |

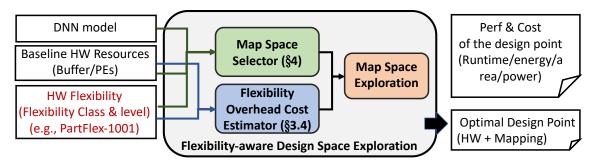

| 3.6  | Flexibility-Aware Automated Design-Space Exploration Framework.                                                                                                                                                                                                                                                                                                                          | 40 |

| 5.0  | The storing-Aware Automated Design-space Exploration Pranework                                                                                                                                                                                                                                                                                                                           | 40 |

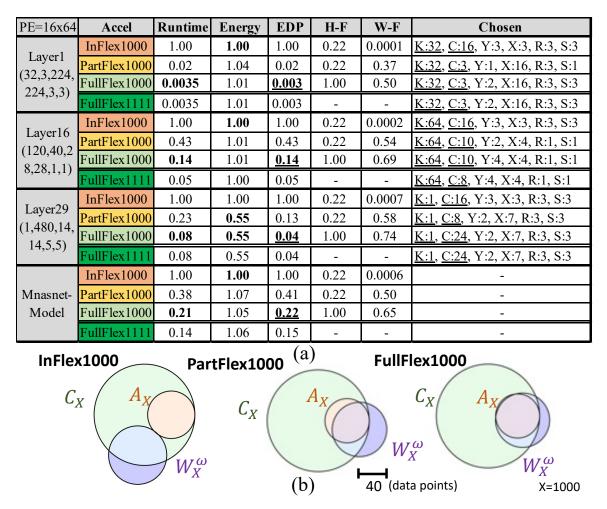

| 3.7  | Tile Axis Isolation. (a) Performance comparisons of accelerators with different level of Tile flexibility running Mnasnet model. (b) Venn diagram of Tile map space on Mnasnet. We use on-chip buffer size=4K in this experiments. Scale: Total Data points in $W_T^{\omega} = \pi (40)^2$ . Runtime/Energy/EDP are normalized against values of InFlex-1000.                            | 43 |

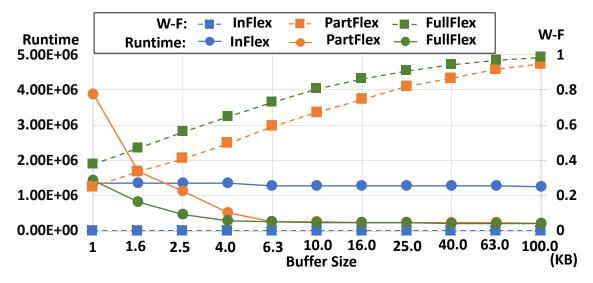

| 3.8  | The runtime performance and workload Flexion of fully-Tile-flexible accelerators with different buffer sizes. (W-F: Workload-dependent Flexion.)                                                                                                                                                                                                                                         | 44 |

| 3.9  | Order Axis Isolation. (a) Performance comparisons of accelerators with different level of Tile flexibility running Mnasnet model. (b) Venn diagram of Tile map space on Mnasnet. Runtime/Energy/EDP are normalized against values of InFlex-0100.                                                                                                                                        | 46 |

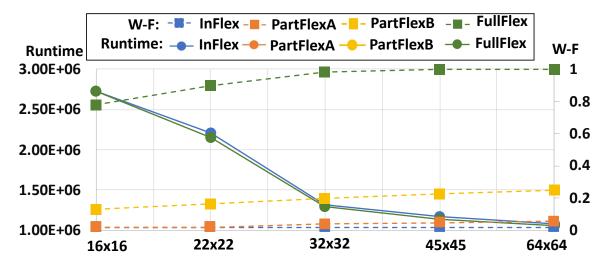

| 3.10 | Parallelism Axis Isolation. Performance comparisons of accelerators with different level of Parallelism flexibility running Mnasnet model with (a) 16x64 PE array and (b) 32x32 PE array. (c) Venn diagram of Parallelism map space on Mnasnet. PRuntime/Energy/EDP are normalized against values of InFlex-0010                                                                         | 48 |

| 3.11 | Shape Axis Isolation. (a) Performance comparisons of accelerators with different level of Tile flexibility running Mnasnet model. (b) Venn diagram of Tile map space on Mnasnet. Runtime/Energy/EDP are normalized against values of InFlex-0001.                                                                                                                                        | 50 |

| 3.12 | The runtime performance and workload Flexion of fully-Shape-flexible accelerators with different size of PE arrays. (W-F: Workload-dependent Flexion)                                                                                                                                                                                                                                    | 51 |

| 3.13 | Runtime performance of accelerators with different flexibility. InFlex-0000-X-Opt means class-0000 (fixed) accelerator that is optimized for DNN model X (X= Alexnet, Mnasnet, etc.). The runtime in each row is normalized by the runtime of        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the values of InFlex-0000-Alexnet-Opt.                                                                                                                                                                                                               | 52 |

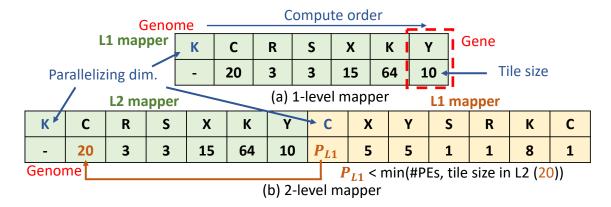

| 4.1  | The GAMMA encoding example of (a) 1-level mapper and (b) 2-level mapper.                                                                                                                                                                             | 60 |

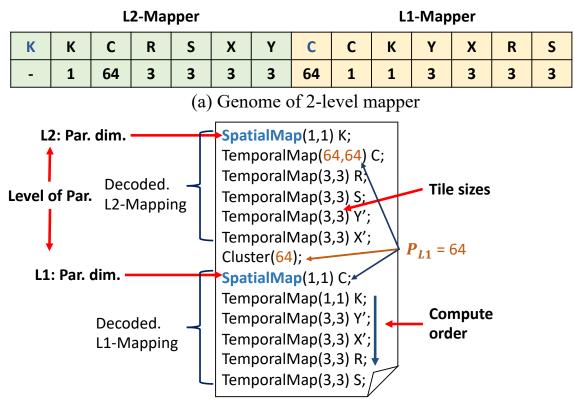

| 4.2  | (a) GAMMA's description of a 2-level mapper and (b) its decoded description for cost model (MAESTRO) of a NVDLA-like [80] 2-level mapper                                                                                                             | 61 |

| 4.3  | (a)The structure and algorithm flow of GAMMA, and (b) The summary of evolution in GAMMA.                                                                                                                                                             | 62 |

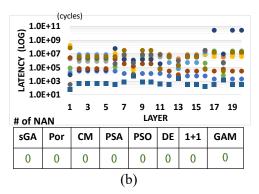

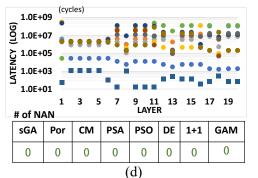

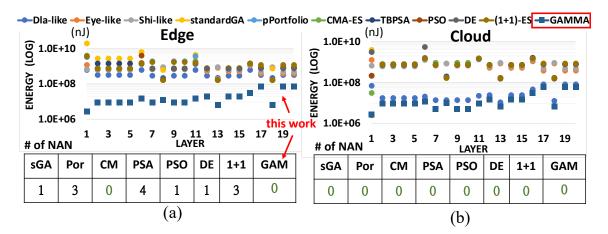

| 4.4  | The performance of found solutions across a suite of optimization methods on different target systems (S1, S2, S3) and different platform constraints (Edge, Cloud) for ResNet-18                                                                    | 67 |

| 4.5  | The energy consumption of S2 on ResNet-18                                                                                                                                                                                                            | 70 |

| 4.6  | GAMMA's found mapping of early, medium, and late layer of ResNet-18 in Figure 4.4(e).                                                                                                                                                                | 71 |

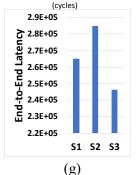

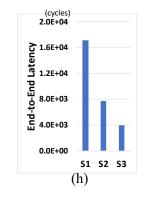

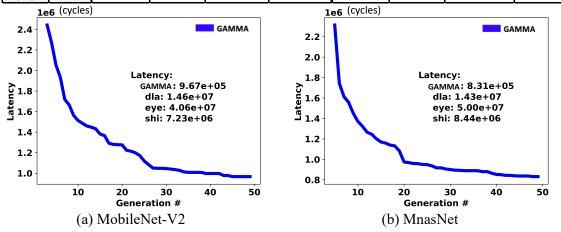

| 4.7  | End-to-end latency improvement over generations with GAMMA for S3 system and edge platform constraint.                                                                                                                                               | 72 |

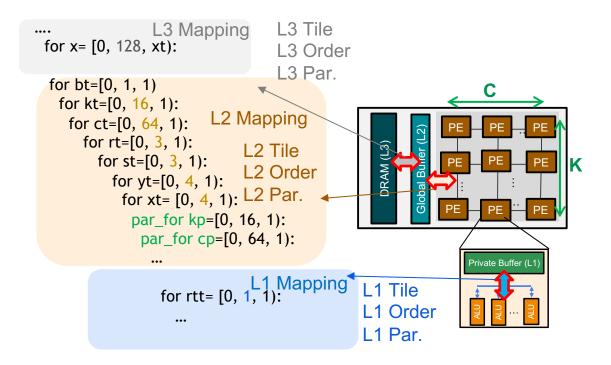

| 5.1  | A loop-nest representation of a NVDLA-like [80] mapping                                                                                                                                                                                              | 78 |

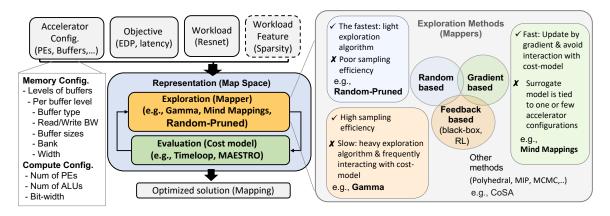

| 5.2  | A canonical Map Space Exploration framework                                                                                                                                                                                                          | 79 |

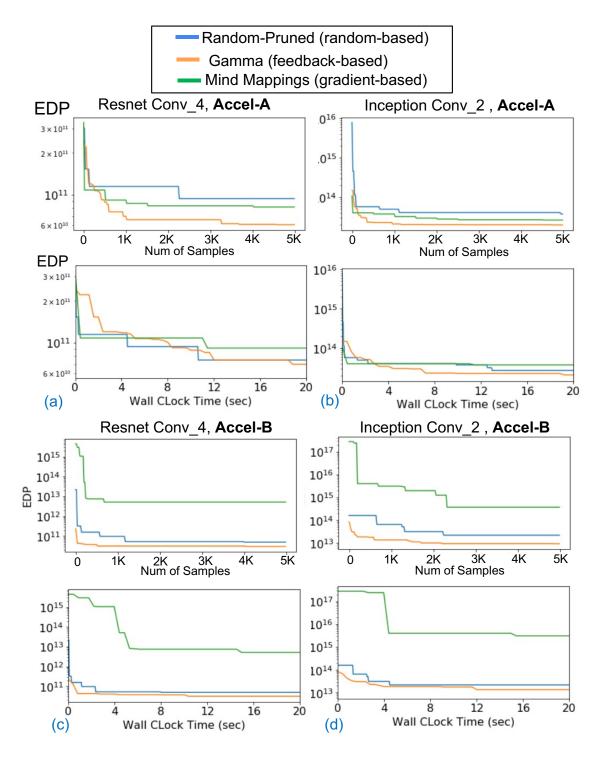

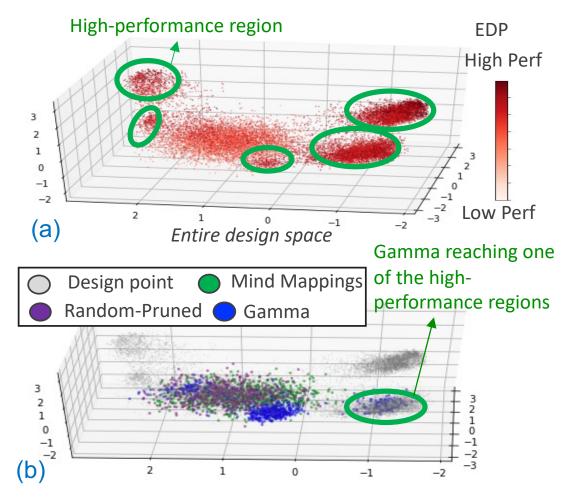

| 5.3  | Comparisons of different types of mappers. Top figures show the converge curve across number of samples. Bottom figures show the converge curve across wall clock time.                                                                              | 83 |

| 5.4  | (a) shows the sampled points by exhaustively sampling the search space of (Resnet Conv_4, Accel-A). The 3D visualization is projected by PCA dimension reduction. (b) shows the sampled points of different types of mappers in this search space.   | 85 |

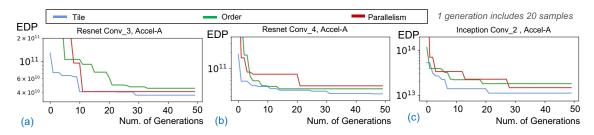

| 5.5  | Mapping axes sensitivity analysis using the mutation operators in Gamma [5].<br>E.g., Tile (blue): means mutating tile only, i.e, only tile is explored, and other<br>mapping axes are fixed, similarly for (mutate-)Order and (mutate-)Parallelism. | 86 |

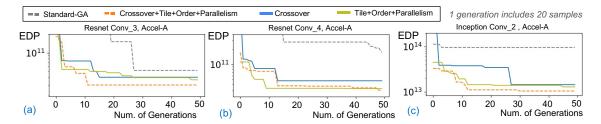

| 5.6  | Crossover (blending two mappings) sensitivity analysis using operators in Gamma [5]. Standard-GA uses the standard mutation and crossover (without domain-specific operators along each mapping axes designed in Gamma [5]).                                                                                              | 88 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

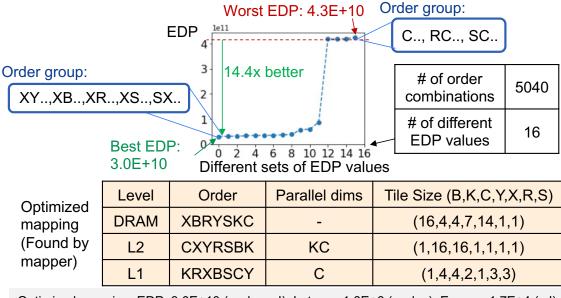

| 5.7  | The EDP difference of the same mapping with different loop order. We sweep through all 7! order combinations assuming all the buffer level utilize the same order. The 7! different mapping leads to 16 different EDP performance, with the best and the worst EDP differs by 14.4x times (under Resnet Conv_4, Accel-B). | 90 |

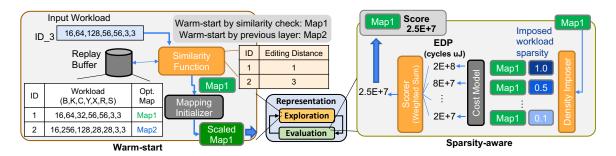

| 5.8  | The workflow of Warm-start and Sparsity-aware techniques in MSE                                                                                                                                                                                                                                                           | 90 |

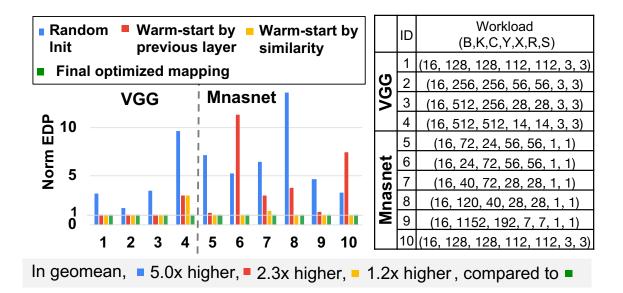

| 5.9  | Performance comparisons of initialized solution by Random Init and two<br>types of warm-start Init comparing to the final optimized performance (after<br>search). The EDP values are normalized by final optimized EDP (green bars).                                                                                     | 91 |

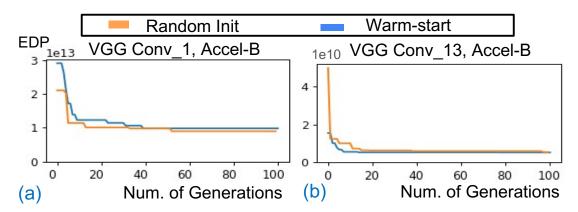

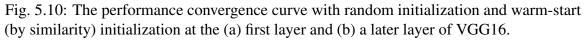

| 5.10 | The performance convergence curve with random initialization and warm-<br>start (by similarity) initialization at the (a) first layer and (b) a later layer of<br>VGG16                                                                                                                                                   | 91 |

| 5.11 | The benefit of warm-start (by similarity) when executing MSE for the DNN models. Warm-start MSE achieves comparable EDP performance to default MSE, but converge 3.3-7.3x faster. Different colors represent different layers of the models.                                                                              | 92 |

| 6.1  | State-of-the-Art HW and Mapping optimization frameworks                                                                                                                                                                                                                                                                   | 08 |

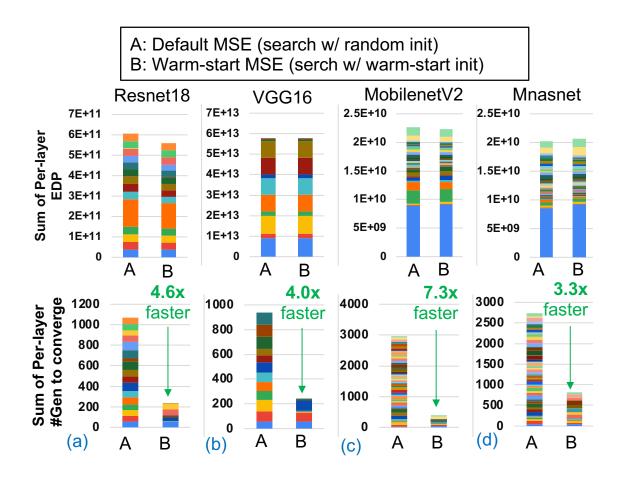

| 6.2  | HW/Mapping Co-optimization Framework. Our three technical contribu-<br>tions are highlighted                                                                                                                                                                                                                              | 09 |

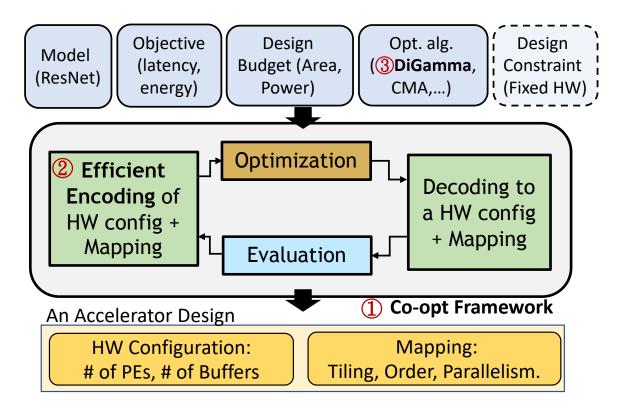

| 6.3  | (a) <b>Co-opt Framework</b> , (b-c) the HW-Mapping encoding representation, and (d-e) the corresponding decoded accelerator configuration. (f) The formula for calculating minimum on-chip buffer requirement. (g) The definition of notations                                                                            | 10 |

| 6.4  | GAMMA's genetic operators <sup>†</sup> and their perturbing space <sup>‡</sup>                                                                                                                                                                                                                                            | 15 |

| 6.5  | State-of-the-Art HW and Mapping optimization frameworks                                                                                                                                                                                                                                                                   | 16 |

| 6.6 | Performance comparisons of different optimization algorithms. Both latency<br>and latency-area-product are normalized by the values of CMA, the best-<br>performing baseline (lower is better). We highlight the best performing<br>algorithm in different tasks (DNN models) in bold. N/A means the algorithm<br>cannot find valid solution that fits in the area constraint under the set 40K<br>sampling budgets |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.7 | Latency of the found solution by different optimization scheme. Latency values are normalized by the values of best-performing baseline method (Compute-focused + Gamma). Grid-S: grid search. Buffer-focused: large buffer design. Compute-focused: large PE arrays design. Meidum-Buf-Com: medium buffer and PE arrays design                                                                                     |

| 6.8 | The solution found by different optimization schemes and their correspond-<br>ing performance on Mnasnet at edge resources                                                                                                                                                                                                                                                                                          |

| 7.1 | The structure and flow <sup><math>\dagger</math></sup> of M3E                                                                                                                                                                                                                                                                                                                                                       |

| 7.2 | The encoding scheme of M3E                                                                                                                                                                                                                                                                                                                                                                                          |

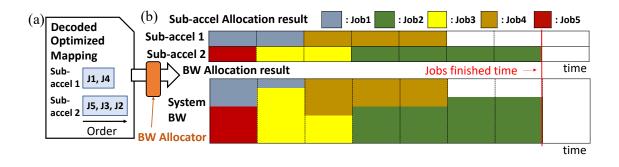

| 7.3 | (a) Mapping description from the decoder. (b) The example BW and sub-<br>accelerators allocation results                                                                                                                                                                                                                                                                                                            |

| 7.4 | (a) Then encoding scheme of M3E. The genetic operators of MAGMA and their implying update on the mapping: (a) mutation, (b) crossover-gen, (c) crossover-rg, and (d) crossover-accel                                                                                                                                                                                                                                |

| 7.5 | The algorithm flow of MAGMA                                                                                                                                                                                                                                                                                                                                                                                         |

| 7.6 | (a) The average per-job no-stall latency and required BW for no-stall across different models on high (HW) and low (LB) bandwidth mapping style. (b) Average no-stall latency and (c) average BW required for no-stalls across all involved jobs                                                                                                                                                                    |

| 7.7 | The experiment results on multi-core homogeneous small accelerator (S1) with BW=16 across four tasks. Throughput values are normalized by the value of MAGMA. The absolute throughput values of MAGMA in (a-d) are: 249, 397, 194, and 329 GFLOPs                                                                                                                                                                   |

| 7.8 | The experiment results on multi-core heterogeneous (a)(b) small (S2, BW=16) and (c)(d) large (S4, BW=256) accelerator on Vision and Mix tasks. Throughput values are normalized by the value of MAGMA. The absolute throughput values of MAGMA in (a-d) are: 254, 271, 254, and 383 GFLOPs 141                                                                                                                      |

| 7.9  | Performance comparisons on multi-core heterogeneous (a) small (S2) and (b) large (S4) accelerator on Mix tasks, given different BWs. Throughput values are normalized by the value of MAGMA                                                                                                                                                                                                                                                                             | 142 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

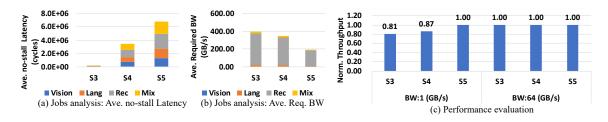

| 7.10 | Jobs analysis of the averaged per-job (a) no-stall latency and (b) required BW.<br>(c) Performance evaluation of MAGMA on S3, S4, and S5 with different<br>BW. In (a-b), we concatenate the four independent no-stall latency (averaged<br>required BWs) into a stacked bar and show the total values. In (c), throughput<br>values are normalized by the value of S5                                                                                                   | 142 |

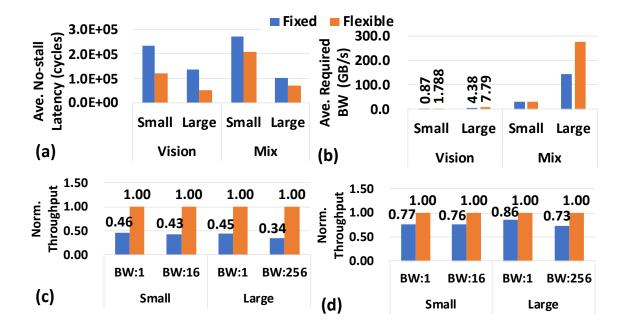

| 7.11 | Jobs analysis of the averaged (a) per-job no-stall latency and (b) required<br>BW of fixed and flexible PEs arrays. Performance evaluation of MAGMA<br>with fixed or flexible PEs array on (c) Vision and (d) Mix. Throughput<br>values are normalized by the value of flexible accelerator                                                                                                                                                                             | 145 |

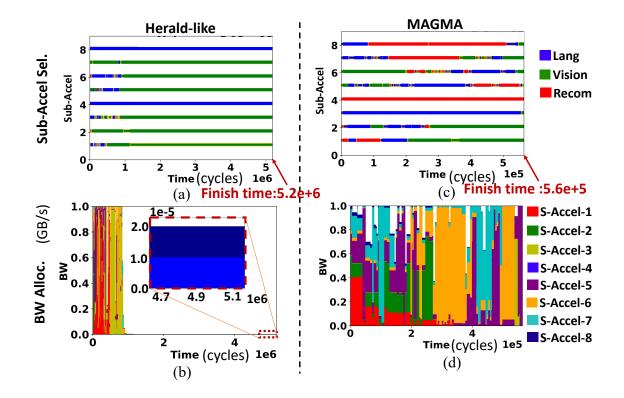

| 7.12 | The visualization of found solution by Herald-like and MAGMA. (a)(c) shows the respective sub-accelerator allocations, and (b)(d) shows the respective BW allocations. (Mix task, S5, BW=1)                                                                                                                                                                                                                                                                             | 146 |

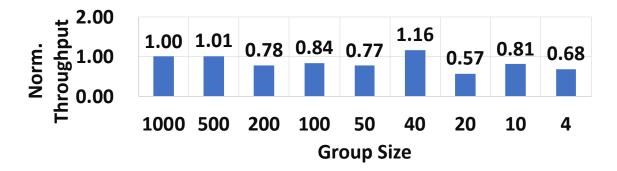

| 7.13 | The reached performance of MAGMA given the same task and setting (Mix, S2, BW=16) with different group sizes. Throughput values are normalized by the value of group size=1000,                                                                                                                                                                                                                                                                                         | 146 |

| 8.1  | Overview of ConfuciuX.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 153 |

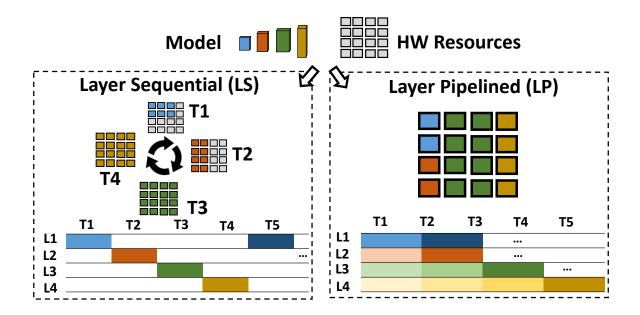

| 8.2  | DNN deployment scenarios and corresponding HW assignments. In Layer Sequential (LS), each layer of the model is mapped one by one on the entire accelerator, with all on-chip compute and memory assigned to it; in Layer Pipelined (LP), the entire model is mapped and run in a pipelined manner, with the compute and memory partitioned across all layers.                                                                                                          | 154 |

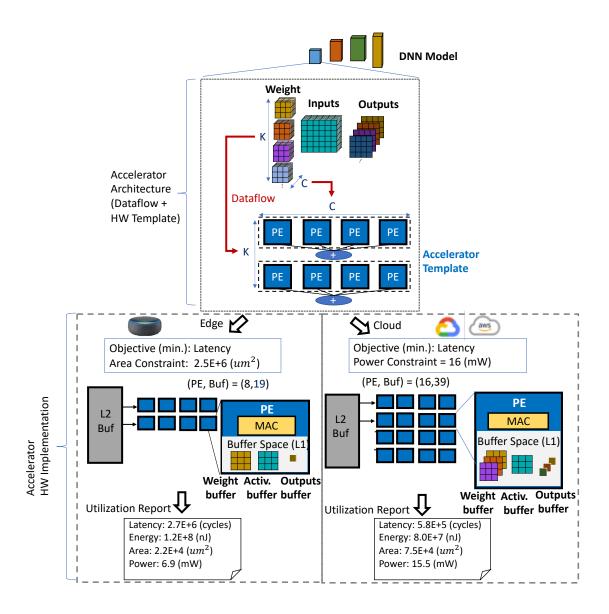

| 8.3  | Different HW resource combinations with the same NVDLA-style dataflow.                                                                                                                                                                                                                                                                                                                                                                                                  | 157 |

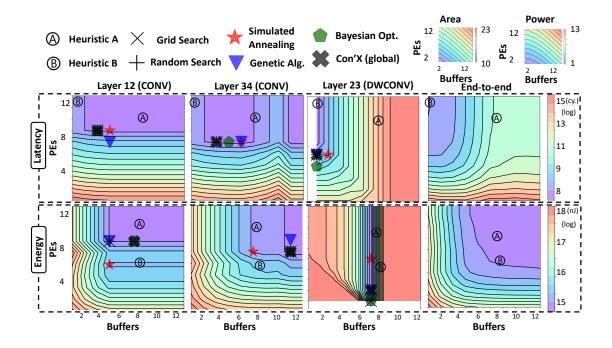

| 8.4  | Searching for per-layer PEs/Buffers configurations to optimize latency/energy with different techniques. Purple indicates lower (better) and red indicates higher (worse) latency/energy. <b>Heuristic A</b> : Determine the PEs/Buffers with the most compute-intensive layer (Layer-38) and apply the same configuration for all the layers. <b>Heuristic B</b> : Determine the PEs/Buffers by the configuration that optimizes end-to-end whole model latency/energy | 164 |

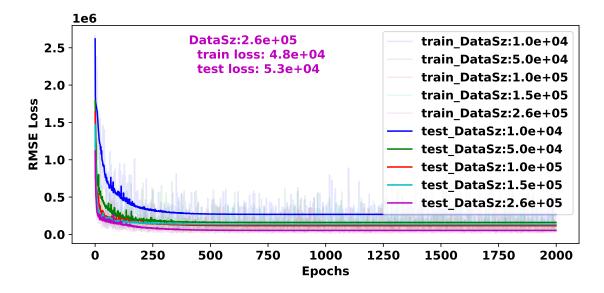

| 8.5  | The learning curve of the critic network.                                                                                                                                                                                                                                                                                                                                                                                                                               | 168 |

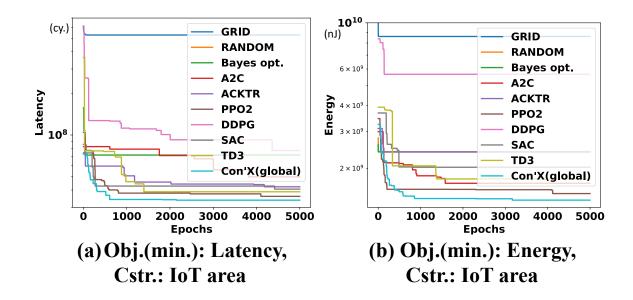

| 8.6  | The fast convergence and sample efficiency of Con'X (global)                                                                                                                                                                                                                                                                                                                                                                                                            | 170 |

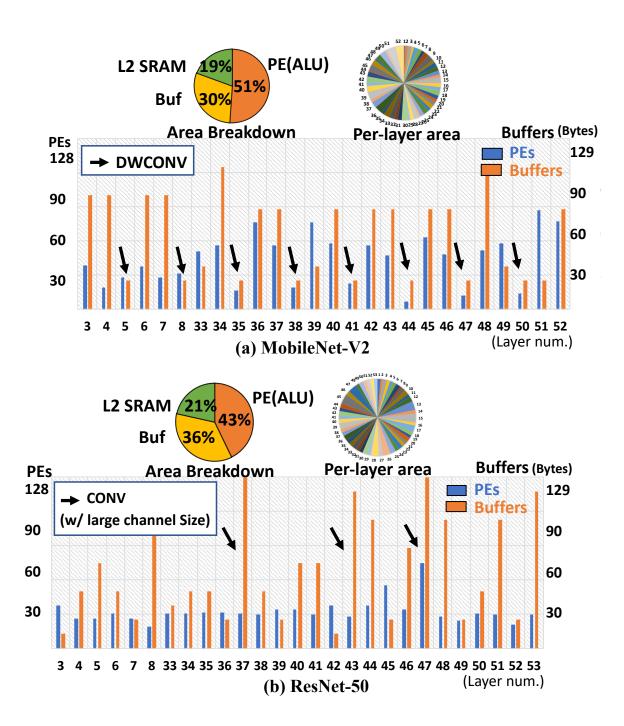

| 8.7 | The solution for (a) MobileNet-V2 and (b) ResNet-50 (Obj.(min.):Latency, Cstr:IoT area).                                                                                                                                                                                                                                                                                  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

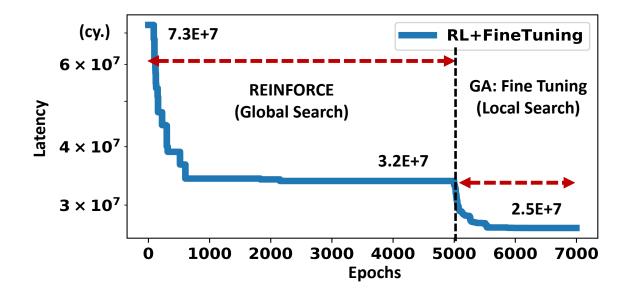

| 8.8 | Overall latency as a function of epochs across two-stage optimization in ConfuciuX (MobileNet-V2, Obj.(min.):Latency, Cstr.:IoT area)                                                                                                                                                                                                                                     |

| 8.9 | Dataflow-HW co-automation with ConfuciuX for MobileNet-V2. (Obj.(min.):Latency, Cstr:IoT area).                                                                                                                                                                                                                                                                           |

| A.1 | The structure of attention-based models. Green matrix notation shows the size of weight tensors; black matrix notation shows the size of activation tensors; Softmax is applied on output of Logit                                                                                                                                                                        |

| A.2 | Potential of Tensor-Tensor Fusion. The operation intensity of single and fused operators in attention layers in TrXL(-large) [70] using batch size=1. The notations are from Figure A.1. $f(X, Y)$ means a fused X and Y operator. 190                                                                                                                                    |

| A.3 | Roofline analysis on TPU-v3 [284] for operators in BERT(-base) [69],<br>TrXL(-large) [70], and XLM(xlm-mem-en) [71], and ResNet50 [142] using<br>sequence length = 512                                                                                                                                                                                                    |

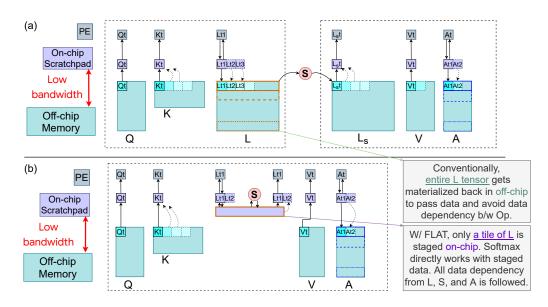

| A.4 | (a) Baseline and (b) FLAT dataflow. FLAT performs inter-operator fusion of L, A while respecting data dependencies introduced by Softmax. FLAT-tile enables staging slices of the logits tensor in the on-chip scratchpad increasing effective memory bandwidth. This fused, interleaved execution of L, A yields higher compute utilization and improved performance 193 |

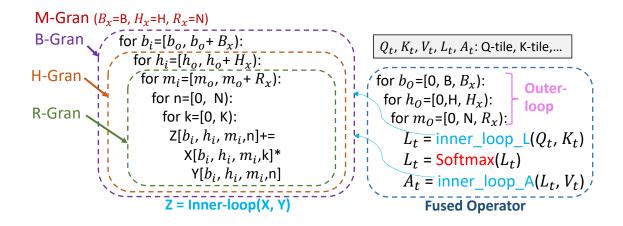

| A.5 | For loop of fused L-Softmax-A (or shortened as L-A in the paper) and the choice of granularity                                                                                                                                                                                                                                                                            |

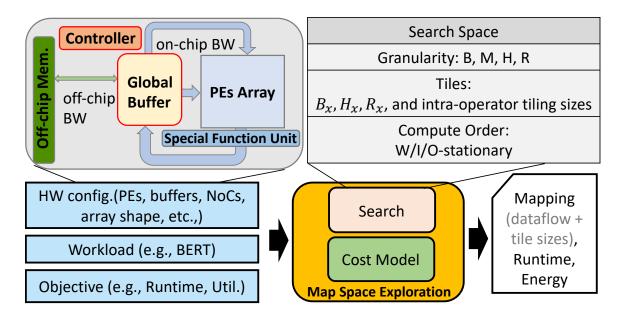

| A.6 | Map space exploration framework. (Special Function Unit: for computing non-linear operations, e.g., softmax, activations.)                                                                                                                                                                                                                                                |

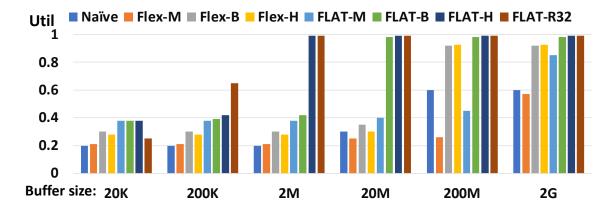

| A.7 | Compute utilization analysis of L-A operators under different dataflow granularities, running BERT with 512 sequence length with edge platform resources. Flex dataflow (Flex-X): Flex dataflow with X-granularity. FLAT dataflow (FLAT-X): Flex dataflow with X-granularity; X could be M (batch-Multi-head), B (Batch), H (head), or R (row)                            |

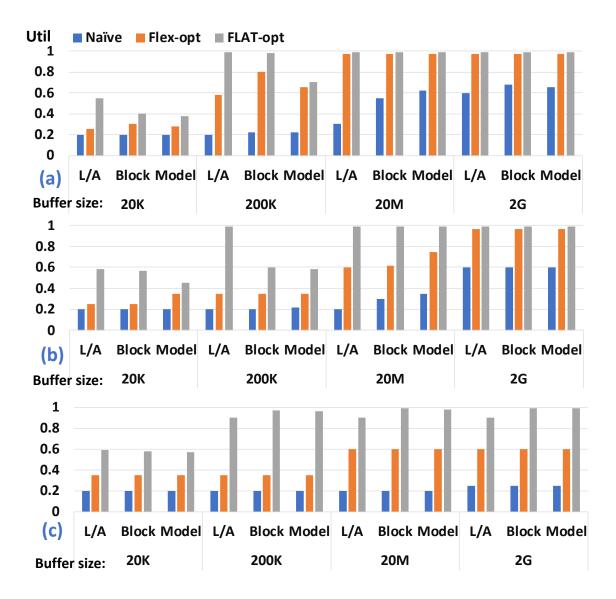

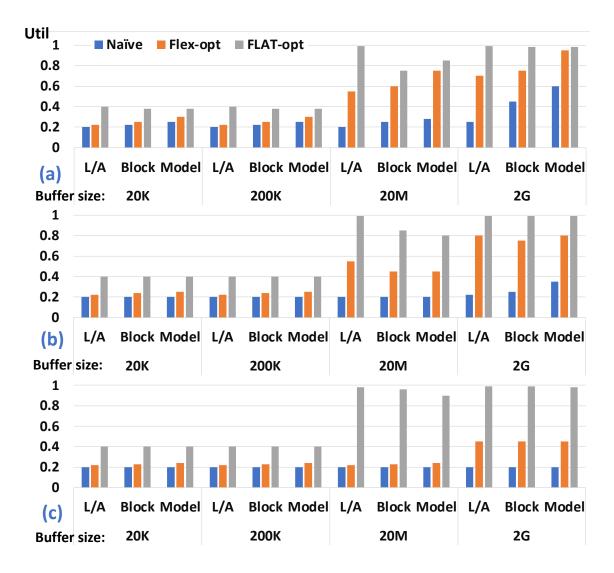

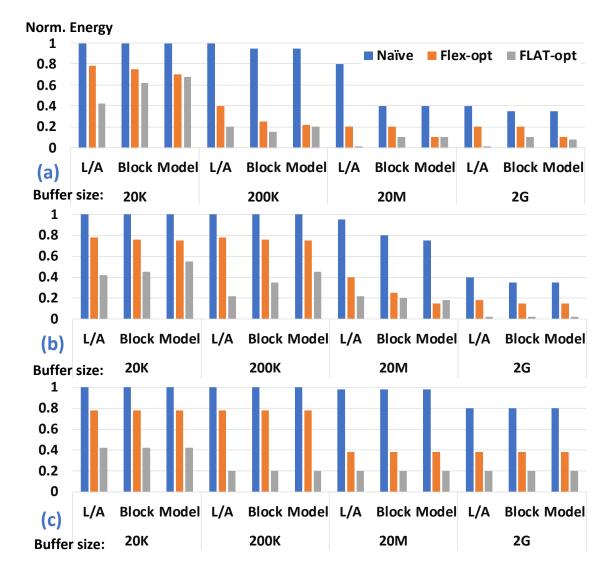

| A.8  | Comparisons of compute utilization across different sequence lengths run-<br>ning BERT under edge platform resources with sequence length of (a) 512,<br>(b) 4K, and (c) 64K. We sweep the available on-chip buffer from size 20KB<br>to 2GB. We list three level of performance analysis, L-A: focusing on per-<br>formance difference at the L, A operators; Block: consider all operators in<br>the attention block; and Model: a model-wise performance                                                                                                                                                                                                                              | . 203 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

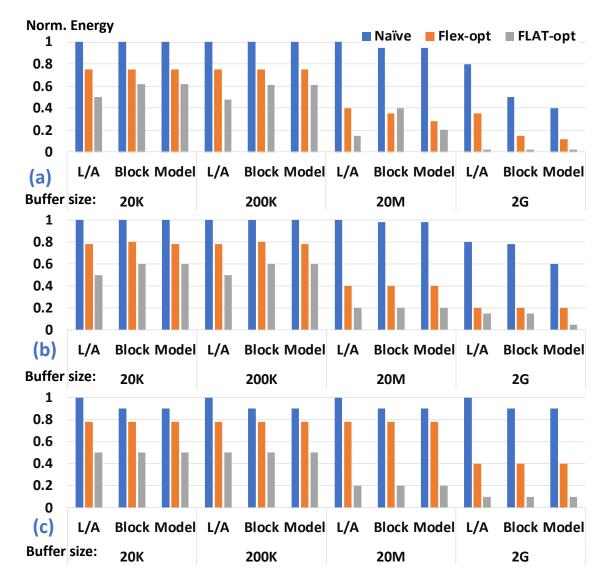

| A.9  | Comparisons of compute utilization across different sequence lengths run-<br>ning XLM under cloud platform resources with sequence length of (a) 4K,<br>(b) 16K, (c) 256K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 206 |

| A.10 | The corresponding energy consumption of each of the data-point in Fig-<br>ure A.8. The energy numbers are normalized by the largest energy number<br>in each sub-plot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 207 |

| A.11 | The corresponding energy consumption of each of the data-point in Figure A.9. The energy numbers are normalized by the largest energy number in each sub-plot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 208 |

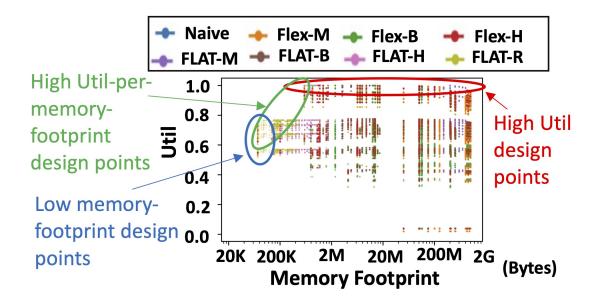

| A.12 | <sup>2</sup> The design space of FLAT when running BERT with sequence length of 512 under edge platform resources. Flex dataflow (Flex-X): Flex dataflow with X-granularity. FLAT dataflow (FLAT-X): Flex dataflow with X-granularity, where X could be M (batch-Multi-head), B (Batch), H (head), or R (row). The design-point with the highest utilization, given a buffer constraint represents Flex-Opt and FLAT-Opt (Table A.2).                                                                                                                                                                                                                                                    | . 210 |

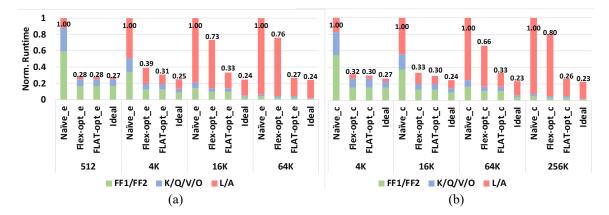

| A.13 | B End-to-end latency breakdown running: (a) BERT on Edge accelerator,<br>(b) XLM on Cloud accelerator. Naive_e(dge): Edge with Naive dataflow.<br>Flex-opt_e(dge): Edge with optimal Flex dataflow. FLAT-opt_e(dge): Edge<br>with optimal FLAT dataflow. Similarly, for Naive_c(loud) and so on. Flex-<br>opt represents the best possible (SOTA) intra-operator dataflow obtained<br>through exhaustive search of the intra-operator map-space. FLAT performs<br>inter-operator L-A fusion to relieve memory-bandwidth boundedness and<br>achieves lower run time. While FLAT realizes benefits even at modest<br>sequence lengths, the gains are pronounced at larger sequence lengths | . 211 |

| A.14 | The end-to-end speedup and energy-consumption ratio of FLAT-opt_e(dge)<br>over Flex-opt_e(dge) and FLAT-opt_c(loud) over Flex-opt_c(loud) on differ-<br>ent models.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 211 |

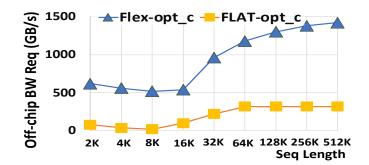

| A.15 | The required BW to reach compute utilization rate higher than 0.95 in the most BW-intensive L-A operator when running XLM using Flex-opt_c(loud) or FLAT-opt_c(loud).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 212 |

#### SUMMARY

The proliferation of AI across a variety of domains (vision, language, speech, recommendations, games) has led to the rise of domain-specific accelerators for deep learning. At design-time, these accelerators carefully architect the on-chip dataflow to maximize data reuse (over space and time) and size the hardware resources (PEs and buffers) to maximize performance and energy-efficiency, while meeting the chip's area and power targets. At compile-time, the target Deep Neural Network (DNN) model is mapped over the accelerator. The mapping refers to tiling the computation and data (i.e., tensors) and scheduling them over the PEs and scratchpad buffers respectively, while honoring the microarchitectural constraints (number of PEs, buffer sizes, and dataflow).

The design-space of valid hardware resource assignments for a given dataflow and the valid mappings for a given hardware is extremely large ( $O(10^{24})$ ) per layer for state-of-theart DNN models today. This makes exhaustive searches infeasible. Unfortunately, there can be orders of magnitude performance and energy-efficiency differences between an optimal and sub-optimal choice, making these decisions a crucial part of the entire design process. Moreover, manual tuning by domain experts become unprecedentedly challenged due to increased irregularity (due to neural architecture search) and sparsity of DNN models. This necessitate the existence of Map Space Exploration (MSE). In this thesis, our goal is to deliver a deep analysis of the MSE for DNN accelerators, propose different techniques to improve MSE, and generalize the MSE framework to a wider landscape (from mapping to HW-mapping co-exploration, from single-accelerator to multi-accelerator scheduling). As part of it, we discuss the correlation between hardware flexibility and the formed map space, formalized the map space representation by four mapping axes: tile, order, parallelism, and shape. Next, we develop dedicated exploration operators for these axes and use genetic algorithm framework to converge the solution. Next, we develop "sparsity-aware" technique to enable sparsity consideration in MSE and a "warm-start" technique to solve the search

speed challenge commonly seen across learning-based search algorithms. Finally, we extend out MSE to support hardware and map space co-exploration and multi-accelerator scheduling.

# CHAPTER 1 INTRODUCTION

Deep Neural Network (DNNs) have become an indispensable tool in the solution toolbox for a variety of complex problems such as object detection, machine translation, language understanding, autonomous driving, and so on. There is a growing demand for specialized DNN accelerators pursuing high performance with high energy, power, and area efficiency. Different applications, objectives, and design budgets create a massive accelerator design space.

In order to achieve high efficiency across a wide range of DNNs, state-of-the-art DNN accelerators are often designed with *flexibility* to adapt to various workloads [1, 2, 3]. These accelerators allow different strategies (i.e., *mappings*) for mapping workloads onto the accelerator to maximize performance and energy efficiency. This flexibility imposes a unique challenge for deployment: finding a high-quality mapping between a DNN workload and the flexible accelerator during runtime. From the space of all legal mappings (i.e., the *map space*) of a workload, the user of such a flexible accelerator needs to find and utilize the best mapping to unlock the full potential of the DNN accelerator.

As a result, *map space exploration* (MSE) is critical for DNN accelerator efficiency. It is a complex and challenging problem because the search space is often massive. Prior work has clearly defined the MSE problem [4, 5, 6, 7], cleanly separating it from the hardware architecture design problem, and has proposed various search algorithms (i.e., *mappers*) [4, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 7, 29, 30, 31, 32, 33] to find optimized mappings for DNN accelerators and workloads.

Despite the success achieved by these prior efforts, MSE remains a computationally challenging problem. This is because the search space for legal mappings for even a single layer of a modern DNN (e.g., ResNet-50) on a typical edge class accelerator [1] is  $\sim$

Fig. 1.1: The overview of DNN Workload, Accelerator, and Mapping.  $O(10^{24})$  [5, 6] which would require more time than the age of the earth to search exhaustively (assuming 1msec to evaluate each mapping sample). This gets exacerbated as newer and ever-larger DNN models are being created with increasing frequency, especially thanks to the success of neural architecture search techniques [34, 35, 36, 37, 38]. Furthermore, the advent of *compressed-sparse* DNNs [39, 40, 41, 42, 43, 44, 45], whose mappings are not performance-portable across sparsity levels, further increase MSE burden.

This thesis aims to develop a scalable MSE for complex DNN workloads. It tackles the following challenges.

#### 1.1 Challenges

#### 1.1.1 Linkage between HW Accelerator Flexibility and Map Space

Traditionally, the efficiency of domain-specific accelerator ASICs has come from *specialization*, i.e., the control path and datapath in the accelerator are tailored to the deep neural networks (DNNs) that are expected to run on the accelerator. In other words, the number of mappings that an accelerator can support (aka *map-space*) is restricted. To this end, there has been growing interest in developing *flexible* DNN accelerators. Flexibility allows the accelerator to better tailor itself to the diverse set of layer parameters within the current DNN being mapped [46, 47], instead of targeting the average case. While the notion HW

flexibility described above makes intuitive sense, the field of DNN accelerators today is inconsistent about the definition. We find that "flexibility" has been used loosely to refer either to the ability to handle different loop tiling/blocking [10], and/or support for different loop orders [12], and/or the ability to spatially partition across different dimensions [48], and/or the ability to logically support different PE aspect ratios [49]. In fact, there is also inconsistency in whether flexibility is a hardware feature [46] or simply a term for compiler loop-transformations over a fixed inner tile [10, 50]. This in-formalism is a serious barrier to the adoption of flexibility features, as it hinders precise quantification of the cost/benefit tradeoff. Moreover, it is a lack of formalism on how different levels of flexibility impact the map space and the performance of the accelerator.

## 1.1.2 Efficient Mapper

The search algorithm in MSE is called – Mapper. Although multiple prior works [9, 51, 52, 30, 53, 54, 55, 56, 57, 18] have studied the mapping problem for DNN accelerators, the size of the map space (exceeding  $O(10^{24})$  even for a single layer of a DNN) makes the problem highly challenging. To cope with this challenge, most prior works restrict the search space. For e.g., coarse-grained strided exhaustive search [23, 12, 16, 17, 22], random search [4], fixed parallelism [23, 16, 22, 56, 57, 18], or limited search for tile sizes for one or more fixed dataflows [21, 12]). Alternately, ML-based search techniques have also been leveraged for guided search to increase sampling efficiency [31, 24, 26, 27]; however, they need to restrict some aspects of the map space (e.g., fixing the parallelism levels) to adapt to the ML algorithms. Such restrictions of the mapping space can lead to local optimal mappings which are significantly sub-optimal, as recent works have highlighted [4, 8].

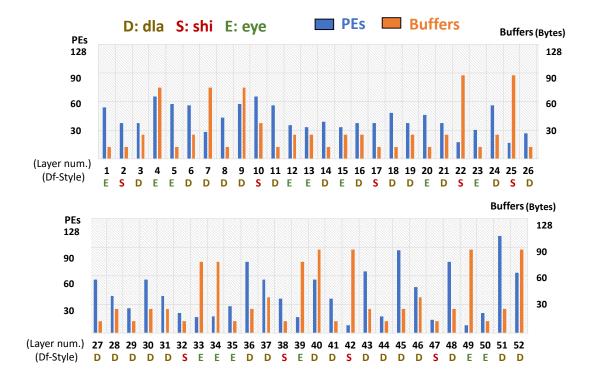

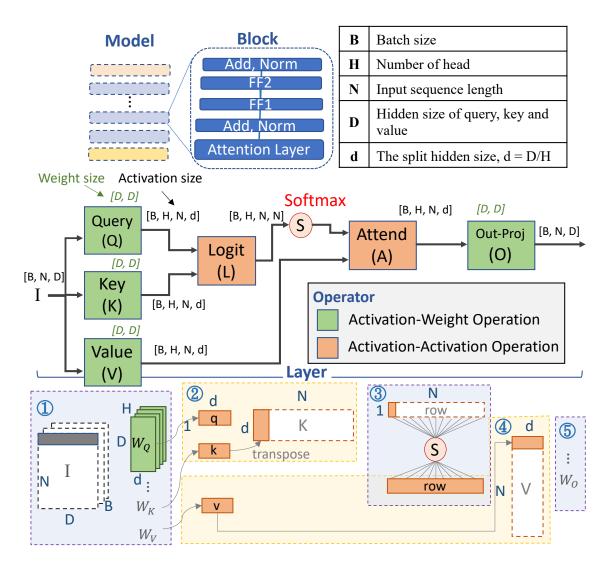

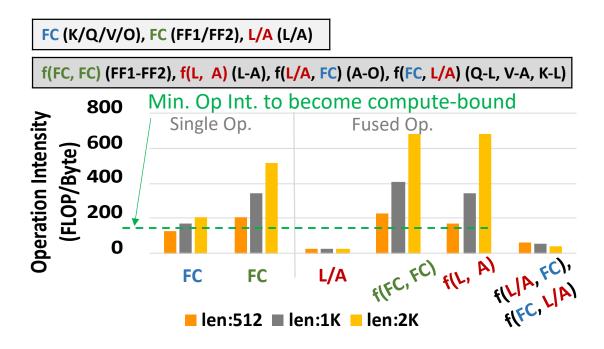

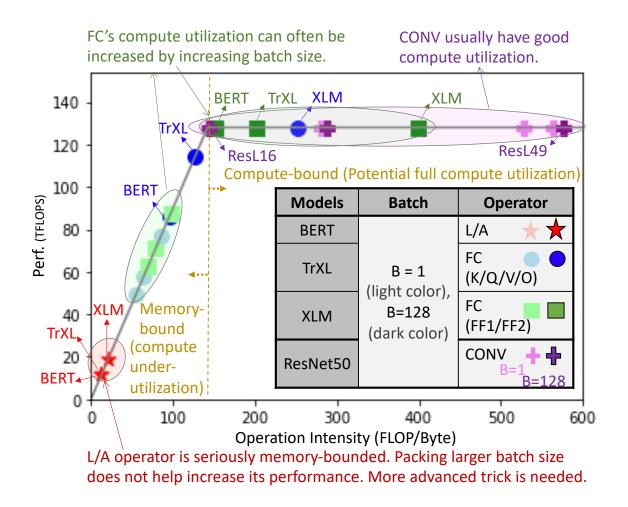

#### 1.1.3 Scalability of MSE