### EFFICIENT LEARNING FOR HARDWARE SECURITY VALIDATION USING ELECTROMAGNETIC SIDE CHANNELS

A Dissertation Presented to The Academic Faculty

By

Erik J. Jorgensen

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Machine Learning in the School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2022

© Erik J. Jorgensen 2022

#### EFFICIENT LEARNING FOR HARDWARE SECURITY VALIDATION USING ELECTROMAGNETIC SIDE CHANNELS

Thesis committee:

Dr. Alenka Zajić, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Matthieu Bloch, Co-Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. David Anderson School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Mark Davenport School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Milos Prvulovic School of Computer Science Georgia Institute of Technology

Dr. Mikko Lipasti Department of Electrical and Computer Engineering University of Wisconsin - Madison

Date approved: August 10, 2022

For Maggy!

This thesis would not exist without the guidance and support of many people. Prof. Alenka Zajić and Prof. Milos Prvulovic took a chance bringing me into the lab and seeing my path toward a doctorate when I was still seeing only one day ahead. I am wholly appreciative for them having taken that chance and further building me into an independent researcher. Any forethought or organization in my research and writing is due largely to their influence.

I also thank my committee members who each have had great impact on my experience and direction throughout my ongoing training in research. I thank Prof. Mikko Lipasti for patiently molding my skills in research and encouraging me to aim higher than I thought made sense. I thank Prof. Mark Davenport for generating enough excitement about signal processing at Georgia Tech to make me want to move out of my comfort zone in the Midwest; and continue when it wasn't always easy. I also want to thank Prof. Matthieu Bloch and Prof. David Anderson for evolving my interests in machine learning through their teaching, mentorship, and kindness toward students.

I need to thank my labmates and friends, both current and former, for helping me stay motivated, keeping things light, and helping me work through countless silly mistakes. I never pictured myself moving to the Southeast, but thank you all for making this whole thing fun. And to Jihui for all the fun we had grading or keeping me afloat in coursework; while constantly being a sounding board for all things research, jobs, and life.

I want to thank my family for all their support and love as I took my time finding out where I'm headed. I thank my brother and sister for clearing the brush so I could find my own trails in life. I thank my parents for their support in every way imaginable, even when I decided to move half the country away. Finally, I thank Nicole for making the choice to follow me when I didn't know where we were going, under circumstances that would have turned away any person less selfless, to learn and grow together far from home.

## TABLE OF CONTENTS

| Acknow    | vledgments                                                                                                  | iv |

|-----------|-------------------------------------------------------------------------------------------------------------|----|

| List of 7 | Tables                                                                                                      | ix |

| List of l | Figures                                                                                                     | xi |

| Summa     | ry                                                                                                          | xv |

| Chapte    | r 1: Introduction                                                                                           | 1  |

| 1.1       | Motivation                                                                                                  | 1  |

| 1.2       | Deep Learning Classification of Motherboard Components by Leveraging EM Side-Channel Signals                | 2  |

| 1.3       | Feature Selection for Non-Destructive Detection of Hardware Trojans us-<br>ing Hyperspectral Scanning       | 3  |

| 1.4       | Hyperspectral Image Recovery via Reliability-Weighted Compressed Sens-<br>ing for Hardware Trojan Detection | 5  |

| 1.5       | Research Contributions                                                                                      | 7  |

| 1.6       | Thesis Outline                                                                                              | 7  |

| Chapte    | r 2: Background                                                                                             | 9  |

| 2.1       | Counterfeit Components                                                                                      | 9  |

| 2.2       | Hardware Trojans                                                                                            | 11 |

| 2.3    | Electro | omagnetic Side Channel                                                                       | 13 |

|--------|---------|----------------------------------------------------------------------------------------------|----|

| 2.4    | Hypers  | spectral Imaging                                                                             | 16 |

| 2.5    | Comp    | ressed Sensing                                                                               | 17 |

| Chapte |         | ep Learning Classification of Motherboard Components by Lever-<br>ng EM Side-Channel Signals | 20 |

| 3.1    | Overvi  | iew                                                                                          | 20 |

| 3.2    | Structu | ured signals                                                                                 | 21 |

|        | 3.2.1   | Component excitations                                                                        | 22 |

|        | 3.2.2   | Features for classification                                                                  | 22 |

| 3.3    | Prepro  | cessing and model architecture                                                               | 25 |

|        | 3.3.1   | Preprocessing                                                                                | 25 |

|        | 3.3.2   | CNN Architecture                                                                             | 28 |

| 3.4    | Experi  | mental design                                                                                | 29 |

|        | 3.4.1   | Device hierarchy                                                                             | 30 |

|        | 3.4.2   | Cross-validation                                                                             | 30 |

|        | 3.4.3   | Measurements                                                                                 | 33 |

|        | 3.4.4   | Anomaly Detection                                                                            | 34 |

|        | 3.4.5   | Training parameters                                                                          | 35 |

| 3.5    | Result  | s and Interpretability                                                                       | 36 |

|        | 3.5.1   | Classification results                                                                       | 37 |

|        | 3.5.2   | Interpreting results                                                                         | 41 |

| 3.6    | Conclu  | usions                                                                                       | 44 |

| Chapter |        | ture Selection for Non-Destructive Detection of Hardware Tro-<br>s using Hyperspectral Scanning       | 46 |

|---------|--------|-------------------------------------------------------------------------------------------------------|----|

| 4.1     | Overvi | ew                                                                                                    | 46 |

| 4.2     | Dorma  | Int Hardware Trojan Detection                                                                         | 47 |

|         | 4.2.1  | Hardware Trojan Threat Model                                                                          | 47 |

|         | 4.2.2  | Backscattering EM Side Channel                                                                        | 49 |

|         | 4.2.3  | Hyperspectral Imaging                                                                                 | 50 |

|         | 4.2.4  | HT Detection Baselines                                                                                | 51 |

| 4.3     |        | rel Feature Selection Strategy for Hardware Trojan Detection using spectral Scanning                  | 56 |

|         | 4.3.1  | Feature Pre-Filtering                                                                                 | 57 |

|         | 4.3.2  | Active Sampling                                                                                       | 58 |

|         | 4.3.3  | Hyperspectral Dormant HT Detection Algorithm                                                          | 60 |

| 4.4     | Trojan | Design and Hyperspectral Measurement Setup                                                            | 61 |

|         | 4.4.1  | Circuit Designs                                                                                       | 62 |

|         | 4.4.2  | Backscattering Measurement Setup                                                                      | 66 |

|         | 4.4.3  | Preprocessing of Measured Data                                                                        | 68 |

| 4.5     | Valida | tion                                                                                                  | 68 |

|         | 4.5.1  | Single Board Performance                                                                              | 70 |

|         | 4.5.2  | Multi-Board Performance                                                                               | 71 |

|         | 4.5.3  | Sampling Reduction                                                                                    | 72 |

| 4.6     | Conclu | isions                                                                                                | 75 |

| Chapter | •      | perspectral Image Recovery via Reliability-Weighted Compressed<br>using for Hardware Trojan Detection | 77 |

| 5.1     | Overv   | iew                                                             | 77  |

|---------|---------|-----------------------------------------------------------------|-----|

| 5.2     | Dorma   | ant Hardware Trojan Detection                                   | 78  |

|         | 5.2.1   | Compressed Sensing                                              | 78  |

|         | 5.2.2   | Backscattering EM Side Channel                                  | 80  |

| 5.3     | HT De   | etection with Compressive Hyperspectral Scanning                | 81  |

|         | 5.3.1   | Hyperspectral Image Recovery with Reliability-Weighted Sampling | 81  |

|         | 5.3.2   | CS Recovery Bases                                               | 84  |

|         | 5.3.3   | Dormant Trojan Detection                                        | 87  |

| 5.4     | Trojan  | Design and Hyperspectral Measurement Setup                      | 88  |

|         | 5.4.1   | Circuit Design                                                  | 88  |

|         | 5.4.2   | Measurement Setup                                               | 90  |

| 5.5     | Experi  | mental Validation                                               | 91  |

|         | 5.5.1   | HT Detection Performance                                        | 91  |

|         | 5.5.2   | Reconstruction Analysis                                         | 93  |

| 5.6     | Conclu  | usions                                                          | 96  |

| Chapte  | r 6: Re | search Contributions and Future Work                            | 98  |

| 6.1     | Resear  | rch Contributions                                               | 98  |

| 6.2     | Future  | Research Directions                                             | 101 |

| Referen | ices .  |                                                                 | 104 |

## LIST OF TABLES

| 3.1 | Component models and counts across different device types and component classes. Blank boxes indicate that the device does not have that component. All devices come from the OLinuXino line of development boards and all processors are in the ARM Cortex line. Memory and ethernet chips are abbreviated to the first eight characters for space.                                                           | 29 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Number of component measurements across all device types in the train-<br>ing, validation, and test sets for each component class. These constitute an<br>approximate 10%, 30%, 60% split for the training, validation, and test sets<br>respectively with a total of 273 distinct components                                                                                                                  | 37 |

| 3.3 | Absolute difference of median CNN prediction accuracy over $k$ -NN accuracy across all component classes and excitation states. Positive values mean the CNN outperformed the $k$ -NN baseline                                                                                                                                                                                                                 | 38 |

| 3.4 | Classification metrics averaged across 10 trials for each component model<br>and excitation type. Shown is the number of ICs of each component model<br>in the test set, True Positive Rate (TPR), True Negative Rate (TNR), False<br>Positive Rate (FPR), and False Negative Rate (FNR) for both excitation<br>states. Component types are group by row and model names are abbrevi-<br>ated where necessary. | 40 |

| 3.5 | Classification metrics for anomaly detection averaged across 10 trials for<br>memory ICs in an excited state. Each group of five rows represents an<br>individual memory IC model being removed from training and treated as<br>unknown. Shown are the True/False Positive/Negative rates and per-model<br>classification accuracy.                                                                            | 42 |

| 4.1 | Relative size of trigger circuitry versus the uninfected circuit, measured by the number of adaptive logic modules.                                                                                                                                                                                                                                                                                            | 64 |

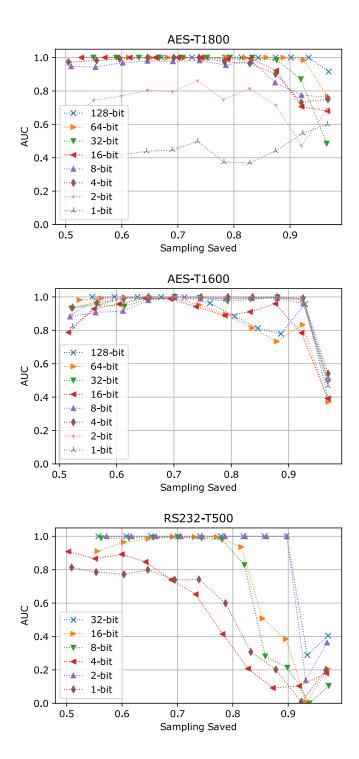

| 4.2 | HT detection performance as the area under the receiver operating charac-<br>teristic curve (AUC) on a single DE0-CV board for each circuit with the<br>HT trigger monitoring a given number of bits. The HT RS232-T500 moni-<br>tors a 32-bit counter, so it is not tested for larger triggers. HTs are detected<br>nearly perfectly for all Trojan types and trigger sizes, except for the small-<br>est AES-T1800 1-bit Trojan. | 71 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3 | HT detection performance (AUC) trained on multiple DE0-CV boards for each circuit with the HT trigger monitoring a given number of bits. HTs are detected more consistently than prior work [25] for the majority of tested circuits, but expectedly less well than when trained on a single board                                                                                                                                 | 72 |

| 5.1 | Relative size of trigger circuitry compared to the resources used by the full uninfected circuit, measured as the number of adaptive logic modules                                                                                                                                                                                                                                                                                 | 89 |

| 5.2 | HT detection performance for each reconstruction basis, compared against prior results on the AES-T1800 circuit with trigger monitoring a given number of bits.                                                                                                                                                                                                                                                                    | 93 |

## LIST OF FIGURES

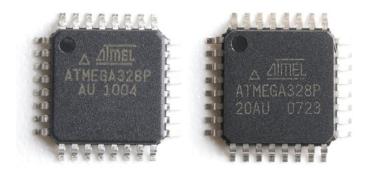

| 2.1 | Integrated circuits with identical footprint and pinout, but a potential warn-<br>ing sign for counterfeiting given their distinct marking styles [38]                                                                                                                                                                                                                                                                                                                                                                           | 10 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

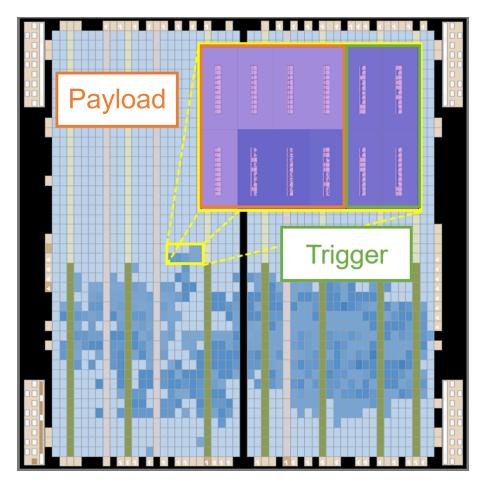

| 2.2 | Hardware Trojan payload and trigger layout hidden in an encryption circuit. Darker shaded blue blocks represent areas using greater logic and storage resources for the circuit when loaded onto an FPGA. This circuitry takes up approximately 0.7% and 0.6% of the area of the normal circuit resources for the Trojan's trigger and payload, respectively.                                                                                                                                                                    | 14 |

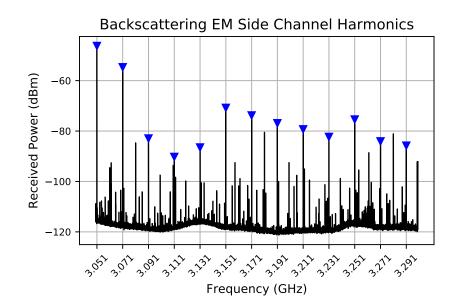

| 2.3 | Received power of backscattered electromagnetic signal with harmonics above the transmitted frequency $f_t = 3.031$ GHz, separated by the device's clock frequency $f_c = 20$ MHz.                                                                                                                                                                                                                                                                                                                                               | 16 |

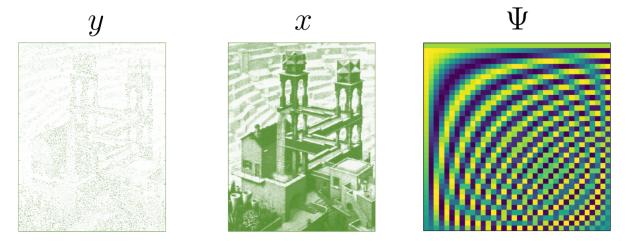

| 2.4 | Compressed sensing reconstruction of a 2-dimensional image from a sparse<br>set of randomly-sampled pixels using the discrete cosine transform basis<br>functions. Randomly sampled pixels (left) are recovered into the full image<br>(middle) using bases such as the one pictured (right), as adapted from [65].                                                                                                                                                                                                              | 19 |

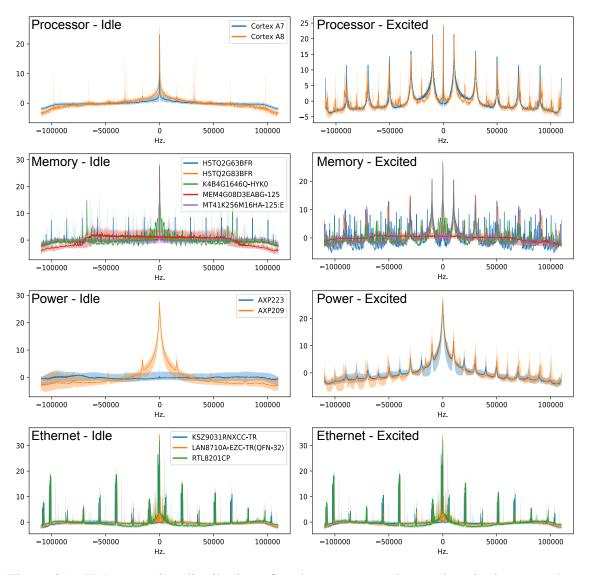

| 3.1 | EM emanation distribution of each component class and excitation state, horizontally centered by the component carrier frequency and with vertical axis converted to dB and mean subtracted. The median emanation measurement across all components of the same model is drawn with shading below and above corresponding to the 10% and 90% quantiles respectively. Components are measured in the idle (left) and excited (right) states. Both ethernet excitation states look identical but do differ, however imperceptibly. | 23 |

| 3.2 | Pseudo-code generating alternating X/Y excitation [66]                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24 |

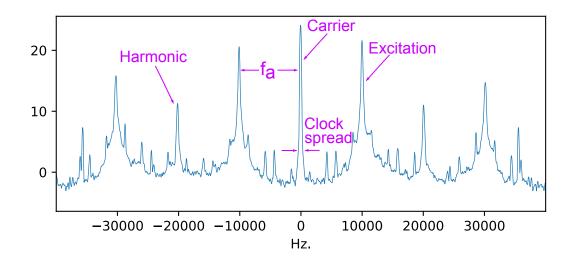

| 3.3 | Excited EM emanation frequency domain structure in decibel scale, set to zero-mean. The carrier frequency is downconverted to zero and shows a modest amount of spread due to clock frequency variation. Harmonics are present on both sides of the carrier, separated by the alternating frequency $f_a$ of the executed program. Odd harmonics are stronger than even harmonics since the program execution acts similarly to a square wave in the time domain. | 24 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

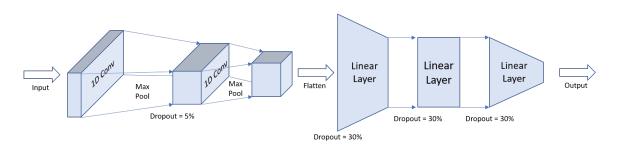

| 3.4 | High-level schematic of the CNN architecture depicting the convolution blocks (left) and fully-connected blocks (right).                                                                                                                                                                                                                                                                                                                                          | 27 |

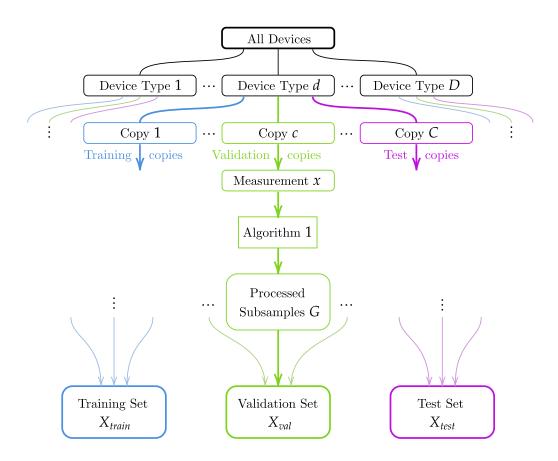

| 3.5 | Data breakdown and preprocessing pipeline. Device copies are broken into training (blue), validation (green), and test (magenta) groups for preprocessing and finally aggregated together with all other copies of their respective sets.                                                                                                                                                                                                                         | 31 |

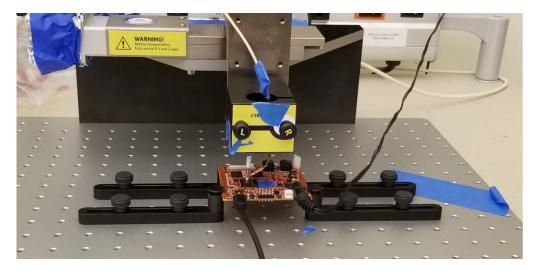

| 3.6 | Measurement setup for capturing EM emanations from components on moth-<br>erboards                                                                                                                                                                                                                                                                                                                                                                                | 33 |

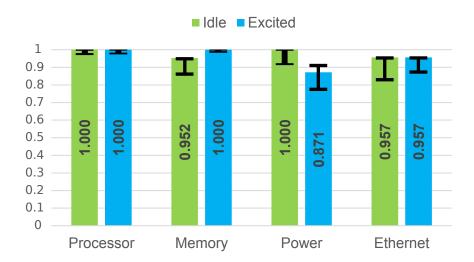

| 3.7 | Classification accuracy distributions across all four component classes in two excitation states each. Bar heights and inlaid number represent the me-<br>dian prediction accuracy across 10 trials, with bottom and top black mark-<br>ings representing the minimum and maximum accuracies respectively                                                                                                                                                         | 38 |

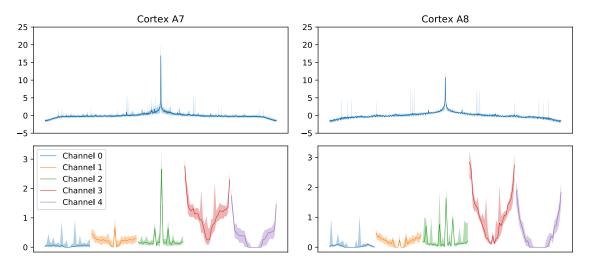

| 3.8 | Median of training set subsamples for processors in the idle state, scaled to dB and subtracted to zero-mean for each component model with shading below and above corresponding to the 10% and 90% quantiles respectively (top). The flattened output of the same median and shaded quantiles after passing through all convolution layers, just before entering linear layers (bottom).                                                                         | 43 |

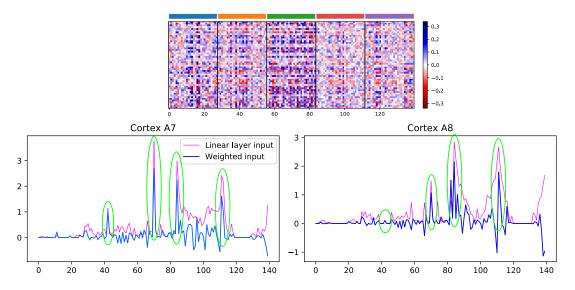

| 3.9 | First linear layer weights W with black vertical lines separating the weights that correspond to the convolution output channels as color-coded in Figure Figure 3.8 (top). Comparison of the inputs of each component model weighted by the sum of neuron weights (blue), overlaying the inputs (magenta) to the first linear layer (bottom). Weighted inputs with strong correlation (or anti-correlation) to inputs circled in green.                          | 44 |

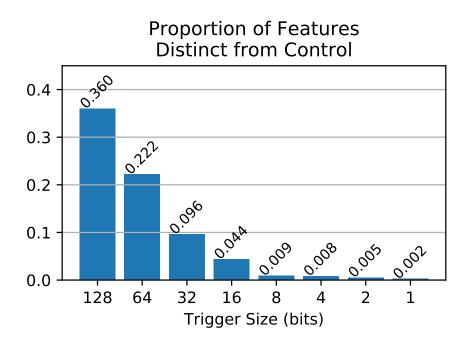

| 4.1 | Proportion of total hyperspectral features showing statistically significant difference between uninfected and infected AES-T1800 circuit                                                                                                                                                                                                                                                                                                                         | 49 |

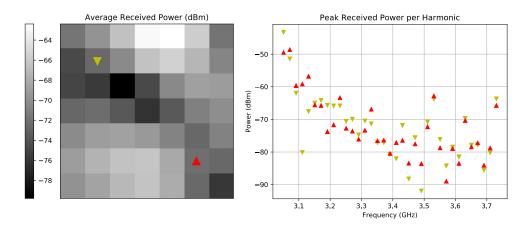

| 4.2  | Average backscattered EM side-channel power across an FPGA with two<br>points of equal power marked (left). Corresponding power across a 700<br>MHz span for the same points on the IC, showing unique spectral charac-<br>teristics (right).                                                                                                                                                                                                                                  | 52 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

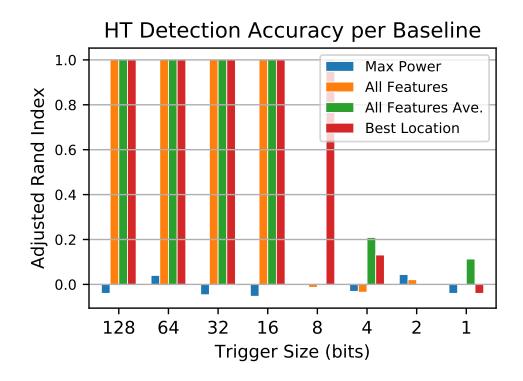

| 4.3  | Clustering performance (adjusted rand index $\in [-1, 1]$ ) between an unin-<br>fected and infected AES circuit for a range of trigger sizes with the four<br>baseline HT detection methods. Scanning at the maximum power location<br>was uninformative for HT detection, using all hyperspectral features de-<br>tects HTs smaller than prior work [25], averaging scans provides negligible<br>improvement, and the best possible location can unveil even smaller Trojans. | 53 |

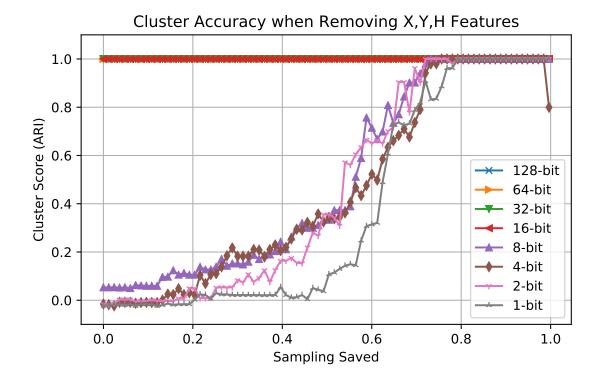

| 4.4  | HT detection accuracy when clustering as the number of features filtered out from the sampling set increases (resulting in less sampling from left to right), for Trojans with triggers of different sizes on the AES circuit                                                                                                                                                                                                                                                  | 55 |

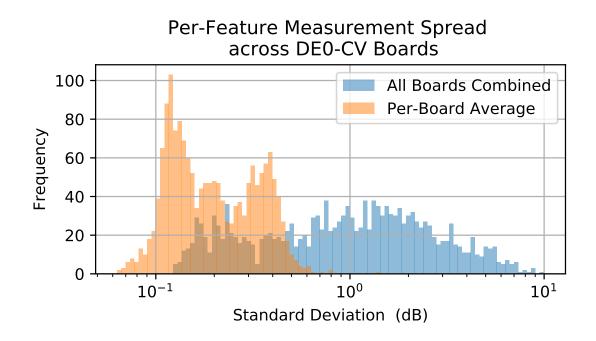

| 4.5  | Distribution of measured received power for hyperspectral point across all measured FPGA boards (blue) and averaged per board (orange).                                                                                                                                                                                                                                                                                                                                        | 59 |

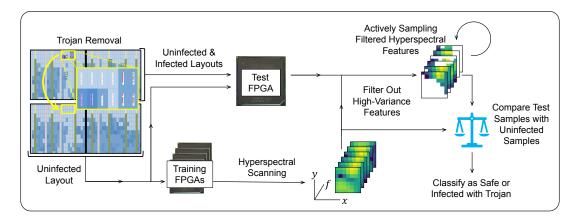

| 4.6  | Process flow diagram depicting the experimental setup, methodology, and validation of the methods in this chapter.                                                                                                                                                                                                                                                                                                                                                             | 62 |

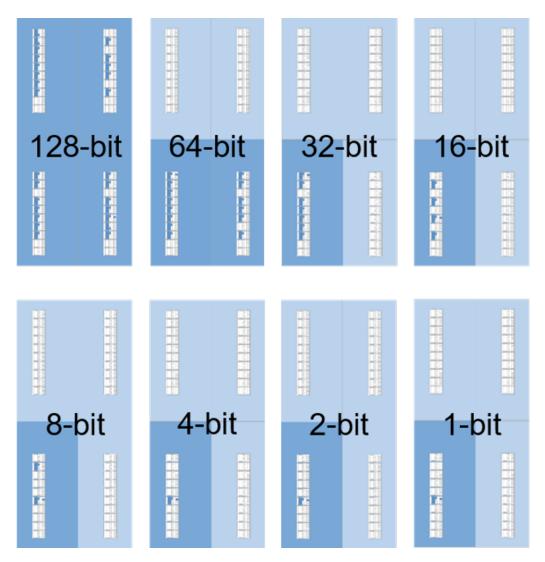

| 4.7  | FPGA allocation of adaptive logic modules for different size triggers. The 4-, 2-, and 1-bit triggers have minute differences that are not visible at this scale                                                                                                                                                                                                                                                                                                               | 63 |

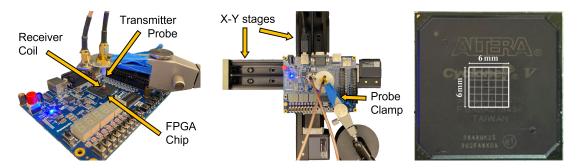

| 4.8  | Hyperspectral scanning measurement setup with DE0-CV board and high-<br>resolution probe (left), X-Y movement stages (middle), and FPGA IC die<br>dimensions (right).                                                                                                                                                                                                                                                                                                          | 67 |

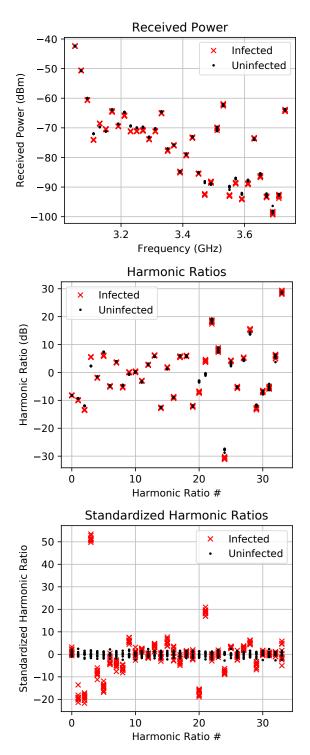

| 4.9  | Effect of preprocessing steps on ten scans of real measurement data from<br>the AES-T1800 circuit with 128-bit trigger, starting from the measured<br>power for an uninfected and infected circuit across several frequencies at<br>a single physical location on the chip (top), to power differences between<br>neighboring frequencies (middle), to standardized power differences (bot-<br>tom).                                                                           | 69 |

| 4.10 | HT detection performance for three tested circuits as the number of features filtered out from the sampling set increases (resulting in less sampling from left to right).                                                                                                                                                                                                                                                                                                     | 73 |

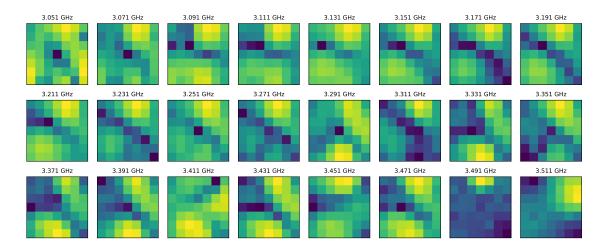

| 5.1 | Normalized spatial measurements of the backscattered EM side-channel signal for the first 24 harmonics above the incident 3.031 GHz signal. Harmonics generally exhibit smooth spatial variation. Variation between between frequencies is generally less smooth at higher harmonics                                                                                                                                                                                                  | 81 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

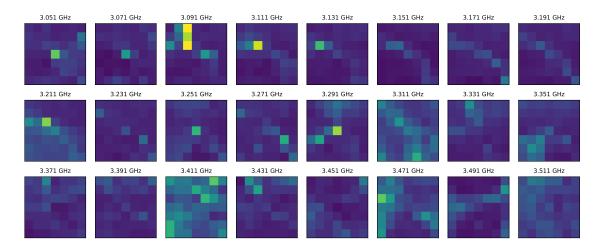

| 5.2 | Reliability-weighted sampling distribution $p_{\text{reliability}}(x, y, h)$ of the backscat-<br>tered EM side-channel signals for the first 24 frequencies above the incident<br>3.031 GHz signal. Larger values correspond to hyperspectral locations that<br>will be sampled with greater likelihood due to the features' lower reliabil-<br>ity across ICs there. Sampling emphasis is generally focused toward local<br>minima of the backscattered EM signal for each frequency | 85 |

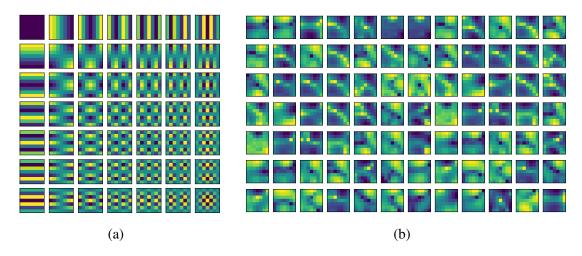

| 5.3 | Example 7x7 two-dimensional basis functions for the (a) DCT and (b) dic-<br>tionary bases learned from spatial slices of hyperspectral backscattering<br>side-channel images captured of uninfected ICs.                                                                                                                                                                                                                                                                              | 87 |

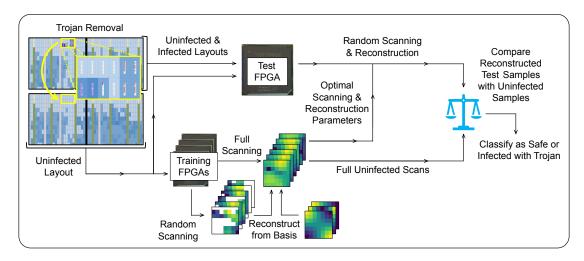

| 5.4 | Flow diagram depicting the circuit layout design, random hyperspectral sampling, image reconstruction, and Trojan detection process in this chapter.                                                                                                                                                                                                                                                                                                                                  | 88 |

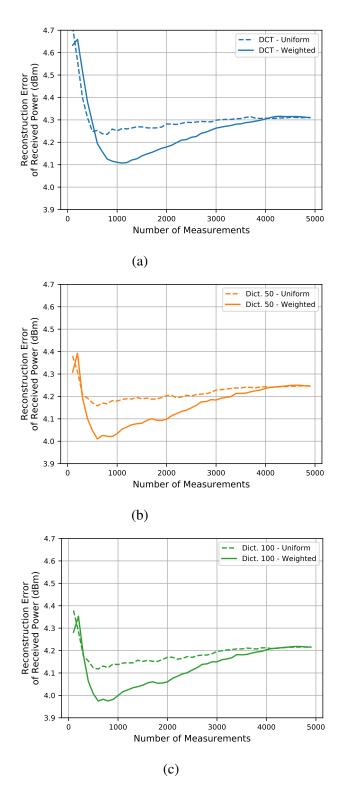

| 5.5 | Image reconstruction error for uniform random sampling compared to our reliability-weighted sampling method for the DCT bases (a), learned dictionary with 50 bases (b), and learned dictionary with 100 bases (c)                                                                                                                                                                                                                                                                    | 94 |

#### SUMMARY

The objective of this thesis is to combine the non-destructive monitoring advantages of standard and backscattering electromagnetic side channels with modern machine learning techniques to efficiently validate the authenticity of individual integrated circuits installed on a motherboard.

The authenticity of integrated circuits is of increasing concern as more steps in the device manufacturing supply chain are outsourced, especially in light of severe global semiconductor shortages. Common methods for integrated circuit validation rely on either destructive techniques before high resolution imaging of the circuit interconnects or functional testing of a variety of test inputs with automated test equipment. These methods are time-consuming or even intractable to detect counterfeit components or stealthy modifications of their underlying circuitry.

Side channels are any means of remotely leaking information related to a circuit's activity or architecture. Our work takes advantage of the electromagnetic (EM) side channel to remotely capture identifying information emitted from or backscattered off integrated circuits in the form of EM signals that can be used to validate their authenticity.

This research attempts to alleviate the need for time-consuming and expensive destructive validation methods for hardware security by robustly detecting inauthentic or modified integrated circuits with remote EM side-channel measurements. The first aim of this research is to apply deep learning methods to classify and detect counterfeits of major ICs on a variety of motherboards. The second aim is to leverage hyperspectral scanning with the backscattered EM side-channel and a novel active learning method to detect dormant hardware trojans several times smaller than before. The last aim is to develop a compressed sensing approach to heavily reduce sampling for hardware trojan detection as well as to develop a hyperspectral characterization of expected and anomalous circuits.

# CHAPTER 1 INTRODUCTION

#### 1.1 Motivation

As companies choose to outsource more steps in the electronic device manufacturing pipeline, the authenticity of the integrated circuits contained on those devices becomes of increasing concern. A device designer cannot trust the origins of its devices blindly due to the ever-increasing number of entities involved in their development and manufacture. A fabricated IC is vulnerable to potentially malicious actors across the design, fabrication, testing, packaging, and other stages. It is estimated that counterfeit ICs represent about 1% of semiconductor sales [1], resulting in losses in excess of \$100 billion annually [2]. Recent semiconductor shortages worldwide are expected to exacerbate the counterfeiting problem. The integrated circuit (IC) supply chain involves several steps with components passing through the facilities of several companies, often in different countries, on the route from a silicon foundry to the electronic device delivered to a customer. Anywhere along that supply chain, malicious actors could introduce counterfeit or otherwise modified ICs in place of the components intended to be placed. Even more, firmware or bitstream modifications could have a similar effect even if the IC is the exact hardware expected. These suspicious IC intrusions could be as simple as the use of a cheap alternative IC posing as the real thing to cut costs, or as severe as the inclusion of hardware Trojans (Trojans or HTs) introduced at the silicon foundry covertly change the circuit's expected behavior. In applications of critical importance like for devices used in infrastructure, military, or healthcare, these inauthentic or modified ICs present a severe risk to both safety and security.

To detect these suspicious ICs, it is common to analyze components through physical or electrical inspection techniques. Thorough physical inspection typically requires destructive defacing of the chip, layer-by-layer, to capture high resolution images of internal circuitry for validation of the layout [3]. Electrical inspection techniques can involve lengthy automated tests that test a set assortment of cases that may not uncover counterfeit ICs or malicious activity on the IC [4]. Side-channel methods have received significant attention for their ability to remotely capture information leaking from devices that can be used to fingerprint them. While certain side channels have been demonstrated to fingerprint entire devices or even some modifications to the ICs on those devices, non-destructive methods are still needed to detect individual inauthentic components or covert modifications to the components.

This thesis demonstrates learning strategies to non-destructively detect counterfeit or inauthentic components at a significantly smaller scale than has been achieved in literature thus far, to the best of our knowledge. Paired with high bandwidth side-channel measurements, this research develops novel methods to detect counterfeit integrated circuits and efficiently uncover hardware Trojans at a scale not previously possible.

## **1.2 Deep Learning Classification of Motherboard Components by Leveraging EM** Side-Channel Signals

It is well known that electronic components leak information through several different "side channels." When a digital device is powered on, this information leakage could arise as variations in acoustic noise [5], temperature [6], power consumption [7], electromagnetic (EM) emanation [8], or any other information leakage through empty space [9]. The conductive traces on a device and inside integrated circuits act as antennas when the electrical current running through them is changing. It has been shown that these changes in current can emanate significantly more information about device activity than the other side channels listed previously [10], [11]. Known as the EM side channel, this information leakage through electromagnetic waves caused by circuit activity has traditionally been cause for security concern by being exploited to steal confidential information [8], [10], [12], [13].

At the same time, these EM side-channel emissions have also been used for identifying devices from the scale of vehicles [14], [15] down to cellphones or microcontrollers [16], [17]. While these EM side-channel techniques have shown success for classifying entire devices, they have not been shown to identify individual ICs or components embedded on those devices.

There is no established state-of-the-art solution to the problem of non-destructively identifying individual components on an *assembled* motherboard from EM side-channel signals. While there has been work to classify single components or entire motherboards based on their EM signatures [18], [16], to our knowledge, there has been no work on classifying components already integrated onto a motherboard. This testing scenario is crucial for device designers, who need to validate that the components on their devices have not been replaced with counterfeits somewhere in the device supply chain before delivering their product to customers.

We present a deep learning strategy to classify components on already-assembled motherboards by leveraging their EM side-channel emanations. With this method, a variety of integrated circuit components are classified from their EM emanations using a lightweight convolutional neural network (CNN) architecture that we specifically design for this datascarce scenario with high-dimensional measurements. Analyzing input signals as they pass through our model allows us to generate insights about the most important discriminative features for classifying each component type and model. Our results demonstrate that we can classify a diverse set of ICs accurately in a practical scenario.

# **1.3** Feature Selection for Non-Destructive Detection of Hardware Trojans using Hyperspectral Scanning

Hardware Trojans are malicious and unauthorized circuitry modifications made to integrated circuits. Like counterfeit components, HTs represent a great security threat that can be introduced at several stages of the device supply chain. These Trojans can be responsible for locking devices, leaking secure information, draining battery, or a host of other changes that can have devastating consequences [19], [20], [21], [22]. When embedded into circuits at the silicon foundry or packaging stages of the device supply chain, these hardware modifications can supersede secure software that relies on a trusted hardware platform. Alternatively, these Trojans may have similar effects by being loaded onto a field programmable gate array (FPGA) through an inconspicuously corrupted bitstream [23], [24]. Thus, detecting ICs whose security has been compromised by a Trojan is of critical importance before those devices have been deployed or the Trojan activated.

No matter their origin, HTs are designed to be stealthy and difficult to detect by routine automated functional testing by activating under rare circumstances [19]. A typical HT is designed with a *trigger* that monitors circuit behavior or inputs before activating a *payload* that executes whatever malicious activity the Trojan is designed to do. A dormant Trojan which has not yet been activated does not modify normal circuit behavior or draw significant power. This makes it particularly hard to detect without destructive testing methods that look at circuit trace architectures with high resolution. Non-destructive detection methods such as side-channel analysis often rely on monitoring for significant changes in current or power consumption to detect when a Trojan is activated. However, detecting a Trojan before its activation is much more valuable due to the grave concerns about the damage that they can inflict when activated.

One method, using the backscattering EM side channel, has shown some success detecting dormant HTs before their activation [25]. This backscattering HT detection method draws inspiration from radio frequency identification (RFID) systems which modulate an incoming signal to transmit information through the signal that reflects back to the transceiver [26], [27]. Similarly, this HT detection method transmits a signal at an IC and captures the reflected (backscattered) waves that will by modulated by a combination of circuit trace architecture and program activity. With large enough Trojans, the difference in transistor architecture between an uninfected and Trojan-infected circuit can be distinguished by the structure of those backscattered signals. Unfortunately, that method was only able to detect large dormant trojans and required tedious manual probing to uncover each type of Trojan's presence. Without *a priori* knowledge of the size of the Trojan or locations on an IC at which it would most reveal itself, that backscattering method may be difficult to implement in the real world.

To overcome the shortcomings of those existing non-destructive HT detection methods, we develop a novel approach to detect dormant HTs through intelligent sampling of hyperspectral backscattering EM side-channel measurements. We spatially scan the IC across space and frequency with a high-resolution probe to generate point-scanned hyperspectral images of the backscattered EM signal. We develop a novel filtering and active learning strategy to greatly reduce the large feature space and selectively capture scans of features based on the confidence of their measurements. This method improves our ability to detect dormant hardware Trojans of much smaller sizes than in prior work.

## 1.4 Hyperspectral Image Recovery via Reliability-Weighted Compressed Sensing for Hardware Trojan Detection

While detecting hardware Trojans using hyperspectral measurements of the backscattering EM side-channel shows tremendous improvements in being able to detect significantly smaller dormant Trojans, it also requires the trade-off of requiring additional sampling time versus methods before it. One of the main benefits of non-destructive HT detection methods is generally their higher throughput compared to destructive methods. A destructive test can involve decapsulating an IC, capturing high resolution images of the surface, removing another layer of material, and repeating the process until the entire trace architecture is imaged [3], [28]. Then, those layered images are painstakingly compared to the IC's netlist-level design by skilled scientists; an entire process which is time-consuming and completely destroys the tested IC. A non-destructive test then has the obvious advantage of not needing to destroy the device under test (DUT), but also being able to make a classification of the IC within minutes or seconds based on its response to automated inputs or its side-side channel emanations. Point-scanning hyperspectral images, while non-destructive and highly effective at detecting small dormant Trojans, can be heavily time-consuming. As we demonstrate in [29], these measurements can potentially requiring an hour or more to scan a single IC. To maintain the benefits of hyperspectral scanning but reduce measurement time, we turn to compressed sensing.

Compressed sensing (CS) is a popular framework to recover high-dimensional images from relatively few samples in a variety of problem domains. CS enables the accurate recovery of signals even when sampling far less than the Shannon-Nyquist rate, assuming the data is sparsely represented in some basis [30],[31]. In the hyperspectral domain, CS is typically used to recover two-dimensional images at visible or near-visible light frequency at tens of frequencies [32], [33]. Due to measurement hardware constraints, capturing high resolution images of the backscattering EM side channel can only be done by pointscanning; one pixel at a time. Thus, we focus on a less-common version of CS which captures individual pixels of an image, uniformly at random, and reconstructs them into full images. However, the differences in hyperspectral measurements caused by small, dormant Trojans are very sparse and not necessarily structured spatially [29]. Sparse uniform random sampling for image recovery with compressed sensing is likely to miss these defects.

To increase the likelihood of uncovering the EM disturbances caused by a dormant hardware Trojan while also maintaining the measurement reduction benefits of a compressed sensing scheme, we develop a non-uniform sampling method that weights sampling toward unreliable measurement regions. This sampling strategy maintains sampling randomness to follow the compressed sensing framework and allows the strategy to recover the backscattered EM side-channel signals more quickly and more accurately. Doing so heavily reduces measurement requirements while maintaining or improving on HT detection performance.

#### **1.5 Research Contributions**

This section outlines a summary of the main contributions of this thesis.

- A method for device designers to non-destructively validate the identity of components and detect unseen components on already-assembled devices [34].

- A novel deep learning architecture, pre-processing, and validation strategy to ensure classification robustness in high-dimensional, data-scarce scenarios using electro-magnetic side-channel signals [34].

- Feature activation map modeling to compare discriminative features learned by the deep network with conventional hand-crafted spectral features [34].

- A hyperspectral point-scanning methodology for measuring IC fingerprints with the backscattering EM side channel [29].

- State-of-the-art non-destructive detection of hardware Trojans as small as 0.03% of the circuit size [29], [35].

- An active learning and feature selection approach to for capturing and comparing hyperspectral images of the backscattering EM side channel [29],

- A reliability-weighted compressed sensing technique for recovering point-scanned hyperspectral images with heavily reduced measurement requirements using up to ten times fewer measurements than previous efforts [35].

#### 1.6 Thesis Outline

The remainder of this thesis is organized as follows. chapter 2 discusses the background of counterfeit ICs, hardware Trojans, EM side channels, hyperspectral imaging, and compressed sensing. chapter 3 discusses efforts to develop robust integrated circuit classification and counterfeit detection on assembled devices. chapter 4 details the first efforts at

Trojan detection with hyperspectral, backscattering EM side-channel signals. Chapter 5 presents a compressed sensing approach to hyperspectral imaging that attains state-of-the-art non-destructive Trojan detection performance. Finally, Chapter 6 draws conclusion to this thesis by summarizing our research contributions and discussing future areas of research.

# CHAPTER 2 BACKGROUND

#### 2.1 Counterfeit Components

A counterfeit integrated circuit is any semiconductor component that is misrepresented as an authentic version of another IC. These could be copies produced by unauthorized manufacturers, discontinued older models, recycled versions represented as new, or many other misrepresentations [36], [37]. These counterfeits may be placed in designs at many stages of the IC supply chain for intentionally malicious reasons, to lower costs, or simply due to negligence or ignorance. In fact, each third-party supplier or assembler in the device manufacturing pipeline introduces a potential vulnerability to counterfeit components being swapped in for their authentic counterparts. No matter their origin, these components can be unreliable, lead to inter-operability issues between software and hardware, and pose a safety and security risk. Components must be tested after the device's complete assembly to be sure that no counterfeits were introduced anywhere in the manufacturing pipeline.

Here we make a few assumptions about the potential threats that a counterfeit component poses. First, we assume that counterfeit components in our intended scenario have different underlying architecture. Counterfeit components with the same transistor architecture pose less of a threat since they should operate in the same way as the intended component, barring any manufacturing variabilities introduced by the counterfeiting supplier. Given a counterfeit with different underlying circuit trace or transistor architecture, the differences will result in variations of the EM side-channel emanations compared to the authentic component since the EM side channel is dependent on the antenna-like characteristics of traces. Even visually identical components with the same footprint and pinout like those shown in Figure Figure 2.1 may have transistor-level architecture differences that

Figure 2.1: Integrated circuits with identical footprint and pinout, but a potential warning sign for counterfeiting given their distinct marking styles [38]

could result in security vulnerabilities or affect performance characteristics.

Second, we assume the device's program activity is in the same state as the devices on which the model is trained. Our method validates the authenticity of hardware through sidechannel emanations that change depending on software activity. Component validation is most simple and reliable for the device designer to perform when the device is powered on in an idle state without loaded program activity. While it may be a stronger assumption to make for devices that are already deployed and in use, it is a standard assumption that the devices be tested after assembly by the device designer or another trusted entity. To ensure our method still can be useful after a device is deployed, we also test our method's performance when the device is running looping program activity to compare with prior work [39]. This looping program activity can be a good proxy for testing edge or internet of things devices that are designed to repeat the same activity monitoring or other repetitive task at all times. However, the validation that we present in this work is not necessarily possible when devices are running unknown programs because these programs can have significant effects on the EM side-channel emanations.

Finally, we assume that the device designer has possession of at least one component that could be a potential counterfeit swapped in for the original, authentic component. IC fabricators regularly iterate on their designs, so it is reasonable to assume knowledge of older IC models that pose a counterfeit risk due to their lower cost but similar design. The neural network model we present here extracts discriminating features from the EM sidechannel emanations of a known set of components and devices. The feature embeddings learned by the presented CNN are used to differentiate between known component models that could be swapped in as counterfeits. Deviation from the CNN's activations for known component models is used as an indicator to detect never-before-seen counterfeits through anomaly detection. While this method could work using measurements of multiple unrelated components, training with very similar components allows the network to learn sensitive yet robust discriminative features to detect those small differences.

#### 2.2 Hardware Trojans

At a smaller scale, components can also be compromised with hidden hardware trojans. Hardware Trojans present on a device represent a significantly more serious risk than simple design errors or natural runtime errors. While random errors may be accounted for with error correction code, HTs act covertly and adversarially which can have unforeseen effects on otherwise secure software. There has been much work to understand the threat that HTs pose [40], [21], [41] while also further understanding and characterizing their implementation [42], [43], [44], [45]. A device designer cannot trust the origins of its devices due to the number of entities involved in their development and manufacture. Much like a circuit counterfeit being replaced for the authentic chip, a fabricated IC is vulnerable to potentially malicious actors across the design, fabrication, testing, packaging, and other stages. Since all of these steps are typically completed by separate specialized entities, ICs fabricated in the most robust supply chains may be vulnerable to HT injection by bad individual, corporate, or political actors. A typical HT threat might modify the design of an application-specific integrated circuit (ASIC), digital signal processor, microprocessor, or other hardware at an untrusted foundry [20]. Even when a trusted designer securely develops circuit modules and generate their layouts using trusted design tools, sending the layouts to an untrusted foundry for manufacture leaves a window for potential modification

of the circuit layouts [46], [20]. Thus, it is necessary to perform final design verification of the functional IC to detect the presence of HTs that may be added in this pipeline.

A growing body of research focuses on analyzing the threat and implementation of HTs [40], [21], [41], [42], [44], [45]. Though traditionally these Trojans are thought of as trace- or transistor-level modifications to an integrated circuit, the recent prevalence of field programmable gate arrays (FPGAs) for prototyping or specialized critical applications also presents a risk for malicious Trojans inserted as firmware modifications through the FPGA's bitstream [23], [24]. Even if an FPGA's configurable logic blocks and programmable interconnects are not modified at the hardware level, the addition of covert Trojans into the bitstream can implement malicious logic independent of the hardware platform [24]. Though the performance gap between FPGAs and ASICs is reducing, FPGAs do not necessarily have the same circuit properties as ICs [23] and further investigation of HTs inserted into ASICs is necessary to validate detection techniques. However, the path length and resulting impedance changes caused by an inserted Trojan that affect EM side-channel emanations or reflections could still be present whether in an FPGA or ASIC [23], [41]. The Trojans analyzed in this work are implemented on FPGA platforms versus custom ASICs for reasons of practicality.

These malicious modifications are designed to be triggered by rare inputs or circuit activity so that the HT can avoid being detected in routine functional testing [21]. Their activation mechanism is known as a trigger and is paired with a payload that modifies the IC's original behavior, as shown for an example circuit in Figure Figure 2.2. As further detailed in [19] and [20], we analyze these rarely-activated Trojans that use what is called a *internally-activated, condition-based* triggering mechanism. As opposed to *externally-activated* triggers that require outside interaction or *always on* triggers that are inserted on rarely-used circuitry, these triggers use small additional circuitry on the IC to monitor a program state, sensor level, input pattern, or other combinational or sequential logic condition to activate the payload. Before activation by the trigger, the dormant payload does

not modify normal circuit behaviour, making it difficult to detect without thorough destructive testing. This trigger and payload design of HTs allows the larger payload circuitry to remain dormant while only a small bit of trigger circuitry is active. Small trigger circuits draw little enough current when dormant compared to the IC's normal circuitry to remain undetectable with power analysis methods. However, once triggered, that HT's payload can leak secure information, drain battery, or many other nefarious activities. The HT's malicious purpose may be functional or non-functional. A functional HT might change the value of the main circuit's outputs or communicate secure information externally while a non-functional HT may cause rapid battery drain or leak sensitive information through a side channel, among many other possibilities. Since the effects of an activated Trojan can be so devastating, it is critical to detect their presence before activation or, ideally, before the device is even deployed. Detecting a dormant Trojan has proven difficult without destructive testing methods that can uncover tiny circuit modifications from high resolution imaging. However, non-destructive methods like side-channel analysis have received more attention to develop strategies that can detect smaller and smaller Trojans.

#### 2.3 Electromagnetic Side Channel

EM side-channel signals are emissions due to changes in current in the ICs and conductive traces on electronic devices [10], [47]. When a component on a digital device is supplied power, the current-based EM emanations from the component follow consistent patterns based on a host of factors. Among any number of noisy variations in the signal, emanations change as a result of the component's signal activation or physical properties. With repeated excitation, such as a device clock signal or repeating code pattern, we expect to see emanations that are especially noticeable in the frequency domain. These emissions can show up as sharp spikes with harmonics in the frequency domain due to consistent transistor switching from a clock signal or looping program activity [9]. While the EM side channel has proven useful for fingerprinting devices based on their emanations due

Figure 2.2: Hardware Trojan payload and trigger layout hidden in an encryption circuit. Darker shaded blue blocks represent areas using greater logic and storage resources for the circuit when loaded onto an FPGA. This circuitry takes up approximately 0.7% and 0.6% of the area of the normal circuit resources for the Trojan's trigger and payload, respectively.

to changing current passing through their components, the static or inactive properties of devices will not naturally produce emanations at a similar power scale. IC resources that lack current flow will not leak significant emissions and are essentially hidden from the perspective of the traditional EM side channel or other current-based side channels [25]. More recently, impedance-based side-channel analysis has shown the ability to fingerprint devices based on their geometric and material properties as a whole.

At a large scale, impedance-based side-channel analysis has been used to fingerprint large metal parts by their response to piezoelectric stimuli to assess their manufacturing quality [48]. Until recently, similar methods had not been developed to probe devices or components at the scale of integrated circuits. The authors of [25] developed what is known as the backscattering EM side channel to reduce issues with noise and interference with the original EM side channel. That work draws inspiration from the way that RFID tags can transmit bits by switching between two antennas with different impedance [49]. The RFID reader's transmitted signal at frequency  $f_t$  acts as a carrier for the impedance of the tag that alternates at  $f_c$ , resulting in an amplitude-modulated signal returning bits of information back to the reader. Similarly, the backscattering EM side channel is captured by transmitting a signal which is modulated depending on the state of an IC. The backscattered signal reflects back differently depending on the transistors' states, which have different impedance when connected to a voltage source versus being grounded [50]. The reflected signal is captured with an EM probe and holds information about the transistor architecture of the circuitry, even without current passing through it. The majority of transistor switching occurs at the IC's clock frequency  $f_c$ ; picked up by a probe as modulated spikes in the frequency domain at  $f_t \pm f_c, \pm 2f_c, \ldots$  as shown in Figure Figure 2.3. Variations of these spikes occur depending on the specific circuit architecture and activity in the region of the probe. These variations may flag the presence of a Trojan in the circuit when compared against a reference signal. Circuits infected with dormant condition-based HTs can be detected through the backscattering EM side channel because their distinct transistor ar-

Figure 2.3: Received power of backscattered electromagnetic signal with harmonics above the transmitted frequency  $f_t = 3.031$  GHz, separated by the device's clock frequency  $f_c = 20$  MHz.

chitecture reflects EM signals differently than their uninfected circuit counterparts. While we do not test other types of internally-activated HTs in the following works, the addition of any Trojan that modifies the IC layout could potentially affect the backscattered signal enough to be detectable. The backscattering EM side channel has the main advantages over the original EM side channel of being impedance-based and being adjustable to avoid frequency bands with significant interference.

#### 2.4 Hyperspectral Imaging

Hyperspectral imaging (HSI) typically refers to the collection of many two-dimensional images at different frequency bands in the visible or near-visible light spectrum. While normal color photos are represented in 3-dimensional space with two spatial dimensions and one frequency dimension for the red, green, and blue channels, HSI captures tens or hundreds of frequencies in a 3-dimensional hypercube of data per image. While visible light HSI is typically used in fields such as geoscience [51] and biomedicine [52], [53],

some HSI techniques have been used to analyze the quality and composition of printed circuit boards [54], [55] for electronics recycling. HSI is typically performed in one of three ways: point-scanning, spectral scanning, and non-scanning imaging [56]. Point-scanning captures individual measurements across frequency, one at a time, and raster scanning in space to capture the whole data hypercube. Spectral scanning involves capturing an entire 2D spatial scene at a single frequency before physically switching or tuning the sensors to the next frequency and repeating. Finally, non-scanning or snapshot imaging captures the entire hypercube at once through projected acquisition and subsequent reconstruction back to the correct perspective [57]. Unfortunately, these well-researched HSI techniques with visible or near-visible light do not penetrate an IC's packaging to fingerprint an integrated circuit.

With existing high resolution probes, the backscattered EM side-channel has been shown to pass through an IC's packaging and reflect back differently based on the underlying trace architecture [58]. Given those constraints, point-scanning must be used to create non-traditional hyperspectral images of the backscattered EM side-channel signals needed to fingerprint ICs at a small scale. Unfortunately, the main drawback of pointscanning is the large increase in scanning time to capture entire hyperspectral images since the time physically move a probe is significant for high-dimensional images. On the other hand, point-scanning allows for flexibility in scans. Scans do not necessarily need to be made sequentially; left-to-right and top-to-bottom. Additionally, point-scanning allows for an arbitrary number of measurements at a fixed point in the spatio-spectral space. With this flexibility, we can investigate unique forms of measurement frameworks like compressed sensing.

#### 2.5 Compressed Sensing

A popular way of reducing measurement costs is to reconstruct images from very few measurements in a compressed sensing framework. Unlike iteratively selecting individual measurements as in an active sampling or reinforcement learning regime, CS takes advantage of an assumed underlying structure in the data's domain to allow sparse random sampling for reconstruction [31]. Many works used basis functions like the Fourier transform or discrete cosine transform (DCT) to approximate the smoothness and continuity of the data's domain [59]. For better reconstruction of natural images, other bases were developed that incorporated piece-wise smooth properties like various wavelet functions [60]. Further work showed that an overcomplete dictionary of bases learned from images similar to those being reconstructed often outperformed any of the former bases for which closed form analytical expressions exist [61], [62].

The CS framework can be represented with the standard linear model  $\mathbf{y} \approx A\mathbf{x}$  where  $\mathbf{y}$  is a vector of measurements,  $\mathbf{A}$  is a measurement sampling matrix and  $\mathbf{x}$  is a set of learned coefficients that represent the reconstructed image. Assuming  $\mathbf{x}$  can be sparsely represented by some set basis vectors  $\Psi$ , then this problem can be rewritten as  $\mathbf{y} = \mathbf{A}\mathbf{x} = \mathbf{A}\Psi\mathbf{s}$  where  $\mathbf{s}$  is the sparse coefficient vector reconstructing  $\mathbf{x}$  in that basis, meaning  $\mathbf{x} = \Psi\mathbf{s}$  as seen for an example image reconstruction problem in Figure 2.4. To ensure that the solution can be stably recovered,  $\mathbf{A}$  and  $\Psi$  should be incoherent, meaning they cannot sparsely represent the other. In practice,  $\Psi$  could be the Fourier, Wavelet, learned dictionary, or any other bases that are sparsifying for the signals to be reconstructed.  $\mathbf{A}$  is then incoherent with  $\Psi$  if it is structured for uniformly-random sampling. This binary matrix  $\mathbf{A}$  could be thought of as measuring a sparse random set of pixels which are then used to reconstruct the entire 2D image. In the heavily underdetermined setting where the number of samples is far fewer than the dimensionality of the data, the sparse recovery problem shown in (Equation 2.1) has a unique solution and can be solved with a standard LASSO solver [63], [64].

$$\min_{\mathbf{s}} \|\mathbf{s}\|_1 \quad \text{subject to} \quad \|A\Psi\mathbf{s} - \mathbf{y}\|_2 \le \epsilon \tag{2.1}$$

Figure 2.4: Compressed sensing reconstruction of a 2-dimensional image from a sparse set of randomly-sampled pixels using the discrete cosine transform basis functions. Randomly sampled pixels (left) are recovered into the full image (middle) using bases such as the one pictured (right), as adapted from [65].

#### **CHAPTER 3**

# DEEP LEARNING CLASSIFICATION OF MOTHERBOARD COMPONENTS BY LEVERAGING EM SIDE-CHANNEL SIGNALS

#### 3.1 Overview

As introduced in Chapter Chapter 1, there is no established non-destructive solution to the problem of accurately identifying individual components present on an already-assembled motherboard. While research has shown the ability to identify entire motherboards or large individual components based on their EM signatures [18], [16], to our knowledge there has been no success classifying components already integrated onto a motherboard. This scenario is important for device designers, who need ways of validating that the components on their devices have not been replaced by an untrusted third-party assembler or supplier with counterfeits.

Motivated by these shortcomings, in this work we develop a novel method to solve a variety of component identification tasks using fingerprints from their electromagnetic emanations. Here we train a single Convolutional Neural Network (CNN) architecture to solve several component identification tasks using measurements of their EM emanations in an idle and active state. We show that this approach can distinguish individual IC models within four general classes (processors, memory ICs, power management ICs, and ethernet transceivers). We choose these four component types due to the security threat they pose if counterfeited given their handling of potentially secure data. Additionally, the relative expense of these four compared to other component types like I/O connectors, capacitors, op-amps, etc. makes them more likely targets of counterfeiting. To demonstrate the robustness of our methods we also test our method's capabilities while the IoT motherboards these ICs reside on are operating in "Idle" and "Excited" conditions. This idle state is the most realistic scenario for component validation on an already-assembled device. Then we test on an excited state to demonstrate the performance of our method in a similar setting as [39]. We train our network with a random bootstrap sampling method of cross-validation to achieve more consistently accurate performance over that of a *k*-Nearest Neighbors baseline. We compare our method against a common off-the-shelf classifier (k-NN) since the problem has no established state-of-the-art solution. It is important to emphasize that we test classification accuracy on held-out devices separate from a training set, rather than subsampling measurements from the same device for training and testing. Additionally, we implement an anomaly detection procedure to show our design can be used to detect components on which the network was never trained. Finally, by examining the signals passing through the neural network, we build hypotheses about the features of different classes of ICs that make them most distinguishable. In doing so, we present a generic approach for accurate and interpretable component-level classification and counterfeit detection on IoT devices.

#### **3.2** Structured signals

When a component on a digital device is supplied power, EM emanations from the component follow consistent patterns based on a host of factors. Among any number of noisy variations in the signal, emanations change as a result of the component's underlying trace architecture and signal activation. With repeated excitation, such as a device clock signal or looping code pattern, we see emanations that are especially noticeable in the frequency domain. In this work, we measure emanations when the device is in an idle state and also when it is activated by a controlled, repeating code execution. This idle state emulates the primary intended use case of this work. Upon receipt of a newly fabricated device, the device designer powers it on to test a variety of functions and confirm the authenticity of its components with non-destructive scans of the EM side channel. We also test with a repeated code execution pattern to emulate the use case of testing the authenticity of a device already deployed and running a known piece of software. Here we discuss these states and the distinguishing features one may look for when understanding the emanated signal.

#### 3.2.1 Component excitations

When powering a device and simply remaining in an idle state, components exhibit minimal structure in their EM emanations besides a peak at the device's clock frequency, as seen in the top-left panel of Figure 3.1. However, with controlled code execution, components can exhibit more structured excitations that are directly related to the activity on the specific integrated circuit. To excite the component, we execute a repeating code pattern to generate amplitude modulation of the looping program activity with the clock frequency [9]. By repeating a pattern of two alternating code sequences (activity X and Y in Figure 3.2), we can control the modulating frequency and duty cycle of amplitude modulation on the device clock frequency. The program execution time spent in one loop versus the other controls duty cycle, while the total execution time of the pattern  $T_a$  controls the alternating rate  $f_a = \frac{1}{T_a}$ . That alternating rate shows up as amplitude modulated peaks (excitation) and harmonics on both sides of the centered carrier (clock) frequency,  $f_c$ . The result is a frequency domain pattern of spikes at frequencies  $f_c \pm f_a$  and their harmonics  $f_c \pm 2f_a$ ,  $f_c \pm 3f_a$ , ... with features marked in Figure 3.3.

## 3.2.2 Features for classification

As seen in each row of Figure 3.1, the distinguishing features of emanations may differ greatly between the idle and excited states. In the idle state, a hand-crafted classifier might extract features related to the clock frequency spread or the trail-off in the sidebands at the edges of the measurement bandwidth. Without color-coding the measurements as in the figure, reliably classifying the signals manually would be difficult. In the excited state, the same features displayed in the idle state are generally present. Additionally, the excited components may be distinguished by features such as the alternating frequency,

Figure 3.1: EM emanation distribution of each component class and excitation state, horizontally centered by the component carrier frequency and with vertical axis converted to dB and mean subtracted. The median emanation measurement across all components of the same model is drawn with shading below and above corresponding to the 10% and 90% quantiles respectively. Components are measured in the idle (left) and excited (right) states. Both ethernet excitation states look identical but do differ, however imperceptibly.

```

while(true) {

1

2

// Execute activity X

3

for(i=0; i<x count; i++) {</pre>

ptr1 = (ptr1 & ~mask1) | ((ptr1 + offset) & mask1);

4

5

// X instruction, e.g. a load operation

6

value = *ptr1;

7

}

8

// Execute activity Y

9

for(i=0; i<y count; i++) {</pre>

ptr2 = (ptr2 & ~mask2) | ((ptr2 + offset) & mask2);

10

11

// Y instruction, e.g. a store operation

*ptr2 = value

12

13

}

14

}

```

Figure 3.2: Pseudo-code generating alternating X/Y excitation [66].

Figure 3.3: Excited EM emanation frequency domain structure in decibel scale, set to zero-mean. The carrier frequency is downconverted to zero and shows a modest amount of spread due to clock frequency variation. Harmonics are present on both sides of the carrier, separated by the alternating frequency  $f_a$  of the executed program. Odd harmonics are stronger than even harmonics since the program execution acts similarly to a square wave in the time domain.

relative excitation and harmonic magnitudes, modulations on other unknown sources, and more. While these features are somewhat distinguishable in the idle and excited states when color-coded, it is clear that robust classification of these signals would be difficult by manual inspection. Additionally, given the high dimensionality of the signals, traditional classification models could suffer from the curse of dimensionality; meaning that the noise present throughout the signal overwhelms the ability of a classifier to find the sparse distinguishing features present. To solve these issues and distinguish the components reliably, we develop a preprocessing pipeline and neural network classifier fit for electromagnetic emanation measurements.

## 3.3 Preprocessing and model architecture

We develop a preprocessing pipeline that is implemented uniformly across eight datasets (four component types with two excitation patterns each) to decrease biases and analyze differences between different datasets. Additionally, we design a convolutional neural network (CNN) classifier to reduce dimensionality while maintaining important discriminatory features of the EM emanations. Here we detail the main preprocessing procedure and our CNN model architecture for classification.

## 3.3.1 Preprocessing