# Control Strategies for Improving Reliability and Efficiency in Modular Power Converters

#### **Dissertation**

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

(Dr.-Ing.)

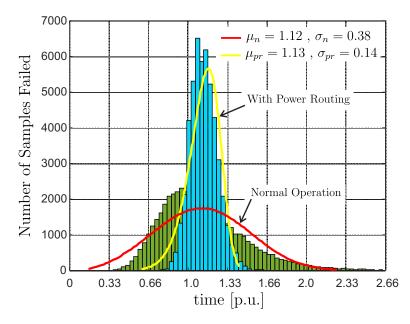

Technische Fakultät

der Christian-Albrechts-Universität zu Kiel

vorgelegt von

Vivek Raveendran, M.Sc.

*Kiel* 2022

Gutachter: Prof. Dr.-Ing. Marco Liserre

Gutachter: Prof. Dr.-Ing. Timm Faulwasser

3. Gutachter: Prof. Dr. Zoubir Khatir

Datum der mündlichen Prüfung: 30.03.2022

# Erklärung

Ich erkläre an Eides statt, dass ich die Dissertation zum Thema:

Control Strategies for Improving Reliability and Efficiency in Modular Power Converters

abgesehen von der Betreuung durch Herrn Prof. Marco Liserre selbstständig und ohne Hilfe angefertigt habe und bisher weder ganz noch zum Teil an einer anderen Stelle im Rahmen eines Prüfungsverfahrens vorgelegt, veröffentlicht oder zur Veröffentlichung eingereicht habe. Weiterhin versichere ich hiermit, dass ich die vorliegende Arbeit unter Einhaltung der Regeln guter wissenschaftlicher Praxis der Deutschen Forschungsgemeinschaft angefertigt habe und alle von anderen Autoren wörtlich übernommenen Stellen wie auch die sich an die Gedankengänge anderer Autoren eng anlehnenden Ausführungen meiner Arbeit besonders gekennzeichnet und die entsprechenden Quellen angegeben sind.

Kiel, den 10. Juni 2021

Vivek Raveendran

## Acknowledgement

This doctoral thesis was carried out as a part of 'The Highly Efficient And Reliable smart Transformer (HEART)' project under the European Union's Seventh Framework Program (FP/2007-2013)/ERC Grant Agreement [616344]. First of all, I would like to sincerely thank my supervisor Prof. Dr.-Ing. Marco Liserre for the opportunities and guidance received during my doctoral journey. His vision and thoughts have always inspired me, and I will cherish the learning for my future ventures. I am grateful to Prof. Dr.-Ing. Timm Faulwasser and Prof. Dr. Zoubir Khatir for being part of the PhD examination committee and for their valuable contributions.

I would like to specially mention Prof. Dr.-Ing. Giampaolo Buttichi and Dr.-Ing. Markus Andresen for giving fruitful insights and guidance that helped me to stay motivated and focused amidst the challenges. My sincere gratitude to all my co-authors for their support and collaboration which helped me to strengthen the research work.

I am thankful to my colleagues and staff at the Chair of Power Electronics for their support, guidance, discussions, and friendship during my time in Kiel. I would like to thank Pramod Kumar Prasobhu, who was always there as a colleague and friend. Special thanks to Xiang Gao and Luis Juarez for our technical and non-technical conversations, and above all, friendship.

I sincerely appreciate the trust and love of my parents and brother who supported me whole-heartedly during my time abroad, without which, I could not have pursued my passion. Last but not least, I would like to thank the special person in my life who backed and trusted me at every stage of this endeavour, my wife Anagha.

Kiel, October 2022

Vivek Raveendran

Contents

# **Contents**

| Ger | man s    | summai   | ry                                                                 |

|-----|----------|----------|--------------------------------------------------------------------|

| Eng | glish s  | ummar    | y                                                                  |

| Use | d syn    | nbols aı | nd abbreviations                                                   |

| 1   | Intro    | oductio  | n                                                                  |

|     | 1.1      | Impor    | tance of Power Electronics Reliability                             |

|     | 1.2      | Motiva   | ation for Modular Power Converters                                 |

|     | 1.3      | Motiva   | ation for Optimal Power Flow Solutions                             |

|     | 1.4      | Resear   | rch Proposal                                                       |

|     | 1.5      | Struct   | ure of the Thesis                                                  |

|     | 1.6      | List of  | f Publications                                                     |

| 2   | Reli     | ability  | in Power Electronics                                               |

|     | 2.1      | Power    | Semiconductor Reliability                                          |

|     | 2.2      | Condi    | tion Monitoring for Power Devices                                  |

|     | 2.3      | Progn    | ostic Maintenance in Power Electronics                             |

|     | 2.4      | Active   | e Thermal Control Strategies                                       |

|     |          | 2.4.1    | Device Level                                                       |

|     |          | 2.4.2    | Modulator Level                                                    |

|     |          | 2.4.3    | System Level                                                       |

|     | 2.5      | Physic   | es-of-Failure based Lifetime Analysis                              |

|     |          | 2.5.1    | Reliability Metrics                                                |

|     |          | 2.5.2    | Motivation for the adoption of PoF based approach                  |

|     |          | 2.5.3    | Lifetime Modeling of Power Semiconductor Devices                   |

|     |          | 2.5.4    | Mission Profile Based Reliability Analysis                         |

|     | 2.6      | Monte    | e-Carlo based Reliability Analysis                                 |

| 3   |          |          | ower Converters: Applications and Graph Theory Representation 38   |

|     |          |          | w of Modular Power Converters                                      |

|     |          | 3.1.1    | CHB                                                                |

|     |          | 3.1.2    | MMC                                                                |

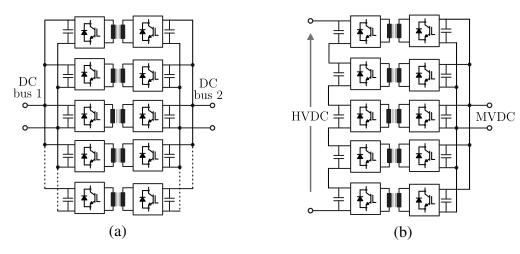

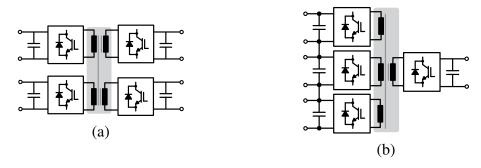

|     |          | 3.1.3    | Modular Dual Active Bridge Topologies                              |

|     |          | 3.1.4    | Multiple Active Bridge Topologies                                  |

|     | 3.2      | Motiva   | ation for the Application of Graph Theory in Modular Converters 42 |

|     |          | 3.2.1    | Reliability Challenge and Power Routing Technique                  |

|     |          | 3.2.2    | Review of Reliability and Efficiency Optimization Algorithms in    |

|     |          |          | Power Electronics                                                  |

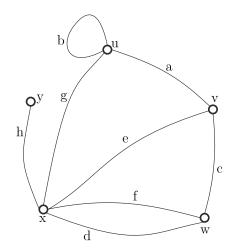

|     | 3.3      | Funda    | mentals of Graph Theory                                            |

|     | 3.4      |          | -Theoretic Representation of Modular Power Converters              |

|     |          | 3.4.1    | Graph-Theoretic Definitions                                        |

|     |          | 3.4.2    | Graph Theory Representation of Selected Modular Topologies 48      |

|     | 3.5      |          | cation of Modular Power Converters in Smart Transformers 50        |

|     | <b>.</b> | 3.5.1    | Concept of Smart Transformers                                      |

|     |          | 3.5.2    | Application of Graph Theory in ST Architectures                    |

|     |          | -        |                                                                    |

II Contents

|     | 3.6  | Brief Summary of the Chapter                                             | 58 |

|-----|------|--------------------------------------------------------------------------|----|

| 4   | Sys  | m Level Active Thermal Control by Power Routing                          | 59 |

|     | 4.1  | Reasons for Unequal Aging in Modular Converters                          | 59 |

|     |      | 4.1.1 Impact of Parameter Variations on Converter Lifetime               | 60 |

|     | 4.2  | Power Routing for Modular Systems                                        | 62 |

|     |      | 4.2.1 Analysis of Power Routing on Series Connected Modular Topologies   | 64 |

|     |      | 4.2.2 Analysis of Power Routing on Parallel Connected Modular Topologies | 66 |

|     | 4.3  | Power Routing Capability of Modular Converters                           | 69 |

|     |      | 4.3.1 Power Routing Capability of CHB with Sinusoidal PWM                | 69 |

|     |      | 4.3.2 Power Routing Capability of CHB with Direct Modulation             | 72 |

|     | 4.4  | Virtual Resistance based Power Routing of Modular Converters             | 75 |

|     |      | 4.4.1 Virtual Resistance based Power Routing for IPOP Modular Converters | 75 |

|     |      | 4.4.2 Virtual Resistance based Power Routing for Multi-Stage ISOP Mod-   |    |

|     |      | ular Converters                                                          | 82 |

|     | 4.5  | Summary of the Chapter                                                   | 91 |

| 5   | Gra  | h Theory Based Optimal Power Flow Solutions                              | 93 |

|     | 5.1  | Review of Graph Theory Algorithms                                        | 93 |

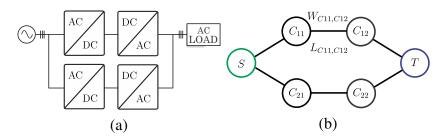

|     |      | 5.1.1 Network Flow Problem in Graph Theory                               | 94 |

|     | 5.2  | Multi-Objective Algorithms for Optimal Power Routing                     | 96 |

|     |      | 5.2.1 Efficiency and Reliability Improvement Algorithm for the ST Appli- |    |

|     |      | cation                                                                   | 96 |

|     |      | 5.2.2 Graph Theory based Algorithm Focusing on Maintenance Schedul-      |    |

|     |      | ing of ST                                                                | 08 |

|     |      | 5.2.3 Optimization Algorithm for Improved Reliability in More Electric   |    |

|     |      | Aircraft                                                                 | 13 |

|     | 5.3  | Summary of the Chapter                                                   | 22 |

| 6   | Mod  | ulator based Implementation of Power Routing                             | 24 |

|     | 6.1  | State-of-the-art Modulation based Junction Temperature Control Methods   |    |

|     |      | for Modular Converters                                                   | 24 |

|     | 6.2  | Principle, Applicability and Validation of ADPWM                         | 25 |

|     | 6.3  | Summary of the Chapter                                                   | 32 |

| 7   | Sun  | mary, conclusion and future research                                     | 33 |

|     | 7.1  | Summary                                                                  | 33 |

|     | 7.2  | Conclusion                                                               | 35 |

|     | 7.3  | Future research                                                          | 37 |

| 8   | Ref  | rences                                                                   | 39 |

| App | endi | es                                                                       | 57 |

| A   | Mod  | eling of Selected Converter Topologies                                   | 57 |

|     | 1.1  | Inverter Modeling                                                        | 57 |

|     | 1.2  | CHB Modeling                                                             | 58 |

|     | 1.3  | DAB Modeling                                                             | 60 |

| В   | CH   | control system design                                                    | 63 |

| C   | Lab  | ratory experimental setups                                               | 66 |

## **Deutsche Kurzfassung der Arbeit**

Die Signifikanz von modularen Stromrichtern hat in verschiedenen Anwendungen wie der elektrischen Energieverteilung, industriellen Antrieben und More Electric Aircraft (MEA) aufgrund der Vorteile wie Skalierbarkeit, Designflexibilität, höherer Fehlertoleranz und besserer Wartung drastisch zugenommen. Darüber hinaus hat der Paradigmenwechsel des Geschäftsmodells in der Leistungselektronik vom Produktlieferanten zum umfassenden Serviceanbieter die Forschung im Bereich der Zuverlässigkeitstechnik in der Leistungselektronik verstärkt. In diesem Zusammenhang haben die Herausforderungen für den zuverlässigen Betrieb modularer Stromrichter und die Lösungen zur Verbesserung ihrer Zuverlässigkeit in den letzten Jahren die notwendige Aufmerksamkeit erhalten. Wartungszyklen in modularen Systemen führen zu einem System von Stromrichterzellen mit unterschiedlicher Alterung. Ein System mit unterschiedlich gealterten Zellen birgt die Gefahr von Mehrfachwartungen, geringerer Zuverlässigkeit und Verfügbarkeit sowie hohen Wartungskosten. Um die auf thermischer Belastung basierende Alterung modularer Stromrichter zu kontrollieren, wurde eine Power-Routing Strategie vorgeschlagen. Die vorliegende Arbeit befasst sich mit den verschiedenen Implementierungsstrategien des Power Routings für modulare Stromrichter. Leistungshalbleiter sind eine der zuverlässigkeitskritischsten Komponenten in Stromrichtern, und thermische Beanspruchung - Temperatur und Temperaturwechsel - wurde als Hauptursache für deren Ausfall identifiziert. Diese Arbeit konzentriert sich auf die Algorithmen zur Verbesserung der Zuverlässigkeit von Leistungshalbleitern. Im Vergleich zu einzelnen Stromrichtern haben modulare Stromrichter eine große Anzahl von Komponenten, die aufgrund von Fertigungstoleranzen und unterschiedlichen Betriebsbedingungen mit unterschiedlichen thermischen Spannungen arbeiten. Die Auswirkung solcher Parametervariationen von Leistungshalbleitern auf die thermische Belastung und folglich auf die Lebensdauer des modularen Systems wird im Detail untersucht. Um die Lebensdauer des Systems zu verbessern, wurden auf virtuellen Widerständen basierende Power-Routing-Algorithmen für einstufige und mehrstufige modulare Architekturen durch Simulationen untersucht und mit Experimenten validiert. Basierend auf der Graphentheorie wird ein einheitlicher Rahmen für das Routing der Leistung in komplexen modularen Wandlerarchitekturen definiert. Beliebte Umrichterarchitekturen für Smart Transformer (ST) und MEA Anwendungen werden als Graphen modelliert, um als Grundlage für die Entwicklung der Leistungsflussoptimierung zu dienen. Die Wirksamkeit der Graphentheorie für die Optimierung des Leistungsflusses in modularen Systemen wird mit Hilfe von drei Algorithmen demonstriert. Der erste Algorithmus konzentriert sich auf die Verbesserung der Zuverlässigkeit des ST ohne Einschränkung der Effizienz. Der zweite Algorithmus hat das Ziel, die Wartungsplanung des ST durch Regelung des internen Leistungsflusses zu verwalten. Die Optimierung des Leistungsflusses zum Erreichen einer hohen Zuverlässigkeit für eine MEA-Anwendung wird im dritten Algorithmus untersucht. Modulationsstrategien für Stromrichter sind weit verbreitet, um ein Power-Routing auf Stromrichterebene zu erreichen. Ein fortschrittliches diskontinuierliches Modulationsschema, das für mehrstufige modulare Umrichter geeignet ist, wird diskutiert. Die Auswirkungen des Modulationsschemas auf die Lebensdauer von Stromrichterzellen in einer CHB-DAB Architektur werden durch Simulationen und Experimente validiert.

## **English Summary**

The significance of modular power converters has escalated drastically in various applications such as electrical energy distribution, industrial motor drives and More Electric Aircraft (MEA) owing to the benefits such as scalability, design flexibility, higher degree of fault tolerance and better maintenance. Moreover, the paradigm shift of power electronics business model from product supplier to comprehensive service provider has boosted the reliability engineering research in power electronics. In this context, challenges for the reliable operation of modular power converters and the solutions for improving their reliability are getting the required attention over the past years.

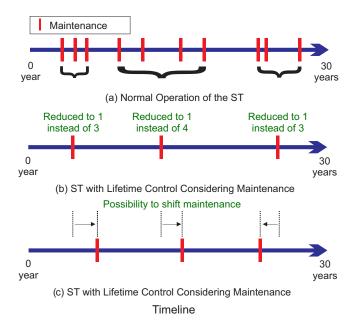

One of the main advantages of modular systems is the ability to replace the faulty converter cells during maintenance instead of the entire system. However, such maintenance cycles will result in a system of converter cells with different aging. A system with cells having different aging arises the threats of multiple maintenance, lower reliability and availability, and high maintenance costs. For controlling the thermal-stress based aging of modular power converters, power routing strategy was proposed. The thesis focuses on the different implementation strategies of power routing for modular converters.

Power semiconductors are one of the most reliability critical components in power converters, and thermal-stress; temperature and thermal cycling, has been identified as the main cause of their failure. This thesis work concentrates on the power semiconductor reliability improvement algorithms. Compared to single converters, modular power converters have large number of components which operates with different thermal-stress due to manufacturing tolerances and variations in operating conditions. The impact of such parameter variations of power semiconductors on the thermal-stress and consequently the modular system lifetime is studied in detail. For improving system lifetime, virtual resistor based power routing algorithms for single stage and multi-stage modular architectures have been investigated through simulations and validated with experiment.

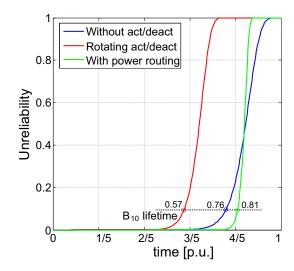

A unified framework for routing the power in complex modular converter architectures is defined based on graph theory. Popular converter architectures for Smart Transformer (ST) and More Electric Aircraft (MEA) applications are modeled as graphs to serve as the basis for developing power flow optimization. The effectiveness of graph theory for optimizing the power flow in modular systems is demonstrated with the help of three algorithms. First algorithm focuses on improving the reliability of ST without sacrificing the efficiency. Second algorithm has the objective of managing the maintenance scheduling of the ST by controlling the internal power flow. Power flow optimization for achieving high reliability for an MEA application is investigated in the third algorithm.

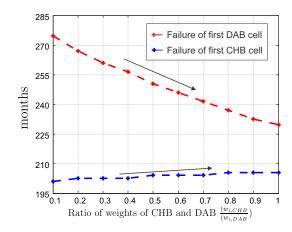

Power converter modulation strategies are widely employed for achieving power routing on converter level. An advanced discontinuous modulation scheme suitable for multi-stage modular converters is discussed. The impact of the modulation scheme on the lifetime of converter cells in a CHB-DAB architecture is validated through simulations and experiment.

## **General symbols**

#### **General symbols**

u(t) Instantaneous value

#### **Superscripts**

\* Reference value

th Order

#### **Subscripts**

dc DC-link related d related to diode

*i* index for converter cells sys system level parameter

x percentage of samples failed exp related to experimental result period related to the control period  $\eta$  efficiency related parameter

## **Special symbols**

\* Convolution  $t_r$  Rise time

$\beta$  Weibull parameter  $\hat{V_g}$  Peak grid voltage

$K_{Bayerer}$  Fitted parameter in Bayerer lifetime model

α Weibull parameter

$\alpha_{v}$  Coefficient of virtual resistor

$\beta_{\nu}$  Exponential coefficient of virtual resistor  $\beta_{1}$  Fitted parameter in Bayerer lifetime model  $\beta_{2}$  Fitted parameter in Bayerer lifetime model  $\beta_{3}$  Fitted parameter in Bayerer lifetime model  $\beta_{4}$  Fitted parameter in Bayerer lifetime model  $\beta_{5}$  Fitted parameter in Bayerer lifetime model  $\beta_{6}$  Fitted parameter in Bayerer lifetime model

$\Delta T_i$  Junction temperature swing

η Efficiency factor

$\lambda$  failure rate

$\lambda_m$  Maintenance interval factor  $\omega$  Grid frequency in radians  $\Psi_G$  Incidence function of graph G

ρ Reliability factor

$\theta$  Angular displacement between voltage and current

A(G) Adjacency matrix of graph G  $a_1$  Fitted parameter in lifetime model  $a_2$  Fitted parameter in lifetime model  $a_3$  Constant parameter in lifetime model

$B_x$   $B_x$  lifetime

C Thermal Capacitance  $C_{dc}$  Cell DC-link capacitance D Accumulated damage

$D_{bond}$  Diameter of bond wire of the power semiconductor device

$d_{diode}$  Duty cycle of anti-parallel diode

$d_{IGBT}$  Duty cycle of IGBT

*D<sub>ini,i</sub>* Initial accumulated damage

$D_{old}$  Total accumulated damage till last sample  $D_{period}$  Damage accumulated during current period

$\begin{array}{ccc} di & & \text{Change in current} \\ dt & & \text{Change in time} \\ dv & & \text{Change in voltage} \\ E(G) & & \text{Edges of graph } G \end{array}$

$E_{

m off}$  Turn-off energy of IGBT  $E_{

m on}$  Turn-on energy of IGBT  $E_{

m rec}$  Diode recovery energy

$E_{sw,igbt}$  Switching energy loss of IGBT for one switching instance

F(t) Unreliability at time t

$f_{sw,DAB}$  Switching frequency of DAB

$f_{sw}$  Switching frequency of power converter

$g_m$  Transconductance

I(G) Incidence matrix of graph G

$i_{device}$  Current flowing through device under consideration  $I_{rated,sys}$  Rated current of the modular converter system

$i_c$  Collector current of IGBT  $i_f$  Diode forward current

$K_{p,bal}$  Proportional constant of PI controller

$K_r$  Resonant controller gain

kA kiloampere kV kilovolt

$L_{i,j}$  Edge connecting nodes i and j

$L_g$  Line inductance

$LT_{exp}$  Expected remaining useful lifetime

*m* Modulation index

Number of cells in modular converter

*n* Order of thermal network

N(G) Nodes of graph G

$N_{un}$  Number of unloaded converter cells

$N_f$  Number of cycles to failure

$N_{fi}$  Durability of the *i*-th stress range

$N_i$  Number of cycles of the *i*-th stress range  $P_{\text{rec,diode,avg}}$  average reverse recovery diode losses

$P_{\text{sw,igbt,avg}}$  Average switching loss in IGBT

$P_{cond,device}$  Conduction loss of device under consideration

$P_{cond,diode,avg}$  Average conduction loss of diode  $P_{cond,IGBT,avg}$  Average conduction loss of IGBT

$P_{cond.IGBT}$  Conduction losses of IGBT

$P_{max}$  Maximum power unbalance limit  $P_{min}$  Minimum power unbalance limit

$P_{rated}$  Rated power of a converter

$P_{tot}$  Total loss of device under consideration

R Thermal resistance

r Number of Monte-Carlo simulations

R(t) Reliability at time t  $R_{th}$  Thermal resistance  $R_{v}$  Virtual resistor  $R_{g}$  Line resistance T Time period

$T_{bal}$  Integral time constant of PI controller

$T_{device}$  Junction temperature of device under consideration

*T<sub>hs</sub>* Heatsink temperature

$T_{i,av}$  Average junction temperature

$T_i$  Junction temperature

$t_{on}$  On-duration of power cycling test

$T_{on}$  On-time of a device in a switching period

$T_{sw}$  Switching period

$T_d$  Junction temperature of diode  $V_c$  Output DC voltage of H-bridge cell  $V_{ce,sat}$  Collector emitter saturation voltage

$V_{DC,i}$  DC-link voltage of cell i

$V_{device}$  Voltage range of the device in power cycling test

$V_g$  RMS grid voltage  $V_{GE,th}$  Gate threshold voltage  $V_f$  Diode forward voltage drop

$W_{i,j}$  Weight of edge connecting nodes i and j  $Z_{th,jhs}$  Thermal impedance from junction to heatsink

#### **Abbreviations**

ADPWM Advanced Discontinuous Pulse Width Modulation

ATC Active Thermal Control

CBM Condition Based Maintenance

CCSN Center-Clamped Side-Non clamped CDF Cumulative Distribution Function

CHB Cascaded H-bridge CL Constant Loads

CM Condition Monitoring

CNSC Center-Non clamped Side-Clamped CTE Coefficient of Thermal Expansion

DAB Dual Active Bridge

DBC Direct Bonded Copper

DER Distributed Energy Resource

EMI Electro-Magnetic Interface

FEM Finite Element Method

FTA Fault-Tree Analysis

HVDC High Voltage Direct Current

IGBT Insulated Gate Bipolar Transistors

IPOP Input Parallel Output Parallel

ISOP Input Series Output Parallel

ISOS Input Series Output Series

LED Light Emitting Diode

LESIT Leistungs Elektronik Systemtechnik und Informations Technologie

LFT Low Frequency Transformer

LVAC Low Voltage Alternating Current

LVDC Low Voltage Direct Current

MAB Multiple Active Bridge

MAB Multiple Active Bridge MEA More Electric Aircraft

MMC Modular Multilevel ConvertersMPC Model Predictive ControlMTTF Mean Time To Failure

MVAC Medium Voltage Alternating Current

MVDC Medium Voltage Direct Current

NPC Neutral Point Clamped PCB Printed Circuit Board

PDF Probability Density Function

PDS Power Distribution System

PI Proportional Integral

PMSM Permanent Magnet Synchronous Machine

PoF Physics-of-Failure

PR Proportional Resonant

PRC Power Routing Control

PV Photo-Voltaic

PWM Pulse Width Modulation

QAB Quadruple Active Bridge

RUL Remaining Useful Lifetime

SM Sub-Module

ST Smart Transformer

SST Solid-State Transformer

THD Total Harmonic Distortion

TSEP Temperature Sensitive Electrical Parameter

UPS Uninterrupted Power Supply

VL Variable Loads

ZCS Zero Current Switching ZVS Zero Voltage Switching

## 1 Introduction

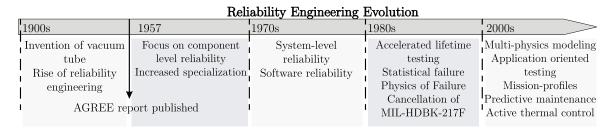

Past decades have witnessed a radical change in the key performance indicators of power electronics systems. Apart from efficiency and power density, reliability has become the third pillar for the design in power electronic applications [1, 2]. The main focus of power electronics research over the years has been the improvement of efficiency and power density driven by power device technologies, magnetic solutions, topologies and control schemes. Motivated by carbon emission reduction policies worldwide, power electronics has emerged as the backbone of numerous industrial sectors such as renewable energy generation and distribution, electric vehicles, more electric aircraft, smart grids etc [3]. The business model of power electronics applications from mere product suppliers to comprehensive service providers has motivated the designers and researchers to give necessary importance to reliability engineering to guarantee reliable operation during the product life-cycle [2]. The evolution of reliability engineering in power electronics over the years illustrated in Fig. 1.1 depicts the gained momentum of reliability research in recent years.

In this context, this thesis work aims to investigate the impact of control strategies to optimize the reliability of the modular converter systems without compromising the efficiency. The importance of power electronics reliability and the application of modular power converters are motivated in this chapter. The necessity of an optimization control strategy through the management of power flow among the modular converter cells is explained to formulate the research proposal of the thesis. The final section of the chapter presents the structure of the thesis including the list of publications resulting from this work.

## 1.1 Importance of Power Electronics Reliability

Reliability is defined as the ability of an item to perform its designated function for the specified period under the given conditions [4, 5]. The reliability is usually measured using reliability metrics such as the probability of failure, frequency of failure, or availability of the item. The automotive and aerospace sectors demand very high reliability constraints since the failures could potentially result in fatal accidents. In the energy sector, power electronics based Smart Transformer (ST) is a promising solution for the various challenges posed by the high renewable energy penetration. However, ST needs to meet the high reliability standards set by its counterpart, the Low Frequency Transformer (LFT) [6].

Figure 1.1: Evolution of reliability engineering over the years [2].

In general, the methodology of reliability engineering in power electronics can be broadly divided into three steps: 1) understanding the reasons of the failure with the help of analytical and empirical models, 2) reliability-oriented design of the system to account for the application specific stressors, and 3) active methods involving condition monitoring and control to enhance the reliability during the life-cycle of the product [6, 7]. As shown in Fig. 1.1, the reliability analysis heavily depended on the failure statistics in the past. Today, it is well-established that the pure statistics-based constant failure rate reliability methods are not relevant to power electronics systems as they do not address the cause of failure. Therefore, the Physics-of-Failure (PoF) approach has been introduced in power electronics to understand the physical causes of the failure and to evaluate the power electronics reliability systematically [1]. Based on the PoF approach, many industrial and academic studies have identified that the main challenges for the reliability in power electronic systems are the power semiconductors and capacitors [8, 9]. The failure mechanisms of the power devices and capacitors have been thoroughly studied in the literature leading to the development of many lifetime models. The major cause for the failure of the power semiconductor devices has been identified as the thermal stress caused by the thermal cycling [9, 10, 11].

The methods for reliability improvement in power electronics can be broadly classified into two categories, 1) passive methods, and 2) active methods [12, 7]. The passive methods mainly focus on designing the hardware of the power converters for enhanced reliability. Such approaches evaluate the reliability of critical components according to the application specific mission profile and lifetime requirements. Reliability-oriented design mainly focuses on optimizing the hardware design for fulfilling the lifetime criteria, and could potentially increase the cost of total hardware [2, 13, 14]. The active methods are mainly software based methods to actively control the failure causes of critical components. In contrast to the reliability-oriented design, the active methods such as the software based Active Thermal Control (ACT) uses the existing hardware and uses control algorithms to reduce the thermal stress of the power devices [15, 16, 12]. Software based thermal stress control methods can be deployed with marginal requirement of additional hardware and even could potentially be incorporated into the existing converter systems resulting in a cost effective solution.

In this thesis, active methods for improving the reliability of the power electronics system are investigated in detail due to their cost-effectiveness and the ability to respond to changes in the working condition of the converter.

#### **1.2 Motivation for Modular Power Converters**

The concept of modularity is not new and it has been widely employed in different fields such as automotive, computer technologies, electric power distributions, solar panels etc. primarily due to the offered benefits such as scalability, re-usability, cost-effectiveness, design flexibility, and augmentation [17, 18, 19, 20]. The motivation for the use of modular solutions in the field of power electronics arises from a multitude of reasons. The main benefits of modular architecture can be summarized as follows.

- Better availability due to a higher degree of fault tolerance and potential derated operation

- Potential increase in efficiency

- Voltage and power scalability

- Superior power quality

- Reduced voltage and current stress (dv/dt) and di/dt

- Decrease in filter size and reduced Electro-Magnetic Interface (EMI) emission

The Smart Transformer employs a multi-stage modular architecture to compete with the high reliability and efficiency benchmarks set by the LFT [6]. The studies show that the use of a lower blocking voltage power device can result in better efficiency compared to the higher blocking voltage devices [21, 22]. Moreover, the voltage and current scalability offered by the modular solutions combined with the unavailability of a single semiconductor power module for the medium voltage applications drives the industry to adopt modular architectures for high power applications [23]. For example, Modular Multilevel Converters (MMC) is one of the main topologies for high voltage applications such as High Voltage Direct Current (HVDC) transmission [17, 18].

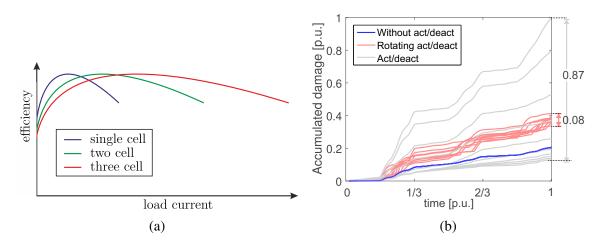

Modular topologies/architectures increase the degree of failure tolerance and facilitate post fault operation without system shutdown [24, 25]. The faulty building block/cell of the modular converter can be replaced with another cell during maintenance [6, 26]. The cost of an additional building block to increase redundancy is much lower than that of adding redundancy to a non-modular system. Moreover, reduced voltage/power stress in the modular converter architectures also decreases the probability of failures [25]. With respect to efficiency, the reduced output filter size in modular architectures increases the system efficiency. The superior electrical parameters of the lower blocking voltage devices result in a better efficiency compared to the non-modular systems [22]. In the case of Input Parallel Output Parallel (IPOP) modular topologies, the light load efficiency is improved by deactivating the modular cells and this technique is popularly known as phase shedding [27].

In short, modular topologies are a necessity when the voltage levels are higher than the available power semiconductor blocking voltage limits. However, for high reliability and high efficiency applications, modular power converters offer cost-effective solutions with superior power quality and better maintenance opportunities.

## 1.3 Motivation for Optimal Power Flow Solutions

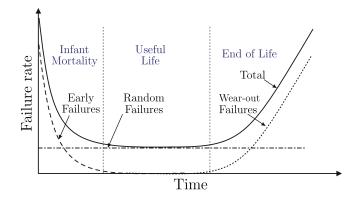

Even though modular converters offer higher flexibility of redundancy, the potential for efficiency improvement, and better maintenance opportunities, some challenges need to be addressed for high reliability applications. For any power electronics system, failures can be classified into random and wear-out based failures according to the bathtub curve [28]. To

1 Introduction

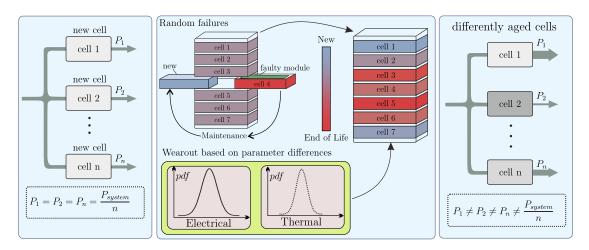

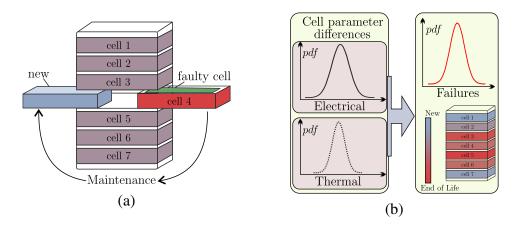

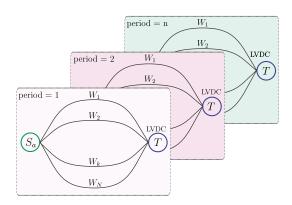

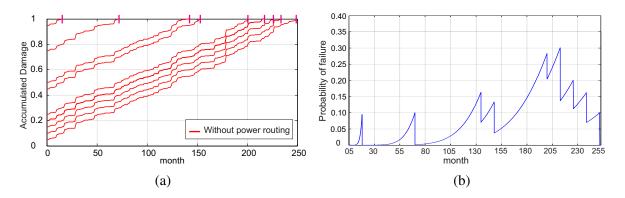

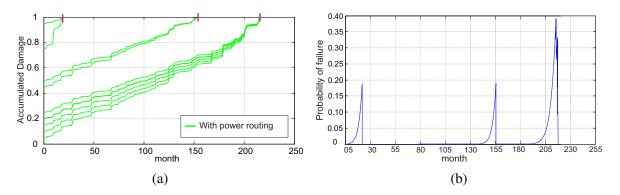

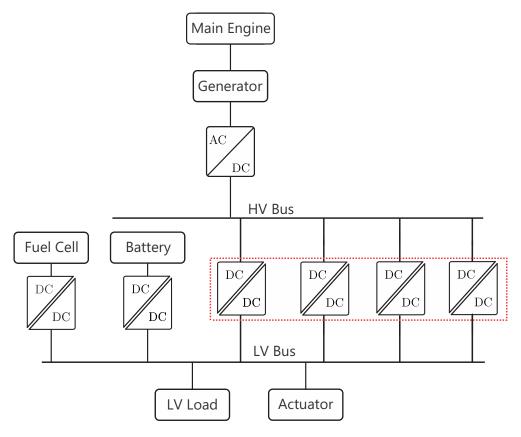

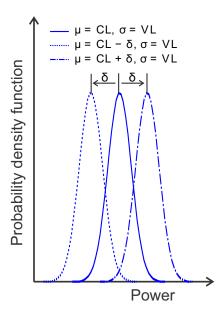

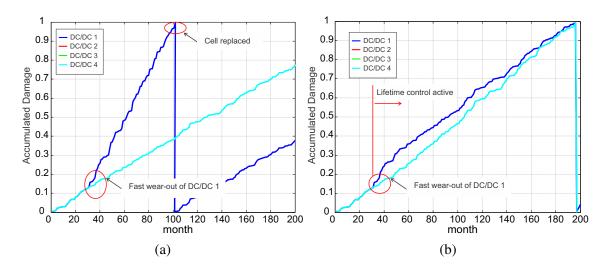

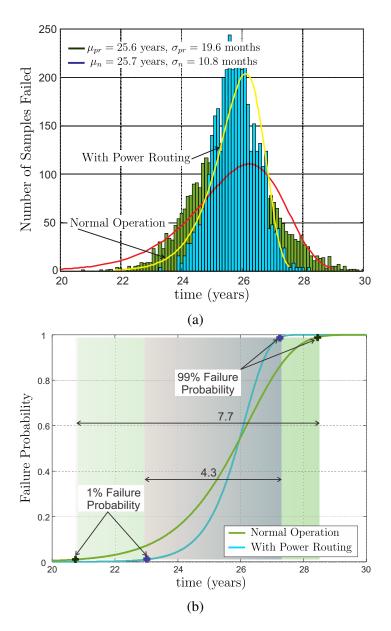

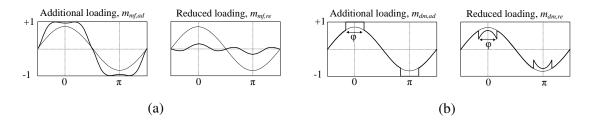

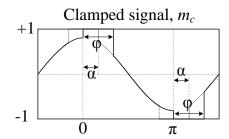

Figure 1.2: Failure and replacement cycle of modular power converters without and with power routing control [6].

ensure the reliable operation of the modular converter, the failure cases and replacement cycle are analyzed and are shown in Fig. 1.2. In the case of any failure, the replacement cycle follows the illustration in Fig. 1.2. It is logical that when one cell fails, it is sent to maintenance and replaced irrespective of the failed component. Consequently, a modular converter system comprises cells with different aging [6]. Fig. 1.2 also shows the failures due to the wear-out-based aging of converter cells. For a modular power converter system with N cells, the power device dependent parameters such as the average on-state voltage drop and on-state resistance vary between these cells due to the tolerances in the manufacturing process. The heatsink temperatures also differ between the cells, even when they process the same power, depending on the spatial configuration of the heatsinks and the direction of flow of the coolant. These electrical and thermal parameter variations result in different junction temperatures among the cells, and thereby different accumulated damages even if they process equal power [29]. Therefore, some cells fail earlier than the other ones, even when the power is equally distributed among them [30, 29].

Therefore, both the failure replacement cycles and asymmetric wear-out due to the differences in electrical and thermal parameters lead to cells with different aging in a modular converter. This has an impact on the maintenance scheduling and can result in intermittent failures leading to higher maintenance costs and possible service interruptions. The solution proposed to overcome this challenge is through power routing: "uneven loading of the cells of a modular converter to control the thermal stress among cells" [6]. With the help of power routing, the thermal stress based failures can be delayed, maintenance can be scheduled optimally and abnormal operation of the converter due to changes in ambient conditions or auxiliary system failures can be controlled.

The thesis work explores different power routing strategies in modular converters to increase system reliability. Since thermal stress is not the only challenge in modular systems, factors such as efficiency and maintenance scheduling shall be considered while developing power routing techniques. To tackle this multi-objective optimization problem, graph theoretic models are used in this work to develop optimal power flow solutions.

## 1.4 Research Proposal

The thesis aims to develop a generalized method to optimize the reliability and efficiency of modular power converters. The reliability analysis is mainly focused on the thermal stress of the power semiconductor devices for different modular converter architectures with different operating conditions. Based on the reliability studies, new algorithms for system level control of the reliability of the modular converters without compromising the efficiency are presented. The main targets of the thesis can be classified into two as follows:

Target I: Analysis, design and implementation of power routing based active thermal control in modular converters

The first research objective is to motivate the necessity of power routing in modular power converters and subsequently develop system level power routing algorithms to control the thermal stress in modular converter cells. The developed algorithms shall be validated by simulation and experimental methods. Challenges to the implementation of power routing algorithms shall be investigated and necessary improvement strategies shall be explored.

Target II: Modeling and development of graph theory based optimal power flow solutions for modular power converters

Another target of this work is to develop a unified modeling technique for the power routing of modular converters using graph theory. Graph theory is well-known for its application in several fields such as computer science and communication, and is typically used for solving network flow problems. The goal is to model the modular power converter as a graph considering the power flow analogous to the information flow in data networks. Afterward, the graph model of modular converters can be used for developing optimal power flow solutions to improve system reliability and efficiency.

#### 1.5 Structure of the Thesis

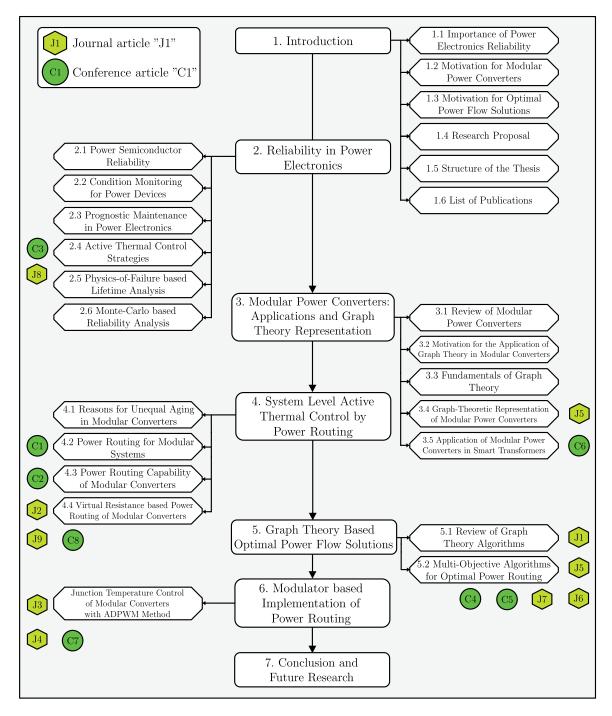

The topics investigated in this thesis are organized into 7 chapters as depicted in Fig. 1.3 along with their associated publications.

- Chapter 2 provides the necessary theoretical background for this work focusing on the fundamentals of power electronics reliability, condition monitoring techniques, and prognostic maintenance. The active thermal control methods are reviewed and the methodology of thermal stress and reliability analysis of the power converters adopted in this work is presented [J8, C3].

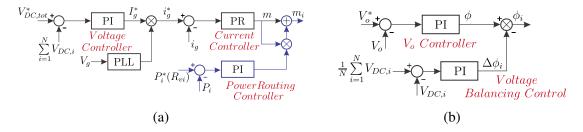

- Chapter 3 introduces the selected modular power converter topologies for Smart Transformer and more electric aircraft applications. A novel approach for the representation of the modular power converters is proposed using graph theory for developing optimal power flow algorithms [J5, C6].

Figure 1.3: Structure of the thesis.

- Chapter 4 explores the power routing strategy for the system level active thermal control in modular power converters. The necessity for power routing is motivated and a virtual resistance based power routing strategy is proposed of modular converter systems [J2, J9, C1, C2, C8].

- Chapter 5 describes the development of graph theory based optimal power flow algorithms in modular converters. Starting from the fundamentals of graph theoretical optimization, three power flow optimization algorithms are developed for improving the reliability, efficiency, and maintenance scheduling of modular systems [J1, J5, J6, J7, C4, C5, C6].

- Chapter 6 depicts the reliability analysis of a novel modulation strategy to implement power routing in multi-stage modular converter systems without compromising system efficiency [J3, J4, C7].

- Chapter 7 summarizes the main findings of this thesis work followed by conclusion and future research.

#### 1.6 List of Publications

The list of scientific papers associated with this thesis which have been published are given as follows:

#### **Journal publications**

- J1 M. Liserre, G. Buticchi, J. I. Leon, A. Marquez Alcaide, V. Raveendran, Y. Ko, M. Andresen, V. G. Monopoli, L. Franquelo, "Power Routing: A New Paradigm for Maintenance Scheduling," in IEEE Industrial Electronics Magazine, vol. 14, no. 3, pp. 33-45, Sept. 2020

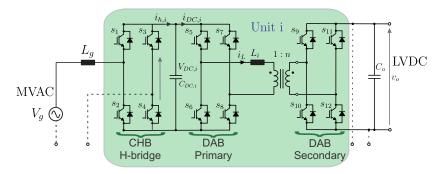

- J2 **V. Raveendran**, M. Andresen, G. Buticchi and M. Liserre, "Thermal Stress Based Power Routing of Smart Transformer With CHB and DAB Converters," in IEEE Transactions on Power Electronics, vol. 35, no. 4, pp. 4205-4215, April 2020.

- J3 Y. Ko, V. Raveendran, M. Andresen and M. Liserre, "Advanced Discontinuous Modulation for Thermally Compensated Modular Smart Transformers," in IEEE Transactions on Power Electronics, vol. 35, no. 3, pp. 2445-2457, March 2020.

- J4 Y. Ko, V. Raveendran, M. Andresen and M. Liserre, "Thermally Compensated Discontinuous Modulation for MVAC/LVDC Building Blocks of Modular Smart Transformers," in IEEE Transactions on Power Electronics, vol. 35, no. 1, pp. 220-231, Jan. 2020.

- J5 M. Liserre, **V. Raveendran** and M. Andresen, "Graph Theory Based Modeling and Control for System-level Optimization of Smart Transformers," in IEEE Transactions on Industrial Electronics.

- J6 V. Raveendran, M. Andresen and M. Liserre, "Improving Onboard Converter Reliability for More Electric Aircraft With Lifetime-Based Control," in IEEE Transactions on Industrial Electronics, vol. 66, no. 7, pp. 5787-5796, July 2019.

- J7 M. Andresen, J. Kuprat, **V. Raveendran**, J. Falck and M. Liserre, "Active thermal control for delaying maintenance of power electronics converters," in Chinese Journal of Electrical Engineering, vol. 4, no. 3, pp. 13-20, September 2018.

1 Introduction

- J8 P. Kumar Prasobhu, V. Raveendran, G. Buticchi and M. Liserre, "Active Thermal Control of GaN-Based DC/DC Converter," in IEEE Transactions on Industry Applications, vol. 54, no. 4, pp. 3529-3540, July-Aug. 2018.

- J9 M. Andresen, V. Raveendran, G. Buticchi and M. Liserre, "Lifetime-Based Power Routing in Parallel Converters for Smart Transformer Application," in IEEE Transactions on Industrial Electronics, vol. 65, no. 2, pp. 1675-1684, Feb. 2018.

#### **Conference publications**

- C1 V. Raveendran, M. Andresen, G. Buticchi and M. Liserre, "Reliability Enhancement of Modular Smart Transformers by Uneven Loading of Cells," PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2017, pp. 1-8.

- C2 V. Raveendran, G. Buticchi, A. Mercante and M. Liserre, "Comparison of voltage control methods of CHB converters for power routing in smart transformer," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, 2017, pp. 1652-1658.

- C3 P. K. Prasobhu, **V. Raveendran**, G. Buticchi and M. Liserre, "Active thermal control of a DC/DC GaN-based converter," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, 2017, pp. 1146-1152.

- C4 **V. Raveendran**, M. Andresen and M. Liserre, "Lifetime Control of Modular Smart Transformers Considering the Maintenance Schedule," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, 2018, pp. 60-66.

- C5 V. Raveendran, M. Andresen and M. Liserre, "Reliability Oriented Control of DC/DC Converters for More Electric Aircraft," 2018 IEEE 27th International Symposium on Industrial Electronics (ISIE), Cairns, QLD, 2018, pp. 1352-1358.

- C6 V. Raveendran, M. Andresen and M. Liserre, "Graph Theory-Based Power Routing in Modular Power Converters Considering Efficiency and Reliability," IECON 2018 44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, 2018, pp. 1237-1242.

- C7 Y. Ko, V. Raveendran, M. Andresen and M. Liserre, "Discontinuous Modulation based Power Routing for Modular Smart Transformers," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, 2018, pp. 1084-1090.

- C8 **V. Raveendran**, M. Andresen, M. Liserre and G. Buticchi, "Lifetime-based power routing of smart transformer with CHB and DAB converters," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, 2018, pp. 3523-3529.

## 2 Reliability in Power Electronics

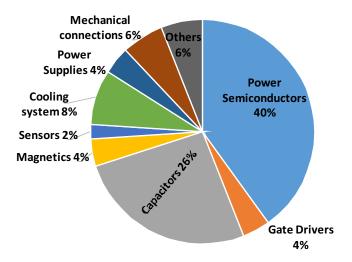

Power electronics is becoming the backbone of a multitude of fields such as the automotive industry, energy sector, aerospace, industrial drives, railway, and shipping sector to achieve higher efficiency, performance, power density, and reduced carbon footprint [3, 31]. With the increased number of power electronic components, reliable operation of power electronics for the designated lifetime becomes more crucial for safety critical applications. There are many stressors identified for the failure of power electronics systems such as temperature cycling, high temperatures, humidity, vibration, pollution, and radiation. According to the latest industrial survey covering various areas such as wind power, Photo-Voltaic (PV), electric vehicles, Uninterrupted Power Supplies (UPS), aviation, and energy transmission, power semiconductor devices are identified as the most vulnerable component to failure [32]. These findings corroborate the earlier studies which have identified power semiconductor devices being one of the most fragile components in a power converter along with the capacitors [9, 1, 33]. The industry believes that the future reliability research of the power converters should mainly focus on the power semiconductors and capacitors as indicated in Fig. 2.1, since about 40% of the failures arise from the power semiconductors [32]. Since it is wellestablished that the power semiconductors are one of the most vulnerable components in a power converter system, the main focus is on the power semiconductor reliability to evaluate the power converter reliability.

The chapter presents the theoretical background for the reliability analysis and methodology of reliability evaluation followed in this work. First, a brief discussion about power module reliability, condition monitoring methods, and maintenance strategies are given. Then, Physics of Failure based reliability analysis using lifetime models, mission profiles, and electro-thermal models is explained in detail. The chapter ends with the fundamentals of Monte-Carlo based reliability analysis relevant for this thesis. The publications [J8] and [C3] contribute to the content of this chapter.

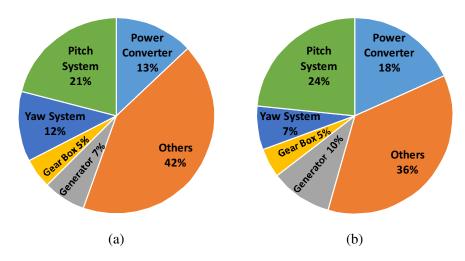

Figure 2.1: Industry perspective: Normalized failures in power electronics components [32].

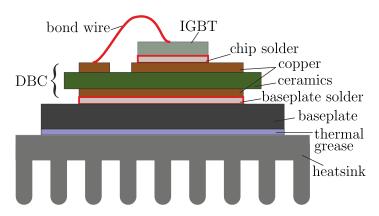

Figure 2.2: Standard structure of an IGBT module.

#### 2.1 Power Semiconductor Reliability

Among the power semiconductor devices, Insulated Gate Bipolar Transistors (IGBT) are the most commonly used ones owing to their high performance, low cost, better reliability and wide power range. Since its invention in 1982, IGBTs have penetrated the power converter market with devices available up to voltage and current ratings in the range of kilovolt (kV) and kiloampere (kA) respectively [4]. For the modular power converter topologies analysed in this thesis, IGBT modules have been considered due to their power rating compatibility.

In several applications, the power devices are used as power modules with special packaging. The module packaging provides the necessary electrical connection between the semiconductor chips, guarantees the necessary insulation, facilitates the dissipation of generated heat, protects the semiconductor chip from ambient conditions, and reduces the costs [34]. One of the widely popular packaging technologies for power devices is the use of Direct Bonded Copper (DBC). Fig. 2.2 shows the Direct Bonded Copper structure of an IGBT module. The DBC structure is adopted to provide good electrical and thermal properties for the IGBT module. The ceramic provides the electrical insulation between the power and cooling components and is usually made of aluminium oxide or aluminium nitride. Copper conducts the current and also provides a good thermal connection to the heatsink. The base plate is an optional component in the low power range. The IGBT chips are soldered to the DBC and the DBC is soldered to the base plate. The chips are connected to the upper copper substrate with the help of solder and the top of the chips are connected electrically using bond wires. The power modules are usually encased with a molding material, and for low voltage applications, open module construction is also followed. [35].

The most fragile connections in the IGBT structure are the bond-wire, chip solder and base-plate solder, and are marked in red in Fig. 2.2 [36]. The main failure mechanisms identified in the IGBT modules are:

- Bond-wire liftoff

- Chip solder fatigue

- Base plate solder fatigue

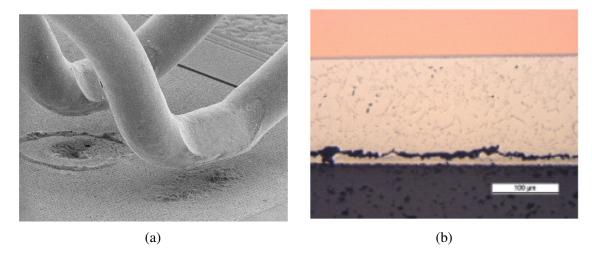

Figure 2.3: IGBT failure mechanisms (a) Bond-wire lift-off (b) Solder joint cracking [34].

#### • Metallization reconstruction

Bond-wire liftoff is perhaps the most prominent failure mechanism of IGBT power modules. It is clear that the IGBT module consists of different materials with different Coefficient of Thermal Expansion (CTE) as shown in Fig. 2.2. The IGBT and diode chips produce losses during the operation, which results in the heating of the materials in the module. The CTE mismatch of the Aluminium bond wires and the silicon IGBT chip is the largest in the module and this leads to the bond wire crack failure or liftoff. Thermal cycling has been identified as the main cause of bond wire liftoff [34]. When one bond wire fails due to crack or liftoff, the remaining bond wires need to carry the full device current, thereby accelerating the degradation due to higher thermo-mechanical stress. An electron microscope image of the bond wire liftoff is illustrated in Fig. 2.3 (a).

Many solutions have been investigated to prevent bond-wire related failures. Since the CTE mismatch between Aluminium and Silicon is the main reason for higher thermo-mechanical stress, copper has been used to replace Aluminium to provide better performance [37]. Other approaches involve avoiding bond-wires through direct bonding, and increasing the contact area offering a lower resistance path [38]. Solutions with an intermediate layer to act as strain buffer and optimal design of bond-wire geometries are also considered [39]. However, the alternatives have not been successful in replacing the Aluminium bond wires in high power IGBT modules due to the simple packaging procedure, flexibility and low cost.

**Solder fatigue** has been identified as another major failure mechanism in IGBT which occurs at the chip solder joint and baseplate solder joint as indicated by the red color in Fig. 2.2. The main reason for the solder fatigue is the thermo-mechanical stress introduced by the thermal cycling and the CTE mismatch between the solder, substrate, silicon chip, and baseplate. The solder fatigue results in cracks and voids in the solder joints as shown in Fig. 2.3 (b). Once the degradation starts, the additional stress on the non-affected part accelerates the damage similar to that of the bond-wire fatigue. The solutions for preventing solder fatigue include replacing the solder interface with sintering technology. The solder interface

between the chip and the substrate is replaced using silver diffusion sinter technology to form a homogeneous layer without voids [40].

**Metallization reconstruction** is the result of thermo-mechanical stress at the interface of silicon chips and electrical connections. In order to facilitate electrical connection with the Silicon, the standard technique is to add a film of Aluminum through vapour deposition and thermal annealing. Similar to other fatigue mechanisms, the CTE mismatch between Aluminium and Silicon creates high thermo-mechanical stress at this interface when subjected to thermal cycling. Prolonged thermal cycling results in the creation of voids or extrusion of aluminium grain at the metallization interface and is called metallization reconstruction. [41].

Since the main failure mechanisms of power devices have been recognized, the next step is to detect and prevent these failures in the field. The following section details the methods for detecting the failures in advance by suitable condition monitoring techniques.

## **2.2** Condition Monitoring for Power Devices

Condition Monitoring (CM) is defined as a technique used to monitor the relevant parameter of an operating system for scheduling maintenance before failure or performance degradation [42, 43]. CM is a multidisciplinary strategy that includes the knowledge of the physics of failure of the components and the system, sensor technology, data acquisition and analysis, and the capability to determine the health of the system. As illustrated in Fig. 2.1, power semiconductor devices constitute the majority share of failures in a power electronics system. Hence, only the CM techniques relevant to the power devices are discussed in this section.

Power semiconductor devices and power converters are striving to improve the power density by reducing the size and increasing the rated power which makes the design of CM techniques more challenging. For any CM technique, the nature of the physical degradation of the device and its impact on the converter operation shall be investigated. The principle behind condition monitoring can be categorized into three types [44];

- Monitoring of device parameters indicative of degradation: Instead of directly measuring the degradation of the component itself, usually it is easier and less invasive to monitor the electrical or mechanical parameters that are sensitive to the device degradation. For example, thermal resistance  $R_{th}$  and on-state collector-emitter voltage drop  $V_{ce,sat}$  of the IGBT modules are used to monitor solder cracks and bond wire liftoff respectively.

- Direct monitoring of device degradation: This can be done using sensors embedded in the device to monitor any physical degradation; for instance, mechanical stress monitoring of the power modules using sensors.

- Model-based Condition Monitoring: Model-based CM plays a major role in system level lifetime estimation and fault-detection strategies. For example, the degree of

| CM Parameter | Detected Failure           | Challenges                          | Pros                         |

|--------------|----------------------------|-------------------------------------|------------------------------|

| $V_{ce,sat}$ | Bond wire liftoff/crack    | Difficult to guarantee accuracy and | Less invasive with           |

|              |                            | immunity to switching transients    | medium implementation effort |

| $R_{th}$     | Solder fatigue/crack       | Internal temperature and            | Less invasive                |

|              |                            | power loss data required            |                              |

| $T_{j}$      | Indirect Bond wire liftoff | Direct sensing is invasive and      | Multiple techniques          |

|              | solder fatigue detection   | indirect methods pose inaccuracy    | available                    |

| Bond wire    | Bond wire liftoff          | Highly invasive                     | Higher accuracy              |

| resistance   |                            |                                     |                              |

Table 2.1: Condition Monitoring Techniques for Power Devices.

degradation can be estimated by the comparison of the response of measurement data with that of prediction by the model.

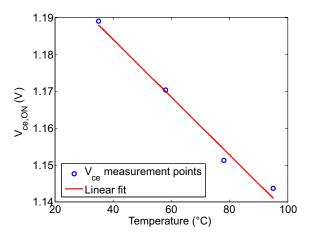

One of the most promising CM techniques for the IGBT power module is the on-state collector-emitter voltage drop measurement. The power cycling tests show that the  $V_{ce,sat}$  changes significantly with bond wire liftoff degradation. When the  $V_{ce,sat}$  increases by 15%, IGBT is considered to be seriously damaged [44]. The on-state voltage drop is also used to calculate the junction temperature of the IGBT since it is a Temperature Sensitive Electrical Parameter (TSEP). The  $V_{ce,sat}$  varies with the junction temperature and by using calibrated  $V_{ce,sat}$  vs. junction temperature curves, device junction temperature can be estimated during the operation of the power converter [45, 46, 47, 48]. In this work, the  $V_{ce,sat}$  sensing circuit illustrated in Fig. C.4 is used to estimate the device junction temperature and health status.

The thermal resistance of the power modules also varies with the degradation of the solder joints. Therefore, thermal resistance based condition monitoring is preferred to detect solder cracks or fatigue within the module. A 20% increase in the  $R_{th}$  from the initial value is considered as the end-of-life of the power device [49, 50]. However, the main challenge for the calculation of the  $R_{th}$  is the knowledge of the internal temperature of the module and the power dissipation. One method to overcome the challenges is to embed thermal sensors within the module and measure the load current for power loss estimation.

Another popular monitoring parameter for the power device is the junction temperature, but it is difficult to measure directly [51, 46]. Therefore, many research works focus on the indirect measurement of junction temperature with the help of TSEPs such as the  $V_{ce,sat}$ , gate threshold voltage  $V_{GE,th}$  and transconductance  $g_m$  [44]. The  $V_{ce,sat}$  varies almost linearly with the temperature and  $V_{GE,th}$  decreases as the temperature rises [45, 52]. The measured/estimated junction temperature can be used to calculate the  $R_{th}$  or as an input for the lifetime models for predicting the health status of the power device [53]. The importance of CM has encouraged power module manufacturers like Semikron to produce intelligent power modules with sensors to detect bond wire liftoff [54]. In these intelligent modules, the DBC layout is modified to incorporate additional sensing elements to detect bond wire liftoff by monitoring the change in resistance. Selected CM techniques for the power devices have been summarized in Table 2.1.

To utilize the advantages offered by CM techniques, and to prevent unwanted disruption of

Figure 2.4: PV plant maintenance experience (a) Unscheduled maintenance event share of subsystems (b) Unscheduled maintenance cost share of subsystems [33].

Figure 2.5: Wind power plant failure share among subsystems (a) Failure rate (b) Downtime [55].

services due to power converter failures, maintenance based on condition monitoring needs to be in place. The next section discusses common maintenance practices and presents the advancements in the field of condition monitoring based maintenance.

## 2.3 Prognostic Maintenance in Power Electronics

In industry, the conventional maintenance strategies can be broadly classified into two categories; corrective and preventive maintenance [26]. Corrective maintenance is performed when a failure occurs whereas preventive maintenance focuses on the maintenance scheduled at predefined intervals to prohibit failures. Even though corrective maintenance does not have the cost burden for condition monitoring and scheduled maintenance routines, the cost of unexpected downtime and repairs may not be acceptable for most of the industries. The preventive maintenance is usually performed after a particular period of time, hours of operation, or kilometers driven. Although preventive maintenance improves the system re-

|               | Maintenance Strategies |                           |                                    |                          |  |

|---------------|------------------------|---------------------------|------------------------------------|--------------------------|--|

|               | Corrective             | Preventive                | <b>Condition Based Maintenance</b> |                          |  |

|               | Corrective             |                           | Diagnostic                         | Prognostic               |  |

| Principle     | Maintenance based      | Based on field            | Identify impending failures        | RUL prediction based     |  |

|               | on demand              | experience                | based on CM data                   | on CM data               |  |

| Advantages    | No CM costs            | Control over maintenance  | Reduced unexpected                 | Higher availability      |  |

|               |                        | schedules, labor and cost | failures                           |                          |  |

|               | No special maintenance | Reduced chances of        | No prognostic know-how             | Higher reliability and   |  |

|               | requirement            | failures                  | required                           | fewer secondary failures |  |

| Disadvantages | Lower reliability      | Scheduled repairs replace | High initial                       | High initial             |  |

|               | and availability       | healthy components        | cost                               | cost                     |  |

|               | High repair costs      | Cannot prevent            | Overall system health              | Requires system model    |  |

|               |                        | unscheduled faults        | is unknown                         | or data-driven methods   |  |

Table 2.2: Overview of Maintenance Strategies [56].

liability through inspections, tests, replacements etc., risk of failures remain high since the health of the system is unknown. For instance, maintaining power electronics in systems such as large fleets of aircraft and remotely located STs can be very challenging.

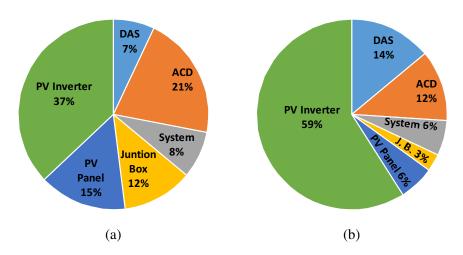

The maintenance activities require trained personnel with expertise, and according to level of fault, the system downtime can vary. Unscheduled maintenance can result in revenue loss and unavailability of the systems and these facts become crucial with increasing operational demands and lack of fiscal resources. For instance, [33] presents maintenance data from a large PV power generation plant. As illustrated in Fig. 2.4 (a), the power converter is the reason for the major share (37%) of unscheduled maintenance events. The impact of unscheduled maintenance events on the maintenance cost is summarized in Fig. 2.4 (b), which clearly shows that the maintenance of the power converter is the most expensive (59%) among all the subsystems. In wind turbine systems, the power converter is responsible for 13% of total failures and 18% of total system downtime as shown in Fig. 2.5 [55]. In short, the power converters play a crucial role in the reliable operation of renewable energy systems such as wind and solar power plants.

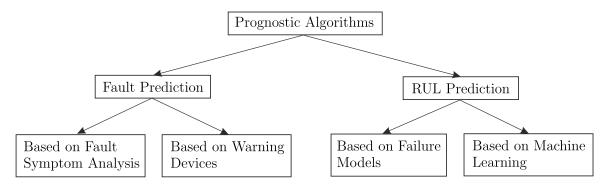

Due to increasing reliability requirements and costs associated with unexpected failures, newer maintenance policies based on Condition Based Maintenance (CBM) have gained importance in the last decades. CBM can be again classified into two sub-categories, namely, diagnostic and prognostic maintenance [56]. Diagnostic maintenance is defined as maintenance based on the current condition of the system under consideration. The definition of prognostics is the ability to provide early detection of the incipient faults of a component and to predict the progression of such a fault resulting in the component failure [26]. With prognostics, the remaining useful life of the system can be predicted with an acceptable degree of confidence and when such a piece of information is used to schedule maintenance, it is termed prognostic maintenance [57]. Prognostic maintenance becomes an essential requirement of systems, which require high reliability and availability.

The major maintenance strategies followed in the industry are summarized in Table. 2.2 clearly indicating the principle, advantages and disadvantages of each maintenance policy. The CBM based on prognostic is preferred in applications requiring high availability and

reliability since the health of the system is evaluated based on physical models, data-driven methods or hybrid approaches. In contrast to the diagnostic approach which monitors impending failures based on CM data, prognostics provides a more concrete picture of the failure probability of the system based on RUL. Prognostics can help to optimally schedule maintenance, procure spare parts and labour optimally, and use the system components to their end of life while keeping the failure probability within limits.

Several papers have discussed optimizing the maintenance schedules and predicting failures based on the monitored data considering operational constraints [58, 57]. In [58], maintenance schedule optimization of an aircraft fleet focusing on a trade-off analysis considering cost, capacity expansion and other key performance indexes in aircraft fleet management is discussed. Engine fault prediction of aircraft using CBM and machine learning has been proposed in [57]. Compared to the traditional data-driven prognostic algorithms, a computationally efficient and real-time RUL estimation of the IGBTs using the degradation profile from the power cycling tests is presented in [59]. Remarkably,  $V_{ce,sat}$  is considered as the CM parameter indicative of power device degradation in this approach [59]. In summary, condition based maintenance has opened up new research frontiers for power electronics reliability.

Although prognostic maintenance relies on the physics-of-failure to detect and prevent failures based on condition monitoring, the root-cause of failures is not addressed. In this context, active thermal control methods have been proposed in the literature to act directly on the failure root-cause, thereby aiming to prolong the power device lifetime. A short overview of active thermal control strategies is detailed in the following section.

### 2.4 Active Thermal Control Strategies

As discussed in the previous sections, thermal cycling has been identified as one of the major causes of failures of power devices. Therefore, it is necessary to develop methods to improve the thermal performance of the power devices by reducing the potentially damaging stresses. These methods shall also safeguard other operating performance indices at the same time. The methods developed to improve the thermal performance of the power electronic devices by controlling the junction temperature cycling are termed active thermal control strategies. The active thermal control methods can be classified into three levels depending on the hierarchy of implementation, namely, device level, modulator level and system level [15, 60, 61].

#### 2.4.1 Device Level

The device level active thermal control methods directly act on the device characteristics to reduce the thermal cycling. This requires modifications in the hardware to directly influence the operation of the device and hence, most of the literature focus on active gate driver methods [62, 63, 64, 65]. A temperature dependent gate driving of power MOSFETs is developed

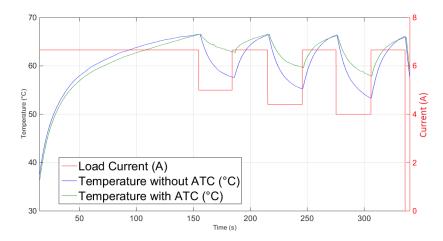

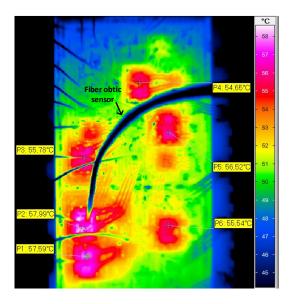

Figure 2.6: Case temperature measurement of GaN device without and with active thermal control for a given load profile [J8].

in [63] to decrease the thermal stress and losses. In [65], an active gate driver is proposed to balance the current among parallel IGBTs since the losses are different due to the tolerances of the semiconductor. The turn-on and turn-off of the devices are controlled to achieve transient current balancing among the paralleled IGBTs. Another method to achieve thermal balance among parallel devices by controlling the gate voltage and resistance is demonstrated in [62]. The main advantage of the gate driver based ATC is that the thermal stress reduction effort is independent of the converter control or modulation strategies. Therefore, these ATC strategies can be used for any converter topology without modification in the control system. The main challenge with device level ATC methods is the hardware efforts while designing the system.

Another popular technique to thermally balance the power devices is active cooling. A dynamic cooling system has been developed in [66] to reduce the thermal cycling of power modules by actively varying the cooling fan speed. This method uses a state observer for estimating the junction temperature and is demonstrated to reduce the thermal cycling under varying load conditions. The development of the required hardware for an active cooling system is described in detail in [67]. Compared to the active gate driver methods, the main disadvantage of the active cooling methods is the inability to reduce the high frequency thermal cycles due to relatively slower cooling time constants.

To limit the thermal cycling induced failures in solder joints, an active thermal control scheme using a two-step gate driver designed for GaN is presented [68]. In contrast to the active thermal control techniques employing variable switching frequency control, this method does not alter the converter operation frequency, instead, it merely controls the GaN device slew rates. The two-step gate driver designed and developed is for GS66508T (top side cooled GaN device from GaNSystems) [69, 70]. The two-gate driver provides a stepped voltage during turn-on to actively control the rise time  $t_r$  of the GaN device. Thus, by varying the rise time  $t_r$ , the switching loss variation is ensured.

The impact of the active thermal control on a bidirectional single-phase DC/DC converter is validated experimentally using the prototype of the two-step gate driver based buck converter

shown in Fig. C.5. In order to show the effectiveness of the thermal cycle minimizing the effect of active gate driver, a mission profile with varying load current is chosen as shown by the red trace in Fig. 2.6. The blue trace in Fig. 2.6 shows the case temperature thermal cycling without active thermal control for the given load profile. When the aforementioned active thermal control scheme is active, the gate driver increases the switching losses to minimize the thermal cycling. The impact of active thermal control is evident by the reduction of temperature swings indicated by the green trace in Fig. 2.6. The result demonstrates a reduction of thermal swing from 13°C to 7°C with the proposed active gate driver.

#### 2.4.2 Modulator Level

One of the well-known modulation based method to control the losses in the power devices is by actively changing the switching frequency. Switching frequency based active thermal control methods are investigated in [71, 72, 73], where the switching frequency is varied to reduce the thermal cycling due to load fluctuations. A novel switching frequency variation based ATC without a priori knowledge of the mission profile for a single phase converter is demonstrated in [71]. An electro-thermal model based junction temperature estimation is developed for realizing ATC for an electric vehicle application is studied in [72]. Another approach combines switching frequency based ATC with active cooling to reduce the thermal stress in wind power converter [73]. The main drawback of the switching frequency variation methods are the varied current spectrum, higher mean temperature, and lower efficiencies at higher switching frequencies. Rather than directly reducing the switching losses by reducing switching frequency, switching losses of power devices in a power converter is reduced through different modulation techniques. For the converter in an electric vehicle application, discontinuous PWM is employed to reduce the switching losses of the power devices during the start-up procedure to safeguard the converter thermal limits [74].

#### 2.4.3 System Level

System level ATC methods focus on adjusting the control parameters to reduce thermal stress. One opportunity to control the device losses of the power devices in a converter is by changing the applied voltage. In the case of a Permanent Magnet Synchronous Machine drive, the DC-link voltage is dynamically adapted to achieve thermal cycling reduction and higher efficiencies in [75]. The losses of the power devices can be reduced by lowering the DC-link voltage, particularly at lower motor speeds. The control system design to provide an optimal torque while reducing the thermal cycling of the devices with a variable DC-link is challenging in this approach. In parallel Neutral Point Clamped (NPC) converters for wind power application, the thermal swing of the most stressed devices is reduced by increasing the generated losses using the reactive power circulation method [76]. The main drawback of the reactive power circulation method is the resulting higher mean junction temperatures of the stressed devices and the increase in thermal stress of the other devices.

#### 2.5 Physics-of-Failure based Lifetime Analysis

Previous sections discussed the major power device failure mechanisms, condition monitoring of the relevant physical parameters to schedule maintenance, as well as active thermal control methods to influence the failure root cause. However, it is essential to quantitatively determine the expected lifetime of a device during the design stage, and to establish scientific methodologies for evaluating the reliability impact of aforementioned ATC approaches. In this context, this section elaborates on the lifetime and reliability evaluation methods adopted in this thesis.

First, a short theoretical background about the reliability metrics is presented. Subsequently, motivation to adopt the Physics-of-Failure (PoF) approach is given. The is followed by the lifetime modeling of power devices based on the physics of failure. The reliability analysis of converters with the help of mission profile and PoF based lifetime models is covered in the final part of the section.

#### 2.5.1 Reliability Metrics

Before venturing into the reliability analysis, the fundamentals of reliability engineering are presented first. For reliability analysis, it is imperative to understand the Weibull distribution and its properties. The distinguishing feature of the Weibull compared to the normal distribution is that the cumulative distribution function (CDF) of Weibull is bounded, which hence makes it attractive for predicting the failure probability. Depending on the number of parameters, Weibull distribution can be classified into a three-parameter distribution and a two-parameter distribution. The CDF of a three-parameter Weibull is expressed as

$$F(x) = 1 - \exp\left[-\left(\frac{x - \gamma_w}{\alpha_w}\right)^{\beta}\right],\tag{2.1}$$

where  $x > \gamma_w$ , and  $\gamma_w$  is called the threshold or location parameter which indicates that the failure occurs only when the x is greater than the threshold value  $\gamma_w$ . Assuming that the failure can occur from the beginning of operation of a component,  $\gamma_w$  becomes 0 and the aforementioned Weibull distribution reduces to a two-parameter version. The parameters  $\alpha_w$  and  $\beta$  are respectively known as the scale parameter and shape parameter. When  $\beta$  is 1, the Weibull distribution transforms into an exponential distribution. The Weibull distribution offers the flexibility to model different lifetime behaviours by adjusting the parameters [77].

In order to quantify the reliability of power electronics systems, different metrics such as reliability, failure rates, unreliability, Mean Time To Failure (MTTF) and  $B_x$  lifetime are employed. It is common practice to use Weibull distribution to define these reliability metrics. However, to derive these metrics, aspects such as failure criteria, environment factors, stress conditions, confidence interval, and time are critical. If any of these factors vary, the reliability description can vary.

Reliability R(t) is defined as the percentage of samples under consideration that can function properly at an instant t. For each sample, R(t) is the probability that the sample functions at time t. The unreliability F(t) is defined as the probability of failure of a sample at an instant t. It is calculated as [5]

$$F(t) = 1 - R(t). (2.2)$$

The variation of unreliability F(t) in time is expressed as the cumulative distribution function curve and in the case of a two-parameter Weibull distribution, the F(t) can be given as

$$F(t) = 1 - \exp\left[-\left(\frac{t}{\alpha_w}\right)^{\beta}\right]. \tag{2.3}$$

In industrial applications, MTTF is the most commonly used reliability metric which denotes the average time at which a sample fails. However, it does not reflect the variation of the reliability over time and the root cause of failure is ignored. MTTF can be calculated as [5, 28]

$$MTTF = \int_0^\infty R(t)d(t). \tag{2.4}$$

Today, the use of  $B_x$  lifetime is gaining popularity over the MTTF metric.  $B_x$  lifetime of a group of samples is defined as the time at which x percentage of samples have failed. For instance,  $B_{10}$  lifetime is defined as the time at which 10% of the samples under the test have failed. The  $B_x$  lifetime can be obtained from the CDF curve and therefore the time-varying nature of the reliability function is reflected in the  $B_x$  lifetime [78, 1].

Another important reliability metric is the failure rate  $\lambda(t)$  which defines the frequency of failure of the sample under consideration. Mathematically, the failure rate is expressed as

$$\lambda(t) = \frac{1}{R(t)} \frac{d(1 - R(t))}{dt}.$$

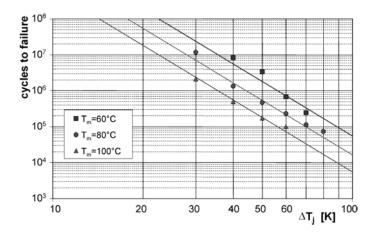

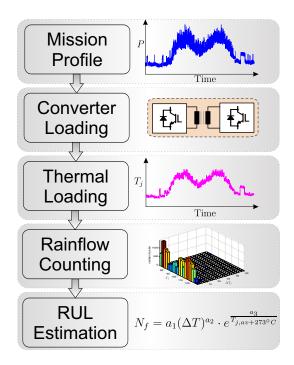

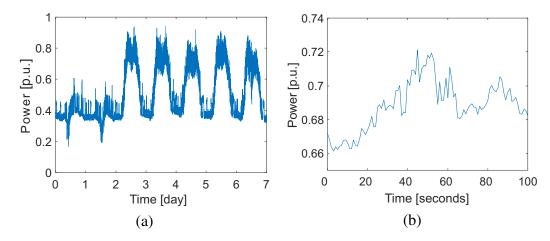

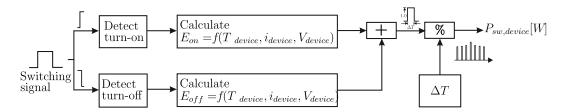

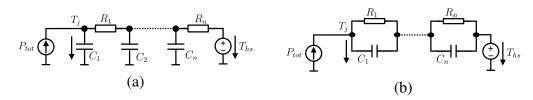

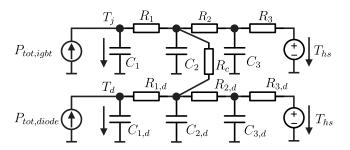

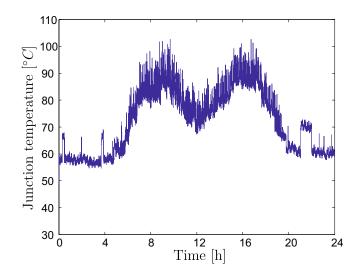

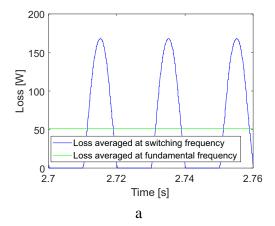

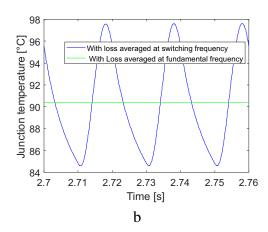

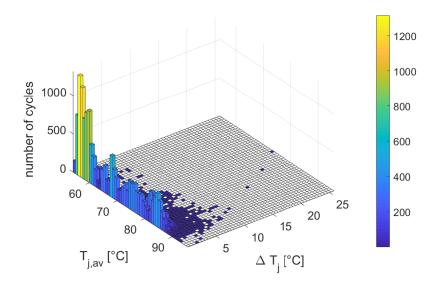

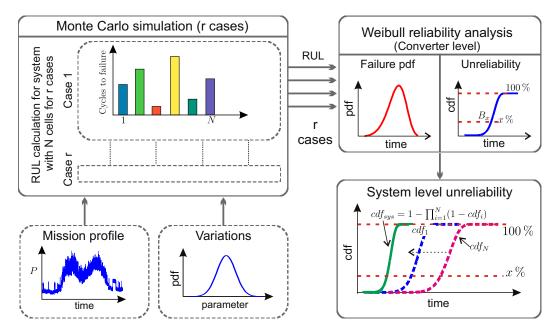

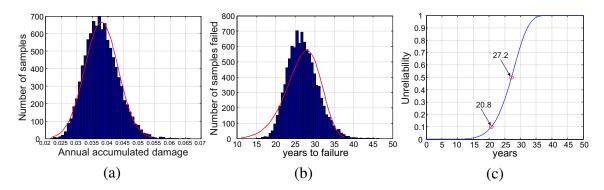

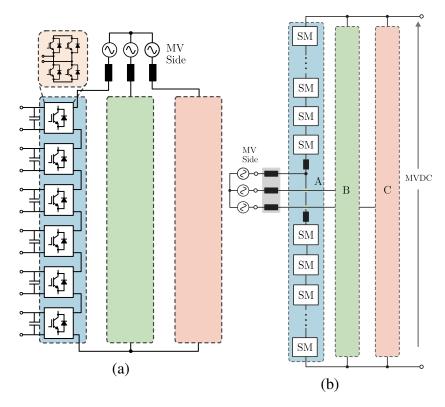

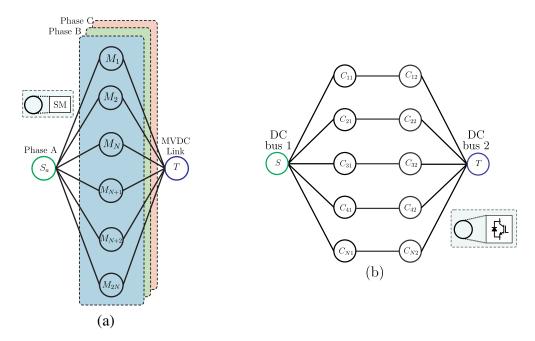

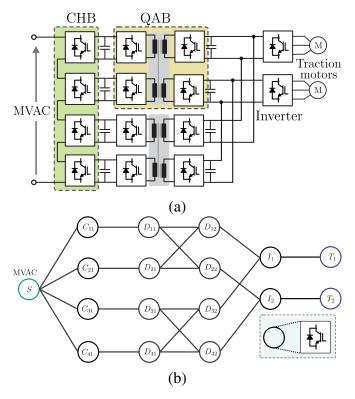

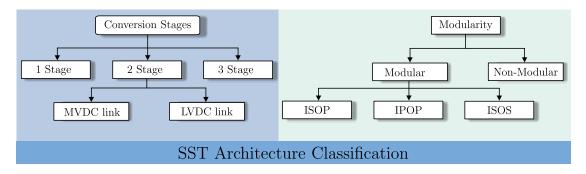

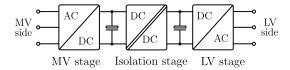

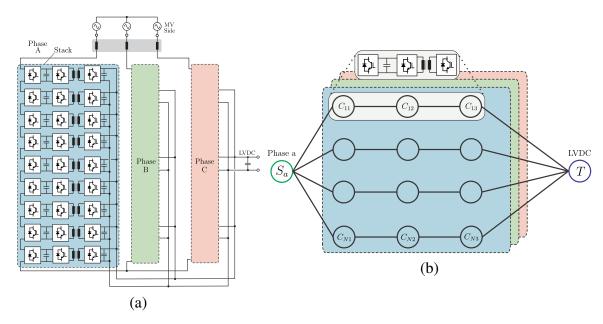

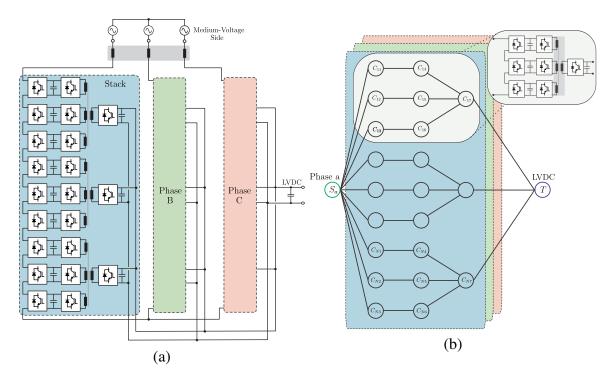

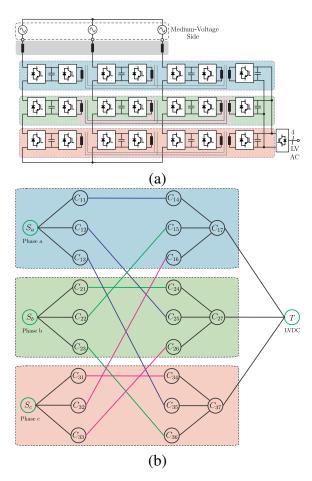

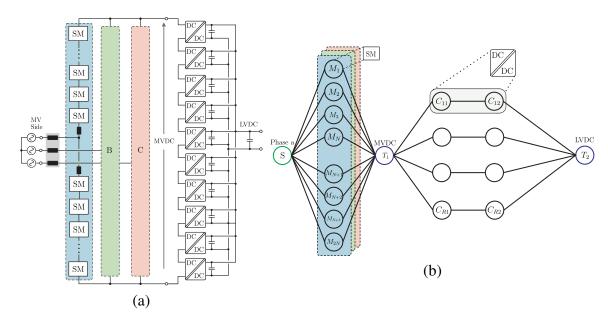

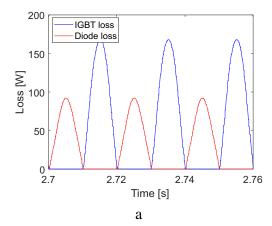

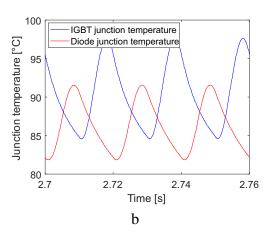

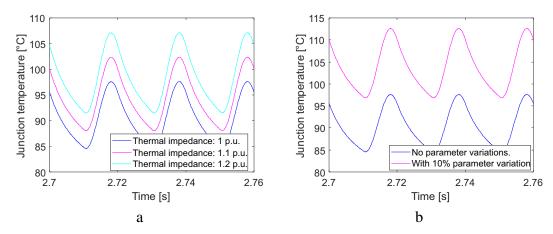

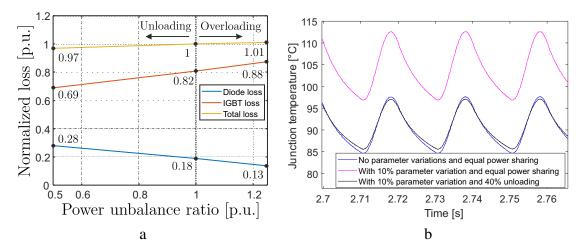

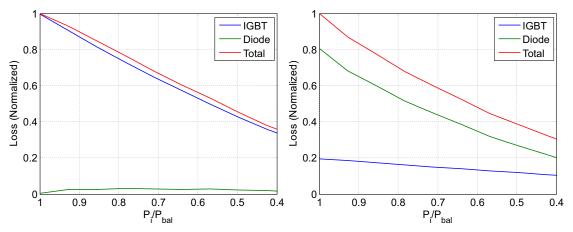

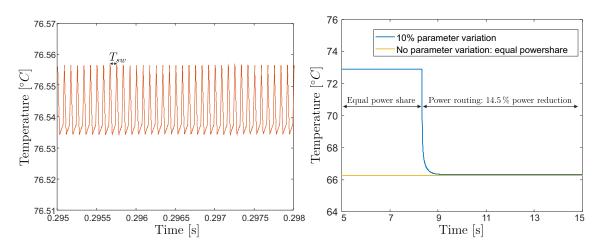

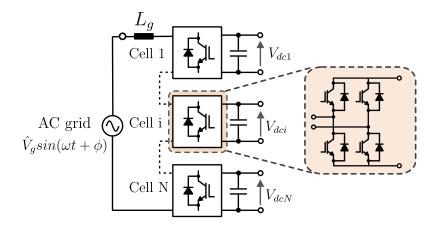

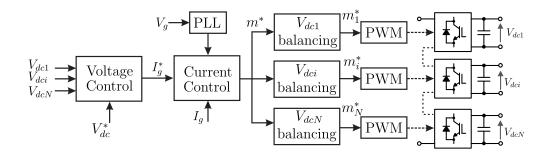

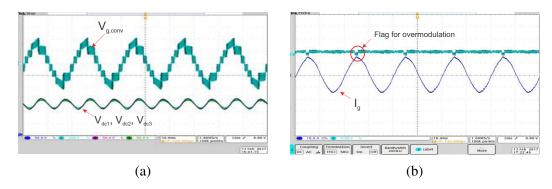

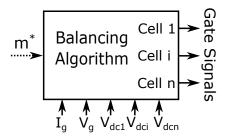

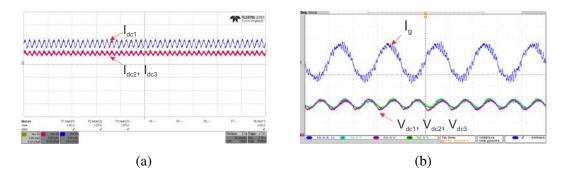

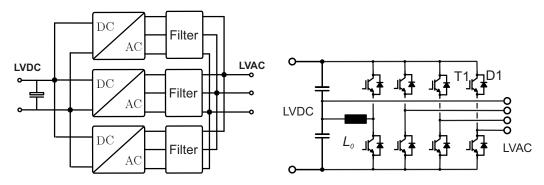

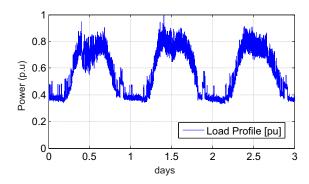

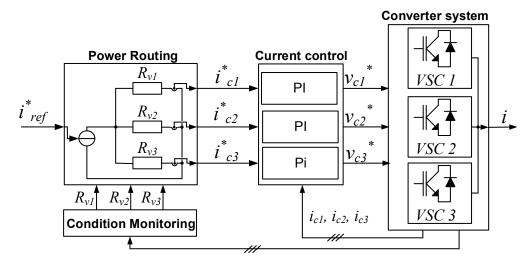

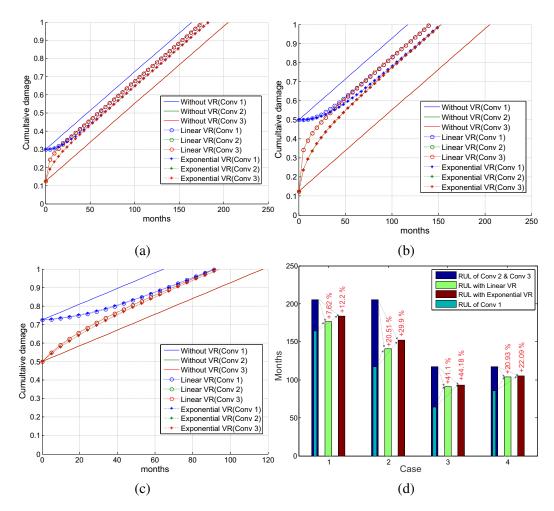

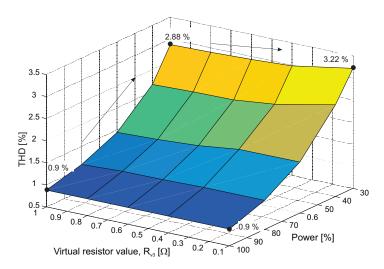

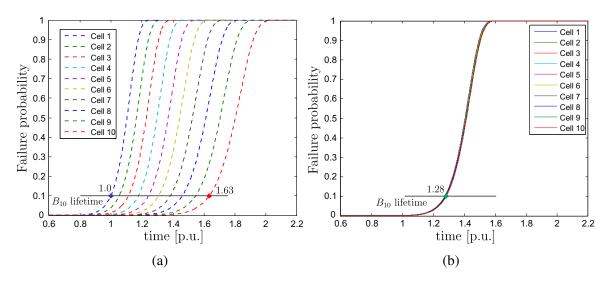

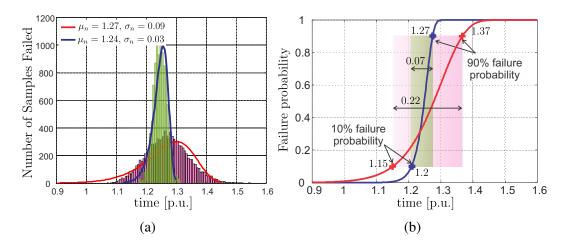

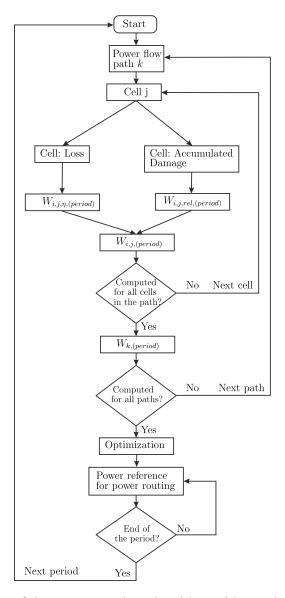

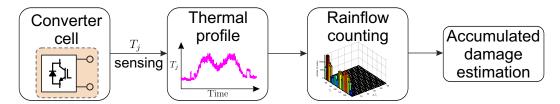

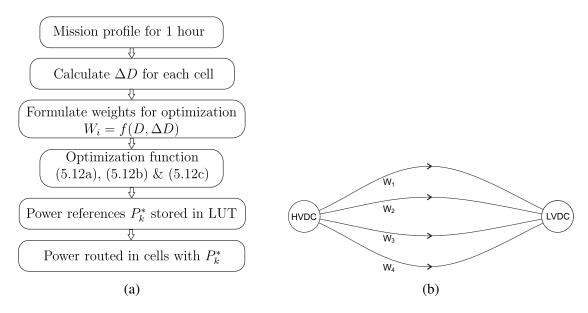

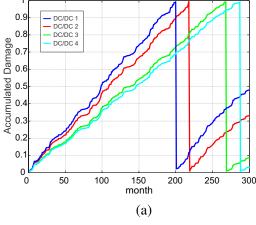

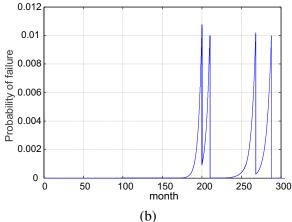

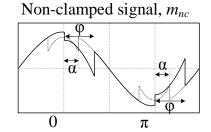

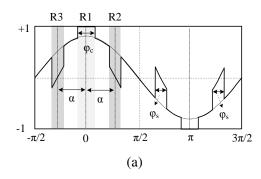

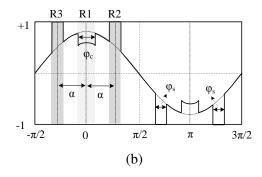

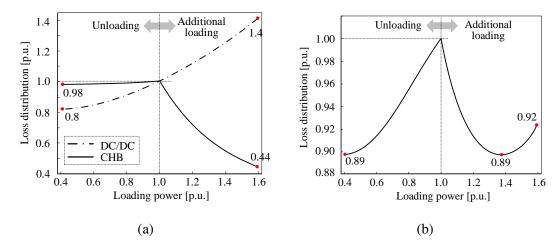

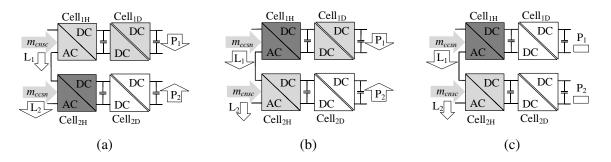

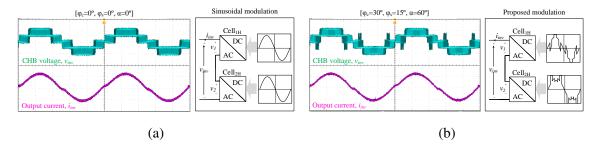

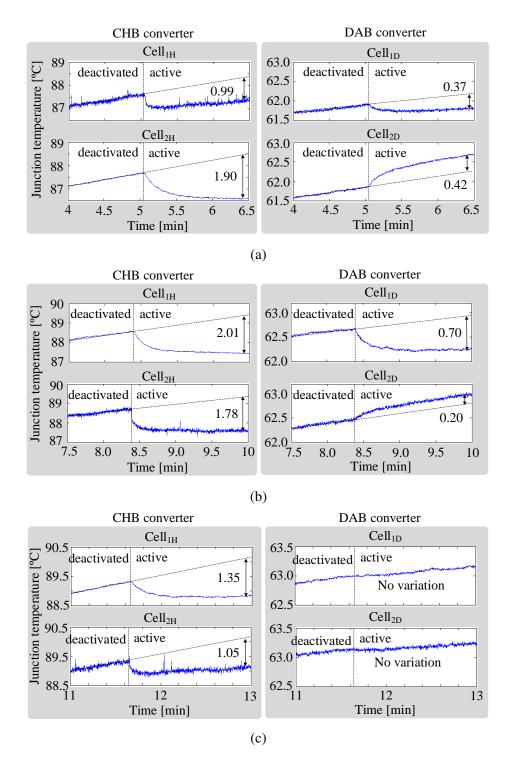

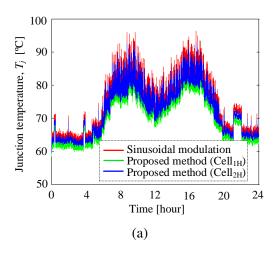

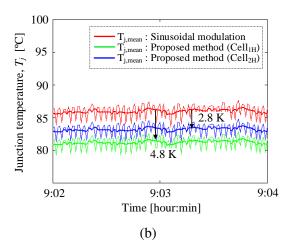

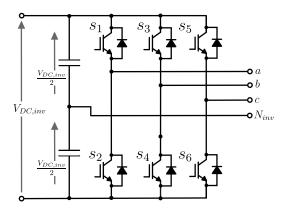

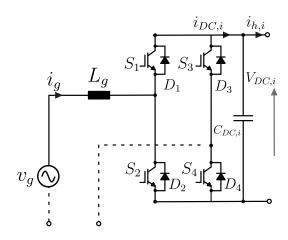

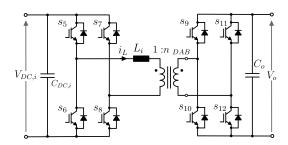

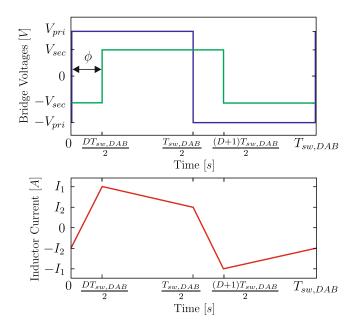

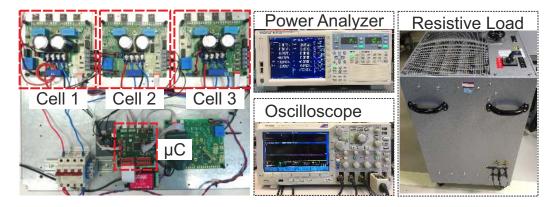

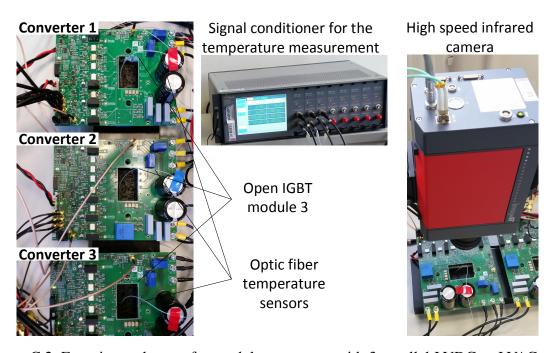

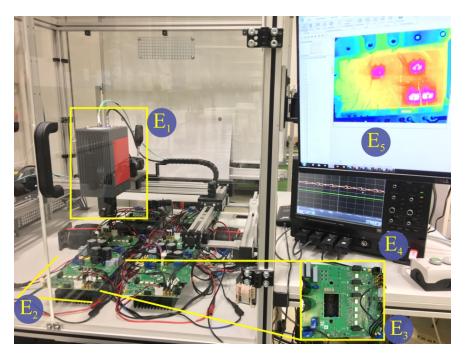

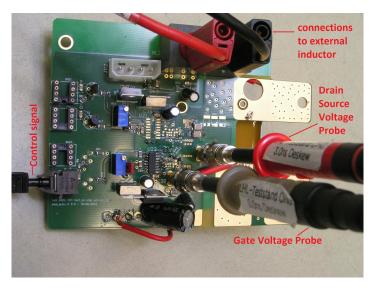

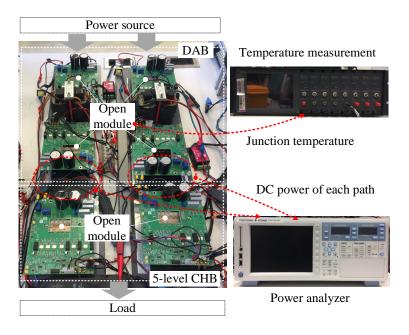

(2.5)