# Review of Rounding Based Approximate Multiplier (ROBA) For Digital Signal Processing

Monika Malviya M.Tech scholar Department of Electronics and Communication SISTec, Bhopal (M.P.)

Prof. Pankaj Vyas Associate Professor Department of Electronics and Communication SISTec, Bhopal (M.P.)

Abstract— The fundamental idea of adjusting put together estimated multiplier depends with respect to adjusting of numbers. This multiplier can be connected for both marked and unsigned numbers. In this paper contemplated an Rounding Based Approximate Multiplier that is fast yet vitality effective. The methodology is to round the operands to the closest example of two. Along these lines the computational concentrated piece of the augmentation is excluded improving rate and vitality utilization at the cost of a little mistake. This methodology is appropriate to both marked and unsigned augmentations. The productivity of the ROBA multiplier is assessed by contrasting its execution and those of some rough and precise multipliers utilizing distinctive plan parameters.

\*\*\*\*

Keywords- FPGA, Multiplier, ROBA, Energy speed efficient.

I.

### INTRODUCTION

Energy minimization is one of the fundamental plan prerequisites in practically any electronic frameworks, particularly the versatile ones, for example, advanced mobile phones, tablets, and unique devices. It is profoundly wanted to accomplish this minimization with insignificant execution (speed) punishment. Advanced signal handling (DSP) squares are key parts of these compact gadgets for acknowledging different sight and sound applications. The computational center of these squares is the numbercrunching rationale unit where increases have the best offer among all number juggling tasks performed in these DSP frameworks. Thusly, improving the speed and power/vitality proficiency attributes of multipliers assumes a key job in improving the productivity of processors.

In FIR channel structured, will utilized plan any multipliers, if last continuous years, the MCM system will utilized, as a FIR channel plan, yet the disadvantage is MCM strategy won't work both thing of marked and un-marked activity, so it will we have to configuration separate MCM for marked and unsigned augmentation. So here, examined a MCM with Adjusted based surmised multiplier that incorporates both marked and unsigned activity in single multiplier, this multiplier will executed in FIR Channel, and demonstrated the productivity of region, power and delay.

Finite Impulse response (FIR) computerized channel is broadly utilized in a few advanced signal preparing application, for example, discourse handling, uproarious speaker balance, reverberation retraction, versatile clamor wiping out, and different correspondence application, including programming characterize radio (SDR, etc. A significant number of this application require FIR channel of

IJRITCC | April 2019, Available @ http://www.ijritcc.org

substantial request to meet the stringent recurrence detail. Regularly these channels need to help high inspecting rate for fast computerized correspondence.

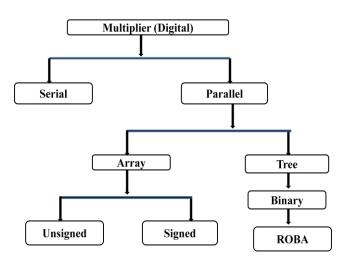

Figure 1: Types of digital multiplier

Figure 1 showing different types of multiplier, ROBA multiplier is part of binary multiplier but it is also applicable in signed and unsigned multiplier.

In FIR channel planned, will utilized structure any multipliers, if last successive years, the MCM method will utilized, as an of FIR channel plan, yet the disadvantage is MCM system won't work both thing of marked and unmarked task, so it will we have to configuration separate MCM for marked and unsigned augmentation. So here, we are a MCM with Adjusted based inexact multiplier that incorporates both marked and unsigned task in single multiplier, this multiplier will executed in FIR Channel, and demonstrated the productivity of territory, power and delay.

#### II. LITERATURE SURVEY

R. Zendegani et al.,[1] In this paper, we propose an estimated multiplier that is rapid yet vitality effective. The methodology is to round the operands to the closest example of two. Along these lines the computational escalated some portion of the duplication is excluded improving velocity and vitality utilization at the cost of a little blunder. The methodology is relevant to both marked and unsigned augmentations. We propose three equipment executions of the rough multiplier that incorporates one for the unsigned and two for the marked tasks.

S. Vahdat et al., [2] A versatile estimated multiplier, called truncation-and adjusting based adaptable surmised multiplier (TOSAM) is displayed, which diminishes the quantity of incomplete items by truncating every one of the information operands dependent on their driving one-piece position. In the structure, increase is performed by move, include, and little fixed-width duplication tasks bringing about vast upgrades in the vitality utilization and region occupation contrasted with those of the accurate multiplier. To improve the complete exactness, input operands of the duplication part are adjusted to the closest odd number. Since information operands are truncated dependent on their driving one-piece positions, the precision turns out to be pitifully reliant on the width of the information operands and the multiplier winds up adaptable. Higher upgrades in plan parameters (e.g., zone and vitality utilization) can be accomplished as the information operand widths increment.

T. Su et al., [3] this work exhibits a formal way to deal with check multipliers that surmised whole number augmentation by yield truncation. The technique depends on separating polynomial mark of a truncated multiplier utilizing mathematical revising. To effectively register the polynomial mark, a multiplier recreation approach is utilized to build the exact multi-plier from the truncated one. The technique comprises of three essential advances: 1) decide the loads (parallel encoding) of the yield bits; 2) reproduce the truncated multiplier utilizing utilitarian consolidating and re-blend; and 3) develop the polynomial mark of the subsequent circuit.

M. J. Schulte et al., [4] This work presents equipment plans that produce precisely adjusted outcomes for the elements of equal, square-root,  $2/\sup x/$ , and  $\log/\sup 2/(x)$ . These structures utilize polynomial estimate in which the terms in the guess are produced in parallel, and afterward summed by utilizing a multi-operand snake. To decrease the quantity of terms in the estimation, the info interim is divided into subintervals of equivalent size, and diverse coefficients are utilized for each subinterval. The coefficients utilized in the estimate are at first decided dependent on the Chebyshev arrangement guess.

P. Lohray et al., [5] Estimated figuring is one of most appropriate effective information preparing for blunder flexible applications, for example, signal and picture handling, PC vision, AI, information mining and so on. Inexact registering lessens precision which is adequate as an expense of expanding the circuit qualities relies upon the application. Attractive precision is the edge point for controlling the exchange off, among exactness and circuit attributes under the control of the circuit planner. In this work, the adjusting procedure is presented as an effective strategy for controlling this exchange off. In such manner multiplier circuits as a basic structure hinder for registering in a large portion of the processors have been considered for the assessment of the adjusting method proficiency. The effect of the adjusting technique is researched by examination of circuit attributes for three multipliers.

A. Ferozpuri et al., [6] Cycle 1 of the NIST post-quantum cryptography (PQC) institutionalization exertion started on November 30th, 2017. The challenge expects to choose the most encouraging quantum-safe calculations, which are right now secure against vast scale quantum PCs. Multivariate cryptosystems have a place with a promising gathering of PQC conspires and depend on multivariate polynomials over limited fields. Among them are the Lopsided Oil and Vinegar (UOV) and Rainbow signature plans, which have been widely considered since 1999 and 2005, individually. The fundamental favorable position of UOV is high trust in its security, and the weaknesses incorporate expansive key and mark sizes. Rainbow is a multi-layer rendition of UOV that offers better execution, littler keys, and littler marks. This work introduces a rapid FPGA usage for the NIST Cycle 1 PQC accommodation of Rainbow. We talk about a rapid plan that utilizes a parameterized framework solver, which can illuminate a nbyn framework in n clock cycles.

E. Hosseini et al., [7] In this paper, another fast and low power unsigned augmentation structure is proposed: in view of the calculation, the information bits of multiplier are broken into a few littler gatherings of bits and the duplication of them are determined simultaneously. The last result of increase is produced after a few rounds of the little gathering's outcomes accumulation. A 32\*32-piece multiplier as per the structure is planned in 0.18um CMOS process. The general postponement of 32\*32-piece multiplier is amazingly low and is just 2.1ns. The power utilization is 41mW.

| Table-1 Summery of literature survey |           |                |                   |

|--------------------------------------|-----------|----------------|-------------------|

| Sr.                                  | Author    | work           | Outcome           |

| No                                   | Name      |                |                   |

| 1                                    | R.        | ROBA           | Applicable to     |

|                                      | Zendegani | multiplier     | both signed and   |

|                                      |           |                | unsigned          |

|                                      |           |                | multiplications   |

| 2                                    | S. Vahdat | Rounding-based | Improves delay,   |

|                                      |           | scalable       | area, and energy  |

|                                      |           | approximate    | consumption up    |

|                                      |           | multiplier     | to 41%, 90%,      |

|                                      |           |                | and 98%,          |

|                                      |           |                | respectively,     |

| 3                                    | T. Su     | Integer        | Accurate in       |

|                                      |           | multiplication | Deletion, D-      |

|                                      |           | by output      | truncation, and   |

|                                      |           | truncation.    | Truncation with   |

|                                      |           |                | Rounding          |

| 4                                    | M. J.     | Polynomial     | Computational     |

|                                      | Schulte   | approximation  | delay by 5% to    |

|                                      |           |                | 30% and the area  |

|                                      |           |                | requirements by   |

|                                      |           |                | 33% to 77%        |

| 5                                    | P. Lohray | Conventional   | Accuracy for      |

| -                                    |           | Wallace tree   | each range of the |

|                                      |           | accurate       | data with         |

|                                      |           | multiplier     | minimum cost on   |

|                                      |           | _              | the hardware.     |

|                                      |           |                |                   |

| 6                                    | E.        | Low power      | Power             |

|                                      | Hosseini  | unsigned       | consumption is    |

|                                      |           | multiplication | 41mW              |

|                                      |           | structure      |                   |

## III. EXISTING SYSTEM

### A. Multiple Constant Multiplications (MCM)

Channel coefficients all the time stay steady and known from the earlier in signal handling applications. This element has been used to lessen the intricacy of acknowledgment of augmentations. A few structures have been recommended by different analysts for effective acknowledgment of FIR channels (having fixed coefficients) utilizing disseminated number juggling (DA) and various steady increase (MCM) techniques. DA-based plans use query tables (LUTs) to store pre processed outcomes to lessen the computational multifaceted nature. The MCM strategy then again diminishes the quantity of increments required for the acknowledgment of augmentations by normal sub articulation sharing, when a given info is increased with a lot of constants.. It gives throughputadaptable plan as well as improves the territory delay productivity. The induction of square based FIR structure is clear when direct-structure arrangement is utilized, while the transpose structure design does not legitimately bolster square preparing. In any case, to exploit the MCM, FIR channel is required to be acknowledged by transpose structure arrangement. Aside from that, transpose structure structures are inalienably pipelined and expected to offer higher working recurrence to help higher inspecting rate. Disadvantages:

•Separate Multiplier structure for Marked and Unsigned Activity

•More rationale measure

•More Power and delay

#### B. APPROXIMATE MULTIPLIER

The fundamental thought behind the inexact multiplier is to make utilization of the simplicity of activity when the numbers are two to the power n (2n). To expound on the task of the inexact multiplier, first, let us mean the adjusted quantities of the contribution of An and B by Ar and Br, separately. The increase of A by B might be changed as

$A \times B = (Ar - A) \times (Br - B) + Ar \times B + Br \times A - Ar \times Br.$ (1)

The key perception is that the duplications of  $Ar \times Br$ ,  $Ar \times B$ , and  $Br \times A$  might be executed just by the move task. The equipment execution of  $(Ar - A) \times (Br - B)$ , be that as it may, is fairly perplexing. The heaviness of this term in the last outcome, which relies upon contrasts of the precise numbers from their adjusted ones, is commonly little. Subsequently, we propose to exclude this part from (1), streamlining the augmentation activity. Consequently, to play out the duplication procedure, the accompanying articulation is utilized:

### $A \times B \sim = Ar \times B + Br \times A - Ar \times Br.$ (2)

Subsequently, one can play out the increase activity utilizing three move and two expansion/subtraction tasks. In this methodology, the closest qualities for An and B as 2n ought to be resolved. At the point when the estimation of An (or B) is equivalent to the  $3 \times 2p-2$  (where p is a self-assertive positive number bigger than one), it has two closest qualities as 2n with equivalent outright contrasts that are 2p and 2p-1. While the two qualities lead to a similar impact on the exactness of the multiplier, choosing the bigger one (aside from the instance of p = 2) prompts a littler equipment execution for deciding the closest adjusted esteem, and thus, it is considered in this paper. It begins from the way that the numbers as  $3 \times 2p-2$  are considered as couldn't care less in both gathering together and down improving the procedure, and littler rationale articulations might be accomplished in the event that they are utilized in the gathering together. The main special case is for three, which for this situation; two is considered as its closest incentive in the surmised multiplier.

It ought to be noticed that in opposition to the past work where the rough outcome is littler than the careful outcome, the last outcome determined by the RoBA multiplier might be either bigger or littler than the precise outcome relying upon the sizes of Ar and Br contrasted and those of An and B, individually. Note that on the off chance that one of the operands (state An) is littler than its relating adjusted esteem while the other operand (state B) is bigger than its comparing adjusted esteem, at that point the inexact outcome will be bigger than the definite outcome. At long last, it ought to be noticed the benefit of the RoBA multiplier exists just for positive sources of info in light of the fact that in the two's supplement portrayal, the adjusted estimations of negative information sources are not as 2n. Advantages:

•Common Multiplier structure for Marked and Unsigned Activity

- •Less Rationale measure

- •Less Power and delay

#### IV. CONCLUSION

Therefore in this review paper, studied rounding based approximate multiplier for digital signal processing and it is clear that such multiple is capable to give fast multiplication of digital signal. Less time and consume less area. Now, ROBA can be designed and simulated in Xilinx software and verify performance improvement.

#### REFERENCE

- [1]. R. Zendegani, M. Kamal, M. Bahadori, A. Afzali-Kusha and M. Pedram, "RoBA Multiplier: A Rounding-Based Approximate Multiplier for High-Speed yet Energy-Efficient Digital Signal Processing," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 25, no. 2, pp. 393-401, Feb. 2017.

- [2]. S. Vahdat, M. Kamal, A. Afzali-Kusha and M. Pedram, "TOSAM: An Energy-Efficient Truncation- and Rounding-Based Scalable Approximate Multiplier," in *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems.

- [3]. T. Su, C. Yu, A. Yasin and M. Ciesielski, "Formal Verification of Truncated Multipliers Using Algebraic Approach and Re-Synthesis," 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, 2017, pp. 415-420

- [4]. M. J. Schulte and E. E. Swartzlander, "Hardware designs for exactly rounded elementary functions," in *IEEE Transactions on Computers*, vol. 43, no. 8, pp. 964-973, Aug. 1994.

- [5]. P. Lohray, S. Gali, S. Rangisetti and T. Nikoubin, "Rounding Technique Analysis for Power-Area & Energy Efficient Approximate Multiplier Design," 2019 IEEE 9th Annual Computing and Communication Workshop and

*Conference (CCWC)*, Las Vegas, NV, USA, 2019, pp. 0420-0425.

- [6]. A. Ferozpuri and K. Gaj, "High-speed FPGA Implementation of the NIST Round 1 Rainbow Signature Scheme," 2018 International Conference on ReConFigurable Computing and FPGAs (ReConFig), Cancun, Mexico, 2018, pp. 1-8.

- [7]. E. Hosseini, M. Mousazadeh and A. Amini, "High-Speed 32\*32 bit Multiplier in 0.18um CMOS Process," 2018 25th International Conference "Mixed Design of Integrated Circuits and System" (MIXDES), Gdynia, 2018, pp. 154-159.

- [8]. I. Hatai, I. Chakrabarti and S. Banerjee, "A Computationally Efficient Reconfigurable Constant Multiplication Architecture Based on CSD Decoded Vertical–Horizontal Common Sub-Expression Elimination Algorithm," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 1, pp. 130-140, Jan. 2018.

- [9]. R. DiCecco, L. Sun and P. Chow, "FPGA-based training of convolutional neural networks with a reduced precision floating-point library," 2017 International Conference on Field Programmable Technology (ICFPT), Melbourne, VIC, 2017, pp. 239-242.

- [10]. T. Su, C. Yu, A. Yasin and M. Ciesielski, "Formal Verification of Truncated Multipliers Using Algebraic Approach and Re-Synthesis," 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, 2017, pp. 415-420.

- [11]. A. Alavian and M. C. Rotkowitz, "Improving ADMM-based optimization of Mixed Integer objectives," 2017 51st Annual Conference on Information Sciences and Systems (CISS), Baltimore, MD, 2017, pp. 1-6.

- [12]. D. De Caro, E. Napoli, D. Esposito, G. Castellano, N. Petra and A. G. M. Strollo, "Minimizing Coefficients Wordlength for Piecewise-Polynomial Hardware Function Evaluation With Exact or Faithful Rounding," in *IEEE Transactions* on Circuits and Systems I: Regular Papers, vol. 64, no. 5, pp. 1187-1200, May 2017.