# A Review of True Single Phase Clocking Based Digital Circuit Design

Iram Khan M.Tech Scholar,VLSI Dept. of ECE SISTec, Bhopal (M.P.) Prof. Vaibhav Jindal Assistant Professor Dept. of ECE SISTec, Bhopal (M.P.) Dr. Paresh Rawat HOD Dept. of ECE SISTec, Bhopal (M.P.)

*Abstract*—True single-phase clock (TSPC) rationale has discovered broad use in digital design. Initially as a fast topology, the TSPC structure likewise devours less power and involves less region than different techniques. In flip-flop design just a single transistor is being clocked by short heartbeat prepare which is known as True Single Phase Clocking (TSPC) flip-flop. In this paper, considering designs of positive edge activated True Single Phase Clocking Flip-flop is done. As True Single Phase Clocking (TSPC) flip-flop design has little region and low power utilization. Also, it tends to be utilized in different applications like digital VLSI clocking framework, chip, cushions and so forth. The investigation for different flip-flops for power dissemination and spread delay has been done at various foundries.

Keywords- TSPC, VLSI, Flip-Flop, Clock

\*\*\*\*\*

#### I. INTRODUCTION

The true single-phase clock (TSPC) is regular unique flip-flop which plays out the flip-flop task with little power and at high speeds. Flip-flops are the essential building square of the information way structure. They consider the capacity of information, prepared by combinational circuit and synchronization of task at a given clock recurrence. They are the principal building square of the digital hardware frameworks utilized in PCs and numerous different kinds of frameworks. Flip flop can be either basic or clocked; basic gadgets are known as hooks. A lock is level delicate, and mostly utilized as capacity component. What's more, clocked gadgets are known as flipflop. Flip-flop is edge delicate means their yield just changes on a single kind of clock edge (positive or negative going edge). Flip-Flop is an electronic circuit that stores the sensible condition of at least one information input signal in light of a clocking beat. They are regularly utilized in computational circuits to work in chosen groupings amid repeating clock interims to get and keep up information temporarily period adequate for different circuits inside a framework to additionally process information. Information is put away in flip-flop at each rising and falling edge of clock signal with the goal that it very well may be connected as contributions to other combinational or successive circuits, such flip-flops that store information on rising or falling edge of clock are alluded as single edge activated flip flops and the flip-flops that store information on both the rising and falling edge of a clock beat are alluded as twofold edge activated flipflops. The power utilization of the FFs utilized in a regular digital framework design, alongside that of clock dissemination systems, comprises as high as 20% - 45% of the aggregate framework control. FF designs are in this way basic to the power utilization execution of the framework design and may likewise significantly affect the chip zone. FF designs

IJRITCC | November 2018, Available @ http://www.ijritcc.org

experience persistent enhancement with the advances in new process innovation. Particular application requests, for example, fast, low power, and low voltage additionally call for new FF designs. Albeit various FF designs have been created, late design emphases have changed bit by bit from ultrahighspeed flipping to a great degree low-control activities. Notwithstanding the exchanging power, the spillage control utilization ought to be diminished. The design is additionally anticipated that would work legitimately for voltage settings underneath the ostensible voltage. In this work, a low-control FF design meeting these necessities is examined. Brief remarks on the current FF designs are exhibited first. A transmission-door based FF (TGFF) is apparently the most broadly utilized FF as of now. One conceivable disadvantage of this design is the unreasonable remaining burden on the clock signal where integral signals are required. The outcome is the nearness of an impressive unique power notwithstanding when the information exchanging action is low. As of late, true single-phase clocking (TSPC) FF designs have been produced with the goal of bringing down the clock signal stacking.

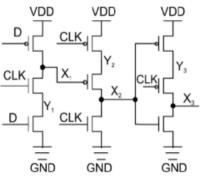

Figure 1: Flip Flop Structure using CMOS

This is typically accomplished through circuit disentanglement. Cross-coupled set– reset (SR) locks are utilized in lieu of the TG-based hook to help single-clock-phase tasks. Deteriorate or topologically compacted SR locks are embraced to bring down the circuit intricacy. This design pursues the standard of TSPC tasks to reduce the clock signal stacking. Both rationale structure decrease and transistor advancement plans are connected to upgrade the design.

#### II. LITERATURE REVIEW

An ultralow-control true single-phase clocking flip-flop (FF) design accomplished utilizing just 19 transistors is proposed. The design pursues an ace slave-type rationale structure and highlights a half and half rationale design containing both static-CMOS rationale and corresponding pass-transistor rationale. In the design, a rationale structure decrease plot is utilized to lessen the quantity of transistors for accomplishing high power and delay execution. In spite of its circuit effortlessness, no inward hubs are left skimming amid the activity to stay away from spillage control utilization. In this design, a virtual VDD design procedure, which encourages a quicker state progress in the slave hook, is conceived to upgrade time execution. In circuit execution, transistor sizes are upgraded concerning the powerdelay item (PDP). A TSMC 90-nm CMOS process was chosen as the execution innovation. In this work, the execution levels of seven FF designs were looked at. The planning parameters of each FF were first portrayed. Post-format recreation results showed that the proposed design exceeded expectations in different execution files, for example, PDP, clock-to-Q delay, normal power utilization, and spillage control utilization. In addition, the design was resolved to have the littlest format territory. Contrasted and the traditional transmission-entryway based FF design, the PDP enhancement in the proposed design was up to 63.5% (at 12.5% exchanging movement) and the region sparing was roughly 10%. Advance reenactments on process corners, supply voltage settings, and working frequencies were directed to consider the design reliability.[1]

A D flipflop is an essential component in rationale design. The creator shows a D flipflop execution. Not at all like a conventional usage in which two correlative D hooks are associated in arrangement, the exhibited circuit depends on a single phase of precharged course differential voltage switch rationale (CVSL). The principle favorable circumstances of the D flipflop are that it has a true single phase clocking plan, i.e. no clock reversal signal is required, has a low clock stack capacitance, and is without glitch and race free[2]

Multi-threshold CMOS (MTCMOS) control gating is a design procedure in which a power gating transistor is associated between the rationale transistors and either power or ground, accordingly making a virtual supply rail or virtual ground rail, individually. Power gating transistor measuring, change (rest mode to dynamic mode) current, impede and progress time are design issues for power gating design. The utilization of intensity gating design results in the delay overhead in the dynamic mode. In the event that both nMOS and pMOS rest transistor are utilized in power gating, delay overhead will increment. This work proposes the design technique for diminishing the delay of the rationale circuits amid dynamic mode. This procedure restricts the most extreme estimation of progress current to a predefined esteem and kills cut off. Examination results indicate 16.83% decrease in the delay.[3]

#### III. EXISTING TECHNIQUES

# 3.1 VARIABLE THRESHOLD CMOS (VTCMOS) TECHNIQUE

In factor threshold CMOS (VTCMOS) system, the substrate predisposition voltage is progressively changed to control the threshold voltage of MOS transistors. As opposed to utilizing numerous threshold voltage transistors, a VTCMOS circuit characteristically utilizes low threshold voltage transistors, and the substrate inclination voltages of the nMOS and pMOS transistors are created by the variable substrate predisposition control circuit.

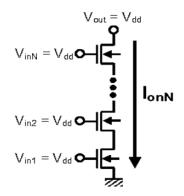

Figure 2: A CMOS inverter circuit using VTCMOS

At the point when the inverter circuit is working in its dynamic mode, the substrate inclination voltage of the nMOS transistor is VBn = 0V and the substrate predisposition voltage of the pMOS transistor is VBp = VDD. In this way the transistors in the circuit don't encounter anyone impact. The circuit works with low-control scattering (because of a low VDD) and a high exchanging pace (because of a low VTH). At the point when the circuit is in the backup mode, the substrate predisposition control circuit produces a lower substrate inclination voltage for the nMOS transistor and a higher substrate inclination voltage for the pMOS transistor. Thus, the sizes of the threshold voltages (VTHn and VTHp) increment in the backup mode because of the body impact. Since the subthreshold spillage current drops exponentially with expanding threshold voltage, the spillage control dispersal in the reserve state can be altogether diminished with

this circuit design method. Be that as it may, with innovation scaling, the viability of VTCMOS strategy decreases as the channel length winds up littler, or the VTH esteems are brought down. Additionally, this strategy is characteristically more risky for unwavering quality since the high voltage over the oxide diminishes the lifetime of the gadget.

# 3.2 MULTI-THRESHOLD CMOS (MTCMOS) TECHNIQUE

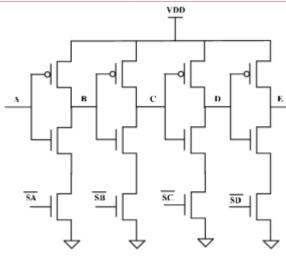

Multi-threshold CMOS is an exceptionally compelling circuit system to diminish the spillage current of a rationale circuit in the backup mode (Mutoh et al. 1995). In this procedure, low VTH transistors are utilized to design the rationale circuit for which the exchanging speed is fundamental and high VTH transistors (additionally called rest transistors) are utilized to viably segregate the rationale circuit from VDD and GND in the backup state and along these lines adequately lessen the reserve subthreshold spillage control dispersal. The circuit structure of MTCMOS circuit system is appeared in Figure 3. In this strategy, a high-threshold voltage pMOS transistor is embedded between the power supply and the rationale circuit (low VTH) and a high-threshold voltage nMOS transistor is put between the rationale circuit (low VTH) and the ground. Amid dynamic method of activity, the high threshold voltage MOS transistors (rest transistors) are turned on, in this manner encouraging typical task of the circuit as there exists an immediate way from the yield to the ground and VDD. Amid backup mode, these high VTH transistors are killed, making a virtual power supply and a virtual ground rail and hence removing the rationale circuit from the power supply and the ground. Since high VTH transistors working in the backup mode powers the rationale circuit to go in rest state, so these high VTH transistors are otherwise called rest transistors. In this method both low and high threshold voltage MOS transistors are manufactured on a single chip. From a visual point of view, these high VTH rest transistors go about as a current entryway to the designed circuit (low VTH). Thus, this strategy is additionally alluded to as power gating circuit method. The subthreshold spillage control dispersal in the reserve mode can be altogether diminished by utilizing this circuit design procedure. The fundamental detriment in utilizing this system is the expansion in circuit delay because of the utilization of high VTH MOS transistors (rest transistors). Additionally this procedure still experiences higher reserve subthreshold spillage control scattering, which can turn into an extraordinary issue for convenient frameworks, for example, burst mode compose frameworks, where a bigger measure of this spillage control is disseminated amid the long reserve time frame.

Figure 3: A CMOS logic circuit using MTCMOS

# 3.3 SLEEPY KEEPER TECHNIQUE

In tired attendant strategy an extra high threshold voltage nMOS transistor is associated in parallel with the rest pMOS transistor (high VTH rest pMOS transistor) and an extra high threshold voltage pMOS transistor is associated in parallel with the rest nMOS transistor (high VTH rest nMOS transistor). In rest or backup method of activity, rest transistors are in cutoff state. In this way, when rest signal is dynamic, at that point the high threshold voltage nMOS transistor associated in parallel with the rest pMOS transistor gives a way to interface the pullup system of the CMOS rationale circuit with the power supply and the high threshold voltage pMOS transistor associated in parallel with the rest nMOS transistor gives a way to associate the pulldown system of the CMOS rationale circuit with ground. The real preferred standpoint in utilizing this circuit method is that it holds the circuit present state even in the rest mode. This circuit system likewise gives a noteworthy technique to diminish the subthreshold spillage control dispersal.

### 3.4 SUPER CUTOFF CMOS (SCCMOS) TECHNIQUE

Another procedure, or, in other words to MTCMOS method, is the super cutoff CMOS system, rest transistors are underdriven (or over-driven) when in backup mode. Subthreshold spillage current in the backup mode lessens exponentially because of the use of positive and negative door voltages to rest pMOS and rest nMOS transistors separately. The key distinction between this procedure and the MTCMOS strategy lies in the utilization of rest transistors of having a similar low threshold voltage as that of the designed rationale circuit. The upside of such a plan is, to the point that the extra delay acquainted due with the utilization of high VTH rest MOS transistors, as in MTCMOS procedure, can be additionally lessened amid the dynamic method of task in light of the fact that the transistor gets higher drive current (because of the utilization of low VTH rest MOS transistors). Amid dynamic method of task, rest transistors (low VTH) are turned on, in this way encouraging ordinary activity of the circuit as there exists an immediate way from the yield to the ground and VDD. Amid backup mode, rest transistors are totally cutoff because of the utilization of positive and negative entryway voltages (VGS1 and VGS2) to rest pMOS transistor and rest nMOS transistor separately. Consequently the sub threshold spillage current in the reserve mode lessens exponentially. Anyway the principle impediment in utilizing this method is the utilization of an unpredictable controller circuit for giving both negative and positive entryway voltages to totally kill rest nMOS and rest pMOS transistors separately.

### IV. CONCLUSION

A proficient design of edge activated True Single Phase Clocking (TSPC) flip-flop is displayed. From the recreation results plainly edge activated TSPC D flip-flop with less transistors is having less power utilization. In the design of 19, 18 and 5 transistors studied and find TSPC DFF just a single transistor being clocked and the clock is having short heartbeat prepare. From the outcome it is presumed that when innovation is downsized proliferation delay declines and static power dissipation increments. These TSPC flip-flop is having slightest power delay item (PDP) subsequently and it gives best execution. There are a few points of interest with this sort of circuit as it disposes of the clock skew caused by various clock phases and clock signals are produced off-chip which fundamentally spares chip territory and power utilization. Besides, it very well may be utilized in a few applications like level converters, microchips, clocking framework counter.

### REFERENCE

- [1] J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.

- [2] W. Wang, S. Jia, Z. Wang, T. Pan and Y. Wang, "Low Voltage Dual-Modulus Frequency Divider Based on Extended True Single-Phase Clock Logic," 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, 2018, pp. 1-2.

- [3] N. Kim and J. M. Rabaey, "A 3.1–10.6-GHz 57-Bands CMOS Frequency Synthesizer for UWB-Based Cognitive Radios," in IEEE Transactions on Microwave Theory and Techniques, vol. 66, no. 9, pp. 4134-4146, Sept. 2018.

- [4] Priyanka Sharma and Rajesh Mehra" TRUE SINGLE PHASE CLOCKING BASED FLIP-FLOP DESIGN USING DIFFERENT FOUNDRIES "International Journal of Advances in Engineering & Technology, May, 2014. ©IJAET ISSN: 22311963 352 Vol. 7, Issue 2, pp. 352-358

- [5] C. G. Huang, "Implementation of true single-phase clock D flipflops," in Electronics Letters, vol. 30, no. 17, pp. 1373-1374, 18 Aug. 2014

- [6] S. Hemantha, A. Dhawan and H. Kar, "Multi-threshold CMOS design for low power digital circuits," TENCON 2008 - 2008 IEEE Region 10 Conference, Hyderabad, 2008, pp. 1-5.

- [7] Yu-Cheng Fan, Yi-Cheng Liu, "High-Speed Memory Cell Circuit Design Based on Low-Temperature Poly Silicon TFT Technology", Magnetics IEEE Transactions on, vol. 45, no. 5, pp. 2320-2323, 2009.

- [8] Sohan Purohit, Marco Lanuzza, Stefania Perri, Pasquale Corsonello, Martin Margala, "Design-Space Exploration of Energy-Delay-Area Efficient Coarse-Grain Reconfigurable Datapath", VLSI Design 2009 22nd International Conference on, pp. 45-50, 2009.

- [9] R. Bai, D. Sylvester, "Analysis and design of levelconverting flip-flops for dual-V/sub integrated circuits", System-on-Chip 2003. Proceedings. International Symposium on, pp. 151-154, 2003.