# HDL Design for Peta Hertz Clock based 2e<sup>31</sup>-1 Peta Bits Per Second (Pbps) PRBS Design for Ultra High Speed Applications/Products

Prof P. N. V. M Sastry<sup>1</sup>

Dean- IT EDA Software

R&D-CELL & ECE

Dept.

J.B.R.E.C

shastrypnvm@gmail.com

Prof. A. Rajaiah<sup>2</sup>

I/C-M.Tech(V.L.S.I)

E.C.E. De.pt.

J.B.R.E.C

rajua1999@gmail.com

Prof. Dr. D. N. Rao<sup>4</sup>

Principal

J.B.R.E.C

principal\_jbr@yahoo.

Dr S. Vathsal<sup>3</sup>

Dean- R&D& HODEEE,

J.B.I.E.T

svathsal@gmail.com

Abstract-The Design is mainly Intended for High Speed Random Frequency Carrier Wave Generator of Peta Bits Per Second P.b.p.s (Peta Bits Per Second) Data Rate 2e<sup>31</sup>-1 Tapped PRBS Pattern Sequence. The P.R.B.S is Designed by using L.F.S.R Linear Feed Back Shift Register & XOR Gate with Specific Tapping Points as per C.C.I.T.T I.T.U Standards. R.T.L Design Architecture Implemented by using V.H.D.L &/Verilog H.D.L, Programming & Debugging Done by using Spartan III F.P.G.A Kit. Transmission done through this carrier frequency. Propagation Carrier Done either Serially / Parallel lines I/O.

**Keywords:** C.C.I.T.T – Consulting Committee for International Telegraph & Telecom, I.T.U – International Telecom Unit, R.T.L- Register Transfer Level, L.F.S.R-Linear Feedback Shift Register, V.H.D.L- Very High Speed Integrated Circuit Hardware Description Language, P.R.B.S-Pseudo Random Binary Sequence. Verilog-Verification Logic.

\*\*\*\*

#### 1.0 INTRODUCTION

In Modern Hi-tech Communication Engineering world, High Speed based Portable Communication System Hardware & Software Products Came to the market, speed is an important factor and is in terms of Giga bits per second for all Hi-tech Real time Smart Computing Portable wireless Communication System Software products like Cloud Computing ,wireless Internet Data Packets Transceivers Computing, Tablets, Pocket Mobile Multimedia Systems, Note Book Computers, Routers, N.O.Cs, Network-Cards/Racks, Wi-Fi, GiFi, Wimax, G.P.S, G.S.M, Q.C.D.M. ATranceivers. For that purpose ,I Designed Peta Bits Per Second, P.b.p.s High Speed P.R.B.S is Pseudo Random Binary Sequence Frequency Generators, Generate & Received Random Frequency Data in the form of Random frequency numbers of different speed w.r.t specific data tapping sequence points for both signal & carrier wave generation. P.R.B.S Generators, Receivers, Transceivers Designed for HiFi Wireless Internet Data Packets Computing and Cloud Computing etc. Transmission, Reception of Data is in the RANDOM Sense,

This P.R.B.S Generator, Receiver is Designed for Identification property of Different Tapped P.R.B.S Sequences like 7,10,15,23,31 at a Clock carrier frequency speed of Pbps(Peta Bits Per Second) .The Length of PRBS sequence is 2<sup>L</sup>-1. 2<sup>L</sup>-1 times repeated the sequences. this is mainly suit for multiple users to transmit and received data in accurate time for very long distance communications like GPS Data Acquisition, GSM Communication Systems, Wi-Fi, Gi-Fi, LTE, Wireless O.F.D.M.A, C.D.M.A, Q.C.D.M.A Computing, wireless internet computing, cloud computing etc because of Ultra High speed Communication Rate in terms Tbps. All these P.R.B.S L.F.S.R Sequences are designed by tapping different points according to I.T.U O.150,O.151,O.152 Standards. This P.R.B.S Design Consists of Multiplexer, PRBS Registers of different tapped sequence points, Clock Frequency Generators of Pbps Speed. The Advantages of these P.R.B.S Generators having In Built Checkers, Bit Error Rate Detection & Correction by using PRBS Checkers. these are simply Linear Polynomial Checkers & C.R.C

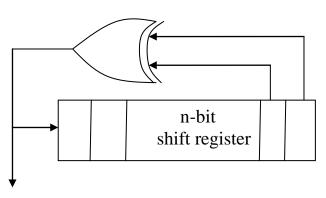

**FIG[1]:** Fibonacci (many-to-one) realization of LFSR with minimum number of taps and XOR gate in its feedback

#### ISSN: 2321-8169 5256 - 5258

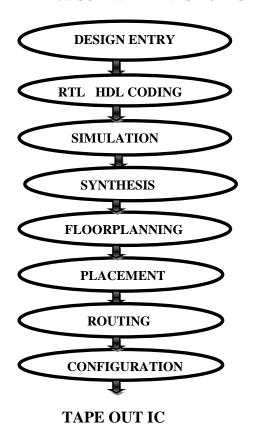

#### 3.0 SOFTWARE – VLSI IC DESIGN FLOW

FIG[3]: VLSI Design Flow Chart

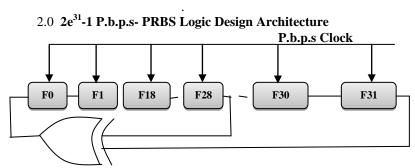

## B. 2e<sup>31</sup>-1 P.b.p.s PRBS RTL Schematic

C. 2e31-1 P.b.p.s PRBS DESIGN PLACED Report

# **4.0** DESIGN FLOW REPORTS OF $2e^{31}$ -1 Pbps PRBS DESIGN

# A. 2e<sup>31</sup>-1 P.b.p.s PRBS DESIGN RTL BLOCK

D. 2e<sup>31</sup>-1 P.b.p.s PRBS DESIGN ROUTED Report

E . SIMULATION WAVE FORM RESULTS -2e<sup>31</sup>-1 P.b.p.s PRBS

### 7.0 CONCLUSION

Designed High Speed Random Carrier Frequency Generator 2e<sup>31</sup>-1 Pbps PRBS for Ultra High Speed Wireless Communication **Engineering Products**

Prof.P.N.V.M Sastry Currently working with a Capacity of Dean- I.T E.D.A Software Industry CELL & R&D CELL &

ECE DEPARTMENT, He Did Master Degree In Science- M.S Electronics, Under Department Of Sciences, College Of Science & Technology AU -1998.Did PG Diploma In V.L.S.I Design ,I.S.O.U.K.A.S Certified From V3 Logic Pvt Ltd, Bangalore-2001, Did M.Tech (ECE) From I.A.S.E Deemed University-2005. Currently Pursuing (Ph.D)-E.C.E(V.L.S.I) , J.N.T.U Hyderabad -2012 , Over Past 17 years of Rich Professional Experience with Reputed IT Software Industrial MNC's, Corporate -CYIENT (INFOTECH), ISITECH as a world top keen IT Industrial Software Specialist - World Top Engineering Team Leader(Level 6) Eng-Eng- HCM Electronics Vertical & Sr. Program Manager -EDS,BT,NON BT Embedded Software ,Avionics & Automotive Hi-tech Software Engineering Verticals & Departments & I/C M.F.G Hi-tech Eng.Software Vertical , Program Lead – Embedded & VLSI & Engineering Delivery Manager - IT Semiconductor Software Engineering Vertical ,at ISiTECH , also worked with Govt R&D, Industrial Organizations, Academic Institutions of Comparative Designations & Rolls . His Areas Of Interest are V.L.S.I - V.H.D.L, Veirilog H.D.L, A.S.I.C, F.P.G.A & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D, Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, I.T Software M.N.C Board Meetings(Tier1/2 Level MRM-V.P,C.O.O Level), Guided R&D, Industrial, Academic Projects / Products -VLSI-ASIC,FPGA & Embedded & Embedded, V.L.S.I Software Project &/ Program Management & Also Coordinated Various In House & External IT Project Workshops & Trainings At CYIENT( INFOTECH) as a I/C- MFG Eng Software Vertical, Also Participated Various National R&D Workshops, FESTS, FDP's &Seminars. Recently He Published Various 31 International Journals of Reputed Journals and Conferences also Certified Conference Chairs - ,I.T.C. I.D.E.S- MC GRAWHILL EDUCATION-Chennai & I.E.E.E -C.S.N.T.-Gwalior & Best Paper Award On behalf of Exa Hertz Wi-Fi Router A.S.I.C Paper at I.S.S.R.D-I.C.S.C.D SANDIEGO, U.S.A., Accepted Journal at High Reputed Journal - Mitteilungen Klosternburg Weiner Strasse, AUSTRIA, Europe etc.), and also J.M.E.S.T – Germany.

Ambati. RAJAIAH, pursuing Ph.D. from JNTU UNIVERSITY, currently working as an Assoc. Professor, in the Department of Electronics and communication Engineering, Joginpally B.R Engineering and Strategic Engineering and Strateneeringcollege, Moinabad, Rangareddy Dist, Hyderabad, Telangana, India. He studied B.E (ECE) from C.B.I.T, Osmania University, Hyderabad and M.Tech (Systems& Signal Processing) from, J.N.T.U, Hyderabad, A.P., India. He is having 13 years of work experience in Academics, Teaching, and Industry & Research. He participated and presented research papers in both national and international conferences, seminars and workshops; also published 7 research paper in international peer reviewed journals.

ISSN: 2321-8169

5256 - 5258

Dr. D.N Rao B.Tech, M.E, Ph.D, principal of JBREC, Hyderabad. His carrier spans nearly three decades in the field of teaching, administration, R&D, and other diversified in-depth experience in academics and administration. He has actively involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international conferences. He is Currently approved reviewer of IASTED International journals and conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities

Dr.Vathsal -PhD ,I.I.S.C, Currently working as a Professor & Dean- R&D & EEE, JBIET, He Obtained PhD from I.I.S.C, Bangalore, also Did Post Doctoral Research in DFVLR, Germany and NASA Goddard Space Flight Centre, USA, and also he worked with keen Designations Scientist E,F,G from Reputed Govt R&D Industry Organizations over past years and closely worked with Dr.A.P.J Abdul Kalam He Published lot of various national, international journals & conferences, He guiding 5 PhD Students from Various universities. He Got Prestigious awarded as a Noble Son of India