# Implementation of Fast, Low Power and Area Efficient Carry Select Adder

Priya H. Agrawal

Department of Electronics Engineering

Priyadarshini College of Engineering

Nagpur, India

pia123agrawal@gmail.com

Prashant R. Rothe

Department of Electronics Engineering

Priyadarshini College of Engineering

Nagpur, India

p rrothe@rediffmail.com

**Abstract**— One of the fastest adders is Carry Select Adder (CSLA) and it perform fast arithmetic functions in many data processing processors. A conventional CSLA has less carry propagation delay (CPD) than ripple carry adder (RCA). A compromise between RCA and carry look ahead adder is provided by Carry select adder.

For the CSLA new logic is proposed by reducing redundant logic operations present in conventional CSLA. In the proposed scheme, schedule the carry select (CS) operation before final sum calculation. which is different approach from the conventional. Two carry words ( $c_{in} = 0$  and 1) bit patterns and fixed  $c_{in}$  bits use for generation units and CS logic optimization. Optimized logic units is used to obtain an efficient CSLA design. The proposed work is carried out using Modelsim SE 6.3f and Quatus2 software.

Keywords- Adder, arithmetic unit, low power, CSLA, RCA, low delay, area efficient.

\*\*\*\*

#### I. INTRODUCTION

In VLSI system design high speed, area and power efficient data path logic systems are the major areas of research. With the increasing the necessity of portable systems, area occupancy plays a vital role in the design of Integrated Circuits. Basic building blocks of any processor or data path application are Adders. The critical path in adder design is carry generation. In arithmetic logic unit and in other parts of the processor adders are used to calculate table, indices addresses and similar applications. In multipliers, high speed integrated circuits and digital signal processing various algorithms like FFT, IIR and FIR are executed by adders.

There are several types of adder designs available (RCA, CLAA, CSA, CSA). Ripple carry adder have compact design but high computation time. Carry look ahead adder have increase in area but gives fast result. Compromise between Carry look ahead adder and RCA is given by Carry select adder. There is a scope for reducing the delay and area in the structure of CSLA. Carry select adder have less area and power consumption. Power consumption of data path is get reduced with the reduction of area in adder. Partial sum and carry is generate by using carry input C<sub>in</sub>=0 and C<sub>in</sub>=1 and the final sum and carry are selected by using the multiplexers. In digital adders the time required by the carry to propagate through the adder limits the speed of addition.

## II. LITERATURE SURVEY

The largest systems in VLSI system design is design of low delay, area and power. Different researchers have done work on this and few are summarised below. M.chithra and G.omkareswari [2] proposed that a simple approach to reduce the area and power of CSLA architecture. Ripple carry adder is used to implement a carry select adder (CSLA). By comparison with the regular 128-bit CSLA the proposed design 128-bit CSLA has reduced more delay and area. This work offers advantage in the reduction of area and total power by reducing number of gates. The modified CSLA architecture is low area, low power, simple and efficient for VLSI hardware implementation

Pandu Ranga Rao and Priyanka Halle [3] proposed that use of a simple and an efficient gate level modification reduces area and delay of the CSLA. By using this concept 16, 32, 64 and 128 bit SQRT CSLA is improved. Area and delay of proposed design is reduced when compared with the regular SQRT CSLA. Replace the RCA with BEC in the structure reduces the number of gates. In modified SQRT CSLA the delay is reduced to a great extent.

Damarla Paradhasaradhi and Prof. K.Anusudha [4] proposed that an area efficient carry select adder by sharing the common Boolean logic term (CBL). The correct output is selected according to the logic states of the carry in signal through the multiplexer. Based on this modification a new architecture has been developed using Binary to Excess-1 converter (BEC). The proposed architecture has reduced area and delay when compared with the regular SQRT CSLA architecture. An 8-bit inputs area efficient square-root carry select adder is proposed. The reduced number of gates gives advantage in the reduction of area.

Sajesh Kumar U and Mohamed Salih K K [6] proposed the carry select adder configuration and parallel adder approach for

the implementation of fast adder for the efficient implementation of parallel adder with optimized area and propagation delay for FPGA applications.

Fig.1 The proposed approach

#### III. PROPOSE WORK

An RCA–RCA configuration is used in a conventional carry select adder (CSLA) and a pair of output carry bit and sum words bit is generated. The Carry Select Adder comes in the category of conditional sum adder. Conditional sum adder works on some condition.

CSLA have a lesser delay than Ripple Carry Adders. Carry Select Adder is used while working with smaller number of bits. Different logic formulation is used to reduce delay and area so that speed is increased. The expression of full adder are listed below.

$$SUM = A \ xor \ B \ xor \ C \tag{1}$$

$$CARRY = (A.B) + (B.C) + (C.A)$$

(2)

Fig.1 shows Internal architecture of 4 bit carry select adder. Two ripple carry adders are multiplexed together. Sum and carry are calculated by assuming input carry as 1 and 0 prior the input carry comes. When actual carry input arrives, the actual calculated values of sum and carry are selected using a multiplexer. Behavioral modeling is used for code.

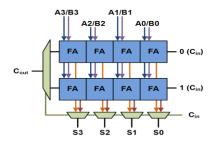

Fig.2 shows basic building block of a carry select adder of block size 4. A ripple carry adder layout is simple.  $C_{out}$  is the output carry and s0, s1, s2, s3 are the sum produce. Structural modeling is used for code.

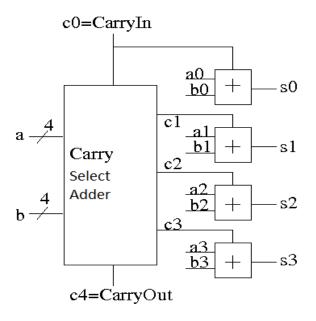

Fig.3 shows 4 bit CSLA where c0 and 4 bit a and b input is applied. s0, s1, s2, s3 are the sum produce by using adder and c4 is output carry produce. Mixed modeling is used for code.

Fig.2 Basic block of a CSLA of size 4

Fig.3 4 bit CSLA

## IV. RESULT

The area analysis, time analysis and power analysis for propose approach, basic building blocks of CSLA of size 4, 4 bit CSLA are shown in following figures.

| Flow Status                        | Successful - Sat Mar 21 19:07:12 2015        |

|------------------------------------|----------------------------------------------|

| Quartus II Version                 | 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition |

| Revision Name                      | csa                                          |

| Top-level Entity Name              | csa                                          |

| Family                             | Cyclone II                                   |

| Device                             | EP2C20F484C7                                 |

| Timing Models                      | Final                                        |

| Met timing requirements            | Yes                                          |

| Total logic elements               | 7 / 18,752 ( < 1 % )                         |

| Total combinational functions      | 7 / 18,752 ( < 1 % )                         |

| Dedicated logic registers          | 0 / 18,752 ( 0 % )                           |

| Total registers                    | 0                                            |

| Total pins                         | 20 / 315 (6%)                                |

| Total virtual pins                 | 0                                            |

| Total memory bits                  | 0 / 239,616 ( 0 % )                          |

| Embedded Multiplier 9-bit elements | 0 / 52 (0 %)                                 |

| Total PLLs                         | 0/4(0%)                                      |

Fig.4 Area analysis for the proposed approach

| Ī | Tir | Timing Analyzer Summary      |       |                  |                |      |       |               |             |                 |

|---|-----|------------------------------|-------|------------------|----------------|------|-------|---------------|-------------|-----------------|

|   |     | Туре                         | Slack | Required<br>Time | Actual<br>Time | From | То    | From<br>Clock | To<br>Clock | Failed<br>Paths |

|   | 1   | Worst-case tpd               | N/A   | None             | 13.439 ns      |      | y1[0] |               |             | 0               |

|   | 2   | Total number of failed paths |       |                  |                |      |       |               |             | 0               |

Fig.5 Time analysis for proposed approach

| PowerPlay Power Analyzer Status        | Successful - Sat Mar 21 19:05:14 2015            |

|----------------------------------------|--------------------------------------------------|

| Quartus II Version                     | 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition     |

| Revision Name                          | csa                                              |

| Top-level Entity Name                  | csa                                              |

| Family                                 | Cyclone II                                       |

| Device                                 | EP2C20F484C7                                     |

| Power Models                           | Final                                            |

| Total Thermal Power Dissipation        | 69.01 mW                                         |

| Core Dynamic Thermal Power Dissipation | 0.00 mW                                          |

| Core Static Thermal Power Dissipation  | 47.35 mW                                         |

| I/O Thermal Power Dissipation          | 21.66 mW                                         |

| Power Estimation Confidence            | Low: user provided insufficient toggle rate data |

|                                        |                                                  |

Fig.6 Power analysis for proposed approach.

| Flow Status                        | Successful - Sat Mar 21 20:00:28 2015        |

|------------------------------------|----------------------------------------------|

| Quartus II Version                 | 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition |

| Revision Name                      | csa2                                         |

| Top-level Entity Name              | csa2                                         |

| Family                             | Cyclone II                                   |

| Device                             | EP2C20F484C7                                 |

| Timing Models                      | Final                                        |

| Met timing requirements            | Yes                                          |

| Total logic elements               | 13 / 18,752 ( < 1 % )                        |

| Total combinational functions      | 13 / 18,752 ( < 1 % )                        |

| Dedicated logic registers          | 0 / 18,752 (0 %)                             |

| Total registers                    | 0                                            |

| Total pins                         | 14/315(4%)                                   |

| Total virtual pins                 | 0                                            |

| Total memory bits                  | 0 / 239,616 ( 0 % )                          |

| Embedded Multiplier 9-bit elements | 0/52(0%)                                     |

| Total PLLs                         | 0/4(0%)                                      |

|                                    |                                              |

Fig.7 Area analysis for the for basic block of a CSLA of size 4

| Ti | Timing Analyzer Summary      |       |                  |                |      |           |               |             |                 |

|----|------------------------------|-------|------------------|----------------|------|-----------|---------------|-------------|-----------------|

|    | Туре                         | Slack | Required<br>Time | Actual<br>Time | From | То        | From<br>Clock | To<br>Clock | Failed<br>Paths |

| 1  | Worst-case tpd               | N/A   | None             | 14.169 ns      |      | outsum[3] |               |             | 0               |

| 2  | Total number of failed paths |       |                  |                |      |           |               |             | 0               |

Fig.8 Time analysis for basic block of a CSLA of size 4

| PowerPlay Power Analyzer Status        | Successful - Sat Mar 21 20:02:15 2015            |

|----------------------------------------|--------------------------------------------------|

| Quartus II Version                     | 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition     |

| Revision Name                          | csa2                                             |

| Top-level Entity Name                  | csa2                                             |

| Family                                 | Cyclone II                                       |

| Device                                 | EP2C20F484C7                                     |

| Power Models                           | Final                                            |

| Total Thermal Power Dissipation        | 68.33 mW                                         |

| Core Dynamic Thermal Power Dissipation | 0.00 mW                                          |

| Core Static Thermal Power Dissipation  | 47.35 mW                                         |

| I/O Thermal Power Dissipation          | 20.98 mW                                         |

| Power Estimation Confidence            | Low: user provided insufficient toggle rate data |

Fig.9 Power analysis for basic block of a CSLA of size 4

Successful - Sat Mar 21 20:14:59 2015 Flow Status Quartus II Versio 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition Revision Name carry\_select\_adder carry\_select\_adder Top-level Entity Name Family Device EP2C20F484C7 Timing Models Met timing requirements Yes 9 / 18,752 ( < 1 % ) 9 / 18,752 ( < 1 % ) Total logic elements Total combinational functions Dedicated logic registers 0 / 18,752 (0%) Total registers Total pins

Total virtual pins 14 / 315 (4%) 0 / 239,616 (0%) Total memory bits Total PLLs 0/4(0%)

Fig.10 Area analysis for 4 bit CSLA

| Т | Timing Analyzer Summary      |       |                  |                |      |      |               |             |                 |

|---|------------------------------|-------|------------------|----------------|------|------|---------------|-------------|-----------------|

|   | Туре                         | Slack | Required<br>Time | Actual<br>Time | From | To   | From<br>Clock | To<br>Clock | Failed<br>Paths |

| 1 | Worst-case tpd               | N/A   | None             | 14.695 ns      | y[2] | z[3] |               |             | 0               |

| 2 | Total number of failed paths |       |                  |                |      |      |               |             | 0               |

Fig.11 Time analysis for 4 bit CSLA

| PowerPlay Power Analyzer Status        | Successful - Sat Mar 21 20:21:09 2015            |

|----------------------------------------|--------------------------------------------------|

| Quartus II Version                     | 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition     |

| Revision Name                          | carry_select_adder                               |

| Top-level Entity Name                  | carry_select_adder                               |

| Family                                 | Cyclone II                                       |

| Device                                 | EP2C20F484C7                                     |

| Power Models                           | Final                                            |

| Total Thermal Power Dissipation        | 68.33 mW                                         |

| Core Dynamic Thermal Power Dissipation | 0.00 mW                                          |

| Core Static Thermal Power Dissipation  | 47.35 mW                                         |

| I/O Thermal Power Dissipation          | 20.98 mW                                         |

| Power Estimation Confidence            | Low: user provided insufficient toggle rate data |

|                                        |                                                  |

Fig.12 Power analysis for 4 bit CSLA

## V. CONCLUSION

Power, delay and area are the important factors that determine the performance of any circuit in VLSI design process. The disadvantage of regular CSLA is more power consumption and large area. The reduced number of gates offers the advantage in the reduction of area and total power.

### REFERENCES

- [1] Shmuel Wimer, Amnon Stanislavsky "Energy efficient hybrid adder architecture" INTEGRATION, the VLSI journal 48 109–115, 2015.

- [2] M.chithra and G.omkareswari "128-Bit Carry Select Adder Having Less Area And Delay" International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol.2, Issue 7, July 2013.

- [3] Pandu Ranga Rao and Priyanka Halle "An Efficient Carry Select Adder with Less Delay and Reduced Area Application" International Journal of Engineering Trends and Technology (IJETT) Volume 4, Issue 9, Sep 2013.

- [4] Damarla Paradhasaradhi, Prof. K. Anusudha "An Area Efficient Enhanced SQRT Carry Select Adder" D Paradhasaradhi et al Int. Journal of Engineering Research and Applications ISSN: 2248-9622, Vol. 3, Issue 6, pp.876-880, Nov-Dec 2013.

- [5] Veena V Nair "Modified Low-Power and Area-Efficient Carry Select Adder using D-Latch" International Journal of Engineering Science and Innovative Technology (IJESIT) Volume 2, Issue 4, July 2013.

- [6] Sajesh Kumar U, Mohamed Salih K K "Efficient Carry Select Adder Design for FPGA Implementation" International Conference on Communication Technology and System Design 2011.

- [7] Massimo Alioto, Gaetano Palumbo, Massimo Poli "Optimized design of parallel carry-select adders" Integration, the VLSI journal 44, 62–74, 2011.

- [8] H.T.Vergos, C.Efstathiou "Efficient modulo2<sup>n</sup> +1 adder architectures" Integration, the VLSI journal 42, pp149–157, 2009.

- [9] K. K. Parhi "VLSI Digital Signal Processing", New York, NY, USA, Wiley, 1998.

- [10] Jayaram Bhasker "A VHDL Primer" P T R Prentice Hall Englewood Cliffs, New Jersey 07632

- [11] M. Moris Mano "Digital Design", Pearson Education, 3<sup>rd</sup> edition 2002.